#### (19) 日本国特許庁(JP)

# 再 公 表 特 許(A1)

(11) 国際公開番号

W02011/036770

発行日 平成25年2月14日 (2013.2.14)

(43) 国際公開日 平成23年3月31日(2011.3.31)

| (51) Int.Cl. |         |           | F I  |        |         | テーマコード    | (参考)     |

|--------------|---------|-----------|------|--------|---------|-----------|----------|

| HO1L         | 29/82   | (2006.01) | HO1L | 29/82  | Z       | 5F064     |          |

| нозк         | 19/0944 | (2006.01) | нозк | 19/094 | A       | 5F092     |          |

| нозк         | 3/037   | (2006.01) | нозк | 3/037  | Z       | 5 J O 4 3 |          |

| HO1L         | 21/82   | (2006.01) | HO1L | 21/82  | A       | 51056     |          |

| HO1L         | 43/08   | (2006.01) | HO1L | 43/08  | Z       |           |          |

|              |         |           |      | 審査討    | 青求 有 予何 | 備審査請求 未請求 | (全 22 頁) |

特願2011-532848 (P2011-532848) 出願番号 (21) 国際出願番号 PCT/JP2009/066678 平成21年9月25日 (2009.9.25) (22) 国際出願日 AP (BW, GH, GM, KE, LS, MW, MZ, NA, SD, (81) 指定国 SL, SZ, TZ, UG, ZM, ZW), EA (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), EP (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, F1, FR, GB, GR, HR, HU , IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, S K, SM, TR), OA (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE , SN, TD, TG) , AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC , EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, I S. JP. KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE , PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, S Y, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW

(71) 出願人 000003078 株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100117787

弁理士 勝沼 宏仁

(74)代理人 100082991

弁理士 佐藤 泰和

弁理士 川崎 康

(74)代理人 100103263

(74)代理人 100107582

弁理士 関根

(74)代理人 100118843

弁理士 赤岡 明

最終頁に続く

(54) 【発明の名称】メモリ機能付きパストランジスタ回路およびこのパストランジスタ回路を有するスイッチングボックス回路

#### (57)【要約】

[課題]高集積化および低消費電力化が可能なパストランジスタ回路を提供する。

[解決手段]第1の信号線に接続される第1の入出力端子24と、第2の信号線に接続される第2の入出力端子26と、一端が第1の電源に接続される第1の素子10 aと、第1の素子の他端に一端が接続され、他端が第2の電源に接続される第2の素子10bと、第1の素子の他端にソースが接続され、ゲートに第1の制御信号を受ける第1のトランジスタ10cと、第1のトランジスタのドレインにゲートが接続され、第1の入出力端子にソースが接続され、第2の入出力端子にドレインが接続され、第2の入出力端子にドレインが接続され、第2のトランジスタ10dと、を備え、第1および第2の素子のうちの少なくとも一方が不揮発性メモリ素子であり、他方がMOSFETである。

[図1]

#### 【特許請求の範囲】

### 【請求項1】

第1の信号線に接続される第1の入出力端子と、

第2の信号線に接続される第2の入出力端子と、

一端が第1の電源に接続される第1の素子と、

前記第1の素子の他端に一端が接続され、他端が第2の電源に接続される第2の素子と

前記第1の素子の他端にソースが接続され、ゲートに第1の制御信号を受ける第1のトランジスタと、

前記第1のトランジスタのドレインにゲートが接続され、前記第1の入出力端子にソースが接続され、前記第2の入出力端子にドレインが接続された第2のトランジスタと、

を備え、前記第1および第2の素子のうちの少なくとも一方が不揮発性メモリ素子であり、他方がMOSFETであることを特徴とするパストランジスタ回路。

## 【請求項2】

前記不揮発性メモリ素子は、スピンMOSFETであることを特徴とする請求項1記載のパストランジスタ回路。

#### 【請求項3】

前記第1の素子はp型MOSFETであり、前記第2の素子はn型スピンMOSFETであることを特徴とする請求項2記載のパストランジスタ回路。

## 【請求項4】

前記第1の素子はp型スピンMOSFETであり、前記第2の素子はn型MOSFETであることを特徴とする請求項2記載のパストランジスタ回路。

#### 【請求項5】

前記第1の素子はp型スピンMOSFETであり、前記第2の素子はn型スピンMOSFETであることを特徴とする請求項2記載のパストランジスタ回路。

#### 【請求項6】

前記第1および第2のトランジスタは、n型MOSFETであることを特徴とする請求項3記載のパストランジスタ回路。

## 【請求項7】

前記第1および第2のトランジスタは、p型MOSFETであることを特徴とする請求項3記載のパストランジスタ回路。

## 【請求項8】

前記第1の素子はMT」素子であり、前記第2の素子はMOSFETであることを特徴とする請求項1記載のパストランジスタ回路。

## 【請求項9】

請求項1記載のパストランジスタ回路と、前記第1および第2の信号線と、を備えていること特徴とするスイッチングボックス回路。

【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、メモリ機能付きパストランジスタ回路およびこのパストランジスタ回路を有するスイッチングボックス回路に関する。

#### 【背景技術】

## [0002]

近年、電子のスピン自由度を利用したスピンエレクトロニクスデバイスの研究開発が盛んに行われている。トンネル磁気抵抗効果(TMR)を基礎とする研究開発が盛んに行われ、磁気ランダムアクセスメモリ(MRAM)やハードディスクドライブ(HDD)の再生ヘッドなどに応用されるに至っている。さらに、半導体と磁性体とを結合したスピントランジスタが注目されている。

## [0003]

50

10

20

30

現在の半導体技術を基にしたリコンフィギャラブル論理回路として、FPGA(Field Programmable Gate Array)と呼ばれる集積回路がある。FPGAは、内部のSRAMに情報を蓄え、このメモリに記憶された情報に基づいて、リコンフィギュラブル論理回路の論理と結線とを制御することができる。このように、ソフトウエアで論理を変更できるため、ハードウエアを作製後に回路の修正が可能となる。複雑化する集積回路を短納期で安価に実現する手段として、近年急速に伸びている。

[0004]

FPGAの中で、スイッチングボックス回路が数多く使用されている。スイッチングボックス回路は、4方向から来る信号線の結線方法を記憶させておき、信号線の入力と出力および信号線間の結線と断線を決定する回路である。このスイッチングボックス回路を有する回路は、メモリを書き換えることにより任意の結線方法を実現できる。

[0005]

スイッチングボックス回路内ではメモリの出力を、パストランジスタ回路に接続する。 パストランジスタ回路はスイッチの役割を果たし、メモリに記憶された情報に基づいて、 信号線間の結線と断線を決める(例えば、非特許文献 1 参照)。

【先行技術文献】

【非特許文献】

[0006]

【非特許文献 1】Design of Interconnection Networks for Programmable Logic, Guy Lemieux and David Lewis, Kluwer Academic Publishers, ISBN:1-4020-7700-9, Chapter6, pages 101-139

【発明の概要】

【発明が解決しようとする課題】

[0007]

半導体のCMOS技術によってスイッチングボックス回路を作製する場合、情報を記憶するメモリとしてSRAMが用いられる。このため、素子数が多くなってしまう。このスイッチボックス回路は、大量のSRAMを使用しているため、動作をしていないときでもリーク電流による消費電力が大きくなってしまう。そのため、高集積化しにくい回路となっている。

[ 0 0 0 8 ]

また、スイッチングボックス回路で多くのパストランジスタ回路を使用するため回路規模は非常に大きくなってしまい、高集積化を妨げる要因の一つとなっている。

[0009]

更に、SRAMは電源を切ると情報が失われてしまう揮発性メモリであるため、電源投入をする毎に外部メモリに蓄えていた情報を書き込む必要がある。このため、電源投入時に手間と時間がかかるという課題がある。

[0010]

また、電源切断時に情報を蓄えておくための外部メモリを確保しておく必要があり、外部メモリのために消費電力および容積が必要になるという課題がある。このため、システム全体での高集積化および低消費電力化を妨げる要因の一つとなっている。

[0011]

本発明は、上記事情を考慮してなされたものであって、高集積化および低消費電力化が可能なパストランジスタ回路およびスイッチングボックス回路を提供することを目的とする。

【課題を解決するための手段】

[0012]

本発明の第1の態様によるパストランジスタ回路は、第1の信号線に接続される第1の 入出力端子と、第2の信号線に接続される第2の入出力端子と、一端が第1の電源に接続 される第1の素子と、前記第1の素子の他端に一端が接続され、他端が第2の電源に接続 される第2の素子と、前記第1の素子の他端にソースが接続され、ゲートに第1の制御信 10

20

30

40

号を受ける第1のトランジスタと、前記第1のトランジスタのドレインにゲートが接続され、前記第1の入出力端子にソースが接続され、前記第2の入出力端子にドレインが接続された第2のトランジスタと、を備え、前記第1および第2の素子のうちの少なくとも一方が不揮発性メモリ素子であり、他方がMOSFETであることを特徴とする。

[0013]

また、本発明の第2の態様によるスイッチングボックス回路は、第1の態様によるパストランジスタ回路と、前記第1および第2の信号線と、を備えていること特徴とする。

## 【発明の効果】

[0014]

本発明によれば、高集積化および低消費電力化が可能なパストランジスタ回路およびスイッチングボックス回路を提供することができる。

【図面の簡単な説明】

[ 0 0 1 5 ]

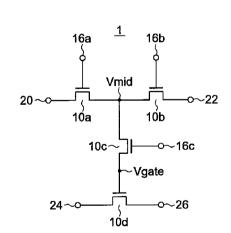

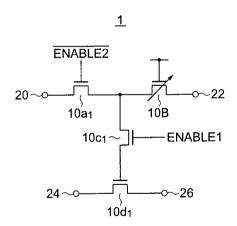

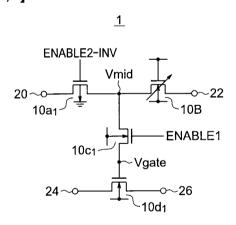

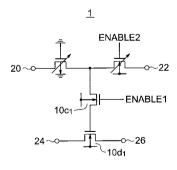

- 【図1】一実施形態のパストランジスタ回路を示す回路図。

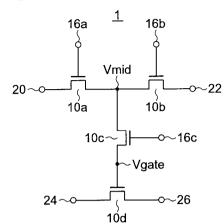

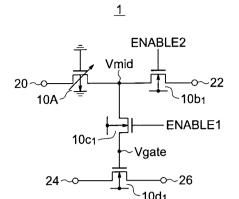

- 【図2】一実施形態のパストランジスタ回路を示す回路図。

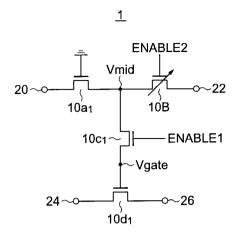

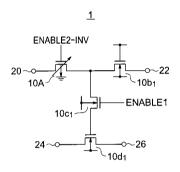

- 【図3】一実施形態のパストランジスタ回路を示す回路図。

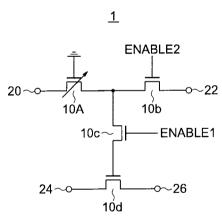

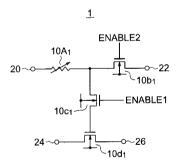

- 【図4】一実施形態のパストランジスタ回路を示す回路図。

- 【図5】第1実施形態のパストランジスタ回路を示す回路図。

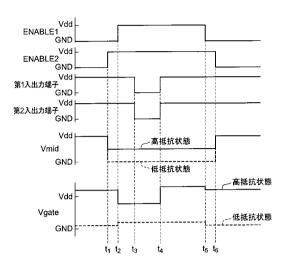

- 【図6A】第1実施形態のパストランジスタ回路の動作を説明する波形図。

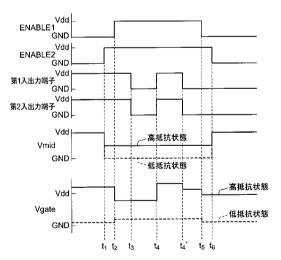

- 【図6B】第1実施形態のパストランジスタ回路の動作を説明する波形図。

- 【図7】第2実施形態のパストランジスタ回路を示す回路図。

- 【図8】第3実施形態のパストランジスタ回路を示す回路図。

- 【 図 9 】 第 3 実 施 形 態 の 変 形 例 に よ る パ ス ト ラ ン ジ ス タ 回 路 を 示 す 回 路 図 。

- 【図10】第4実施形態のパストランジスタ回路を示す回路図。

- 【図11】第5実施形態のパストランジスタ回路を示す回路図。

- 【 図 1 2 】 第 5 実 施 形 態 の 変 形 例 に よ る パ ス ト ラ ン ジ ス タ 回 路 を 示 す 回 路 図 。

- 【図13】第6実施形態のパストランジスタ回路を示す回路図。

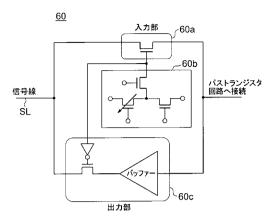

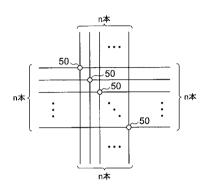

- 【 図 1 4 】 一 実 施 形 態 の ス イ ッ チ ン グ ボ ッ ク ス 回 路 を 示 す 回 路 図 。

- 【図15】入出力部の一具体例を示すブロック図。

- 【図16】一実施形態のスイッチングブロック回路を示す回路図。

【発明を実施するための形態】

[0016]

以下に、本発明の実施形態を、図面を参照して詳細に説明する。ただし、図面は模式的なものであり、各部分の大きさ、各電圧の高さおよび各時間の長さ、部分間の大きさの比率、電圧間の比率、時間の間隔などは現実のものとは異なる。また、図面の相互間においても、同じ部分を指す場合であっても、互いの寸法や比率が異なって示されている部分もある。

[0017]

まず、本発明の実施形態を説明する前に、本発明の各実施形態によるメモリ機能付きパストランジスタ回路の概要について説明する。本発明の各実施形態は、不揮発性メモリ素子を備えたメモリ機能付きパストランジスタ回路である。不揮発性メモリ素子としては、スピンMOSFETまたはMTJ(Magnetic Tunneling Junction)素子が用いられる。スピンMOSFETは、通常のMOSFET構造のソースおよびドレイン電極にそれぞれは、かつメモリ機能を有している。また、MTJ素子は、2つの磁性体間にトンネルバリアを挟んだ構造を有しており、2つの磁性体の磁化の向きにより抵抗値が異なり、メモリアを挟んだ構造を有しており、2つの磁性体の磁化の向きにより抵抗値が異なり、メモリ機能を有している。このため、スピンMOSFETまたはMTJ素子を用いると、少なFETおよびMTJ素子は、強磁性体を用いてメモリ機能を実現しかつ不揮発性であるため、電源投入する毎にスイッチングボックス回路のメモリへの書き込みをしなくてすむ。そ

10

20

30

40

10

20

30

40

50

て、このパストランジスタ回路は内部に不揮発性メモリを有しているため、動作していない場合は電源を切断することが可能になり、低消費電力なスイッチングボックス回路を構築できる。

## [0018]

スピンMOSFETは、2つの強磁性体の互いの磁化の向きにより、2つの強磁性体間の抵抗値が異なる。このスピンMOSFETにおけるソースおよびドレイン電極の磁性体の磁化の向きは略平行か略反平行のいずれかになっており、2つの強磁性体間の抵抗も低抵抗と高抵抗のいずれかの状態になっている。MTJ素子も同様に、2つの強磁性体の互いの磁化の向きにより、2つの強磁性体間の抵抗値が異なる。2つの強磁性体間の抵抗値において、低抵抗の場合を低抵抗状態、高抵抗の場合を高抵抗状態と呼ぶ。

## [0019]

本発明の一実施形態によるメモリ機能付きパストランジスタ回路を図1に示す。このパストランジスタ回路1は、4個のトランジスタ10a、10b、10c、10dを備えている。トランジスタ10aは、ソースが第1電源20に接続され、ゲートが第1端子16aに接続され、ドレインがトランジスタ10bのドレインに接続されている。トランジスタ10a、10bのドレインに接続されている。トランジスタ10a、10bのドレインに接続されている。トランジスタ10a、10bは直列に接続されている。トランジスタ10a、10bのドレインに接続されている。トランジスタ10a、10bのドレインに接続され、ゲートが第3端子16cに接続され、ドレインがトランジスタ10dのゲートに接続されている。トランジスタ10dは、ソースが第1入出力端子24に接続され、ドレインが第2入出力端子26に接続されている。第1乃至第3端子16a、16b、16cにはタイミング信号(制御信号)、電源電圧Vdd、もしくは基準電圧GNDが印加される。

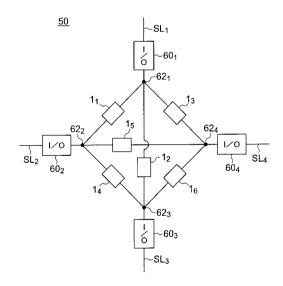

#### [0020]

次に、本発明の一実施形態におけるパストランジスタ回路 1 を備えたスイッチングボックス回路の一具体例を図 1 4 に示す。一般に、スイッチングボックス回路は、 4 方向からの信号線が合流する領域において、結線と断線を決定する回路である。この具体例のスイッチングボックス回路 5 0 は、 4 本の信号線 S L  $_1$  、 S L  $_2$  、 S L  $_3$  、 S L  $_4$  の結線と断線を決定するものであって、 4 個の入出力部60 $_1$  ~ 6 0  $_4$  と、 4 個の接続ノード62 $_1$  ~ 6 2  $_4$  と、 6 個のパストランジスタ回路 1  $_1$  ~ 1  $_6$  とを有している。パストランジスタ回路 1  $_1$  ~ 1  $_6$  は、それぞれ本発明の一実施形態におけるパストランジスタ回路 1 と同じ構成となっている。

#### [0021]

4 本の信号線 S L <sub>1</sub> 、 S L <sub>2</sub> 、 S L <sub>3</sub> 、 S L <sub>4</sub> は、 4 方向に 1 本ずつ配置される構成と なっている。図14においては、上方には信号線SL┒が、左方には信号線SLっが、下 方には信号線SLュが、右方には信号線SLュが配置される。各信号線SL;(i=1, ・・・4)に入出力部60,が接続される。各入出力部60,(i=1,・・・4)に接 続 ノード 6 2 <sub>i</sub> が 接 続 される。 パストランジスタ回 路 1 <sub>1</sub> は、 第 1 および第 2 入出力端子 の一方の入出力端子が接続ノード62 』に接続され、他方の入出力端子が接続ノード62 っに接続される。パストランジスタ回路1っは、第1および第2入出力端子の一方の入出 力端子が接続ノード62 1 に接続され、他方の入出力端子が接続ノード62 3 に接続され る。パストランジスタ回路 1 。は、第 1 および第 2 入出力端子の一方の入出力端子が接続 ノード62 <sub>1</sub>に接続され、他方の入出力端子が接続ノード62 ₄ に接続される。パストラ ン ジ ス タ 回 路 1 ¼ は 、 第 1 お よ び 第 2 入 出 力 端 子 の 一 方 の 入 出 力 端 子 が 接 続 ノ ー ド 6 2 🤈 に接続され、他方の入出力端子が接続ノード62ぇに接続される。パストランジスタ回路 1、は、第1および第2入出力端子の一方の入出力端子が接続ノード62っに接続され、 他方の入出力端子が接続ノード624に接続される。パストランジスタ回路16は、第1 お よ び 第 2 入 出 力 端 子 の 一 方 の 入 出 力 端 子 が 接 続 ノ ー ド 6 2 ₃ に 接 続 さ れ 、 他 方 の 入 出 力 端子が接続ノード62ょに接続される。したがって、任意の一つの信号線は、入出力部、 接続ノード、パストランジスタ回路、接続ノード、入出力部を通して他の任意の信号線と

接続することができる。例えば、信号線SL╷は、入出力部60╷、接続ノード62╷、パストランジスタ回路1╷、接続ノード62<sub>2</sub>、入出力部60<sub>2</sub>からなるルートを通して信号線SLっと接続される。

#### [0022]

次に、上記スイッチングボックス回路50の入出力部60の一具体例を図15に示す。この具体例の入出力部60は、入力部60a、メモリ部60b、および出力部60cを備えている。メモリ部60bは、図15に示すように、1個の不揮発性記憶素子(スピンMOSFET)と、2個のトランジスタとからなるパストランジスタ回路を有している。そして、入力部60aと出力部60cのいずれか一方だけが導通となるように接続される。

## [ 0 0 2 3 ]

したがって、パストランジスタ回路1がスイッチングボックス回路50に用いられた場合には、第1入出力端子24は、入出力部を介して、4方向の内のある一方向における一本の信号線に接続され、第2入出力端子26は、他の入出力部を介して他の方向における一本の信号線に接続される。すなわち、トランジスタ10dがパストランジスタとなる。このパストランジスタのオンまたはオフ状態に応じて、信号線間の結線と断線が決定される。

#### [0024]

図1に示す本発明の一実施形態において、トランジスタ10aをp型MOSFET10a1に置き換え、トランジスタ10bをn型スピンMOSFET10Bに置き換え、トランジスタ10c、10dをn型MOSFET10c1、10d1にそれぞれ置き換えたパストランジスタ回路1を図2に示す。このパストランジスタ回路1においては、第1電源20に電源電圧Vddを印加し、第2電源22に基準電圧GNDを印加する。更に、トランジスタ10a1のゲートに基準電圧GNDが印加され、スピンMOSFET10Bのゲートおよびトランジスタ10c1のゲートには制御信号ENABLE2およびENABLE1がそれぞれ入力される。

#### [0025]

本発明の一実施形態のパストランジスタ回路 1 には、充電期間と動作期間を持つ。このパストランジスタ回路を論理動作させる前に、充電期間を設けて動作の安定化を行う。そして、動作期間の間に論理動作を行う。

## [0026]

次に、本発明の一実施形態のパストランジスタ回路1の動作を説明する。本明細書においては、Hレベルは電源電圧Vddの半分以上の電圧とし、Lレベルは電源電圧Vddの半分未満の電圧とする。

## [0027]

## 充電期間中の動作

ENABLE2信号がHレベルに達したときにトランジスタ10a1とスピンMOSFET10Bに直列に電流が流れる。トランジスタ10a1とスピンMOSFET10Bとの間のノードの電圧Vmidは、トランジスタ10a1とスピンMOSFET10Bの抵抗値により決まる。また、スピンMOSFET10Bの抵抗状態により、電圧Vmidが異なる。トランジスタ10d1のゲート電圧をVgateとする。

## [0028]

今、ENABLE1信号をHレベルとする。ENBALE1信号がHレベルでは、トランジスタ10d1のソースとドレイン間が導通しているため、電圧Vmidと電圧Vgateが略同電圧となる。このとき、第1入出力端子24もしくは第2入出力端子26のいずれか、もしくは第1入出力端子24と第2入出力端子26の両方の端子を、充電期間の間にLレベルにする。トランジスタ10d1のゲートに充電される電荷量はスピンMOSFET10Bの抵抗状態に依存する。

## [0029]

スピンMOSFET10Bの抵抗状態が高抵抗状態の場合、トランジスタ10d1のゲートに正電荷が充電される。スピンMOSFET10Bの抵抗状態が低抵抗状態の場合、

10

20

30

40

トランジスタ10d1のゲートに正電荷が充電されないか、もしくは少ない量の正電荷だけが充電される。第1入出力端子24もしくは第2入出力端子26を、充電が完了して電圧Vgateが略一定電圧になった後に、Hレベルにする。その後、ENABLE1信号およびENABLE2信号をそれぞれLレベルにする。

## [0030]

#### 動作期間中の動作

ENABLE1信号がLレベルなので、トランジスタ10c1は非導通状態となっている。トランジスタ10d1のゲートに十分な正電荷が充電されていれば、第1入出力端子24と第2入出力端子26は導通状態となり、第1入出力端子24と第2入出力端子26が結線された状態となる。これに対して、トランジスタ10d1のゲートに十分な正電荷が充電されていなければ、第1入出力端子24と第2入出力端子26は非導通状態となり、第1入出力端子24と第2入出力端子26は非導通状態となり、第1入出力端子24と第2入出力端子26が断線の状態となる。このように論理動作の直前に充電期間の動作を行う。トランジスタ10d1のゲートは、トランジスタ10c1のリーク電流により長い時間が経つと充電される。リーク電流により充電される前に、充電期間の動作を行う。

#### [0031]

本発明の一実施形態では、図1に示すトランジスタ10 aをp型MOSFETに置き換え、トランジスタ10 bをn型スピンMOSFET10 Bに置き換えた。しかし、図3に示す本発明の他の実施形態のようにトランジスタ10 aをp型スピンMOSFET10 Aに置き換え、トランジスタ10 bをn型MOSFET10 b1に置き換えてもよい。

#### [0032]

また、上記実施形態では、トランジスタ10cおよびトランジスタ10dをn型MOS FETとしたが、p型MOSFETを用いても構わない。

#### [0033]

また上記実施形態では、トランジスタ10 a 1 のゲートに基準電圧 G N D 、スピン M O S F E T 1 0 B のゲートに E N A B L E 2 信号を印加したが、図 4 に示すようにトランジスタ10 a 1 のゲートに E N A B L E 2 の反転信号を入力し、スピン M O S F E T 1 0 B のゲートに電源電圧 V d d を印加しても構わない。

## [0034]

また、上記実施形態では、メモリ機能付き素子としてスピンMOSFETを用いたが、MTJ(強磁性トンネル接合)素子を用いても構わない。この場合は、制御信号が不要となる。

#### [0035]

SRAMを用いた従来のメモリ付きパストランジスタ回路は7個の素子(SRAMが6個の素子+1個のパストランジスタ)を使用するのに対し、本発明の一実施形態では4個の素子でメモリ機能付きパストランジスタ回路を実現できる。また、SRAMを用いた従来のメモリ付きパストランジスタ回路は、揮発性メモリであるため電源を切断できないが、本発明の一実施形態では論理動作をしていないときは電源を切断できるため、低消費電力のメモリ機能付きパストランジスタ回路が実現できる。

#### [0036]

以上説明したように、本発明の一実施形態によれば、少ない素子数でメモリ機能付きパストランジスタ回路を実現することができる。これにより、小面積のメモリ機能付きパストランジスタ回路を実現することが可能となり、小面積のスイッチングボックス回路を得ることができる。また、本発明の一実施形態によるメモリ機能付きパストランジスタ回路を用いれば、低消費電力のスイッチングボックス回路を構成することができる。したがって、本発明の一実施形態によるメモリ機能付きパストランジスタ回路を用いれば、高集積でかつ低消費電力のリコンフィギャラブル論理回路を実現することができる。

#### [0037]

また、上記スイッチングボックス回路を用いて、例えば、図16に示すスイッチングブロック回路80を構成することができる。このスイッチングブロック回路80は、縦方向

10

20

30

40

10

20

30

40

50

と横方向にn(1)本の信号線が配置され、縦方向の信号線と横方向の信号線との交差点に例えば図14に示すスイッチングボックス回路50を設けた構成となっている。このように構成されたスイッチングブロック回路80も低消費電力となる。

#### [0038]

## (第1実施形態)

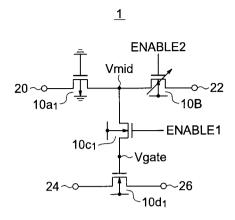

本発明の第1実施形態によるメモリ機能付きパストランジスタ回路を図5に示す。この実施形態のパストランジスタ回路1は、図1に示すパストランジスタ回路1において、トランジスタ10aをp型MOSFET10a1(以下、トランジスタ10a1ともいう)に置き換え、トランジスタ10bをn型スピンMOSFET10B(以下、トランジスタ10c1(以下、トランジスタ10c1ともいう)に置き換え、トランジスタ10dをn型MOSFET10c1(以下、トランジスタ10c1ともいう)に置き換えた構成となっている。トランジスタ10a1のゲートには基準電圧GNDが印加され、トランジスタ10Bのゲートには制御信号ENABLE2が入力し、トランジスタ10c1のゲートには制御信号ENABLE1が入力する。

#### [0039]

次に、本実施形態のパストランジスタ回路1の動作について図6Aを参照して説明する。図6Aは、制御信号ENABLE1、ENABLE2、第1および第2入出力端子24、26、および電圧Vmid、Vgateの波形図である。ここで、電圧Vmidはトランジスタ10a1のドレインと、トランジスタ10Bのドレインの接続ノードの電圧であり、電圧Vgateはトランジスタ10d1のゲートの電圧である。

図 6 A の電圧 V m i d の波形および電圧 V g a t e の波形において、スピンMOSFET10Bが高抵抗状態の場合を実線で示し、低抵抗状態の場合を破線で示す。時刻 t 1 において、ENABLE2信号をLレベルからHレベルにする。すると、電圧 V m i d はHレベルから、スピンMOSFET10Bの抵抗状態に応じたレベルとなる。スピンMOSFET10Bが高抵抗状態のときは V d d と G N D との間のレベルとなり、スピンMOSFET10Bが低抵抗状態のときはLレベルになる。

#### [0040]

## [0041]

次に、時刻  $t_3$  において、第 1 および第 2 入出力端子 2 4 、 2 6 の電圧を H レベルから L レベルにする。なお、図 6 A では、時刻  $t_3$  以前の第 1 入出力端子 2 4 および第 2 入出力端子 2 6 の電圧が H レベルとなっているが、L レベルでも構わない。また、第 1 および第 2 入出力端子 2 4 、 2 6 の電圧を L レベルにする時刻  $t_3$  は、図 6 A では時刻  $t_2$  の後であるが、時刻  $t_3$  から時刻  $t_4$  の間に、トランジスタ 1 0 d 1 のゲートに電荷が充電、もしくはゲートから電荷が放電される。

## [0042]

値電圧を引いた値と同程度のため、トランジスタ10c1にはほとんど電流が流れない。 しかしトランジスタ10d1のゲートには正電荷が充電されているため、時刻t4の直後 に、電圧Vgateが電源電圧Vdd以上の高電圧となる。

#### [0043]

次に、時刻  $t_5$  において、制御信号 E N A B L E 1 を H レベルから L レベルにする。すると、電圧 V g a t e は、その値が少し小さくなる。時刻  $t_2$  から時刻  $t_5$  の間は、電圧 V m i d、 V g a t e がスピン M O S F E T 1 0 B の抵抗状態に依存する。なお、時刻  $t_5$  は、時刻  $t_4$  より後とする。時刻  $t_5$  において、電圧 V g a t e は低くなるが、電圧低下量は非常に小さいため、パストランジスタ 1 0 d 1 の動作には影響を与えない。制御信号 E N A B L E 1 が L レベルになると、トランジスタ 1 0 c 1 は非導通状態になり、電圧 V m i d が変動しても、電圧 V g a t e i に小さな変動しか与えない。

[0044]

次に、時刻t。において、制御信号ENABLE2をHレベルからLレベルにする。制御信号ENABLE1がLレベルであるため、トランジスタ10c1は非導通状態である。トランジスタ10d1のゲートに充電された電荷は、トランジスタ10d1のゲートに保持される。なお、時刻t。は、時刻t。と略同時、もしくは時刻t。より後とする。

[0045]

上記の動作を充電動作と呼び、上記の動作を行う期間を充電期間と呼ぶ。図6Aでは、 時刻t<sub>1</sub>から時刻t<sub>6</sub>までが充電期間となる。

[0046]

図6Aに示すように、上記の動作の後では、電圧VgateはスピンMOSFET10Bの高抵抗状態と低抵抗状態で大きな差がある。高抵抗状態では電圧Vgateが非常に高く、低抵抗状態では電圧Vgateが低い。

[ 0 0 4 7 ]

スピンMOSFET10Bが高抵抗状態のときは、トランジスタ10d1のゲートに十分な電荷が充電されているため、トランジスタ10d1は導通状態となり、第1および第 2入出力端子24、26は結線された状態となっている。

[0048]

これに対して、スピンMOSFET10Bが低抵抗状態のときは、トランジスタ10d 1のゲートに電荷がほとんど充電されていないため、トランジスタ10d1は非導通状態となり、第1および第2入出力端子24、26は断線された状態となっている。

[0049]

制御信号ENABLE1およびENABLE2がLレベルのときに、本実施形態のメモリ機能付きパストランジスタ回路は論理動作を行う。

[0050]

なお、上記の動作説明では、第1および第2入出力端子の電圧は、時刻  $t_4$  以降は、 H レベルとなっていたが、図6Bに示すように、時刻  $t_4$  と時刻  $t_5$  との間の時刻  $t_4$  'において、 L レベルとしてもよいし、時刻  $t_5$  と時刻  $t_6$  との間に L レベルとしてもよい。

[0051]

スピンMOSFET10Bが低抵抗状態であった場合に、時間が経つと、トランジスタ 10c1のリーク電流により、トランジスタ10d1のゲートに充電され、電圧Vgateがあがる。非常に長い時間が経つと、電圧Vgateはトランジスタ10d1の閾値電圧Vthよりも高くなり、誤動作を引き起こす。誤動作を防ぐために、論理動作を行う直前に充電動作を行うか、もしくは一定間隔毎に充電動作を行うことが好ましい。

[0052]

一定間隔で充電動作を行う場合の充電間隔 c は、トランジスタ10d1のゲートのキャパシタンス成分 C g と、トランジスタ10c1が非導通状態のときのトランジスタ10c1のソースとドレイン間の抵抗 R o f f で決まる。一定間隔で充電動作を行う場合の充電間隔 c は、 c = C g × R o f f / 2 より短いことが必要となる。本実施形態では、

c = 1 0 μ s とした。

10

20

30

40

#### [0053]

スピンMOSFET10Bは不揮発性メモリであるため、本実施形態のメモリ機能付きパストランジスタ回路が論理動作していないときにはメモリ機能付きパストランジスタ回路の電源を切断する。

## [0054]

SRAMを用いた従来のメモリ付きパストランジスタ回路は7個の素子を使用するのに対し、本実施形態では4個の素子でメモリ機能付きパストランジスタ回路を実現できる。また、SRAMを用いた従来のメモリ付きパストランジスタ回路は、揮発性メモリであるため電源を切断できないが、本実施形態では論理動作をしていないときは電源を切断できるため、低消費電力のメモリ機能付きパストランジスタ回路を実現することができる。

[0055]

以上説明したように、本実施形態によれば、少ない素子数でメモリ機能付きパストランジスタ回路を実現することができる。これにより、小面積のメモリ機能付きパストランジスタ回路を実現することが可能となり、小面積のスイッチングボックス回路を得ることができる。

#### [0056]

また、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、低消費電力のスイッチングボックス回路を構成することができる。したがって、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、高集積でかつ低消費電力のリコンフィギャラブル論理回路を実現することができる。

[ 0 0 5 7 ]

## (第2実施形態)

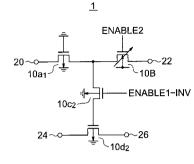

次に、本発明の第2実施形態によるパストランジスタ回路を図7に示す。この実施形態のパストランジスタ回路は、図5に示す第1実施形態において、トランジスタ10a1のゲートに制御信号ENABLE2・INVを入力し、スピンMOSFET10Bのゲートに電源電圧Vddを印加した構成となっている。

#### [0058]

このように構成された本実施形態のパストランジスタ回路において、第1実施形態と同様に、充電動作を行った後に、論理動作を行う。

## [0059]

本実施形態も第1実施形態と同様に、低消費電力のメモリ機能付きパストランジスタ回路を実現することができる。

[0060]

また、少ない素子数でメモリ機能付きパストランジスタ回路を実現することができる。 これにより、小面積のメモリ機能付きパストランジスタ回路を実現することが可能となり 、小面積のスイッチングボックス回路を得ることができる。

[0061]

また、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、低消費電力のスイッチングボックス回路を構成することができる。したがって、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、高集積でかつ低消費電力のリコンフィギャラブル論理回路を実現することができる。

[0062]

## (第3実施形態)

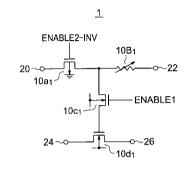

次に、本発明の第3実施形態によるパストランジスタ回路を図8に示す。この実施形態のパストランジスタ回路は、図5に示す第1実施形態において、トランジスタ10a1をp型スピンMOSFET10Aに置き換え、スピンMOSFET10Bをn型MOSFET10b1(以下、トランジスタ10b1ともいう)に置き換えた構成となっている。そして、スピンMOSFET10Aのゲートに基準電圧GNDが印加され、トランジスタ10b1のゲートに制御信号ENABLE2が入力される。

[0063]

10

20

30

50

このように構成された本実施形態のパストランジスタ回路において、第1実施形態と同様に、充電動作を行った後に、論理動作を行う。なお、本実施形態においては、第1実施形態と異なり、p型スピンMOSFET10Aが高抵抗状態の場合に、トランジスタ10d1は非導通状態となり、p型スピンMOSFET10Aが低抵抗状態の場合に、トランジスタ10d1は導通状態となる。

#### [0064]

本実施形態も第1実施形態と同様に、低消費電力のメモリ機能付きパストランジスタ回路を実現することができる。

### [0065]

また、少ない素子数でメモリ機能付きパストランジスタ回路を実現することができる。 これにより、小面積のメモリ機能付きパストランジスタ回路を実現することが可能となり 、小面積のスイッチングボックス回路を得ることができる。

#### [0066]

また、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、低消費電力のスイッチングボックス回路を構成することができる。したがって、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、高集積でかつ低消費電力のリコンフィギャラブル論理回路を実現することができる。

#### [0067]

なお、本実施形態において、図9に示すように、p型スピンMOSFET10Aのゲートに制御信号ENABLE2-INV信号を入力し、トランジスタ10b1のゲートに電源電圧Vddを印加してもかまわない。この図9に示す、本実施形態の変形例によるパストランジスタ回路も、本実施形態と同様の効果を得ることができる。

#### [0068]

#### (第4実施形態)

次に、本発明の第4実施形態によるパストランジスタ回路を図10に示す。この実施形態のパストランジスタ回路は、図5に示す第1実施形態において、n型MOSFET10c1、10d1をp型MOSFET10c2、10d2にそれぞれ置き換え、p型MOSFET10c2のゲートに制御信号ENABLE1の反転信号ENABLE1・INVを入力した構成となっている。

## [0069]

本実施形態のパストランジスタ回路は、第1実施形態と同様に、充電動作を行った後に、論理動作を行う。なお、本実施形態においては、n型スピンMOSFET10Bが高抵抗状態の場合に、p型MOSFET10d2は非導通状態となり、n型スピンMOSFET10Bが低抵抗状態の場合に、p型MOSFET10d2は導通状態となる。

### [0070]

なお、第4実施形態の変形例として、図7、図8、図9に示すパストランジスタ回路において、n型MOSFET10c1、10d1を、それぞれp型MOSFETに置き換え、ENABLE1信号をENABLE1-INV信号に置き換えた構成としてもよい。

#### [0071]

本実施形態およびその変形例も、第1実施形態と同様に、低消費電力のメモリ機能付きパストランジスタ回路を実現することができる。

#### [0072]

また、少ない素子数でメモリ機能付きパストランジスタ回路を実現することができる。 これにより、小面積のメモリ機能付きパストランジスタ回路を実現することが可能となり 、小面積のスイッチングボックス回路を得ることができる。

## [0073]

また、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、低消費電力のスイッチングボックス回路を構成することができる。したがって、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、高集積でかつ低消費電力のリコンフィギャラブル論理回路を実現することができる。

10

20

30

50

#### [0074]

## (第5実施形態)

次に、本発明の第5実施形態によるパストランジスタ回路を図11に示す。この実施形態のパストランジスタ回路は、図5に示す第1実施形態において、スピンMOSFET10BをMTJ(強磁性トンネル接合)素子10B1に置き換え、トランジスタ10a1のゲートに制御信号ENABLE2-INVを入力した構成となっている。MTJ素子10B1は高抵抗状態および低抵抗状態を持ち、抵抗状態は不揮発性である。

### [0075]

本実施形態は第1実施形態と同様に、充電動作を行った後に、論理動作を行う。本実施形態においては、MTJ素子10B1が高抵抗状態の場合に、トランジスタ10d1は導通状態となり、MTJ素子10B1が低抵抗状態の場合に、トランジスタ10d1は非導通状態となる。

## [0076]

なお、第5実施形態の変形例として、図12に示すように、トランジスタ10a1をMT」素子10A1に置き換えるとともにMT」素子10B1をn型MOSFET10b1 に置き換え、トランジスタ10b1のゲートに制御信号ENABLE2を入力するように、構成してもよい。

また、第1乃至第4実施形態およびそれらの変形例において、スピンMOSFETを、 MTJ素子に置き換えてもよい。

#### [0077]

本実施形態も、第1実施形態と同様に、低消費電力のメモリ機能付きパストランジスタ 回路を実現することができる。

#### [0078]

また、少ない素子数でメモリ機能付きパストランジスタ回路を実現することができる。 これにより、小面積のメモリ機能付きパストランジスタ回路を実現することが可能となり 、小面積のスイッチングボックス回路を得ることができる。

### [0079]

また、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、低消費電力のスイッチングボックス回路を構成することができる。したがって、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、高集積でかつ低消費電力のリコンフィギャラブル論理回路を実現することができる。

#### [0800]

## (第6実施形態)

次に、本発明の第6実施形態によるパストランジスタ回路を図13に示す。この実施形態のパストランジスタ回路は、図5に示す第1実施形態において、p型MOSFET10a1をp型のスピンMOSFET10Aに置き換えた構成となっている。すなわち、直列に2個のスピンMOSFET10A、10Bが接続された構成となっている。

## [0081]

そして、本実施形態においては、2つのスピンMOSFET10A、10Bのうちの一方のスピンMOSFETの磁化状態を反平行とし、他方のスピンMOSFETの磁化状態を平行状態とする。このように、直列に接続された2つのスピンMOSFET10A、10Bの磁化状態を相補的にしておくことで、大きな抵抗変化が得られるため、安定に回路動作することができる。

#### [0082]

本実施形態も 本実施形態は第1実施形態と同様に、充電動作を行った後に、論理動作を行う。

## [0083]

本実施形態も、第1実施形態と同様に、低消費電力のメモリ機能付きパストランジスタ 回路を実現することができる。 10

20

30

00

40

#### [0084]

更に、少ない素子数でメモリ機能付きパストランジスタ回路を実現することができる。 これにより、小面積のメモリ機能付きパストランジスタ回路を実現することが可能となり 、小面積のスイッチングボックス回路を得ることができる。

## [0085]

また、本実施形態によるメモリ機能付きパストランジスタ回路を用いれば、低消費電力 のスイッチングボックス回路を構成することができる。したがって、本実施形態によるメ モリ機能付きパストランジスタ回路を用いれば、高集積でかつ低消費電力のリコンフィギ ャラブル論理回路を実現することができる。

## [0086]

なお、本実施形態では、スピンMOSFET10Aのゲートに基準電圧GNDを印加し 、 スピンMOSFET10Bのゲートに制御信号ENABLE2を入力したが、スピンM OSFET10Aのゲートに制御信号ENABLE-INVを入力し、スピンMOSFE T10Bのゲートに電源電圧Vddを印加してもよい。

#### [0087]

また、本実施形態では、トランジスタ10c1、10d1にn型MOSFETを用いた が、トランジスタ 1 0 c 1 、 1 0 d 1 に p 型 M O S F E T を用いてもよい。

#### 【符号の説明】

#### [0088]

10a トランジスタ

10a1 p型MOSFET

10A p型スピンMOSFET

10 A 1 M T J 素子

10b トランジスタ

10b1 n型MOSFET

10B n型スピンMOSFET

10 B 1 M T J 素子

10c トランジスタ

10c1 n型MOSFET

10c2 p型MOSFET

10d トランジスタ(パストランジスタ)

10d1 n型MOSFET

10d2 p型MOSFET

2 0 第 1 電 源

2 2 第 2 電 源

2 4 第 1 入 出 力 端 子

26 第2入出力端子

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

## 【図6A】

【図 6 B】

【図7】

# 【図8】

## 【図9】

## 【図12】

## 【図13】

## 【図10】

## 【図11】

## 【図14】

# 【図15】

# 【図16】

#### 【国際調査報告】

## INTERNATIONAL SEARCH REPORT International application No. PCT/JP2009/066678 A. CLASSIFICATION OF SUBJECT MATTER H01L29/82(2006.01)i, H01L21/8234(2006.01)i, H01L21/8246(2006.01)i, H01L27/088(2006.01)i, H01L27/105(2006.01)i, H01L43/08(2006.01)i According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) HO1L29/82, HO1L21/8234, HO1L21/8246, HO1L27/088, HO1L27/105, HO1L43/08, H03K19/173, H01L29/786, H01L29/66 Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Jitsuyo Shinan Koho 1922-1996 Jitsuyo Shinan Toroku Koho 1996-2009 Kokai Jitsuyo Shinan Koho 1971-2009 Toroku Jitsuyo Shinan Koho 1994-2009 Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) C. DOCUMENTS CONSIDERED TO BE RELEVANT Category\* Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. JP 2009-509460 A (Actel Corp.), 1-9 Υ 05 March 2009 (05.03.2009), entire text & US 2007/0064484 A1 & EP 1927112 A & WO 2007/037823 A1 JP 2006-339235 A (Renesas Technology Corp.), 14 December 2006 (14.12.2006), Υ 1-9 paragraphs [0002], [0046]; fig. 14 (Family: none) X Further documents are listed in the continuation of Box C. See patent family annex. later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention Special categories of cited documents: "A" document defining the general state of the art which is not considered to be of particular relevance "E" earlier application or patent but published on or after the international document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination document referring to an oral disclosure, use, exhibition or other means being obvious to a person skilled in the art document published prior to the international filing date but later than the priority date claimed document member of the same patent family Date of mailing of the international search report 22 December, 2009 (22.12.09) Date of the actual completion of the international search 10 December, 2009 (10.12.09) Name and mailing address of the ISA/ Authorized officer Japanese Patent Office

Telephone No.

Facsimile No.

Form PCT/ISA/210 (second sheet) (April 2007)

## INTERNATIONAL SEARCH REPORT

International application No. PCT/JP2009/066678

|               |                                                                                                                                                                                                                       | PCT/JP2 | 2009/066678           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|

| (Continuation | a). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                               |         | _                     |

| Category*     | Citation of document, with indication, where appropriate, of the relev                                                                                                                                                |         | Relevant to claim No. |

| Y             | JP 2009-135533 A (Japan Science and Tech<br>Agency),<br>18 June 2009 (18.06.2009),<br>paragraphs [0002] to [0006], [0011], [009<br>[0100]; fig. 11, 17<br>& US 2008/0061336 A1 & EP 1555694 A1<br>& WO 2004/012272 A1 |         | 2-8                   |

| Y             | JP 2009-124175 A (NEC Corp.),<br>04 June 2009 (04.06.2009),<br>paragraphs [0003], [0082] to [0086]; fig.<br>& US 2005/0045919 A1                                                                                      | . 19    | 9                     |

| A             | JP 2009-059807 A (Fujitsu Ltd.), 19 March 2009 (19.03.2009), entire text (Family: none)                                                                                                                               |         | 1-9                   |

Form PCT/ISA/210 (continuation of second sheet) (April 2007)

#### 国際調查報告

国際出願番号 PCT/JP2009/066678

発明の属する分野の分類(国際特許分類(IPC))

Int.Cl. H01L29/82(2006.01)i, H01L21/8234(2006.01)i, H01L21/8246(2006.01)i, H01L27/088(2006.01)i, H01L27/105 (2006. 01) i, H01L43/08 (2006. 01) i

#### B. 調査を行った分野

調査を行った最小限資料(国際特許分類(IPC))

Int.Cl. H01L29/82, H01L21/8234, H01L21/8246, H01L27/088, H01L27/105, H01L43/08, H03K19/173, H01L29/786, H01L29/66

#### 最小限資料以外の資料で調査を行った分野に含まれるもの

日本国実用新案公報 1922-1996年 1971-2009年 日本国公開実用新案公報 日本国実用新案登録公報 1996-2009年 1994-2009年 日本国登録実用新案公報

国際調査で使用した電子データベース(データベースの名称、調査に使用した用語)

#### 関連すると認められる文献

| C.              |                                                                                                            |                |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| 引用文献の<br>カテゴリー* | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                          | 関連する<br>請求項の番号 |  |  |  |

| Y               | JP 2009-509460 A (アクテル・コーポレイション) 2009.03.05,<br>全文 & US 2007/0064484 A1 & EP 1927112 A & WO 2007/037823 A1 | 1-9            |  |  |  |

| Y               | JP 2006-339235 A (株式会社ルネサステクノロジ) 2006.12.14,<br>段落【0002】、【0046】、図14 (ファミリーなし)                              | 1-9            |  |  |  |

|                 |                                                                                                            |                |  |  |  |

|                 |                                                                                                            |                |  |  |  |

#### ☑ C欄の続きにも文献が列挙されている。

パテントファミリーに関する別紙を参照。

- \* 引用文献のカテゴリー

- 「A」特に関連のある文献ではなく、一般的技術水準を示す 「T」国際出願日又は優先日後に公表された文献であって もの

- 「E」国際出願日前の出願または特許であるが、国際出願日 以後に公表されたもの

- 「L」優先権主張に疑義を提起する文献又は他の文献の発行 日若しくは他の特別な理由を確立するために引用す 「Y」特に関連のある文献であって、当該文献と他の1以 る文献 (理由を付す)

- 「O」口頭による開示、使用、展示等に言及する文献 よって進歩性がないと考え「P」国際出願目前で かつ優先権の主張の基礎となる出願 「&」同一パテントファミリー文章

- の日の後に公表された文献

- 出願と矛盾するものではなく、発明の原理又は理論 の理解のために引用するもの

- 「X」特に関連のある文献であって、当該文献のみで発明 の新規性又は進歩性がないと考えられるもの

- 上の文献との、当業者にとって自明である組合せに よって進歩性がないと考えられるもの

| 「P」国际田願日削じ、かつ懐元権の主張の基礎となる田願                         | 「&」同一ハテントノアミリー文献                |     |      |

|-----------------------------------------------------|---------------------------------|-----|------|

| 国際調査を完了した日 10.12.2009                               | 国際調査報告の発送日<br>22.12.            | 200 | 9    |

| 国際調査機関の名称及びあて先                                      | 特許庁審査官(権限のある職員)                 | 4 M | 3349 |

| 日本国特許庁(ISA/JP)<br>郵便番号100-8915<br>東京都千代田区霞が関三丁目4番3号 | 川村 裕二<br>  電話番号 03-3581-1101 内; | · 3 | 462  |

様式PCT/ISA/210 (第2ページ) (2007年4月)

国際調査報告

国際出願番号 PCT/JP2009/066678

| C(続き).          | 関連すると認められる文献                                                                                                                                                 |                |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 引用文献の<br>カテゴリー* | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                            | 関連する<br>請求項の番号 |

| Y               | JP 2009-135533 A (独立行政法人科学技術振興機構) 2009.06.18,<br>段落【0002】-【0006】、【0011】、【0098】-【0<br>100】、図11、17<br>& US 2008/0061336 A1 & EP 1555694 A1 & WO 2004/012272 A1 | 2-8            |

| Y               | JP 2009-124175 A(日本電気株式会社)2009.06.04,<br>段落【0003】、【0082】-【0086】、図19<br>& US 2005/0045919 A1                                                                  | 9              |

| A               | JP 2009-059807 A(富士通株式会社)2009.03.19,<br>全文(ファミリーなし)                                                                                                          | 1-9            |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

|                 |                                                                                                                                                              |                |

様式PCT/ISA/210 (第2ページの続き) (2007年4月)

#### フロントページの続き

(出願人による申告)平成21年度 独立行政法人新エネルギー・産業技術総合開発機構「ナノテクノロジープログラム/ナノテク・先端部材実用化研究開発/高スピン偏極率材料を用いた スピンMOSFETの研究開発」委託研究、産業技術力強化法第19条の適用を受ける特許出願

(72)発明者 杉 山 英 行

東京都港区芝浦一丁目1番1号 株式会社東芝 知的財産部内

(72) 発明者 棚 本 哲 史

東京都港区芝浦一丁目1番1号 株式会社東芝 知的財産部内

(72) 発明者 丸 亀 孝 生

東京都港区芝浦一丁目 1番 1号 株式会社東芝 知的財産部内

(72) 発明者 石 川 瑞 恵

東京都港区芝浦一丁目1番1号 株式会社東芝 知的財産部内

(72)発明者 井 口 智 明

東京都港区芝浦一丁目1番1号 株式会社東芝 知的財産部内

(72) 発明者 斉 藤 好 昭

東京都港区芝浦一丁目1番1号 株式会社東芝 知的財産部内

F ターム(参考) 5F064 AA08 BB12 BB37 CC09 FF04 FF36 FF46

5F092 AB10 AC24

5J043 AA03 AA05 HH01 JJ10

5J056 AA00 BB17 BB57 DD13 DD39 KK01

(注)この公表は、国際事務局(WIPO)により国際公開された公報を基に作成したものである。なおこの公表に係る日本語特許出願(日本語実用新案登録出願)の国際公開の効果は、特許法第184条の10第1項(実用新案法第48条の13第2項)により生ずるものであり、本掲載とは関係ありません。