(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-322915

(P2005-322915A)

(43) 公開日 平成17年11月17日(2005.11.17)

(51) Int.Cl.<sup>7</sup>

H05K 3/34

F 1

H05K 3/34 502E

テーマコード(参考)

5E319

審査請求 未請求 請求項の数 19 O L (全 11 頁)

(21) 出願番号 特願2005-134097 (P2005-134097)

(22) 出願日 平成17年5月2日 (2005.5.2)

(31) 優先権主張番号 10/838897

(32) 優先日 平成16年5月4日 (2004.5.4)

(33) 優先権主張国 米国(US)

(71) 出願人 500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン パークウェイ エヌイー 1110

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

(74) 代理人 100094112

弁理士 岡部 譲

最終頁に続く

(54) 【発明の名称】構成要素の表面実装アタッチメント

## (57) 【要約】

【課題】高デバイス密度回路基板を製造するための表面実装方法を提供すること。

【解決手段】ボード上の構成要素のスタンドオフ空間は、構成要素パッケージの下にあるはんだマスクを選択的に省略することによって、または選択的に除去することによって、著しく拡大することができる。このため、清浄化操作中に構成要素の下に向かう清浄用流体の進入が改善される。

【選択図】図12

**【特許請求の範囲】****【請求項 1】**

a . 上面および底面を有する相互接続基板であって、前記上面が構成要素フットプリント領域および複数のはんだ部位を含む相互接続基板を提供する工程と、

b . 前記上面にはんだマスク層を形成する工程であって、前記はんだマスク層が、

i . 前記はんだ部位を取り囲む複数の開口と、

i i . 前記構成要素フットプリント領域の少なくとも一部を取り囲む少なくとも 1 つの開口であり、それによって、はんだマスクの無い構成要素フットプリント領域の少なくとも一部を残す少なくとも 1 つの開口と

を有するものである工程と、

c . 電気構成要素の一部を前記はんだ部位にはんだ付けすることによって前記基板に前記構成要素を取付する工程であって、前記電気構成要素が、前記基板に隣接しつつ前記基板から間隔を空けて設けられた底面を有し、それによって前記基板の上面と前記構成要素の底面との間にスタンドオフ空間を残す工程と、

d . 前記基板を清浄用流体に曝すことによって前記基板を清浄化する工程であって、前記スタンドオフ空間を前記清浄用流体に曝すことによって前記スタンドオフ空間を清浄化することを含む工程と

を含む、電気デバイスの製造方法。

**【請求項 2】**

はんだペーストを前記はんだ部位に選択的に付着させる、請求項 1 に記載の方法。

20

**【請求項 3】**

前記構成要素がリードレス・デバイスである、請求項 1 に記載の方法。

**【請求項 4】**

前記構成要素がリード付きデバイスである、請求項 1 に記載の方法。

**【請求項 5】**

b . i i における開口のサイズが前記構成要素フットプリント領域のサイズを超える、請求項 1 に記載の方法。

**【請求項 6】**

前記基板上に光画像形成可能なポリマーのプランケット層を堆積し、前記プランケット層の領域を露光し、前記露光された領域を除去することによって、前記はんだマスクを形成し、前記露光された領域が b . i および b . i i に対応する、請求項 1 に記載の方法。

30

**【請求項 7】**

前記はんだペーストを、ステンシル法を使用して選択的に付着させる、請求項 2 に記載の方法。

**【請求項 8】**

構成要素を前記基板の底面に実装する、請求項 1 に記載の方法。

**【請求項 9】**

a . 上面および底面を有する相互接続基板であって、前記上面が構成要素フットプリント領域および複数のはんだ部位を含む相互接続基板と、

b . 前記上面にあるはんだマスク層であって、

i . 前記はんだ部位を取り囲む複数の開口と、

i i . 前記構成要素フットプリント領域の少なくとも一部を取り囲む少なくとも 1 つの開口であり、それによって、はんだマスクの無い構成要素フットプリント領域の少なくとも一部を残す少なくとも 1 つの開口と

を有するはんだマスク層と、

c . 前記はんだ部位にはんだ付けされた電気構成要素であって、前記基板に隣接しつつ前記基板から間隔を空けて設けられた底面を有し、それによって前記基板の上面と前記構成要素の底面との間にスタンドオフ空間を残す電気構成要素と

を含む S M T デバイス。

40

**【請求項 10】**

50

b . i i における開口の面積が前記構成要素フットプリント領域の面積を超える、請求項 9 に記載の S M T デバイス。

【請求項 1 1】

前記デバイスがリードレス・チップ・キャリアである、請求項 9 に記載の S M T デバイス。

【請求項 1 2】

前記デバイスがリード付きデバイスである、請求項 9 に記載の S M T デバイス。

【請求項 1 3】

前記はんだマスク層が光画像形成可能なポリマーを含む、請求項 9 に記載の S M T デバイス。

10

【請求項 1 4】

前記構成要素フットプリント領域の基板に凹部をさらに含む、請求項 9 に記載の S M T デバイス。

【請求項 1 5】

前記基板がプリント回路基板である、請求項 9 に記載の S M T デバイス。

【請求項 1 6】

前記基板がポリマーである、請求項 1 5 に記載の S M T デバイス。

【請求項 1 7】

前記基板がセラミックである、請求項 9 に記載の S M T デバイス。

【請求項 1 8】

前記はんだ部位に基板の隆起部をさらに含む、請求項 9 に記載の S M T デバイス。

20

【請求項 1 9】

前記基板の底面に実装された構成要素をさらに含む、請求項 9 に記載の S M T デバイス

。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、表面実装技術（S M T）と、はんだ付け後の清浄化の改善を促す S M T 構成要素を実装するための方法に関する。

30

【背景技術】

【0 0 0 2】

電子装置用プリント回路基板（P C B）を製造する手法は、構成要素のサイズの縮小と支持基板の構成要素の密度の増加に伴って、数多くの変遷を経てきた。スルーホール・リードを備えたよく知られているデュアルインライン・パッケージ（D I P）は、その大部分が、ボードの片面から実装および取付する表面実装技術（S M T）デバイスへと代わっている。S M T の実装は様々な形態を持つ。多くは個別の構成要素をハイブリッド回路に実装することに対処している。典型的な構成要素は、コンデンサ、抵抗器、インダクタ、L E D、ディスクリート・トランジスタなどである。これらの要素の組合せを備えたサブ回路またはサブアセンブリ・パッケージも、S M T 構成要素として一般的にパッケージにされる。例えばフィルタやその他のR C 回路は、しばしば単一のユニットとしてパッケージにされる。受動素子と能動トランジスタの両方を含めた多数のデバイスを備えた集積回路デバイスは、しばしば S M T を使用して実装される。

40

【0 0 0 3】

ボード表面への構成要素の取付において、はんだはほぼ普遍的な取付媒体である。このような取付は、電気的な相互接続としての役割も果たす。構成要素上の電気接点を、ボード上の導体パッドにはんだ付けする。構成要素上の電気接点はリードレスでよく、すなわち平らで予めスズめっきした表面でよく、または構成要素のパッケージから延びたりードでよい。リード・チップ・キャリア・パッケージ上のリードは、典型的な場合、明確に異なる形状を有し、例えばガルウィング型やJ字型、I字型である。

【発明の開示】

50

## 【発明が解決しようとする課題】

## 【0004】

はんだ付けの操作では、典型的な場合、残渣および細片が生ずる。残渣は、酸性、腐食性でありまた電気信号を伝えるイオン成分を含有する可能性のあるはんだフラックス剤によって生成される。これらの残渣が完全に除去されない場合、製品の信頼性に関する問題が生ずる可能性がある。細片は、はんだリフロー工程中に形成されるはんだおよび／またはその他の材料の小さな粒子、すなわち完成したデバイスに有害でもある小さな粒子を含む可能性がある。したがってSMTはんだ付け操作は、通常、実装したデバイス全体に流体を循環させる清浄化工程で終わる。清浄用流体の流れは構成要素とボードとの間に空間にも侵入するが、この空間にはしばしば有害な残渣および細片が入っている。構成要素の底部とボードまたは基板との間の空間を、以下ではスタンドオフ空間と呼び、この基板表面と構成要素の底部とを隔てる距離を、スタンドオフ高さと呼ぶ。ボードまたは基板上ではんだマスクを使用するSMT法では、スタンドオフ高さを、はんだマスク層の上面と構成要素パッケージの底面との間の垂直距離によって決定する。リード・パッケージでは、スタンドオフ空間を、リードのサイズおよび形状によって名目上制御する。リードレス・チップ・キャリアおよび同様のパッケージでは、スタンドオフを、リフロー中のはんだの表面張力およびへこみ高さによって主に決定する。

## 【0005】

小型で小さいプロファイルのパッケージの高パッキング要件を満たすようにボード上のデバイス密度が増加するにつれ、スタンドオフ空間はさらに狭くなる。狭くなった空間は、残渣および細片を捕捉する傾向が高くなると共に、清浄用流体の流れと接触しにくくなる。したがってスタンドオフ空間が非常に狭い場合、清浄化操作はその効果がなくなる可能性がある。

## 【課題を解決するための手段】

## 【0006】

スタンドオフ空間は、構成要素パッケージの下のはんだマスクを選択的に省略したり選択的に除去することによって、著しく拡大することができる。構成要素パッケージの下にある基板上に、この構成要素をはんだ付けする領域を、本明細書では構成要素フットプリントと呼ぶ。これは典型的な場合、四角形または長方形である。構成要素の下のはんだマスクを選択的に省略することによって、スタンドオフ高さは、その省略されたはんだマスクが占めていた厚さ分だけ増加する。現況技術のSMTでは、スタンドオフ高さは典型的な場合は小さく、はんだマスクの厚さはスタンドオフ高さのかなりの部分を占める。

本発明は、図面と併せて考察することによって、より良く理解することができる。

## 【発明を実施するための最良の形態】

## 【0007】

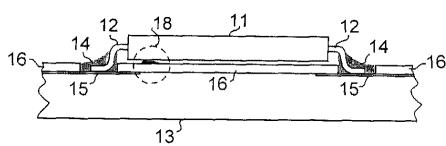

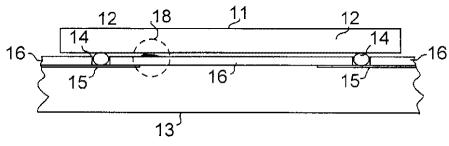

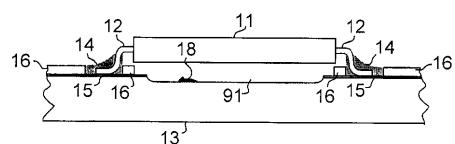

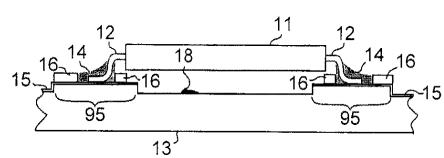

図1を参照すると、ガルウィング・リード12を備えたリード構成要素11が、はんだフィレット14によって基板13に表面実装された状態が示されている。本発明の記述に関係する構造を断面で示す（構成要素の内部フィーチャは示していない）。エポキシ樹脂などの回路基板（FR4）でよい基板13は、切り取った状態が示され、すなわちこの図に示すボードは、大型回路基板の一部のみであり、典型的な場合には小さい部分を示している。はんだフィレットの下には導体パッド15がある。導体パッドは、ボード上の多数の構成要素を相互接続する回路ランナと一体化している。導体パッドは、典型的な場合は銅であるが、アルミニウムまたは別の金属であってもよく、すなわち塗布されるはんだで導体パッドが確実に濡れるように上面がめっきされた金属という何らかの形を持つものでよい。

## 【0008】

図1は、本明細書では符号16で示されるはんだマスクを使用して基板上のはんだの位置を選択的に限定する、一般的なSMT法を表す。はんだ付けの操作から生ずる細片を符号18で示すが、この細片は、はんだマスク層16と構成要素11の底部との間のスタンドオフ空間内に捕捉されている。

## 【0009】

図中の各要素は、必ずしもその縮尺を合わせる必要がないことが理解されよう。例えば、他の寸法に対するはんだマスクの厚さは、本発明を例示するためにいくらか誇張してよい。

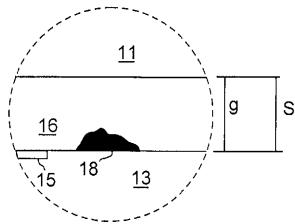

## 【0010】

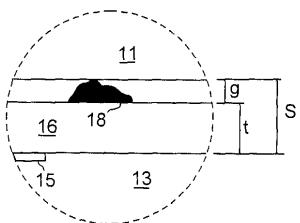

図2は、図1の破線による円形部分を示し、スタンドオフ空間をより詳細に示す。はんだマスク層の厚さを、この図では $t$ で示す。スタンドオフ高さ $S$ は、リード12のサイズおよび形状によって名目上決定される。リードは、基板13の表面に接触し、または構成要素が非常に小さい場合には、基板表面上にわずかに浮くことができる。しかし、はんだ部位に関する名目上のスタンドオフ高さは基板表面によって決定され、最大高さは $S$ である。しかし実際には、構成要素11の下のスタンドオフ高さは、基板13の表面によってではなく、はんだマスク層16の表面によって決定する。したがって実際のスタンドオフ高さは、図2では $g$ である。前に述べたように、このスタンドオフ高さはデバイスのサイズが縮小するにつれて小さくなる。図2は、隙間 $g$ にしっかりと捕捉された細片18を示す。

## 【0011】

図1および図2は、一般に、スタンドオフ空間に捕捉されまたは形成された細片または残渣の問題を示す。この図に示す構成要素はガルティング・リードを備えたリード・パッケージであるが、そのような問題は、広く様々な個別の構成要素および集積回路パッケージで広範に生ずる。例として、図3は、リードレス表面実装構成要素での問題を示す。全ての要素は、リード12が無いことを除いて図1と同じである。表面実装構成要素の下のスタンドオフは、はんだリフロー中のはんだの表面張力／へこみ特性によって主に決定される。構成要素の端部は、典型的な場合スズめっきされて（図示せず）、構成要素と導体パッドとの間の濡れを促進させる。図4は、デバイス11を取付するにはんだバンプまたはBGAボール14を使用する、別のSMTパッケージ・タイプである。典型的な場合、BGA技術におけるデバイス11は集積回路であり、ボールまたは相互接続の数を非常に大きくすることができる。

細片および残渣の問題は様々なSMTパッケージ・タイプに存在することを示してきたが、以下の詳細事項は、図1のガルティング・パッケージに関して記述するものである。

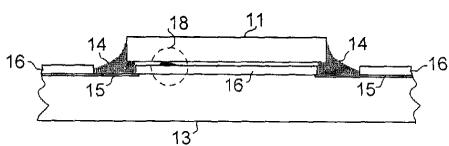

## 【0012】

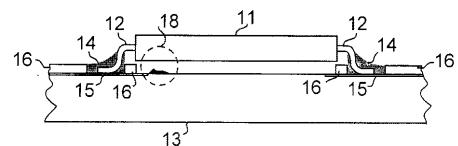

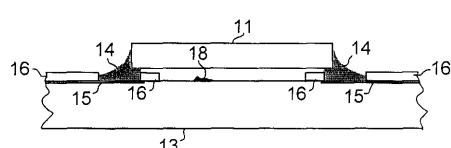

図5は、図1のパッケージであって、構成要素のフットプリントにほぼ対応する領域からはんだマスクを省略した状態を示す。はんだマスク16は、図示するようにはんだ部位を取り囲んだ状態で依然として残っている。構成要素のフットプリントからはんだマスクを省略する効果は図6で明らかであり、すなわち構成要素11の底部と基板との間の隙間 $g$ が図2に示す最大スタンドオフに等しく、したがってはんだ付け後の清浄化操作中、清浄用流体によるスタンドオフ空間への進入が著しく高まる。

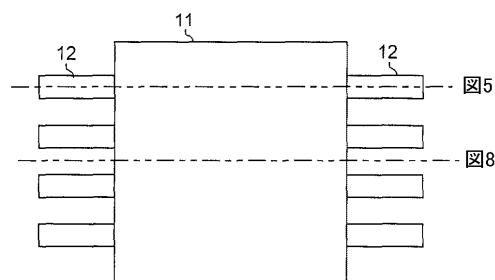

## 【0013】

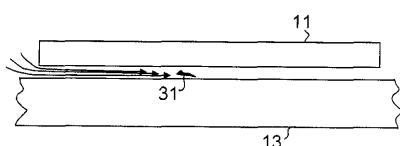

図5は、構成要素11のリード12を経た断面を示し、すなわち図7中「図5」で示される線に沿った断面を示す。図7中の切断線「図8」で示されるリード間の図を、図8に示す。清浄用流体の流れを矢印で示し、取り除かれる細片を符号31で示す。清浄用流体の流れは、はんだマスクによって妨害されないことがわかる。

## 【0014】

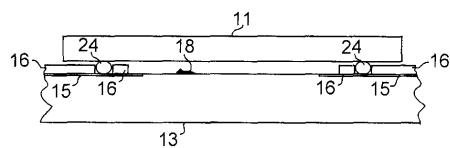

図9は、図3の実施形態であって構成要素のフットプリントからはんだマスクを省略したSMTリードレス・チップ・キャリア(LCC)を示し、図10は、図4の実施形態であってフットプリントからはんだマスクを省略した状態を示す。どちらの場合も、図5に関して述べたものと同じ効果があることが明らかである。

## 【0015】

SMT技術において、はんだマスク層は典型的な場合ポリマーであり、例えばポリイミド、ポリアクリレート、または適切な代替例である。光画像形成可能なポリマーであることが好ましい。はんだマスク材料は、好ましくは基板上に堆積したプランケットであり、

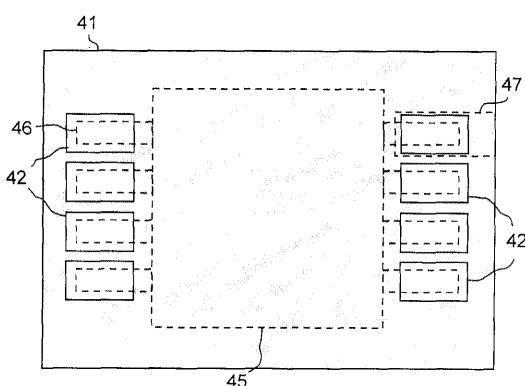

10 フォトリソグラフィを使用してパターニングされる。広く様々なフォトレジスト型材料が当技術分野では知られており、これらのタイプの材料は、周知のかつ十分に開発された技法によって容易に塗布されかつパターニングされる。層をマスクし、露光し、現像する。代替の方法、例えばスクリーン印刷のような相加法を使用してもよい。図11は、はんだ部位42を除いて基板を覆うように、従来技術の教示によってパターニングされたはんだマスク層41の平面図を示す。構成要素の外形を符号45の破線で示し、構成要素のリードを符号46で示す。また、導体パッド47を破線で示す。明確にするために、導体パッドを1つだけ示すが、導体パッドは各はんだ部位42の下に在ることが理解されよう。リード同士の間隔は図示されるよりも大きくなる可能性があり、それによってリードと導体パッドとの間に若干のアライメント誤差が生ずるようになる。導体パッドは、典型的な場合、ガルウイングの基部全体がパッド上に存在するように、リードよりも大きく作製される。従来技術のSMTでは、はんだマスクを製造するフォトマスクは図11と非常によく似ており、開口パターンがはんだ部位に対応している。

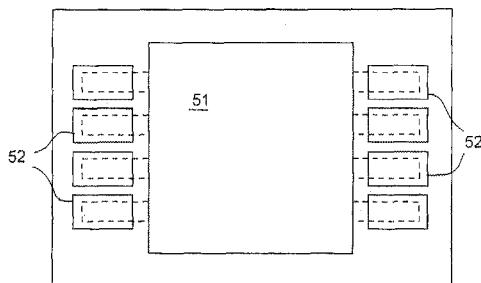

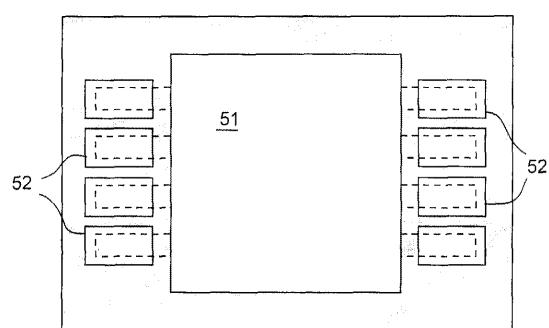

#### 【0016】

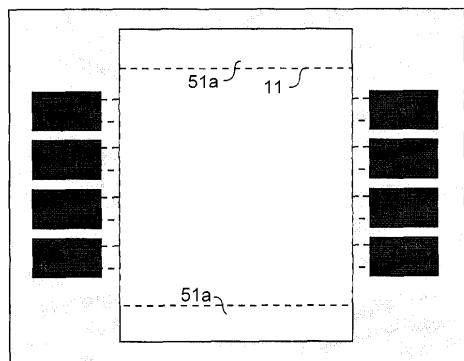

対照的に、本発明を実施するためのはんだマスクを図12に示すが、これは構成要素のフットプリントにほぼ対応する開口51を備えている。はんだ部位窓52が図に示すように設けられている。

#### 【0017】

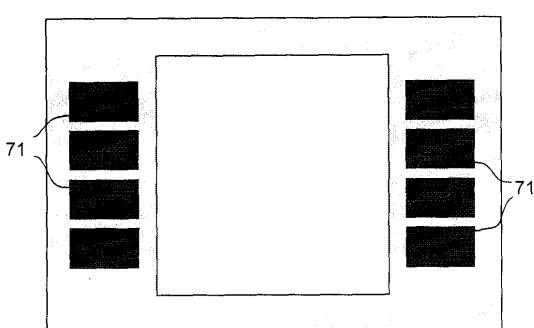

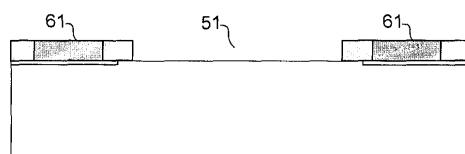

20 図12のはんだマスクが所定の位置にある場合、はんだペースト操作は、そのペーストをはんだ部位窓52に選択的に塗布して構成要素のフットプリント領域では省略すること以外、通常の手法で実施する。これを図13に示すが、はんだペースト61は、はんだ部位窓に選択的に堆積されている。はんだペーストの選択的な塗布は、周知のステンシル法を使用して容易に実施することができる。ステンシルにははんだ部位用の開口を設けるが、構成要素のフットプリント領域内には開口を設けない。次いではんだペーストのリフローを行って、図14に符号71で示すようなはんだバンプを生成する。適切なはんだバンプは、他の方法により生成してもよい。例えばはんだを、シャドウ・マスクを通して蒸発させることができる。

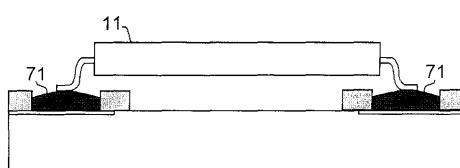

#### 【0018】

30 はんだバンプを形成したら、図15に示すように、はんだバンプ71にリードを位置合わせした状態で構成要素11を配置し、はんだのリフローを行って、図5のアセンブリを生成する。次いで上述の清浄化操作を実施する。清浄用流体は、数多くの周知の有機溶媒または洗剤のいずれかでよい。

#### 【0019】

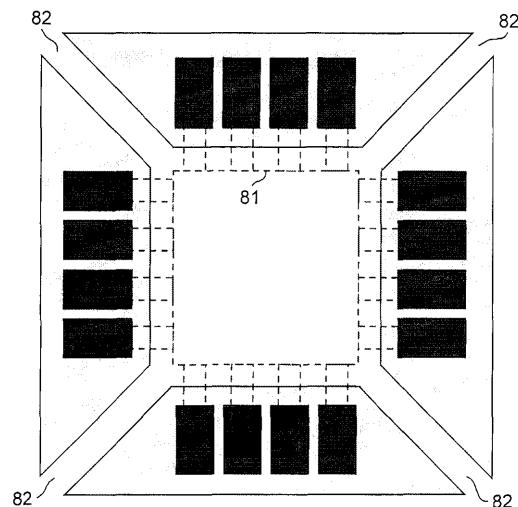

その後、構成要素の下の領域に清浄用流体がさらに進入するように、いくつかの代替の措置をとる。例えば図7の構成要素11は、四方の側面のうち2つの側面にしかリードがないことがわかると、はんだマスク端部の開口空間を拡張して、ボイド空間を拡大することができる。これを図16に示すが、拡張されたボイド領域51aは構成要素のフットプリントを拡大して、構成要素の下の領域への進入を増大させる。図17は、破線の外形81で示す構成要素が四方の側面全てにリードを有する実施形態を示す。構成要素の下のはんだマスクの開口は、構成要素のフットプリントよりもわずかに大きく作製され、さらに、構成要素の下への清浄用流体の進入が増大するように、1つまたは複数のチャネル82が設けられている。

#### 【0020】

40 上述のように、本発明を使用して製造することのできる多種類のSMTデバイスがある。また様々な実装基板もある。PCBは、典型的な場合、エポキシ樹脂板であり、例えばFR4である。これらは単層または多層にできる。実装基板はセラミックまたはシリコンでよい。

#### 【0021】

50 はんだマスクを形成するときに構成要素のフットプリント領域のはんだマスクを省略する措置は、本発明の簡単な実現例であるが、その他の工程順序で同等の結果を実現するこ

とができる。清浄化操作中、構成要素の下にはんだマスクが存在しないことが、極めて重要である。さらに、構成要素のフットプリント内のはんだマスクは、個別の工程でエッチング除去することができる。この順序は、はんだペーストをちょうどはんだ部位にのみ閉じ込めるのがより難しくなるスケイジで、はんだペーストを塗布する場合に有用と考えられる。そのような場合、従来のはんだマスクを形成し、はんだペーストを堆積してリフローさせ、次いではんだマスクの構成要素フットプリント領域を除去することができる。はんだマスクを選択的にエッチングするのに利用可能いくつかの周知の有機溶媒がある。

#### 【0022】

既に述べた本発明のいくつかの実施形態では、はんだマスクの一部を除去することによってスタンドオフ空間が拡張する。この代替例は、基板の一部を除去し、または基板を成形し、それによってスタンドオフ高さを増大させることである。この結果を実現するための2つの実施形態を図18および図19に示す。図18では、構成要素のフットプリントの下にある基板の上面領域を選択的にエッチングして、基板に凹部91を形成する。はんだマスクは存在してもよく、または好みに応じて省略してもよい。スタンドオフ高さは、エッチングされた凹部の深さ分だけ増大する。あるいは基板を、事前に製作された凹部と共に製造することができる。ボード上に適切に位置付けられた凹部を備える回路基板の形成は簡単であるが、それは特に、この回路基板が、典型的な場合には成形工程によって形成されるからである。図19は、基板が隆起部95を備えた状態で成形される実施形態を示す。隆起部ははんだ部位に位置付けられ、ボード表面から構成要素を持ち上げるように機能し、したがってスタンドオフ高さを増大させるという目的を達成する。

#### 【0023】

当業者なら、本発明の様々な追加の修正例を思い浮かべるであろう。当技術分野のこれまでの進歩の拠り所である原理およびその均等物に基本的に依拠する本明細書の特定の教示からの全ての逸脱は、記述されかつ主張される本発明の範囲内にあると適正に考慮される。

#### 【図面の簡単な説明】

#### 【0024】

【図1】細片の捕捉という従来技術の問題を示す、回路基板上にはんだ付けされたガルウイング・リード構成要素の一部断面概略図である。

#### 【図2】上述の関連寸法を特定するより詳細な概略図である。

【図3】図1と同様であるが別の形のSMTにおける細片の捕捉という問題を示す、はんだ付けされたリードレス表面実装構成要素の概略図である。

【図4】図1と同様であるがボール・グリッド・アレイ(BGA)またはフリップチップSMT構成要素を示す図である。

【図5】構成要素の下の領域からはんだマスクを省略した状態を示す、図1のSMTはんだ付け構成要素の概略図である。

【図6】構成要素の下のはんだマスクが存在しない場合の、図2の関連寸法に対する作用を示す図である。

【図7】図5の構成要素の平面図であり、図5および図8を得るために切断線を示す図である。

【図8】図7に示される図5のSMT構成要素の断面図であり、スタンドオフ空間内の清浄用流体の流れを示す図である。

【図9】図3と同様であり、ただし構成要素の下の領域からはんだマスクを省略した状態を示す図である。

【図10】図4と同様であり、ただし構成要素の下の領域からはんだマスクを省略した状態を示す図である。

#### 【図11】リード構成要素も破線で示す、従来技術のはんだマスクの平面図である。

【図12】構成要素の下の部分が存在しない状態の、本発明により製作されたはんだマスクの平面図である。

#### 【図13】はんだペーストを塗布した後の、図12の断面図である。

10

20

30

40

50

【図14】はんだペーストを塗布しリフローした後の、図12と同様の平面図である。

【図15】はんだバンプのリフローおよびSMT配置後の、SMTデバイスの立面図である。

【図16】スタンドオフ空間への進入の向上をもたらす、はんだマスクの修正例を示す図である。

【図17】スタンドオフ空間への進入の向上をもたらす、はんだマスクの修正例を示す図である。

【図18】スタンドオフ空間への進入の向上をもたらす、基板形状の変形形態を示す図である。

【図19】スタンドオフ空間への進入の向上をもたらす、基板形状の変形形態を示す図である。 10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(74)代理人 100096943

弁理士 臼井 伸一

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 パトリシア マリー アルバニーズ

アメリカ合衆国 19428 ペンシルヴァニア, コンシヨーホークン, ウエスト ツエルヴス

アヴェニュー 300

(72)発明者 ジョン ダブリュ. オーゼンバッハ

アメリカ合衆国 19530 ペンシルヴァニア, カッツタウン, ウォルナット ドライブ 17

(72)発明者 トーマス エッチ. シリング

アメリカ合衆国 18062 ペンシルヴァニア, マッカンジー, フィールドビュー ドライブ

2631

F ターム(参考) 5E319 AA03 AB03 AB05 AC02 AC04 AC13 AC20 BB05 CC33 CD01

CD29 GG20