(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5363009号

(P5363009)

(45) 発行日 平成25年12月11日(2013.12.11)

(24) 登録日 平成25年9月13日(2013.9.13)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78 616V

H01L 21/336 (2006.01)

H01L 29/78 612Z

G02F 1/1345 (2006.01)

H01L 29/78 613A

H01L 29/78 618E

H01L 29/78 616J

請求項の数 6 (全 15 頁) 最終頁に続く

(21) 出願番号

特願2008-49885 (P2008-49885)

(22) 出願日

平成20年2月29日 (2008.2.29)

(65) 公開番号

特開2009-206437 (P2009-206437A)

(43) 公開日

平成21年9月10日 (2009.9.10)

審査請求日

平成22年12月7日 (2010.12.7)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 100075959

弁理士 小林 保

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区妻鹿日田町1-6

(74) 代理人 100075959

弁理士 小林 保

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(72) 発明者 三宅 秀和

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

最終頁に続く

(54) 【発明の名称】表示装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に p 型薄膜トランジスタを備える表示装置であって、

前記 p 型薄膜トランジスタは、

ゲート電極の上面に絶縁膜を介して半導体層が形成され、

前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成され、

前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、p 型不純物の拡散層が形成されて構成されており、

前記 p 型不純物の拡散層は、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されていることを特徴とする表示装置。

## 【請求項 2】

基板上に p 型薄膜トランジスタおよび n 型薄膜トランジスタを備える表示装置であって、

これら各薄膜トランジスタは、ゲート電極の上面に絶縁膜を介して半導体層が形成され、前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成されて構成され、

前記 p 型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソ

10

20

ース電極と前記半導体層の界面に、p型不純物の拡散層が形成され、前記p型不純物の拡散層は、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されており、

前記n型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、n型不純物がドープされた半導体層が介在されていることを特徴とする表示装置。

【請求項3】

基板上にp型薄膜トランジスタおよびn型薄膜トランジスタを備える表示装置であって、

これら各薄膜トランジスタは、ゲート電極の上面に絶縁膜を介して半導体層が形成され、前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成されて構成され、

前記p型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、p型不純物の拡散層が形成され、前記p型不純物の拡散層は、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されており、

前記n型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、n型不純物がドープされた半導体層および前記ドレイン電極とソース電極の材料の前記半導体層への拡散を防止する拡散バリア層の順次積層体が介在されていることを特徴とする表示装置。

【請求項4】

前記半導体層は、多結晶半導体層で形成されていることを特徴とする請求項1に記載の表示装置。

【請求項5】

前記半導体層は、多結晶半導体層と非晶質半導体層の順次積層体から構成されていることを特徴とする請求項1に記載の表示装置。

【請求項6】

基板上にp型薄膜トランジスタを備え、該p型薄膜トランジスタは、ゲート電極の上面に絶縁膜を介して半導体層が形成され、前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成されて構成される表示装置の製造方法であって、

アニールを施すことによって、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されるp型不純物の拡散層を形成することを特徴とする表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示装置およびその製造方法に係り、特に、その基板に形成された薄膜トランジスタを備える表示装置およびその製造方法に関する。

【背景技術】

【0002】

アクティブ・マトリックス型の表示装置は、マトリックス状に配置された各画素において、行方向に配列された各画素に共通の信号線（ゲート信号線）に走査信号を供給することにより、それらの画素を列方向に順次選択し、その選択のタイミングに合わせ、列方向に配列された各画素に共通の信号線（ドレイン信号線）を通して映像信号を供給するように構成されている。

【0003】

10

20

30

40

50

このため、各画素には、前記走査信号の供給によって、ドレイン信号線からの映像信号を当該画素（画素電極）に取り込むための薄膜トランジスタを備える。

#### 【0004】

また、前記画素が形成された基板と同一の基板に、前記ゲート信号線に走査信号を供給し、また、前記ドレイン信号線に映像信号を供給するための駆動回路を備え、この駆動回路は複数の薄膜トランジスタを含む回路によって構成されている。

#### 【0005】

そして、該駆動回路における薄膜トランジスタは、n型薄膜トランジスタおよびp型薄膜トランジスタを有するとともに、それらの半導体層としてアモルファスシリコンを結晶化した多結晶シリコン（Low Temperature Poli Si）で構成したものが知られている。半導体層をこのような多結晶シリコンで構成した薄膜トランジスタは電界効果移動度が高く、前記駆動回路を高速駆動させることができるからである。10

#### 【0006】

このような薄膜トランジスタとしてはたとえば下記特許文献1に開示がなされている。

【特許文献1】特開平5-63196号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

しかし、n型薄膜トランジスタおよびp型薄膜トランジスタを、それぞれポリSiの半導体層で構成する場合、ポリSiの半導体層とドレイン電極およびソース電極との間に、n型薄膜トランジスタにあってはn型の不純物がドープされたアモルファスSiを形成し、p型薄膜トランジスタにあってはp型の不純物がドープされたアモルファスSiを形成しなければならない構成となっていた。20

#### 【0008】

このため、n型の不純物がドープされたアモルファスSiの形成と、p型の不純物がドープされたアモルファスSiの形成を、別個のマスク工程で行わなければならず、製造の工程を増大させていた。

#### 【0009】

本発明の目的は、製造の工数を低減できる構成の表示装置を提供することにある。

#### 【0010】

本発明の目的は、製造の工数を低減させた表示装置の製造方法を提供することにある。30

#### 【課題を解決するための手段】

#### 【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

#### 【0012】

（1）本発明による表示装置は、たとえば、基板上にp型薄膜トランジスタを備える表示装置であって、

前記p型薄膜トランジスタは、

ゲート電極の上面に絶縁膜を介して半導体層が形成され、

前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成され。40

前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、p型不純物の拡散層が形成されて構成されており、

前記p型不純物の拡散層は、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されていることを特徴とする。

#### 【0013】

（2）本発明による表示装置は、たとえば、基板上にp型薄膜トランジスタおよびn型薄膜トランジスタを備える表示装置であって、

10

20

30

40

50

これら各薄膜トランジスタは、ゲート電極の上面に絶縁膜を介して半導体層が形成され、前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成されて構成され、

前記p型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、p型不純物の拡散層が形成され、前記p型不純物の拡散層は、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されており、

前記n型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、n型不純物がドープされた半導体層が介在されていることを特徴とする。

#### 【0014】

(3) 本発明による表示装置は、たとえば、基板上にp型薄膜トランジスタおよびn型薄膜トランジスタを備える表示装置であって、

これら各薄膜トランジスタは、ゲート電極の上面に絶縁膜を介して半導体層が形成され、前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成されて構成され、

前記p型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、p型不純物の拡散層が形成され、前記p型不純物の拡散層は、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されており、

前記n型薄膜トランジスタは、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、n型不純物がドープされた半導体層および前記ドレイン電極とソース電極の材料の前記半導体層への拡散を防止する拡散バリア層の順次積層体が介在されていることを特徴とする。

#### 【0016】

(4) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記半導体層は多結晶半導体層で形成されていることを特徴とする。

#### 【0017】

(5) 本発明による表示装置は、たとえば、(1)の構成を前提とし、前記半導体層は多結晶半導体層と非晶質半導体層の順次積層体から構成されていることを特徴とする。

#### 【0018】

(6) 本発明による表示装置の製造方法は、たとえば、基板上にp型薄膜トランジスタを備え、該p型薄膜トランジスタは、ゲート電極の上面に絶縁膜を介して半導体層が形成され、前記半導体層の上面に離間部を有して互いに対向配置され、アルミニウム、ガリウム、インジウム、タリウムのうちのいずれかの材料を主材料とするドレイン電極とソース電極とが形成されて構成される表示装置の製造方法であって、

アニールを施すことによって、前記ドレイン電極と前記半導体層の界面、および前記ソース電極と前記半導体層の界面に、前記ドレイン電極と前記ソース電極を構成する主材料が前記半導体層に拡散して形成されるp型不純物の拡散層を形成することを特徴とする。

#### 【0019】

なお、本発明は以上の構成に限定されず、本発明の技術思想を逸脱しない範囲で種々の変更が可能である。

#### 【発明の効果】

#### 【0020】

このように構成された表示装置は、製造の工数を低減できる構成とすることができる。

#### 【0021】

このように構成された表示装置の製造方法は、製造の工数を低減できるようになる。

#### 【発明を実施するための最良の形態】

## 【0022】

以下、図面を用いて本発明による表示装置の実施例を説明する。

## 【0023】

## 実施例1

## (全体の構成)

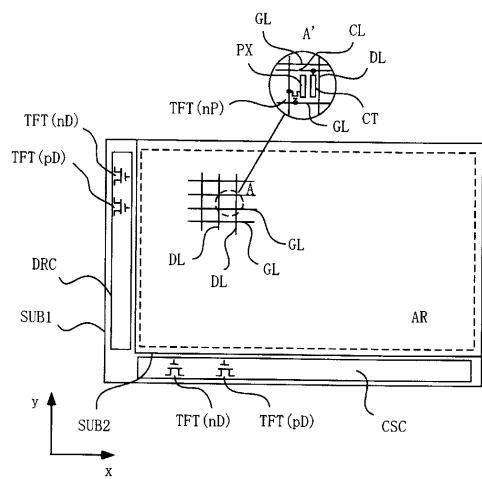

図8は、本発明による表示装置の一実施例を示す概略構成図である。図8はたとえば液晶表示装置を例に挙げて示している。

## 【0024】

液晶を介して対向配置される基板SUB1、SUB2があり、たとえば前記基板SUB2の側の面には液晶表示領域ARが形成されている。

10

## 【0025】

この液晶表示領域ARにおける前記基板SUB1、SUB2の前記液晶側の面には、マトリックス状に配置された複数の画素が形成されている。

## 【0026】

これら画素は、図中点線枠Aの拡大図A'に示すように、図中x方向に伸張されy方向に並設されるドレン信号線DLと、図中y方向に伸張されx方向に並設されるゲート信号線GLとで囲まれる領域内に形成されている。

## 【0027】

そして、各画素は、一方のゲート信号線GLからの走査信号(電圧)によってオンされる薄膜トランジスタTFT(後述の他の薄膜トランジスタTFTと区別するため、符号TFT(nP)で示す)と、このオンされた薄膜トランジスタTFT(nP)を介して一方のドレン信号線DLからの映像信号(電圧)が供給される画素電極PXと、この画素電極PXとの間に電界を生じさせる対向電極CTとを有する。

20

## 【0028】

なお、前記対向電極CTはたとえばゲート信号線GLと平行に配置される対向電圧信号線CLに接続され、該対向電圧信号線CLを介して前記映像信号に対して基準となる信号(電圧)が供給されるようになっている。

## 【0029】

前記液晶表示領域ARの外側(たとえば、図中左側)における前記基板SUB1の表面には、前記各ゲート信号線GLに順次走査信号を供給し、また、この走査信号の供給のタイミングに合わせ、前記各ドレン信号線DLに映像信号を供給するための駆動回路DRCが形成されている。この駆動回路DRCはn型薄膜トランジスタTFT(nD)、およびp型薄膜トランジスタTFT(pD)を備えて構成されている。

30

## 【0030】

また、前記液晶表示領域ARの外側(たとえば、図中下側)における前記基板SUB1の表面には、カラー表示の単位画素において三原色のそれぞれを担当するドレン信号線DLを色ごとに切換えて接続させるためのRGB切換回路CSCが形成されている。このRGB切換回路CSCには、前記駆動回路DRCにおける前記薄膜トランジスタTFT(nD)、TFT(pD)とほぼ同じ構成からなり、該薄膜トランジスタTFT(nD)、TFT(pD)の形成と並行して形成されるようになっている。このため、該RGB切換回路CSCにおけるn型薄膜トランジスタも符号TFT(nD)で示し、p型薄膜トランジスタTFT(pD)も符号TFT(pD)で示す。

40

## 【0031】

## (p型薄膜トランジスタ)

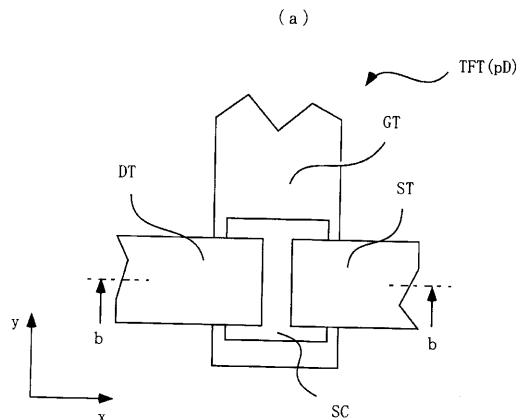

図1は、前記p型薄膜トランジスタTFT(pD)の一実施例を示す構成図で、(a)は平面図を、(b)は(a)のb-b線における断面図を示している。

## 【0032】

基板SUB1の表面にゲート電極GTが形成されている。このゲート電極GTは基板SUB1の表面にたとえば図中y方向に伸張して形成されている。

## 【0033】

50

そして、前記基板 S U B 1 の表面には前記ゲート電極 G T をも被って絶縁膜 G I が形成されている。この絶縁膜 G I は前記 p 型薄膜トランジスタ T F T ( p D ) の形成領域において該 p 型薄膜トランジスタ T F T ( p D ) のゲート絶縁膜として機能するようになっている。

【 0 0 3 4 】

前記絶縁膜 G I の上面において前記ゲート電極 G T に重畠するようにしてたとえばポリシリコン ( p - S i ) からなる半導体層 S C が島状に形成されている。この半導体層 S C はたとえば不純物がドープされていない i 型の半導体層を構成している。

【 0 0 3 5 】

さらに、前記半導体層 S C の上面に、前記ゲート電極 G T の上方にて離間部を有して互いに対向配置される一対の電極 D T 、 S T を備え、これら電極 D T 、 S T はそれぞれ前記絶縁膜 G I 上を図中 x 方向へ伸張して形成されている。

【 0 0 3 6 】

前記電極 D T 、 S T の離間部における前記半導体層 S C の表面の前記電極 D T 、 S T の離間部における領域はチャネル領域を構成し、前記電極 D T 、 S T の離間距離は当該 p 型薄膜トランジスタ T F T ( p D ) のチャネル長に相当するようになっている。

【 0 0 3 7 】

これら電極 D T 、 S T は、たとえばアルミニウム ( A l ) から構成され、これら電極 D T 、 S T の形成後のたとえば約 400 のアニールの際ににおいて、該アルミニウムが半導体層 S C 中に拡散することによって、前記電極 D T と前記半導体層 S C との界面、および前記電極 S T と前記半導体層 S C との界面において、 p ( + ) 型の拡散層 D F が形成されている。

【 0 0 3 8 】

このような p 型薄膜トランジスタ T F T ( p D ) は、いわゆるボトムゲート型の M I S ( Metal Insulator Semiconductor ) トランジスタを構成し、そのバイアスの印加によって、前記電極 D T 、 S T は、その一方がドレイン電極、他方がソース電極として機能するが、この明細書の説明にあっては、便宜上、図中左側の電極をドレイン電極 D T 、図中右側の電極をソース電極 S T と称するようにする。

【 0 0 3 9 】

このように構成された p 型薄膜トランジスタ T F T ( p D ) は、ドレイン電極 D T と半導体層 S C との間に、また、ソース電極 S T と半導体層 S C との間に、コンタクト層を特別に形成する必要がなくなり、したがって、簡単な工程で前記 p 型薄膜トランジスタ T F T ( p D ) を形成することができる。

【 0 0 4 0 】

なお、上述した実施例では、 p 型薄膜トランジスタ T F T ( p D ) のドレイン電極 D T 、ソース電極 S T の材料はアルミニウムとしたものであるが、他の材料として、ガリウム ( G a ) 、インジウム ( I n ) 、あるいはタリウム ( T I ) であってもよい。このような材料を用いることによっても、ドレイン電極 D T と半導体層 S C の界面、ソース電極 S T と半導体層 S C の界面に、それぞれ、 p ( + ) 型の拡散層 D F を形成できるからである。

【 0 0 4 1 】

( p 型薄膜トランジスタと n 型薄膜トランジスタ )

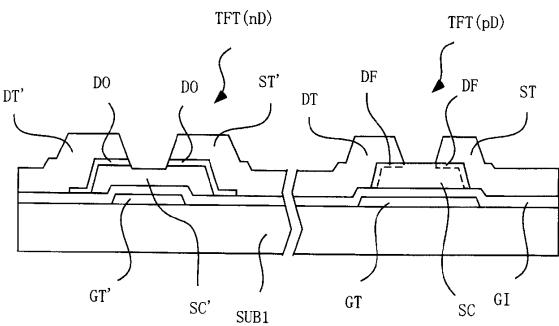

図 2 は、本発明による表示装置の基板上に、前記 p 型薄膜トランジスタ T F T ( p D ) とともに、 n 型薄膜トランジスタ T F T ( n D ) を形成した、たとえばコンプリメンタリ型薄膜トランジスタの構成を示す断面図である。

【 0 0 4 2 】

図 2 に示す p 型薄膜トランジスタ T F T ( p D ) は、図 1 に示した p 型薄膜トランジスタ T F T ( p D ) と同様の構成となっている。したがって、以下の説明においては、図中左側に配置されている n 型薄膜トランジスタ T F T ( n D ) の構成について説明する。

【 0 0 4 3 】

基板 S U B 1 の上面にゲート電極 G T ' が形成されている。このゲート電極 G T ' は前記

10

20

30

40

50

p型薄膜トランジスタTFT (pD) のゲート電極GTと同層かつ同材料で形成されている。

【0044】

前記基板SUB1の表面には前記ゲート電極GT'をも被って絶縁膜GIが形成されている。この絶縁膜GIは前記p型薄膜トランジスタTFT (pD) の形成領域において形成された絶縁膜GIの延在部として構成されたものである。

【0045】

前記絶縁膜GIの上面において前記ゲート電極GT'に重畳するようにしてたとえばポリシリコン(p-Si)からなる半導体層SC'が島状に形成されている。

【0046】

この半導体層SC'は前記p型薄膜トランジスタTFT (pD) の半導体層SCと同層かつ同材料で形成されている。

【0047】

また、前記半導体層SC'の表面、すなわち該半導体層の上面から側壁面にかけての表面、さらに、該半導体層SC'が形成されていない絶縁膜GIの表面に至るようにして、P(+)型不純物がドープされたコンタクト層DOが形成されている。

【0048】

なお、このコンタクト層DOは、後述するドレイン電極DT'およびソース電極ST'から露出された部分において形成されておらず、その下層の半導体層SC'が露出されるようになっている。

【0049】

さらに、前記半導体層SC'の上面に、前記コンタクト層DOを介して、ドレイン電極DT'およびソース電極ST'が形成されている。これにより前記コンタクト層DOは、ドレイン電極DT'と前記半導体層SC'の界面、およびソース電極ST'と前記半導体層SCの界面に形成されることになる。

【0050】

前記ドレイン電極DT'およびソース電極ST'は、前記p型薄膜トランジスタTFT (pD) の前記ドレイン電極DTおよびソース電極STと同層かつ同材料で形成されている。

【0051】

なお、n型薄膜トランジスタTFT (nD) と比較して明らかのように、p型薄膜トランジスタTFT (pD)において、そのゲート電極GTの幅が半導体層SCの幅よりも大きく該半導体層SCの形成領域からはみ出して形成されている。オン電流を高くするためである。

【0052】

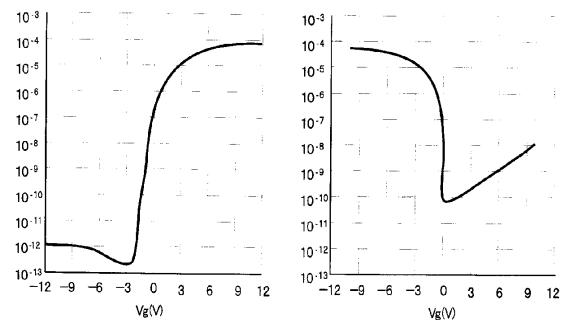

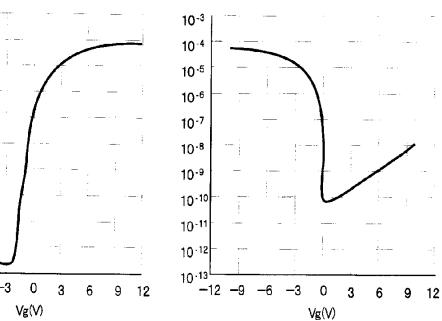

ちなみに、図3は、前記n型薄膜トランジスタTFT (nD)と前記p型薄膜トランジスタTFT (pD)のそれぞれのVgId特性を示した図である。図3(a)は前記n型薄膜トランジスタTFT (nD)のVgId特性を、図3(b)は、前記p型薄膜トランジスタTFT (pD)のVgId特性を示している。各図において、その横軸にはゲート電圧Vg(V)を、縦軸にはドレイン電圧Vdが5Vの際のドレイン電流Id(A)をとっている。

【0053】

前記前記p型薄膜トランジスタTFT (pD)は、そのオン・オフの電流差が充分に大きく、スイッチング素子として機能できることが判る。

【0054】

(製造方法)

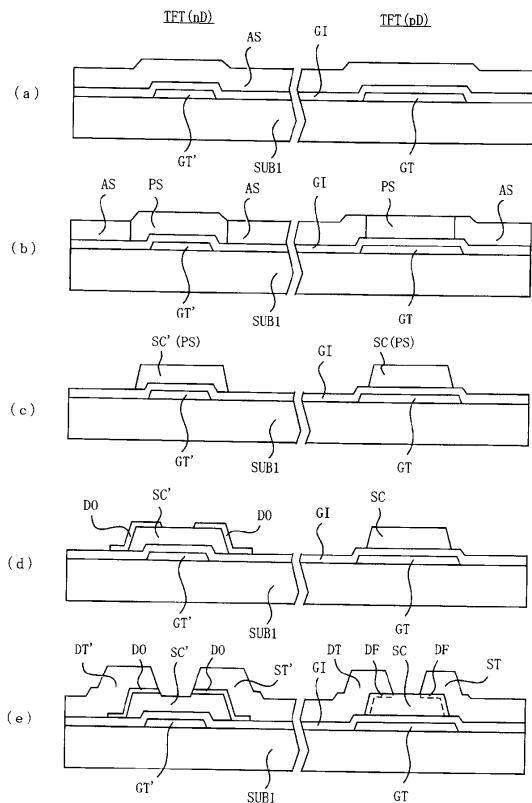

図4(a)ないし(e)は、図2に示したn型薄膜トランジスタTFT (nD)とp型薄膜トランジスタTFT (pD)の製造方法の一実施例を示した工程図である。以下、工程順に説明する。

【0055】

10

20

30

40

50

図4(a)ないし(e)の各図は図2に対応して描いており、したがって、図中左側にn型薄膜トランジスタTFT(nD)の製造工程、図中右側にp型薄膜トランジスタTFT(pD)の製造工程を示している。

【0056】

以下、工程順に説明する。

【0057】

工程1.(図4(a))

たとえばガラスからなる基板SUB1の表面には、ゲート電極GT'およびゲート電極GTを形成し、これらゲート電極GT'およびゲート電極GTをも被って絶縁膜GIを形成する。

10

【0058】

前記ゲート電極GT'およびゲート電極GTは、いずれも、たとえばモリブデン(Mo)等の高融点金属またはその合金をたとえばスパッタリングで成膜(膜厚50~150nm)し、フォトリソグラフィ技術による選択エッチングで形成する。

【0059】

前記絶縁膜GIは、たとえばSiO、SiN、あるいはこれらの積層膜で構成され、膜厚100~300nmで形成する。

【0060】

そして、前記絶縁膜GIの上面の全域に、アモルファスSiからなる半導体層ASをたとえばCVD(Chemical Vapor Deposition)によって膜厚50~300nmで形成する。

20

【0061】

工程2.(図4(b))

前記半導体層ASに、脱水素処理を行った後、選択的に、パルスあるいは連続発振レーザを照射し、n型薄膜トランジスタTFT(nD)の形成領域およびp型薄膜トランジスタTFT(pD)の形成領域における前記半導体層ASの結晶化を行い、ポリSiからなる半導体層PSを形成する。この場合、前記半導体層ASの結晶化は全面に施すようにしてもよい。

【0062】

工程3.(図4(c))

30

前記半導体層ASをフォトリソグラフィ技術による選択エッチングをすることにより、n型薄膜トランジスタTFT(nD)の形成領域およびp型薄膜トランジスタTFT(pD)の形成領域に、それぞれ、ポリSiからなる半導体層PSを残存させる。

【0063】

n型薄膜トランジスタTFT(nD)の形成領域に形成された前記半導体層PSは図2に示した半導体層SC'に相当し、p型薄膜トランジスタTFT(pD)の形成領域に形成された前記半導体層PSは図2に示した半導体層SCに相当する。

【0064】

工程4.(図4(d))

基板SUB1の表面の全域に、たとえばCVD(Chemical Vapor Deposition)を用い、たとえばリン(P)がドープされた半導体層(n(+))型半導体層)を厚さ10~50nmで形成する。

40

【0065】

そして、前記n(+)型半導体層を、フォトリソグラフィ技術によるエッチングによって、n型薄膜トランジスタTFT(nD)の半導体層SC'の上面に残存させ、この残存された前記n(+)型半導体層をコンタクト層DOとする。前記n(+)型半導体層のエッチングは、n型薄膜トランジスタTFT(nD)のチャネル領域となる部分においてもなされるようになっている。

【0066】

工程5.(図4(e))

50

基板S U B 1の表面の全域に、たとえばスパッタリングによって、アルミニウム(A 1)を膜厚300~500nmで成膜する。

【0067】

この際、A 1層の上下のそれぞれの面に、チタン(T i)あるいはモリブデン(M o)等の高融点金属膜を膜厚30~100nmで形成するようとする。この高融点金属膜は、いわゆるバリアメタル層と称し、コンタクト抵抗の低減のために形成される。なお、このバリアメタル層は電極の下層側において形成しなくてもよい。

【0068】

その後、前記A 1層をフォトリソグラフィ技術による選択エッチングをすることによって、n型薄膜トランジスタT F T(n D)の形成領域においてドレイン電極D T'およびソース電極S T'を、p型薄膜トランジスタT F T(p D)の形成領域においてドレイン電極D Tおよびソース電極S Tを形成する。

10

【0069】

さらに、基板S U B 1の表面の全域に、n型薄膜トランジスタT F T(n D)、p型薄膜トランジスタT F T(p D)を被って、たとえばC V D(Chemical Vapor Deposition)を用い、たとえばSi N膜からなる保護膜(図示せず)を形成する。

【0070】

そして、H 2あるいはN 2の雰囲気中、350~450の温度で1~3時間のアニールを行う。このアニールによって、p型薄膜トランジスタT F T(p D)のドレイン電極D T、およびソース電極S T内のアルミニウム(A 1)が半導体層S C内に拡散(前記バリアメタル層がある場合、このバリアメタル層を通して拡散)され、前記ドレイン電極D Tと半導体層S Cの界面、および前記ソース電極S Tと半導体層S Cの界面に、それぞれ、p(+)+型の拡散層D Fが形成されるようになる。なお、このアニールは、前記保護膜の形成前に行っててもよい。

20

【0071】

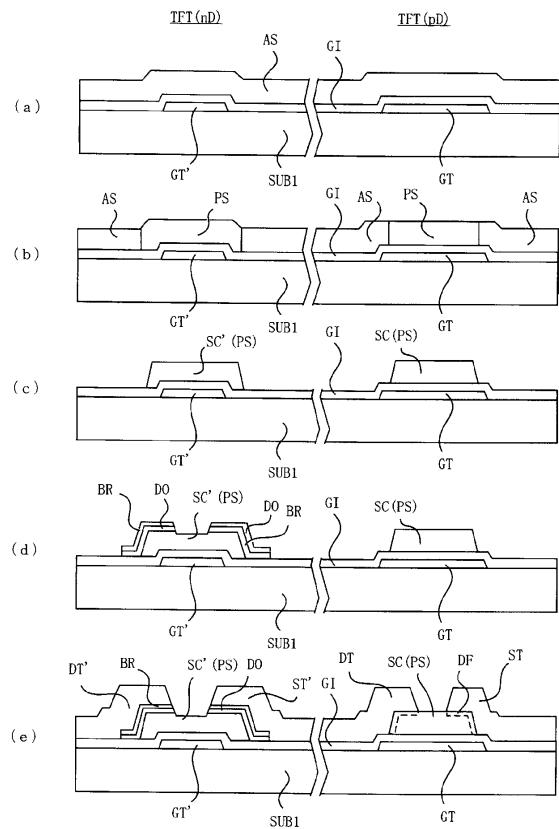

実施例2

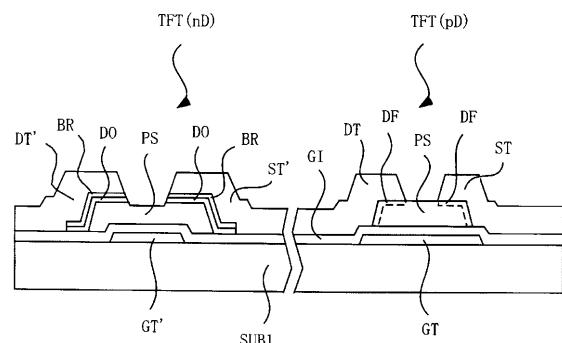

図5は、本発明による表示装置の他の実施例を示す構成図で、図2と対応した図となっている。図5において、図2と同符号のものは同材料で、同機能を有するようになっている。

【0072】

30

図5において、図2の場合と比較して異なる構成は、n型薄膜トランジスタT F T(n D)において、ドレイン電極D T'とコンタクト層D Oの界面に拡散バリア層B Rが形成され、ソース電極S T'もコンタクト層D Oの界面に拡散バリア層B Rが形成されていることにある。

【0073】

この拡散バリア層B Rは、前記アニール時において、ドレイン電極D T'およびソース電極S T'を構成するアルミニウム(A 1)がコンタクト層D Oへ拡散するのを防止するための層となっている。

【0074】

40

該拡散バリア層B Rは、たとえば、M o、T i、あるいはそれらの合金で構成され、前記アルミニウム(A 1)がコンタクト層D Oへ拡散するのを回避できる程度の厚さで形成されている。

【0075】

このようにした場合、コンタクト層D Oの不純物濃度の変化を惹き起こすことなく、当初から該コンタクト層D Oの不純物濃度を所定の値に設定することができる。

【0076】

図6(a)~(e)は、図5に示したn型薄膜トランジスタT F T(n D)とp型薄膜トランジスタT F T(p D)の製造方法の一実施例を示した工程図で、図4に対応させて描いている。図6において、図4と同符号のものは同一材料で、同一機能を有するようになっている。

50

## 【0077】

図6において、図4の場合と異なる構成は、図6(d)に示した工程にある。

## 【0078】

すなわち、基板SUB1の表面の全域に、たとえばCVD(Chemical Vapor Deposition)を用い、たとえばリン(P)がドープされた半導体層(n(+)型半導体層)、さらに、モリブデン(Mo)、チタン(Ti)、あるいはこれらの合金からなる金属層を順次形成する。

## 【0079】

そして、前記n(+)型半導体層と前記金属層の順次積層体を、フォトリソグラフィ技術による一括エッチングによって、n型薄膜トランジスタTFT(nD)の半導体層SC'の上面に残存させ、この残存された前記n(+)型半導体層をコンタクト層DOとし、前記金属層を拡散バリア層BRとする。前記積層体のエッチングは、n型薄膜トランジスタTFT(nD)のチャネル領域となる部分においてもなされるようになっている。

## 【0080】

このように構成した製造方法によれば、図4に示した製造方法と比較して工程数を増大させずに、前記拡散バリア層BRを形成することができる。

## 【0081】

## 実施例3

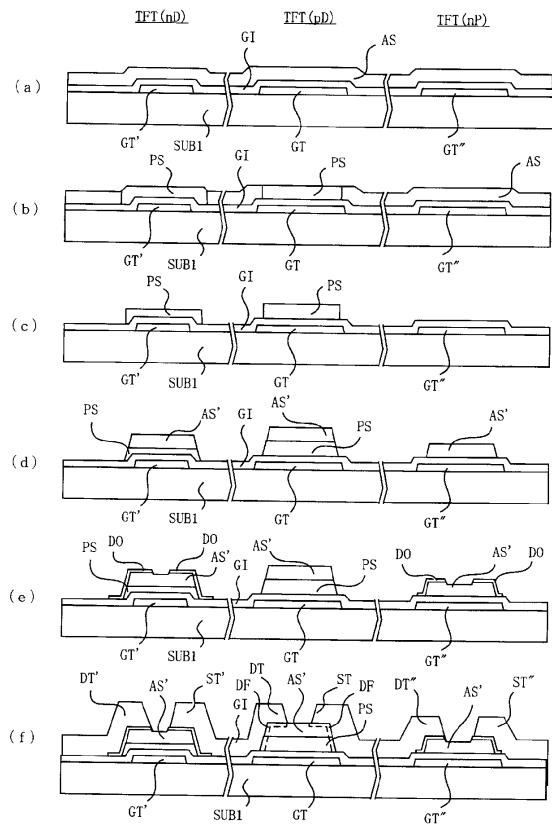

図7(a)ないし(f)は、本発明による表示装置の製造方法の他の実施例を示す工程図である。

## 【0082】

図7に示す表示装置は、画素選択用に用いられるn型薄膜トランジスタTFT(nP)の半導体層をアモルファスSiとしたものであり、図7(a)ないし(f)の工程図は、該n型薄膜トランジスタTFT(nP)とともに、駆動回路の前記n型薄膜トランジスタTFT(nD)とp型薄膜トランジスタTFT(pD)を形成する場合を示している。

## 【0083】

図中、左側にn型薄膜トランジスタTFT(nD)を、真ん中にp型薄膜トランジスタTFT(pD)を、右側にn型薄膜トランジスタTFT(nP)を示している。以下、工程順に説明をする。

## 【0084】

## 工程1.(図7(a))

たとえばガラスからなる基板SUB1の表面に、ゲート電極GT'、ゲート電極GT、およびゲート電極GT"を形成し、これらゲート電極GT'、ゲート電極GT、およびゲート電極GT"をも被って絶縁膜GIを形成する。

## 【0085】

前記ゲート電極GT'、ゲート電極GT、およびゲート電極GT"は、いずれも、たとえばモリブデン(Mo)等の高融点金属またはその合金をたとえばスパッタリングで成膜(膜厚50~150nm)し、フォトリソグラフィ技術による選択エッチングで形成する。

## 【0086】

前記絶縁膜GIは、たとえばSiO、SiN、あるいはこれらの積層膜で構成され、膜厚100~300nmで形成する。

## 【0087】

そして、前記絶縁膜GIの上面の全域に、アモルファスSiからなる半導体層ASをたとえばCVD(Chemical Vapor Deposition)によって膜厚50~300nmで形成する。

## 【0088】

## 工程2.(図7(b))

前記半導体層ASに、脱水素処理を行った後に、選択的に、パルスあるいは連続発振レーザを照射し、n型薄膜トランジスタTFT(nD)の形成領域およびp型薄膜トランジスタTFT(pD)の形成領域における前記半導体層ASの結晶化を行い、ポリSiから

10

20

30

40

50

なる半導体層 P S を形成する。この場合、前記半導体層 A S の結晶化は全面に施すようにしてもよい。

【 0 0 8 9 】

工程 3 . ( 図 7 ( c ) )

前記半導体層 A S をフォトリソグラフィ技術による選択エッチングをすることにより、n 型薄膜トランジスタ TFT ( n D ) の形成領域および p 型薄膜トランジスタ TFT ( p D ) の形成領域に、それぞれ、ポリ Si からなる半導体層 P S を残存させる。

【 0 0 9 0 】

工程 4 . ( 図 7 ( d ) )

前記基板 SUB 1 の表面に、たとえば CVD ( Chemical Vapor Deposition ) を用いて、アモルファス Si からなる半導体層 A S ' を膜厚 50 ~ 250 nm で形成し、この半導体層 A S ' をフォトリソグラフィ技術による選択エッチングをすることにより、n 型薄膜トランジスタ TFT ( n D ) 、 p 型薄膜トランジスタ TFT ( p D ) 、および n 型薄膜トランジスタ TFT ( n P ) の各形成領域に残存させる。

10

【 0 0 9 1 】

このため、n 型薄膜トランジスタ TFT ( n D ) における半導体層 A S ' は前記半導体層 P S に積層され、p 型薄膜トランジスタ TFT ( p D ) における半導体層 A S ' は前記半導体層 P S に積層されて形成される。また、n 型薄膜トランジスタ TFT ( n P ) における半導体層 A S 0 ' は絶縁膜 GI 上に直接形成される。

【 0 0 9 2 】

20

すなわち、n 型薄膜トランジスタ TFT ( n D ) p 型薄膜トランジスタ TFT ( p D ) のそれぞれの半導体層は、ポリ Si の半導体層 P S とアモルファス Si の半導体層 A S の順次積層体として構成されることになる。

【 0 0 9 3 】

工程 5 . ( 図 7 ( e ) )

基板 SUB 1 の表面の全域に、たとえば CVD ( Chemical Vapor Deposition ) を用い、たとえばリン ( P ) がドープされた半導体層 ( n ( + ) 型半導体層 ) を厚さ 10 ~ 50 nm で形成する。

【 0 0 9 4 】

そして、前記 n ( + ) 型半導体層を、フォトリソグラフィ技術によるエッチングによって、n 型薄膜トランジスタ TFT ( n D ) の半導体層 SC ' の上面、および n 型薄膜トランジスタ TFT ( n P ) の半導体層 A S ' の上面にそれぞれ残存させ、この残存された前記 n ( + ) 型半導体層を n 型薄膜トランジスタ TFT ( n D ) のコンタクト層 DO 、 n 型薄膜トランジスタ TFT ( n P ) のコンタクト層 DO とする。前記 n ( + ) 型半導体層のエッチングは、n 型薄膜トランジスタ TFT ( n D ) のチャネル領域、および n 型薄膜トランジスタ TFT ( n P ) のチャネル領域となる部分においてもなされるようになっている。

30

【 0 0 9 5 】

工程 6 . ( 図 7 ( f ) )

基板 SUB 1 の表面の全域に、たとえばスパッタリングによって、アルミニウム ( Al ) を膜厚 300 ~ 500 nm で成膜する。

40

【 0 0 9 6 】

この際、 Al 層の上下のそれぞれの面に、チタン ( Ti ) あるいはモリブデン ( Mo ) 等の高融点金属膜を膜厚 30 ~ 100 nm で形成するようにする。この高融点金属膜は、いわゆるバリアメタル層と称し、コンタクト抵抗の低減のために形成される。

【 0 0 9 7 】

その後、前記 Al 層をフォトリソグラフィ技術による選択エッチングをすることによって、n 型薄膜トランジスタ TFT ( n D ) の形成領域においてドレイン電極 DT ' およびソース電極 ST ' を、 p 型薄膜トランジスタ TFT ( p D ) の形成領域においてドレイン電極 DT およびソース電極 ST を、 n 型薄膜トランジスタ TFT ( n P ) の形成領域にお

50

いてドレイン電極 D T "およびソース電極 S T "を形成する。

【0098】

さらに、基板 S U B 1 の表面の全域に、n 型薄膜トランジスタ T F T ( n D ) 、 p 型薄膜トランジスタ T F T ( p D ) 、 および n 型薄膜トランジスタ T F T ( n P ) を被って、たとえば C V D ( Chemical Vapor Deposition ) を用い、たとえば S i N 膜からなる保護膜(図示せず)を形成する。

【0099】

そして、 H 2 あるいは N 2 の雰囲気中、 350 ~ 450 の温度で 1 ~ 3 時間のアニールを行う。このアニールによって、 p 型薄膜トランジスタ T F T ( p D ) のドレイン電極 D T 、 およびソース電極 S T 内のアルミニウム( A 1 )が半導体層 S C 内に拡散(前記バリアメタル層を通して拡散)され、前記ドレイン電極 D T と半導体層 S C の界面、 および前記ソース電極 S T と半導体層 S C の界面に、 それぞれ、 p ( + ) 型の拡散層 D F が形成されるようになる。なお、このアニールは、前記保護膜の形成前に行ってもよい。

【0100】

上述した各実施例はそれぞれ単独に、あるいは組み合わせて用いても良い。それぞれの実施例での効果を単独であるいは相乗して奏することができるからである。

【図面の簡単な説明】

【0101】

【図1】本発明による表示装置の基板上に形成される p 型薄膜トランジスタの一実施例を示す構成図である。

20

【図2】本発明による表示装置の基板上に形成される p 型薄膜トランジスタと n 型薄膜トランジスタの一実施例を示す構成図である。

【図3】図2に示した p 型薄膜トランジスタと n 型薄膜トランジスタのそれぞれの特性を示したグラフである。

【図4】図2に示した p 型薄膜トランジスタと n 型薄膜トランジスタの製造方法の一実施例を示した工程図である。

【図5】本発明による表示装置の基板上に形成される p 型薄膜トランジスタと n 型薄膜トランジスタの他の実施例を示す構成図である。

【図6】図6に示した p 型薄膜トランジスタと n 型薄膜トランジスタの製造方法の一実施例を示した工程図である。

30

【図7】本発明による表示装置の製造方法の他の実施例を示す図で、駆動回路内の p 型薄膜トランジスタと n 型薄膜トランジスタと、画素内の n 型薄膜トランジスタの製造の工程図である。

【図8】本発明による表示装置の一実施例を示す概略構成図である。

【符号の説明】

【0102】

S U B 1 、 S U B 2 ..... 基板、 A R ..... 液晶表示領域、 G L ..... ゲート信号線、 D L ..... ドレイン信号線、 C L ..... 対向電圧信号線、 T F T ( n P ) ..... n 型薄膜トランジスタ(画素内)、 P X ..... 画素電極、 C T ..... 対向電極、 D R C ..... 駆動回路、 C S C ..... R G B 切換回路、 T F T ( n D ) ..... n 型薄膜トランジスタ(駆動回路内)、 T F T ( p D ) ..... p 型薄膜トランジスタ(駆動回路)、 G T 、 G T ' 、 G T " ..... ゲート電極、 G I ..... 絶縁膜、 D T 、 D T ' 、 D T " ..... ドレイン電極、 S T 、 S T ' 、 S T " ..... ソース電極、 S C ..... 半導体層、 D F ..... 拡散層、 D O ..... コンタクト層、 A S ..... アモルファス S i 、 P S ..... ポリ S i 、 B R ..... 拡散バリア層。

40

【図1】

【図2】

【図3】

(a)

(b)

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

G 0 2 F 1/1345

(72)発明者 大植 栄司

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

(72)発明者 海東 拓生

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

(72)発明者 宮沢 敏夫

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

審査官 棚田 一也

(56)参考文献 特開平10-135480 (JP, A)

特開平05-063196 (JP, A)

特開2004-104101 (JP, A)

特開2006-179878 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8 6

G 0 2 F 1 / 1 3 4 5

H 0 1 L 2 1 / 3 3 6