(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6328131号

(P6328131)

(45) 発行日 平成30年5月23日(2018.5.23)

(24) 登録日 平成30年4月27日(2018.4.27)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| HO4R 31/00   | (2006.01)  |

| HO4R 19/00   | (2006.01)  |

| B81C 1/00    | (2006.01)  |

| B81B 3/00    | (2006.01)  |

| A61B 8/00    | (2006.01)  |

| HO4R 31/00   | HO4R 31/00 |

| HO4R 19/00   | HO4R 19/00 |

| B81C 1/00    | B81C 1/00  |

| B81B 3/00    | B81B 3/00  |

| A61B 8/00    | A61B 8/00  |

請求項の数 12 (全 22 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-542385 (P2015-542385)  |

| (86) (22) 出願日 | 平成25年11月6日 (2013.11.6)        |

| (65) 公表番号     | 特表2015-536622 (P2015-536622A) |

| (43) 公表日      | 平成27年12月21日 (2015.12.21)      |

| (86) 國際出願番号   | PCT/IB2013/059932             |

| (87) 國際公開番号   | W02014/080310                 |

| (87) 國際公開日    | 平成26年5月30日 (2014.5.30)        |

| 審査請求日         | 平成28年11月1日 (2016.11.1)        |

| (31) 優先権主張番号  | 61/728,339                    |

| (32) 優先日      | 平成24年11月20日 (2012.11.20)      |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 590000248<br>コーニンクレッカ フィリップス エヌ<br>ヴェ<br>KONINKLIJKE PHILIPS<br>N. V.<br>オランダ国 5656 アーネー アイン<br>ドーフェン ハイテック キャンパス 5<br>High Tech Campus 5,<br>NL-5656 AE Eindhoven<br>n<br>(74) 代理人<br>110001690<br>特許業務法人M&Sパートナーズ |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

最終頁に続く

(54) 【発明の名称】容量性マイクロマシントラנסデューサ及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

容量性マイクロマシントラنسデューサを製造する方法であって、

第1の電極層を堆積するステップと、

前記容量性マイクロマシントラنسデューサのキャビティを形成するために除去可能で

ある犠牲層を堆積させるステップと、

第2の電極層を堆積するステップと、

エッチングホールを設け、前記犠牲層をエッチングすることによって、前記犠牲層を除

去して、上面、底面及び側面を備える前記キャビティを形成するステップと、

原子層堆積によって、前記キャビティ内で、前記第1の電極層上に第1の誘電体膜を、

前記第2の電極層上に第2の誘電体膜を堆積させるステップとを含み、

堆積された前記第1の誘電体膜及び堆積された前記第2の誘電体膜は、前記キャビティ

の前記上面、前記底面及び前記側面を覆う、方法。

## 【請求項 2】

前記犠牲層を除去するステップの前に、堆積された層の少なくとも1つをパターニング

するステップを含む、請求項1に記載の方法。

## 【請求項 3】

前記犠牲層を除去するステップの前に、原子層堆積によって、前記犠牲層上に前記第2

の電極層を堆積させるステップと、前記第2の電極層をパターニングするステップとを更

に含む、請求項2に記載の方法。

**【請求項 4】**

前記犠牲層を除去するステップの前に、原子層堆積によって、基板上に前記第1の電極層を堆積させるステップと、前記第1の電極層をパターニングするステップとを更に含む、請求項2に記載の方法。

**【請求項 5】**

原子層堆積によって、前記犠牲層を堆積させるステップと、前記犠牲層をパターニングするステップとを更に含む、請求項2に記載の方法。

**【請求項 6】**

前記犠牲層を除去するステップの前に、原子層堆積によって、前記犠牲層を覆う誘電体層を堆積させるステップを更に含む、請求項1に記載の方法。 10

**【請求項 7】**

基板上の第1の電極層と、

前記第1の電極層上の第1の誘電体膜と、

前記第1の誘電体膜の上方に形成されるキャビティと、

前記キャビティを覆う第2の誘電体膜と、

前記第2の誘電体膜上の第2の電極層と、

前記基板の中に組み込まれたASICと、

を含み、

前記第1の誘電体膜及び前記第2の誘電体膜は、前記キャビティの上面及び底面だけではなく、側面も覆っており、 20

前記ASICは、前記基板の中に埋め込まれた伝導性ピアによって前記第1の電極層に接続されており、

前記伝導性ピアは、前記基板を通じて、前記ASICから前記第1の電極層へ延びている、

容量性マイクロマシントラنسデューサ。

**【請求項 8】**

前記堆積された層の少なくとも1つはパターニングされる、請求項7に記載のトランスデューサ。

**【請求項 9】**

前記第1の電極層及び／又は前記第2の電極層は、非金属伝導材料を含み、前記非金属伝導材料は、TiN、TaN、TaCN、IrO<sub>2</sub>、ITO、LaNiO<sub>3</sub>及びSrRuO<sub>3</sub>を含む群から選択される少なくとも1つの材料である、請求項7に記載のトランスデューサ。 30

**【請求項 10】**

前記少なくとも1つのパターニングされた層及び／又は膜は、前記層及び／又は膜の側部において、突然に又は非連続的に終端する、請求項8に記載のトランスデューサ。

**【請求項 11】**

前記堆積された層及び膜を覆う誘電体層を更に含み、前記誘電体層は、前記堆積された層及び膜の上面及び側面を、実質的に同じ被覆率で覆う、請求項7に記載のトランスデューサ。 40

**【請求項 12】**

前記第1の誘電体膜及び／又は前記第2の誘電体膜は、酸化物を含む第1の層と、高k材料を含む第2の層と、酸化物を含む第3の層とを含む、請求項7に記載のトランスデューサ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、容量性マイクロマシントラансデューサ、特に超音波を送信及び／又は受信する容量性マイクロマシン超音波トランスデューサ(CMUT)を製造する方法に関する 50

。本発明は更に、容量性マイクロマシントラスデューサ、特に超音波を送信及び／又は受信する容量性マイクロマシン超音波トランスデューサに関する。

#### 【背景技術】

##### 【0002】

あらゆる超音波（撮像）システムの心臓部は、電気エネルギーを音響エネルギーに、また、音響エネルギーを電気エネルギーに変換するトランスデューサである。従来では、これらのトランスデューサは、リニア（1D）トランスデューサアレイに配置された圧電性結晶から作られ、最大10MHzの周波数において動作する。しかし、マトリクス（2D）トランスデューサアレイへの傾向及び超音波（撮像）機能を、カーテルやガイドワイヤ内に組み込む小型化への動きは、いわゆる容量性マイクロマシン超音波トランスデューサ（CMUT）の開発をもたらした。CMUTは、メンブレン（又はダイアフラム）と、メンブレン下のキャビティと、コンデンサを形成する電極とを含む。超音波の受信には、超音波がメンブレンを動かし又は振動させ、電極間の電気容量変化が検出される。これにより、超音波は、対応する電気信号に変換される。反対に、電極に印加される電気信号が、メンブレンを動かし又は振動させ、これにより、超音波が送信される。10

##### 【0003】

しかし、帯電は、容量性マイクロマシン超音波トランスデューサの知られている欠点である。国際特許公開公報WO2010/032156A2に、帯電問題を解決する特定の層構造体を有する容量性マイクロマシン超音波トランスデューサが説明されている。誘電体を含む第1の絶縁層が、第1の電極と第2の電極との間に配置される。更に、誘電体を含む第2の絶縁層が、第2の電極とキャビティとの間に配置されてもよい。特に、いわゆるONO（酸化物・窒化物・酸化物）誘電体層が、帯電に対する解決策を提供する。20

##### 【0004】

国際特許公開公報WO2010/032156A2では、第1の誘電体絶縁層と第2の誘電体絶縁層とは、第1の電極及び第2の電極を絶縁する。このような誘電体絶縁層は、かなりの程度まで、CMUTデバイスの全体的性能を決定する。理想的なケースでは、誘電体絶縁層は、非常に薄いか、又は、高誘電率及び高絶縁破壊電圧を有する。しかし、ONO誘電体層にも限界があり、比較的厚い層（例えば「プラズマ化学気相成長法（PECVD）」を使用して約250nm）の上にしか堆積できず、また、窒化物の誘電率が、約5乃至7であるため、誘電率が低い。したがって、CMUTの性能は、ONO誘電体層の最小厚さ、電気絶縁破壊電圧及びその誘電率によって制限される。このようなCMUTデバイスの特定の問題は、動作電圧がかなり高く、出力圧力が比較的低いことである。したがって、当該CMUTを更に向上させる必要性がある。30

#### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

本発明は、特に性能が向上され（例えば動作電圧が減少され及び／又は出力圧力が増加され）、及び／又は、製造が容易である改良された容量性マイクロマシントラスデューサ（特に、CMUT）を提供することを目的とする。本発明は更に、そのような容量性マイクロマシントラスデューサ（特に、CMUT）を製造する改良された方法を提供することを目的とする。40

##### 【課題を解決するための手段】

##### 【0006】

本発明の第1の態様では、容量性マイクロマシントラスデューサ、特に、CMUTを製造する方法が提示される。当該方法は、容量性マイクロマシントラスデューサのキャビティを形成するために除去可能である犠牲層を堆積させるステップと、エッチングホールを設け、キャビティを形成するために犠牲層をエッチングすることによって、犠牲層を除去するステップとを含み、原子層堆積によって、キャビティ内に第1の電極層及び第2の電極層を堆積させるステップ、及び／又は、原子層堆積によって、キャビティ内で、第1の電極層上に第1の誘電体膜を、第2の電極層上に第2の誘電体膜を堆積させるステッ50

のうちの少なくとも 1 つが続いて行われる。

【0007】

本発明の更なる態様では、本発明の方法によって製造される容量性マイクロマシントラ nsデューサ、特に、CMUTが提示される。

【0008】

本発明の更なる態様では、基板上の第1の電極層と、第1の電極層上の第1の誘電体膜と、第1の誘電体膜の上方に形成されるキャビティと、キャビティを覆う第2の誘電体膜と、第2の誘電体膜上の第2の電極層とを含み、第1の誘電体膜及び第2の誘電体膜は、キャビティの上面及び底面だけでなく、側面も覆う、容量性マイクロマシントラ nsデューサ、特に、CMUTが提示される。

10

【0009】

本発明の基本的な考え方の1つは、製造方法に原子層堆積(AlD)を使用することである。AlD技術は、現行の処理の限界、従って、CMUT性能限界を解決する利点及びオプションを提供する。すべてのCMUT機能層が、特に、従来技術の処理では一般に必要である基板を周囲環境に晒すことなく、制御された環境下において、1回の単一処理手順で堆積される製造方法が提供される。CMUT機能層は、具体的には、第1の電極層(第1の電極を提供する)、第1の誘電体膜(電気絶縁を提供する)、犠牲層(キャビティを形成する)、第2の誘電体膜(電気絶縁を提供する)及び第2の電極層(第2の電極を提供する)である。この処理は、全層AlD(Al\_ALD) CMUT処理とも呼ばれる。このようにして、堆積層(又は膜)のスタックを有するウェーハが実現される。ウェーハは、層スタックを成長させている間、AlDマシンから離れないため、非常にきれいな物質界面が実現される。更に、個々の層及び界面の、例えば応力及び帯電特性を制御及び微調整することによって、性能が向上される。

20

【0010】

本発明は、CMUTデバイス性能を著しく向上させることに関する。CMUTデバイスを実現する1つの重要な処理ステップが、犠牲層をエッチングすることによって、キャビティの開口を形成する。このステップは更に、デバイス性能に著しく影響を及ぼす。本発明は、最初に、犠牲層をエッチングすることによってキャビティを実現し、続いて、既に存在している開口を介して、AlDによって、誘電体膜及び/又は金属層(電極層)を成長させることを提案する。これによって、キャビティを完全にきれいにすることができる。次に、誘電体膜及び/又は電極層が追加されるが、これらは、後から追加されることによって、堆積後の化学物質による攻撃を受けない。この処理オプションを適用することによって、例えば個々の層及びそれらの界面の応力及び帯電特性を制御及び微調整することによって、従来の処理、即ち、完全な「上から下への」パターニングにおいては不可能であった更なる性能向上が期待される。しかし、キャビティは、依然として、犠牲層をエッチングすることによって開けられる必要があり、エッチング後の残留物は、デバイス動作中の帯電の重要な原因となりうる。この新しい提案における重要なポイントは、最初にキャビティを実現し、次に当該キャビティ内で電極層及び誘電体膜を堆積させた後は、当該キャビティ内で追加の処理ステップが不要であり、これにより、誘電体層上の残留物のリスクを最小限にすることである。犠牲層の除去後、したがって、キャビティを開けた後、AlDによって少なくとも誘電体膜が付与されると、当該誘電体膜は、エッチング化学物質によって攻撃を受けず、これらの誘電体層上に、エッチャント残留物はない。したがって、具体的には、キャビティをエッチング残留物がないようにきれいにするステップが、犠牲層をエッチングするステップ後で、AlDによってキャビティ内で第1及び第2の電極層並びに/又は第1及び第2の誘電体膜を堆積させる前に、行われる。製造方法は、部分的に、特に「上から下への」パターニングを使用する。上から下へのパターニングは、CMUTに、特徴的なピラミッド構造、特に階段状ピラミッド構造を与える。この典型的な横断面は、例えばFIB又はSEM(走査型電子顕微鏡)横断面を使用する分析方法を介して特定される。パターニングとは、構造体(例えば堆積層のスタック)にパターンが形成されることを意味する。パターニングは、例えば感光層が露光される(光

30

40

50

) リソグラフィを使用して行われる。露光ツールは、ステッパーと呼ばれる。レジストと呼ばれる感光層が現像される。パターンは、層内にエッチングで付けられてもよい。エッチング処理は、「湿式」処理であっても「乾式」処理であってもよい。

#### 【0011】

原子層堆積は、気相化学処理の連続使用に基づく薄膜堆積技術である。ALD反応の大部分は、通常「前駆物質」と呼ばれる2つの化学物質を使用する。これらの前駆物質は、1回ずつ、連続的に、表面と反応する。前駆物質を成長面に繰り返し晒すことによって、薄膜が堆積される。ALDは、様々な組成の基板上に、材料の共形薄膜を堆積させる自己制限的（即ち、各反応サイクルにおいて堆積される薄膜材料量は一定である）な連続界面化学である。ALDによって堆積された層は、通常、アモルファスである。ALDによって堆積された層は、通常、高品質で、ピンホールがなく、低温で堆積できる。低処理温度によって、ALDは、CMOSと相性が良い。誘電体絶縁層がより薄くなると、低動作電圧で出力圧力が大きくなり、受信感度が向上される。これは、メンブレンが、電極間の電気力によってキャビティの底部への方向に引き寄せられることによる。薄い誘電体膜又は高誘電率を有する材料（高イフシロン材料又は高k材料とも呼ぶ）は、この電気力を著しく増加させ、これは、（クーロンの逆二乗の法則に基づいて）より大きい出力電力を生成するか又は受信感度を増加させる。これは、特に、陥没モード（即ち、例えば電極間にバイアス電圧を印加することによって、メンブレンが、動作中、キャビティの底部に部分的に接触する）で動作されるCMUTの場合に成り立つが、一般に、非陥没モードのCMUTの場合にも成り立つ。10

#### 【0012】

本発明の好適な実施形態は、従属請求項において規定される。当然ながら、請求項に係るCMUTは、請求項に係る方法及び従属請求項において規定される実施形態と同様の及び／又は同一の好適な実施形態を有する。同様に、当然ながら、請求項に係る方法は、請求項に係るCMUT及び従属請求項において規定される実施形態と同様の及び／又は同一の好適な実施形態を有する。20

#### 【0013】

特に好適な実施形態では、第1の誘電体膜及び／又は第2の誘電体膜は、酸化物を含む第1の層と、高k材料を含む第2の層と、酸化物を含む第3の層とを含む。したがって、誘電体絶縁層は、酸化物層（O）と、高k層と、別の酸化物層（O）とを含む。つまり、高k層は、2つの酸化物層（特にシリコーン酸化物）の間に挟まれている。これが、いわゆるラミネートである。高kは、高誘電率（例えば8以上）を指す。誘電率は、一般に、文字k（又は<sub>r</sub>とも）によって略記される。このようにすると、トランスデューサ性能は、ONO誘電体絶縁層に比べて、著しく向上される（例えば低動作電圧においてより大きい出力圧力）。したがって、ONO誘電体絶縁層を、原子層堆積（ALD）によって堆積された高k材料によって置換することによって、動作電圧及び出力圧力に関して、CMUT性能が著しく向上される。更に、ONO誘電体絶縁層に比べて、デバイスの安定性に関する同様の性能（特に時間に対する安定した出力）を達成できる。つまり、ラミネートは、超音波出力をドリフトさせる電荷を蓄積しない。30

#### 【0014】

本実施形態の変形態様では、高k材料は、酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）及び／又は酸化ハフニウム（HfO<sub>2</sub>）である。酸化アルミニウム（7乃至9、特に約8又は9のk又は<sub>r</sub>）又は酸化ハフニウム（12乃至27、特に約14又は20のk又は<sub>r</sub>）は、高い誘電率を有する。一例では、酸化物-酸化アルミニウム-酸化物（OAO）からなるラミネート（交互層）がこのように提供される。別の例では、酸化物-酸化ハフニウム-酸化物（OH<sub>2</sub>O）からなるラミネート（交互層）がこのように提供される。40

#### 【0015】

本実施形態の別の変形態様では、第2の層が、酸化アルミニウムを含む第1の副層と、酸化ハフニウムを含む第2の副層と、酸化アルミニウムを含む第3の副層とを含む。このようにして、酸化物-酸化アルミニウム-酸化ハフニウム-酸化アルミニウム-酸化物（50

O A H A O ) からなるラミネート ( 交互層 ) が提供される。酸化アルミニウム ( アルミナとも呼ぶ ) は、高い電気絶縁破壊電圧と組み合わされる高い誘電率を有する。酸化ハフニウムは、より高い誘電率を有するが、絶縁破壊電圧は低い。したがって、O A H A O 誘電体絶縁層は、低応力、高誘電率及び高絶縁破壊電圧を組み合わせる。

#### 【 0 0 1 6 】

別の変形態様では、第 2 の層は、100 nm 未満の厚さを有する。したがって、非常に薄い高 k 層が、特に A L D を使用して、提供される。

#### 【 0 0 1 7 】

一実施形態では、犠牲層を除去するステップの前に、堆積層の少なくとも 1 つがパターニングされる。具体的には、エッチングの前に堆積された C M U T 機能層の少なくとも 1 つがパターニングされる。より具体的には、第 1 の電極層、犠牲層及び / 又は第 2 の電極層がパターニングされる。このパターニングは複数のステップ、例えば最上部層をパターニングする第 1 のステップと、最下部層をパターニングする第 2 のステップとを含む。各ステップにおいて、層は、異なる ( 層の上面に平行な方向における ) 横寸法を有するようにパターニングされる。このようにして、( 階段状 ) ピラミッド構造体が作られる。或いは、パターニングは、複数の層が同じ横寸法を有するようにパターニングされる単一のステップで行われてもよい。

10

#### 【 0 0 1 8 】

一実施形態では、パターニングは、犠牲層を除去するステップの前に、原子層堆積 ( A L D ) によって、犠牲層上に第 2 の電極層を堆積させるステップと、当該第 2 の電極層をパターニングするステップとを含む。このようにして、第 2 の電極の横寸法が規定される。例えば第 2 の電極層は、第 1 の電極層よりも小さいようにパターニングされる。このようにして、「上から下への」パターニングが ( 例えば第 1 のエッチングマスクを使用して ) 行われる。したがって、特徴的なピラミッド構造体、特に、階段状のピラミッド構造体が提供される。

20

#### 【 0 0 1 9 】

別の実施形態又は変形態様では、当該方法は、犠牲層を除去するステップの前に、原子層堆積によって、基板上に第 1 の電極層を堆積させるステップと、当該第 1 の電極層をパターニングするステップとを含む。別の実施形態又は変形態様では、当該方法は、原子層堆積によって、犠牲層を堆積させるステップと、当該犠牲層をパターニングするステップとを含む。犠牲層をパターニングすることによって、キャビティの横寸法が規定される。「上から下への」パターニングは、このようにして、( 例えば第 2 のエッチングマスクを使用して ) 更に行われる。犠牲層のパターニングは、第 2 の電極層をパターニングするステップとは別個のステップにおいて行われてもよい。或いは、犠牲層のパターニング及び第 2 の電極層のパターニングは、共通のステップにおいて行われてもよい。第 1 の電極層をパターニングすることによって、第 1 の電極の横寸法が規定される。「上から下への」パターニングは、このようにして、( 例えば第 3 のエッチングマスクを使用して ) 更に行われる。第 1 の電極層のパターニングは、第 2 の電極層をパターニングするステップ及び / 又は犠牲層をパターニングするステップとは別個のステップにおいて行われてもよい。或いは、第 1 の電極層のパターニング及び犠牲層のパターニングは、共通のステップにおいて行われてもよい。これは、第 2 の電極層のパターニングと共にステップにおいて行われてもよい。

30

#### 【 0 0 2 0 】

別の実施形態では、ほとんどの又はすべての堆積層及び膜がパターニングされる。具体的には、ほとんどの又はすべての A L D によって堆積された層及び膜がパターニングされる。具体的には、すべての C M U T 機能層がパターニングされる。より具体的には、第 1 の電極層、第 1 の誘電体膜、犠牲層、第 2 の誘電体膜及び第 2 の電極層がパターニングされる。このパターニングは複数のステップ、例えば最上部層をパターニングする第 1 のステップと、最下部層をパターニングする第 2 のステップとを含む。各ステップにおいて、層は、異なる ( 層の上面に平行な方向における ) 横寸法を有するようにパターニングされ

40

50

る。このようにして、(階段状)ピラミッド構造体が作られる。或いは、パターニングは、複数の層が同じ横寸法を有するようにパターニングされる単一のステップで行われてもよい。

#### 【0021】

別の実施形態では、当該方法は更に、堆積層を覆う誘電体層を堆積させるステップを含む。この堆積ステップは、特に、原子層堆積を使用して行われる。誘電体層は、特に、堆積層及び膜の上面及び側面を、実質的に同じ被覆率で覆う。これは、特に原子層堆積による非常に優れた階段状の被覆を提供する。

#### 【0022】

別の実施形態では、当該方法は更に、エッチングホールを設け、キャビティを形成するために犠牲層をエッチングすることによって、当該犠牲層を除去するステップを含む。このようにして、CMUTのキャビティが容易に(例えば第4のエッチングマスクを使用して)提供される。

10

#### 【0023】

別の実施形態では、第1の電極層及び/又は第2の電極層は、非金属伝導材料を含む。したがって、原子層堆積技術は、1つの単一処理手順の間にCMUTのあらゆる機能層を堆積させる独自のオプションを提供する。非金属伝導材料は、例えば半導体である。

#### 【0024】

本実施形態の変形態様では、非金属伝導材料は、TiN(窒化チタン)、TaN(窒化タンタル)、TaCN、IrO<sub>2</sub>(酸化イリジウム)、ITO(インジウムスズ酸化物)、LaNiO<sub>3</sub>及びSrRuO<sub>3</sub>(ルテニウム酸ストロンチウム)を含む群から選択される少なくとも1つの材料である。これらの材料は、原子堆積法に適している。本変形態様の変形態様において、非金属伝導材料は、TiN(窒化チタン)である。窒化チタンは、特に原子層堆積にとりわけ適している。例えば窒化チタンは、(例えばポリシリコーンに比べて)電気抵抗が低く、及び/又は、(例えばポリシリコーンに比べて)非常に薄い層として堆積できる。

20

#### 【0025】

別の実施形態では、第1及び第2の電極層は、それぞれ、キャビティの周りを、第1及び第2の誘電体膜に隣接して延在する。したがって、本実施形態では、犠牲層のエッチングの後、誘電体膜だけでなく、第1及び第2の電極層も、ALDによってキャビティ内に堆積される。最初に、第1及び第2の電極層が、ALDによってキャビティ内に堆積される。次に、第1及び第2の誘電体膜が、ALDによってキャビティ内に堆積される。したがって、キャビティは、誘電体膜によって囲まれる。また、キャビティとは反対側の誘電体膜の片側に、第1及び第2の電極層が、誘電体膜に隣接して位置付けられる。

30

#### 【0026】

代替の実施形態では、第1の電極層及び/又は第2の電極層は、金属伝導材料を含む。具体的には、金属伝導材料は、Ni(ニッケル)、銅(Cu)、W(タンゲスタン)、Pt(白銀)、Ir(イリジウム)及びAl(アルミニウム)を含む群から選択される少なくとも1つの材料を含む。例えば金属は、それらの合金であってもよい。

#### 【0027】

40

別の実施形態では、第1の誘電体膜及び/又は第2の誘電体膜は、炭素又は塩素残留物といった処理残留物を含む。これらの残留物は、ALD処理に使用される前駆物質の残余物である。これは、CMUTが原子層堆積を使用して製造されたことを示す。残留物は、例えばXPS(X線光電子分光法)又はSIMS(二次イオン質量分析)といった他の特性分析方法を使用して検出される。

#### 【0028】

別の実施形態では、少なくとも1つのパターニングされた層及び/又は膜は、その側部において、突然に又は非連続的に終端する。つまり、層の上面及び側面は、互いに実質的に直交する。これは、CMUTがパターニングを使用して製造されたことを示す。理想的には、層の上面と側面とは、互いに直交(90°)、又は直角である。しかし、実際には

50

、層は、パターニング処理（特にエッチング処理）が完全ではないことによって、幾らかの傾斜を有する、又は、意図的に傾斜が与えられる。また、様々な材料のエッチング速度も同じではない。したがって、様々な特性を有する層のスタックをパターニングする（特にエッチングする）場合、層の、その端における上面と側面とは、完全な直角とはならない。例えば張り出している構造が作成されてもよい。したがって、実質的に直交とは、 $70^\circ$ 乃至 $110^\circ$ （ $90^\circ \pm 20^\circ$ ）、 $80^\circ$ 乃至 $100^\circ$ （ $90^\circ \pm 10^\circ$ ）又は $85^\circ$ 乃至 $95^\circ$ （ $90^\circ \pm 5^\circ$ ）の角度であると理解される。

#### 【0029】

別の実施形態では、第2の電極層は、第2の電極層よりも小さくなるようにパターニングされる。これは、CMUTが「上から下への」パターニングを使用して製造されたことを示す。したがって、特徴的なピラミッド構造体、特に階段状のピラミッド構造体が提供される。10

#### 【0030】

別の実施形態では、CMUTは更に、第1の電極層及び／又は第2の電極層から、層の上面に直交する方向に延在する少なくとも1つの伝導性ビアを含む。したがって、伝導性ビアは、堆積層に直交又は直角である。このようにして、第1の電極、第2の電極、又は、両電極に電気的接続が提供される。例えば、伝導性ビアは、CMUTの下のASICに電気的に接続される。

#### 【0031】

別の実施形態では、CMUTは更に、堆積層及び膜を覆う誘電体層を含む。特に、誘電体層は、堆積層及び膜の上面及び側面を、同じ被覆率で覆う。これは、CMUTが、特に原子層堆積を使用して、非常に優れた階段状の被覆を提供することを示す。具体的には、誘電体層の垂直部は、堆積層及び／又は膜に実質的に直交して延在する。上記されたように、実質的に直交するとは、 $70^\circ$ 乃至 $110^\circ$ （ $90^\circ \pm 20^\circ$ ）、 $80^\circ$ 乃至 $100^\circ$ （ $90^\circ \pm 10^\circ$ ）又は $85^\circ$ 乃至 $95^\circ$ （ $90^\circ \pm 5^\circ$ ）の角度であると理解される。20

#### 【図面の簡単な説明】

#### 【0032】

本発明のこれらの及び他の態様は、以下に説明される実施形態を参照することにより明らかとなろう。

#### 【0033】

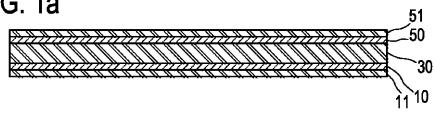

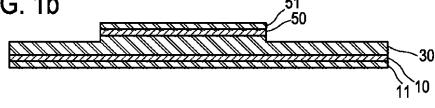

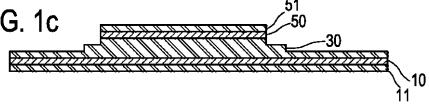

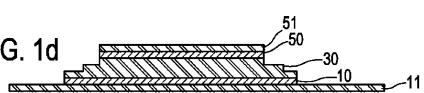

【図1a】図1aは、第1の実施形態によるCMUTを製造する方法を示す。30

【図1b】図1bは、第1の実施形態によるCMUTを製造する方法を示す。

【図1c】図1cは、第1の実施形態によるCMUTを製造する方法を示す。

【図1d】図1dは、第1の実施形態によるCMUTを製造する方法を示す。

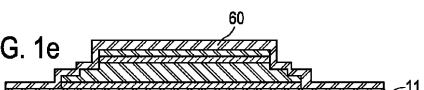

【図1e】図1eは、第1の実施形態によるCMUTを製造する方法を示す。

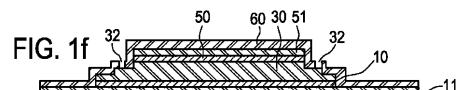

【図1f】図1fは、第1の実施形態によるCMUTを製造する方法を示す。

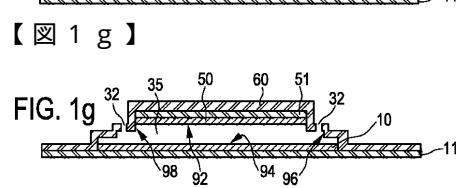

【図1g】図1gは、第1の実施形態によるCMUTを製造する方法を示す。

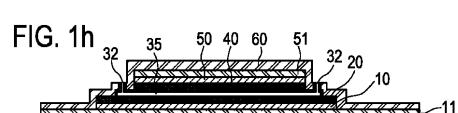

【図1h】図1hは、第1の実施形態によるCMUTを製造する方法を示す。

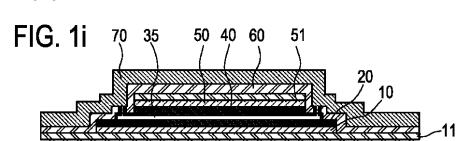

【図1i】図1iは、第1の実施形態によるCMUTを製造する方法を示す。

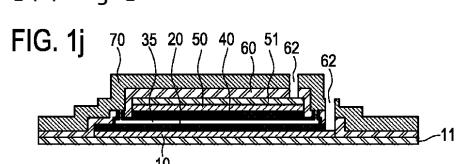

【図1j】図1jは、第1の実施形態によるCMUTを製造する方法を示す。

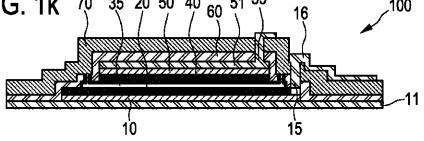

【図1k】図1kは、第1の実施形態によるCMUTの略横断面を示す。

【図2a】図2aは、第2の実施形態によるCMUTを製造する方法を示す。

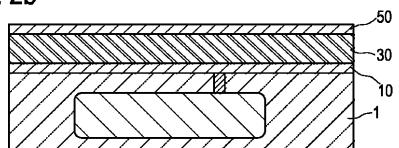

【図2b】図2bは、第2の実施形態によるCMUTを製造する方法を示す。

【図2c】図2cは、第2の実施形態によるCMUTを製造する方法を示す。

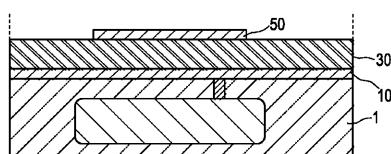

【図2d】図2dは、第2の実施形態によるCMUTを製造する方法を示す。

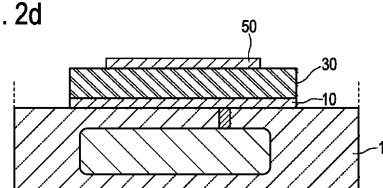

【図2e】図2eは、第2の実施形態によるCMUTを製造する方法を示す。

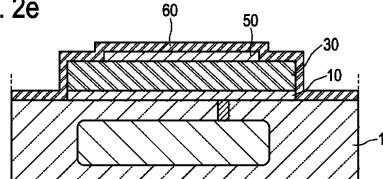

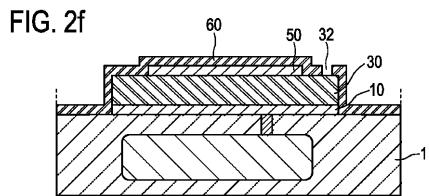

【図2f】図2fは、第2の実施形態によるCMUTを製造する方法を示す。

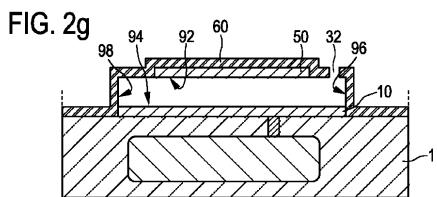

【図2g】図2gは、第2の実施形態によるCMUTを製造する方法を示す。

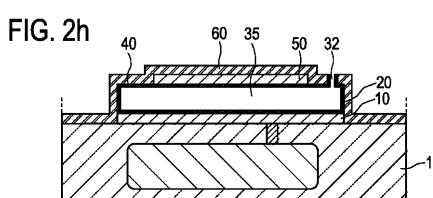

【図2h】図2hは、第2の実施形態によるCMUTを製造する方法を示す。

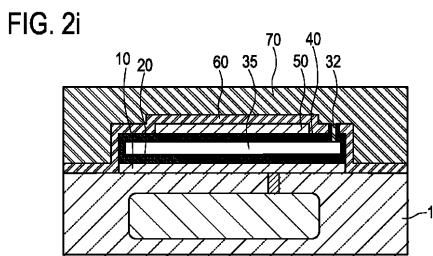

【図2i】図2iは、第2の実施形態によるCMUTを製造する方法を示す。

40

50

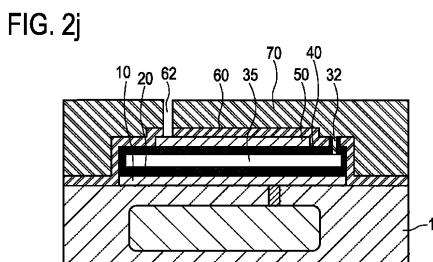

【図2 j】図2 jは、第2の実施形態によるCMUTを製造する方法を示す。

【図2 k】図2 kは、第2の実施形態によるCMUTの略横断面を示す。

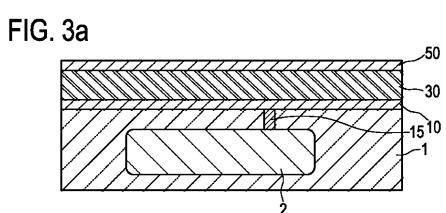

【図3 a】図3 aは、第3の実施形態によるCMUTを製造する方法を示す。

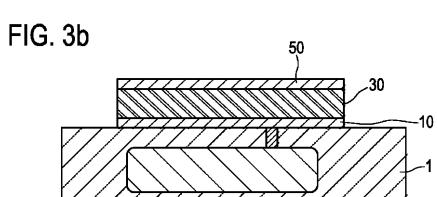

【図3 b】図3 bは、第3の実施形態によるCMUTを製造する方法を示す。

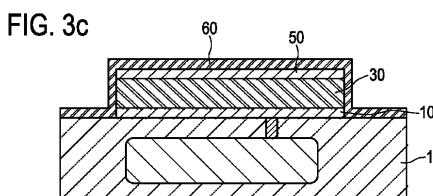

【図3 c】図3 cは、第3の実施形態によるCMUTを製造する方法を示す。

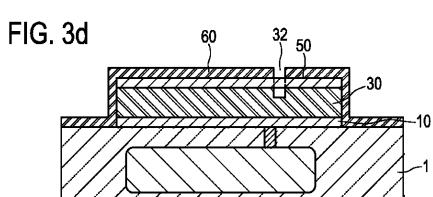

【図3 d】図3 dは、第3の実施形態によるCMUTを製造する方法を示す。

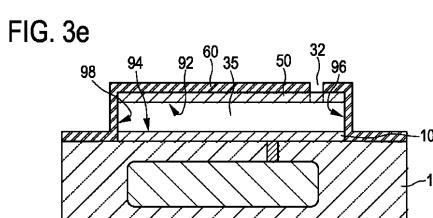

【図3 e】図3 eは、第3の実施形態によるCMUTを製造する方法を示す。

【図3 f】図3 fは、第3の実施形態によるCMUTを製造する方法を示す。

【図3 g】図3 gは、第3の実施形態によるCMUTを製造する方法を示す。

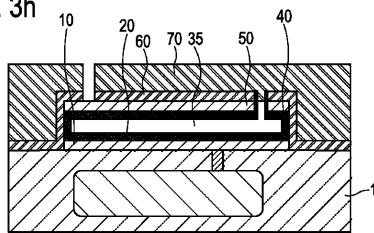

【図3 h】図3 hは、第3の実施形態によるCMUTを製造する方法を示す。

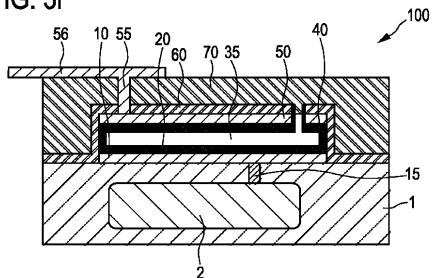

【図3 i】図3 iは、第3の実施形態によるCMUTの略横断面を示す。

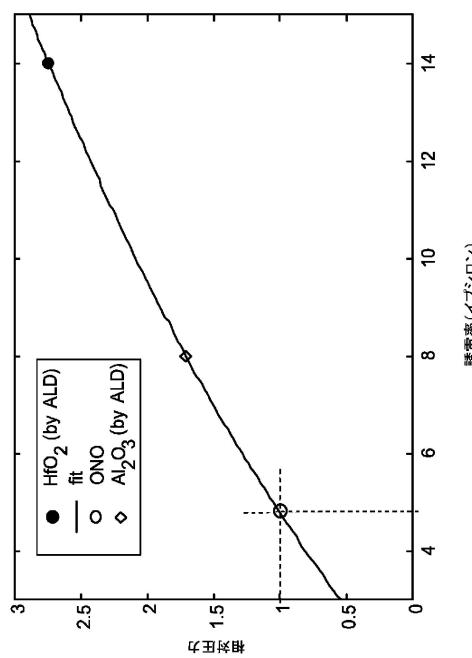

【図4】図4は、CMUTの誘電率(イブシロン)対相対音響出力圧力のグラフを示す。

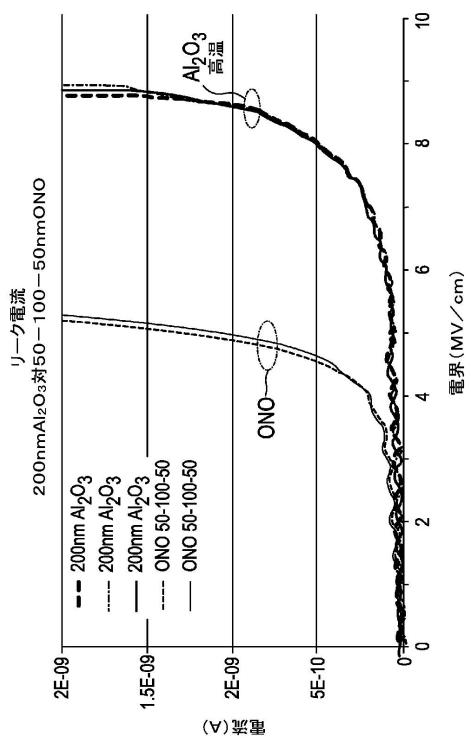

【図5】図5は、誘電体全体の電界対誘電体を流れる電流の例示的なグラフを示す。

#### 【発明を実施するための形態】

##### 【0034】

図1a～図1kは、第1の実施形態によるCMUT100を製造する方法を示す。特に、図1b～図1jは、原子層堆積(ALD)を使用して、1つの処理手順においてすべてのCMUT機能層が堆積された後(図1aを参照)の概略的な上から下への処理フローを示す。

##### 【0035】

当該方法は、ALDを使用する処理手順(図1aを参照)から開始する。まず、第1の電極層10が、基板(図示せず)又は誘電体層11上に堆積される。図1aに示される実施形態では、誘電体層11が、当該基板と第1の電極層10との間に提供又は堆積される。誘電体層11は、ここでは、基板上の第1の層である。この場合、誘電体層は、特に平坦化ステップがしばしば使用されて平滑面が作成されるASIC上で処理を行う場合は、例えば酸化(シリコン)又は窒化(シリコン)で作られる。しかし、誘電体層11は、省略されてもよい。次に、犠牲層30が、第1の電極層10上に堆積される。犠牲層30は、後にトランスデューサのキャビティを形成するために除去可能である。その次に、第2の電極層50が犠牲層30上に堆積される。図1aの実施形態では、追加の誘電体層51が、第2の電極層50上に堆積される。誘電体層51は、第2の電極層50を覆うか、又は、特に犠牲層30を除去するために犠牲エッチングが行われる際に、第2の電極層50を保護する。しかし、誘電体層51も省略されてもよい。上記されたこれらの堆積ステップは、それぞれ、原子層堆積(ALD)によって行われる。このようにすると、誘電体材料と伝導材料との交互の層からなるスタックが提供される(図1aを参照)。したがって、すべてのCMUT機能層(AL-ALD CMUT)は、ALDマシン内の1つの単一処理手順、即ち、單一ランで堆積される。つまり、ウェーハはマシンを離れないが、幾つかの(処理又は堆積)ステップが行われる。したがって、様々な材料が、1つの処理手順において互いの上に積み重ねられるが、材料は、この処理手順内の様々な(処理又は堆積)ステップで、次々と堆積される。この処理又は処理手順は、全層ALD(AL-ALD)CMUT処理とも呼ばれる。

##### 【0036】

当該方法は更に、堆積層10、30、50、51のうちの少なくとも1つをパターニングするステップを含む。当該パターニングの例は、図1b～図1dを参照して説明される。当該製造方法は、「上から下へ」のパターニングを使用する。上から下へのパターニングは、CMUTに、特徴的なピラミッド構造、特に階段状ピラミッド構造(その典型的な横断面は、例えばFIB又はSEM横断面を使用する分析方法を介して特定される)を与える。少なくとも1つのパターニングされた層及び/又は膜は、その側部において、突然に又は非連続的に終端する。つまり、1つの層の上面と側面とは、互いに実質的に直交する。これは、CMUTが、パターニングを使用して製造されたことを示す。理想的には、層の上面と側面とは、互いに直交(90°)する。しかし、実際には、層は、パターニン

10

20

30

40

50

グ処理（特にエッティング処理）が完全ではないことによって、幾らかの傾斜を有する、又は、意図的に傾斜が与えられる。また、様々な材料のエッティング速度も同じではない。したがって、様々な特性を有する層のスタックをパターニングする（特にエッティングする）場合、層の、その端における上面と側面とは、完全な直角とはならない。例えば張り出している構造が作成されてもよい。したがって、実質的に直交とは、 $70^\circ$ 乃至 $110^\circ$ （ $90^\circ \pm 20^\circ$ ）、 $80^\circ$ 乃至 $100^\circ$ （ $90^\circ \pm 10^\circ$ ）又は $85^\circ$ 乃至 $95^\circ$ （ $90^\circ \pm 5^\circ$ ）の角度であると理解される。

#### 【0037】

この第1の実施形態では、図1bから分かるように、パターニングは、第2の電極層50をパターニングする第1のステップを含む。これは、第1のエッティングマスク（「マスク1」とラベル付けされる）を使用して行われる。このようにして、第2の電極層50の（層の上面又は基板の上面に平行な方向における）横寸法、即ち、長さが規定される。この例では、第1のパターニングステップにおいて、第2の誘電体フィルム40も（更には、第2の電極層50上の追加の誘電体層51も）パターニングされる。図から分かるように、第2の電極層50は、第1の電極層10よりも小さく、即ち、長さが規定される。例えば第2の電極層50は、リング電極の形にパターニングされてもよい。これは、音響性能に有益である。パターニングは更に、図1cに示されるように、犠牲層30をパターニングする第2の（別個の）ステップを含む。これは、第2のエッティングマスク（「マスク2」とラベル付けされる）を使用して行われる。このようにして、CMUTのキャビティの（層の上面又は基板の上面に平行な方向における）横寸法、即ち、長さが規定される。更に、図1dに示されるように、パターニングは、第1の電極層10をパターニングする第3の（別個の）ステップを含む。これは、第3のエッティングマスク（「マスク3」とラベル付けされる）を使用して行われる。このようにして、第1の電極層10の（層の上面又は基板の上面に平行な方向における）横寸法、即ち、長さが規定される。この例では、複数のパターニングステップにおいて、犠牲層30もパターニングされる。この例では、基板上の誘電体層11のみがパターニングされない。したがって、（誘電体層11を除き）堆積層及び膜のほとんどが、パターニングされる。ALD堆積後のパターニングステップが完了する。すべての堆積CMUT機能層10、30、50、51がパターニングされる。

#### 【0038】

後続ステップにおいて、次に図1eを参照して、当該方法は、堆積層及び膜10、20、30、40、50、51を覆う誘電体層60を堆積させるステップを含む。この堆積ステップも、原子層堆積（ALD）を使用して行われる。或いは、PECVDといった別の技術が使用されてもよい。誘電体層60は、堆積層及び膜10、30、50、51の上面及び側面を、実質的に同じ被覆率で覆う（例えば誘電体層60の水平部の厚さと誘電体層60の垂直部の厚さとは実質的に同じである）。このようにして、非常に優れた階段状の被覆（step coverage）が提供される。つまり、誘電体層60の垂直部と誘電体層60の水平部の厚さとは、ほぼ同じ被覆率又は厚さを有する（図1eを参照）。誘電体層60の（層の上面又は基板の上面に直交する方向における）垂直部は、堆積層及び膜10、20、30、40、50、51に実質的に直交して延在する。理想的には、誘電体層60の垂直部は、堆積層及び膜に直交（ $90^\circ$ ）か、又は、直角にある。しかし、実際には、誘電体層60は、幾らかの傾斜を有する。したがって、誘電体層60の垂直部は、完全な直角ではない。したがって、実質的に直交とは、 $70^\circ$ 乃至 $110^\circ$ （ $90^\circ \pm 20^\circ$ ）、 $80^\circ$ 乃至 $100^\circ$ （ $90^\circ \pm 10^\circ$ ）又は $85^\circ$ 乃至 $95^\circ$ （ $90^\circ \pm 5^\circ$ ）の角度であると理解される。

#### 【0039】

次に、当該方法は、エッティングホール32（図1fを参照）、特に複数のエッティングホール（例えば3つ以上）を設け、キャビティ35（図1gを参照）を形成するために犠牲層30をエッティングすることによって、犠牲層30を除去するステップを含む。キャビティ35は、上面92、底面94及び側面96、98を有する。エッティングホール32の提

10

20

30

40

50

供は、第4のエッティングマスク（「マスク4」とラベル付けされる）を使用して行われる。エッティングホール32は、誘電体層60に設けられる。キャビティの（層の上面又は基板の上面に直交する方向における）高さは、除去される犠牲層30の厚さによって規定される。犠牲層30を除去して、キャビティ35を形成した後、キャビティ35は、エッティング処理からの任意の残留物がないようにきれいにされる。次に、第1の誘電体膜20及び第2の誘電体膜40が、キャビティ35内に、ALDによって堆積される（図1hを参照）。したがって、第1の誘電体膜20は、第1の電極層10を覆い、第2の誘電体膜40は、第2の電極層50を覆う。キャビティ内のALD処理によって、上面92及び底面94だけが誘電体膜によって覆われるのではなく、側面96、98も覆われる。

## 【0040】

10

次に、図1iを参照するに、誘電体層60を覆う追加の層70、具体的には、追加の誘電体層が提供される。追加層70は、エッティングホール32を閉じる又はシールする。

## 【0041】

更に、当該方法は、第1の電極層10及び第2の電極層50からそれぞれ、層の上面（又は基板の上面）に直交する方向に延在する少なくとも1つの伝導性ピア15、55を設けるステップを含む。したがって、伝導性ピア15、55は、堆積層に直交か、又は、直角である。この例では、これは、エッティングホール62を設け、当該エッティングホール62を伝導材料で埋めて、伝導性ピア15、55を形成することによって行われる。ここでは、（追加層70、誘電体層60及び第1の誘電体膜20を通り）第1の電極層10までつながる第1のエッティングホール62が設けられ、（誘電体層60及び追加層70を通り）第2の電極層50までつながる第2のエッティングホール62が設けられる。第1のエッティングホール62は、第1の電極層10からのピア15を形成するための伝導材料が埋められる。第2のエッティングホール62は、第2の電極層50からのピア55を形成するための伝導材料が埋められる。各ピア15、55からの（例えばASIC及び/又は電源への、例えばバイアス電圧に接続するための、又は、ケーブル若しくはワイヤボンドへの接続のための）外部電気接続を提供する伝導部16が提供される。このようにして、第1の電極10及び第2の電極50は共に、（例えばCMUTの下のASICへの）電気的接続が提供される。当然ながら、第1のエッティングホール、又は、第2のエッティングホールだけが設けられてもよい。例えば第1の電極10からの伝導性ピア15は、基板内にも形成されてもよい。

20

## 【0042】

30

更に、代替の方法では、第1の電極層10及び第2の電極層50は、キャビティ35が形成された後に、既に形成され、きれいにされたキャビティ35内にALDによって堆積されてもよい。この場合は、第1の電極層10及び第2の電極層50は、エッティングの前にパターニングされることによって形成される必要がない。

## 【0043】

40

図1kは、第1の実施形態によるCMUT100の略横断面を示す。図1kのCMUT100は、具体的には、図1を参照して上記された方法を使用して製造されている。CMUT100は、基板（図示せず）上の第1の（下部）電極層10と、第1の電極層10上の第1の誘電体膜20と、第1の誘電体膜20の上方に形成されるキャビティ35と、キャビティ35を覆う第2の誘電体膜40と、第2の誘電体膜40上の第2の（上部）電極層50とを含む。キャビティ内のALD処理によって、上面92及び底面94だけが誘電体膜によって覆われるのではなく、側面96、98も覆われる。任意選択的に、CMUT100は、誘電体層11及び誘電体層51を含んでもよい。堆積層及び膜のほとんどが、パターニングされる。本実施形態では、すべての堆積CMUT機能層及び膜10、20、30、40、50がパターニングされる。したがって、堆積CMUT機能層及び膜10、20、30、40、50のそれぞれがパターニングされる。第2の電極層50は、第1の電極層10よりも小さくなるようにパターニングされ（例えばリング電極の形にパターニングされ）、これは、音響性能に有益である。第2の電極層50は、キャビティ35よりも小さくなるようにパターニングされる。キャビティ35は、第1の電極層10よりも小さ

50

くなるようにパターニングされる。このようにして、特徴的な（階段状）ピラミッド構造体が提供される。C M U T 1 0 0 は更に、堆積層及び膜 1 0 、 2 0 、 3 0 、 4 0 、 5 0 を覆う誘電体層 6 0 を含む。誘電体層 6 0 は、上記されたように、堆積層及び膜 1 0 、 2 0 、 3 0 、 4 0 、 5 0 の上面及び側面を、実質的に同じ被覆率又は厚さで覆う。誘電体層 6 0 の垂直部は、堆積層 1 0 、 2 0 、 3 0 、 4 0 、 5 0 に実質的に直交して延在する。C M U T 1 0 0 は更に、誘電体層 6 0 を覆う追加層 7 0 を含む。特に、追加層 7 0 は、例えば 2 倍以上又は 5 倍以上で、他の層又は膜に比べて大幅に厚い（例えば層 4 0 の厚さが約 2 0 0 n m であるのに対し、層 7 0 の厚さは約 1 μ m である）。更に、C M U T は、第 1 の電極層 1 0 から、層の上面に直交する方向（図 1 k における垂直方向）に延在する伝導性ビア 1 5 を含む。また、C M U T 1 0 0 は、第 2 の電極層 5 0 から、層の上面に直交する方向（図 1 k における垂直方向）に延在する伝導性ビア 5 5 を含む。C M U T 1 0 0 は更に、各ビア 1 5 、 5 5 からの（例えば A S I C 及び / 又は電源への、例えばバイアス電圧に接続するための、又は、ケーブル若しくはワイヤボンドへの接続のための）外部電気接続を提供する伝導部 1 6 を含む。ビア 1 5 、 5 5 は、（層又は基板の上面に直交する）垂直方向に延在し、伝導部 1 6 は、（層又は基板の上面に平行な）水平方向に延在する。

10

#### 【 0 0 4 4 】

図 2 a ~ 図 2 k は、第 2 の実施形態による C M U T の製造方法を示す。本実施形態では、基板 1 が、その中に組み込まれた A S I C 2 と、基板内の伝導性ビア 1 5 とを含む。或いは、A S I C 2 は、基板 1 に取り付けられてもよい。当該方法は、第 1 の電極層 1 0 を基板 1 上に堆積させることから開始する。次に、犠牲層 3 0 が、第 1 の電極層 1 0 上に堆積される。犠牲層 3 0 は、後に、トランステューサのキャビティを形成するために除去可能である。次に、第 2 の電極層 5 0 が犠牲層 3 0 上に堆積される。これらの堆積ステップは、それぞれ、原子層堆積（ A L D ）によって行われる。このようにすると、誘電体材料と伝導材料との交互の層からなるスタックが提供される（図 2 b を参照）。したがって、すべての C M U T 機能層（ A L - A L D C M U T ）は、1 つの単一処理手順で堆積される。

20

#### 【 0 0 4 5 】

当該方法は更に、すべての堆積層 1 0 、 3 0 、 5 0 、具体的には、すべての堆積 C M U T 機能層 1 0 、 3 0 、 5 0 をパターニングするステップを含む。本実施形態では、パターニングは、第 2 の電極層 5 0 をパターニングする第 1 のステップ（図 2 c を参照）と、犠牲層 3 0 と第 1 の電極層 1 0 とをパターニングする第 2 の（別個の）ステップ（図 2 d を参照）と含む。したがって、本実施形態では、犠牲層 3 0 及び第 1 の電極層 1 0 は、共通ステップにおいてパターニングされる。第 2 の電極層 5 0 をパターニングする第 1 のステップは、第 1 のエッチングマスク（マスク 1 ）を使用して行われる。第 2 のパターニングステップは、第 2 のエッチングマスク（マスク 2 ）を使用して行われる。図面から分かるように、第 2 の電極層 5 0 は、第 1 の電極層 1 0 よりも小さくなるように（例えばリング電極の形に）パターニングされる。これにより、パターニングステップは完了する。

30

#### 【 0 0 4 6 】

後続ステップにおいて、図 2 e を参照するに、当該方法は、堆積層及び膜 1 0 、 3 0 、 5 0 を覆う誘電体層 6 0 を堆積させるステップを含む。この堆積ステップも、原子層堆積（ A L D ）を使用して行われる。誘電体層 6 0 は、上記されたように、堆積層及び膜 1 0 、 3 0 、 5 0 の上面及び側面を、実質的に同じ被覆率又は厚さで覆う。このようにして、非常に優れた階段状の被覆が提供される。つまり、誘電体層 6 0 の垂直部と誘電体層 6 0 の水平部とは、ほぼ同じ被覆率又は厚さを有する（図 2 e を参照）。誘電体層 6 0 の垂直部は、堆積層 1 0 、 3 0 、 5 0 に実質的に直交して延在する。

40

#### 【 0 0 4 7 】

次に、当該方法は、エッチングホール 3 2 （図 2 f を参照）を設け、キャビティ 3 5 （図 2 g を参照）を形成するために犠牲層 3 0 をエッチングすることによって、犠牲層 3 0 を除去するステップを含む。キャビティ 3 5 は、上面 9 2 、底面 9 4 及び側面 9 6 、 9 8 を有する。エッチングホール 3 2 は、誘電体層 6 0 に設けられる。エッチングホール 3 2

50

は、第3のエッティングマスク（マスク3）を使用して設けられる。犠牲層30を除去して、キャビティ35を形成した後、キャビティ35は、エッティング処理からの任意の残留物がないようにきれいにされる。次に、第1の誘電体膜20及び第2の誘電体膜40が、キャビティ35内に、ALDによって堆積される（図2hを参照）。したがって、第1の誘電体膜20は、第1の電極層10を覆い、第2の誘電体膜40は、第2の電極層50を覆う。キャビティ内のALD処理によって、上面92及び底面94だけが誘電体膜によって覆われるのではなく、側面96、98も覆われる。

#### 【0048】

次に、図2iを参照すると、誘電体層60を覆う追加の層70、具体的には、追加の誘電体層が提供される。追加層70は、エッティングホール32を閉じる又はシールする。

10

#### 【0049】

更に、当該方法は、第2の電極層50から、層の上面に直交する方向に延在する伝導性ピア55を設けるステップを含む。したがって、伝導性ピア55は、堆積層に直交、又は、直角である。この例では、これは、エッティングホール62（図2jを参照）を設け、当該エッティングホール62を伝導材料で埋めて、伝導性ピア55を形成する（図2kを参照）ことによって行われる。エッティングホール62の提供は、第4のエッティングマスク（マスク4）を使用して行われる。第1の電極10への伝導性ピア15は、基板1内に形成されている。更に、ピア55からの外部電気接続を提供する伝導部56が提供される。これは、追加層70上に導電層を堆積し、次に当該導電層をパターニングすることによって行われる。これは、第5のエッティングマスク（マスク5）を使用して行われる。

20

#### 【0050】

図2kは、第2の実施形態によるCMUT100の横断面を示す。図2kのCMUT100は、具体的には、図2を参照して上記された方法を使用して製造されている。CMUT100は、基板1上の第1の電極層10と、第1の電極層10上の第1の誘電体膜20と、第1の誘電体膜20の上方に形成されるキャビティ35と、キャビティ35を覆う第2の誘電体膜40と、第2の誘電体膜40上の第2の電極層50とを含む。任意選択的に、CMUT100は、第1の実施形態を参照して説明されたように、基板上の誘電体層11及び第2の電極層50上の誘電体層51を含んでもよい。図2kに示される実施形態では、すべての堆積CMUT機能層及び膜10、20、30、40、50がパターニングされる。第2の電極層50は、第1の電極層10及びキャビティ35よりも小さくなるように、即ち、小さい（層又は基板の上面に平行な方向における）横寸法、例えば円形の場合には、小さい直径を有するように、パターニングされる。このようにして、特徴的な（階段状）ピラミッド構造体が提供される。CMUT100は更に、堆積層及び膜10、20、30、40、50を覆う誘電体層60を含む。誘電体層60は、上記されたように、堆積層及び膜10、20、30、40、50の上面及び側面を、実質的に同じ被覆率で覆う。誘電体層60の垂直部は、堆積層10、20、30、40、50に実質的に直交して延在する。CMUT100は更に、誘電体層60を覆う追加層70を含む。特に、追加層70は、例えば2倍以上又は5倍以上で、他の層又は膜に比べて大幅に厚い（例えば層40の厚さが約200nmであるのに対し、層70の厚さは約1μmである）。なお、図2kでは、追加層70は、概略的にしか示されていないが、追加層70は、図1kに示される追加層70と同様に、誘電体層60の形状に従う。更に、CMUTは、第2の電極層50から、層の上面に直交する方向（図2kにおける垂直方向）に延在する伝導性ピア55を含む。CMUT100は更に、ピア55からの（例えばASIC及び/又は電源への、例えばバイアス電圧に接続するための、又は、ケーブル若しくはワイヤボンドへの接続のための）外部電気接続を提供する伝導部56を含む。また、CMUT100は、第1の電極10からの伝導性ピア15を含む。伝導性ピア15は、基板1内に形成されている。ピア15、55は、（層又は基板の上面に直交する）垂直方向に延在し、伝導部56は、（層又は基板の上面に平行な）水平方向に延在する。

30

#### 【0051】

更に、代替の方法では、第1の電極層10及び第2の電極層50は、キャビティ35が

40

50

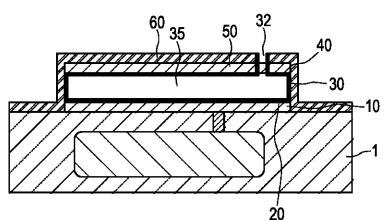

形成された後に、既に形成され、きれいにされたキャビティ 3 5 内に A L D によって堆積されてもよい。この場合は、第 1 の電極層 1 0 及び第 2 の電極層 5 0 は、エッチングの前にパターニングされることによって形成される必要がない。図 3 a ~ 図 3 i は、第 3 の実施形態による C M U T の製造方法を示す。図 3 a ~ 図 3 h の第 3 の実施形態による方法は、図 2 a ~ 図 2 k の第 2 の実施形態による方法と同様である。しかし、第 2 の実施形態に比べて、第 2 の電極層 5 0 を単独でパターニングする図 2 c のステップは省略されている。したがって、第 3 の実施形態では、使用されるエッチングマスクの数は少ない。

#### 【 0 0 5 2 】

第 3 の実施形態においても、基板 1 が、その中に組み込まれた A S I C 2 と、基板内の伝導性ピア 1 5 とを含む。当該方法は、第 1 の電極層 1 0 を基板 1 上に堆積させることから開始する。次に、犠牲層 3 0 が、第 1 の電極層 1 0 上に堆積される。犠牲層 3 0 は、後に、トランスデューサのキャビティを形成するために除去可能である。次に、第 2 の電極層 5 0 が犠牲層 3 0 上に堆積される。これらの堆積ステップは、それぞれ、原子層堆積( A L D )によって行われる。このようにすると、誘電体材料と伝導材料との交互の層からなるスタックが提供される(図 3 a を参照)。したがって、すべての C M U T 機能層( A L - A L D C M U T )は、1 つの単一処理手順で堆積される。

#### 【 0 0 5 3 】

当該方法は更に、すべての堆積層及び膜 1 0 、 3 0 、 5 0 、具体的には、すべての堆積 C M U T 機能層 1 0 、 3 0 、 5 0 をパターニングするステップを含む。本実施形態では、パターニングは、第 2 の電極層 5 0 と、犠牲層 3 0 と、第 1 の電極層 1 0 とをパターニングする共通ステップ(図 3 b を参照)を含む。したがって、本実施形態では、すべての堆積層(第 2 の電極層 5 0 、犠牲層 3 0 及び第 1 の電極層 1 0 )が、共通のステップでパターニングされる。図面から分かるように、すべての堆積層及び膜 1 0 、 3 0 、 5 0 が、同じ(層又は基板の上面に平行な方向における)横寸法、例えば円形の場合には、直径を有する。共通パターニングステップは、第 1 のエッチングマスク(マスク 1 )を使用して行われる。これにより、パターニングステップは完了する。

#### 【 0 0 5 4 】

後続ステップにおいて、図 3 c を参照するに、当該方法は、堆積層及び膜 1 0 、 3 0 、 5 0 を覆う誘電体層 6 0 を堆積させるステップを含む。この堆積ステップも、原子層堆積( A L D )を使用して行われる。誘電体層 6 0 は、堆積層及び膜 1 0 、 3 0 、 5 0 の上面及び側面を、実質的に同じ被覆率で覆う。このようにして、非常に優れた階段状の被覆が提供される。つまり、誘電体層 6 0 の垂直部と誘電体層 6 0 の水平部とは、ほぼ同じ被覆率又は厚さを有する(図 3 c を参照)。

#### 【 0 0 5 5 】

次に、当該方法は、エッチングホール 3 2 (図 3 d を参照)を設け、キャビティ 3 5 (図 3 e を参照)を形成するために犠牲層 3 0 をエッチングすることによって、犠牲層 3 0 を除去するステップを含む。キャビティ 3 5 は、上面 9 2 、底面 9 4 及び側面 9 6 、 9 8 を有する。エッチングホール 3 2 は、誘電体層 6 0 に設けられる。図 3 d 及び図 3 e に示されるように、エッチングホール 3 2 は、第 2 の電極層 5 0 には設けられず、第 2 の電極層 5 0 に隣接するどこかに設けられることが好適である。図 3 d 及び図 3 e の破線によって示されるように、エッチングホール 3 2 は、誘電体層 6 0 から、第 2 の電極層 5 0 の側を通って延在する。エッチングホール 3 2 は、第 2 のエッチングマスク(マスク 2 )を使用して設けられる。次に、犠牲層 3 0 を除去し、キャビティ 3 5 を形成するために、キャビティ 3 5 は、エッチング処理からの任意の残留物がないようにきれいにされる。次に、第 1 の誘電体膜 2 0 及び第 2 の誘電体膜 4 0 が、キャビティ 3 5 内に A L D によって堆積される(図 3 f を参照)。したがって、第 1 の誘電体膜 2 0 は、第 1 の電極層 1 0 を覆い、第 2 の誘電体膜 4 0 は、第 2 の電極層 5 0 を覆う。キャビティ内の A L D 処理によって、上面 9 2 及び底面 9 4 だけが誘電体膜によって覆われるのでなく、側面 9 6 、 9 8 も覆われる。

#### 【 0 0 5 6 】

10

20

30

40

50

次に、図3gを参照すると、誘電体層60を覆う追加の層70、具体的には、追加の誘電体層が提供される。追加層70は、エッティングホール32を閉じる又はシールする。

#### 【0057】

更に、当該方法は、第2の電極層50から、層の上面に直交する方向に延在する伝導性ビア55を設けるステップを含む。したがって、伝導性ビア55は、堆積層に直交、又は、直角である。この例では、これは、エッティングホール62(図3hを参照)を設け、当該エッティングホール62を伝導材料で埋めて、伝導性ビア55を形成する(図3iを参照)ことによって行われる。エッティングホール62の提供は、第3のエッティングマスク(マスク3)を使用して行われる。第1の電極10への伝導性ビア15は、基板1内に形成されている。更に、ビア55からの外部電気接続を提供する伝導部56が提供される。これは、追加層70上に導電層を堆積させ、次に当該導電層をパターニングすることによって行われる。これは、第4のエッティングマスク(マスク4)を使用して行われる。

#### 【0058】

図3iは、第3の実施形態によるCMUT100の横断面を示す。図3iのCMUT100は、具体的には、図3を参照して上記された方法を使用して製造されている。CMUT100は、基板1上の第1の電極層10と、第1の電極層10上の第1の誘電体膜20と、第1の誘電体膜20の上方に形成されるキャビティ35と、キャビティ35を覆う第2の誘電体膜40と、第2の誘電体膜40上の第2の電極層50とを含む。任意選択的に、CMUT100は、第1の実施形態を参照して説明されたように、基板上の誘電体層11及び第2の電極層50上の誘電体層51を含んでもよい。図3iに示される実施形態では、すべての堆積CMUT機能層及び膜10、20、30、40、50が共通ステップにおいてパターニングされる。したがって、すべての堆積CMUT機能層及び膜10、20、30、40、50は、同じ(層又は基板の上面に平行な方向における)横寸法、例えば円形の場合には、直径を有するようにパターニングされる。したがって、本実施形態では、特徴的な(階段状)ピラミッド構造体は提供されない。CMUT100は更に、堆積層及び膜10、20、30、40、50を覆う誘電体層60を含む。誘電体層60は、上記されたように、堆積層及び膜10、20、30、40、50の上面及び側面を、実質的に同じ被覆率で覆う。誘電体層60の垂直部は、堆積層10、20、30、40、50に実質的に直交して延在する。CMUT100は更に、誘電体層60を覆う追加層70を含む。特に追加層70は、例えば2倍以上又は5倍以上で、他の層又は膜に比べて大幅に厚い(例えば層40の厚さが約200nmであるのに対し、層70の厚さは約1μmである)。なお、図3hでは、追加層70は、概略的にしか示されていないが、追加層70は、図1kに示される追加層70と同様に、誘電体層60の形状に従う。更に、CMUTは、第2の電極層50から、層の上面に直交する方向(図3iにおける垂直方向)に延在する伝導性ビア55を含む。CMUT100は更に、ビア55からの(例えばASIC及び/又は電源への、例えばバイアス電圧に接続するための、又は、ケーブル若しくはワイヤ bondへの接続のための)外部電気接続を提供する伝導部56を含む。また、CMUT100は、第1の電極10からの伝導性ビア15を含む。伝導性ビア15は、基板1内に形成されている。ビア15、55は、(層又は基板の上面に直交する)垂直方向に延在し、伝導部は、(層又は基板の上面に平行な)水平方向に延在する。

#### 【0059】

更に、代替の方法では、第1の電極層10及び第2の電極層50は、キャビティ35が形成された後に、既に形成され、きれいにされたキャビティ35内にALDによって堆積されてもよい。この場合は、第1の電極層10及び第2の電極層50は、エッティングの前にパターニングされることによって形成されることによって形成される必要がない。

#### 【0060】

好適には、図示される実施形態のいずれにおいても、第1の誘電体膜20及び第2の誘電体膜40は、それぞれ、酸化物を含む第1の層と、高k材料を含む第2の層と、酸化物を含む第3の層とを含む。したがって、誘電体絶縁層20、40は、酸化物層(O)と、高k層と、もう1つの酸化物層(O)とを含む。つまり、高k層は、2つの酸化物層(特

10

20

30

40

50

にシリコーン酸化物)の間に挟まれている。具体的には、高k材料は、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)及び/又は酸化ハフニウム(HfO<sub>2</sub>)であってよい。例えば酸化物-酸化アルミニウム-酸化物(OAO)からなるラミネート(交互層)が提供される。別の例では、第2の層が、酸化アルミニウムを含む第1の副層と、酸化ハフニウムを含む第2の副層と、酸化アルミニウムを含む第3の副層とを含む。このようにして、酸化物-酸化アルミニウム-酸化ハフニウム-酸化アルミニウム-酸化物(OAHAO)からなるラミネート(交互層)が提供される。

#### 【0061】

堆積層の誘電率は、通常、材料の密度、従って、処理温度(層が形成される温度)といった堆積又は処理設定に依存する。酸化アルミニウムは、堆積又は処理設定に依存して、7乃至9の誘電率(k又は $\epsilon_r$ )を有する。例えば酸化アルミニウムの誘電率は、7.5(例えば約265の低温で堆積)、8(例えば約350の高温で堆積)又は9であってよい。酸化ハフニウムは、堆積又は処理設定に依存して、12乃至27の誘電率(k又は $\epsilon_r$ )を有する。例えば酸化ハフニウムの誘電率は、14、20又は25であってよい。酸化アルミニウム-酸化ハフニウム-酸化アルミニウムからなるラミネートの誘電率は、例えば10である。

#### 【0062】

好適には、図示される実施形態のそれぞれにおいて、第1の電極層10及び第2の電極層50は、それぞれ、非金属伝導材料(例えば半導体)を含む。例えば非金属伝導材料は、TiN(窒化チタン)、TaN(窒化タンタル)、TaCN、IrO<sub>2</sub>(酸化イリジウム)、ITO(インジウムスズ酸化物)、LaNiO<sub>3</sub>及びSrRuO<sub>3</sub>(ルテニウム酸ストロンチウム)を含む群から選択される少なくとも1つの(又は1つだけの)材料である。これらの材料は、原子層堆積に適している。特に、非金属伝導材料は、窒化チタン(TiN)である。窒化チタン(TiN)は、約30乃至70μcmの伝導率を有し、優れた導体であると見なされる。更に、(500μcmのオーダーの伝導率を有する)ポリシリコンを使用することもできる。当然ながら、電極層の材料は、特にNi(ニッケル)、銅(Cu)、W(タンクステン)、Pt(白金)、Ir(イリジウム)及びAl(アルミニウム)を含む群から選択される少なくとも1つの(又は1つだけの)材料を含む例えば金属といった任意の他の伝導材料であってもよい。例えば金属は、その合金であってもよい。例えばアルミニウムは、3μcmのオーダーの伝導率を有する。いずれにせよ、電極、金属及び非金属の伝導材料は、(例えばALDマシンにおける)ALDによる堆積に適していなければならない。

#### 【0063】

誘電体層60及び/又は追加層70は、例えば酸化物(特に酸化シリコン)、窒化物(特に窒化シリコン)又は両者の組み合わせであるか又はこれらを含む。例えば誘電体層60は、酸化(シリコン)及び窒化(シリコン)の組み合わせであるか又は当該組み合わせを含む。例えば追加層70は、窒化(シリコン)を含む。しかし、当然ながら、任意の他の適切な誘電体材料を使用してもよい。誘電体層60は、例えばALDによって又はPECVDによって堆積される。追加層70は、その厚さが高いことにより、特にPECVDによって堆積される。特に、犠牲層30は、誘電体絶縁層20、40とは異なる材料(異なるエッチング特性を有する)で作られる。このようにすると、犠牲層は、選択的に除去される。

#### 【0064】

図4は、CMUTの誘電率(イプシロン)対相対音響出力圧力のグラフを示す。図4は、シミュレーションに基づいている。全ての寸法(間隙厚さ、誘電体厚さ等)は、一定であると仮定する。黒丸印は、ALDによって堆積された酸化ハフニウム(HfO<sub>2</sub>)を示す(ここでは、14のイプシロン)。白丸印は、ONOを示す。ひし形印は、ALDによって堆積された酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)を示す(ここでは、8のイプシロン)。グラフから分かるように、高k材料は、バイアス電圧を印加できる限り、出力圧力をほぼ2倍にする(例えばAl<sub>2</sub>O<sub>3</sub>について約70%)。

10

20

30

40

50

## 【0065】

図5は、誘電体全体の電界対誘電体を流れる電流の例示的なグラフを示す。電界対電流のグラフは、ONO及び高温の酸化アルミニウム $\text{Al}_2\text{O}_3$ のそれぞれについて示されている。図5から分かるように、同じ電界値に対し、(高温の)酸化アルミニウム $\text{Al}_2\text{O}_3$ の方が、ONOに比べてリーク電流が少ない。また、(高温の)酸化アルミニウム $\text{Al}_2\text{O}_3$ に対し、ONOと比べて少なくとも同じバイアス電圧を印加することができる。

## 【0066】

原子層堆積(ALD)技術を使用して製造される高k誘電体層及び層スタックを提供することによって、CMUTの性能が(例えば動作電圧が減少され及び/又は(音響)出力圧力が増加されることによって)向上されることが示された。具体的には、金属電極の代わりに非金属電極(例えばTiN)を提供することによって、ALD技術は、1つの単一処理ステップの間に、すべてのCMUT機能層を堆積させるという独特的なオプションを提供する。したがって、より高い実効誘電率を有する誘電体スタックが、誘電体層における電荷トラップによるCMUTの同様の又はより低いドリフトと組み合わされる性能向上を提供する。全層ALD(AL-ALD)CMUT処理は、個々の層及びそれらの界面の特性を調整することによって、CMUT性能を更に向上させるオプションを提供するので、非常に有益である。AL-ALD技術は、上から下へのパターニングと共に、様々な誘電体間の高品質の界面を確実にし、操作者の介入をあまり多く必要としない。

## 【0067】

CMUTにおいて、ある層がALDによって堆積されたかどうかが検出される。一例において、ALDによって堆積された場合、第1の誘電体膜20及び/又は第2の誘電体膜40は、炭素又は塩素残留物といった処理残留物を含む。残留物は、例えばXPS(X線光電子分光法)又はSIMS(二次イオン質量分析)といった他の特性分析方法を使用して検出される。別の例では、誘電体絶縁層20、40の第2の層は、100nm未満の厚さを有する。このように非常に薄い高k層は、ALDを使用することによって(のみ)提供可能である。

## 【0068】

本明細書において説明される方法(AL-ALD)では、まず、スタックのほぼすべての層が堆積され、次にパターニングされる(そして、最後に、キャビティもシールする誘電体層が堆積される)。したがって、この方法によって製造されたCMUTについて、メンブレンに隣接する領域におけるCMUTの横断面において、すべて又はほとんどの誘電体層が除去されるか又は存在しない。しかし、例えばスパッタリングといった別の方法(ALD以外)で製造されたCMUTについては、メンブレンに隣接する領域におけるCMUTの横断面において、CMUTを構成するすべて又はほとんどの誘電体層が存在する。

## 【0069】

ALDによって堆積された層(特に $\text{Al}_2\text{O}_3$ 及び/又は $\text{HfO}_2$ からなる層)は、次の特徴のうちの1つ以上を示す:

(1) ALDによって堆積された $\text{Al}_2\text{O}_3$ の階段状の被覆は、例えばスパッタリングされた $\text{Al}_2\text{O}_3$ に比べて、非常に優れ、非常に共形性が高い。これは、例えば(横断面)SEMにおいて検出可能である。

(2) ALD-酸化物は、帯電影響をよりうまく制御でき、また、リーク電流は大幅に低い(これはピンホールがないことによる)。この点は、容量-電圧-測定結果(CV曲線)に現れる。

(3)  $\text{Al}_2\text{O}_3$ の組成が(例えばスパッタリングされた $\text{Al}_2\text{O}_3$ に比べて)異なり、RBS及び/又はXPSによって検出可能である。

(4)(例えばスパッタリングされた $\text{Al}_2\text{O}_3$ では見つけられない)炭素といった典型的な処理残留物がXPS又はSIMSによって検出される。

## 【0070】

ほんの一例として、SIMS(二次イオン質量分析)を使用して、スパッタリングされた酸化アルミニウムと、ALDによって堆積された酸化アルミニウムとの違いを検出する

10

20

30

40

50

ことができる。例えばスパッタリング処理では、アルゴンが使用され、その残余物がスパッタリングされた層内に見つけられる（例えば数パーセント）。これは、S I M S（二次イオン質量分析）によって容易に検出される。

#### 【0071】

O A O誘電体絶縁層における酸化物層（O）の機能は、O N O誘電体絶縁層における酸化物層（O）に比べて、非常に異なっている。O N O誘電体絶縁層における酸化物層（O）は、電気的な理由で存在している。酸化物層（O）なしでは、C M U Tデバイスは著しく帯電し、これは、性能を深刻に劣化させる。実際には、（P E C V Dによって堆積された）単一のO層の最小厚さは、約50nmである。O N O誘電体絶縁層における酸化物層（O）は、処理の理由で存在している。酸化物層がなければ（即ち、アルミナ層のみ）、層は、非常に大きな機械的応力を受けることが分かり、これは、メンブレンを極端に変形させ、C M U Tデバイスは動作不能となる。しかし、O A O誘電体絶縁層を使用すると、応力レベルは低い。酸化物層は薄くできる。更に、O A O誘電体絶縁層は、アルミナ層だけに比べて、より優れた電気的挙動を有する。

10

#### 【0072】

容量性マイクロマシントランステューサは、超音波が関与するC M U Tとして説明された。しかし、当然ながら、容量性マイクロマシントランステューサは、例えば圧力センサ又は圧力トランスデューサとして、他の用途にも使用される。

#### 【0073】

容量性マイクロマシントランステューサ、特にC M U Tは、単一のセル、特にC M U Tセルを含むか又は当該セルである。しかし、当然ながら、容量性マイクロマシントランステューサ、特にC M U Tは、複数のセル（特にC M U Tセル）又はセルアレイを含んでもよい。容量性マイクロマシントランステューサ、特にC M U T及び／又はその層は、円形の形状を有する。しかし、矩形又は六角形といった他の形状を使用してもよい。

20

#### 【0074】

本発明は、図面及び上記説明において詳細に例示かつ説明されたが、当該例示及び説明は、例示的であって限定的に解釈されるべきではない。本発明は、開示された実施形態に限定されない。開示された実施形態に対する他の変形態様も、図面、開示内容及び従属請求項を検討することにより、請求項に係る発明を実施する当業者には理解されかつ実施可能である。

30

#### 【0075】

請求項において、「含む」との用語は、他の要素又はステップを排除するものではなく、また、「a」又は「a n」との不定冠詞も、複数形を排除するものではない。単一の要素又は他のユニットが、請求項に記載される幾つかのアイテムの機能を果たしてもよい。特定の手段が相互に異なる従属請求項に記載されるからといって、これらの手段の組み合わせを有利に使用することができないことを示すものではない。

#### 【0076】

請求項における任意の参照符号は、範囲を限定しているものと解釈されるべきではない。

。

【図 1 a】

FIG. 1a

【図 1 b】

FIG. 1b

【図 1 c】

FIG. 1c

【図 1 d】

FIG. 1d

【図 1 e】

FIG. 1e

【図 1 k】

FIG. 1k

【図 2 a】

FIG. 2a

【図 2 b】

FIG. 2b

【図 1 f】

FIG. 1f

【図 1 g】

FIG. 1g

【図 1 h】

FIG. 1h

【図 1 i】

FIG. 1i

【図 1 j】

FIG. 1j

【図 2 c】

FIG. 2c

【図 2 d】

FIG. 2d

【図 2 e】

FIG. 2e

【図 2 f】

【図 2 g】

【図 2 h】

【図 2 i】

【図 2 j】

【図 2 k】

【図 3 a】

【図 3 b】

【図 3 c】

【図 3 d】

【図 3 e】

【図3f】

FIG. 3f

【図3h】

FIG. 3h

【図3g】

FIG. 3g

【図3i】

FIG. 3i

【図4】

図4

【図5】

図5

---

フロントページの続き

(72)発明者 クルートワイク ヨハン ヘンドリック

オランダ国 5656 アーエー アインドーフェン ハイ テック キャンパス 5

(72)発明者 ムルダー マルセル

オランダ国 5656 アーエー アインドーフェン ハイ テック キャンパス 5

(72)発明者 デ ウィルド ニコ マリス エイドリアーン

オランダ国 5656 アーエー アインドーフェン ハイ テック キャンパス 5

(72)発明者 カラカヤ コーライ

オランダ国 5656 アーエー アインドーフェン ハイ テック キャンパス 5

(72)発明者 バン デン フーベル コルネリウス アントニウス

オランダ国 5656 アーエー アインドーフェン ハイ テック キャンパス 5

審査官 武田 裕司

(56)参考文献 特開2007-074628(JP,A)

特表2010-524010(JP,A)

特開2012-080095(JP,A)

特開2008-166713(JP,A)

特開2012-085239(JP,A)

特表2007-528153(JP,A)

特開2011-023658(JP,A)

特表2011-523503(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| H 04 R | 31 / 00 |

| A 61 B | 8 / 00  |

| B 81 B | 3 / 00  |

| B 81 C | 1 / 00  |

| H 04 R | 19 / 00 |