(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5686896号

(P5686896)

(45) 発行日 平成27年3月18日(2015.3.18)

(24) 登録日 平成27年1月30日(2015.1.30)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 21/8229 (2006.01) | HO 1 L 27/10 3 9 1 |

| HO 1 L 27/102 (2006.01)  | HO 1 L 29/74 J     |

| HO 1 L 29/74 (2006.01)   | HO 1 L 29/74 F     |

請求項の数 9 (全 8 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-520812 (P2013-520812)  |

| (86) (22) 出願日 | 平成23年7月19日 (2011.7.19)        |

| (65) 公表番号     | 特表2013-536572 (P2013-536572A) |

| (43) 公表日      | 平成25年9月19日 (2013.9.19)        |

| (86) 國際出願番号   | PCT/US2011/044546             |

| (87) 國際公開番号   | W02012/012435                 |

| (87) 國際公開日    | 平成24年1月26日 (2012.1.26)        |

| 審査請求日         | 平成26年7月18日 (2014.7.18)        |

| (31) 優先権主張番号  | 12/838,803                    |

| (32) 優先日      | 平成22年7月19日 (2010.7.19)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595168543<br>マイクロン テクノロジー, インク.<br>アメリカ合衆国, アイダホ州 83716<br>-9632, ボイズ, サウス フェデ<br>ラル ウエイ 8000 |

| (74) 代理人  | 100106851<br>弁理士 野村 泰久                                                                        |

| (74) 代理人  | 100074099<br>弁理士 大菅 義之                                                                        |

| (72) 発明者  | マシュー, スラジ ジェイ.<br>アメリカ合衆国, アイダホ州 83716<br>, ボイズ, イースト レッド ファー コ<br>ート 2832                    |

最終頁に続く

(54) 【発明の名称】高密度サイリスタ・ランダムアクセスメモリ装置及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

2つの上向き端及びその間の折り曲げ導電路を有する第1の型のドープ半導体ベースと、

前記導電路に沿って第1及び第2のp-n接合を形成するための、前記第1の型のドープ半導体ベースに垂直に結合された1対の第2の型のドープ半導体構造と、

前記導電路に沿って第3のp-n接合を形成するための第1の型のドープ半導体最上部構造と、

前記第1及び第2のp-n接合の間に位置するゲートであつて、前記第1及び第2のp-n接合の間に前記第1の型のドープ半導体ベースを実質的に包囲するゲートと、

を含むメモリセル。

## 【請求項 2】

前記第1の型のドープ半導体ベースは、それよりも下方の半導体領域から絶縁されている、請求項1のメモリセル。

## 【請求項 3】

前記第1の型のドープ半導体がp型で、前記第2の型のドープ半導体がn型である、請求項1のメモリセル。

## 【請求項 4】

前記メモリセルが約4F<sup>2</sup>の量の基板面積を使用する、請求項1のメモリセル。

## 【請求項 5】

前記第1の型のドープ半導体ベースが「U」形状に形成されている、請求項1のメモリセル。

**【請求項6】**

プロセッサと、

メモリセルのアレイを含む半導体メモリと、

前記プロセッサと前記半導体メモリの間を接続する入力／出力接続と、

を含む電子機器システムであって、

前記半導体メモリのセルが、

2つの上向き端及びその間の折り曲げ導電路を有する第1の型のドープ半導体ベースと

、

前記導電路に沿って第1及び第2のp-n接合を形成するための、前記第1の型のドープ半導体ベースに垂直に結合された1対の第2の型のドープ半導体構造と、

前記導電路に沿って第3のp-n接合を形成するための第1の型のドープ半導体最上部構造と、

前記第1及び第2のp-n接合の間のみに位置するゲートであって、前記第1及び第2のp-n接合の間の前記第1の型のドープ半導体ベースを実質的に包囲するゲートと、

を含む、電子機器システム。

**【請求項7】**

前記第1の型のドープ半導体ベースは、それよりも下方の半導体領域から絶縁されている、請求項6の電子機器システム。

**【請求項8】**

前記第1の型のドープ半導体ベースはシリコン・オン・インシュレータのうちの半導体領域から形成される、請求項6の電子機器システム。

**【請求項9】**

前記第1の型のドープ半導体がp型で、前記第2の型のドープ半導体がn型である、請求項6の電子機器システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

優先出願

本特許出願は本明細書に参照として組み込まれる2010年7月19日に出願された米国出願第12/838,803号からの優先権の利益を請求する。

**【背景技術】**

**【0002】**

サイリスタ・ランダムアクセスメモリ(TRA M)は、メモリ状態を保存するための、選択トランジスタとは別の専用の蓄積キャパシタを必要としない、メモリ構造を提供する。しかしながら、今までの装置構成は大量の表面積を使用する。更に記録密度を向上するために装置構成の改善が必要である。更に、信頼でき効率的な製造方法を用いた装置を形成することが望ましい。

**【図面の簡単な説明】**

**【0003】**

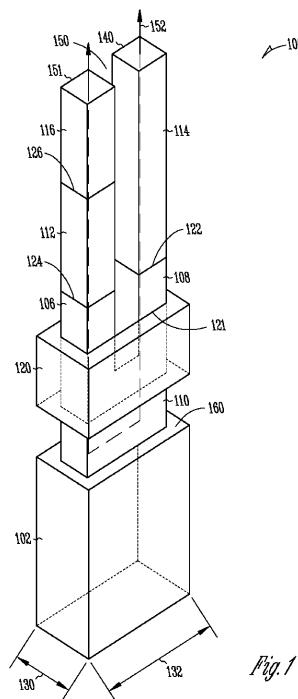

【図1】本発明の実施形態に基づく実施例のメモリセルを示す図である。

【図2】本発明の実施形態に基づく様々なゲート電圧での実施例のメモリセルのトリガ電圧を示す図である。

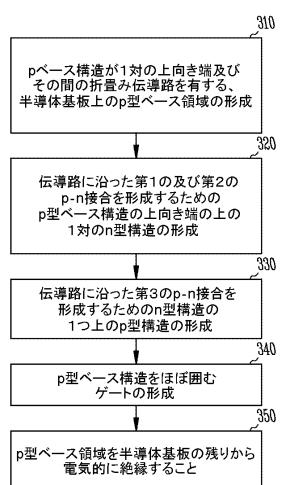

【図3】本発明の実施形態に基づくメモリセルの形成の実施例の方法を示す図である。

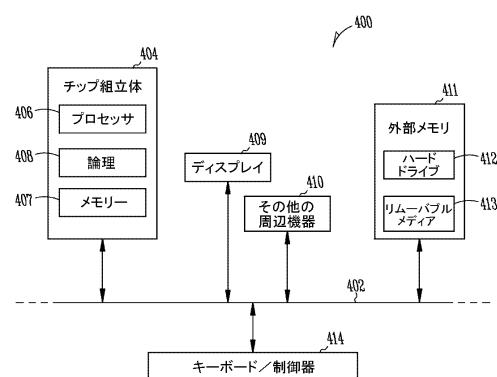

【図4】本発明の実施形態に基づく実施例のメモリセルを含む情報処理システム示す図である。

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

10

20

30

40

50

本発明の以下の詳細な説明において、本明細書の一部をなす添付の図面が参照され、その中に例示として本発明が実施される具体的な実施形態が示される。こうした実施形態は当業者が本発明を実行可能にするように十分に詳細に記載される。その他の実施形態が用いられて良く、化学的、構造的、論理的、電子的変更等がされて良い。

**【課題を解決するための手段】**

**【0005】**

以下の記述に用いられるウエハ及び基板という用語は装置又は集積回路（I C）構造を形成する露外面を有するいかなる構造も包含する。基板という用語は半導体ウエハを包含すると理解されている。基板という用語はまた処理中の半導体構造をさすためにも用いられ、その上に製造されるシリコン・オン・インシュレータ（SOI）等のような、その他の層を包含しうる。ウエハ及び基板の両方はドープ及び非ドープ半導体、ベース半導体又は絶縁体に支持されるエピタキシャル半導体層及び当業者に公知のその他の半導体構造を包含する。導体という用語は半導体を包含すると理解され、絶縁体又は誘電体という用語は導体と称される物質より電気伝導性（導電性）が少ないいかなる物質も包含すると定義される。

10

**【0006】**

本出願で用いられる「水平」という用語はウエハ又は基板がどの方向を向いているかに関わらず、ウエハ又は基板の従来の面又は表面に平行な面として定義される。「垂直」という用語は上記で定義される水平に垂直な方向をさす。「上」、「側壁」における「側」のような、「側」、「より高い」、「より低い」、「上の」及び「下の」のような前置詞はウエハ又は基板がどの方向を向いているかに関わらず、ウエハ又は基板の天面（最上面）内にある従来の面又は表面に関して定義される。以下の詳細な説明はそれゆえ限定的な意味で解されるべきでなく、本発明の範囲は付属の特許請求の範囲及びこうした特許請求の範囲が権利化されるところの均等物の全範囲によってのみ定義される。

20

**【0007】**

図1は本発明の実施形態に基づくメモリセル100を示す。メモリセル100は第1の種類（型）のドープ半導体ベース110を包含する。第1の種類のドープ半導体ベース110が2つの上向き端106及び108を有するよう示される。上記のように、本明細書内の「上向き」という用語は製造中の半導体ウエハに関して定義される。製造されたメモリチップは使用中に複数の可能な方向の内どれを有しても良い。2つの上向き端106及び108の間にスペースが包含される。1つの実施形態において、スペースは、以下に詳細に記されるように、伝導路（導電路）140の一部を画定する。

30

**【発明の効果】**

**【0008】**

図1は第1の上向き端106に連結される第2の種類（型）のドープ半導体構造112及び第2の上向き端108に連結されるもう1つの第2の種類のドープ半導体構造114を更に示す。1つの実施形態において、第1の種類（型）のドープ半導体はp型で、第2の種類のドープ半導体はn型であるが、本発明はそのように限定されるものではない。他の実施形態において、第1の種類（型）のドープ半導体はn型で、第2の種類（型）のドープ半導体はp型である。

40

**【0009】**

第2の種類のドープ半導体構造112より上に位置する第1の種類のドープ半導体頂構造（ドープ半導体最上部構造）116も示される。図1に示される構成は第1のp-n接合122、第2のp-n接合124、及び第3のp-n接合126を形成する。p-n接合（122、124、126）はサイリストア装置を形成するために伝導路（導電路）140に沿って直列に連結される。

**【発明を実施するための形態】**

**【0010】**

図示の構成において、第1の種類のドープ半導体ベース110が上向き端106及び108とともに折畳み（折り曲げ）構造を画定する。折畳み構造は水平構造より設置面積に

50

おいてよりコンパクトである。1つの実施形態において、設置面積は幅130及び長さ132を包含し、これはリソグラフィック加工寸法の約4倍の面積( $4 F^2$ )である。リソグラフィック加工寸法の面積は光学的リソグラフィによって製造されたときに基板上の所定の面積内にいくつの装置または装置の素子がフィット可能かを示す。実際の装置寸法はリソグラフィ及びエッチング条件を含むいくつかの要素に依存することがある。しかしながら、相対性能指数「F」は波長に無関係で、空間的効率における互いのデバイス構造を比較するために半導体業界で頻繁に使用される。

#### 【0011】

図1に示される折畳み(折り曲げ)構造では電気接点151及び152がメモリセル100の頂面(最上面)にあることになる。これはメモリアレイのための後の配線が、メモリセルの下の代わりに、すなわちメモリセルの頂面150の下ではなく、メモリセルの頂上(最上部上)に形成されることを可能にする。装置の頂面150の下に形成される導体線又はその他の配線は製造がより困難なことがある。例えば、埋設伝導線(導電線)構造を形成するために深いイオン注入処理、又はエッチングされた溝内深くへの堆積が必要となることがある。これに対し、頂面上に接点151及び152を有するメモリセル100は、深い溝の形成やイオン注入なしに、導線のためのより信頼できる堆積プロセスを可能にする。

#### 【0012】

図1は第1の種類のドープ半導体ベース110が絶縁体領域102上に位置する実施形態を更に示す。1つの実施例において、絶縁体領域102は絶縁材としての酸化物を包含する。絶縁体領域102を有する実施形態において、浮体(フローティングボディ)領域160はメモリ装置100の基部に作られる。浮体領域160を有する実施形態は、絶縁体領域なしの半導体材料上に直接形成される実施形態より少ない電荷漏洩を示すことがある。

#### 【0013】

1つの実施例において、絶縁体領域102はシリコン・オン・インシュレータ(SOI)ウエハ内の絶縁体領域である。SOIウエハの使用時に、第1の種類のドープ半導体ベース110はウエハ内の頂(最上部)半導体領域から形成されて良い。1つの実施例において一番上の半導体領域はウエハ形態内のpドープ領域として提供される。1つの実施例において一番上の半導体領域はメモリ装置100の製造中にドープされる。

#### 【0014】

別の実施例において、絶縁体領域102はシャロートレンチアイソレーション(STI)アンダーカット工程を用いて個々のメモリ装置100の下に形成される。STIアンダーカット工程の1つの実施例において、溝がメモリ装置100に隣接してエッチングされ、アンダーカット領域を形成するために異方性エッチングが使用され、これは続いて例えば堆積によって、シリコンの酸化物のような絶縁材で埋められる。

#### 【0015】

図1は第1の種類のドープ半導体ベース110の少なくとも1つの側に隣接して形成されるゲート120を更に示す。図1に示される実施例は第1の種類のドープ半導体ベース110をほぼ囲むために第1の種類のドープ半導体ベース110の四方に隣接して形成されるゲート120を示す。1つの実施形態において、ゲート120と第1の種類のドープ半導体ベース110との間のインターフェース(界面)121にゲート絶縁膜が形成される。

#### 【0016】

動作の際、ゲート120への、閾値を越えるゲート電圧の印加は、第1の種類のドープ半導体ベース110を反転させ第2の種類のドープ半導体構造114が第1の種類のドープ半導体ベース110のバリアを超えて第2の種類のドープ半導体構造112に接続するようになる。ゲート反転のためには、陽極陰極間電圧はアバランシェ発生を生じさせる程十分高い必要が無く、それゆえスナップバック電圧がダイオード・ターンオンに類似する。1つの実施形態において、ゲート結合ベース、例えば図示されるようなゲート12

10

20

30

40

50

0が、メモリ装置100の「書き込み」電圧条件を変調するために使用される。

#### 【0017】

図2はゲート電圧(VG)スペクトル及び第2の種類のドープ半導体構造114での電流対印加電圧への効果を示す。図2の実施例に見られるように、ゲートトリガの助けなしに「書き込み」操作を行うためにより高い陽極陰極間電圧が必要である。

#### 【0018】

図3は本発明の実施形態に基づくメモリセルの形成の実施例の方法を示す。操作310において、p型ベース領域が半導体基板上に形成される。操作310は、p型ベース領域内に1対の上向き端を形成することを更に記し、1対の上向き端の間には折畳み伝導路(折り曲げ導電路)を有する。

10

#### 【0019】

操作320は、p型ベース構造の上向き端の上に1対のn型構造を形成して、伝導路(導電路)に沿った第1及び第2のpn接合を形成することを記す。上記のように、p型ベース構造及びこのベース構造に取り付けられたn型構造が記されるが、代替のドープ配置も可能である。

#### 【0020】

操作330は、n型構造のうちの1つの上にp型構造を形成して、伝導路(導電路)に沿った第3のpn接合を形成することを記し、操作340は、p型ベース構造を実質的に包囲するゲートを形成することを記す。

20

#### 【0021】

操作350は、p型ベース領域を半導体基板の残りから電気的に絶縁することを記す。1つの実施例において、SOI基板上にメモリ装置100を形成することにより、電気的絶縁が行われる。この実施例において、SOI基板の絶縁体領域は電気的絶縁を提供し、少なくともベース領域がSOI基板の表面半導体領域から形成される。絶縁体領域はウエハの一部であって、製造過程中に作られる必要は無いので、この実施例は少数の処理手順を用いてよい。しかしながら、SOIウエハはシリコンウエハよりコストがかかることがある。別の実施例において、シリコンウエハが用いられ、メモリ装置を半導体基板から電気的に絶縁するためにSTIアンダーカット工程が用いられる。このプロセスは製造においてより多くの工程を用いることがあるが、ウエハはより廉価でありうる。

30

#### 【0022】

本発明のためのハイレベル装置適用の実施形態を示すために図4にコンピューターのような情報処理システムの実施形態が含まれる。図4は上記の本発明の実施形態に基づくメモリセルを包含する少なくとも1つのチップ又はチップ組立体404を含む情報処理システム400のブロック図である。情報処理システム400はその中で本発明が使用可能である電子機器システムの1つの実施形態にすぎない。他の実施例はネットブック、カメラ、携帯情報端末(PDA)、携帯電話、MP3プレーヤー、航空機、人工衛星、軍事車両を含むがそれらに制限されるものではない。

#### 【0023】

この実施例において、情報処理システム400はシステムの様々な部分を連結するためのシステムバス402を包含するデータ処理システムを備える。システムバス402は情報処理システム400の様々な部分の間の通信リンクをもたらし単一バスとして、バスの組み合わせとして、又はいかなる他の適切なやり方で実施されて良い。

40

#### 【0024】

チップ組立体404はシステムバス402に連結されて良い。チップ組立体404はいかなる回路又は操作可能に互換性のある回路の組み合わせを包含して良い。1つの実施形態において、チップ組立体404はいかなる種類でも良いプロセッサ406を包含して良い。本明細書で用いられる、「プロセッサ」は例えばマイクロプロセッサ、グラフィックプロセッサ、デジタル信号プロセッサ(DSP)又はいかなる種類のプロセッサや処理回路だがこれに限らないかなる種類の計算回路を意味する。

#### 【0025】

50

1つの実施形態において、メモリチップ407はチップ組立体404内に含まれる。1つの実施形態において、メモリチップ407は上記の実施形態に記載されるサイリスタメモリ装置を包含する。

【0026】

1つの実施形態において、プロセッサチップ以外の追加の論理チップ408がチップ組立体404内に含まれる。プロセッサ以外の論理チップ408の実施例はアナログ・デジタル変換機を包含する。カスタム回路、特定用途向け集積回路（ASIC）等のような論理チップ408上の他の回路も本発明の1つの実施形態内に含まれる。

【0027】

情報処理システム400はまた外部メモリ411も包含して良く、これは1つ以上のハードドライブ412のような、特定用途に適した1つ以上の記憶素子、及び／又はフロッピー（登録商標）ディスク、コンパクトディスク（CD）、フラッシュドライブ、デジタルビデオディスク（DVD）等のようなリムーバブルメディア413を扱う1つ以上のドライブを包含して良い。上記の実施例に記載されるように構成されるメモリは情報処理システム400に含まれる。10

【0028】

情報処理システム400はまたモニターのような表示装置409、スピーカー等のような追加の周辺構成要素410、及びキーボード及び／又はマウス、トラックボール、ゲームコントローラ、音声認識装置又はシステム使用者が中に情報を入力し情報処理システム400から情報を受けることを可能にする他のいかなる装置を含んで良い、コントローラ414を包含して良い。20

【0029】

本発明の複数の実施形態が記載されるが、上の表は包括的なものを意図するものではない。具体的な実施形態が図示され本明細書に記載されるが、記される具体的な実施形態の代わりに同じ目的を達成するために考えられるいかなる配置も用いられて良いことが当業者には理解いただけるであろう。本出願は本発明の任意の変形もしくは変更を包含することを意図する。上記の記載は例示を意図し制限を意図するものではないことをご理解いただきたい。上記の実施形態の組み合わせ、及びその他の実施形態は上記の記載を学べば当業者には明らかになるであろう。

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 モウリ , チャンドラ ヴィー .

アメリカ合衆国 , アイダホ州 83712 , ボイズ , サウス グラナイト ウェイ 727

審査官 小山 満

(56)参考文献 特表2009-514212 (JP, A)

特開2007-049113 (JP, A)

特開2007-067133 (JP, A)

特開2003-030980 (JP, A)

米国特許第07195959 (US, B1)

米国特許出願公開第2009/0219426 (US, A1)

特開2002-216482 (JP, A)

特表2007-536737 (JP, A)

特表2007-525004 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

H01L 21/8229

H01L 27/102

H01L 29/74