(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6278881号

(P6278881)

(45) 発行日 平成30年2月14日(2018.2.14)

(24) 登録日 平成30年1月26日(2018.1.26)

|                      |            |

|----------------------|------------|

| (51) Int.Cl.         | F 1        |

| HO4N 5/378 (2011.01) | HO4N 5/378 |

| HO4N 5/374 (2011.01) | HO4N 5/374 |

| HO3M 1/56 (2006.01)  | HO3M 1/56  |

請求項の数 14 (全 14 頁)

|              |                               |           |                                            |

|--------------|-------------------------------|-----------|--------------------------------------------|

| (21) 出願番号    | 特願2014-230107 (P2014-230107)  | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成26年11月12日 (2014.11.12)      | (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (65) 公開番号    | 特開2015-130652 (P2015-130652A) | (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (43) 公開日     | 平成27年7月16日 (2015.7.16)        | (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| 審査請求日        | 平成28年3月29日 (2016.3.29)        | (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (31) 優先権主張番号 | 特願2013-253613 (P2013-253613)  | (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (32) 優先日     | 平成25年12月6日 (2013.12.6)        | (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                            |

最終頁に続く

(54) 【発明の名称】撮像素子、撮像装置及び携帯電話機

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素と、

時間と共に信号レベルが変化する第1の参照信号を出力する第1の参照信号発生手段と、

前記第1の参照信号の信号レベルより大きく、時間と共に信号レベルが変化する第2の参照信号を出力する第2の参照信号発生手段と、

前記複数の画素それぞれから出力される画素信号の大きさに応じて、前記第1の参照信号と前記第2の参照信号のいずれかを用いて、前記画素信号をアナログ・デジタル変換するアナログ・デジタル変換手段とを有し、

前記複数の画素と、前記第1の参照信号発生手段を第1のチップに配置し、前記第2の参照信号発生手段を第2のチップに配置したことを特徴とする撮像素子。

## 【請求項 2】

前記アナログ・デジタル変換手段は、

前記画素信号と基準信号とを比較する第1の比較手段と、

前記アナログ・デジタル変換に用いる参照信号として、前記画素信号が前記基準信号よりも小さい場合に前記第1の参照信号を選択し、前記画素信号が前記基準信号以上の場合に前記第2の参照信号を選択する選択手段と、

前記選択手段により選択された参照信号と前記画素信号とを比較する第2の比較手段と、

10

20

カウンタ値を出力するカウンタ手段と、

前記参照信号が前記画素信号を越えたときの前記カウンタ値を記憶する第1の記憶手段と

を有することを特徴とする請求項1に記載の撮像素子。

【請求項3】

前記第1のチップに、前記選択手段及び前記第2の比較手段を配置し、前記第2のチップに前記第1の比較手段、前記カウンタ手段、及び前記第1の記憶手段を配置したことを特徴とする請求項2に記載の撮像素子。

【請求項4】

前記選択手段による1フレーム分の選択結果を記憶する第2の記憶手段を更に有し、

前記第2の記憶手段に選択結果が記憶されている場合に、前記選択手段は、前記第1の比較手段による比較を行わずに、前記第2の記憶手段に記憶されている選択結果に応じて、前記参照信号を選択することを特徴とする請求項2または3に記載の撮像素子。

【請求項5】

前記第2の記憶手段に前記選択結果を記憶してから予め決められたフレーム数もしくは時間が経過すると、前記第2の記憶手段に記憶された前記選択結果を前記第2の記憶手段から削除する削除手段を更に有することを特徴とする請求項4に記載の撮像素子。

【請求項6】

前記アナログ・デジタル変換手段は、

前記画素信号と基準信号とを比較する、列毎に設けられた第1の比較手段と、

前記基準信号を出力する、列毎に設けられた信号発生手段と、

前記アナログ・デジタル変換に用いる参照信号として、前記画素信号が前記基準信号よりも小さい場合に前記第1の参照信号を選択し、前記画素信号が前記基準信号以上の場合に前記第2の参照信号を選択する選択手段と、

前記選択手段による選択結果を記憶する第1の記憶手段と、

カウンタ値を出力するカウンタ手段と、

前記選択手段により選択された参照信号と前記画素信号とを比較する第2の比較手段と、

前記参照信号が前記画素信号を越えたときの前記カウンタ値を記憶する第2の記憶手段とを有し、

前記信号発生手段は、前記第1の記憶手段に記憶された選択結果に応じて、前記基準信号の信号レベルを制御することを特徴とする請求項1に記載の撮像素子。

【請求項7】

前記信号発生手段は、前記第1の記憶手段に記憶された選択結果が前記第1の参照信号である場合に、前記基準信号の信号レベルを上げ、前記第1の記憶手段に記憶された選択結果が前記第2の参照信号である場合に、前記基準信号の信号レベルを下げる特徴とする請求項6に記載の撮像素子。

【請求項8】

複数の画素と、

時間と共に信号レベルが変化する第1の参照信号を出力する第1の参照信号発生手段と、

前記第1の参照信号の信号レベルより大きく、時間と共に信号レベルが変化する第2の参照信号を出力する第2の参照信号発生手段と、

前記第1の参照信号と前記第2の参照信号のいずれかを用いて、前記複数の画素から出力される画素信号をアナログ・デジタル変換するアナログ・デジタル変換手段とを有し、

前記複数の画素と、前記第1の参照信号発生手段を第1のチップに配置し、前記第2の参照信号発生手段を第2のチップに配置し、

前記アナログ・デジタル変換手段は、

前記アナログ・デジタル変換に用いる参照信号として、前記画素信号が主に表す色に応じて、前記第1の参照信号または第2の参照信号を選択する選択手段と、

10

20

30

40

50

前記選択手段により選択された参照信号と前記画素信号とを比較する比較手段と、カウンタ値を出力するカウンタ手段と、

前記参照信号が前記画素信号を越えたときの前記カウンタ値を記憶する記憶手段とを有することを特徴とする撮像素子。

【請求項 9】

前記画素信号が主に表す色が、赤、緑、青の何れかであって、前記選択手段は、前記画素信号が主に表す色が赤及び青の場合に前記第1の参照信号を選択し、前記画素信号が主に表す色が緑の場合に前記第2の参照信号を選択することを特徴とする請求項8に記載の撮像素子。

【請求項 10】

前記第1の参照信号及び前記第2の参照信号は、時間に比例して信号レベルが変化し、前記第2の参照信号の傾きは前記第1の参照信号の傾きよりも大きいことを特徴とする請求項1乃至9のいずれか1項に記載の撮像素子。

【請求項 11】

前記アナログ・デジタル変換手段に変換された画素信号を転送する水平走査手段をさらに有し、

前記水平走査手段を前記第2のチップに配置したことを特徴とする請求項1乃至10のいずれか1項に記載の撮像素子。

【請求項 12】

前記第1のチップと前記第2のチップは互いに積層されることを特徴とする請求項1乃至11のいずれか1項に記載の撮像素子。

【請求項 13】

請求項1乃至12のいずれか1項に記載の撮像素子を有することを特徴とする撮像装置。

【請求項 14】

請求項1乃至12のいずれか1項に記載の撮像素子を有することを特徴とする携帯電話機。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像素子及び該撮像素子を用いた撮像装置及び携帯電話機に関する。

【背景技術】

【0002】

従来、固体撮像素子の1つであるCMOSイメージセンサにおいて、CMOSロジックプロセスとイメージセンサプロセスとの融合によって、センサチップ上に複雑なアナログ回路、デジタル回路、および信号処理部等を搭載することが可能となっている。その1つとして、2次元状に画素が配置されたイメージセンサチップ上にアナログ・デジタル(AD)変換器を搭載したCMOSイメージセンサが既に実用化されている。

【0003】

CMOSイメージセンサ(以下、「CMOSセンサ」と呼ぶ。)等の撮像素子にAD変換器を搭載する場合、行列状に配置された画素アレイに対して、画素の列毎にAD変換器を設ける所謂カラムAD構造が用いられている。このカラムAD構造においては、AD変換器1つ当たりの変換レートを、1画素の読み出しレートから一行の読み出しレートまで低下させることができる。このため、AD変換器自体の変換レートを低下させて全体的な消費電力を下げるができるばかりでなく、結果的にCMOSセンサの読み出しレートの高速化も図り易いという利点がある。

【0004】

カラムAD構造を用いたCMOSセンサとして、三角波を用いるランプ型のAD変換器を用いたCMOSセンサが実用化されている。ランプ型のAD変換器では、入力端の一方にはアナログ値が入力され、入力端の他方にはカウンタの動作と共に出力が増加する参照

10

20

30

40

50

出力値が印加される。そして、参照出力値がアナログ値を上回る際のカウンタ値をデジタル値として取り出すことによって、A D 変換を行う。

【 0 0 0 5 】

この三角波はカウンタに同期して電圧を変化させるため、例えばA D 変換器が8ビットである場合には、A D 変換の動作に最大で2の8乗のステップ、つまり256ステップ分の処理が必要となる。このようなランプ型のA D 変換器を用いたC M O S センサにおいては、入力端のアナログ信号が大きければステップ数が増えてしまい、A D 変換の処理が遅くなってしまう。また、三角波の出力を大きくして処理の高速化を図ろうとすると、入力端のアナログ信号が小さい場合に、A D 変換のビット精度が落ちることになってしまう。

【 0 0 0 6 】

これに対し、特許文献1においては、多ビット化を重視する動作モードと高速化を重視する動作モードとで、A D 変換器の構成を切換えることによって、A D 変換の多ビット化と高速化を実現するような提案がなされている。

【先行技術文献】

【特許文献】

【 0 0 0 7 】

【特許文献1】特開2005-333316号公報

【発明の概要】

【発明が解決しようとする課題】

【 0 0 0 8 】

しかしながら、特許文献1に開示された技術では、A D 変換器の多ビット化と高速化を同時に両立することができない。また、動作モードに応じて使用するA D 変換器を切換えるため、A D 変換の精度が画素信号のレベルによってばらつく可能性がある。

【 0 0 0 9 】

本発明は上記問題点を鑑みてなされたものであり、カラムA D 構造の撮像素子において、各回路の配置面積を圧迫することなく、高画質な画像をより高速に取得できるようにすることを目的とする。

【課題を解決するための手段】

【 0 0 1 0 】

上記目的を達成するために、本発明の撮像素子は、複数の画素と、時間と共に信号レベルが変化する第1の参照信号を出力する第1の参照信号発生手段と、前記第1の参照信号の信号レベルより大きく、時間と共に信号レベルが変化する第2の参照信号を出力する第2の参照信号発生手段と、前記複数の画素それぞれから出力される画素信号の大きさに応じて、前記第1の参照信号と前記第2の参照信号のいずれかを用いて、前記画素信号をアナログ・デジタル変換するアナログ・デジタル変換手段とを有し、前記複数の画素と、前記第1の参照信号発生手段を第1のチップに配置し、前記第2の参照信号発生手段を第2のチップに配置したことを特徴とする。

【発明の効果】

【 0 0 1 1 】

本発明によれば、カラムA D 構造の撮像素子において、各回路の配置面積を圧迫することなく、高画質な画像をより高速に取得することができる。

【図面の簡単な説明】

【 0 0 1 2 】

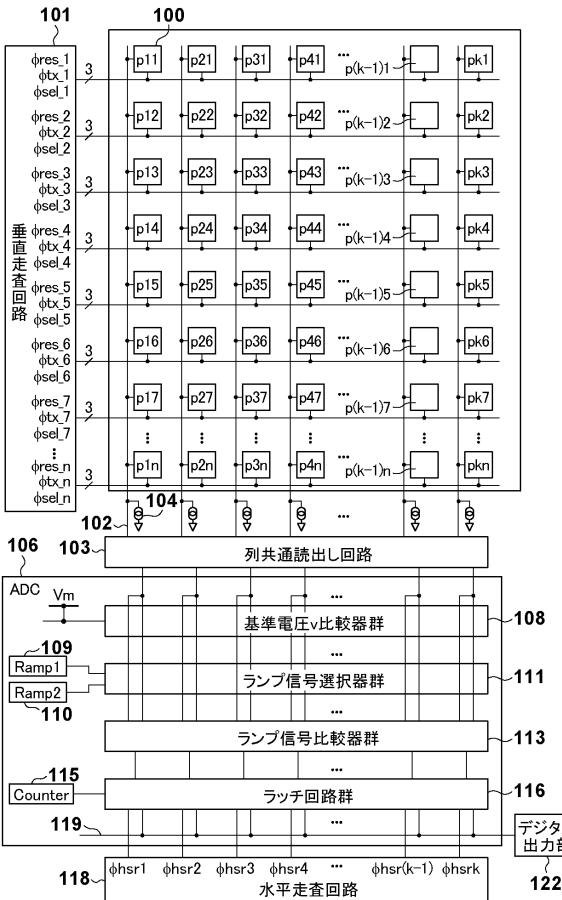

【図1】本発明の第1の実施形態における撮像素子の全体構成を示す図。

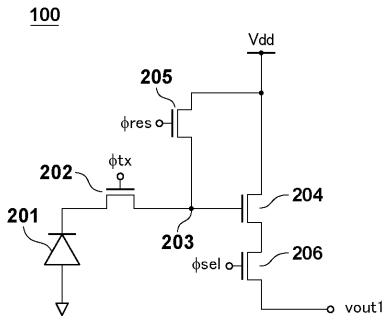

【図2】画素の構成を示す回路図。

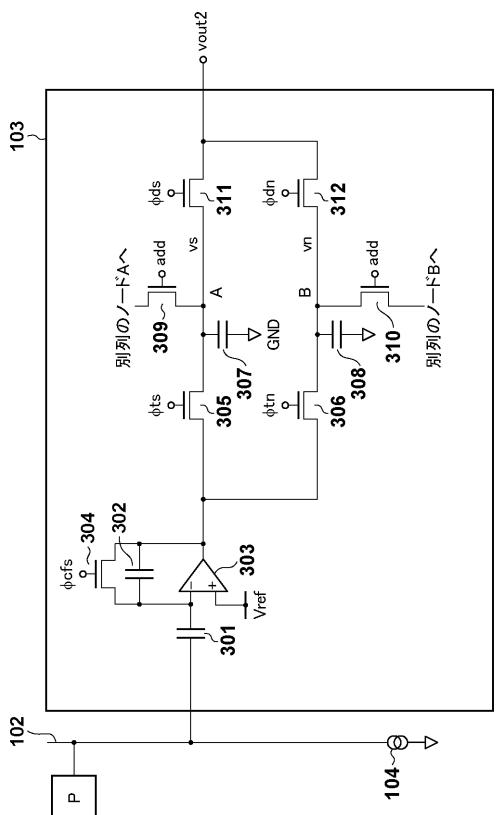

【図3】撮像素子の各列の読み出し回路の構成を示す回路図。

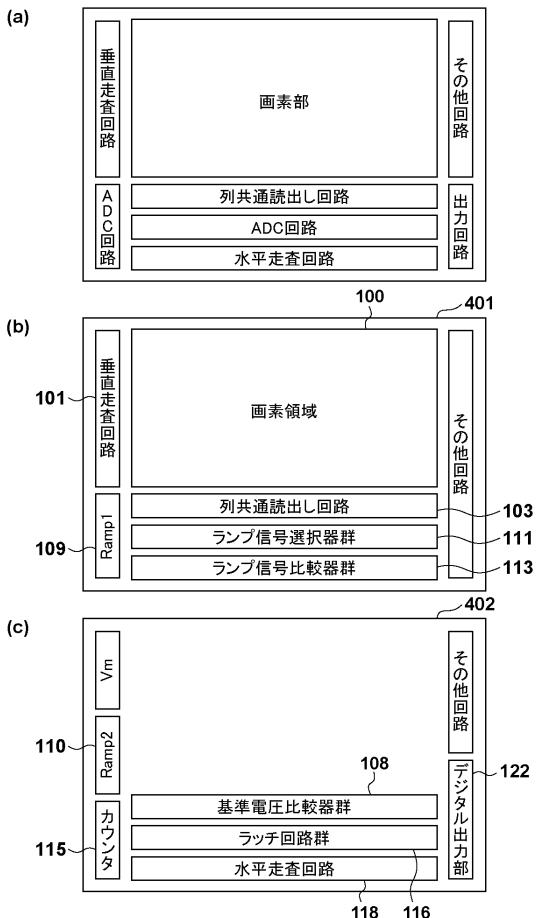

【図4】第1の実施形態における撮像素子のチップ構成を示す図。

【図5】第1の実施形態における撮像素子のA D 変換器の回路構成を示す図。

【図6】変形例における撮像素子のA D 変換器の回路構成を示す図。

【図7】変形例における撮像素子のA D 変換器の回路構成を示す図。

10

20

30

40

50

【図8】変形例における撮像素子のA/D変換器の回路構成を示す図。

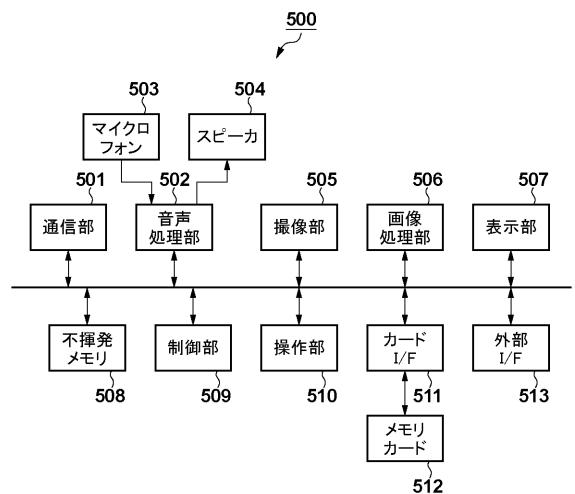

【図9】第2の実施形態における携帯電話機の概略構成を示すブロック図。

【発明を実施するための形態】

【0013】

以下、添付図面を参照して本発明を実施するための最良の形態を詳細に説明する。

【0014】

図1は、例えばデジタルスチルカメラやデジタルビデオカメラ等の撮像装置で用いられる、本発明の第1の実施形態における撮像素子の全体構成を示す図である。画素領域100には、複数の画素pが行列状に配置されている。なお、図1では、行を1～n、列を1～kとして、画素p<sub>11</sub>～p<sub>kn</sub>と表している。

10

【0015】

ここで、画素pの構成について、図2を用いて説明する。フォトダイオード(PD)201は、入射光を光電変換し、入射光量に応じた電荷を蓄積する。PD201に蓄積された電荷は、信号txをHighレベルにして転送ゲート202をONにすることで、フローティングディフュージョン(FD)部203に転送される。FD部203は、アンプ204のゲートに接続されており、このアンプ204でPD201から転送してきた電荷の電荷量に応じた電圧値に変換される。そして、画素選択スイッチ206への信号selをHighレベルとすることで、アンプ204で電圧に変換された画素信号を画素pの出力vout1として出力する。

【0016】

20

また、信号resをHighレベルとすることでリセットスイッチ205がONとなり、FD部203をリセットすることができる。さらに、信号txと信号resを同時にHighレベルにして転送ゲート202とリセットスイッチ205の両方を同時にONにすることで、FD部203経由でPD201のリセットを行うことができる。

【0017】

図1に戻り、垂直走査回路101は、信号res、tx、sel等の駆動信号を水平信号線を介して上述した構成を有する各画素pのリセットスイッチ205、転送ゲート202、画素選択スイッチ206にそれぞれ供給する。なお、図1では、同じ行に配置された画素pが同じ水平信号線に接続されており、第1～n行の各行の水平信号線に出力される信号をそれぞれ信号res\_1～n、tx\_1～n、sel\_1～nと表している。

30

【0018】

各画素pの出力vout1は、垂直走査回路101の制御により行単位で読み出される。更に列毎に垂直出力線(列出力線)102を介して、各列毎に構成された列共通読出し回路103に出力される。

【0019】

ここで、列共通読出し回路103の構成について、図3を用いて説明する。列毎に設けられた垂直出力線102に接続された画素pの出力vout1が出力される。垂直出力線102には電流源104が接続されており、この電流源104と、垂直出力線102に接続された画素pのアンプ204によってソースフォロワ回路が構成される。

40

【0020】

垂直出力線102に出力された画素信号は、クランプ容量301を介して演算増幅器303の反転入力端子に入力される。演算増幅器303の非反転入力端子には基準電圧Vrefが接続されている。スイッチ304は、フィードバック容量302の両端をショートさせるためのスイッチであり、信号cfsで制御される。

【0021】

S信号転送スイッチ305は、画素pから読み出される画素信号SをS信号保持容量307に転送するためのスイッチである。信号tsをHighレベルにすることにより、演算増幅器303で増幅された画素信号SがS信号転送スイッチ305を介してS信号保持容量307に保持される。そして、S信号保持容量307に保持された画素信号Sは、

50

信号  $d_s$  を  $H_i g h$  レベルにすることにより、S 信号出力スイッチ 311 を介して  $v_{out2}$  に出力される。

【0022】

N 信号転送スイッチ 306 は、ノイズ信号 N を N 信号保持容量 308 に転送するためのスイッチである。信号  $t_n$  を  $H_i g h$  レベルにすることにより、演算増幅器 303 で増幅された画素信号 N が N 信号転送スイッチ 306 を介して N 信号保持容量 308 に保持される。そして、N 信号保持容量 308 に保持された画素信号 N は、信号  $d_n$  を  $H_i g h$  レベルにすることにより、N 信号出力スイッチ 312 を介して  $v_{out2}$  に出力される。

【0023】

つまり、 $v_{out2}$  からは、S 信号出力スイッチ 311 および N 信号出力スイッチ 312 のオン・オフに応じて、画素信号 S もしくは画素信号 N が出力される。

【0024】

図 1 に戻り、列共通読出し回路 103 の出力信号  $v_{out2}$  は、基準電圧比較器群 108、ランプ信号選択器群 111、ランプ信号比較器群 113、ラッチ回路群 116 を含むアナログ・デジタル変換器 (ADC) 106 に入力される。

【0025】

基準電圧比較器群 108 (第 1 の比較手段) には列毎に比較器が配置され、各列の  $v_{out2}$  と基準電圧  $V_m$  (基準信号) を比較する。各比較器は、 $v_{out2}$  が基準電圧  $V_m$  よりも小さい場合には  $L_o w$  レベルを出力し、基準電圧  $V_m$  以上 (基準信号以上) の場合には  $H_i g h$  レベルを出力する。この各比較器の比較結果はランプ信号選択器群 111 に 20 出力される。

【0026】

ランプ信号選択器群 111 には列毎に選択器が配置され、それぞれに基準電圧比較器群 108 からの信号、及び、第 1 のランプ信号発生器 109 (第 1 の参照信号発生手段) 及び第 2 のランプ信号発生器 110 (第 2 の参照信号発生手段) の信号が入力される。第 1 のランプ信号発生器 109 及び第 2 のランプ信号発生器 110 は、それぞれ時間経過に比例して信号レベルが変化する波形を出力する。また、第 1 のランプ信号発生器 109 と第 2 のランプ信号発生器 110 とでは、出力する波形の傾きの大きさが異なり、第 1 の実施形態では、第 2 のランプ信号発生器 110 の方が第 1 のランプ信号発生器 109 よりも傾きが大きい波形を出力するものとする。ランプ信号選択器群 111 は、基準電圧比較器群 108 からの入力に応じて、第 1 のランプ信号発生器 109 と第 2 のランプ信号発生器 110 のいずれか一方のランプ信号を列毎に選択し、ランプ信号比較器群 113 に出力する。第 1 の実施形態では、ランプ信号選択器群 111 の各選択器は、基準電圧比較器群 108 から  $L_o w$  レベルの信号が入力された場合には、第 1 のランプ信号発生器 109 のランプ信号 (第 1 のランプ信号) を出力する。逆に、基準電圧比較器群 108 から  $H_i g h$  レベルの信号が入力された場合には、第 2 のランプ信号発生器 110 のランプ信号 (第 2 のランプ信号) を出力する。

【0027】

ランプ信号比較器群 113 (第 2 の比較手段) には列毎に比較器が配置され、列共通読出し回路 103 の出力信号  $v_{out2}$ 、及び、第 1 のランプ信号 (第 1 の参照信号) または第 2 のランプ信号 (第 2 の参照信号) が入力されている。ランプ信号比較器群 113 の各比較器は、各列の出力信号  $v_{out2}$  とランプ信号選択器群 111 からのランプ信号とを比較し、比較結果に応じてラッチ回路群 116 に信号を出力する。具体的には、入力されたランプ信号の信号レベルが時間の経過とともに大きくなり、その信号レベルが各列の出力信号  $v_{out2}$  の値を上回った時点で、ラッチ回路群 116 に出力する信号を  $L_o w$  レベルから  $H_i g h$  レベルに反転させる。

【0028】

ラッチ回路群 116 (第 1 の記憶手段、第 2 の記憶手段) には列毎にラッチ回路が配置され、ランプ信号比較器群 113、カウンタ 115、及び水平走査回路 118 からの信号が入力されている。ラッチ回路群 116 の各ラッチ回路は、ランプ信号比較器群 113 か

10

20

30

40

50

らの信号が Low レベルから High レベルに反転されると、その時にカウンタ 115 から入力されているカウンタ値をラッチする。以上の動作によって、画素から読み出したアナログ信号をデジタル値に変換する。

【 0029 】

ラッチ回路群 116 にはさらに、水平走査回路 118 からの制御信号  $hsri$  ( $i$  は列番号、 $1 \sim k$ ) によって制御される。水平走査回路 118 は制御信号  $hsri$  を High レベルとすることにより、ラッチ回路群 116 の各ラッチ回路でラッチしたカウンタ値を水平出力線（行出力線）119 へ転送させる。水平出力線 119 はデジタル出力部 122 に接続されており、デジタル出力部 122 を介して A/D 変換された画素信号を出力する。なお、各ラッチ回路からデジタル値を出力する際には、ランプ信号選択器群 111 の各選択器がいずれのランプ信号を選択したかに応じて、上位ビットあるいは下位ビットに「0」を付加する。例えば、第 2 のランプ信号が第 1 のランプ信号に対して 4 倍の傾きを持つ場合を考える。このとき、第 1 のランプ信号が選択されて A/D 変換された結果には、上位に「0」を 2 ビット付加し、第 2 のランプ信号が選択されて A/D 変換された結果には、下位に「0」を 2 ビット付加する。これにより、2 つのランプ信号による A/D 変換結果の分解能を揃えることができる。10

【 0030 】

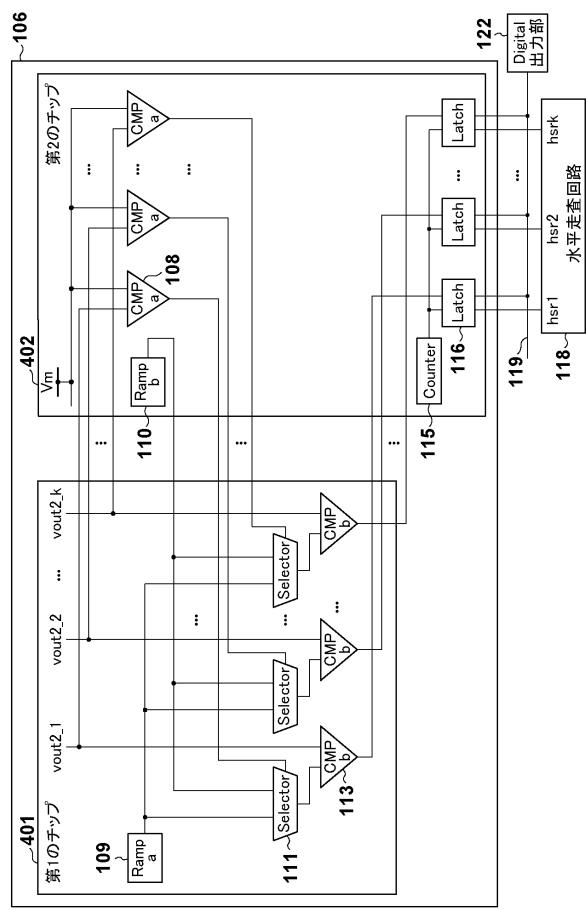

上記構成を有する ADC 106 の回路は、2 つのチップに分けて構成されている。ここで図 4 及び図 5 を用いて、第 1 の実施形態における ADC 106 を構成する回路の第 1 のチップ及び第 2 のチップへの配置について説明する。なお、図 4 において、斜線部は、それぞれのチップ構造における ADC 回路を構成する回路を表している。20

【 0031 】

図 4 (a) は従来の 1 チップ構成の撮像素子を表したものであり、画素部、垂直走査回路、列共通読出し回路、ADC 回路、水平走査回路、出力回路、その他の回路が 1 チップ上に構成されている。

【 0032 】

これに対し、第 1 の実施形態における撮像素子は、図 4 (b) 及び (c) に示す第 1 のチップ 401 と第 2 のチップ 402 を互いに積層させた 2 チップ構造となっている。図 4 (b) は第 1 のチップ 401 を示し、図 4 (c) は第 2 のチップ 402 を示している。第 1 のチップ 401 には、画素領域 100、垂直走査回路 101、列共通読出し回路 103、第 1 のランプ信号発生器 109、ランプ信号選択器群 111、ランプ信号比較器群 113、及び電流源 104 を含むその他回路が構成されている。一方、第 2 のチップ 402 には、基準電圧  $V_m$  の電源または端子、基準電圧比較器群 108、第 2 のランプ信号発生器 110、カウンタ 115、ラッチ回路群 116、水平走査回路 118、デジタル出力部 122、及びその他回路が構成されている。このように、互いに積層された第 1 のチップ 401 および第 2 のチップ 402 の両方に ADC 106 の構成に必要な回路を分けて配置することによって、高速で多ビットの A/D 変換を実現しつつ、各回路要素の面積を大きく確保し、アナログ特性の精度を確保することが可能になる。30

【 0033 】

図 5 は、ADC 106 の第 1 のチップ 401 及び第 2 のチップ 402 における回路構成を示す図である。第 1 のチップ 401 から第 2 のチップ 402 に対しては、S 信号または N 信号である出力信号  $vout_2_i$  ( $i$  は列数、 $1 \sim k$ )、及びランプ信号比較器群 113 (CMPb) からの信号が出力されている。また、第 2 のチップ 402 から第 1 のチップ 401 に対しては、基準電圧比較器群 108 (CMPa) からの信号及び第 2 のランプ信号が出力される。40

【 0034 】

一般的に、チップ間で信号を伝送すると、チップ間のインピーダンスの影響から波形などの信号品質が劣化する。そこで、第 1 の実施形態における ADC 106 を構成する回路を、図 4 及び図 5 に示すように配置する理由を説明する。まず、基準電圧比較器群 108 は、出力信号  $vout_2$  と基準電圧  $V_m$  との大小比較に用いられるだけであり、A/D 変換50

精度に直接関係ないことから、チップ間における伝送による信号品質劣化の画像に対する影響が軽微である。また、第2のランプ信号発生器110が発生する第2のランプ信号は第1のランプ信号発生器109が発生する第1のランプ信号よりも出力波形の傾きが大きく、レベルが高い信号を変換する際に用いられる際に選択される。レベルが高い信号を変換するため、チップ間の伝送による信号品質劣化の影響は相対的に軽微となる。上記の理由により、第1の実施形態では基準電圧比較器群108及び第2のランプ信号発生器110を、第2のチップ402に構成している。

【0035】

なお、これらのチップ間における信号の伝送の影響が大きい場合には、伝送元もしくは伝送先において伝送信号を補正してもよい。例えば、ランプ信号比較器群113の出力が第1のチップ401ではHighレベルを出力したのに対し、第2のチップ402に伝送した時点でLowレベルとの区別がつかなくなるような場合には、次のように対処しても良い。即ち、ランプ信号比較器群113の出力信号の振幅を増加するような增幅回路を追加してもよい。

【0036】

このようにして、第1のチップ401及び第2のチップ402間で信号を伝送しながら、最終的にデジタル出力部122から画像信号が出力される。

【0037】

以上のように第1の実施形態によれば、第1のチップ401と第2のチップ402にADC106の各回路を分けて配置することによって、撮像素子を構成する各回路要素の配置面積を確保しつつ、高速でビット精度が高いADC106を実現できる。

【0038】

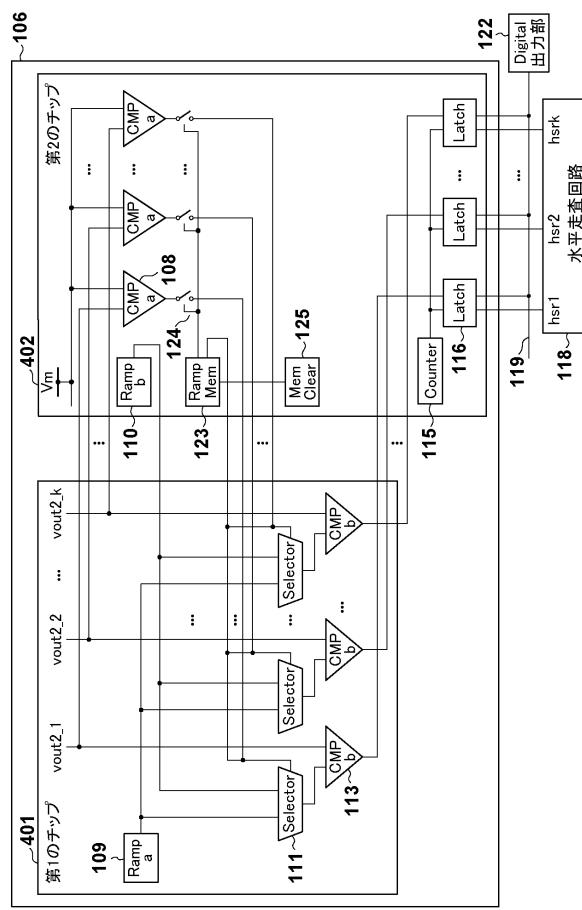

<変形例>

上述した第1の実施形態においては、列共通読出し回路103の出力信号vout2の大きさに応じて、第1のランプ信号と第2のランプ信号のいずれかを選択していたが、本発明はこれに限られるものではない。例えば、図6に示すように、ランプ信号記憶器123(Ramp Mem)(第2の記憶手段)を設けてもよい。この場合、あるフレームにおいて画素pから読み出されたそれぞれの出力信号vout2に対してどちらのランプ信号を用いたか(選択結果)を、1フレーム分記憶しておく。そして、以降のフレームにおいて、ランプ信号記憶器123に記憶されたランプ信号発生器を選択するような構成としてもよい。

【0039】

そのような構成の場合、ランプ信号記憶器123に何も記憶されていなければ、スイッチ124を制御して出力信号vout2と基準電圧Vmとの大小関係から、使用するランプ信号選択器群111によって使用するランプ信号発生器を選択する。そして、ランプ信号記憶器123に使用したランプ信号を記憶する。一方、ランプ信号記憶器123に使用したランプ信号が記憶されている場合には、スイッチ124をオープンにして、ランプ信号記憶器123に記憶されたランプ信号を選択して使用するように制御する。このような構成とすることによって、2フレーム目以降では画像毎に基準電圧Vmと比較する必要がなくなり、処理の高速化が可能となる。

【0040】

また、使用期限制御器125(Mem Clear)によってランプ信号記憶器123に記憶されているランプ信号発生器の情報を削除するか否かを制御するような構成としてもよい。この場合、所定フレーム数もしくは所定時間経過すると、ランプ信号記憶器123に記憶されたランプ信号発生器の情報を削除する。そして再び出力信号vout2と基準電圧Vmとの比較によって使用するランプ信号を選択してランプ信号記憶器123に記憶することによって、使用するランプ信号発生器を適宜更新する。

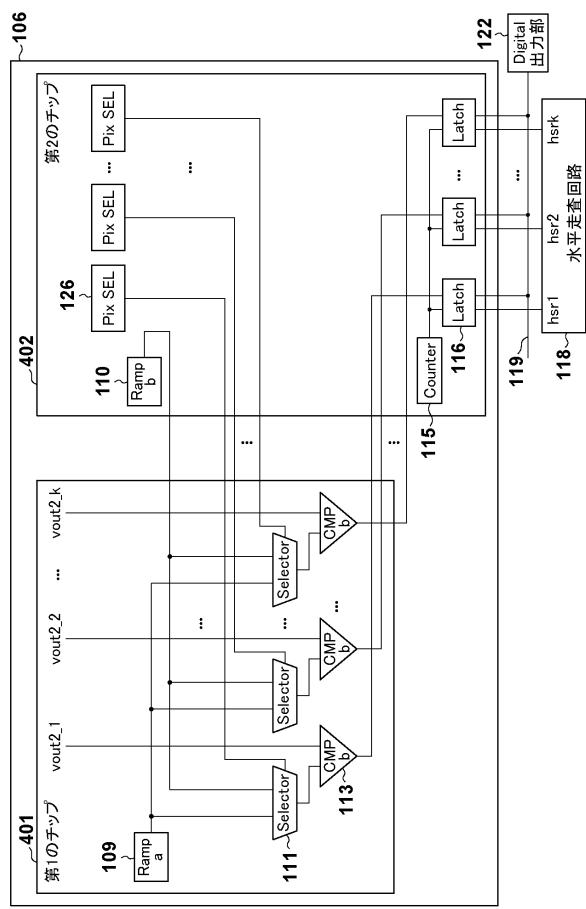

【0041】

また、図7のように、画素色切換器126(Pixl SEL)によって、画素の色毎に使用するランプ信号発生器を切換える構成としてもよい。このような構成の場合、例えば、R

10

20

30

40

50

画素もしくはB画素を読み出してから得られた出力信号vout2の場合、画素色切換え器126はランプ信号選択器群111にLowレベルの信号を入力することによって、第1のランプ信号発生器109の出力を使用する。逆に、G画素から読み出して得られた出力信号vout2の場合、画素色切換え器126はランプ信号選択器群111にHighレベルの信号を入力することによって、第2のランプ信号発生器110の出力を使用する。このような構成とすることにより、画素毎に基準電圧Vmと比較する機構が不要となり、回路規模の削減が可能となる。

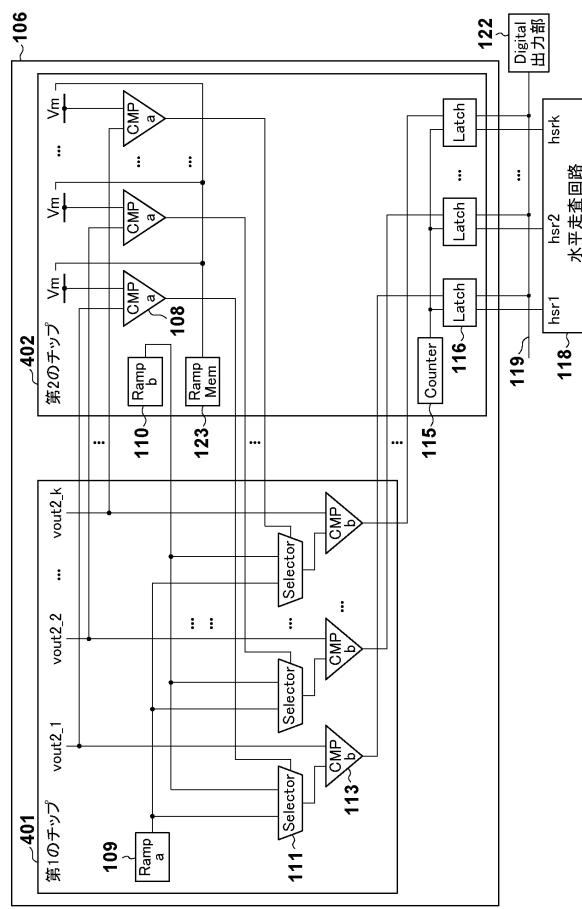

#### 【0042】

また、上述した第1の実施形態においては、基準電圧Vmを各列共通としたが、本発明はこれに限られるものではない。図8のように、基準電圧Vmを列毎に配置してVmの大きさを列毎に切換え可能とし、さらにランプ信号記憶器123と基準電圧Vmとを接続する構成としても良い。そのような構成の場合、ランプ信号記憶器123(第1の記憶手段)に何も記憶されていない場合には出力信号vout2とある初期値を持つ基準電圧Vmとの大小関係から、使用するランプ信号選択器群111によって使用するランプ信号発生器を選択する。そして、ランプ信号記憶器123に使用したランプ信号発生器を記憶する。ランプ信号記憶器123に使用したランプ信号発生器が記憶されている場合には、記憶されたランプ信号発生器に応じて、基準電圧Vmの大きさを変更する。

10

#### 【0043】

例えば、ランプ信号記憶器123に第1のランプ信号が記憶されている場合には、基準電圧Vmのある初期値より大きい出力値に設定して使用する。逆に、ランプ信号記憶器123に第2のランプ信号が記憶されている場合には、基準電圧Vmのある初期値よりも小さい出力値に設定して使用する。このようなヒステリシスを持つ構成とすることによって、基準電圧Vmに前後する出力信号vout2が連続的に出力されても、使用するランプ信号発生器がその都度切り替わらない。このため、ランプ信号発生器109とランプ信号発生器110との電気的な特性の差異による、AD変換のばらつきを抑えることができる。

20

#### 【0044】

<第2の実施形態>

図9は、本発明の第2の実施形態として、携帯電話機500の構成を示すブロック図である。第7の実施形態の携帯電話機500は、音声通話機能の他、電子メール機能や、インターネット接続機能、画像の撮影、再生機能等を有する。

30

#### 【0045】

図9において、通信部501は、ユーザが契約した通信キャリアに従う通信方式により他の電話機との間で音声データや画像データを通信する。音声処理部502は、音声通話時において、マイクロフォン503からの音声データを発信に適した形式に変換して通信部501に送る。また、音声処理部502は、通信部501から送られた通話相手からの音声データを復号し、スピーカ504に送る。

#### 【0046】

撮像部505は、第1の実施形態及びその変形例で示した撮像素子を備え、被写体の画像を撮影し、画像データを出力する。画像処理部506は、画像の撮影時においては、撮像部505により撮影された画像データを処理し、記録に適した形式に変換して出力する。また、画像処理部506は、記録された画像の再生時には、再生された画像を処理して表示部507に送る。表示部507は、数インチ程度の液晶表示パネルを備え、制御部509からの指示に応じて各種の画面を表示する。不揮発メモリ508は、アドレス帳の情報や、電子メールのデータ、撮像部505により撮影された画像データ等のデータを記憶する。

40

#### 【0047】

制御部509はCPUやメモリ等を有し、不図示のメモリに記憶された制御プログラムに従って電話機500の各部を制御する。操作部510は、電源ボタンや番号キー、その他ユーザがデータを入力するための各種の操作キーを備える。カードIF511は、メモ

50

リカード 512 に対して各種のデータを記録再生する。外部 IF513 は、不揮発メモリ 508 やメモリカード 512 に記憶されたデータを外部機器に送信し、また、外部機器から送信されたデータを受信する。外部 IF513 は、USB 等の有線の通信方式や、無線通信など、公知の通信方式により通信を行う。

#### 【0048】

次に、電話機 500 における音声通話機能を説明する。通話相手に対して電話をかける場合、ユーザが操作部 510 の番号キーを操作して通話相手の番号を入力するか、不揮発メモリ 508 に記憶されたアドレス帳を表示部 507 に表示し、通話相手を選択し、発信を指示する。発信が指示されると、制御部 509 は通信部 501 に対し、通話相手に発信する。通話相手に着信すると、通信部 501 は音声処理部 502 に対して相手の音声データを出力すると共に、ユーザの音声データを相手に送信する。

10

#### 【0049】

また、電子メールを送信する場合、ユーザは、操作部 510 を用いて、メール作成を指示する。メール作成が指示されると、制御部 509 はメール作成用の画面を表示部 507 に表示する。ユーザは操作部 510 を用いて送信先アドレスや本文を入力し、送信を指示する。制御部 509 はメール送信が指示されると、通信部 501 に対しアドレスの情報とメール本文のデータを送る。通信部 501 は、メールのデータを通信に適した形式に変換し、送信先に送る。また、通信部 501 は、電子メールを受信すると、受信したメールのデータを表示に適した形式に変換し、表示部 507 に表示する。

#### 【0050】

20

次に、電話機 500 における撮影機能について説明する。ユーザが操作部 510 を操作して撮影モードを設定した後、静止画或いは動画の撮影を指示すると、撮像部 505 は静止画データ或いは動画データを撮影して画像処理部 506 に送る。画像処理部 506 は撮影された静止画データや動画データを処理し、不揮発メモリ 508 に記憶する。また、画像処理部 506 は、撮影された静止画データや動画データをカード IF511 に送る。カード IF511 は静止画や動画データをメモリカード 512 に記憶する。

#### 【0051】

また、電話機 500 は、この様に撮影された静止画や動画データを含むファイルを、電子メールの添付ファイルとして送信することができる。具体的には、電子メールを送信する際に、不揮発メモリ 508 やメモリカード 512 に記憶された画像ファイルを選択し、添付ファイルとして送信を指示する。

30

#### 【0052】

また、電話機 500 は、撮影された静止画や動画データを含むファイルを、外部 IF513 により PC や他の電話機等の外部機器に送信することもできる。ユーザは、操作部 510 を操作して、不揮発メモリ 508 やメモリカード 512 に記憶された画像ファイルを選択し、送信を指示する。制御部 509 は、選択された画像ファイルを不揮発メモリ 508 或いはメモリカード 512 から読み出し、外部機器に送信するよう、外部 IF513 を制御する。

#### 【符号の説明】

#### 【0053】

40

100：画素領域、106：アナログ・デジタル変換器、108：基準電圧比較器群 109：第 1 のランプ信号発生器、110：第 2 のランプ信号発生器、111：ランプ信号選択器群、113：ランプ信号比較器群、115：カウンタ、116：ラッチ回路群、401：第 1 のチップ、402：第 2 のチップ、p：画素

【 図 1 】

【図2】

【図3】

【 図 4 】

【 図 5 】

【 図 6 】

【 図 7 】

【 図 8 】

【図9】

---

フロントページの続き

(72)発明者 内田 峰雄

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 兎澤 尚平

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 粕谷 満成

(56)参考文献 特開2011-041091(JP, A)

特開2011-159958(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/374

H04N 5/378

H03M 1/56