(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6186380号

(P6186380)

(45) 発行日 平成29年8月23日(2017.8.23)

(24) 登録日 平成29年8月4日(2017.8.4)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| H01L 33/36 (2010.01)  | H01L 33/36      |

| H01L 21/28 (2006.01)  | H01L 21/28 301B |

| H01L 29/868 (2006.01) | H01L 29/91 F    |

| H01L 29/861 (2006.01) | H01L 29/91 A    |

| H01L 21/329 (2006.01) | H01L 33/20      |

請求項の数 16 (全 17 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-558905 (P2014-558905)  |

| (86) (22) 出願日 | 平成25年2月22日 (2013.2.22)        |

| (65) 公表番号     | 特表2015-513798 (P2015-513798A) |

| (43) 公表日      | 平成27年5月14日 (2015.5.14)        |

| (86) 国際出願番号   | PCT/US2013/027496             |

| (87) 国際公開番号   | W02013/126828                 |

| (87) 国際公開日    | 平成25年8月29日 (2013.8.29)        |

| 審査請求日         | 平成28年2月10日 (2016.2.10)        |

| (31) 優先権主張番号  | 61/602,155                    |

| (32) 優先日      | 平成24年2月23日 (2012.2.23)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 507186469<br>センサー エレクトロニック テクノロジ<br>ー インコーポレイテッド<br>アメリカ合衆国, サウス カロライナ州<br>, コロンビア, アトラス ロード 1<br>195 |

| (74) 代理人  | 110000408<br>特許業務法人高橋・林アンドパートナーズ                                                                      |

| (72) 発明者  | ギャスカ, レミギウス<br>アメリカ合衆国 29212 サウス カ<br>ロライナ州, コロンビア, プレス リン<br>ドラー ロード 432                             |

最終頁に続く

(54) 【発明の名称】半導体層に対するオーミックコンタクトを含むデバイスヘテロ構造を形成することを含む方法および半導体層に対するオーミックコンタクトを含むデバイスヘテロ構造を含むデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体層をエッチングすることなく、デバイスヘテロ構造の一セットの半導体層において半導体層に対するオーミックコンタクトを含む前記デバイスヘテロ構造を形成することを含む方法であって、

前記デバイスヘテロ構造を形成することは、

前記半導体層の表面上の前記オーミックコンタクトに対応する一セットのコンタクト領域上にマスキング材料を適用し、

前記マスキング材料を適用した後に、前記半導体層の表面の一セットのマスクされていない領域を覆う隆起領域を形成し、

前記一セットのコンタクト領域上に一セットの高導電性半導体層を形成し、

前記隆起領域の形成後に前記一セットの高導電性半導体層上にオーミックコンタクトを形成することを含み、

前記一セットの高導電性半導体層を形成することは、前記一セットのコンタクト領域からの距離に関して前記一セットの高導電性半導体層を形成する材料の少なくとも1つの元素のモル分率に傾斜を持たせることを含み、

前記オーミックコンタクトを形成することは、デバイスヘテロ構造に前記一セットの半導体層のいずれかを形成する材料の品質が損なわれる温度範囲よりも低い処理温度において実施されることを特徴とする方法。

## 【請求項 2】

10

20

前記オームイックコンタクトを形成する前に、前記隆起領域上に少なくとも1つの追加の半導体層を形成することをさらに含む、請求項1に記載の方法。

【請求項3】

前記オームイックコンタクトを形成する前に、前記一セットのコンタクト領域のそれぞれから前記マスキング材料を除去することをさらに含む、請求項1に記載の方法。

【請求項4】

前記オームイックコンタクトを形成する前に、前記一セットのマスクされていない領域に対応する前記デバイスヘテロ構造の表面にマスキング材料を適用することをさらに含む、請求項1に記載の方法。

【請求項5】

10

前記一セットの高導電性半導体層がIII族窒化物材料で形成され、

前記一セットの高導電性半導体層が、前記半導体層と前記一セットの高導電性半導体層との界面において前記半導体層と格子整合される、請求項1に記載の方法。

【請求項6】

前記一セットの高導電性半導体層を形成することが、前記一セットの高導電性半導体層をデルタドーピングする工程を含む、請求項1に記載の方法。

【請求項7】

前記一セットの高導電性半導体層が、III族窒化物材料で形成され、

前記傾斜を持たせることが、前記一セットのコンタクト領域から離れる方向にアルミニウムのモル分率が増加することである、請求項1に記載の方法。

20

【請求項8】

前記傾斜を持たせることが、前記一セットのコンタクト領域から離れる方向にインジウムのモル分率が減少することである、請求項7に記載の方法。

【請求項9】

前記一セットのコンタクト領域と前記一セットの高導電性半導体層との界面において、前記アルミニウムのモル分率が0である、請求項7または8に記載の方法。

【請求項10】

前記傾斜が、前記一セットのコンタクト領域において逆キャリアの蓄積の誘起を避けるように構成される、請求項1に記載の方法。

【請求項11】

30

前記デバイスヘテロ構造の前記一セットの半導体層がIII族窒化物材料で形成される、請求項1に記載の方法。

【請求項12】

デバイスヘテロ構造の一セットの半導体層において半導体層に対するオームイックコンタクトを含むデバイスヘテロ構造を含むデバイスであって、

前記オームイックコンタクトが、前記半導体層の一セットのコンタクト領域上に形成された一セットの高導電性半導体層を含み、

前記一セットの高導電性半導体層が、前記半導体層と前記一セットの高導電性半導体層との界面において前記半導体層と格子整合されることを特徴とするデバイス。

【請求項13】

40

前記一セットの高導電性半導体層がIII族窒化物材料で形成される、請求項12に記載のデバイス。

【請求項14】

前記一セットの高導電性半導体層がデルタドーピングされる、請求項12に記載のデバイス。

【請求項15】

前記一セットの高導電性半導体層が、前記一セットのコンタクト領域からの距離について前記一セットの高導電性半導体層を形成する材料の少なくとも1つの元素の傾斜したモル分率を有する、請求項12に記載のデバイス。

【請求項16】

50

前記傾斜が、前記一セットのコンタクト領域での逆キャリアの蓄積の誘起を避けるように構成される、請求項15に記載のデバイス。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示は、概して、半導体に対するコンタクト、より詳細には半導体、例えば窒化物ベースの半導体などに対するオーミックコンタクトに関する。

**【背景技術】**

**【0002】**

高出力のIII-V族材料ベースの半導体デバイス、例えば、発光ダイオード(LED)、レーザーダイオード(LD)、バイポーラ接合トランジスタ(BJT)、およびヘテロ接合バイポーラトランジスタ(HBT)などの開発における課題は、低い比抵抗および高い電流輸送能力の両方を有するオーミックコンタクトの開発である。例えば、n型材料に対する低抵抗のオーミックコンタクトを製造するための課題は、高いモル分率においてアルミニウムを含むIII族窒化物材料、例えば、窒化アルミニウムガリウム(AlGaN)または窒化アルミニウムガリウムインジウム(AlGAINN)などから作成される深紫外線LEDにとって特に重要である。

**【0003】**

窒化物ベースのデバイスにおいて低いn型コンタクト抵抗を達成するために、一般的には、数種のコンタクト金属および比較的高いアニール処理温度が用いられる。この点に関して、Alは、およそ660と比較的低い融点を有することから、コンタクト金属として使用することができる。さらに、チタン(Ti)またはクロム(Cr)は、窒化物に対して低い金属仕事関数を有することから、このコンタクトの第一層として使用することができる。具体例としては、5ナノメートルから5ミクロンの厚さを有し、400以上の温度でアニール処理された、Ti/Al/Ti/金(Au)またはTi/Al/ニッケル(Ni)/Auが挙げられる。別のアプローチでは、TiおよびAlの順序を逆にして、Al/Ti/白金(Pt)/Auを含み、400~600の温度でアニール処理された、n型GaN半導体に対するAl/Tiベースのコンタクトが形成される。さらなる別のアプローチでは、様々な金属構成、例えば、Cr/Al/Cr/Au、Cr/Al/Pt/Au、Cr/Al/Pd/Au、Cr/Al/Ti/Au、Cr/Al/コバルト(Co)/Au、およびCr/Al/Ni/Auなどを含む、n型GaN半導体に対するCr/Alベースのコンタクトが形成される。

**【0004】**

コンタクトの信頼性も問題となり得る。例えば、今日まで、265ナノメートルの短波長を放つ紫外線LEDのためのTi/Alベースのn型コンタクトにおいて、高い信頼性は示されていない。

**【0005】**

いくつかのアプローチでは、エッチング処理を実施した後に半導体層を再成長させることにより、オーミックコンタクトを向上させている。例えば、アプローチの1つでは、半導体層を再成長させるプロセスにより非合金系コンタクトが形成される。このプロセスは、(1) サファイアなどの基板上に半導体層を成長させる工程；(2) 最上部の半導体層の上に再成長マスクを配置する工程であって、再成長マスク材料(例えば、窒化シリコンまたは二酸化シリコン)が、半導体層上においてパッシベーション層として機能することができるよう、選択され、被着され、および(例えば、フォトレジストの使用により)選択的に除去される工程；(3) 最上部の半導体層の表面からおよそ5ナノメートルから千ナノメートルの許容可能な深さに半導体層をエッチングする工程；(4) エッチングした領域において構造体を成長させる工程；ならびに(5) 任意により、ゲートを有するデバイスのために、フォトリソグラフィを適用してゲート領域を形成する工程、を含む。

**【0006】**

10

20

30

40

50

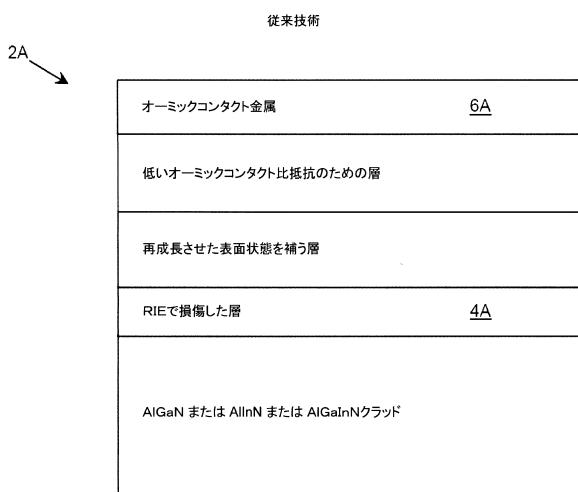

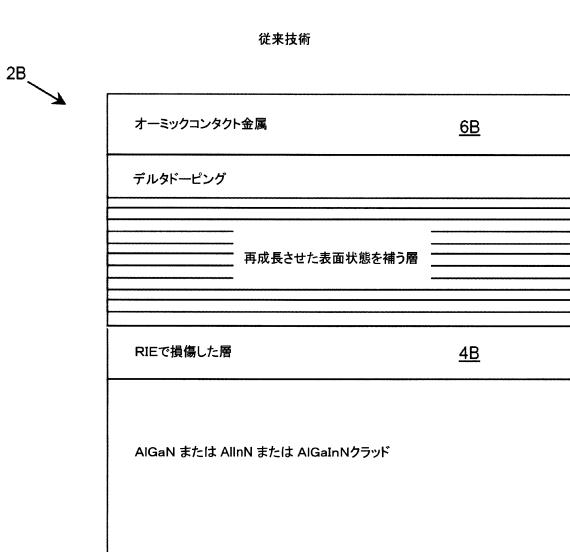

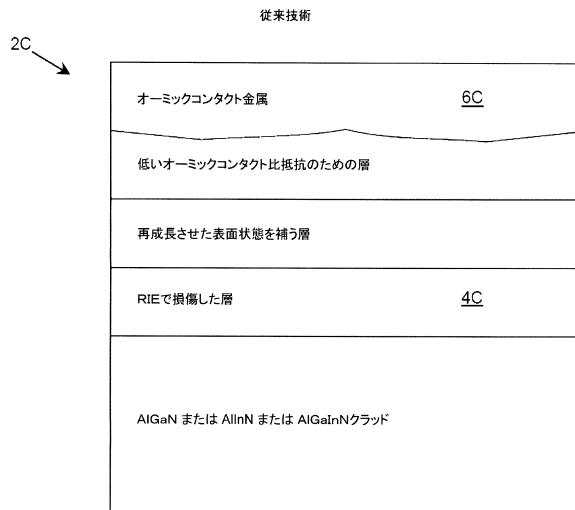

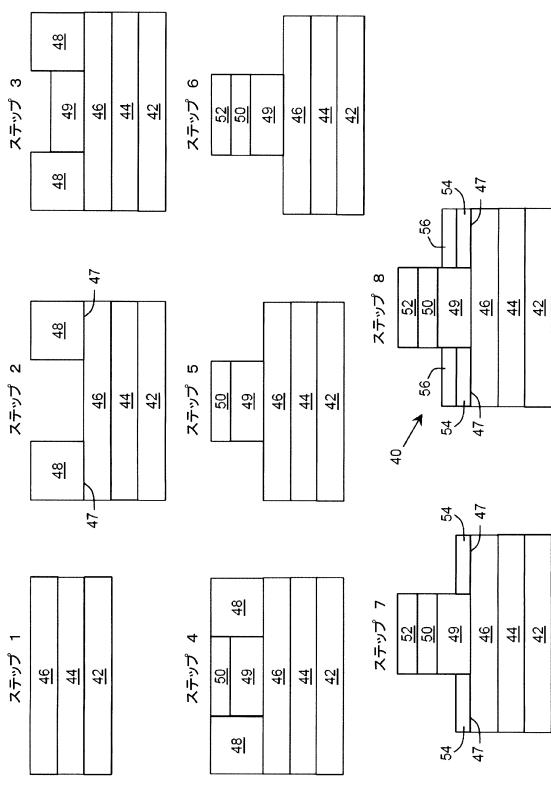

図1A～1Cは、それぞれ、先行技術による反応性イオンエッティング(RIE)および再成長プロセスを使用して形成された典型的なオーミックコンタクト2A～2Cを示している。それぞれの場合において、半導体層4A～4CのRIEは、再成長の前に行われている。その後にオーミック金属6A～6Cを被着させることによって再成長が実施される。図1Aにおいて、オーミックコンタクト2Aは、RIEで損傷した層4Aの上に、再成長させた表面状態を補う層を含む。図1Bにおいて、オーミックコンタクト2Bは、再成長させた表面状態を補う層およびデルタドーピング層を含む。図1Cにおいて、オーミックコンタクト2Cは、再成長させた表面状態を補う層および低いオーミックコンタクト比抵抗のための層を含む。図1A～1Cに示されるように、再成長技術は、他の特徴、例えば、図1Bに示されるようなデルタ-ドーピングなどと併用することができる。デルタ-ドーピングは、高速デバイス、例えば、高いキャリア密度およびゲートの大きな破壊電圧を達成するためにデルタ-ドーピング技術を利用するヘテロ構造電解効果トランジスタなどにとって重要である。さらに、再成長技術は、図1Cに示されるような荒いモルホロジー(rough morphology)を有するコンタクト、ならびに再成長領域と共にアニール処理されかつ再成長領域中への突出部を有するコンタクトと一緒に使用することができます。コンタクト2A～2Cのそれぞれの品質は、オーミック金属6A～6Cを直接被着させる場合と比べて再成長によって著しく向上するが、その一方で、各プロセスは、RIEエッティング領域4A～4Cに多くの欠陥を有し、これが、オーミックコンタクト2A～2Cの品質を低下させ、ならびにオーミックコンタクト2A～2Cを含む対応するデバイスの寿命全体を低下させる。

10

20

#### 【0007】

別の再成長アプローチは、特に、III族窒化物半導体層を再成長させるように設計されるものである。このプロセスは、(1)半導体層と、半導体層を覆う非意図的にドープされた(UID)窒化ガリウム(GaN)層と、GaN半導体層を覆うUID窒化アルミニウムガリウム(UID-AlGaN)層とを含む半導体本体を基板上に成長させる工程；(2)絶縁膜を被着させ、パターン形成する工程；ならびに(3)UID-AlGaN半導体の表面をエッティングすることなく、絶縁膜で覆われていないUID-AlGaNの表面におけるある領域にn+GaN層を再成長させる工程、を含む。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

30

#### 【0008】

本発明の態様は、半導体層に対するオーミックコンタクトを形成するための解決策を提供する。マスキング材料を半導体層の表面上の一セットのコンタクト領域に適用する。それに続いて、半導体層のマスキングされていない領域上に、デバイスヘテロ構造の1つもしくは複数の層を形成する。デバイスヘテロ構造の1つもしくは複数の層を形成した後に、オーミックコンタクトを形成することができる。オーミックコンタクト形成は、デバイスヘテロ構造に任意の半導体層を形成する材料の品質が損なわれる温度範囲よりも低い処理温度において実施することができる。

#### 【課題を解決するための手段】

#### 【0009】

40

本発明の第一の態様は、半導体層をエッティングすることなく、デバイスヘテロ構造の一セットの半導体層において半導体層に対するオーミックコンタクトを含む前記デバイスヘテロ構造を形成することを含む方法であって、前記デバイスヘテロ構造を形成することは、前記半導体層の表面上の前記オーミックコンタクトに対応する一セットのコンタクト領域上にマスキング材料を適用し、前記マスキング材料を適用した後に、前記半導体層の表面の一セットのマスクされていない領域を覆う隆起領域を形成し、前記隆起領域の形成後に前記一セットのコンタクト領域上にオーミックコンタクトを形成することを含み、前記オーミックコンタクトを形成することは、デバイスヘテロ構造に前記一セットの半導体層のいずれかを形成する材料の品質が損なわれる温度範囲よりも低い処理温度において実施されることを特徴とする方法を提供する。

50

**【0010】**

本発明の第二の態様は、デバイスヘテロ構造の一セットの半導体層において半導体層に対するオーミックコンタクトを含むデバイスヘテロ構造を含むデバイスであって、前記オーミックコンタクトが、前記半導体層の一セットのコンタクト領域上に形成された一セットの高導電性半導体層を含み、前記一セットの高導電性半導体層が、前記半導体層と前記一セットの高導電性半導体層との界面において前記半導体層と格子整合されることを特徴とするデバイスを提供する。

**【0011】**

本発明の第三の態様は、半導体層をエッチングすることなく、デバイスヘテロ構造の一セットの半導体層において該半導体層に対するオーミックコンタクトを含む前記デバイスヘテロ構造を形成するための製造システムを含むシステムであって、前記デバイスヘテロ構造を形成することは、前記半導体層の表面上に該オーミックコンタクトに対応する一セットのコンタクト領域上にマスキング材料を適用し、前記マスキング材料を適用した後に、前記半導体層の表面の一セットのマスクされていない領域を覆う隆起領域を形成し、前記隆起領域の形成後に前記一セットのコンタクト領域上にオーミックコンタクトを形成することを含み、前記オーミックコンタクトを形成することは、デバイスヘテロ構造に前記一セットの半導体層のいずれかを形成する材料の品質が損なわれる温度範囲よりも低い処理温度において実施されることを特徴とするシステムを提供する。

10

**【0012】**

本発明の例示の態様は、本明細書において説明した1つもしくは複数の問題および／または説明していない他の1つもしくは複数の問題を解決するように設計される。

20

**【0013】**

本開示のこれらおよび他の特徴は、本発明の様々な態様を表す添付の図面と共に為される以下の本発明の様々な態様の詳細な説明からより容易に理解されるであろう。

**【図面の簡単な説明】****【0014】**

【図1A】先行技術による反応性イオンエッティング（RIE）および再成長プロセスを使用して形成された典型的なオーミックコンタクトを示す。

【図1B】先行技術による反応性イオンエッティング（RIE）および再成長プロセスを使用して形成された典型的なオーミックコンタクトを示す。

30

【図1C】先行技術による反応性イオンエッティング（RIE）および再成長プロセスを使用して形成された典型的なオーミックコンタクトを示す。

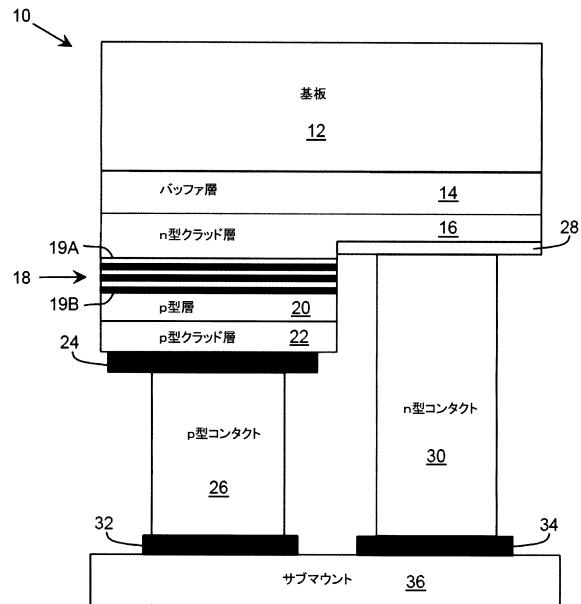

【図2】一実施形態による例示的なエミッティングデバイスの模式構造を示す。

【図3】一実施形態によるデバイスヘテロ構造を製造するための例示的な一セットの作業を示す。

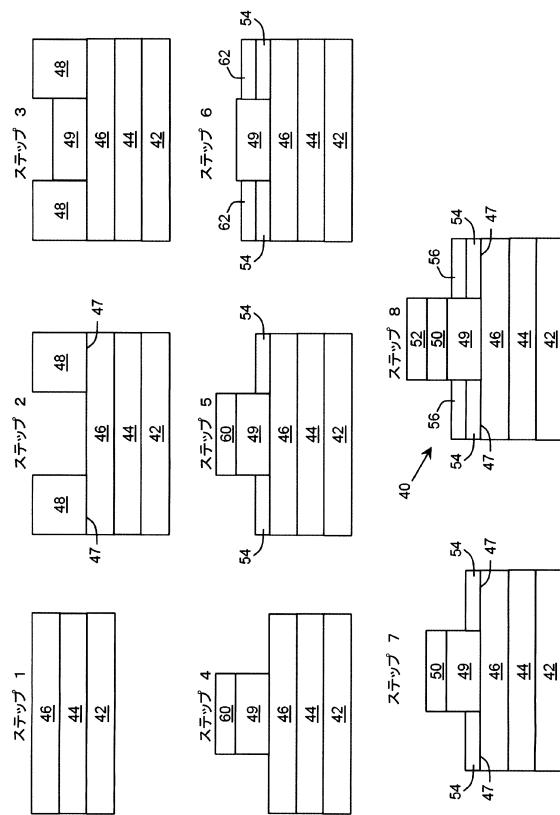

【図4】一実施形態によるデバイスヘテロ構造を製造するための別の例示的な一セットの作業を示す。

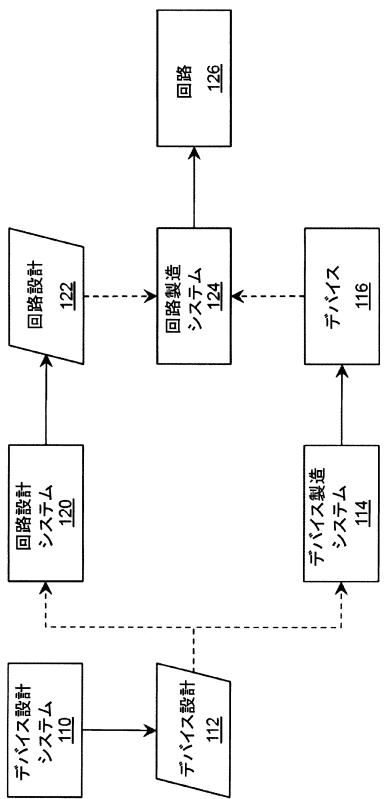

【図5】は、一実施形態による回路を製造するための例示的なフロー図を示す。

**【発明を実施するための形態】****【0015】**

40

図面は原寸に比例していない場合もあり得ることに注意されたい。図面は、本発明の典型的な態様を表すことのみを意図するものであり、したがって、本発明の範囲を限定するものとしてみなすべきではない。図面において、同様の付番は、図面間において同様の要素を表している。

**【0016】**

上記において示したように、本発明のある態様は、半導体層に対するオーミックコンタクトを形成するための解決策を提供する。半導体層の表面上の一セットのコンタクト領域に、マスキング材料が適用される。それに続いて、半導体層のマスクされていない領域上に、デバイスヘテロ構造の1つまたは複数の層が形成される。デバイスヘテロ構造の1つまたは複数の層が形成された後に、オーミックコンタクトが形成され得る。オーミックコ

50

ンタクトの形成は、デバイスヘテロ構造に任意の半導体層を形成する材料の品質が損なわれる温度範囲よりも低い処理温度において実施され得る。オームックコンタクトの形成は、半導体層をエッティングすることなく実施することができ、ならびにオームックコンタクトを、半導体層とオームックコンタクトの界面において半導体層に格子整合させることができる。結果として得られるオームックコンタクトは、従来のアプローチを使用して形成されたオームックコンタクトよりも高い信頼性を有し得る。本明細書において使用される場合、特に明記されない限り、用語「一セット（set）」は、1つもしくは複数（すなわち、少なくとも1つ）を意味し、語句「任意の解決策」は、既知の解決策または後に開発される解決策を意味する。

## 【0017】

10

図2を参照すると、図2は、一実施形態による例示的なエミッティングデバイス10の模式構造を示している。より詳細な実施形態において、エミッティングデバイス10は、発光ダイオード（LED）、例えば、従来のLEDまたはスーパールミネッセントLEDなどとして作動するように構成される。あるいは、エミッティングデバイス10は、レーザーダイオード（LD）として作動するように構成することもできる。どちらの場合においても、エミッティングデバイス10の作動の際、バンドギャップに相当するバイアスを印加することにより、結果として、当該エミッティングデバイス10の活性領域18から電磁放射線が放出される。エミッティングデバイス10によって放出された電磁放射線は、可視光、紫外線、深紫外線、赤外光、および／または同様のものを含む、波長の任意の範囲内にピーク波長を含み得る。

## 【0018】

20

本発明の態様は、エミッティングデバイス10と併せて示され説明されるが、本発明の態様は、他のタイプのデバイスの形成においても利用することができますことは理解されたい。例えば、当該デバイスは、光検出装置、フォトディテクター、フォトダイオード、および／または同様のものであり得る。同様に、当該デバイスは、バイポーラ接合トランジスタ（BJT）、ヘテロ接合バイポーラトランジスタ（HBT）、pn接合ダイオード、スイッチングダイオード、サイリスタ、および／または同様のものであり得る。

## 【0019】

いずれにせよ、半導体ベースのデバイス、例えばエミッティングデバイス10など、は、典型的には、複数の層で構成される。それぞれの層は、様々な要素に対してモル分率の特定の組み合わせを有する（例えば、所定の値のx、y、および／またはz）。2つの層の間の界面は、半導体ヘテロ接合として形成される。界面において、モル分率の組み合わせは、別々の量によって変化すると考えられる。モル分率の組み合わせが連続的に変化する層は、傾斜化されていると言われる。半導体層のスタックは、いくつかのn型ドープされた層と1つもしくは複数のp型ドープされた層とを含み得る。典型的な半導体デバイスは、オームックコンタクトを必要とする。

## 【0020】

30

図2に示されているように、エミッティングデバイス10は、基板12と、基板12に隣接するバッファ層14と、バッファ層14に隣接するn型クラッド層16（例えば、電子供給層）と、n型クラッド層16に隣接する、n型面19Aを有する活性領域18とを含むヘテロ構造を含む。さらに、エミッティングデバイス10のヘテロ構造は、活性領域18のp型面19Bに隣接するp型層20（例えば、電子ブロッキング層）およびp型層20に隣接するp型クラッド層22（例えば、正孔供給層）を含む。

## 【0021】

40

より詳細な例示的な実施形態において、エミッティングデバイス10は、様々な層のうちのいくつもしくはすべてがII - V族材料系から選択される元素で形成されている、II - V族材料ベースのデバイスである。さらにより詳細な例示的な実施形態において、エミッティングデバイス10の様々な層は、II族窒化物ベースの材料で形成される。II族窒化物材料は、 $B_w A_l X_g Y_I n_z N$ （式中、0 < W、X、Y、Z < 1およびW + X + Y + Z = 1である）のように、1種または複数種のII族元素（例えば、ホ

50

ウ素 (B)、アルミニウム (Al)、ガリウム (Ga)、およびインジウム (In) ) と窒素 (N) とを含む。例示的なIII族窒化物材料としては、III族元素の任意のモル分率を有する、AlN、GaN、InN、BN、AlGaN、AlInN、AlBN、AlGaInN、AlGaBN、AlInBN、およびAlGaInBNが挙げられる。

#### 【0022】

III族窒化物ベースのエミッティングデバイス10の例示的な実施形態は、 $In_y Al_{1-x-y} Ga_{1-x-y} N$ 、 $Ga_z In_y Al_x B_{1-x-y-z} N$ 、 $Al_x Ga_{1-x} N$ 半導体合金、または同様のもので構成される活性領域18(例えば、一セットの交互の量子井戸および量子障壁)を含む。同様に、n型クラッド層16およびp型層20の両方を、 $In_y Al_x Ga_{1-x-y} N$ 合金、 $Ga_z In_y Al_x B_{1-x-y-z} N$ 合金、または同様のもので構成することもできる。

x、y、およびzで与えられるモル分率は、様々な層16、18、および20の間で変わり得る。基板12は、サファイア、ケイ素(Si)、ゲルマニウム、シリコンカーバイド(SiC)、バルク半導体テンプレート材料、例えば、AlN、GaN、BN、AlGaN、AlInN、AlON、LiGaO<sub>2</sub>、AlGaBN、AlGaInN、AlGaIN、および/または同様のもの、あるいは他の好適な材料であり得、ならびに、極性、非極性、半極性であり得る。バッファ層14は、AlN、AlGaN、AlInN、AlGaBN、AlGaInN、AlGaInBN、AlGaN/AlN超格子、および/または同様のもので構成され得る。

#### 【0023】

エミッティングデバイス10に関連して示されているように、p型金属24をp型クラッド層22に取り付けることができ、p型コンタクト26をp型金属24に取り付けることができる。さらに、本明細書において説明されるように、n型コンタクト層28を、n型クラッド層16上に形成することができ、本明細書において説明されるプロセスを使用して、n型コンタクト30をn型コンタクト層28上に形成することができる。p型金属24およびn型コンタクト層28は、それぞれ、対応する層22、16に対するオーミックコンタクトを形成し得る。一実施形態において、p型金属24は、数層の導電性および反射性の金属層を有し、その一方で、p型コンタクト26は、高い導電性の金属を含む。一実施形態において、p型クラッド層22および/またはp型コンタクト26は、活性領域18が発生される電磁放射線に対して透明(例えば、半透明または透明)であり得る。例えば、p型クラッド層22および/またはp型コンタクト26は、短周期超格子、例えば、透明なマグネシウム(Mg)ドープされたAlGaN/AlGaNの短周期超格子構造(SPSL)など、を含み得る。さらに、p型コンタクト26および/またはn型コンタクト層28は、活性領域18が発生される電磁放射線に対して反射性であり得る。別の実施形態において、n型クラッド層16および/またはn型コンタクト層28は、AlGaNのSPSLなどの短周期超格子で形成することができ、これらは、活性領域18が発生される電磁放射線に対して透明である。

#### 【0024】

本明細書において使用される場合、層が放射線波長の対応領域における電磁放射線の少なくとも一部を通過させる場合、当該層は透明である。例えば、透明層は、活性領域18が放出する光(例えば、紫外線光または深紫外線光など)のピーク放出波長に対応するある範囲の放射線波長(例えば、ピーク放出波長+/-5ナノメートル)の光の少なくとも一部を通過させるように構成することができる。本明細書において使用される場合、層がおよそ0.5パーセントを超える放射線を通過させる場合、当該層は当該放射線に対して透明である。より詳細な実施形態において、透明層は、およそ5パーセントを超える放射線を通過させるように構成される。さらにより詳細な実施形態において、透明層は、およそ10パーセントを超える放射線を通過させるように構成される。同様に、層が、関連する電磁放射線(例えば、活性領域のピーク放出に近い波長を有する光)の少なくとも一部を反射する場合、当該層は反射性である。一実施形態において、反射層は、少なくともおよそ5パーセントの放射線を反射するように構成される。

#### 【0025】

10

20

30

40

50

エミッティングデバイス 10 に関するより詳細に示されるように、当該デバイス 10 は、コンタクト 26、30 を介してサブマウント 36 に取り付けられ得る。この場合、基板 12 は、エミッティングデバイス 10 の上部に位置される。この点に関して、p 型コンタクト 26 および n 型コンタクト 30 は両方とも、それぞれ、コンタクトパッド 32、34 を介してサブマウント 36 に取り付けられ得る。一実施形態において、n 型コンタクト層 28 は透明材料であり、その一方で、n 型コンタクト 30 は、当該 n 型コンタクト層 28 からの光抽出を向上させるために、反射性材料（例えば、金属）である。サブマウント 36 は、窒化アルミニウム（AlN）、シリコンカーバイド（SiC）、および／または同様のもので形成され得る。

## 【0026】

10

本明細書において説明するエミッティングデバイス 10 の層構成が例示に過ぎないことは理解されたい。この点に関して、エミッティングデバイス／ヘテロ構造は、交互の層構成、1つもしくは複数の追加の層、および／または同様のものを含み得る。結果として、様々な層がお互いに直接隣接している（例えば、お互いにコンタクトしている）ように示されているが、エミッティングデバイス／ヘテロ構造に1つもしくは複数の中間層が存在していてもよいことは理解されたい。

## 【0027】

先行技術の解決策を使用したデバイス 10 の形成は、典型的には、p 型クラッド層 22、p 型層 20、および活性領域 18 をエッチングすることによって、n 型コンタクトが形成されるべき領域において n 型クラッド層 16 を露出させる工程を含む。それに続いて、金属（図示されず）が、典型的には、n 型クラッド層 16 上に被着され、n 型オームックコンタクトを形成するために、n 型コンタクト 30 が当該金属上に形成される。同様の手順が、トランジスタおよび他のタイプの半導体デバイスのためのオームックコンタクトを形成するために用いられる。その一方で、本発明者らは、デバイス、例えば、エミッティングデバイス 10 など、または当該デバイスのためのヘテロ構造を製造するためのプロセスを提案しており、これは、1つもしくは複数のコンタクト、例えば、n 型コンタクト 30などを形成するために、n 型クラッド層 16 および／または任意の他の層のエッチングを必要としない。n 型コンタクト 30 の形成に関する説明したが、本発明の態様は、p 型コンタクト、例えば、p 型コンタクト 26 など、の形成も対象とし得ることは理解されたい。

20

## 【0028】

30

この点に関して、図 3 は、ある態様によるデバイスヘテロ構造 40 において半導体層 46 に対する少なくとも1つのコンタクト 56 を含むデバイスヘテロ構造 40（ステップ 8 に示されている）を製造するための例示的な一セットの作業を示している。本明細書において説明されるように、当該プロセスは、半導体層 46 に対する1つもしくは複数のオームックコンタクトを形成するために使用することができる。当該半導体層 46 は、p 型層であってもまたはn型層であってもよい。本明細書において説明されるプロセスは、エッチングすることなく、そのようなコンタクトの製造を可能にする。

## 【0029】

40

ステップ 1 において、基板 42 と、当該基板 42 上の第一層 44 と、当該第一層 44 上の第二層 46 とを含むヘテロ構造を得る（例えば、形成するか、成長させるか、購入するか、および／または同様の方法により得る）。一実施形態において、層 44、46 は、本明細書において説明されるような任意のタイプの基板材料を含む基板 42 上においてエピタキシャルに成長させたII族窒化物層である。別の実施形態において、層 44 は、他の層、例えば層 46 など、のエピタキシャル成長の前に基板 42 上に成長させたバッファ層または核形成層である。3つの層 42、44、46 が示されているが、任意の数の層を含ませることは理解されたい。この点に関して、層 44、46 は、複数の半導体層および／またはある層のための複数の副層を含み得る。

## 【0030】

いずれにしても、各半導体層は、様々な成長条件下において成長させた様々な組成を含

50

み得る。例えば、一実施形態において、同じ組成の層を、異なる温度、異なるV/I比、および/または同様の条件において成長させることができる。さらに、層46は、ドープされた材料で形成された少なくとも1つの層を含み得る。当該ドーピングは、層46の一セットのコンタクト領域上に続いて形成されるオームックコンタクトの間に導電性経路を提供するように構成され得る。一実施形態において、層46は、低いキャリアイオンエネルギーを有するドープされた窒化ガリウム(GaN)半導体材料で形成される。

#### 【0031】

ステップ2において、一セットのマスク48が、層46の表面における一セットのコンタクト領域47上に形成される。当該マスク48は、下にある半導体層46を損なうことなく除去することができる、任意のタイプのマスキング材料であり得る。一実施形態において、当該マスク48は、二酸化シリコン(SiO<sub>2</sub>)または窒化シリコン(Si<sub>3</sub>N<sub>4</sub>)を含む。より詳細な実施形態において、当該一セットのマスク48は、最初に、層46の表面の実質的全体にマスキング材料を適用することによって形成される。それに続いて、当該マスキング材料を、層46の表面のいくつかの領域から除去することにより、一セットのコンタクト領域47上に一セットのマスク48が形成され得る。当該マスキング材料の除去は、例えば、フォトリソグラフィ技術などを用いて実施することができる。

#### 【0032】

ステップ3において、高いキャリア伝導性を有する半導体領域49のような隆起したメサが、層46を覆うように形成される。隆起領域49には、層46とは異なる光学的および/または電気的特性を持たせることができる。例えば、隆起領域49は、層46の材料よりも高い導電率を有する材料で形成することができる。ただし、隆起領域49は、層46と同じ型(例えば、n型またはp型)であってもよい。ドープした半導体材料(例えば、本明細書において説明したドープしたGaNなど)を使用する過成長(overgrowth)手順は、隆起領域49を形成するために用いることができる。ステップ4において、隆起領域49の上に半導体層50が成長され得る。半導体層50は、例えば、異なる組成を有する、および/または異なる成長条件を使用して成長させた、いくつかの半導体副層を含むことができる。可能な一実施形態において、半導体層50は、隆起領域49を形成する材料のバンドギャップよりも広いバンドギャップを有する材料で形成される。半導体層50が、高濃度でドープされた材料で形成される場合、半導体層50と隆起領域49との間の界面において、二次元電子ガスが形成され得る。

#### 【0033】

別の可能な実施形態において、半導体層50は、層46を形成する材料とは異なる光学的および/または電気的特性を有する材料で形成される。例えば、半導体層50は、様々なV/I比、温度、および他の成長パラメータを含む異なるエピタキシャル成長条件下で成長させることができる。さらなる別の実施形態において、半導体層50には、多層構造、例えば、I-II族窒化物副層の超格子など、を含ませることができる。別の実施形態において、半導体層50は、半導体層50と隆起領域49との間の界面が量子井戸および量子障壁で構成される発光領域を含有するp型領域を形成し得る。

#### 【0034】

デバイスヘテロ構造40のために所望の一セットの半導体層が形成されると、一セットのオームックコンタクトの形成のために、デバイスヘテロ構造を調製することができる。この点に関して、ステップ5において、マスク48を形成するマスキング材料が、その後の半導体過成長のために除去される。ステップ6において、マスク52が、任意の解決策を使用して(例えば、SiO<sub>2</sub>、Si<sub>3</sub>N<sub>4</sub>などのマスキング材料を適用することによって)、半導体層50(または、半導体層50が存在しない場合には、隆起領域49)の上に位置され得る。当該ヘテロ構造40がトランジスタデバイスのために使用される場合、例えば、絶縁表面の上にゲートコンタクトを被着させるなどのためにマスク52が適用され得る。この点に関して、いくつかのタイプの半導体デバイスに対しては、マスク52が適用されない場合もあることを理解されたい。

#### 【0035】

10

20

30

40

50

それに続いて、半導体層46の一セットのコンタクト領域47上に、一セットのオーミックコンタクトが形成され得る。一実施形態において、当該一セットのオーミックコンタクトは、デバイスヘテロ構造40における半導体層42、44、46、50のいずれかを形成する材料の品質が損なわれる温度範囲よりも低い処理温度において形成される。例えば、例示的実施例として図2のデバイス10を簡潔に参照すると、p型クラッド層22、p型層20、活性領域18、またはn型クラッド層16を形成する材料の品質を損なわないであろう温度において、n型コンタクト30の形成を実施することができる。一実施形態において、III族窒化物材料を使用して形成されるデバイスヘテロ構造の場合、p型層の成長にとって好ましい温度範囲は、950～1050である。この場合、当該一セットのオーミックコンタクトの形成において使用される処理温度は、950より低い、

10 例えば、およそ850～およそ950の範囲であり得る。

#### 【0036】

ステップ7において、一セットの高導電性半導体層54が、任意の解決策を使用してヘテロ構造40の一セットのコンタクト領域47上に過成長され得る。ヘテロ構造40が使用されるであろう対応するデバイスに応じて、標的厚さまでエピタキシャル成長を実施することができ、この厚さは、隆起領域49の厚さを超えてよくまたは超えなくてもよい。例えば、発光デバイスの場合、当該過成長させた半導体層54は、隣接する半導体層と同じ型であり得る。この場合、半導体層54の厚さは、隆起領域49の厚さと等しいかそれ未満であり得る。

20

#### 【0037】

ステップ8において、一セットの半導体層54の上にオーミック金属56を被着させることにより、半導体層46に対する低抵抗のオーミックコンタクトが形成され得る。オーミック金属56は、任意の解決策、例えば、熱蒸発、電子ビーム蒸発、化学蒸着、電気メッキ、電着、および／または同様の方法、を使用して被着させることができる。さらに、当該オーミック金属56をアニール処理することにより、当該オーミック金属56とその下の一セットの半導体層54との間に中間層を形成することができる。当該中間層は、当該一セットの半導体層54中の、オーミック金属56のナノサイズの突起部を含み得る。当該オーミックコンタクトの実施形態は、図1Cに示されるような荒い表面を含み得、このような表面は、例えば、当該一セットの半導体層54に対して適切な一セットの成長条件を選択することによって調製することができる。当該一セットの成長条件は、高いV/III比での成長、低い温度（例えば、1000以下の温度）での成長、および／または同様の条件を含み得る。

30

#### 【0038】

一実施形態において、当該一セットの半導体層54は、 $A_{1-w}I_{n_x}G_{a_y}B_zN$ （式中、 $0 \leq w \leq 1$  および  $w + x + y + z = 1$  である）で形成される。より詳細な実施形態において、A1の組成は、100パーセント未満であるが、1パーセントを超えるものであり、すなわち、 $0.01 < w < 1$  である。この場合、例示的なIII族材料としては、AlGaN、AlInGaN、AlInN、AlBN、AlInBN、AlGaBN、AlGaNBN、および／または同様のものが挙げられる。さらに、当該材料は、 $0.001$  を超えるモル分率xのインジウムを含み得る。一セットの半導体層54が複数の層を含む場合、当該層は、異なる成長条件（例えば、温度、質量流量比、例えばV/III比など、および／または同様のもの）および／または同様の条件を使用して成長させた、III族元素の異なるモル分率（すなわち、異なる値のw、x、y、z）を有し得る。一実施形態において、一セットの半導体層54は、半導体層46よりも広いバンドギャップを有する材料で形成され、その結果、半導体層46（例えば、発光デバイスのクラッド層）と一セットの半導体層54との間の界面において二次元自由キャリアガスを生じる。

40

#### 【0039】

一セットの半導体層54の組成は、実質的に一定にすことができ、または傾斜を持たせることもできる。一実施形態において、アルミニウムのモル分率xは、オーミック金属

50

5 6 からの距離の関数として変わる。例えば、当該アルミニウムのモル分率は、一セットの半導体層 5 4 とオーミック金属 5 6 との界面から一セットの半導体層 5 4 と半導体層 4 6 の界面へと減少し得る。別の実施形態において、当該アルミニウムのモル分率は、インジウムの濃度の変化に合わせて変わる。例えば、インジウムのモル分率が増加すると、一方で、上記において説明したように、アルミニウムのモル分率が減少し得る。傾斜が存在していてもよく、当該傾斜は、例えば、0 ~ 0 . 6 の値のアルミニウムのモル分率の変化を含み得る。あるいは、インジウムのモル分率は、一セットの半導体層 5 4 とオーミック金属 5 6 との界面から一セットの半導体層 5 4 と半導体層 4 6 との界面へと減少し得、その一方で、アルミニウムのモル分率は、実質的に一定に保たれ、結果として、ガリウムまたは他の I II 属材料によるインジウムとの置き換えが生じる。

10

#### 【 0 0 4 0 】

当該傾斜は、例えば、コンタクト領域 4 7 での逆キャリア（例えば、n 型コンタクトの場合の正孔および p 型コンタクトの場合の電子）の蓄積の誘起を避けることができるよう、一セットの半導体層 5 4 の標的の伝導帯エネルギーに基づいて、および / または一セットの半導体層 5 4 （例えば、高濃度でドープされた）と底部半導体層 4 6 （例えば、ほとんどドープされていない）との間において鉛直電流を輸送することができるように、構成することができる。例えば、半導体層 4 6 が、（例えば、非常に短い紫外波長で作動する L E D の一部として）4 0 パーセントより高いアルミニウムのモル分率を有する I II 族窒化物材料を含む場合、当該傾斜は、一セットの半導体層 5 4 の任意のポイントの間の伝導バンドエネルギーおよび半導体層 4 6 のコンタクト領域 4 7 の表面ポイントの伝導バンドエネルギーにおけるエネルギー変化全体がおよそ 3 k T 未満（この場合、k はボルツマン定数であり、T はデバイスの作動温度である）である構成することができる。当該表面ポイントは、コンタクト領域 4 7 に対応する半導体層 4 6 の表面の 1 0 ナノメートル以内の半導体層 4 6 の任意のポイントであり得る。

20

#### 【 0 0 4 1 】

一セットの半導体層 5 4 の 1 つもしくは複数は超格子を含み得る。この場合、当該超格子は、ピリオドからピリオドへの組成の周期的または非周期的変動を有し得る。さらに、半導体層 5 4 の成長は、材料をデルタドーピングするステップを含み得る。一実施形態において、半導体層 5 4 は、n 型ドーパントを含む。より詳細な例示的実施形態において、一セットの半導体層 5 4 は、高濃度にドープされた n + G a N 層を含み得る。

30

#### 【 0 0 4 2 】

一セットの半導体層 5 4 および / またはオーミック金属 5 6 の 1 つもしくは複数の態様は、一セットの半導体層 5 4 とオーミック金属 5 6 との間のコンタクトを向上させるよう、および / または、オーミックコンタクトの 1 つもしくは複数の態様を変えるように構成することができる。例えば、一セットの半導体層 5 4 は、テクスチャード加工された材料またはパターン形成された材料、例えば、I II 族窒化物材料などを含み得る。一実施形態において、一セットの半導体層 5 4 の表面は、一セットのピラミッド形の開口部を含み得、それに対し、オーミック金属 5 6 が、一セットの半導体層 5 6 中へと延びる一セットの対向するピラミッド形の突出部を形成する。この場合、オーミック金属 5 6 と一セットの半導体層 5 6 との間の接着が向上され得る。ピラミッド形の開口部が単なる例示的実施例にすぎないことは理解されたい。概して、オーミック金属 5 6 から一セットの半導体層 5 4 中へと延びる任意のタイプの突出部は、コンタクト抵抗および接着性などのコンタクト特性を向上させ得る。これらの不均一領域の形成は、例えば、適切な成長条件を選択して、荒いモルホロジーを有する一セットの半導体層 5 4 を製造することにより、達成することができる。例えば、そのような条件は、いわゆる三次元成長に起因し得、これは、高い値の V / I II 比および低い温度、例えば、およそ 1 0 0 0 またはそれ以下の温度など、において達成することができる。あるいは、オーミック金属 5 6 の被着の前に、一セットの半導体層 5 4 をエッティングまたはパターン形成してもよい。最後に、当該不均一領域は、オーミック金属 5 6 のアニール処理の際に生じ得る。

40

#### 【 0 0 4 3 】

50

同様に、オーミック金属 5 6 は、一セットの半導体層 5 4 の表面にコンタクトする複数の針状突起部を含んでもよい。例えば、当該針状突起部は、周期的な針状突起部を含み得、これは、例えば、リソグラフィ処理を使用して形成することができる。オーミック金属 5 6 は、当該針状突起部を接続する金属のオーバーレイ層を含んでいてもよい。当該針状突起部は、光抽出および/または光反射のための回折格子として機能し得る。

#### 【 0 0 4 4 】

一実施形態において、オーミック金属 5 6 は、オーミック金属 5 6 が一セットの半導体層 5 4 を貫通しかつその下の半導体層 4 6 にコンタクトするように、合金化され得る。さらに、オーミック金属 5 6 は、(図 2 の層 3 4 に関連して示されるような)ヒートシンクへのフリップチップ接続のために使用することができる。

10

#### 【 0 0 4 5 】

図 3 に示されるステップ 1 ~ 8 は変更またはステップを追加もしくは除去できることは理解されたい。例えば、図 4 は、一実施形態によるデバイスヘテロ構造を製造するための別の例示的な一セットの作業を示している。この場合、ステップ 1 ~ 3 は図 3 と同じであるが、後続のステップは変更されている。特に、ステップ 4 において、マスキング領域 6 0 が、隆起領域 4 9 上に形成され、一セットのマスク 4 8 が除去される。ステップ 5 において、一セットの半導体層 5 4 の再成長が実施される。ステップ 6 において、マスキング領域 6 0 が除去され、一セットのマスキング領域 6 2 が、一セットの半導体層 5 4 上に形成される。ステップ 7 において、半導体層 5 0 が形成され、一セットのマスキング領域 6 2 が除去される。ステップ 8 において、マスキング層 5 2 が、半導体層 5 0 上に形成され、オーミック金属 5 6 が、一セットの半導体層 5 4 上に被着される。このプロセスにおいて、半導体層 5 0 は、一セットの半導体層 5 4 の後に形成されており、これは、一セットの半導体層 5 4 のエピタキシャル成長が生じる温度のさらなる制御を可能にし得る。例えば、図 4 の実施形態は、半導体層 5 0 のエピタキシャル成長のための温度が一セットの半導体層 5 4 のエピタキシャル成長のための温度より低い場合に用いることができる。

20

#### 【 0 0 4 6 】

エッチングを必要としない、過成長手順を使用して一セットのオーミックコンタクトを形成するためのプロセスに関連して示し説明したが、本発明の態様は追加の実施形態を提供することを理解されたい。例えば、一実施形態は、本明細書において説明した手順を使用して形成された、過成長させたコンタクトを提供する。この場合、当該コンタクトは、一セットの半導体層 5 4 が、半導体層 4 6 と一セットの半導体層 5 4 との界面において半導体層 4 6 と格子整合する、シュードモルフィック整合を含み得る。さらに、一実施形態は、本明細書において説明したプロセスを使用して形成された 1 つもしくは複数のオーミックコンタクトを含むデバイスを製造するためのプロセスを提供する。

30

#### 【 0 0 4 7 】

一実施形態において、本発明は、本明細書において説明されるように設計および製造された 1 つもしくは複数のデバイスを含む回路を設計および/または製造する方法を提供する。この点に関して、図 5 は、一実施形態による回路 1 2 6 を製造するための例示的フローダイアグラムを示している。最初に、使用者は、デバイス設計システム 1 1 0 を用いて、本明細書において説明されるような半導体デバイスのためのデバイス設計 1 1 2 を生成することができる。デバイス設計 1 1 2 は、デバイス設計 1 1 2 によって定義された特徴に従って一セットの物理的デバイス 1 1 6 を生成するためにデバイス製造システム 1 1 4 が使用することのできるプログラムコードを含み得る。同様に、デバイス設計 1 1 2 は、(例えば、回路で使用するために利用することができる構成要素として)回路設計システム 1 2 0 に提供され得、使用者はそれを利用して、(例えば、1 つもしくは複数の入力および出力を、回路に含まれる様々なデバイスに接続することによって)回路設計 1 2 2 を生成することができる。回路設計 1 2 2 は、本明細書において説明されるように設計されたデバイスを含むプログラムコードを含み得る。いずれにしても、回路設計 1 2 2 および/または 1 つもしくは複数の物理的デバイス 1 1 6 が、回路設計 1 2 2 に従って物理的回路 1 2 6 を生成することができる回路製造システム 1 2 4 に提供され得る。当該物理的回路 1 2 6 を生成することができる回路製造システム 1 2 4 に提供され得る。

40

50

路 126 は、本明細書において説明されるように設計された 1 つもしくは複数のデバイス 116 を含み得る。

#### 【 0048 】

別の実施形態において、本発明は、本明細書において説明されるような半導体デバイス 116 を設計するためのデバイス設計システム 110 および / または製造するためのデバイス製造システム 114 を提供する。この場合、当該システム 110、114 は、本明細書において説明されるような半導体デバイス 116 を設計および / または製造するための方法を実践するようにプログラミングされた、汎用のコンピューティングデバイスを含み得る。同様に、本発明の一実施形態は、本明細書において説明されるように設計および / または製造された少なくとも 1 つのデバイス 116 を含む回路 126 を設計するための回路設計システム 120 および / または製造するための回路製造システム 124 を提供する。この場合、当該システム 120、124 は、本明細書において説明されるような少なくとも 1 つの半導体デバイス 116 を含む回路 126 を設計および / または製造するための方法を実践するようにプログラミングされた、汎用のコンピューティングデバイスを含み得る。10

#### 【 0049 】

さらなる別の実施形態において、本発明は、少なくとも 1 つのコンピュータ読み込み可能な媒体に固定されたコンピュータプログラムであって、実行された場合に、本明細書において説明されるような半導体デバイスを設計および / または製造する方法をコンピュータシステムが実践することを可能にする、コンピュータプログラムを提供する。例えば、当該コンピュータプログラムは、デバイス設計システム 110 が本明細書において説明されるようなデバイス設計 112 を生成できるようにし得る。この点に関して、当該コンピュータ読み込み可能な媒体は、コンピュータシステムによって実行された場合に本明細書において説明したプロセスのいくつかまたはすべてを実践する、プログラムコードを含む。用語「コンピュータ読み込み可能な媒体」は、コンピューティングデバイスがプログラムコードの保存コピーを理解、再生、またはそれ以外で通信することができるよう、現在既知のまたは後に開発される任意のタイプの 1 つもしくは複数の有形的表現媒体を包含することを理解されたい。20

#### 【 0050 】

別の実施形態において、本発明は、コンピュータシステムによって実行された場合に本明細書において説明されたプロセスのいくつかまたは全てを実践する、プログラムコードのコピーを提供する方法を提供する。この場合、コンピュータシステムは、当該プログラムコードのコピーを処理して、一セットのデータシグナルにおけるプログラムコードのコピーをエンコードするように設定および / または変更された 1 つもしくは複数の特性を有する一セットのデータシグナルを、第二の異なる場所での受信のために、生成および転送することができる。同様に、本発明の一実施形態は、本明細書において説明したプロセスのいくつかまたは全てを実践するプログラムコードのコピーを取得する方法を提供し、これは、本明細書において説明した一セットのデータシグナルを受信して、当該一セットのデータシグナルを、少なくとも 1 つのコンピュータ読み取り可能な媒体中に固定されたコンピュータプログラムのコピーへと翻訳するコンピュータシステムを含む。どちらの場合も、当該一セットのデータシグナルは、任意のタイプの通信リンクを使用して転送 / 受信することができる。3040

#### 【 0051 】

さらなる別の実施形態において、本発明は、本明細書において説明されるような半導体デバイスを設計するためのデバイス設計システム 110 および / または製造するためのデバイス製造システム 114 を生成する方法を提供する。この場合、コンピュータシステムを得ること（例えば、作り出すこと、維持すること、利用可能にすること、など）ができ、本明細書において説明したプロセスを実施するための 1 つもしくは複数の構成要素を、得ること（例えば、作成すること、購入すること、使用すること、変更すること、など）ができ、コンピュータシステムへと展開することができる。この点に関して、当該展開は50

、(1)コンピューティングデバイスへのプログラムコードのインストール；(2)1つもしくは複数のコンピューティングデバイスおよび／またはI/Oデバイスをコンピュータシステムに追加すること；(3)コンピュータシステムが本明細書において説明したプロセスを実行できるように、当該コンピュータシステムを組み込むことおよび／または変更すること；および／または同様のもの、の1つもしくは複数を含み得る。

#### 【0052】

本発明の様々な態様についての前述の説明は、例示および説明の目的のために提示されたものである。これらは、包括的であること、または開示された厳密な形態に本発明を限定することを意図するものではなく、明らかに、多くの変更および変形が可能である。当業者に明らかであり得るそのような変更および変形は、添付の請求項によって定義されるような本発明の範囲内に含まれる。

10

#### 【0053】

##### 関連出願の参照

本出願は、同時係属中の「Ohmic Contact to Semiconductors and the Process of Producing the Same」の名称において2012年2月23日に出願された米国特許仮出願第61/602,155号の恩典を主張するものであり、なお、当該仮出願は、参考により本明細書に組み入れられる。

【図1A】

【図1B】

【図1C】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 33/20 (2010.01) H 01 L 33/32

H 01 L 33/32 (2010.01) H 01 L 31/10 H

H 01 L 31/10 (2006.01)

(72)発明者 シュール,マイケル

アメリカ合衆国 12110 ニュー ヨーク州, ラサム, スターボード ウェイ 10

(72)発明者 ヤン,ジンウェイ

アメリカ合衆国 29209 サウス カロライナ州, コロンビア, チムニー ヒル ロード 4

24

(72)発明者 ドプリンスキ,アレクサンダー

アメリカ合衆国 02906 ロード アイルランド州, プロヴィデンス, エヴァレット アヴェニ

ュ 23

(72)発明者 シャタロフ,マキシム,エス.

アメリカ合衆国 29212 サウス カロライナ州, コロンビア, ソーンヒル ロード 273

審査官 村井 友和

(56)参考文献 特表2006-517726(JP,A)

特開2006-287212(JP,A)

特開2010-287637(JP,A)

特開平08-255929(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 33 / 00 - 33 / 64