(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6189484号

(P6189484)

(45) 発行日 平成29年8月30日(2017.8.30)

(24) 登録日 平成29年8月10日(2017.8.10)

|              |           |            |      |

|--------------|-----------|------------|------|

| (51) Int.Cl. | F 1       |            |      |

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 616V |

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 618B |

| HO1L 21/8234 | (2006.01) | HO1L 29/78 | 618E |

| HO1L 27/088  | (2006.01) | HO1L 29/78 | 616U |

| HO1L 21/28   | (2006.01) | HO1L 29/78 | 626C |

請求項の数 1 (全 45 頁) 最終頁に続く

|            |                               |                 |                              |

|------------|-------------------------------|-----------------|------------------------------|

| (21) 出願番号  | 特願2016-114367 (P2016-114367)  | (73) 特許権者       | 000153878                    |

| (22) 出願日   | 平成28年6月8日(2016.6.8)           | 株式会社半導体エネルギー研究所 |                              |

| (62) 分割の表示 | 特願2012-230365 (P2012-230365)  | 神奈川県厚木市長谷398番地  |                              |

| 原出願日       | 平成24年10月17日(2012.10.17)       | (72) 発明者        | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社 |

| (65) 公開番号  | 特開2016-167636 (P2016-167636A) | 半導体エネルギー研究所内    |                              |

| (43) 公開日   | 平成28年9月15日(2016.9.15)         | (72) 発明者        | 須澤 英臣<br>神奈川県厚木市長谷398番地 株式会社 |

| 審査請求日      | 平成28年7月6日(2016.7.6)           | 半導体エネルギー研究所内    |                              |

|            |                               | (72) 発明者        | 笹川 慎也<br>神奈川県厚木市長谷398番地 株式会社 |

|            |                               | (72) 発明者        | 半導体エネルギー研究所内                 |

|            |                               | (72) 発明者        | 田中 哲弘<br>神奈川県厚木市長谷398番地 株式会社 |

|            |                               | (72) 発明者        | 半導体エネルギー研究所内                 |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

酸素を含有する下地絶縁層と、

前記下地絶縁層上に設けられた島状の酸化物積層と、

前記酸化物積層の上面に接する領域と、前記酸化物積層のチャネル長方向の側面と接する領域とを有する第1のソース電極層と、

前記酸化物積層の上面に接する領域と、前記酸化物積層の前記チャネル長方向の側面と接する領域とを有する第1のドレイン電極層と、

前記第1のソース電極層上に設けられ、前記酸化物積層の上面に接する領域を有する第2のソース電極層と、

前記第1のドレイン電極層上に設けられ、前記酸化物積層の上面に接する領域を有する第2のドレイン電極層と、

前記第2のソース電極層上及び前記第2のドレイン電極層上に設けられ、前記第2のソース電極層と前記第2のドレイン電極層との間で前記酸化物積層の上面と接する領域を有するゲート絶縁層と、

前記ゲート絶縁層を介して前記酸化物積層と重畳する領域を有するゲート電極層と、

前記ゲート絶縁層上及び前記ゲート電極層上に接して設けられた保護絶縁層と、を有し、

前記酸化物積層は、少なくともチャネル形成領域を有する酸化物半導体層と、前記酸化物半導体層と前記下地絶縁層との間の第1の酸化物層と、前記酸化物半導体層と前記ゲー

ト絶縁層との間の第2の酸化物層と、を含み、

前記第1のソース電極層及び前記第1のドレイン電極層の各々は、前記チャネル形成領域側の上端部に曲面を有し、

前記第2のソース電極層及び前記第2のドレイン電極層の各々は、窒化金属を含み、

前記下地絶縁層と前記ゲート絶縁層とは、前記酸化物積層の外周部において接する領域を有し、

前記保護絶縁層は、前記ゲート絶縁層よりも酸素に対する透過性が低い半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

10

本明細書等で開示する発明は、半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、画像表示装置、半導体回路及び電子機器は、全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（単に表示装置とも表記する）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

20

【0004】

例えば、酸化物半導体として、酸化亜鉛、又は、In-Ga-Zn系酸化物半導体を用いてトランジスタを作製する技術が開示されている（特許文献1及び特許文献2参照）。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007-123861号公報

30

【特許文献2】特開2007-96055号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の一態様は、酸化物半導体を用いた半導体装置に良好な電気特性を付与することを課題の一とする。

【0007】

また、本発明の一態様は、酸化物半導体を用いた半導体装置の電気特性の変動を抑制し、信頼性の高い半導体装置を提供することを課題の一とする。

【課題を解決するための手段】

【0008】

40

酸化物半導体を用いてトランジスタを作製する場合、酸化物半導体のキャリアの供給源の一つとして、酸素欠損が挙げられる。トランジスタのチャネル形成領域を含む酸化物半導体に酸素欠損が多く存在すると、チャネル形成領域中に電子を生じさせてしまい、トランジスタのノーマリーオン化、リーク電流の増大、ストレス印加によるしきい値電圧のシフトなど、電気特性の不良を引き起こす要因となる。また、酸化物半導体層において、水素、シリコン、窒素、炭素及び主成分以外の金属元素は不純物となる。例えば、酸化物半導体層中で水素は、ドナー準位を形成し、キャリア密度を増大させる。また、酸化物半導体層中でシリコンは、不純物準位を形成し、該不純物準位がトラップとなって、トランジスタの電気特性を劣化させることがある。

【0009】

50

そのため、酸化物半導体を用いた半導体装置において安定した電気特性を得るために、該酸化物半導体層の酸素欠損を低減し、且つ、水素及びシリコン等の不純物濃度を低減すること措置を講じることが求められる。

#### 【0010】

そこで、本発明の一態様の半導体装置では、酸化物半導体層の下側に設けられた下地絶縁層及び酸化物半導体層の上側に設けられたゲート絶縁層からチャネル形成領域へ酸素を供給することで、チャネル領域に形成されうる酸素欠損を補填する。また、酸化物半導体層で形成されるチャネル領域の近傍において、ソース電極層又はドレイン電極層による酸化物半導体層からの酸素の引き抜きを抑制することで、チャネル領域での酸素欠損を抑制する。さらに、ゲート電極層上に、水素の含有量が低く、酸素の透過性が低いバリア層として機能する保護絶縁層を形成することで、ゲート絶縁層及び/又は下地絶縁層からの酸素の脱離を抑制して、チャネル形成領域へ効果的に酸素を供給する。10

#### 【0011】

また、チャネルを形成する酸化物半導体層の上側及び下側に接して、該酸化物半導体層を構成する金属元素を一種以上含む酸化物層を設ける。これにより、チャネルをゲート絶縁層から離すことができる。また、該酸化物層と酸化物半導体層との界面には、界面準位が形成されにくいため、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。

#### 【0012】

本発明の一態様に係る半導体装置は、上述の構成を有することで、チャネルとして機能する(キャリアの主な経路となる)酸化物半導体層の不純物濃度を低減して、高純度真性化することができる。高純度真性化とは、酸化物半導体層を真性または実質的に真性にすることをいう。なお、本明細書等において実質的に真性という場合、酸化物半導体層のキャリア密度は、 $1 \times 10^{17} / \text{cm}^3$ 未満、 $1 \times 10^{15} / \text{cm}^3$ 未満、または $1 \times 10^{13} / \text{cm}^3$ 未満である。酸化物半導体層を高純度真性化することで、トランジスタに安定した電気特性を付与することができる。20

#### 【0013】

より具体的には、例えば以下の構成とすることができます。

#### 【0014】

本発明の一態様は、酸素を含有する下地絶縁層と、下地絶縁層上に設けられた島状の酸化物積層と、島状の酸化物積層の上面の一部及びチャネル形成方向の側面と接する第1のソース電極層及び第1のドレイン電極層と、第1のソース電極層及び第1のドレイン電極層上にそれぞれ設けられ、酸化物積層の上面の一部に接する、窒化金属膜でなる第2のソース電極層及び第2のドレイン電極層と、第2のソース電極層及び第2のドレイン電極層上に設けられ、第2のソース電極層及び第2のドレイン電極層との間で酸化物積層の上面と接するゲート絶縁層と、ゲート絶縁層を介して酸化物積層と重畠するゲート電極層と、ゲート絶縁層及びゲート電極層上に接して設けられた保護絶縁層と、を有し、酸化物積層は、少なくともチャネルを形成する酸化物半導体層と、酸化物半導体層と下地絶縁層との間に設けられた第1の酸化物層と、酸化物半導体層とゲート絶縁層との間に設けられた第2の酸化物層と、を含み、下地絶縁層とゲート絶縁層とは、島状の酸化物積層の外周部において接する領域を有し、保護絶縁層は、ゲート絶縁層よりも酸素に対する透過性が低い半導体装置である。30

#### 【0015】

また、本発明の一態様は、酸素を含有する下地絶縁層と、下地絶縁層上に設けられた島状の酸化物積層と、島状の酸化物積層の上面の一部及びチャネル形成方向の側面と接する第1のソース電極層及び第1のドレイン電極層と、第1のソース電極層及び第1のドレイン電極層上にそれぞれ設けられ、酸化物積層の上面の一部に接する、窒化金属膜でなる第2のソース電極層及び第2のドレイン電極層と、第2のソース電極層及び第2のドレイン電極層上に設けられ、第2のソース電極層及び第2のドレイン電極層との間で酸化物積層の上面と接するゲート絶縁層と、ゲート絶縁層を介して、酸化物積層、第2のソース電極層及40

び第2のドレイン電極層の一部と重畳するゲート電極層と、を有し、酸化物積層は、少なくともチャネルを形成する酸化物半導体層と、酸化物半導体層と下地絶縁層との間に設けられた第1の酸化物層と、酸化物半導体層とゲート絶縁層との間に設けられた第2の酸化物層と、を含み、下地絶縁層とゲート絶縁層とは、島状の酸化物積層の外周部において接する領域を有し、保護絶縁層は、ゲート絶縁層よりも酸素に対する透過性が低い半導体装置である。

【0016】

上記の半導体装置において、酸化物半導体層、第1の酸化物層及び第2の酸化物層は、In-M-Zn酸化物 (MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf) であり、第1の酸化物層及び第2の酸化物層は、Inに対するMの原子数比が酸化物半導体層よりも大きいことが好ましい。

10

【0017】

また、上記の半導体装置において、酸化物半導体層は、結晶部を含み、結晶部のc軸は、酸化物半導体層の表面の法線ベクトルに平行であることが好ましい。

【0018】

また、上記の半導体装置において、第1のソース電極層及び第1のドレイン電極層には、第2のソース電極層及び第2のドレイン電極層よりも酸素と結合しやすい材料を用いるものとする。

【0019】

また、上記の半導体装置において、保護絶縁層に含まれる水素濃度は、 $5 \times 10^{-9} \text{ cm}^{-3}$  未満であることが好ましい。

20

【発明の効果】

【0020】

本発明の一態様によって、酸化物半導体を用いた半導体装置に良好な電気特性を付与することができる。

【0021】

また、本発明の一態様によって、酸化物半導体を用いた半導体装置の電気特性の変動を抑制し、信頼性の高い半導体装置を提供することができる。

【図面の簡単な説明】

【0022】

30

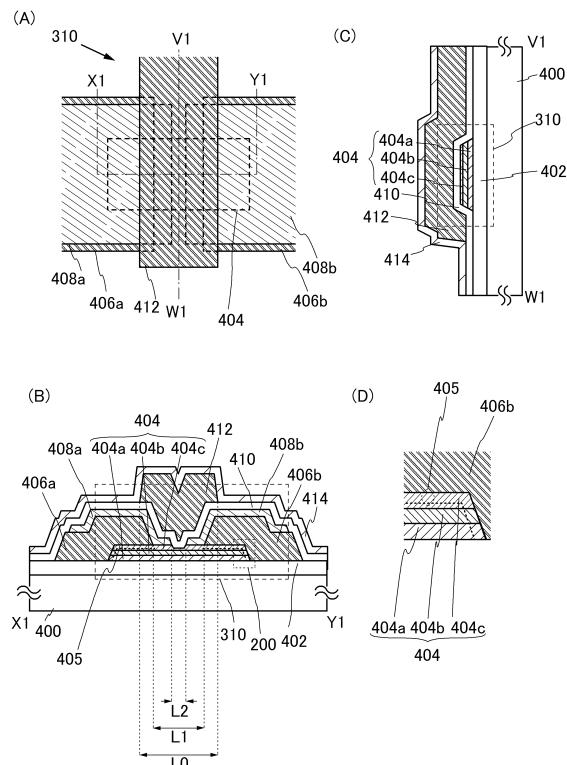

【図1】半導体装置の一態様を説明する平面図及び断面図。

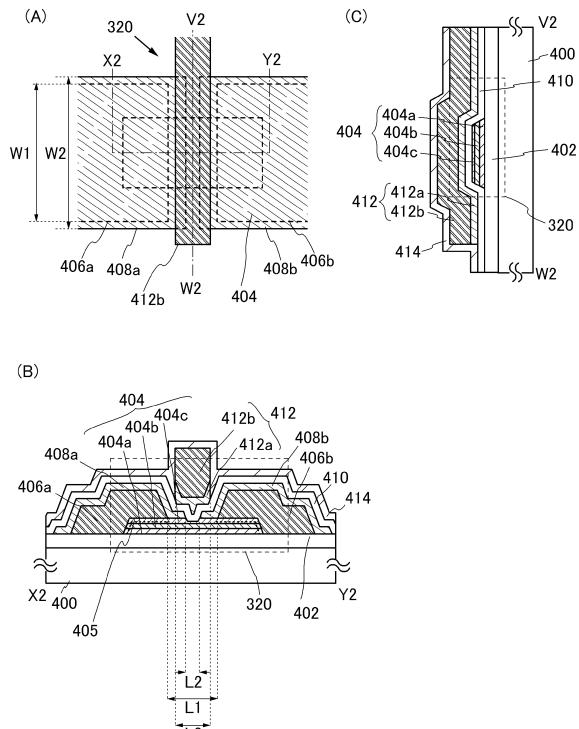

【図2】半導体装置の一態様を説明する平面図及び断面図。

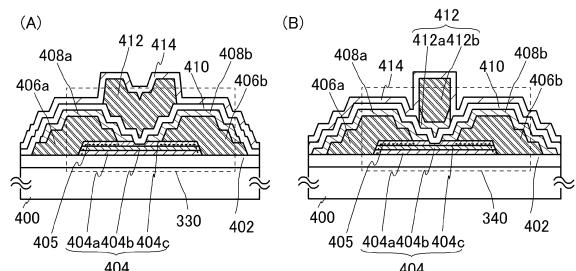

【図3】半導体装置の一態様を説明する断面図。

【図4】半導体装置の作製方法の一例を説明する断面図。

【図5】半導体装置の作製方法の一例を説明する断面図。

【図6】酸化物積層のバンド構造を説明する図。

【図7】酸化物積層のバンド構造を説明する図。

【図8】酸化物積層のバンド構造を説明する図。

【図9】半導体装置の一態様を説明する平面図及び断面図。

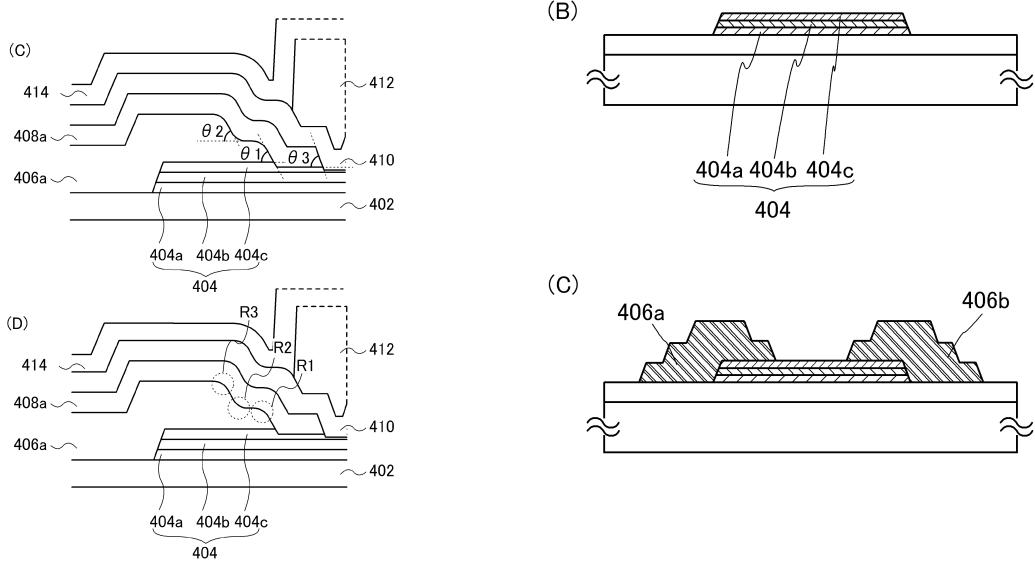

【図10】トランジスタに含まれる積層構造を示す概念図。

40

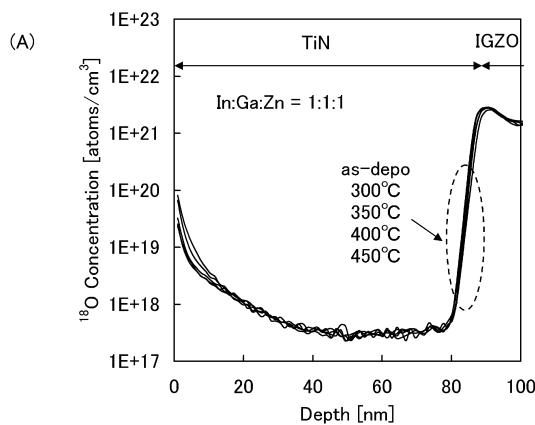

【図11】SIMS測定結果を示す図。

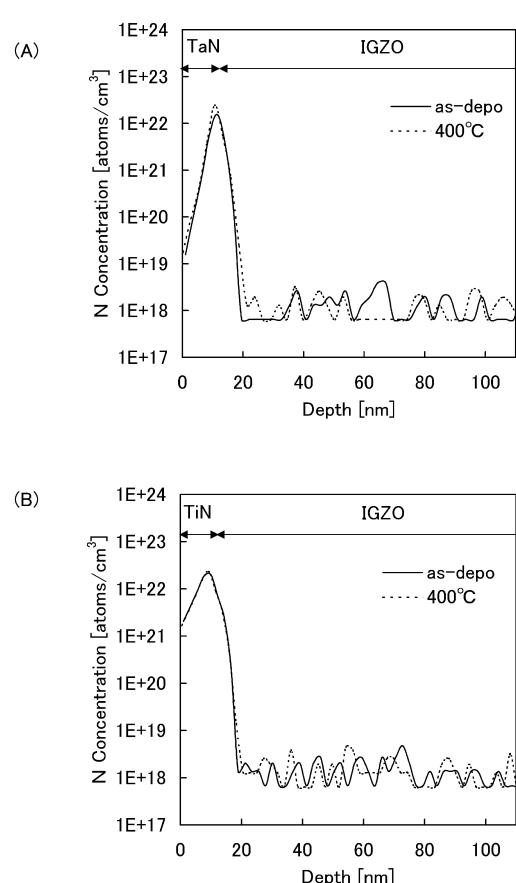

【図12】SIMS測定結果を示す図。

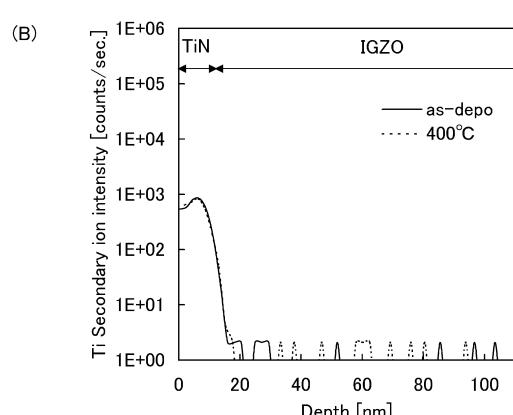

【図13】SIMS測定結果を示す図。

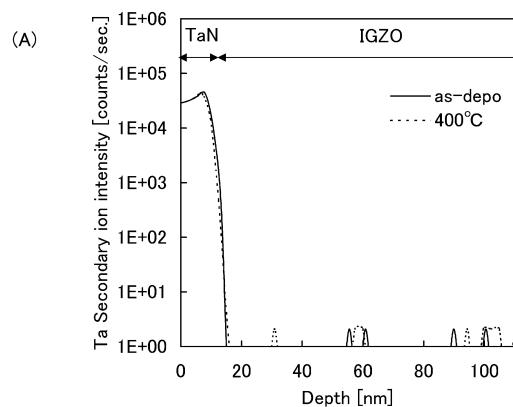

【図14】SIMS測定結果を示す図。

【図15】シート抵抗の測定結果を示す図。

【図16】シート抵抗の測定結果を示す図。

【図17】シート抵抗の測定結果を示す図。

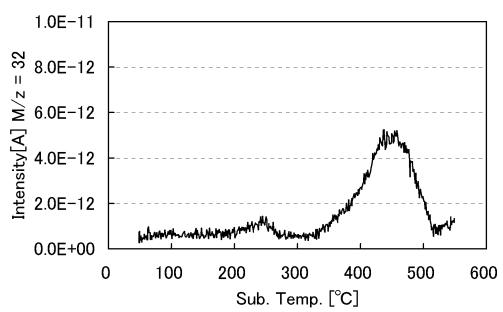

【図18】TDS分析結果を示す図。

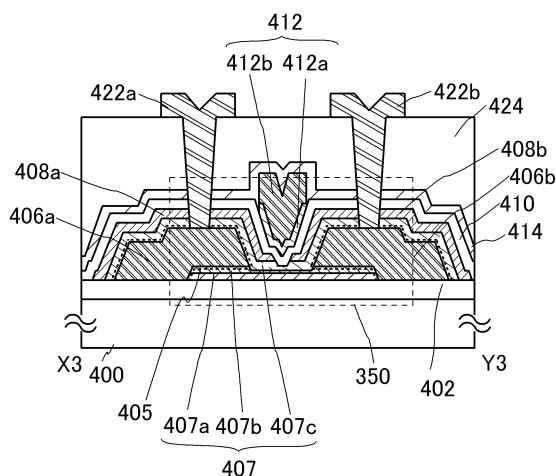

【図19】半導体装置の一態様を示す断面図。

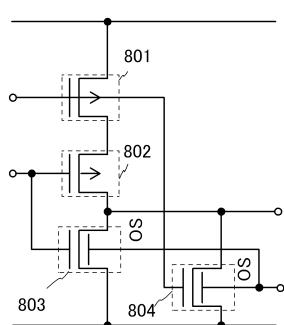

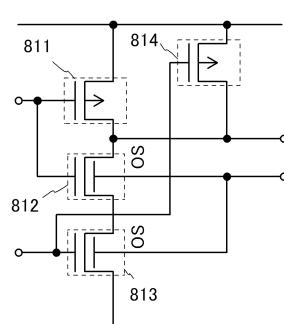

【図20】本発明の一態様の半導体装置の回路図。

50

【図21】本発明の一態様の半導体装置の回路図及び概念図。

【図22】本発明の一態様の半導体装置のブロック図。

【図23】本発明の一態様の半導体装置のブロック図。

【図24】本発明の一態様の半導体装置のブロック図。

【図25】本発明の一態様の半導体装置を適用することができる電子機器。

【発明を実施するための形態】

【0023】

以下では、開示する発明の実施の形態について図面を用いて詳細に説明する。但し、本明細書に開示する発明は以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。 10

【0024】

なお、以下に示す本発明の一態様の構成において、同一部分又は同様の機能を有する部分には、同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0025】

なお、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

【0026】

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。 20

【0027】

(実施の形態1)

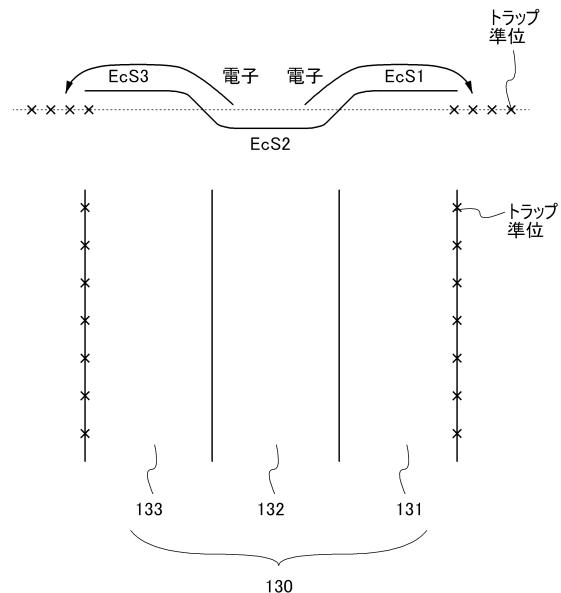

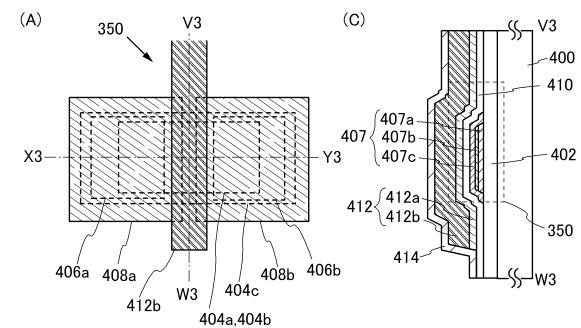

本実施の形態では、本発明の一態様の半導体装置に含有される積層構造について、図10を用いて説明する。

【0028】

<積層構造の構成>

図10に積層構造の一例の概念図を示す。 30

【0029】

半導体装置に含まれる積層構造は、下地絶縁層402と、ゲート絶縁層410との間に、酸化物積層404を有して構成される。また、酸化物積層404は、第1の酸化物層404a、酸化物半導体層404b、及び第2の酸化物層404cを含む。

【0030】

第1の酸化物層404a及び第2の酸化物層404cは、酸化物半導体層404bを構成する金属元素を一種以上含む酸化物層である。

【0031】

酸化物半導体層404bとしては、少なくともインジウム、亜鉛及びM(A1、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物で表記される層を含む。酸化物半導体層404bがインジウムを含むと、トランジスタのキャリア移動度が高くなるため、好ましい。 40

【0032】

酸化物半導体層404bの下層の第1の酸化物層404aとしてはIn-M-Zn酸化物(A1、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)で表記され、酸化物半導体層404bよりもMの原子数比が高い酸化物層を含む。具体的には、第1の酸化物層404aとして、酸化物半導体層404bよりも前述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物層を用いる。前述の元素はインジウムよりも酸素と強く結合するため、酸素欠損が酸化物層に生じる 50

ことを抑制する機能を有する。即ち、第1の酸化物層404aは酸化物半導体層404bよりも酸素欠損が生じにくい酸化物層である。

【0033】

また、酸化物半導体層404bの上層の第2の酸化物層404cとしては、第1の酸化物層404aと同様にIn-M-Zn酸化物(Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)で表記され、酸化物半導体層404bよりもMの原子数比が高い酸化物層を含む。具体的には、第2の酸化物層404cとして、酸化物半導体層404bよりも前述の元素を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比で含む酸化物層を用いる。

【0034】

つまり、第1の酸化物層404a、酸化物半導体層404b、第2の酸化物層404cが、少なくともインジウム、亜鉛およびM(Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)を含むIn-M-Zn酸化物であるとき、第1の酸化物層404aをIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub> [原子数比]、酸化物半導体層404bをIn:M:Zn=x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub> [原子数比]、第2の酸化物層404cをIn:M:Zn=x<sub>3</sub>:y<sub>3</sub>:z<sub>3</sub> [原子数比]とすると、y<sub>1</sub>/x<sub>1</sub>およびy<sub>3</sub>/x<sub>3</sub>がy<sub>2</sub>/x<sub>2</sub>よりも大きくなることが好ましい。y<sub>1</sub>/x<sub>1</sub>およびy<sub>3</sub>/x<sub>3</sub>はy<sub>2</sub>/x<sub>2</sub>よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、酸化物半導体層404bにおいて、y<sub>2</sub>がx<sub>2</sub>以上であるとトランジスタの電気特性を安定させることができる。ただし、y<sub>2</sub>がx<sub>2</sub>の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、y<sub>2</sub>はx<sub>2</sub>と同じか3倍未満であることが好ましい。

【0035】

なお、第1の酸化物層404aがIn-M-Zn酸化物であるとき、InとMの原子数比率は好ましくはInが50 atomic%未満、Mが50 atomic%以上、さらに好ましくはInが25 atomic%未満、Mが75 atomic%以上とする。また、酸化物半導体層404bがIn-M-Zn酸化物であるとき、InとMの原子数比率は好ましくはInが25 atomic%以上、Mが75 atomic%未満、さらに好ましくはInが34 atomic%以上、Mが66 atomic%未満とする。また、第2の酸化物層404cがIn-M-Zn酸化物であるとき、InとMの原子数比率は好ましくはInが50 atomic%未満、Mが50 atomic%以上、さらに好ましくはInが25 atomic%未満、Mが75 atomic%以上とする。

【0036】

なお、第1の酸化物層404aと、第2の酸化物層404cとは、異なる構成元素を含む層としてもよいし、同じ構成元素を同一の原子数比で、又は異なる原子数比で含む層としてもよい。

【0037】

第1の酸化物層404a、酸化物半導体層404b、及び第2の酸化物層404cには、例えば、インジウム、亜鉛及びガリウムを含んだ酸化物半導体を用いることができる。

【0038】

第1の酸化物層404aの厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。また、酸化物半導体層404bの厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

【0039】

また、第1の酸化物層404a及び第2の酸化物層404cは、酸化物半導体層404bを構成する金属元素を一種以上含み、伝導帯下端のエネルギーが酸化物半導体層404bよりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

【0040】

10

20

30

40

50

このような構造において、ゲート電極層412に電界を印加すると、酸化物積層404のうち、伝導帯下端のエネルギーが最も小さい酸化物半導体層404bにチャネルが形成される。すなわち、酸化物半導体層404bとゲート絶縁層410との間に第2の酸化物層404cが形成されていることによって、トランジスタのチャネルをゲート絶縁層410と接しない構造とすることができます。

【0041】

<酸化物積層のバンド構造>

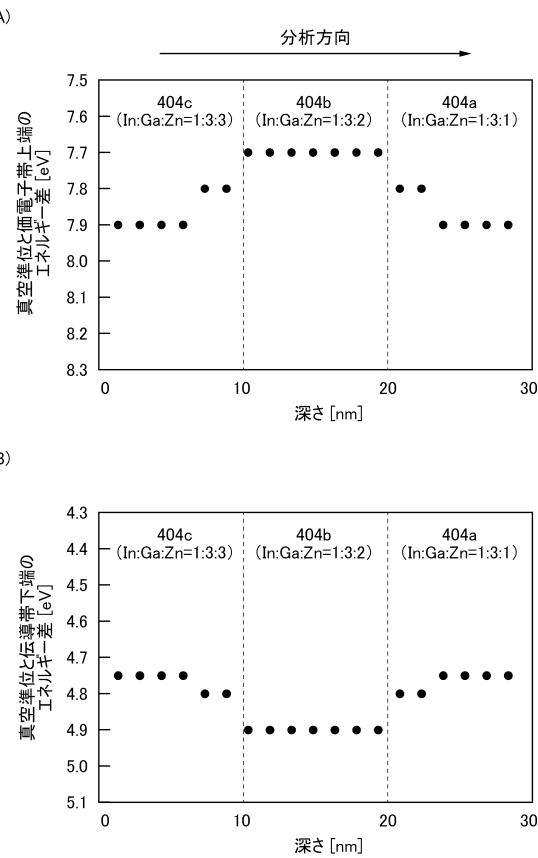

酸化物積層404のバンド構造を説明する。バンド構造の解析は、第1の酸化物層404a及び第2の酸化物層404cに相当する層としてエネルギーギャップが3.15eVであるIn-Ga-Zn酸化物、酸化物半導体層404bに相当する層としてエネルギーギャップが2.8eVであるIn-Ga-Zn酸化物を用い、酸化物積層404に相当する積層を作製して行っている。なお、便宜的に当該積層を酸化物積層、当該積層を構成するそれぞれの層を第1の酸化物層、酸化物半導体層、第2の酸化物層と称して説明する。

10

【0042】

第1の酸化物層、酸化物半導体層、第2の酸化物層の膜厚はそれぞれ10nmとし、エネルギーギャップは、分光エリプソメータ(HORIBA JOBIN YVON社UT-300)を用いて測定した。また、第1の酸化物層と酸化物半導体層との界面近傍のエネルギーギャップは3eV、第2の酸化物層と酸化物半導体層との界面近傍のエネルギーギャップは3eVとした。

20

【0043】

図6(A)は、酸化物積層を第2の酸化物層からエッティングしつつ、各層の真空準位と価電子帯上端のエネルギー差を測定し、その値をプロットした図である。真空準位と価電子帯上端のエネルギー差は、紫外線光電子分光分析(UPS: Ultraviolet Photoelectron Spectroscopy)装置(PHI社Versaprobe)を用いて測定した。

【0044】

図6(B)は、真空準位と価電子帯上端のエネルギー差と、各層のエネルギーギャップとの差分として算出される真空準位と伝導帯下端のエネルギー差(電子親和力)をプロットした図である。

30

【0045】

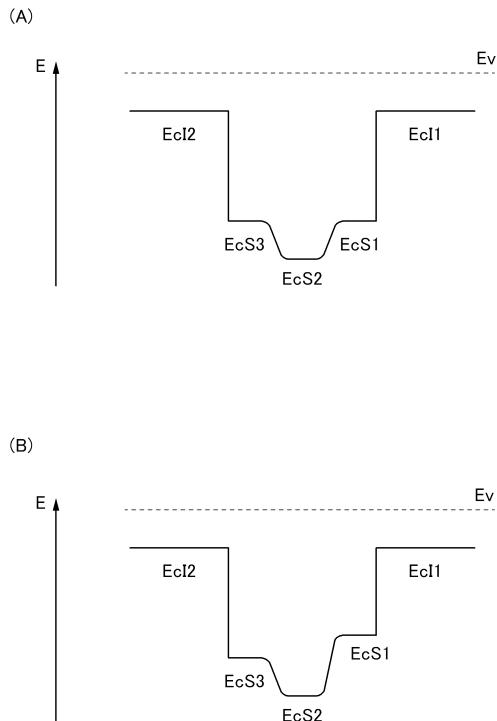

そして、図6(B)を模式的に示したバンド構造の一部が、図7(A)である。図7(A)では、第1の酸化物層及び第2の酸化物層と接して、酸化シリコン膜を設けた場合について説明する。ここで、Evは真空準位のエネルギー、EcI1及びEcI2は酸化シリコン膜の伝導帯下端のエネルギー、EcS1は第1の酸化物層の伝導帯下端のエネルギー、EcS2は酸化物半導体層の伝導帯下端のエネルギー、EcS3は第2の酸化物層の伝導帯下端のエネルギーを示す。

【0046】

図7(A)に示すように、第1の酸化物層、酸化物半導体層、第2の酸化物層において、伝導帯下端のエネルギーが連続的に変化する。これは、第1の酸化物層、酸化物半導体層、第2の酸化物層の組成が近似することにより、酸素が相互に拡散しやすい点からも理解される。

40

【0047】

なお、図7(A)では第1の酸化物層及び第2の酸化物層が同様のエネルギーギャップを有する酸化物層である場合について示したが、それぞれが異なるエネルギーギャップを有する酸化物層であっても構わない。例えば、EcS3よりもEcS1が高いエネルギーを有する場合、バンド構造の一部は、図7(B)のように示される。また、図7に示さないが、EcS1よりもEcS3が高いエネルギーを有しても構わない。

【0048】

図6(A)、(B)及び図7(A)、(B)より、酸化物積層における酸化物半導体層がウェル(井戸)となり、酸化物積層を用いたトランジスタにおいて、チャネルが酸化物半

50

導体層に形成されることがわかる。なお、酸化物積層は伝導帯下端のエネルギーが連続的に変化しているため、U字型井戸（U Shape Well）とも呼ぶことができる。また、このような構成で形成されたチャネルを埋め込みチャネルということもできる。

#### 【0049】

第1の酸化物層404a及び第2の酸化物層404cは、酸化物半導体層404bを構成する金属元素を一種以上含む酸化物層であるから、酸化物積層404は主成分を共通して積層された酸化物積層ともいえる。主成分を共通として積層された酸化物積層は、各層を単に積層するのではなく連続接合（ここでは、特に伝導帯下端のエネルギーが各層の間で連続的に変化するU字型の井戸構造）が形成されるように作製する。なぜなら、各層の界面に酸化物半導体にとってトラップ中心や再結合中心のような欠陥準位、あるいはキャリアの流れを阻害するバリアを形成するような不純物が混在していると、エネルギー・バンドの連続例が失われ、界面でキャリアがトラップあるいは再結合により消滅してしまうためである。

#### 【0050】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置（スパッタリング装置）を用いて各層を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $1 \times 10^{-4}$  Pa ~  $5 \times 10^{-7}$  Pa程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

#### 【0051】

高純度真性酸化物半導体を得るためにには、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下にまで高純度化したガスを用いることで酸化物半導体に水分等が取り込まれることを可能な限り防ぐことができる。

#### 【0052】

酸化物半導体層404bの上層又は下層に設けられる第1の酸化物層404a及び第2の酸化物層404cはバリア層として機能し、酸化物積層404に接する絶縁層（下地絶縁層402及びゲート絶縁層410）と、酸化物積層404との界面に形成されるトラップ準位の影響が、トランジスタのキャリアの主な経路（キャリアパス）となる酸化物半導体層404bへと及ぶことを抑制することができる。

#### 【0053】

例えば、酸化物半導体層に含まれる酸素欠損は、酸化物半導体のエネルギー・ギャップ内の深いエネルギー位置に存在する局在準位として顕在化する。このような局在準位にキャリアがトラップされることで、トランジスタの信頼性が低下するため、酸化物半導体層に含まれる酸素欠損を低減することが必要となる。酸化物積層404においては、酸化物半導体層404bと比較して酸素欠損の生じにくい酸化物層を酸化物半導体層404bの上下に接して設けることで、酸化物半導体層404bにおける酸素欠損を低減することができる。例えば、酸化物半導体層404bは、一定電流測定法（CPM: Constant Photocurrent Method）により測定された局在準位による吸収係数を $1 \times 10^{-3}$  / cm未満、好ましくは $1 \times 10^{-4}$  / cm未満とすることができる。

#### 【0054】

また、酸化物半導体層404bが、構成元素の異なる絶縁層（例えば、酸化シリコン膜を含む下地絶縁層）と接する場合、2層の界面に界面準位が形成され、該界面準位はチャネルを形成することがある。このような場合、しきい値電圧の異なる第2のトランジスタが出現し、トランジスタの見かけ上のしきい値電圧が変動することがある。しかしながら、酸化物積層404においては酸化物半導体層404bを構成する金属元素を一種以上含んで第1の酸化物層404aが構成されるため、第1の酸化物層404aと酸化物半導体層

10

20

30

40

50

404bの界面に界面準位を形成しにくくなる。よって第1の酸化物層404aを設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。

【0055】

また、ゲート絶縁層410と酸化物半導体層404bとの界面にチャネルが形成される場合、該界面で界面散乱が起こり、トランジスタの電界効果移動度が低くなる。しかしながら、酸化物積層404においては、酸化物半導体層404bを構成する金属元素を一種以上含んで第2の酸化物層404cが構成されるため、酸化物半導体層404bと第2の酸化物層404cとの界面ではキャリアの散乱が起こりにくく、トランジスタの電界効果移動度を高くすることができる。

10

【0056】

また、第1の酸化物層404a及び第2の酸化物層404cは、酸化物積層404に接する絶縁層（下地絶縁層402、ゲート絶縁層410）の構成元素が、酸化物半導体層404bへ混入して、不純物による準位が形成されることを抑制するためのバリア層としても機能する。

【0057】

例えば、酸化物積層404に接する下地絶縁層402、又はゲート絶縁層410として、シリコンを含む絶縁層を用いる場合、該絶縁層中のシリコン、又は絶縁層中に混入される炭素が、第1の酸化物層404a又は第2の酸化物層404cの中へ界面から数nm程度まで混入することがある。シリコン、炭素等の不純物が酸化物半導体層中に入ると不純物準位を形成し、不純物準位がドナーとなり電子を生成することでn型化することができる。

20

【0058】

しかしながら、第1の酸化物層404a及び第2の酸化物層404cの膜厚が、数nmよりも厚ければ、混入したシリコン、炭素等の不純物が酸化物半導体層404bにまで到達しないため、不純物準位の影響は低減される。

【0059】

ここで、酸化物半導体層に含まれるシリコンの濃度は $3 \times 10^{18} / \text{cm}^3$ 以下、好ましくは $3 \times 10^{17} / \text{cm}^3$ 以下とする。また、酸化物半導体層に含まれる炭素の濃度は $3 \times 10^{18} / \text{cm}^3$ 以下、好ましくは $3 \times 10^{17} / \text{cm}^3$ 以下とする。特に酸化物半導体層404bに第14族元素であるシリコン又は炭素が多く混入しないように、第1の酸化物層404a及び第2の酸化物層404cで、キャリアパスとなる酸化物半導体層404bを挟む、または囲む構成とすることが好ましい。すなわち、酸化物半導体層404bに含まれるシリコン及び炭素の濃度は、第1の酸化物層404a及び第2の酸化物層404cに含まれるシリコン及び炭素の濃度よりも低いことが好ましい。

30

【0060】

なお、酸化物半導体層中の不純物濃度は二次イオン分析法（S I M S : Secondary Ion Mass Spectrometry）で測定することができる。

【0061】

また、水素や水分が不純物として酸化物半導体層に含まれてしまうとドナーを作りn型化するため、酸化物積層404の上方に水素や水分が外部から侵入することを防止する保護絶縁層（窒化シリコン層など）を設けることは、井戸型構造を実現する上で有用である。

40

【0062】

なお、図8に示すように、第1の酸化物層及び第2の酸化物層と、酸化シリコン膜などの絶縁膜との界面近傍には、不純物や欠陥に起因したトラップ準位が形成され得る。第1の酸化物層及び第2の酸化物層があることにより、酸化物半導体層と当該トラップ準位とを遠ざけることができる。ただし、E<sub>cS1</sub>またはE<sub>cS3</sub>と、E<sub>cS2</sub>とのエネルギー差が小さい場合、酸化物半導体層の電子が第1の酸化物層または第2の酸化物層を超えてトラップ準位に達することができる。トラップ準位に電子が捕獲されることで、マイナスの固定電荷となり、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。

50

## 【0063】

したがって、ECS1及びECS3と、ECS1とのエネルギー差を、それぞれ0.1eV以上、好ましくは0.15eV以上とすることで、トランジスタのしきい値電圧の変動が低減され、安定した電気特性を得ることができる。

## 【0064】

## &lt;酸化物積層の成膜&gt;

多層構造を構成する各酸化物層は、少なくともインジウム(In)を含み、スパッタリング法好ましくはDCスパッタリング法で成膜することのできるスパッタリングターゲットを用いて成膜する。スパッタリングターゲットにインジウムを含ませることで導電性が高まるため、DCスパッタリング法で成膜することを容易なものとする。

10

## 【0065】

第1の酸化物層404a及び第2の酸化物層404cを構成する材料は、In-M-Zn酸化物(Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属)で表記される材料を用いる。Mとしては、Gaを用いることが好ましい。但し、含ませるGaの割合が多い、具体的には $In_{1-x}Zn_xO$ で表記できる材料で $x = 1.0$ を超えると成膜時に粉が発生する恐れがあり、スパッタリング法で成膜することが困難となりため不適である。

## 【0066】

なお、第1の酸化物層404a及び第2の酸化物層404cは、酸化物半導体層404bに用いる材料よりもインジウムの原子数比が少ない材料を用いる。酸化物層中のインジウムやガリウムなどの含有量は、飛行時間型二次イオン質量分析法(ToF-SIMS)や、X線電子分光法(XPS)で比較できる。

20

## 【0067】

第1の酸化物層404aは、下地絶縁層402の構成元素(例えば、シリコン)を不純物として含有することで、非晶質構造を有する場合がある。但し、チャネルを形成する酸化物半導体層404bは、結晶部を有することが好ましい。非晶質構造を有する第1の酸化物層404a上に結晶部を有する酸化物半導体層404bを積層する場合、当該酸化物積層を、結晶構造の異なるヘテロ構造と呼ぶことができる。

## 【0068】

また、第2の酸化物層404cは、非晶質構造としてもよいし、結晶部を有していてもよい。但し、結晶部を有する酸化物半導体層404b上に第2の酸化物層404cを成膜すると、第2の酸化物層404cも結晶構造を有する膜になりやすく、その場合には、酸化物半導体層404bと第2の酸化物層404cの境界を断面TEM(TEM: Transmission Electron Microscope)観察では判別することが困難となる場合もある。ただし、第2の酸化物層404cの結晶性は酸化物半導体層404bよりも低いため、結晶性の程度で境界を判別できると言える。

30

## 【0069】

なお、酸化物積層404において、少なくとも酸化物半導体層404bは、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)層であることが好ましい。本明細書等において、CAAC-OS層とは、c軸が酸化物半導体層の表面に概略垂直である結晶部を含む酸化物半導体膜をいう。

40

## 【0070】

CAAC-OS層は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS層は、非晶質相に結晶部及び非晶質部を有する結晶-非晶質混相構造の酸化物半導体層である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさが多い。また、透過型電子顕微鏡による観察像では、CAAC-OS層に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS層には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC-OS層は、粒界に起因する電子移動度の低下が抑制される。

## 【0071】

50

C A A C - O S 層に含まれる結晶部は、c 軸が C A A C - O S 層の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃っている。なお、異なる結晶部間で、それぞれ a 軸及び b 軸の向きが異なっていてもよい。本明細書等において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

【0072】

なお、C A A C - O S 層において、結晶部の分布が一様でなくてもよい。例えば、C A A C - O S 層の形成過程において、酸化物半導体層の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、C A A C - O S 層にも酸素を添加されることにより、当該元素や酸素の添加領域において結晶部が非晶質化することもある。

10

【0073】

C A A C - O S 層に含まれる結晶部のc軸は、C A A C - O S 層の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、C A A C - O S 層の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、C A A C - O S 層が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

【0074】

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

20

【0075】

なお、酸化物積層404において、第1の酸化物層404aを非晶質構造として、該非晶質構造の表面からC A A C - O S 膜を成膜して酸化物半導体層404bとすることが好ましい。

【0076】

< C A A C - O S 膜の成膜方法 >

C A A C - O S 膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa-b面から劈開し、a-b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、C A A C - O S 膜を成膜することができる。

30

【0077】

平板状のスパッタリング粒子は、例えば、a-b面に平行な面の円相当径が3nm以上10nm以下、厚さ（a-b面に垂直な方向の長さ）が0.7nm以上1nm未満である。なお、平板状のスパッタリング粒子は、a-b面に平行な面が正三角形または正六角形であってもよい。ここで、面の円相当径とは、面の面積と等しい正円の直径をいう。

【0078】

また、C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

40

【0079】

成膜時の基板温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。このとき、スパッタリング粒子が正に帯電することで、スパッタリング粒子同士が反発しながら基板に付着するため、スパッタリング粒子が偏って不均一に重なることがなく、厚さの均一なC A A C - O S 膜を成膜することができる。

【0080】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制でき

50

る。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素及び窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が -80 以下、好ましくは -100 以下である成膜ガスを用いる。

【0081】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積%以上、好ましくは 100 体積%とする。

【0082】

C A A C - O S 膜を成膜した後、加熱処理を行ってもよい。加熱処理の温度は、100 以上 740 以下、好ましくは 200 以上 500 以下とする。また、加熱処理の時間は 1 分以上 24 時間以下、好ましくは 6 分以上 4 時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えよ。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、C A A C - O S 膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により C A A C - O S 膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。また、加熱処理を行うことで、C A A C - O S 膜の結晶性をさらに高めることができる。なお、加熱処理は 1000 Pa 以下、100 Pa 以下、10 Pa 以下または 1 Pa 以下の減圧下で行ってもよい。減圧下では、C A A C - O S 膜の不純物濃度をさらに短時間で低減することができる。

【0083】

スパッタリング用ターゲットの一例として、In - Ga - Zn - O 化合物ターゲットについて以下に示す。

【0084】

In O<sub>x</sub> 粉末、Ga O<sub>y</sub> 粉末及びZn O<sub>z</sub> 粉末を所定の m o 1 数比で混合し、加圧処理後、1000 以上 1500 以下の温度で加熱処理をすることで多結晶である In - Ga - Zn - O 化合物ターゲットとする。なお、X、Y 及びZ は任意の正数である。ここで、所定の m o 1 数比は、例えば、In O<sub>x</sub> 粉末、Ga O<sub>y</sub> 粉末及びZn O<sub>z</sub> 粉末が、2 : 2 : 1、8 : 4 : 3、3 : 1 : 1、1 : 1 : 1、4 : 2 : 3 または 3 : 1 : 2 である。なお、粉末の種類、及びその混合する m o 1 数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

【0085】

または、C A A C - O S 膜は、以下の方法により形成する。

【0086】

まず、第 1 の酸化物半導体膜を 1 nm 以上 10 nm 未満の厚さで成膜する。第 1 の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を 100 以上 500 以下、好ましくは 150 以上 450 以下とし、成膜ガス中の酸素割合を 30 体積%以上、好ましくは 100 体積%として成膜する。

【0087】

次に、加熱処理を行い、第 1 の酸化物半導体膜を結晶性の高い第 1 の C A A C - O S 膜とする。加熱処理の温度は、350 以上 740 以下、好ましくは 450 以上 650 以下とする。また、加熱処理の時間は 1 分以上 24 時間以下、好ましくは 6 分以上 4 時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えよ。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第 1 の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第 1 の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は 1000 Pa 以下、100 Pa 以下、10 Pa 以下または 1 Pa 以下の減圧下で行ってもよい。減圧下では、第 1 の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。

【0088】

10

20

30

40

50

第1の酸化物半導体膜は、厚さが1nm以上10nm未満であることにより、厚さが10nm以上である場合と比べ、加熱処理によって容易に結晶化させることができる。

【0089】

次に、第1の酸化物半導体膜と同じ組成である第2の酸化物半導体膜を10nm以上50nm以下の厚さで成膜する。第2の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を100以上500以下、好ましくは150以上450以下とし、成膜ガス中の酸素割合を30体積%以上、好ましくは100体積%として成膜する。

【0090】

次に、加熱処理を行い、第2の酸化物半導体膜を第1のCAC-OS膜から固相成長させることで、結晶性の高い第2のCAC-OS膜とする。加熱処理の温度は、350以上740以下、好ましくは450以上650以下とする。また、加熱処理の時間は1分以上24時間以下、好ましくは6分以上4時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えばよい。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第2の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第2の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は1000Pa以下、100Pa以下、10Pa以下または1Pa以下の減圧下で行ってもよい。減圧下では、第2の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。

【0091】

以上のようにして、合計の厚さが10nm以上であるCAC-OS膜を形成することができる。当該CAC-OS膜を、酸化物積層における酸化物半導体層として好適に用いることができる。

【0092】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0093】

(実施の形態2)

本実施の形態では、実施の形態1で示した積層構造を含む半導体装置、及び当該半導体装置の作製方法の一態様を図1乃至図5を用いて説明する。本実施の形態では、半導体装置の一例として、酸化物半導体層を有するトップゲート構造のトランジスタを示す。

【0094】

<半導体装置の構成例1>

図1にトランジスタ310の構成例を示す。図1(A)はトランジスタ310の平面図であり、図1(B)は図1(A)のX1-Y1における断面図であり、図1(C)は、図1(A)のV1-W1における断面図である。また、図1(D)は、図1(B)の領域200の部分拡大図である。なお、図1(A)では、煩雑になることを避けるため、トランジスタ310の構成要素の一部(例えば、保護絶縁層414等)を省略して図示している。

【0095】

図1に示すトランジスタ310は、基板400上に形成された下地絶縁層402、下地絶縁層402上に形成された島状の酸化物積層404、島状の酸化物積層404の上面の一部及びチャネル形成方向の側面と接する第1のソース電極層406a及び第1のドレイン電極層406bと、第1のソース電極層406a及び第1のドレイン電極層406b上にそれぞれ設けられ、酸化物積層404の上面の一部に接する、窒化金属膜でなる第2のソース電極層408a及び第2のドレイン電極層408bと、第2のソース電極層408a及び第2のドレイン電極層408b上に設けられ、第2のソース電極層408a及び第2のドレイン電極層408bとの間で酸化物積層404の上面と接するゲート絶縁層410と、ゲート絶縁層410を介して酸化物積層404と重畳するゲート電極層412と、ゲ

10

20

30

40

50

ート絶縁層 410 及びゲート電極層 412 上に接して設けられた保護絶縁層 414 を有する。なお、保護絶縁層 414 の上部に他の絶縁層を形成してもよい。

#### 【0096】

##### 基板

基板 400 は、単なる支持材料に限らず、他のトランジスタなどのデバイスが形成された基板であってもよい。この場合、トランジスタ 310 のゲート電極層 412、第 1 のソース電極層 406a、第 1 のドレイン電極層 406b、第 2 のソース電極層 408a または第 2 のドレイン電極層 408b の少なくとも一つは、上記の他のデバイスと電気的に接続されていてもよい。

#### 【0097】

10

##### 下地絶縁層

下地絶縁層 402 は、基板 400 からの不純物の拡散を防止する役割を有するほか、酸化物積層 404 に酸素を供給する役割を担うため、酸素を含む絶縁層を用いるものとする。また、上述のように基板 400 が他のデバイスが形成された基板である場合、下地絶縁層 402 は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるように CMP (Chemical Mechanical Polishing) 法等で平坦化処理を行うことが好ましい。

#### 【0098】

本実施の形態のトランジスタ 310 において、酸素を含有する下地絶縁層 402 が、酸化物半導体層を含む積層構造（酸化物積層 404）の下方に設けられている。このような構成とすることで、下地絶縁層 402 に含まれる酸素を、チャネル形成領域へ供給することが可能となる。下地絶縁層 402 は、化学量論的組成よりも過剰に酸素を含有する領域を有することが好ましい。下地絶縁層 402 が過剰に酸素を含有することで、チャネル形成領域への酸素の供給がより促進されうる。

20

#### 【0099】

なお、本明細書等において、過剰な酸素とは、加熱処理により酸化物半導体層中、又は酸化シリコン中、又は酸化窒化シリコン中を移動可能な酸素、又は、本来の化学量論比にある酸素より過剰に存在する酸素、又は、酸素の不足による  $V_o$ （酸素ベーカンシー（空孔））を満たす又は充填する機能を有する酸素を示す。

#### 【0100】

30

##### ゲート絶縁層

酸化物積層 404 の上方に接して設けられたゲート絶縁層 410 からも酸化物積層 404 へ酸素が供給される。ゲート絶縁層 410 は、島状の酸化物積層 404 の外周部において下地絶縁層 402 と接する領域を有している。従って、ゲート絶縁層 410 と下地絶縁層 402 とが接する領域から、ゲート絶縁層 410 を経路（パス）として、下地絶縁層 402 に含まれる酸素を酸化物積層 404 へと供給することができる。

#### 【0101】

ゲート絶縁層 410 は、下地絶縁層 402 に含まれる酸素を、酸化物積層 404 へ供給する経路となる層である。ゲート絶縁層 410 には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム及び酸化タンタルを一種以上含む絶縁層を用いることができる。また、ゲート絶縁層 410 は上記材料の積層であってもよい。

40

#### 【0102】

酸化物積層 404 の下側及び上側から、酸素が供給されるため、該酸化物積層 404 に含まれうる酸素欠損を低減することができる。

#### 【0103】

##### 保護絶縁層

トランジスタ 310 において、ゲート絶縁層 410 及びゲート電極層 412 上に設けられる保護絶縁層 414 として、ゲート絶縁層 410 よりも酸素に対する透過性が低い（酸素

50

に対するバリア性を有する)絶縁層を設ける。ゲート絶縁層410及びゲート電極層412上に接して酸素に対するバリア性を有する保護絶縁層414を設けることで、ゲート絶縁層410からの酸素の脱離を抑制することができる。ゲート絶縁層410はチャネル形成領域へ酸素を供給する経路となる絶縁層であるため、該ゲート絶縁層410からの酸素の脱離を抑制することで、ゲート絶縁層410に含まれる酸素欠損に起因する酸化物積層404からの酸素の引き抜きを抑制することができ、結果としてチャネル形成領域の酸素欠損を抑制することができる。このような保護絶縁層として、例えば、窒化シリコン膜又は窒化酸化シリコン膜を設けることができる。

#### 【0104】

また、酸化物半導体は、酸素欠損に加えて水素がキャリアの供給源となる。酸化物半導体中に水素が含まれると、伝導帯から浅い準位にドナーが生成され低抵抗化(  $n$  型化)してしまう。よって、保護絶縁層414に含まれる水素濃度を低減することが好ましい。具体的には、保護絶縁層414に含まれる水素濃度は、 $5 \times 10^{19} \text{ cm}^{-3}$ 未満とすることが好ましく、 $5 \times 10^{18} \text{ cm}^{-3}$ 未満とすることがより好ましい。

#### 【0105】

##### 酸化物積層

酸化物積層404は、少なくともチャネルを形成する酸化物半導体層404bと、酸化物半導体層404bと下地絶縁層402との間に設けられた第1の酸化物層404aと、酸化物半導体層404bとゲート絶縁層410との間に設けられた第2の酸化物層404cとを含んで構成される。

#### 【0106】

第1の酸化物層404a及び第2の酸化物層404cは、酸化物半導体層404bを構成する金属元素を一種以上含む酸化物層である。酸化物積層404の詳細は、実施の形態1を参照することができる。

#### 【0107】

酸化物積層404において、チャネルを形成する酸化物半導体層404bの上側及び下側に接して、酸化物半導体層404bよりも酸素欠損の生じにくい酸化物層を設けることで、トランジスタのチャネルにおける酸素欠損の形成を抑制することができる。

#### 【0108】

なお、酸化物半導体層を真性または実質的に真性とするためには、SIMSにおける分析において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、好ましくは $3 \times 10^{18} \text{ atoms/cm}^3$ 未満、好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とする。また、水素濃度は、 $2 \times 10^{20} \text{ atoms/cm}^3$ 以下、好ましくは $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下とする。また、窒素濃度は、 $5 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$ 以下とする。

#### 【0109】

また、酸化物半導体層が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物半導体層の結晶性を低下させことがある。酸化物半導体層の結晶性を低下させないためには、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とすればよい。また、炭素濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とすればよい。

#### 【0110】

また、上述のように高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さい。例えば、高純度化された酸化物半導体膜を用いたトランジスタがオフ状態のときのドレイン電流は、室温(25程度)にて $1 \times 10^{-18} \text{ A}$ 以

10

20

30

40

50

下、好ましくは  $1 \times 10^{-2.1}$  A 以下、さらに好ましくは  $1 \times 10^{-2.4}$  A 以下、または 85 にて  $1 \times 10^{-1.5}$  A 以下、好ましくは  $1 \times 10^{-1.8}$  A 以下、さらに好ましくは  $1 \times 10^{-2.1}$  A 以下とすることができます。なお、トランジスタがオフ状態とは、n チャネル型のトランジスタの場合、ゲート電圧がしきい値電圧よりも十分小さい状態をいう。具体的には、ゲート電圧がしきい値電圧よりも 1 V 以上、2 V 以上または 3 V 以上小さければ、トランジスタはオフ状態となる。

【0111】

ソース電極層及びドレイン電極層

トランジスタ 310 においてソース電極層及びドレイン電極層は、酸化物積層 404 のチャネル長方向の側面と接する第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b と、第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b 上に設けられ、第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b よりもチャネル長方向に延在した領域を有する第 2 のソース電極層 408a 及び第 2 のドレイン電極層 408b を有する。

【0112】

第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b には、酸素と結合し易い導電材料を用いることができる。例えば、Al、Cr、Cu、Ta、Ti、Mo、Wなどを用いることができる。後のプロセス温度が比較的高くできることなどから、融点の高い W を用いることが特に好ましい。なお、酸素と結合し易い導電材料には、酸素が拡散し易い材料も含まれる。

【0113】

このような導電材料と酸化物積層 404 を接触させると、酸化物積層 404 中の酸素が、酸素と結合し易い導電材料側に取り込まれる。トランジスタの作製工程には、いくつかの加熱工程があることから、上記酸素の移動により、酸化物積層 404 において第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b と接触した界面近傍の領域に酸素欠損が発生し、n 型化した領域 405 が形成される（図 1 (D) 参照）。したがって、n 型化した領域 405 はトランジスタ 310 のソースまたはドレインとして作用させることができる。

【0114】

なお、領域 405 には、第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b の構成元素が混入することがある。また、領域 405 に接する第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b では、一部酸素の濃度が高い領域が形成される。また、領域 405 に接する第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b では、酸化物積層 404 の構成元素が混入することがある。すなわち、酸化物積層 404 の第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b に接触する界面近傍には、当該接触した 2 層の混合領域又は混合層と呼ぶことのできる箇所が形成されることもある。なお、図 1 では、n 型化した領域 405 の界面を模式的に点線で図示している。これは以降の図面においても同様である。

【0115】

また、チャネル長が極短いトランジスタを形成する場合、上記酸素欠損の発生によって n 型化した領域がトランジスタのチャネル長方向に延在してしまうことがある。この場合、トランジスタの電気特性には、しきい値電圧のシフトやゲート電圧でオンオフの制御ができない状態（導通状態）が現れる。そのため、チャネル長が極短いトランジスタを形成する場合は、ソース電極及びドレイン電極に酸素と結合し易い導電材料を用いることは好ましくない。

【0116】

そこで、第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b よりもチャネル長方向に延在した領域を有する第 2 のソース電極層 408a 及び第 2 のドレイン電極層 408b を第 1 のソース電極層 406a 及び第 1 のドレイン電極層 406b に積層とし、チャネル長を定める第 2 のソース電極層 408a 及び第 2 のドレイン電極層 408b には、

10

20

30

40

50

酸素と結合しにくい導電材料を用いる。当該導電材料としては、例えば、窒化タンタル、窒化チタンなどを用いることが好ましい。なお、酸素と結合しにくい導電材料には、酸素が拡散しにくい材料も含まれる。

【0117】

なお、図1の構造のトランジスタにおいて、チャネル長とは、第2のソース電極層408aと第2のドレイン電極層408bの間隔L2のことをいう。

【0118】

また、図1の構造のトランジスタにおいて、チャネルとは、第2のソース電極層408aと第2のドレイン電極層408bの間ににおける酸化物半導体層404bのことをいう。

【0119】

また、図1の構造のトランジスタにおいて、チャネル形成領域とは、第2のソース電極層408aと第2のドレイン電極層408bの間ににおける第1の酸化物層404a、酸化物半導体層404b、第2の酸化物層404cのことをいう。

【0120】

上記酸素と結合しにくい導電材料を第2のソース電極層408a及び第2のドレイン電極層408bに用いることによって、酸化物積層404に形成されるチャネル形成領域に酸素欠損が形成されることを抑制することができ、チャネルのn型化を抑えることができる。したがって、チャネル長が極短いトランジスタであっても良好な電気特性を得ることができる。

【0121】

なお、上記酸素と結合しにくい導電材料のみでソース電極層及びドレイン電極層を形成すると、酸化物積層404とのコンタクト抵抗が高くなりすぎることから、図1に示すように、第1のソース電極層406a及び第1のドレイン電極層406bを酸化物積層404上に形成し、第1のソース電極層406a及び第1のドレイン電極層406b上に接するように第2のソース電極層408a及び第2のドレイン電極層408bを形成することが好ましい。

【0122】

このとき、第1のソース電極層406a及び第1のドレイン電極層406bと酸化物積層404との接触面積を大として酸素欠損生成によってn型化した領域405によりコンタクト抵抗を下げ、第2のソース電極層408a及び第2のドレイン電極層408bと酸化物積層404との接触面積は小さくすることが好ましい。第2のソース電極層408a及び第2のドレイン電極層408bと酸化物積層404との接触面積が大きいとトランジスタの電気特性を低下させる場合があるためである。

【0123】

第2のソース電極層408aと第2のドレイン電極層408bとの間隔L2は、L1より小さい値とすることができます、例えば、30nm以下としても良好なトランジスタの電気特性を得ることができる。

【0124】

ゲート電極層

ゲート電極層412は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Ta及びWなどの導電膜を用いることができる。

【0125】

上記本発明の一態様におけるトランジスタの構成は、酸化物半導体層中の酸素欠損の増加を抑制することができる。したがって、良好な電気特性を示すとともに長期信頼性の高い半導体装置を提供することができる。

【0126】

<半導体装置の構成例2>

図2にトランジスタ320の構成例を示す。図2(A)はトランジスタ320の平面図であり、図2(B)は図2(A)のX2-Y2における断面図であり、図2(C)は、図2(A)のV2-W2における断面図である。なお、図2(A)では、煩雑になることを避

10

20

30

40

50

けるため、トランジスタ320の構成要素の一部（例えば、保護絶縁層414等）を省略して図示している。

【0127】

図2に示すトランジスタ320は、基板400上に形成された下地絶縁層402、下地絶縁層上に形成された島状の酸化物積層404、島状の酸化物積層の上面の一部及びチャネル形成方向の側面と接する第1のソース電極層406a及び第1のドレイン電極層406bと、第1のソース電極層406a及び第1のドレイン電極層406bを覆うように設けられ、酸化物積層404の上面の一部に接する、窒化金属膜でなる第2のソース電極層408a及び第2のドレイン電極層408bと、第2のソース電極層408a及び第2のドレイン電極層408b上に設けられ、第2のソース電極層408a及び第2のドレイン電極層408bとの間で酸化物積層404の上面と接するゲート絶縁層410と、ゲート絶縁層410及びゲート電極層412を介して酸化物積層404と重疊するゲート電極層412と、ゲート絶縁層410及びゲート電極層412上に接して設けられた保護絶縁層414を有する。なお、保護絶縁層414の上部に他の絶縁層を形成してもよい。

【0128】

トランジスタ310とトランジスタ320の相違点の一は、ゲート電極層412のチャネル長方向の長さL0である。トランジスタ320においては、ゲート-ドレイン間及びゲート-ソース間の寄生容量を小さくするため、第1のソース電極層406a及び第1のドレイン電極層406bとゲート電極層412が重疊しない構造とする。ゲート電極層412の長さをL0とするとき、L1 L0 L2（L0はL2以上L1以下）とすることでき、ゲート-ドレイン間及びゲート-ソース間の寄生容量を極力小さくすることができ、半導体装置の周波数特性を向上することができる。なお、良好なトランジスタの電気特性を得るには、（L1 - L2）/2をL2の20%以下未満とすることが好ましい。

【0129】

トランジスタ320の上面積は1~25μm<sup>2</sup>以下とすることが好ましい。例えば、図2のトランジスタ320において酸化物積層404のチャネル長方向の長さを300nmとする時、L0を40nmとして、L2を30nmとすることが好ましい。このとき、島状の酸化物積層404の上面積を、1μm<sup>2</sup>以下とすることができます。

【0130】

ただし、高い周波数特性を必要としない半導体装置においては、図1（B）に示すように、L0 L1 L2（L1はL2以上L0以下）としてもよい。このような構造では、ゲート電極形成時の工程の難易度を低減させることができる。

【0131】

また、トランジスタ310とトランジスタ320の相違点の他の一は、ゲート電極層412の構成である。トランジスタ320においては、ゲート電極層412は、ゲート絶縁層410と接する第1のゲート電極層412aと第2のゲート電極層412bの積層構造である。ここで、第1のゲート電極層412aとして、第2のソース電極層408a及び第2のドレイン電極層408bと同様の材料を用いることにより、ゲート電極層412によるゲート絶縁層410からの酸素の引き抜きを防止することができる。

【0132】

また、トランジスタ310とトランジスタ320の相違点の他の一は、第2のソース電極層408a及び第2のドレイン電極層408bの構成である。トランジスタ320においては、第1のソース電極層406a（又は第1のドレイン電極層406b）のチャネル幅方向の幅をW1、第2のソース電極層408a（又は第2のドレイン電極層408b）のチャネル幅方向の幅をW2とするとき、W1 > W2とすることで、第2のソース電極層408a（又は第2のドレイン電極層408b）が、第1のソース電極層406a（又は第1のドレイン電極層406b）を覆う構成を有している。

【0133】

このような構成とすることで、ゲート絶縁層410が、酸素と結合しやすい導電材料で形成される第1のソース電極層406a及び第1のドレイン電極層406bと接しない構成

10

20

30

40

50

とすることができる。よって、ゲート絶縁層410からの酸素の引き抜きを防止することができる。

【0134】

ゲート絶縁層410は、酸化物積層404への酸素の供給経路となる層であるため、第1のソース電極層406a及び第1のドレイン電極層406bによるゲート絶縁層410からの酸素の引き抜きを防止することで、酸化物積層404へ効果的に酸素を供給することができる。従って、酸化物積層404において酸素欠損の発生を抑制することができるため、トランジスタ320の信頼性を向上させることができる。

【0135】

なお、トランジスタ320のそのほかの構成は、上述のトランジスタ310と同様であり、トランジスタ310の説明を参照することができる。 10

【0136】

<半導体装置の構成例3>

図3(A)及び図3(B)に、上述のトランジスタ310又はトランジスタ320の変形例を示す。図3(A)に示すトランジスタ330は、トランジスタ310の第1のソース電極層406a及び第1のドレイン電極層406bの端部が異なる構成であり、図3(B)に示すトランジスタ340は、トランジスタ320の第1のソース電極層406a及び第1のドレイン電極層406bの端部が異なる構成である。なお、第1のソース電極層406a及び第1のドレイン電極層406bの端部以外の構成は上述のトランジスタと同様であり、先の説明を参照することができる。 20

【0137】

トランジスタ330及びトランジスタ340において、第1のソース電極層406aの拡大図を図3(C)及び図3(D)に示す。トランジスタ330及びトランジスタ340において、第1のソース電極層406a及び第1のドレイン電極層406bの端部は、階段状に複数の段を設けた形状であり、下段の端面は、酸化物積層404の上面を基準として1の角度で形成されており、上段の端面は、下段上面を基準として2の角度で形成されていることが好ましい。また、下段上面と下段端面の間にはR1の曲率半径を有する曲面を有し、上段上面と上段端面の間にはR3の曲率半径を有する曲面を有し、下段上面と上段端面の間にはR2の曲率半径を有する曲面で形成されていることが好ましい。 30

【0138】

なお、図3においては、第1のソース電極層406a及び第1のドレイン電極層406bの端部に二つの段を設けた形状を例示しているが、段数は三つ以上であってもよい。第1のソース電極層406a及び第1のドレイン電極層406bの膜厚が厚いほど、当該段数を増やすことが好ましい。なお、第1のソース電極層406a及び第1のドレイン電極層406bの端部は対象的でなくともよい。また、第1のソース電極層406a及び第1のドレイン電極層406bの膜厚を薄くできる場合は、当該段数は一つ、すなわち1、R1のみを有する形状であってもよい。

【0139】

ここで、1及び2は、20°以上80°以下、好ましくは25°以上70°以下、さらに好ましくは30°以上60°以下とする。また、R1、R2、R3は、第1のソース電極層406aまたは第1のドレイン電極層406bの段が形成されていない領域の膜厚を基準として、当該膜厚の10%以上100%以下、好ましくは20%以上75%以下、さらに好ましくは30%以上60%以下とする。また、R2は、R1、R3のいずれか、または両方より大きいことが好ましい。 40

【0140】

第1のソース電極層406a及び第1のドレイン電極層406bを上記のような複数の段を設けた形状とすることで、それらの上方に形成される膜、具体的には、第2のソース電極層408a、第2のドレイン電極層408b、ゲート絶縁層410などの被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができる。

【0141】

10

20

30

40

50

また、第2のソース電極層408aまたは第2のドレイン電極層408bの端面は、酸化物積層404の上面を基準として3の角度で形成されている。3は、30°以上80°以下、好ましくは35°以上75°以下とする。このような角度にすることで、ゲート絶縁層410などの被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができる。

【0142】

<半導体装置の構成例4>

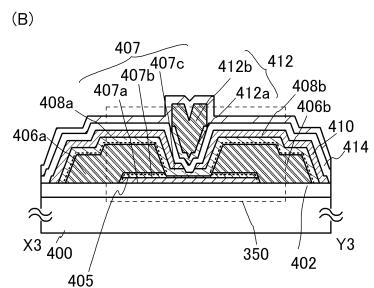

図9にトランジスタ350の構成例を示す。トランジスタ350は、図2のトランジスタ320の変形例である。図9(A)はトランジスタ350の平面図であり、図9(B)は図9(A)のX3-Y3における断面図であり、図9(C)は、図9(A)のV3-W3における断面図である。なお、図9(A)では、煩雑になることを避けるため、トランジスタ350の構成要素の一部(例えば、保護絶縁層414等)を省略して図示している。

10

【0143】

トランジスタ320とトランジスタ350の相違点は、酸化物積層404と、ソース電極層及びドレイン電極層の積層順である。すなわち、トランジスタ350では、島状の第1の酸化物層407aのチャネル長方向の側面と、島状の酸化物半導体層407bのチャネル長方向の側面及び上面の一部を覆うように、第1のソース電極層406a及び第1のドレイン電極層406bが設けられており、第1のソース電極層406a及び第1のドレイン電極層406b上に接して島状の酸化物半導体層407bが設けられている。そして、酸化物半導体層407b上に、第2のソース電極層408a及び第2のドレイン電極層408bが設けられている。

20

【0144】

第1の酸化物層407a、酸化物半導体層407b及び第2の酸化物層404cにおいて、第1のソース電極層406a又は第1のドレイン電極層406bと接する領域には、当該電極によって酸素が引き抜かることで、n型化した領域405が形成される。トランジスタ350において、下地絶縁層402とゲート絶縁層410との間には、第1の酸化物層407a、酸化物半導体層407b及び第2の酸化物層407cを含む酸化物積層407が形成される。

【0145】

酸化物積層407に含まれる酸化物半導体層404bの、第1のソース電極層406a及び第1のドレイン電極層406bと重畳しない領域(n型化されない領域)は、第1のソース電極層406a及び第1のドレイン電極層406bの加工時に一部がエッチングされて、膜厚の小さい領域となる場合がある。また、第2の酸化物層404cの、第2のソース電極層408a及び第2のドレイン電極層408bと重畳しない領域は、第2のソース電極層408a及び第2のドレイン電極層408bの加工時に一部がエッチングされて、膜厚の小さい領域となる場合がある。

30

【0146】

図9(C)に示すように、トランジスタ350ではW長方向の断面において島状の第1の酸化物層407a及び酸化物半導体層407bの側面を第2の酸化物層407cによって覆う構成とすることができます。当該構成とすることで、酸化物積層407のW長方向端部において生じうる寄生チャネルの影響を低減することができる。よって、トランジスタの信頼性を向上させることができる。

40

【0147】

なお、図19に示すように、第1のソース電極層406aと第2のソース電極層408aとは、保護絶縁層414上に設けられた層間絶縁層424に、第1のソース電極層406aに達するコンタクトホールを形成し、該コンタクトホールに電極層422aを形成することで電気的に接続される。同様に、第1のドレイン電極層406bと第2のドレイン電極層408bとは、層間絶縁層424に第1のドレイン電極層406bに達するコンタクトホールを形成し、該コンタクトホールに電極層422bを形成することで、電気的に接続される。

50

**【 0 1 4 8 】**

第1のソース電極層406a及び第1のドレイン電極層406bの大きさ(上面積)は、層間絶縁層424に設けられるコンタクトホールの大きさ(開口部の平面積)以上とすればよく、トランジスタの微細化のためには、当該電極層の大きさを縮小することが好ましい。

**【 0 1 4 9 】**

層間絶縁層424には、有機絶縁層、又は無機絶縁層を適宜用いることができる。特に平坦性の良好な膜を形成することが容易な有機樹脂膜を用いることが好ましい。また、電極層422a及び電極層422bとしては、第1のソース電極層406a及び第1のドレイン電極層406bと同様の材料を用いることが好ましい。

10

**【 0 1 5 0 】**

以上が本発明の一態様におけるトランジスタである。本実施の形態で示すトランジスタは、下地絶縁層に含まれる酸素を、下地絶縁層から、又は、島状の酸化物積層の外周部で下地絶縁層と接するゲート絶縁層を経路としてチャネル形成領域へ供給し続けることが可能である。当該トランジスタの構成は、酸化物半導体層中の酸素欠損の増加を抑制して、不純物濃度を低減することができ、酸化物半導体層を高純度真性化することができる。

**【 0 1 5 1 】**

よって、チャネル形成領域の酸素欠損に起因して起こりうるしきい値電圧の変動等の電気的特性の変動を抑制することができる。具体的には、例えば、しきい値電圧のノーマリオフ化を安定に成就することができる。したがって、良好な電気特性を示すとともに長期信頼性の高い半導体装置を提供することができる。

20

**【 0 1 5 2 】**

なお、本実施の形態で示すトランジスタの構成は、それぞれ自由に組み合わせができる。例えば、トランジスタ310のゲート電極層を、トランジスタ320で示す積層構造としてもよい。

**【 0 1 5 3 】**

なお、本実施の形態は、本明細書で示す他の実施の形態または実施例と適宜組み合わせることができる。

**【 0 1 5 4 】****(実施の形態3)**

30

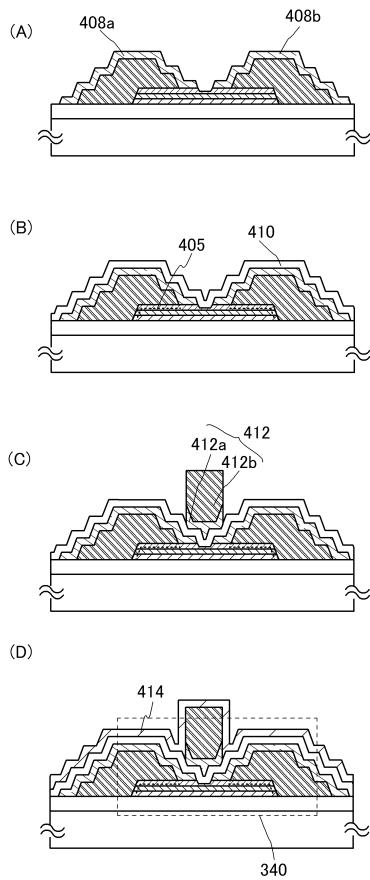

本実施の形態では、実施の形態1で説明したトランジスタの作製方法の一例を示す。本実施の形態では、図4及び図5を用いて図3(B)に示したトランジスタ340を作製する場合を例に説明する。

**【 0 1 5 5 】**

まず、絶縁表面を有する基板400上に、下地絶縁層402を形成する(図4(A)参照)。

**【 0 1 5 6 】**

下地絶縁層402の膜厚は、1nm以上100nm以下とし、プラズマCVD法またはスパッタ法等により、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム及び酸化タンタルなどの酸素を含む絶縁膜を用いて形成することができる。

40

**【 0 1 5 7 】**

下地絶縁層402は、少なくとも後に形成される酸化物積層404及びゲート絶縁層410と接する上層は酸化物積層404への酸素の供給源となりえる酸素を含む材料で形成する。また、過剰に酸素を含む膜とすることが好ましい。

**【 0 1 5 8 】**

下地絶縁層402に過剰に酸素を含有させるには、例えば、酸素雰囲気下にて下地絶縁層402を成膜すればよい。又は、成膜後の下地絶縁層402に酸素を導入して過剰に酸素を含有させてもよく、双方の手段を組み合わせてもよい。

50

## 【0159】

本実施の形態においては、成膜後の下地絶縁層402に酸素302（少なくとも、酸素ラジカル、酸素原子、酸素イオンのいずれかを含む）を導入して過剰に酸素を含有する領域を形成する。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。

## 【0160】

酸素導入処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素導入処理において、酸素を含むガスに希ガスを含ませてもよい。

## 【0161】

次いで、下地絶縁層402上に第1の酸化物層404a、酸化物半導体層404b、第2の酸化物層404cをスパッタリング法、CVD法、MBE法、ALD法またはPLD法を用いて成膜し、選択的にエッチングを行うことで酸化物積層404を形成する（図4（B）参照）。なお、エッチングの前に加熱工程を行ってもよい。

## 【0162】

第1の酸化物層404a、酸化物半導体層404b、及び第2の酸化物層404cには、実施の形態1で説明した材料を用いることができる。

## 【0163】

例えば、第1の酸化物層404aには、In:Ga:Zn = 1:3:2 [原子数比] のIn-Ga-Zn酸化物、In:Ga:Zn = 1:6:4 [原子数比] のIn-Ga-Zn酸化物、In:Ga:Zn = 1:9:6 [原子数比] のIn-Ga-Zn酸化物、又はその近傍の組成を有する酸化物を用いることが好ましい。

## 【0164】

また、例えば、酸化物半導体層404bには、In:Ga:Zn = 1:1:1 [原子数比] のIn-Ga-Zn酸化物、In:Ga:Zn = 3:1:2 [原子数比] のIn-Ga-Zn酸化物、又はその近傍の組成を有する酸化物を用いることが好ましい。

## 【0165】

また、例えば、第2の酸化物層404cには、In:Ga:Zn = 1:3:2 [原子数比] のIn-Ga-Zn酸化物、又はその近傍の組成を有する酸化物を用いることが好ましい。

## 【0166】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn = a:b:c (a+b+c = 1) である酸化物の組成が、原子数比がIn:Ga:Zn = A:B:C (A+B+C = 1) の酸化物の組成の近傍であるとは、a、b、cが、(a-A)<sup>2</sup> + (b-B)<sup>2</sup> + (c-C)<sup>2</sup>  $r^2$  を満たすことをいう。rとしては、例えば、0.05とすればよい。

## 【0167】

なお、各酸化物層の組成は上述の原子数比に限られない。但し、酸化物半導体層404bは、第1の酸化物層404a及び第2の酸化物層404cよりもインジウムの含有量を多くするといい。酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、より多くのs軌道が重なるため、InがGaよりも多い組成となる酸化物はインジウムがガリウムと同等または少ない組成となる酸化物と比較して移動度が高くなる。また、ガリウムはインジウムと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、ガリウムの含有量の多い酸化物は安定した特性を備える。

## 【0168】

そのため、酸化物半導体層404bにインジウムの含有量が多い酸化物を用いることで、高い移動度のトランジスタを実現することができる。また、絶縁層との界面側にガリウムの含有量の多い酸化物を用いることで、トランジスタの信頼性を高めることが可能となる。

## 【0169】

10

20

30

40

50

また、第1の酸化物層404a、酸化物半導体層404b、及び第2の酸化物層404cとして用いることのできる酸化物半導体は、少なくともインジウム(Indium)もしくは亜鉛(Zinc)を含むことが好ましい。または、IndiumとZincの双方を含むことが好ましい。特に、酸化物半導体層404bがインジウムを含有すると、トランジスタのキャリア移動度を高めることができ、亜鉛を含有すると、CACC-OS膜を形成しやすくなるため好ましい。また、酸化物半導体層を用いたトランジスタの電気特性のばらつきを減らすため、インジウム及び亜鉛と共に、スタビライザーを含むことが好ましい。

#### 【0170】

スタビライザーとしては、ガリウム(Gallium)、スズ(Silver)、ハフニウム(Hafnium)、アルミニウム(Aluminum)、またはジルコニウム(Zirconium)等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン(Lanthanum)、セリウム(Cerium)、プラセオジム(Praseodymium)、ネオジム(Neodimium)、サマリウム(Samarium)、ユウロピウム(Europium)、ガドリニウム(Gadolinium)、テルビウム(Terbium)、ジスプロシウム(Dysprosium)、ホルミウム(Holmium)、エルビウム(Erbium)、ツリウム(Triplutonium)、イッテルビウム(Ytterbium)、ルテチウム(Lutetium)等がある。

#### 【0171】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、Indium-Zinc酸化物、Silver-Zinc酸化物、Aluminum-Zinc酸化物、Zinc-Magnesium酸化物、Silver-Magnesium酸化物、Indium-Gallium酸化物、Indium-Gallium-Zinc酸化物、Indium-Aluminum-Zinc酸化物、Indium-Silver-Zinc酸化物、Silver-Gallium-Zinc酸化物、Aluminum-Gallium-Zinc酸化物、Silver-Aluminum-Zinc酸化物、Indium-Hafnium-Zinc酸化物、Indium-Lanthanum-Zinc酸化物、Indium-Cerium-Zinc酸化物、Indium-Praseodymium-Zinc酸化物、Indium-Neodimium-Zinc酸化物、Indium-Samarium-Zinc酸化物、Indium-Europium-Zinc酸化物、Indium-Gadolinium-Zinc酸化物、Indium-Terbium-Zinc酸化物、Indium-Dysprosium-Zinc酸化物、Indium-Holmium-Zinc酸化物、Indium-Erbium-Zinc酸化物、Indium-Triplutonium-Zinc酸化物、Indium-Lutetium-Zinc酸化物、Indium-Silver-Gallium-Zinc酸化物、Indium-Aluminum-Gallium-Zinc酸化物、Indium-Silver-Aluminum-Zinc酸化物、Indium-Hafnium-Aluminum-Zinc酸化物、Indium-Silver-Hafnium-Zinc酸化物、Indium-Hafnium-Aluminum-Zinc酸化物を用いることができる。

#### 【0172】

ただし、実施の形態1に詳細を記したように、第1の酸化物層404a及び第2の酸化物層404cは、酸化物半導体層404bよりも電子親和力が大きくなるように材料を選択する。

#### 【0173】

なお、酸化物積層の成膜には、スパッタ法を用いることが好ましい。スパッタ法としては、RFスパッタ法、DCスパッタ法、ACスパッタ法等を用いることができる。特に、成膜時に発生するゴミを低減でき、かつ膜厚分布も均一とすることからDCスパッタ法を用いることが好ましい。

#### 【0174】

なお、第1の酸化物層404aを成膜後、酸化物半導体層404bの成膜前に、第1の酸化物層404aに対して酸素を導入してもよい。当該酸素導入処理により、第1の酸化物層404aが過剰に酸素を含有し、その後の成膜工程における熱処理によって該過剰な酸素を酸化物半導体層404bへ供給することができる。

#### 【0175】

よって、第1の酸化物層404aへの酸素導入処理によって、酸化物半導体層404bの酸素欠損をより抑制することが可能となる。

#### 【0176】

なお、第1の酸化物層404aは酸素の導入処理によって非晶質化する場合がある。酸化物積層404において、少なくとも酸化物半導体層404bは、CACC-OS膜とすることが好ましい。よって、当該酸素の導入処理は、第1の酸化物層404aの成膜後であって、酸化物半導体層404bの成膜前に行なうことが好ましい。

10

20

30

40

50

## 【0177】

酸化物積層404を形成後、第1の加熱処理を行うことが好ましい。第1の加熱処理は、250以上650以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、または減圧状態で行えばよい。また、加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行ってもよい。第1の加熱処理によって、酸化物半導体層404bの結晶性を高め、さらに下地絶縁層402、第1の酸化物層404a、酸化物半導体層404b、又は第2の酸化物層404cの少なくとも一から水素や水などの不純物を除去することができる。なお、酸化物積層404を形成するエッチングの前に加熱工程を行ってもよい。

10

## 【0178】

その後、酸化物積層404上に第1のソース電極層406a及び第1のドレイン電極層406bとなる第1の導電膜を形成する。第1の導電膜としては、Al、Cr、Cu、Ta、Ti、Mo、W、またはこれらを主成分とする合金材料を用いることができる。例えば、スパッタ法などにより100nmのタンゲステン膜を形成する。

## 【0179】

次いで、第1の導電膜を酸化物積層404上で分断するようにエッチングし、第1のソース電極層406a及び第1のドレイン電極層406bを形成する(図4(C)参照)。このとき、第1のソース電極層406a及び第1のドレイン電極層406bの端部は図示するように階段状に形成することが好ましい。当該端部の加工は、アッシングによってレジストマスクを後退させる工程とエッチングの工程を交互に複数回行うことで形成することができる。

20

## 【0180】

なお、図示しないが、第1の導電膜のオーバーエッチングによって、酸化物積層404の一部(露出する領域)がエッチングされた形状となる場合がある。

## 【0181】

次に、酸化物積層404、第1のソース電極層406a及び第1のドレイン電極層406b上に、第2のソース電極層408a及び第2のドレイン電極層408bとなる第2の導電膜を形成する。第2の導電膜としては、窒化タンタル、窒化チタン等の窒化金属膜またはこれらを主成分とする合金材料を用いることができる。例えば、スパッタ法などにより20nmの窒化タンタル膜を形成する。

30

## 【0182】

次に、第2の導電膜を酸化物積層404上で分断するようにエッチングし、第2のソース電極層408a及び第2のドレイン電極層408bを形成する(図5(A)参照)。このとき、酸化物積層404の一部(より具体的には、第2の酸化物層404cの一部)がエッチングされた形状としてもよい。なお、図示しないが、第2のソース電極層408a及び第2のドレイン電極層408bを形成するためのエッチング処理によって、下地絶縁層402において第2のソース電極層408a及び第2のドレイン電極層408bから露出した領域がエッチングされ、当該領域の膜厚が小さくなる場合もある。

## 【0183】

40

なお、チャネル長(第2のソース電極層408aと第2のドレイン電極層408bとの間)が極短いトランジスタを形成する場合は、少なくとも第2の導電膜を分断する領域は、電子ビーム露光などの細線加工に適した方法を用いてレジストマスク加工を行い、エッチング工程によって当該領域をエッチングすればよい。なお、当該レジストマスクとしては、ポジ型レジストを用いれば、露光領域を最小限にすことができ、スループットを向上させることができる。このような方法を用いれば、チャネル長を30nm以下とするトランジスタを形成することができる。

## 【0184】

次に、酸化物積層404、第2のソース電極層408a及び第2のドレイン電極層408b上にゲート絶縁層410を形成する(図5(B)参照)。ゲート絶縁層410には、酸

50

化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム及び酸化タンタルなどを用いることができる。なお、ゲート絶縁層410は、上記材料の積層であってもよい。ゲート絶縁層410は、スパッタ法、CVD法、MBE法、ALD法またはPLD法などを用いて形成することができる。特に、ゲート絶縁層410をCVD法、好ましくはプラズマCVD法によって成膜すると、被覆性が良好であるため好ましい。

【0185】

ゲート絶縁層410成膜後、第2の加熱処理を行うことが好ましい。第2の加熱処理によって、ゲート絶縁層410に含まれる水、水素等の不純物を脱離（脱水化、又は脱水素化）させることができる。第2の加熱処理の温度は、300以上400以下とすることが好ましい。第2の加熱処理は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを10ppm以上含む雰囲気で行うことが好ましい。第2の加熱処理によって、ゲート絶縁層410から水素や水などの不純物を除去することができる。また、酸化物積層404からさらに水素や水などの不純物を除去されることもある。また、酸化性ガスを含む雰囲気下で加熱処理を行うことでゲート絶縁層410へ酸素を供給することができる。

【0186】

なお、第2の加熱処理は、ゲート絶縁層410を成膜後、成膜室内にて連続的に行うことが好ましい。または、ゲート絶縁層410成膜時の加熱によって、第2の加熱処理を兼ねることもできる。

【0187】

また、第1のソース電極層406a及び第1のドレイン電極層406bと、酸化物積層404とが接した状態で第2の加熱処理を行うことで、酸化物積層404から酸素と結合しやすい第1のソース電極層406a及び第1のドレイン電極層406bへ酸素が取り込まれる。よって、酸化物積層404の第1のソース電極層406a及び第1のドレイン電極層406bに接触する界面近傍の領域に酸素欠損が発生し、n型化した領域405が形成される。但し、第2の加熱処理の温度によっては、n型化が起こらない場合もある。

【0188】

次に、ゲート絶縁層410上にゲート電極層412となる導電膜を形成する。当該導電膜は、スパッタ法などにより形成することができる。そして、チャネル形成領域と重畳するように当該導電膜をエッチングして、ゲート電極層412を形成する（図5（C）参照）。

【0189】

本実施の形態では、第2の導電膜と同様の材料を用いた第1のゲート電極層412aと、第1の導電膜と同様の材料を用いた第2のゲート電極層412bの積層構造を有するゲート電極層412を形成する。

【0190】

次いで、ゲート絶縁層410及びゲート電極層412上に、保護絶縁層414を形成する（図5（D）参照）。保護絶縁層414としては、ゲート絶縁層410よりも酸素に対する透過性が低い（酸素に対するバリア性を有する）絶縁層を設ける。例えば、保護絶縁層414として窒化シリコン膜又は窒化酸化シリコン膜を設けることができる。

【0191】

なお、保護絶縁層414は含有される水素濃度を低減することが好ましいため、スパッタリング法によって成膜することが好ましい。保護絶縁層414に含まれる水素濃度は、 $5 \times 10^{-9} \text{ cm}^{-3}$ 未満とすることが好ましく、 $5 \times 10^{-8} \text{ cm}^{-3}$ 未満とすることがより好ましい。

【0192】

保護絶縁層414を形成後に、第3の加熱処理を行うことが好ましい。第3の加熱処理の温度は、350以上450以下とすることが好ましい。第3の加熱処理により、下地

10

20

30

40

50

絶縁層 402 及びゲート絶縁層 410 から酸素が放出されやすくなり、酸化物積層 404 の酸素欠損を低減することができる。

【0193】

また、第3の加熱処理によって、酸化物積層 404 から酸素と結合しやすい第1のソース電極層 406a 及び第1のドレイン電極層 406b へ酸素が移動しうる。よって、n型化した領域 405 においてより n型化されることがある。又は、第2の加熱処理によって、界面近傍の領域の n型化が起こらなかった場合でも、第3の加熱処理によって n型化した領域 405 とすることができます。

【0194】

以上によって、本実施の形態のトランジスタ 340 を作製することができる。

10

【0195】

なお、本実施の形態は、本明細書で示す他の実施の形態または実施例と適宜組み合わせることができる。

【0196】

(実施の形態 4)

本発明の一態様に係る半導体装置の一例として、論理回路である NOR 型回路の回路図の一例を図 20 (A) に示す。図 20 (B) は NAND 型回路の回路図である。

【0197】

図 20 (A) に示す NOR 型回路において、pチャネル型トランジスタであるトランジスタ 801、802 は、チャネル形成領域に酸化物半導体以外の半導体材料 (例えば、シリコンなど) を用いたトランジスタとし、nチャネル型トランジスタであるトランジスタ 803、804 は、酸化物半導体を含む酸化物積層を含み実施の形態 2 で示すトランジスタと同様な構造を有するトランジスタを用いる。

20

【0198】

シリコンなどの半導体材料を用いたトランジスタは高速動作が容易である。一方、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0199】

論理回路の小型化のために、nチャネル型のトランジスタであるトランジスタ 803、804 は、pチャネル型のトランジスタであるトランジスタ 801、802 上に積層されることが好ましい。例えば、単結晶シリコン基板を用いてトランジスタ 801、802 を形成し、絶縁層を介してトランジスタ 801、802 上にトランジスタ 803、804 を形成することが可能である。

30

【0200】

なお、図 20 (A) に示す NOR 型回路において、トランジスタ 803、804 として、トランジスタ 520 と同様な構成を有する構成として、第2のゲート電極の電位を制御し、例えば GND とすることでトランジスタ 803、804 のしきい値電圧をよりプラスとし、さらにノーマリオフのトランジスタとすることができます。

【0201】

また、図 20 (B) に示す NAND 型回路では、pチャネル型トランジスタであるトランジスタ 811、814 は、チャネル形成領域に酸化物半導体以外の半導体材料 (例えば、シリコンなど) を用いたトランジスタとし、nチャネル型トランジスタであるトランジスタ 812、813 は、酸化物半導体を含む酸化物積層を含み、上記実施の形態 2 で示すトランジスタと同様な構造を有するトランジスタを用いる。

40

【0202】

なお、図 20 (B) に示す NAND 型回路において、トランジスタ 812、813 として、トランジスタ 520 と同様な構成を有する構成として、第2のゲート電極の電位を制御し、例えば GND とすることでトランジスタ 812、813 のしきい値電圧をよりプラスとし、さらにノーマリオフのトランジスタとすることができます。

【0203】

また、図 20 (A) に示す NOR 回路と同様に、論理回路の小型化のために、nチャネル

50

型のトランジスタであるトランジスタ 812、813 は、p チャネル型のトランジスタであるトランジスタ 811、812 上に積層されることが好ましい。

【0204】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、消費電力を十分に低減することができる。

【0205】

また、異なる半導体材料を用いた半導体素子を積層することにより、微細化及び高集積化を実現し、かつ安定で高い電気的特性を付与された半導体装置、及び該半導体装置の作製方法を提供することができる。

10

【0206】

また、上記実施の形態 2 に示すトランジスタの構成を適用することで、信頼性が高く、安定した特性を示す NOR 型回路と NAND 型回路を提供することができる。

【0207】

なお、本実施の形態では、実施の形態 2 に示すトランジスタを使用した NOR 型回路と NAND 型回路の例を示したが、特に限定されず、AND 型回路や OR 回路などを形成することもできる。

【0208】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

20

【0209】

(実施の形態 5)

本実施の形態では、実施の形態 2 に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置（記憶装置）の一例を、図面を用いて説明する。

【0210】

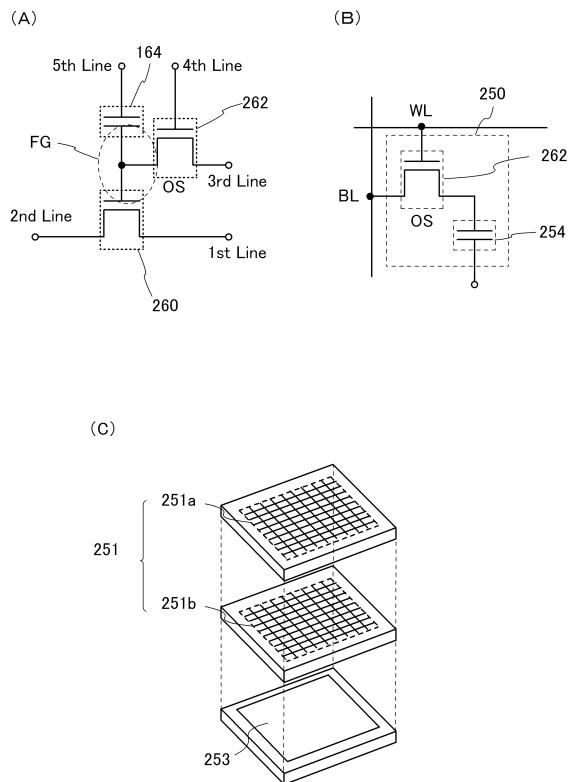

図 21 (A) は、本実施の形態の半導体装置を示す回路図である。

【0211】

図 21 (A) に示すトランジスタ 260 は、酸化物半導体以外の半導体材料（例えば、シリコンなど）を用いたトランジスタを適用することができ、高速動作が容易である。また、トランジスタ 262 には酸化物半導体積層を含み実施の形態 2 で示すトランジスタと同様な構造を有するトランジスタを適用することができ、その特性により長時間の電荷保持を可能とする。

30

【0212】

なお、上記トランジスタは、いずれも n チャネル型トランジスタであるものとして説明するが、本実施の形態に示す半導体装置に用いるトランジスタとしては、p チャネル型トランジスタを用いることもできる。

【0213】

図 21 (A) において、第 1 の配線 (1st Line) とトランジスタ 260 のソース電極層とは、電気的に接続され、第 2 の配線 (2nd Line) とトランジスタ 260 のドレイン電極層とは、電気的に接続されている。また、第 3 の配線 (3rd Line) とトランジスタ 262 のソース電極層又はドレイン電極層の一方とは、電気的に接続され、第 4 の配線 (4th Line) と、トランジスタ 262 のゲート電極層とは、電気的に接続されている。そして、トランジスタ 260 のゲート電極層と、トランジスタ 262 のソース電極層又はドレイン電極層の他方は、容量素子 264 の電極の一方と電気的に接続され、第 5 の配線 (5th Line) と、容量素子 264 の電極の他方は電気的に接続されている。

40

【0214】

図 21 (A) に示す半導体装置では、トランジスタ 260 のゲート電極層の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能であ

50

る。

【0215】

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ262がオン状態となる電位にして、トランジスタ262をオン状態とする。これにより、第3の配線の電位が、トランジスタ260のゲート電極層、および容量素子264に与えられる。すなわち、トランジスタ260のゲート電極層には、所定の電荷が与えられる（書き込み）。ここでは、異なる二つの電位レベルを与える電荷（以下Lowレベル電荷、Highレベル電荷という）のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ262がオフ状態となる電位にして、トランジスタ262をオフ状態とすることにより、トランジスタ260のゲート電極層に与えられた電荷が保持される（保持）。 10

【0216】

トランジスタ262のオフ電流は極めて小さいため、トランジスタ260のゲート電極層の電荷は長時間にわたって保持される。

【0217】

次に情報の読み出しについて説明する。第1の配線に所定の電位（定電位）を与えた状態で、第5の配線に適切な電位（読み出し電位）を与えると、トランジスタ260のゲート電極層に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ260をnチャネル型とすると、トランジスタ260のゲート電極層にHighレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、トランジスタ260のゲート電極層にLowレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ260を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を $V_{th\_H}$ と $V_{th\_L}$ の中間の電位 $V_0$ とすることにより、トランジスタ260のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位が $V_0 (> V_{th\_H})$ となれば、トランジスタ260は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位が $V_0 (< V_{th\_L})$ となっても、トランジスタ260は「オフ状態」のままである。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。 30

【0218】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極層の状態にかかわらずトランジスタ260が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線に与えればよい。又は、ゲート電極層の状態にかかわらずトランジスタ260が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線に与えればよい。

【0219】

図21(B)に異なる記憶装置の構造の一形態の例を示す。図21(B)は、半導体装置の回路構成の一例を示し、図21(C)は半導体装置の一例を示す概念図である。まず、図21(B)に示す半導体装置について説明を行い、続けて図21(C)に示す半導体装置について、以下説明を行う。 40

【0220】

図21(B)に示す半導体装置において、ビット線BLとトランジスタ262のソース電極またはドレイン電極とは電気的に接続され、ワード線WLとトランジスタ262のゲート電極層とは電気的に接続され、トランジスタ262のソース電極またはドレイン電極と容量素子254の第1の端子とは電気的に接続されている。

【0221】

酸化物半導体を用いたトランジスタ262は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ262をオフ状態とすることで、容量素子254の第1 50

の端子の電位（あるいは、容量素子 254 に蓄積された電荷）を極めて長時間にわたって保持することが可能である。

【0222】

次に、図 21 (B) に示す半導体装置（メモリセル 250）に、情報の書き込み及び保持を行う場合について説明する。

【0223】

まず、ワード線 WL の電位を、トランジスタ 262 がオン状態となる電位として、トランジスタ 262 をオフ状態とする。これにより、ビット線 BL の電位が、容量素子 254 の第1の端子に与えられる（書き込み）。その後、ワード線 WL の電位を、トランジスタ 262 がオフ状態となる電位として、トランジスタ 262 をオフ状態とすることにより、容量素子 254 の第1の端子の電位が保持される（保持）。 10

【0224】

トランジスタ 262 のオフ電流は極めて小さいため、容量素子 254 の第1の端子の電位（あるいは容量素子に蓄積された電荷）を長時間にわたって保持することができる。

【0225】

次に、情報の読み出しについて説明する。トランジスタ 262 がオン状態となると、浮遊状態であるビット線 BL と容量素子 254 とが導通し、ビット線 BL と容量素子 254 の間に電荷が再分配される。その結果、ビット線 BL の電位が変化する。ビット線 BL の電位の変化量は、容量素子 254 の第1の端子の電位（あるいは容量素子 254 に蓄積された電荷）によって、異なる値をとる。 20

【0226】

例えば、容量素子 254 の第1の端子の電位を V、容量素子 254 の容量を C、ビット線 BL が有する容量成分（以下、ビット線容量とも呼ぶ）を CB、電荷が再分配される前のビット線 BL の電位を V B 0 とすると、電荷が再分配された後のビット線 BL の電位は、 $(CB \times V B 0 + C \times V) / (CB + C)$  となる。従って、メモリセル 250 の状態として、容量素子 254 の第1の端子の電位が V 1 と V 0 (V 1 > V 0) の2状態をとるとすると、電位 V 1 を保持している場合のビット線 BL の電位 ( $= CB \times V B 0 + C \times V 1$ ) / (CB + C) は、電位 V 0 を保持している場合のビット線 BL の電位 ( $= CB \times V B 0 + C \times V 0$ ) / (CB + C) よりも高くなることがわかる。 30

【0227】

そして、ビット線 BL の電位を所定の電位と比較することで、情報を読み出すことができる。

【0228】

このように、図 21 (B) に示す半導体装置は、トランジスタ 262 のオフ電流が極めて小さいという特徴から、容量素子 254 に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することができる。

【0229】

次に、図 21 (C) に示す半導体装置について、説明を行う。

【0230】

図 21 (C) に示す半導体装置は、上部に記憶回路として図 21 (B) に示したメモリセル 250 を複数有するメモリセルアレイ 251 a 及びメモリセルアレイ 251 b を有し、下部に、メモリセルアレイ 251 (メモリセルアレイ 251 a 及びメモリセルアレイ 251 b) を動作させるために必要な周辺回路 253 を有する。なお、周辺回路 253 は、メモリセルアレイ 251 と電気的に接続されている。

【0231】

図 21 (C) に示した構成とすることにより、周辺回路 253 をメモリセルアレイ 251 (メモリセルアレイ 251 a 及びメモリセルアレイ 251 b) の直下に設けることができ 50

るため半導体装置の小型化を図ることができる。

【0232】

周辺回路253に設けられるトランジスタは、トランジスタ262とは異なる半導体材料を用いるのがより好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、前記トランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することが可能である。

【0233】

10

なお、図21(C)に示した半導体装置では、2つのメモリセルアレイ251（メモリセルアレイ251aと、メモリセルアレイ251b）が積層された構成を例示したが、積層するメモリセルの数はこれに限定されない。3つ以上のメモリセルを積層する構成としてもよい。

【0234】

トランジスタ262として、酸化物半導体をチャネル形成領域に用いるトランジスタを適用することによって、長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

【0235】

20

また、本実施の形態に示す半導体装置として実施の形態1に示す酸化物積層を含み、チャネル領域となる酸化物半導体層が酸化物積層の表面から遠ざけられている半導体装置を適用することで、信頼性が高く、安定した電気特性を示す半導体装置とすることができます。

【0236】

（実施の形態6）

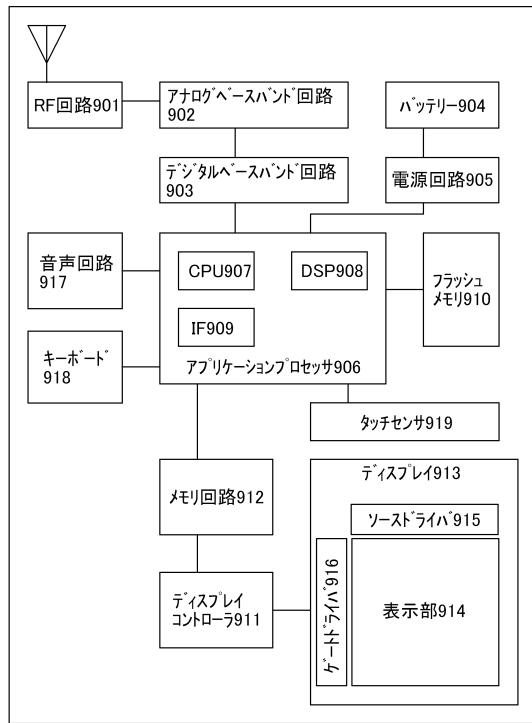

本実施の形態では、先の実施の形態で示した半導体装置を携帯電話、スマートフォン、電子書籍などの電子機器に応用した場合の例を図22乃至図25を用いて説明する。

【0237】

図22に電子機器のブロック図を示す。図22に示す電子機器はRF回路901、アナログベースバンド回路902、デジタルベースバンド回路903、バッテリー904、電源回路905、アプリケーションプロセッサ906、フラッシュメモリ910、ディスプレイコントローラ911、メモリ回路912、ディスプレイ913、タッチセンサ919、音声回路917、キーボード918などより構成されている。ディスプレイ913は表示部914、ソースドライバ915、ゲートドライバ916によって構成されている。アプリケーションプロセッサ906はCPU907、DSP908、インターフェイス(IF)909を有している。一般にメモリ回路912はSRAMまたはDRAMで構成されており、この部分に先の実施の形態で説明した半導体装置を採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された信頼性の高い電子機器を提供することができる。

30

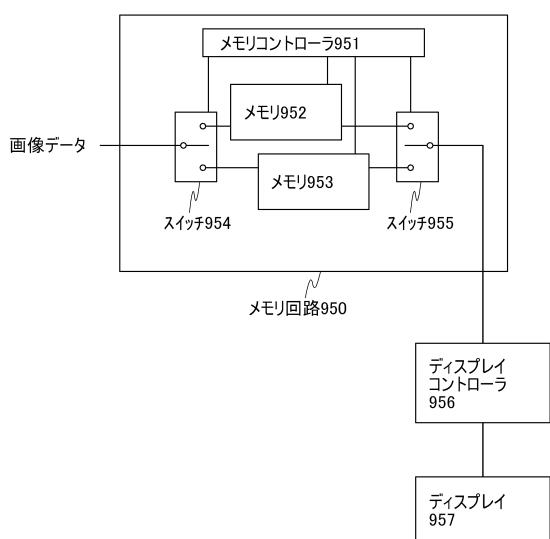

【0238】

40

図23に、ディスプレイのメモリ回路950に先の実施の形態で説明した半導体装置を使用した例を示す。図23に示すメモリ回路950は、メモリ952、メモリ953、スイッチ954、スイッチ955及びメモリコントローラ951により構成されている。また、メモリ回路は、画像データ（入力画像データ）からの信号線、メモリ952及びメモリ953に記憶されたデータ（記憶画像データ）を読み出し、及び制御を行うディスプレイコントローラ956と、ディスプレイコントローラ956からの信号により表示するディスプレイ957が接続されている。

【0239】

まず、ある画像データがアプリケーションプロセッサ（図示しない）によって、形成される（入力画像データA）。入力画像データAは、スイッチ954を介してメモリ952に

50

記憶される。そしてメモリ 952 に記憶された画像データ（記憶画像データ A）は、スイッチ 955、及びディスプレイコントローラ 956 を介してディスプレイ 957 に送られ、表示される。

【 0240 】

入力画像データ A に変更が無い場合、記憶画像データ A は、通常 30 ~ 60 Hz 程度の周期でメモリ 952 からスイッチ 955 を介して、ディスプレイコントローラ 956 から読み出される。

【 0241 】

次に、例えばユーザーが画面を書き換える操作をしたとき（すなわち、入力画像データ A に変更が有る場合）、アプリケーションプロセッサは新たな画像データ（入力画像データ B）を形成する。入力画像データ B はスイッチ 954 を介してメモリ 953 に記憶される。この間も定期的にメモリ 952 からスイッチ 955 を介して記憶画像データ A は読み出されている。メモリ 953 に新たな画像データ（記憶画像データ B）が記憶し終わると、ディスプレイ 957 の次のフレームより、記憶画像データ B は読み出され、スイッチ 955、及びディスプレイコントローラ 956 を介して、ディスプレイ 957 に記憶画像データ B が送られ、表示がおこなわれる。この読み出しはさらに次に新たな画像データがメモリ 952 に記憶されるまで継続される。

10

【 0242 】

このようにメモリ 952 及びメモリ 953 は交互に画像データの書き込みと、画像データの読み出しを行うことによって、ディスプレイ 957 の表示をおこなう。なお、メモリ 952 及びメモリ 953 はそれぞれ別のメモリには限定されず、1 つのメモリを分割して使用してもよい。先の実施の形態で説明した半導体装置をメモリ 952 及びメモリ 953 に採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。また、外部からの水、水分等の侵入の影響を受けにくい信頼性の高い半導体装置とすることができる。

20

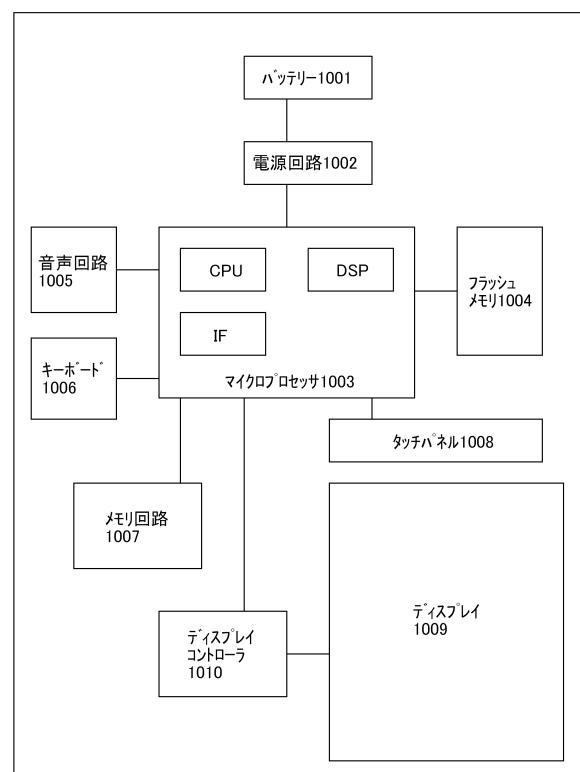

【 0243 】

図 24 に電子書籍のブロック図を示す。図 24 はバッテリー 1001、電源回路 1002、マイクロプロセッサ 1003、フラッシュメモリ 1004、音声回路 1005、キーボード 1006、メモリ回路 1007、タッチパネル 1008、ディスプレイ 1009、ディスプレイコントローラ 1010 によって構成される。

30

【 0244 】

ここでは、図 24 のメモリ回路 1007 に先の実施の形態で説明した半導体装置を使用することができる。メモリ回路 1007 は書籍の内容を一時的に保持する機能を持つ。例えば、ユーザーがハイライト機能を使用する場合、メモリ回路 1007 は、ユーザーが指定した箇所の情報を記憶し、保持する。なおハイライト機能とは、ユーザーが電子書籍を読んでいるときに、特定の箇所にマーキング、例えば、表示の色を変える、アンダーラインを引く、文字を太くする、文字の書体を変えるなどによってマーキングして周囲との違いを示すことである。メモリ回路 1007 は短期的な情報の記憶に用い、長期的な情報の保存にはフラッシュメモリ 1004 に、メモリ回路 1007 が保持しているデータをコピーしてもよい。このような場合においても、先の実施の形態で説明した半導体装置を採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を十分に低減することができる。また、外部からの水、水分等の侵入の影響を受けにくい信頼性の高い半導体装置とすることができる。

40

【 0245 】

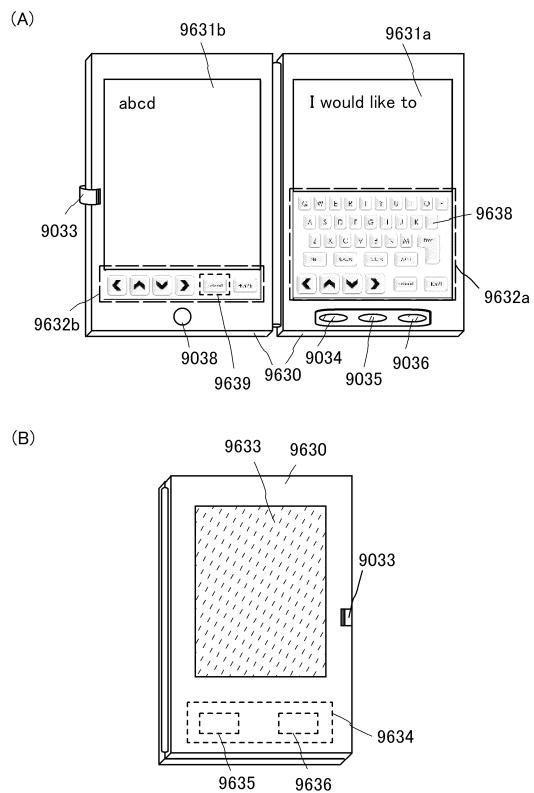

図 25 に電子機器の具体例を示す。図 25 (A) 及び図 25 (B) は、2 つ折り可能なタブレット型端末である。図 25 (A) は、開いた状態であり、タブレット型端末は、筐体 9630、表示部 9631a、表示部 9631b、表示モード切り替えスイッチ 9034、電源スイッチ 9035、省電力モード切り替えスイッチ 9036、留め具 9033、操作スイッチ 9038 を有する。

【 0246 】

50

先の実施の形態に示した半導体装置は、表示部 9631a、表示部 9631b に用いることが可能であり、信頼性の高いタブレット型端末とすることが可能となる。また、先の実施の形態に示す記憶装置を本実施の形態の半導体装置に適用してもよい。

【0247】

表示部 9631a は、一部をタッチパネルの領域 9632a とすることができます、表示された操作キー 9638 にふれることでデータ入力をすることができる。なお、表示部 9631a においては、一例として半分の領域が表示のみの機能を有する構成、もう半分の領域がタッチパネルの機能を有する構成を示しているが、該構成に限定されない。表示部 9631a の全面をキーボードボタン表示させてタッチパネルとし、表示部 9631b を表示画面として用いることができる。

10

【0248】

また、表示部 9631b においても表示部 9631a と同様に、表示部 9631b の一部をタッチパネルの領域 9632b とすることができます。また、タッチパネルのキーボード表示切り替えボタン 9639 が表示されている位置に指やスタイルスなどでふれることで表示部 9631b にキーボードボタン表示することができる。

【0249】

また、タッチパネルの領域 9632a とタッチパネルの領域 9632b に対して同時にタッチ入力することもできる。

【0250】

また、表示モード切り替えスイッチ 9034 は、縦表示または横表示などの表示の向きを切り替え、白黒表示やカラー表示の切り替えなどを選択できる。省電力モード切り替えスイッチ 9036 は、タブレット型端末に内蔵している光センサで検出される使用時の外光の光量に応じて表示の輝度を最適なものとすることができます。タブレット型端末は光センサだけでなく、ジャイロ、加速度センサ等の傾きを検出するセンサなどの他の検出装置を内蔵させてもよい。

20

【0251】

また、図 25 (A) では表示部 9631b と表示部 9631a の表示面積が同じ例を示しているが特に限定されず、一方のサイズともう一方のサイズが異なっていてもよく、表示の品質も異なっていてもよい。例えば一方が他方よりも高精細な表示を行える表示パネルとしてもよい。

30

【0252】

図 25 (B) は、閉じた状態であり、タブレット型端末は、筐体 9630、太陽電池 9633、充放電制御回路 9634、バッテリー 9635、DCDC コンバータ 9636 を有する。なお、図 12 (B) では充放電制御回路 9634 の一例としてバッテリー 9635、DCDC コンバータ 9636 を有する構成について示している。

【0253】

なお、タブレット型端末は 2 つ折り可能なため、未使用時に筐体 9630 を閉じた状態にすることができる。従って、表示部 9631a、表示部 9631b を保護できるため、耐久性に優れ、長期使用の観点からも信頼性の優れたタブレット型端末を提供できる。

40

【0254】

また、この他にも図 25 (A) および図 25 (B) に示したタブレット型端末は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付または時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作または編集するタッチ入力機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。

【0255】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【実施例 1】

【0256】

50

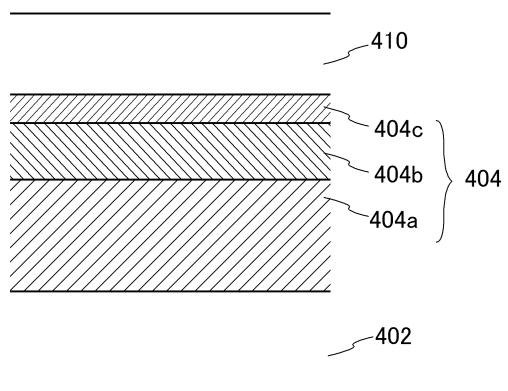

本実施例では、酸化物半導体膜上に導電膜を形成し、S I M S 分析により、積層された膜間の元素の移動について調べた結果について説明する。

【 0 2 5 7 】

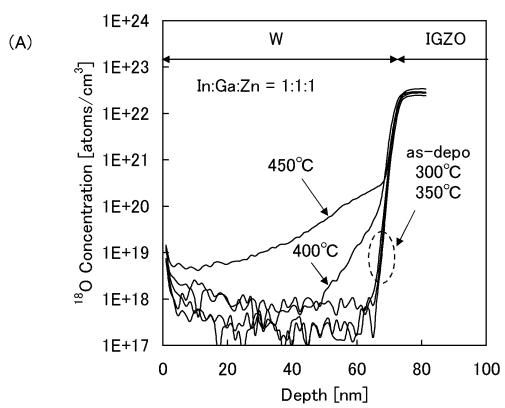

図 1 1 ( A )、( B )は、スパッタリング法を用いて I G Z O 膜及びタンゲステン膜の積層サンプルを作製し、酸素同位体 ( $^{18}\text{O}$ ) の深さ方向のプロファイルを熱処理前後で S I M S 分析した結果である。なお、I G Z O 膜は、In : Ga : Zn = 1 : 1 : 1 または 1 : 3 : 2 (原子数比) をスパッタリングターゲットとし、Ar : O<sub>2</sub> ( $^{18}\text{O}$ ) = 2 : 1 (流量比) を成膜ガスとして用いて D C スパッタリング法で形成している。また、タンゲステン膜は、金属タンゲステンをスパッタリングターゲットとし、Ar 100 % を成膜ガスとして D C スパッタリング法を用いて形成した。なお、熱処理は、300 、 350 10 、 400 、 450 の各 1 時間で行い、熱処理を施していないサンプルを含めて各 5 サンプルで比較を行った。

【 0 2 5 8 】

ここで、In : Ga : Zn = 1 : 1 : 1 (原子数比) をスパッタリングターゲットとして形成した I G Z O 膜は、C AAC - O S 膜であり、In : Ga : Zn = 1 : 3 : 2 (原子数比) をスパッタリングターゲットとして形成した I G Z O 膜は、非晶質の I G Z O 膜である。

【 0 2 5 9 】

図 1 1 ( A )、( B )に示すように、酸化物半導体膜の組成 (結晶性) に関わらず、熱処理温度が高くなると、酸化物半導体膜中の酸素がタンゲステン膜側に取り込まれることがわかる。

【 0 2 6 0 】

トランジスタの作製工程にはいくつかの加熱工程があることから、上記現象により、酸化物半導体層のソース電極及びドレイン電極と接した近傍の領域に酸素欠損が発生し、当該領域は n 型化する。したがって、n 型化した当該領域は、トランジスタのソースまたはドレインとして機能させることができる。

【 0 2 6 1 】

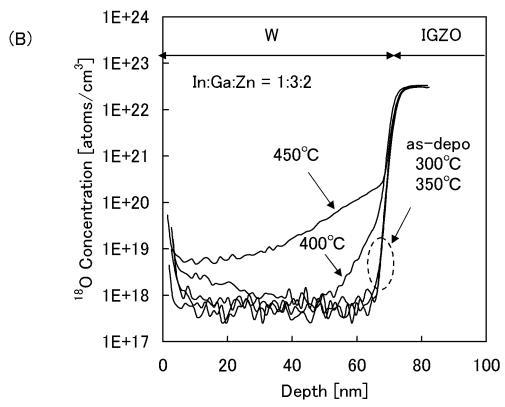

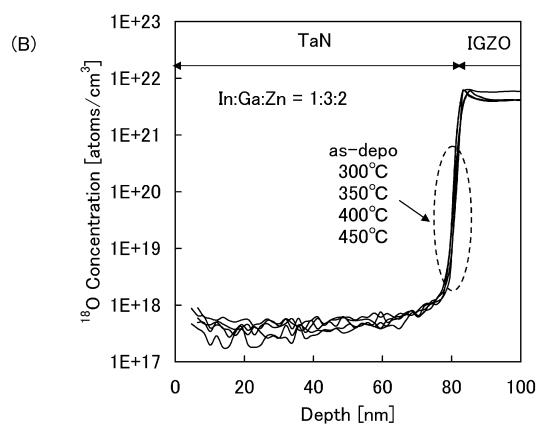

図 1 2 ( A )、( B )は上記タンゲステン膜に換えて、窒化タンタル膜を用いて作製したサンプルについて S I M S 分析した結果である。窒化タンタル膜は、金属タンタルをスパッタリングターゲットとし、Ar : N<sub>2</sub> = 5 : 1 (流量比) を成膜ガスとして反応性スパッタリング法 (D C スパッタリング法) で形成した。なお、熱処理として、上記と同様の各 4 条件で行い、熱処理を施していないサンプルを含めて各 5 サンプルで比較を行った。

【 0 2 6 2 】

図 1 2 ( A ) は、In : Ga : Zn = 1 : 1 : 1 の I G Z O 膜と窒化タンタル膜の積層サンプルにおける S I M S 分析結果である。いずれのサンプルも窒化タンタル膜中の酸素の移動 (取り込み) は確認されず、図 1 1 ( A ) に示したタンゲステン膜とは異なった挙動を示した。また、図 1 2 ( B ) は、In : Ga : Zn = 1 : 3 : 2 の I G Z O 膜と窒化タンタル膜の積層サンプルにおける S I M S 分析結果である。いずれのサンプルも窒化タンタル膜中の酸素の移動 (取り込み) は確認されず、図 1 1 ( B ) に示したタンゲステン膜とは異なった挙動を示した。したがって、窒化タンタル膜は酸素と結合しにくい膜、または酸素を取り込みにくい膜ということができる。

【 0 2 6 3 】

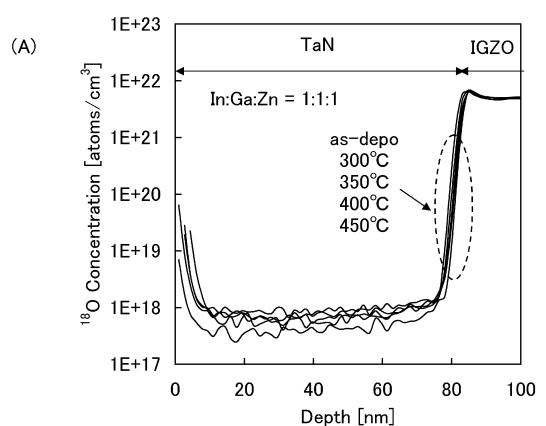

図 1 3 ( A )、( B )は、上記タンゲステン膜に換えて、窒化チタン膜を用いて作製したサンプルについて S I M S 分析した結果である。窒化チタン膜は、金属チタンをスパッタリングターゲットとし、N<sub>2</sub> 100 % を成膜ガスとして反応性スパッタリング法 (D C スパッタリング法) で形成した。なお熱処理として、上記と同様の各 4 条件で行い、熱処理を施していないサンプルを含めて各 5 サンプルで比較を行った。

【 0 2 6 4 】

図 1 3 ( A ) は、In : Ga : Zn = 1 : 1 : 1 の I G Z O 膜と窒化チタン膜の積層サンプルにおける S I M S 分析結果である。いずれのサンプルも窒化チタン膜中の酸素の移

10

20

30

40

50

動（取り込み）は確認されず、図11（A）に示したタンゲステン膜とは異なった挙動を示した。また、図13（B）は、In:Ga:Zn = 1:3:2のIGZO膜と窒化チタン膜の積層サンプルにおけるSIMS分析結果である。いずれのサンプルも窒化チタン膜中への酸素の移動（取り込み）は確認されず、図11（B）に示したタンゲステン膜とは異なった挙動を示した。したがって、窒化チタン膜は酸素と結合しにくい膜、または酸素を取り込みにくい膜ということができる。

#### 【0265】

続いて、IGZO膜中への不純物の移動についてSIMS分析により調べた結果について説明する。

#### 【0266】

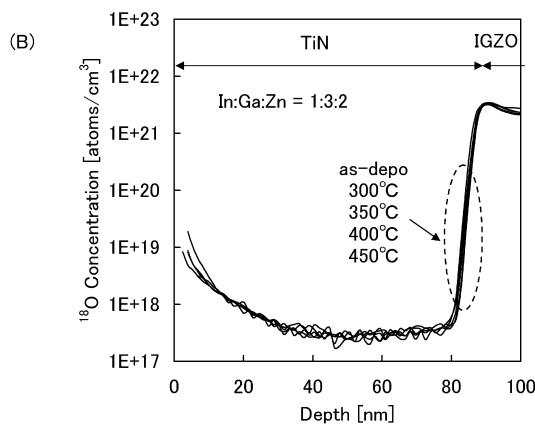

図14（A）、（B）は、スパッタリング法でIGZO膜上に窒化タンタルまたは窒化チタン膜を形成し、窒素の深さ方向のプロファイルを熱処理前後でSIMS分析した結果である。なお、IGZO膜は、In:Ga:Zn = 1:1:1（原子数比）をスパッタリングターゲットとし、Ar:O<sub>2</sub> = 2:1（流量比）を成膜ガスとして用いてDCスパッタリング法で形成した。また、窒化タンタル膜及び窒化チタン膜は、前述の作製方法で形成した。なお、熱処理は、400、1時間の条件で行い、熱処理を施していないサンプルを含めて各2サンプルで比較を行った。

#### 【0267】

図14（A）、（B）に示すように、いずれのサンプルもIGZO膜中への窒素の移動は確認されないことが分かった。したがって、IGZO膜中でドナーとなる窒素は、窒化タンタル及び窒化チタン膜からIGZO膜中に広く移動することができないため、トランジスタのチャネル形成領域をn型化させないことが分かった。

#### 【0268】

また、図15（A）、（B）は、図14で例示した同様のサンプルについて、TaまたはTiの深さ方向のプロファイルをSIMS分析した結果である。図15（A）、（B）に示すように、IGZO膜中へのTaまたはTiの移動が確認されないことが分かった。したがって、トランジスタの電気特性に影響する不純物となりえるTi及びTaは、窒化タンタル膜または窒化チタン膜からIGZO膜中に広く移動することができないことが分かった。

#### 【0269】

以上により、窒化タンタル、窒化チタンなどの導電性窒化物は、酸素と結合しにくい膜または酸素を取り込みにくい膜であり、当該導電性窒化膜中の窒素及び金属元素は、酸化物半導体膜中に移動しにくいことが示された。

#### 【0270】

本実施例は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【実施例2】

#### 【0271】

本実施例では、酸化物半導体膜上に導電膜を形成した後に導電膜を除去し、酸化物半導体膜のシート抵抗値を測定した結果について説明する。

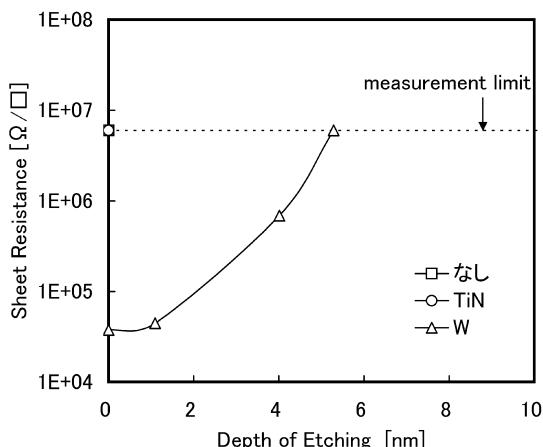

#### 【0272】

図16は、スパッタリング法を用いてIGZO膜を形成し、IGZO膜に積層してスパッタリング法によりタンゲステン膜または窒化チタン膜を形成し、その後タンゲステン膜又は窒化チタン膜を除去して作製したサンプルについて、IGZO膜をエッチングした深さに対するシート抵抗値を測定した結果である。また、比較として、IGZO膜上に導電膜を形成していないサンプルも作製した。なお、IGZO膜は、In:Ga:Zn = 1:1:1（原子数比）をスパッタリングターゲットとし、Ar:O<sub>2</sub>（<sup>18</sup>O） = 2:1（流量比）を成膜ガスとして用いてDCスパッタリング法で形成した。また、タンゲステン膜は、金属タンゲステンをスパッタリングターゲットとし、Ar 100%を成膜ガスとしてDCスパッタリング法を用いて形成した。窒化チタン膜は、金属チタンをスパッタリング

10

20

30

40

50

ターゲットとし、N<sub>2</sub> 100%を成膜ガスとして反応性スパッタリング法（DCスパッタリング法）で形成した。タンゲステン膜及び窒化チタン膜のエッチングには、過酸化水素水を用いた。IGZO膜のエッチングには、過酸化水素水とアンモニアの混合水溶液を用いた。また、IGZO膜のエッチング深さは、エッチングの前後における分光エリプソメトリーを用いて測定した残膜の厚さから求めた。

#### 【0273】

図16に示すように、IGZO膜上にタンゲステン膜を形成したサンプルでは、IGZO膜の表面から約5nmの深さまで低抵抗化していることが確認できた。これは、IGZO膜の表面近傍に低抵抗なIGZOとタンゲステンの混合層が形成されていること、またはIGZO膜中の酸素がタンゲステン膜中に取り込まれることで、IGZO膜の表面近傍の酸素欠損によるn型化した領域が形成されていること、などを示唆している。

10

#### 【0274】

一方、IGZO膜上に窒化チタンを形成したサンプル、及び導電膜を形成していないサンプルでは、IGZO膜の低抵抗化は確認できなかった。これは、窒化チタンを構成する元素がIGZO膜中に取り込まれにくいこと、または、IGZO膜中の酸素は窒化チタン膜に取り込まれにくいこと、などを示唆している。

#### 【0275】

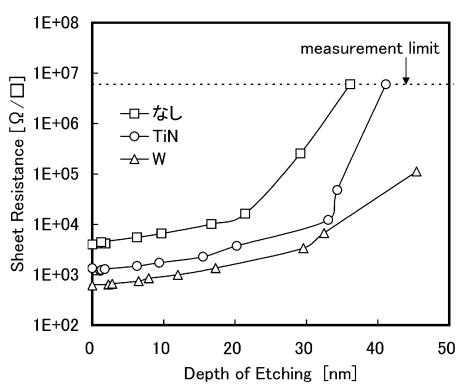

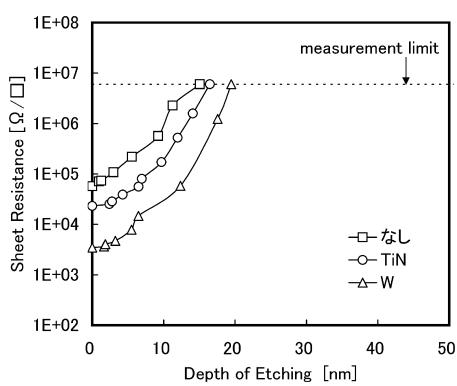

図17（A）は、スパッタリング法を用いてIGZO膜を形成し、IGZO膜に積層してスパッタリング法によりタンゲステン膜または窒化チタン膜を形成し、その後加熱処理を施した後に、タンゲステン膜または窒化チタン膜を除去して作製したサンプルについて、IGZO膜をエッチングした深さに対するシート抵抗値を測定した結果である。また、比較として、IGZO膜上に導電膜を形成していないサンプルも作製した。なお、IGZO膜、タンゲステン膜、窒化チタン膜の形成及び除去は、上述と同様に行った。加熱処理は、N<sub>2</sub>雰囲気下で400 1hの条件で行った。

20

#### 【0276】

図17（A）に示すように、いずれのサンプルにおいても、IGZO膜の低抵抗化が確認された。ここで、IGZO膜上にタンゲステン膜を形成したサンプルが、表面近傍で最も低抵抗化され、且つ、最も深くまで低抵抗化されていることが確認できた。これは、タンゲステン膜が最もIGZO膜中の酸素を取り込みやすいことを示している。また、IGZO膜上に窒化チタンを形成したサンプルでは、IGZO膜上に導電膜を形成しないサンプルと同様の挙動を示している。すなわち、IGZO膜上にタンゲステン膜が形成されたサンプルでは、タンゲステン膜にIGZO膜中の酸素が取り込まれることによりIGZO膜の低抵抗化が生じるのに対し、IGZO膜上に窒化チタン膜を形成したサンプルでは、IGZO膜から放出される酸素は窒化チタン膜を透過して上方に放出されることを示唆している。この結果は、実施例1で示したSIMS分析の結果とよく一致している。

30

#### 【0277】

図17（B）は、スパッタリング法により酸化シリコン膜を形成し、酸化シリコン膜上にスパッタリング法を用いてIGZO膜を形成し、IGZO膜に積層してスパッタリング法によりタンゲステン膜または窒化チタン膜を形成し、その後加熱処理を施した後に、タンゲステン膜または窒化チタン膜を除去して作製したサンプルについて、IGZO膜をエッチングした深さに対するシート抵抗値を測定した結果である。また、比較として、IGZO膜上に導電膜を形成していないサンプルも作製した。酸化シリコン膜は、シリコンをスパッタリングターゲットとし、O<sub>2</sub> 100%を成膜ガスとして反応性スパッタリング法（DCスパッタリング法）で形成した。なお、IGZO膜、タンゲステン膜、窒化チタン膜の形成及び除去は、上述と同様に行った。加熱処理は、N<sub>2</sub>雰囲気下で400 1hの条件で行った。

40

#### 【0278】

図17（B）では、図17（A）に示した結果と比較して、IGZO膜が低抵抗化される領域が厚さ方向に浅くなっていることが確認できた。これは、熱処理によって酸化シリコン膜からIGZO膜に酸素が供給されることにより、IGZO膜中の酸素欠損が低減され

50

ることによりIGZO膜が高抵抗化されたことを示している。このように、IGZO膜よりも下側に酸素放出可能な膜を用いることで、IGZO膜の低抵抗化される領域の厚さを制御することができることが分かった。

【0279】

以上により、タンゲステン膜などの酸素を取り込みやすい導電膜をIGZO膜と接して形成することにより、IGZO膜の該導電膜と接する近傍の領域を低抵抗化させることができることが確認できた。さらに、熱処理を施すことにより、IGZO膜中の低抵抗化する領域を深さ方向に拡大させることができることが確認できた。また、IGZO膜の近傍に酸素放出可能な膜を形成することにより、低抵抗化する領域の厚さを制御することができることが分かった。

10

【0280】

本実施例は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【実施例3】

【0281】

本実施例では、酸化物半導体膜にイオンインプランテーション法により酸素を添加したサンプルを作製し、そのTDS(Thermal Desorption Spectroscopy)分析、及び膜密度の評価を行った結果について説明する。

【0282】

まず、作製したサンプルについて説明する。HCl雰囲気下で熱酸化処理を施したシリコンウェハ上にプラズマCVD法により酸化窒化シリコン膜を形成し、次いで酸化窒化シリコン膜の表面をCMP法により平坦化処理を施した。その後、酸化窒化シリコン膜上にIGZO膜を形成し、IGZO膜に対してイオンインプランテーション法により酸素イオン(O<sup>+</sup>)を添加した。ここで、IGZO膜はIn:Ga:Zn=1:3:2(原子数比)をスペッタリングターゲットとし、Ar:O<sub>2</sub>=2:1(流量比)を成膜ガスとして用いてDCスペッタリング法で形成した。酸素イオンは、加速電圧5kV、ドーザ量1.0×10<sup>16</sup>ions/cm<sup>2</sup>の条件で行った。また、比較として酸素イオンの添加を行っていないサンプルも作製した。

20

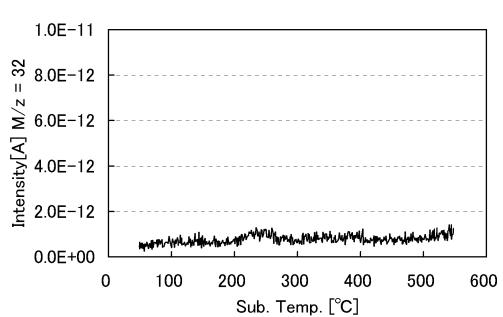

【0283】

図18(A)は、酸素イオンの添加を行っていないサンプルにおける、質量数32の気体の放出量を測定したTDS分析結果である。約50から約550までの範囲で質量数32の気体の放出ピークは確認されなかった。図18(B)は、酸素イオンの添加を行ったサンプルにおける、質量数32の気体の放出量を測定したTDS分析結果である。約400から約500付近において、顕著な放出ピークが確認された。これより、酸化物半導体膜に酸素イオンを添加することにより、酸化物半導体膜中に過剰な酸素を留めておくことができること、さらに、酸素イオンが添加された酸化物半導体膜を加熱することにより、酸化物半導体膜から過剰な酸素が放出されることが分かった。したがって、トランジスタのチャネルを形成する酸化物半導体層に接して、このような酸素が添加された酸化物半導体膜を設けることにより、これらに加熱処理を施すことにより、酸素が添加された酸化物半導体膜からチャネルを形成する酸化物半導体層に効果的に酸素を供給できる。

30

【0284】

また、酸素イオンの添加を行っていないサンプルと、酸素イオンの添加を行ったサンプルについて、酸化物半導体膜の膜密度をX線反射率測定法(XRR:X-Ray Reflectivity)を用いて評価した。

【0285】

まず、作製したサンプルについて説明する。HCl雰囲気下で熱酸化処理を施したシリコンウェハ上にプラズマCVD法により酸化窒化シリコン膜を形成し、該酸化窒化シリコン膜に対してイオンインプランテーション法により酸素イオン(O<sup>+</sup>)を添加し、次いで酸化窒化シリコン膜の表面をCMP法により平坦化処理を施した。その後、酸化窒化シリコン膜上にIGZO膜を形成し、IGZO膜に対してイオンインプランテーション法により

40

50

酸素イオン(  $O^+$  )を添加した。ここで、IGZO膜の形成、及びIGZO膜に対する酸素イオンの添加は上述と同様の条件で行った。酸化窒化シリコン膜への酸素イオンの添加は、加速電圧60kV、ドーズ量 $2.0 \times 10^{16}$  ions/cm<sup>2</sup>の条件で行った。また、比較として酸素イオンの添加を行っていないサンプルも作製した。

【0286】

XRRにより膜密度を測定した結果、酸素イオンの添加を行っていないサンプルでは、膜密度の値が $5.8\text{ g/cm}^3$ であり、酸素イオンの添加を行ったサンプルでは、膜密度の値が $5.6\text{ g/cm}^3$ であり、酸素イオンの添加により酸化物半導体膜の膜密度が低下することがわかった。これより、酸素イオンの添加によって酸化物半導体膜はより無秩序な原子配置となる、すなわち顕著な非晶質膜に改質することが可能であることが示唆される。例えば、酸化物半導体膜上に結晶性を有する酸化物半導体膜を積層して用いる場合、下層に異なる結晶構造を示す結晶性の酸化物半導体膜を用いると、上層に形成した酸化物半導体膜の結晶性が低下してしまうことがある。このような場合であっても、上層の酸化物半導体膜の形成前に、下層の酸化物半導体膜に酸素イオンを添加して非晶質化させることにより、結晶性が向上した酸化物半導体膜を上層に形成することができる。

【0287】

本実施例は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0288】

|       |            |    |

|-------|------------|----|

| 200   | 領域         | 20 |

| 302   | 酸素         |    |

| 310   | トランジスタ     |    |

| 320   | トランジスタ     |    |

| 330   | トランジスタ     |    |

| 340   | トランジスタ     |    |

| 350   | トランジスタ     |    |

| 400   | 基板         |    |

| 402   | 下地絶縁層      |    |

| 404   | 酸化物積層      | 30 |

| 404 a | 第1の酸化物層    |    |

| 404 b | 酸化物半導体層    |    |

| 404 c | 第2の酸化物層    |    |

| 405   | 領域         |    |

| 406 a | 第1のソース電極層  |    |

| 406 b | 第1のドレイン電極層 |    |

| 407   | 酸化物積層      |    |

| 407 a | 第1の酸化物層    |    |

| 407 b | 酸化物半導体層    |    |

| 407 c | 第2の酸化物層    | 40 |

| 408 a | 第2のソース電極層  |    |

| 408 b | 第2のドレイン電極層 |    |

| 410   | ゲート絶縁層     |    |

| 412   | ゲート電極層     |    |

| 412 a | 第1のゲート電極層  |    |

| 412 b | 第2のゲート電極層  |    |

| 414   | 保護絶縁層      |    |

| 422 a | 電極層        |    |

| 422 b | 電極層        |    |

| 424   | 層間絶縁層      | 50 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

(A)

(B)

【図18】

(A)

(B)

【図19】

【図20】

(A)

(B)

【図21】

【図22】

【図23】

【図24】

## 【図25】

## フロントページの続き

| (51)Int.Cl. |                  | F I    |               |

|-------------|------------------|--------|---------------|

| H 01 L      | 29/417 (2006.01) | H 01 L | 29/78 6 1 9 A |

| H 01 L      | 29/49 (2006.01)  | H 01 L | 27/088 B      |

| H 01 L      | 29/423 (2006.01) | H 01 L | 27/088 H      |

| H 01 L      | 29/788 (2006.01) | H 01 L | 27/088 E      |

| H 01 L      | 29/792 (2006.01) | H 01 L | 21/28 3 0 1 B |

|             |                  | H 01 L | 29/50 M       |

|             |                  | H 01 L | 29/58 G       |

|             |                  | H 01 L | 29/78 3 7 1   |

審査官 市川 武宜

(56)参考文献 特許第5 9 5 1 4 4 2 (JP, B2)

特開2 0 1 1 - 2 4 3 7 4 5 (JP, A)

特開2 0 1 1 - 2 2 8 6 9 5 (JP, A)

特開2 0 1 2 - 1 3 4 4 7 5 (JP, A)

特開2 0 1 1 - 1 2 4 3 6 0 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 2 9 / 7 8 6

H 01 L 2 1 / 2 8

H 01 L 2 1 / 3 3 6

H 01 L 2 1 / 8 2 3 4

H 01 L 2 7 / 0 8 8

H 01 L 2 9 / 4 1 7

H 01 L 2 9 / 4 2 3

H 01 L 2 9 / 4 9

H 01 L 2 9 / 7 8 8

H 01 L 2 9 / 7 9 2