(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4971069号

(P4971069)

(45) 発行日 平成24年7月11日(2012.7.11)

(24) 登録日 平成24年4月13日(2012.4.13)

(51) Int.Cl.

F 1

HO3F 3/24 (2006.01)

HO3F 3/72 (2006.01)HO3F 3/24

HO3F 3/72

請求項の数 2 (全 8 頁)

(21) 出願番号 特願2007-204915 (P2007-204915)

(22) 出願日 平成19年8月7日 (2007.8.7)

(65) 公開番号 特開2009-44281 (P2009-44281A)

(43) 公開日 平成21年2月26日 (2009.2.26)

審査請求日 平成22年8月6日 (2010.8.6)

(73) 特許権者 000004330

日本無線株式会社

東京都三鷹市下連雀5丁目1番1号

(74) 代理人 100075258

弁理士 吉田 研二

(74) 代理人 100096976

弁理士 石田 純

(72) 発明者 伊藤 恵二郎

東京都三鷹市下連雀5丁目1番1号 日本

無線株式会社内

(72) 発明者 倉持 孝雄

東京都三鷹市下連雀5丁目1番1号 日本

無線株式会社内

最終頁に続く

(54) 【発明の名称】 FET増幅回路

## (57) 【特許請求の範囲】

## 【請求項 1】

ソースが接地されたFET増幅素子と、

FET増幅素子のゲートソース間に並列に接続されたバイアス抵抗と、

FET増幅素子のドレイン又はソースに直列に接続されFET増幅素子のドレインソース間電流を検出するモニタ素子と、ゲート側に接続されたバイアス抵抗端子に接続されモニタ素子により検出されるドレインソース間電流が定電流化するバイアス電圧がFET増幅素子のゲートソース間に印加されるようバイアス抵抗に電流を供給する電流供給源と、

を含む電流回路と、

所定のタイミングでオンオフが切り替わる制御信号に応じて電流回路の動作のオンオフを切り替える電源スイッチと、

を備え、

制御信号がオンのときに、FET増幅素子がゲートに入力された高周波信号を増幅してドレインから出力するFET増幅回路であって、

ゲート側に接続されたバイアス抵抗端子と所定の電源との間に直列に接続されたキャパシタと電圧印加スイッチとを含み、制御信号がオンのときに電圧印加スイッチがオンし、これにより所定の電源からバイアス抵抗にキャパシタを介して過渡電流を流してFET増幅素子のゲートソース間のバイアス電圧を上げるバイアス急昇圧回路と、

バイアス抵抗に並列に接続された電圧降下スイッチを含み、制御信号がオフのときに電圧降下スイッチがオンし、これによりFET増幅素子のゲートソース間のバイアス電圧を

10

20

下げるバイアス急降圧回路と、

を備えることを特徴とする F E T 増幅回路。

【請求項 2】

請求項 1 に記載の F E T 増幅回路において、

前記キャパシタと前記電圧印加スイッチとの間の経路に一端が接続され、他端が接地さ

れた抵抗を備えることを特徴とする F E T 増幅回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力された高周波信号を増幅して出力する F E T 増幅回路に関する。

10

【背景技術】

【0002】

T D D (Time Division Duplex) 方式を採用する無線通信システムの一例として、良好な無線データ通信サービスを低コストで実現する移動体通信方式の P H S (Personal Handy-phone System) がある。この P H S の変調方式には、Q P S K (Quadrature Phase Shift Keying) 方式が用いられている。一般的に、Q P S K 方式のような振幅情報の伝達が必要な信号の増幅には線形性が要求され、その増幅回路はバイアス電流を予め流しておく A 級や A B 級の動作クラスのものが用いられている（特許文献 1）。また、温度などにより、その動作クラスに影響が与えられないように増幅素子にはバイアス電流を定電流化する電流回路が取り付けられている。

20

【0003】

一方、前述したように P H S では、その複信方式に T D D 方式が用いられている。このため、増幅回路は、その動作時間の半分は受信のための待機時間となり、高周波信号の増幅に用いられないことがある。このような待機時間に増幅素子に対してバイアス電流を流し続けるのは、受信系へのノイズ混入を避けるという点及び省電力化という点から好ましくなく、一般的な T D D 方式における増幅回路では、高周波信号の増幅が必要なときだけバイアス電流が流れるように構成されている。

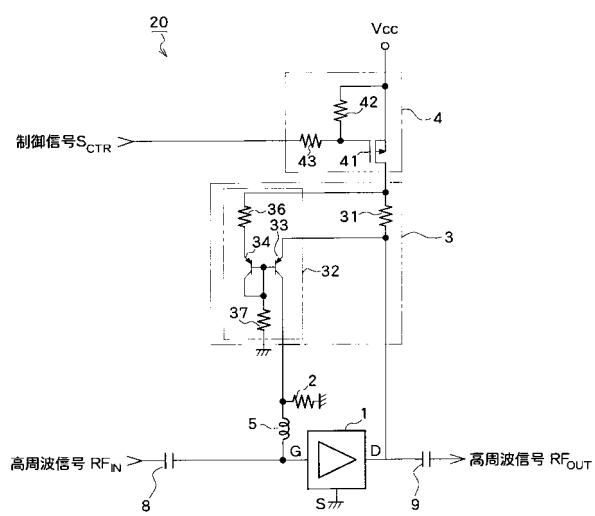

【0004】

以下、従来の増幅回路について説明する。図 2 は、従来の F E T 増幅回路 20 の回路図である。図 2 に示す F E T 増幅回路 20 は、F E T 増幅素子 1 と、バイアス抵抗 2 と、電流供給回路 3 と、電源スイッチ 4 と、を備えている。また、インダクタ 5 はデカップリング用のコイルまたはインピーダンス線路であり、キャパシタ 8 及び 9 は D C カット用キャパシタである。

30

【0005】

F E T 増幅素子 1 は、ゲートから入力された高周波信号を増幅してドレインから出力する L D - M O S F E T であり、そのソースが接地されている。バイアス抵抗 2 は、後述する電流供給回路 3 から供給される電流に応じたバイアス電圧を F E T 増幅素子 1 のゲートソース間に印加するための抵抗であり、F E T 増幅素子 1 のゲートソース間に並列に接続されている。

【0006】

電流供給回路 3 は、モニタ抵抗 31 と、電流供給源 32 と、を備えている。モニタ抵抗 31 は、F E T 増幅素子 1 のドレインソース間電流を検出するための抵抗であり、F E T 増幅素子 1 のドレインに直列に接続されている。電流供給源 32 は、トランジスタ 33 及び 34 と、抵抗 36 及び 37 と、を備えており、モニタ抵抗 31 に流れる電流に応じてバイアス抵抗 2 に電流を供給する。この電流供給源 32 は、モニタ抵抗 31 に発生する電圧と、トランジスタ 33 のベースエミッタ間電圧と、抵抗 37 に発生する電圧と、を合わせた電圧値が一定であり、モニタ抵抗 31 に流れる電流と抵抗 2 に流れる電流とが差動の関係にある。このため、電流供給回路 32 は、モニタ抵抗 31 に流れる電流が増えるとバイアス抵抗 2 に供給する電流を減らし、モニタ抵抗 31 に流れる電流が減るとバイアス抵抗 2 に供給する電流を増やして、モニタ抵抗 31 に流れる電流を定電流化させる。

40

50

## 【0007】

電源スイッチ4は、スイッチングFET41と、抵抗42及び43と、を備えている。スイッチングFET41は、電流供給回路3の動作のオンオフをスイッチングするためのpチャネルFETであり、電源V<sub>cc</sub>と電流供給回路3のモニタ抵抗31との間に接続されている。この電源スイッチ4は、PHS等の無線基地局内でTDD周期に同期した制御信号S<sub>CTR</sub>がローレベル(オン)のときにスイッチングFET41がオンして電流供給回路3に電源電圧を供給し、制御信号S<sub>CTR</sub>がハイレベル(オフ)のときにスイッチングFET41がオフして電流供給回路3に電源電圧の供給を止める。また、抵抗42及び43は、スイッチングFET41に電圧を印加するための分圧抵抗である。FET增幅回路20は、このように制御信号S<sub>CTR</sub>がオフのときに、電流供給回路3への電源電圧の供給が止まりその動作がオフするため、前述したような待機時間に電流を消費せず受信中のノイズ混入回避や省電力化を実現している。10

## 【0008】

【特許文献1】特開2001-244757号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0009】

一般的に、FET増幅素子は、そのゲートに寄生容量を有しており、またバイアス回路のデカップリング用のコンデンサが付加されており、そのオンオフには容量成分に対する電荷の充放電が必要になる。また、前述した電流供給回路3の動作抵抗及び、FET増幅素子のゲートソース間に並列に接続されたバイアス抵抗2などの抵抗成分を持っており、その時定数は大きな値となる。このため、ゲートバイアス回路の容量成分への電荷の充放電速度が低下し、これに伴いFET増幅素子のオンオフのスイッチング速度が低下する。20

## 【0010】

このため、FET増幅素子のスイッチング速度の向上のためには何らかの対策が必要である。本発明の目的は、上記課題を解決することであり、FET増幅素子のスイッチング速度をより高速化したFET増幅回路を実現することにある。

## 【課題を解決するための手段】

## 【0011】

本発明は、ソースが接地されたFET増幅素子と、FET増幅素子のゲートソース間に並列に接続されたバイアス抵抗と、FET増幅素子のドレイン又はソースに直列に接続されFET増幅素子のドレインソース間電流を検出するモニタ素子と、ゲート側に接続されたバイアス抵抗端子に接続されモニタ素子により検出されるドレインソース間電流が定電流化するバイアス電圧がFET増幅素子のゲートソース間に印加されるようバイアス抵抗に電流を供給する電流供給源と、を含む電流回路と、所定のタイミングでオンオフが切り替わる制御信号に応じて電流回路の動作のオンオフを切り替える電源スイッチと、を備え、制御信号がオンのときに、FET増幅素子がゲートに入力された高周波信号を増幅してドレインから出力するFET増幅回路であって、ゲート側に接続されたバイアス抵抗端子と所定の電源との間に直列に接続されたキャパシタと電圧印加スイッチとを含み、制御信号がオンのときに電圧印加スイッチがオンし、これにより所定の電源からバイアス抵抗にキャパシタを介して過渡電流を流してFET増幅素子のゲートソース間のバイアス電圧を上げるバイアス急昇圧回路と、バイアス抵抗に並列に接続された電圧降下スイッチを含み、制御信号がオフのときに電圧降下スイッチがオンし、これによりFET増幅素子のゲートソース間のバイアス電圧を下げるバイアス急降圧回路と、を備えることを特徴とする。3040

## 【発明の効果】

## 【0012】

本発明によれば、FET増幅素子のスイッチング速度をより高速化したFET増幅回路を実現することができる。

## 【発明を実施するための最良の形態】

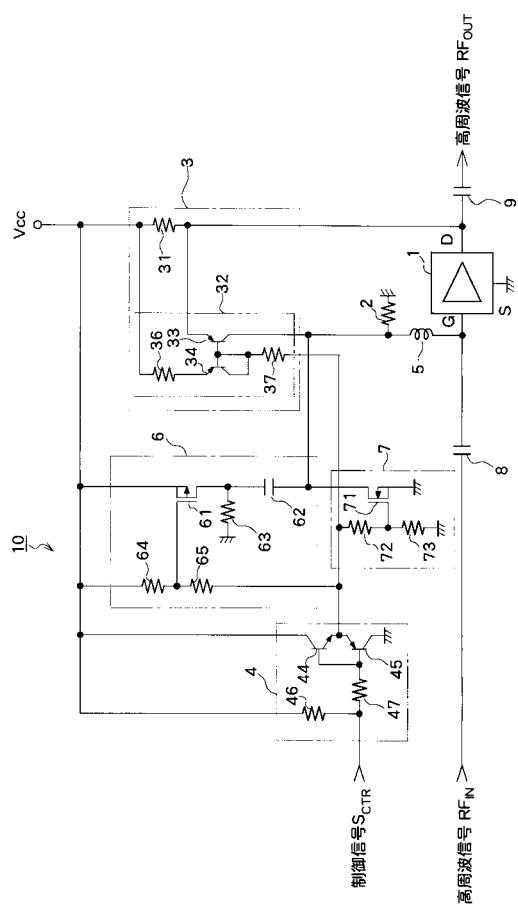

## 【0013】

以下、本発明を実施するための最良の形態について図面を用いて説明する。図1は、本実施形態に係るFET増幅回路10の回路図である。なお、従来のFET増幅回路20と同じ若しくは同様な構成には同一の符号を用いるものとする。本実施形態に示すFET増幅回路10は、あらたに、バイアス急昇圧回路6と、バイアス急降圧回路7と、を備えている。

【0014】

バイアス急昇圧回路6は、スイッチングFET61と、キャパシタ62と、抵抗63と、抵抗64及び65と、を備えている。このバイアス急昇圧回路6では、スイッチングFET61と、キャパシタ62と、が電源Vccとバイアス抵抗2との間に直列に接続されている。そして、制御信号SCTRがオンのときスイッチングFET61がオンし、これにより電源Vccからバイアス抵抗2に過渡電流を流すことにより、FET増幅素子1のゲートソース間のバイアス電圧を上げる構成となっている。10

【0015】

以下、バイアス急昇圧回路6の構成について詳細に説明する。スイッチングFET61は、pチャネルFETであり、そのソースが電源Vccに接続されている。キャパシタ62は、一方の端子がスイッチングFET61のドレインに接続され、他方の端子がバイアス抵抗2の端子（FET増幅素子1のゲート側に接続された端子）に接続されている。

【0016】

抵抗63は、一方の端子がスイッチングFET61のドレイン側に接続され、他方の端子が接地されている。抵抗64及び65は、スイッチングFET61に電圧を印加するための分圧抵抗である。この抵抗64は、一方の端子が電源Vccに接続され、他方の端子がスイッチングFET61のゲートに接続されている。また、抵抗65は、一方の端子がスイッチングFET61のゲートに接続されている。後述するように、この抵抗64及び65に印加される電圧に応じてスイッチングFET61のオンオフが制御される。20

【0017】

バイアス急降圧回路7は、スイッチングFET71と、抵抗72及び73と、を備えている。このバイアス急降圧回路7は、スイッチングFET71がバイアス抵抗2に並列に接続されており、制御信号SCTRがオフのときにスイッチングFET71がオンし、これによりFET増幅素子1のゲートソース間のバイアス電圧を下げる構成となっている。抵抗72及び73は、スイッチングFET71に電圧を印加するための分圧抵抗である。この抵抗72は、一方の端子が電流供給回路3の抵抗37に接続され、他方の端子がスイッチングFET71のゲートに接続されている。また、抵抗73は、一方の端子がスイッチングFET71のゲートに接続され、他方の端子が接地している。後述するように、この抵抗72及び73に印加される電圧に応じてスイッチングFET71のオンオフが制御される。30

【0018】

以下、バイアス急降圧回路7の構成について詳細に説明する。スイッチングFET71は、nチャネルFETであり、ドレインがバイアス抵抗2の端子（FET増幅素子1のゲート側に接続された端子）に接続され、ソースが接地されている。抵抗72は、一方の端子が抵抗65に接続され、他方の端子がスイッチングFET71のゲートに接続されている。また、抵抗73は、一方の端子がスイッチングFET71のゲートに接続され、他方の端子が接地されている。40

【0019】

また、本実施形態に示すFET増幅回路10では、電源スイッチ4は、電流供給回路3の下流側に接続されている。この電源スイッチ4は、トランジスタ44及び45と、抵抗46及び47と、を備えている。

【0020】

トランジスタ44は、NPN型バイポーラトランジスタであり、コレクタが電源Vccに接続され、エミッタが抵抗65及び72の接続点に接続されている。トランジスタ45は、PNP型バイポーラトランジスタであり、エミッタがトランジスタ44のエミッタに接続されている。50

接続され、ベースがトランジスタ 4 4 のベースに接続され、コレクタが接地されている。抵抗 4 6 は、一方の端子が電源 Vcc に接続されている。

【0021】

抵抗 4 7 は、一方の端子が抵抗 4 6 の他方の端子に接続され、他方の端子がトランジスタ 4 4 及び 4 5 のベースに接続されている。なお、この抵抗 4 6 及び 4 7 の接続点に制御信号が入力される。以下動作について説明する。

【0022】

次に本実施形態に係る FET 増幅回路 10 の動作について説明する。なお、FET 増幅回路 10 の動作については、「制御信号  $S_{CTR}$  がオンのとき」と「制御信号  $S_{CTR}$  がオフのとき」に分けて説明する。

10

【0023】

「制御信号  $S_{CTR}$  がオンのとき」

図 1 に示す FET 増幅回路は、制御信号  $S_{CTR}$  がローレベル（オン）のとき、電流供給回路 3 の動作がオンになる。まず、制御信号  $S_{CTR}$  がローレベルになると、電源スイッチ 4 のトランジスタ 4 5 のエミッタ電位が制御信号  $S_{CTR}$  の入力端子よりも電位が高くなり、トランジスタ 4 5 にベース電流が流れる。また、このベース電流に応じた電流がトランジスタ 4 5 のエミッタコレクタ間に流れる。すなわち、トランジスタ 4 5 のエミッタコレクタ間の抵抗値が下がり、ショートに近い状態となる。なお、このときトランジスタ 4 4 のコレクタエミッタ間には電流が流れない。すなわち、トランジスタ 4 4 のエミッタコレクタ間の抵抗値は開放に近い状態となる。

20

【0024】

そして、トランジスタ 4 5 のエミッタコレクタ間に電流が流れることにより、電流供給回路 3 は、その動作がオンする。このように動作がオンした電流供給回路 3 は、バイアス抵抗 2 への電流の供給及び FET 増幅素子 1 のゲートバイアス回路の容量成分への充電を始める。

【0025】

ここで、バイアス急昇圧回路 6 のスイッチング FET 6 1 は、制御信号  $S_{CTL}$  がローレベルになったことにより、そのゲート電位が下がる。また、これにより、スイッチング FET 6 1 は、オフする。なお、このときのスイッチング FET 7 1 はオフである。スイッチング FET 6 1 がオフしたことにより、電源 Vcc からキャパシタ 6 2 及びバイアス抵抗 2 が直列接続された閉回路（CR 直列回路）が形成される。

30

【0026】

このように、電源 Vcc からキャパシタ 6 2 及びバイアス抵抗 2 が直列接続された閉回路が形成されることにより、バイアス抵抗 2 には過渡電流が流れ、FET 増幅回路 1 のゲートソース間にバイアス電圧が印加される。

【0027】

そして、電流供給回路 3 によりバイアス抵抗 2 に定電流が供給され、定常的な動作に移行する。このとき、電流供給回路 3 は、モニタ抵抗 3 1 に流れる電流が増えるとバイアス抵抗 2 に供給する電流を減らし、モニタ抵抗 3 1 に流れる電流が減るとバイアス抵抗 2 に供給する電流を増やして、モニタ抵抗 3 1 に流れる電流を定電流化させる。これにより、FET 増幅回路 1 は、制御信号  $S_{CTR}$  がオンになると直ぐに FET 増幅素子 1 を動作させてから定常状態にすることができる。

40

【0028】

「制御信号  $S_{CTR}$  がオフのとき」

次に、図 1 に示す FET 増幅回路 10 は、制御信号  $S_{CTR}$  がハイレベル（オフ）のとき、電流供給回路 3 の動作がオフになる。制御信号  $S_{CTR}$  がハイレベルになると、電源スイッチ 4 のトランジスタ 4 4 のエミッタ電位が制御信号  $S_{CTR}$  の入力端子よりも電位が低くなり、トランジスタ 4 4 にベース電流が流れる。また、このベース電流に応じた電流がトランジスタ 4 4 のエミッタコレクタ間に流れる。すなわち、トランジスタ 4 4 のエミッタコレクタ間の抵抗値が下がり、ショートに近い状態となる。なお、このときトラン

50

ジスタ45のコレクタエミッタ間には電流が流れない。すなわち、トランジスタ45のコレクタエミッタ間は開放状態（又はそれに近い状態）になる。

【0029】

そして、トランジスタ45のエミッタコレクタ間に電流が流れず、かつ、トランジスタ44のエミッタコレクタ間の電位差が小さく（ゼロ近く）なることにより、電流供給回路3は、その動作がオフする。このように動作がオフした電流供給回路3は、バイアス抵抗2への電流の供給を止める。

【0030】

ここで、急降圧回路7のスイッチングFET71は、制御信号 $S_{CTR}$ がハイレベルになったことにより、そのゲート電位が上がる。また、これにより、スイッチングFET71は、オンする。なお、このときのスイッチングFET61はオフである。スイッチングFET71がオンしたことにより、バイアス抵抗2のゲート側端子は接地電位（すなわち0V）になる。

10

【0031】

このように、バイアス抵抗2のゲート側端子は接地電位になる際に、FET増幅素子1のゲートバイアス回路の容量成分から電荷が急放電される。また、ゲート電位が急激に下がったFET増幅素子1は、次の動作まで待機する、これにより、FET増幅回路1は、制御信号 $S_{CTR}$ がオフになると直ぐにFET増幅素子1の動作をオフさせることができる。

【0032】

20

以上説明したように、本実施形態に係るFET増幅回路は、ゲート側に接続されたバイアス抵抗端子と所定の電源との間に直列に接続されたキャパシタと電圧印加スイッチとを含み、制御信号がオンのときに電圧印加スイッチがオンし、これにより所定の電源からバイアス抵抗に過渡電流を流してFET増幅素子のゲートソース間のバイアス電圧を急速に引き上げるバイアス急昇圧回路と、バイアス抵抗に並列に接続された電圧降下スイッチを含み、制御信号がオフのときに電圧降下スイッチがオンし、これによりFET増幅素子のゲートソース間のバイアス電圧を急速に低下させるバイアス急降圧回路と、を備えることにより、FET増幅素子のスイッチング速度をより高速化したFET増幅回路を実現することができる。

【0033】

30

なお、本発明は、TDD方式に限定されるものではなく、他の時分割方式（TDMなど）に用いられてもよい。また、バイアス急昇圧回路のキャパシタ及びバイアス抵抗の時定数は、その仕様に合わせて隨時設計するのが望ましい。さらに、バイアス抵抗2の接地側接続を負電源に接続し、各回路の電位を調整することによりGaaSなど負バイアスの必要なFET増幅素子にも適用可能である。

【図面の簡単な説明】

【0034】

【図1】本実施形態に係るFET増幅回路の構成を示す図である。

【図2】従来のFET増幅回路の構成を示す図である。

【符号の説明】

40

【0035】

1 FET増幅素子、2 バイアス抵抗、3 電流供給回路、4 電源スイッチ、5 インダクタ、6 バイアス急昇圧回路、7 バイアス急降圧回路、8, 9 キャパシタ、10, 20 FET増幅回路。

【図1】

【図2】

---

フロントページの続き

(72)発明者 長峰 正治

東京都三鷹市下連雀五丁目1番1号 日本無線株式会社内

(72)発明者 山口 剛

東京都三鷹市下連雀五丁目1番1号 日本無線株式会社内

(72)発明者 古木 邦彦

東京都三鷹市下連雀五丁目1番1号 日本無線株式会社内

審査官 高橋 義昭

(56)参考文献 特開2001-284974(JP,A)

特開平07-162241(JP,A)

実開昭56-108609(JP,U)

(58)調査した分野(Int.Cl., DB名)

H 03 F 1/00 3/24 3/26 3/30 3/72