## (10) **DE 10 2013 104 196 A1** 2013.11.07

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2013 104 196.5

(22) Anmeldetag: 25.04.2013

(43) Offenlegungstag: 07.11.2013

(51) Int Cl.: **G11C 16/10** (2013.01)

> G06F 12/02 (2013.01) G06F 13/00 (2013.01)

(30) Unionspriorität:

10-2012-0047503 04.05.2012 KR 10-2012-0071715

02.07.2012

KR

(71) Anmelder:

Samsung Electronics Co., Ltd., Kyonggi, KR

(74) Vertreter:

Kuhnen & Wacker Patent- und Rechtsanwaltsbüro, 85354, Freising, DE

Jun, Byung Hei, Seoul, Dongjak-gu, KR; Kwak, Dong-Hun, Kyonggi, Hwaseong-si, KR

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

(54) Bezeichnung: System und Verfahren mit dreidimensionaler nichtflüchtiger Speichervorrichtung und Direktzugriffsspeicher

(57) Zusammenfassung: Programmierverfahren für ein Speichersystem mit einen dreidimensionalen nichtflüchtigen Speicher mit Multi-Level-Speicherzellen und einem Direktzugriffsspeicher. Das Verfahren verwendet den Direktzugriffsspeicher, um auf verschiedene Arten ausgewählte Bits von Multi-Bit-Daten während des Programmierens einer Zeile von Speicherzellen in dem dreidimensionalen nichtflüchtigen Speicher zu speichern.

#### **Beschreibung**

Bezugnahme auf zugehörige Anmeldungen

**[0001]** Es wir die Priorität der Koreanischen Patentanmeldungen Nr. 10-2012-0071715 eingereicht am 02. Juli 2012 und Nr. 10-2012-0047503, deren Gegenstand durch Bezugnahme mit umfasst ist in Anspruch genommen.

#### Hintergrund

[0002] Das erfindungsgemäße Konzept bezieht sich auf Speichersysteme, Halbleiterspeichervorrichtungen und Verfahren zum Programmieren von Halbleiterspeichervorrichtungen. Insbesondere bezieht sich das erfindungsgemäße Konzept auf Speichersysteme mit einer dreidimensionalen nichtflüchtigen Speichervorrichtung und Verfahren um diese zu programmieren.

[0003] Halbleiterspeichervorrichtungen können entsprechend ihrer Betriebsart als flüchtig oder nichtflüchtig klassifiziert werden. Flüchtige Speichervorrichtungen verlieren ohne Betriebsspannung ihre Daten und umfassen den statischen RAM (SRAM), dynamischen RAM (DRAM), synchronen DRAM (SDRAM) und Ähnliche. Nichtflüchtige Speicher können auch ohne angelegte Betriebsspannung die Daten erhalten und umfassen Nur-Lesespeicher (ROM), programmierbare Speicher (PROM), elektrisch programmierbare Speicher (EPROM), elektrisch lösch- und programmierbare ROM (EE-PROM) und Flashspeicher, Phasen-Änderungsspeicher (PRAM), magnetische RAM (MRAM), Widerstandsspeicher (RRAM), ferroelektrische Speicher (FRAM) und Ähnliche.

**[0004]** Insbesondere Flashspeicher haben sich zu bedeutsamen nichtflüchtigen Speichern entwickelt und umfassen NOR Typen und NAND Typen.

[0005] In den letzten Jahren wurden sogenannte dreidimensionale Speicherarchitekturen und Strukturen vorgeschlagen um die Integrationsdichte von Flashspeichern weiter zu erhöhen. Ganz allgemein umfassen dreidimensionale Flashspeicher eine oder mehrere Halbleiterstrukturen bei denen Speicherzellen auf einem grundsätzlichen Substrat gestapelt sind. Verglichen mit gewöhnlichen zweidimensionalen (oder planaren) Speichern, bietet der dreidimensionale Speicher Vorteile im Hinblick auf Integration und Kosten. Jedoch muss die Zuverlässigkeit der dreidimensionalen Speicher verbessert werden.

### Zusammenfassung

[0006] Gemäß einer Ausführungsform umfasst das erfindungsgemäße Konzept ein Verfahren zum Programmieren eines Speichersystems mit einem drei-

dimensionalen nichtflüchtigen Speicher mit einem Seitenpuffer und Multi-Levelspeicherzellen die entlang einer Zeilenrichtung angeordnet sind, und einem Direktzugriffspeicher. Das Verfahren umfasst; das Empfangen extern bereitgestellter Programmdaten, das Ermitteln ob die empfangenen Programmdaten alles Daten sind, die zu den Speicherzellen gehören und Multi-Pagedaten entsprechen, und nach dem Erfassen, dass die empfangenen Programmdaten komplette Daten sind, das Programmieren der Programmdaten durch das Laden der Multi-Pagedaten in den Seitenpuffer und dann gleichzeitiges Programmieren der Multi-Pagedaten von dem Seitenpuffer in die Speicherzellen, und ansonsten Speichern der empfangenden Programmdaten in dem Direktzugriffspeicher.

[0007] Gemäß einer anderen Ausführungsform stellt das erfindungsgemäße Konzept ein Verfahren zur Programmierung eines Speichersystems bereit mit einem Controller, einem dreidimensionalen nichtflüchtigen Speicher mit Seitenpuffer und Multi-Levelspeicherzellen die entlang einer Zeilenrichtung angeordnet sind, und einen Zuführzugriffsspeicher. Das Verfahren umfasst; das Empfangen extern bereitgestellter, Multi-Page-Programmdaten in dem Controller, das Speichern der empfangenen Programmdaten in dem Direktzugriffspeicher bis die in dem Direktzugriffspeicher gespeicherten Programmdaten komplette Daten sind die mit den Speicherzellen verknüpft sind und entsprechend der Multi-Pagedaten, Laden der Multi-Pagedaten in den Seitenpuffer, und gleichzeitig Programmieren der Multi-Pagedaten des Seitenpuffers in die Speicherzellen.

[0008] Gemäß einer anderen Ausführungsform umfasst das erfindungsgemäße Konzept ein Verfahren zum Programmieren eines Speichersystems mit einem Controller, einem dreidimensionalen nichtflüchtigen Speicher mit einem Seitenpuffer und N-Bit Speicherzellen die entlang einer Zeilenrichtung angeordnet sind und einem Direktzugriffspeicher. Das Verfahren umfasst; das Empfangen eines ersten Bit von N-Bitdaten in dem Controller und Speichern des ersten Bit der N-Bitdaten in den Direktzugriffspeicher, und nach dem Speichern des ersten Bit der N-Bitdaten in dem Direktzugriffspeicher, Empfangen eines zweiten Bit von N-Bitdaten in dem Controller, wobei die Kombination von wenigstens dem ersten Bit und zweitem Bit der N-Bitdaten alles Daten sind die mit den Speicherzellen verknüpft sind und Multi-Pagedaten entsprechen, Laden der Multi-Pagedaten in den Seitenpuffer, wobei das Laden der Multi-Pagedaten in den Seitenpuffer das Übertragen des ersten Bit der N-Bitdaten von dem Direktzugriffspeicher in den Seitenspeicher umfasst und das direkte Übertragen des zweiten Bit der N-Bitdaten von dem Controller zu dem Seitenpuffer durch Umgehung des Direktzugriffspeichers und gleichzeitiges Programmieren der Multi-Pagedaten von dem Seitenpuffer in den Speicherzellen.

[0009] Gemäß einer weiteren Ausführungsform umfasst das erfindungsgemäße Konzept ein Verfahren zum Programmieren eines Speichersystems mit einem Controller, einem dreidimensionalen nichtflüchtigen Speicher mit einem Seitenpuffer und entlang einer Zeilenrichtung angeordneter N-Bitspeicherzellen, und einem Direktzugriffspeicher. Das Verfahren umfasst; das Empfangen eines ersten Bit von N-Bitdaten in dem Controller, direktes Laden des ersten Bit der N-Bitdaten in den Seitenpuffer ohne durch den Direktzugriffspeicher hindurchzugehen und dann das Programmieren des ersten Bit der N-Bitdaten in die Speicherzellen, nach dem Programmieren des ersten Bit der N-Bitdaten in die Speicherzellen Empfangen eines zweiten Bit von N-Bitdaten in dem Controller und Speichern des zweiten Bit der N-Bitdaten in dem Direktzugriffspeicher, und nach dem Speichern des zweiten Bit der N-Bitdaten in dem Direktzugriffspeicher übertragen des zweiten Bit der N-Bitdaten von dem Direktzugriffspeicher in den Seitenspeicher, Empfangen eines dritten Bit von N-Bitdaten in dem Controller und direktes Laden des dritten Bit des N-Bitdaten in den Seitenspeicher ohne durch den Direktzugriffspeicher hindurchzugehen, wobei die Kombination des ersten Bit, des zweiten Bit und des dritten Bit der N-Bitdaten Gesamtdaten in Verbindung mit den Speicherzellen entspricht und mit den Multi-Seitendaten übereinstimmt sind und gleichzeitiges Programmieren des zweiten Bit und dritten Bit der N-Bitdaten von dem Seitenpuffer in die Speicherzellen.

[0010] Gemäß einer weiteren Ausführungsform umfasst das erfindungsgemäße Konzept ein Verfahren zum Programmieren eines Speichersystems mit einem Controller, einem dreidimensionalen nichtflüchtigen Speicher mit einem Seitenpuffer, N-Bitspeicherzellen, die entlang einer Zeilenrichtung angeordnet sind und einem Direktzugriffsspeicher. Das Verfahren umfasst; das Empfangen eines ersten Bit von N-Bitdaten in den Controller und Speichern des ersten Bit der N-Bitdaten in dem Direktzugriffsspeicher, Empfangen eines zweiten Bit von N-Bitdaten in dem Controller und Speichern des zweiten Bit von N-Bitdaten in dem Direktzugriffsspeicher, gleichzeitig Laden des ersten Bit und zweiten Bit der N-Bitdaten von dem Direktzugriffsspeicher in den Seitenpuffer, und dann gleichzeitiges Programmieren des ersten Bit und zweiten Bit der N-Bitdaten von dem Seitenpuffer in die Speicherzellen, Empfangen eines dritten Bit von N-Bitdaten in dem Controller nach dem gleichzeitigen Programmieren des ersten Bit und des zweiten Bits der N-Bitdaten von dem Seitenpuffer in die Speicherzellen, Speichern des dritten Bit der N-Bitdaten in dem Direktzugriffsspeicher, Laden des dritten Bit der N-Bitdaten von dem Direktzugriffsspeicher in den Seitenpuffer, und dann Programmieren des dritten Bit der N-Bitdaten von dem Seitenpuffer in die Speicherzellen, wobei die Kombination des ersten Bit, des zweiten Bit und des dritten Bit der N-Bitdaten alles mit den Speicherzellen verbundene Gesamtdaten sind und Multi-Seitendaten entsprechen.

#### Kurze Beschreibung der Figuren

**[0011]** Die oben beschriebenen und andere Merkmale und Eigenschaften dieses erfindungsgemäßen Konzepts werden unter Berücksichtigung der folgenden Beschreibung mit Bezugnahme auf die beiliegenden Figuren noch klarer.

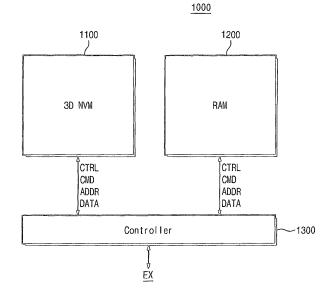

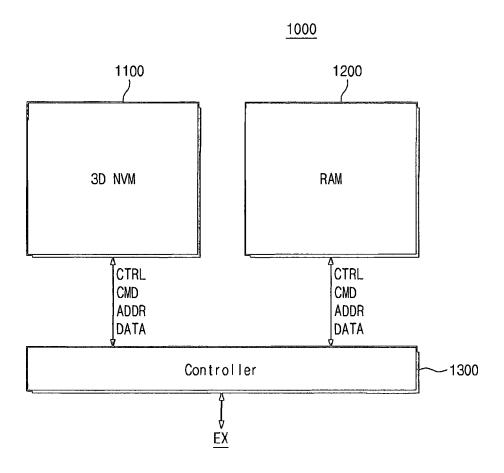

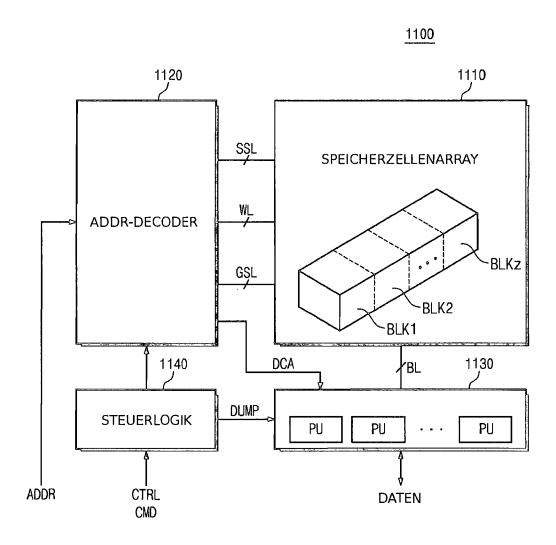

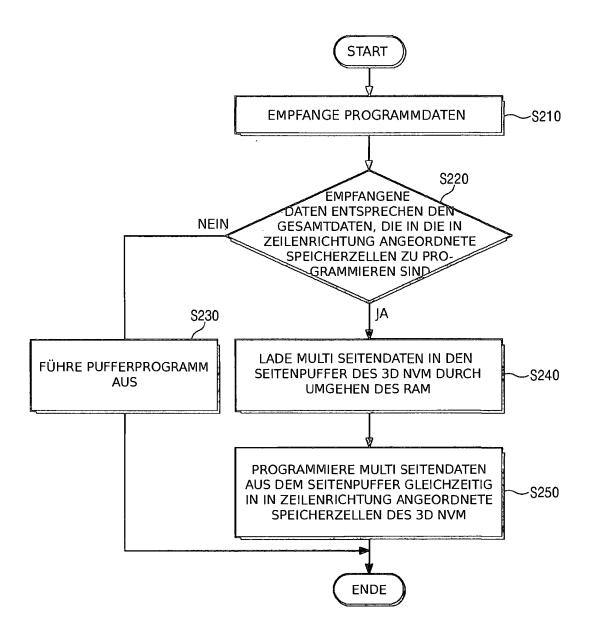

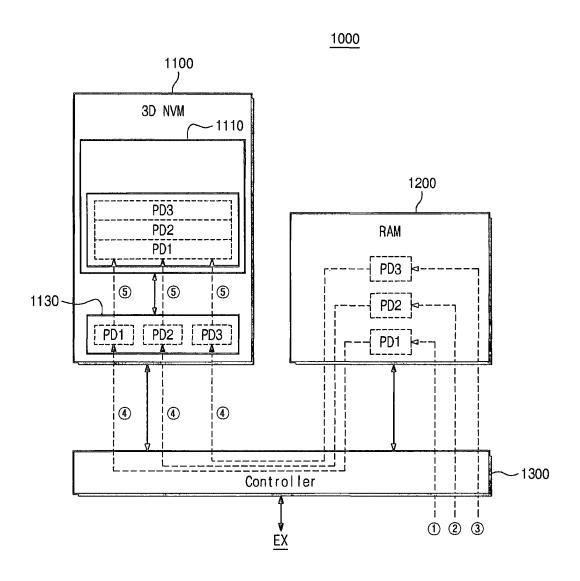

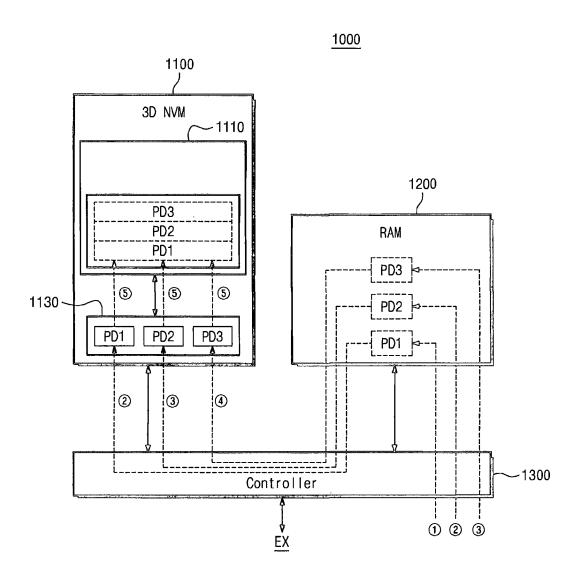

**[0012]** Fig. 1 zeigt ein Blockdiagramm, das ein Speichersystem gemäß einer Ausführungsform des erfindungsgemäßen Konzepts zeigt.

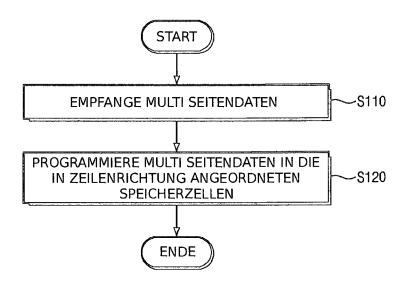

**[0013]** Fig. 2 zeigt ein Flussdiagramm, das allgemein ein Programmierverfahren gemäß einer Ausführungsform des erfindungsgemäßen Konzepts zusammenfasst.

[0014] Fig. 3 zeigt ein Blockdiagramm, das den dreidimensionalen nichtflüchtigen Speicher (1100) aus Fig. 1 näher darstellt.

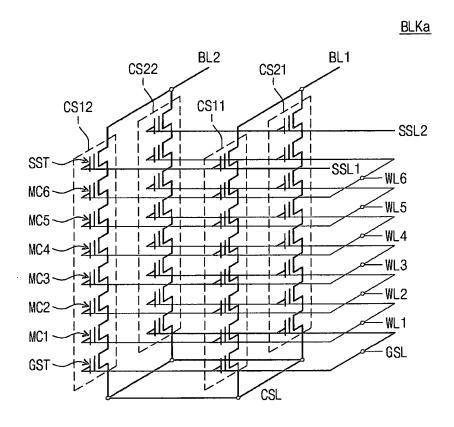

**[0015]** Fig. 4 zeigt ein Schaltungsdiagramm, das einen Speicherblock der Vielzahl der Speicherblöcke in dem Speicherzellenarray aus Fig. 3 darstellt.

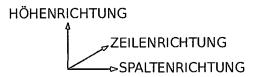

[0016] Fig. 5 zeigt eine perspektivische Ansicht einer möglichen Struktur eines Speicherblocks aus Fig. 4.

**[0017]** Fig. 6 zeigt ein Diagramm, das eine Seitenstruktur von mit einer Wortleitung verbundenen Speicherzellen in dem Speicherblock aus Fig. 4 zeigt.

**[0018]** Fig. 7 zeigt ein Flussdiagramm, das ein Programmierverfahren einer Ausführungsform des erfindungsgemäßen Konzepts zusammenfasst.

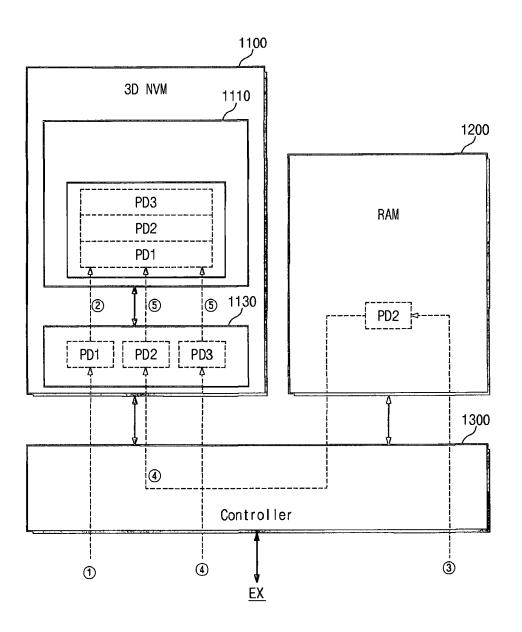

**[0019]** Fig. 8 zeigt ein Diagramm, das ein Speichersystem gemäß Fig. 1 mehr darstellt, wie es gesteuert wird, um einen Programmablauf gemäß des Verfahrens aus Fig. 7 durchzuführen.

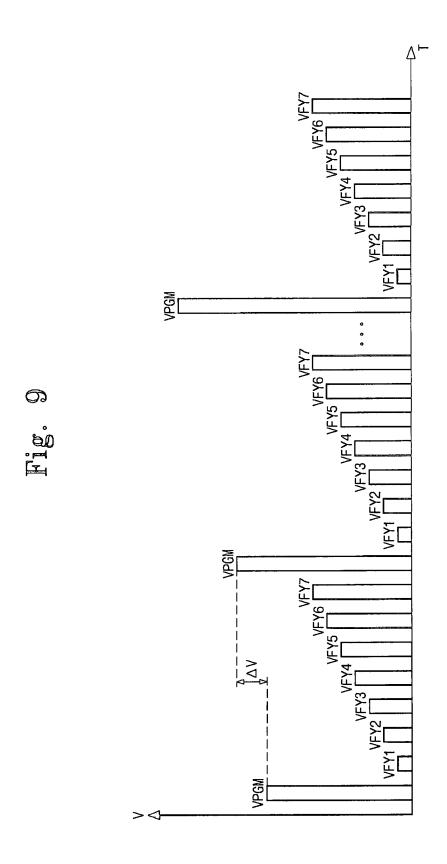

[0020] Fig. 9 zeigt ein Diagramm, das angelegte Spannungen während eines Programmablaufs eines dreidimensionalen nichtflüchtigen Speichers darstellt

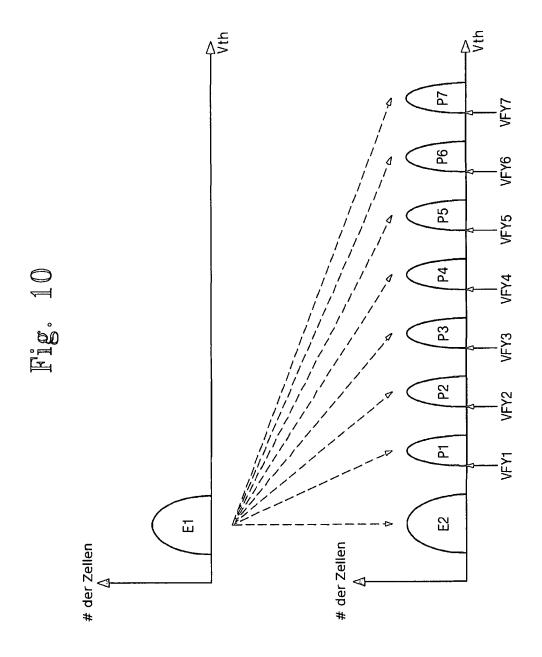

**[0021]** Fig. 10 zeigt ein Diagramm, das die Programmiereffekte von Spannungen darstellt, die während eines Betriebs des dreidimensionalen nichtflüchtigen Speichers angelegt sind.

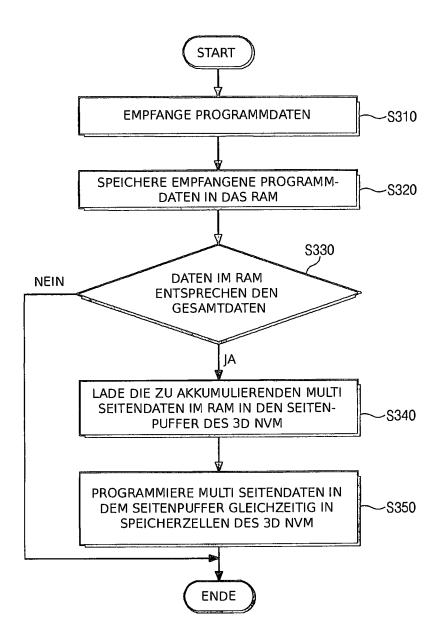

**[0022]** Fig. 11 zeigt ein Flussdiagramm, das einen Programmieransatz unter Verwendung eines Direkt-

zugriffsspeichers als Puffer in dem System von Fig. 1 zusammenfasst.

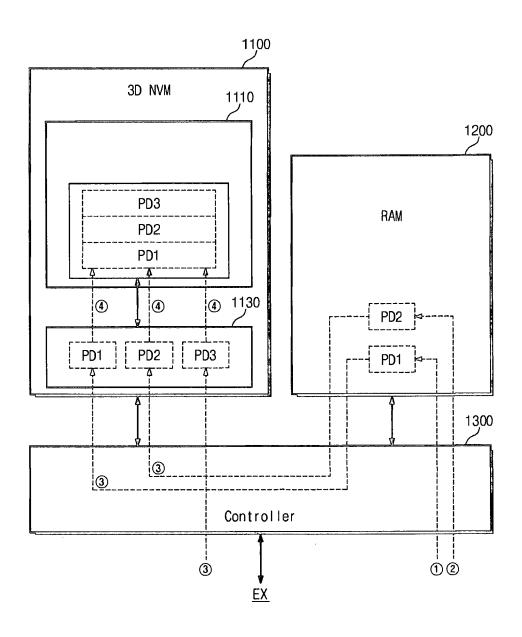

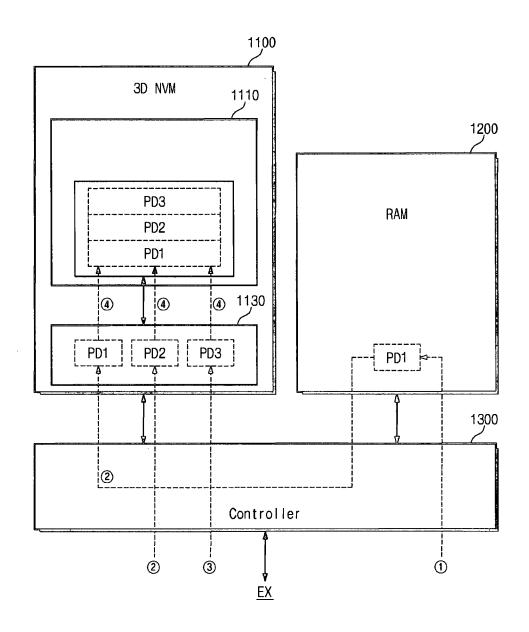

**[0023]** Fig. 12 und Fig. 13 zeigen Diagramme, welche Ausführungen, in denen das Speichersystem aus Fig. 1 einen Programmierbetrieb gemäß des Programmierverfahren aus Fig. 11 durchführt, näher darstellt.

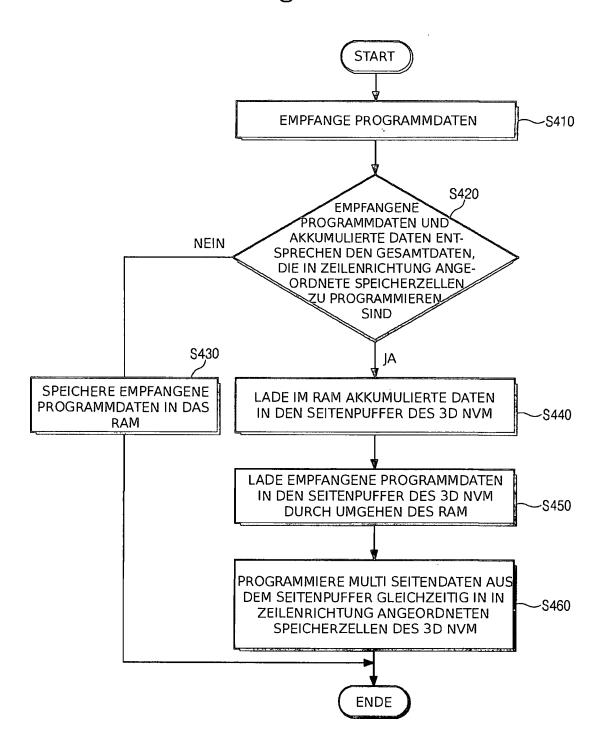

**[0024]** Fig. 14 zeigt ein Flussdiagramm, das ein anderes Pufferprogrammierverfahren zusammenfasst, das den Direktzugriffsspeicher aus Fig. 1 gemäß einer Ausführungsform des erfindungsgemäßen Konzepts nutzt.

**[0025]** Fig. 15 und Fig. 16 zeigen Diagramme, welche Ausführungsformen, in denen das Speichersystem aus Fig. 1 einen Programmbetrieb gemäß des Programmierverfahren aus Fig. 14 durchführt, näher darstellen.

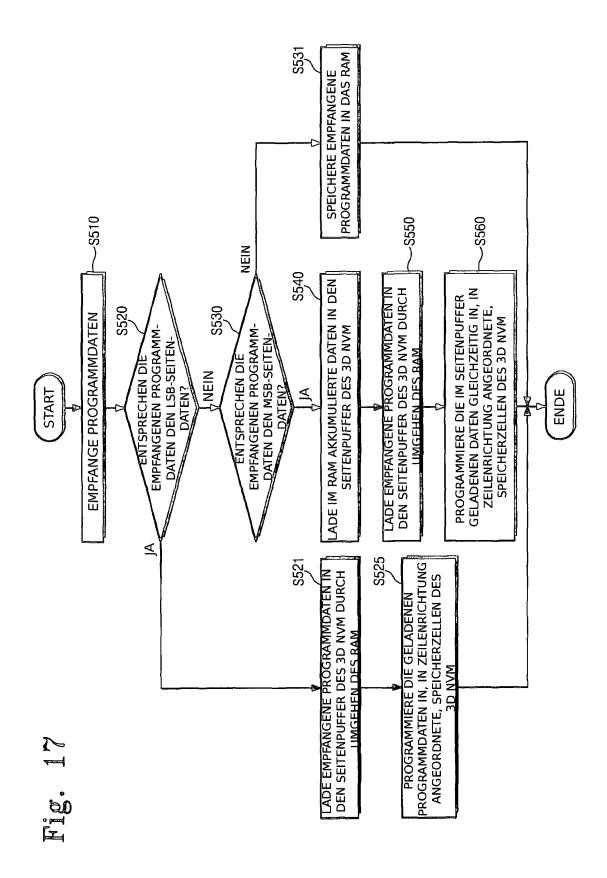

**[0026]** Fig. 17 zeigt ein Flussdiagramm, das ein anderes Pufferprogrammierverfahren unter Verwendung des Direktzugriffsspeicher aus Fig. 1 gemäß einer Ausführungsform des erfindungsgemäßen Konzepts zusammenfasst.

**[0027]** Fig. 18 zeigt ein Diagramm, in dem das Speichersystem aus Fig. 1 einen Programmierbetrieb gemäß des Programmierverfahren aus Fig. 17 durchführt, näher darstellt.

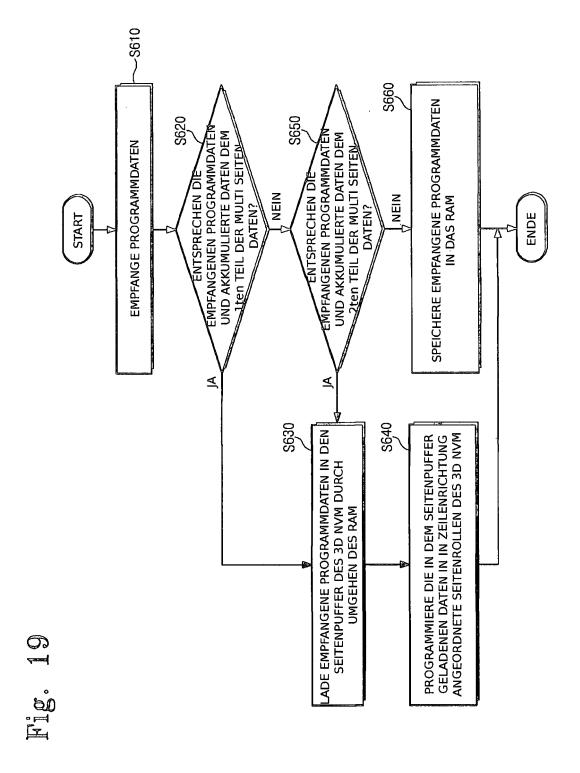

**[0028]** Fig. 19 zeigt ein Flussdiagramm, das ein anderes Pufferprogrammierverfahren zusammenfasst, welches den Direktzugriffsspeicher aus Fig. 1 gemäß einer Ausführungsform des erfindungsgemäßen Konzepts nutzt.

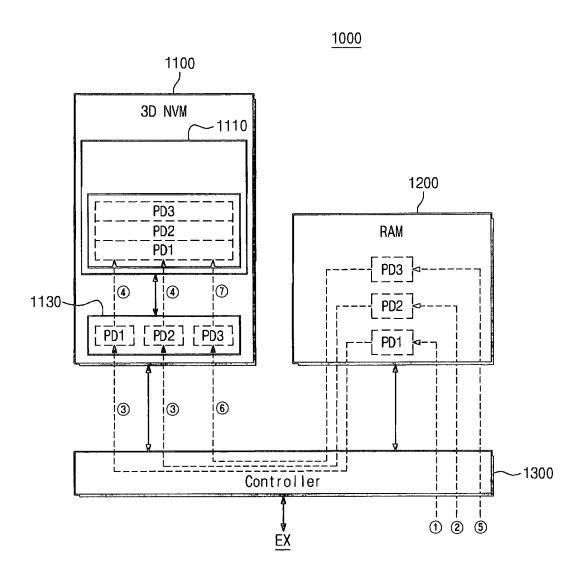

**[0029]** Fig. 20 und Fig. 21 zeigen Diagramme, die Ausführungsformen, in denen das Speichersystem aus Fig. 1 einen Programmierbetrieb gemäß des Programmierverfahren aus Fig. 19 durchführt, näher darstellen.

**[0030]** Fig. 22 zeigt ein Blockdiagramm, das eine der Seitenpuffereinheiten aus Fig. 3 näher darstellt.

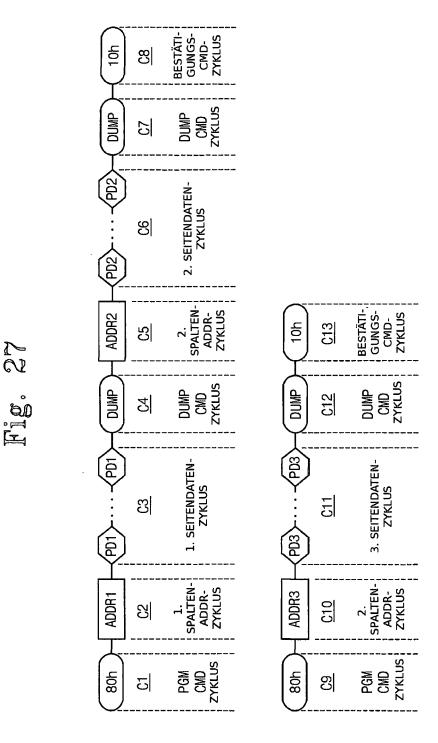

[0031] Fig. 23, Fig. 25, Fig. 27, Fig. 29 und Fig. 31 stellen entsprechende Taktdiagramme dar, welche Beispiele von Signalen darstellen, die von einem Controller während des Programmierens gemäß einiger spezieller Ausführungsformen des erfindungsgemäßen Konzepts an einen dreidimensionalen nichtflüchtigen Speicher übertragen werden.

[0032] Die Fig. 24, Fig. 26, Fig. 28 und Fig. 30 zeigen entsprechende Tabellen, die Programmieradressansätze für einen dreidimensionalen nichtflüchtigen Speicher gemäß beispielhafter Programmabschnitte auflistet.

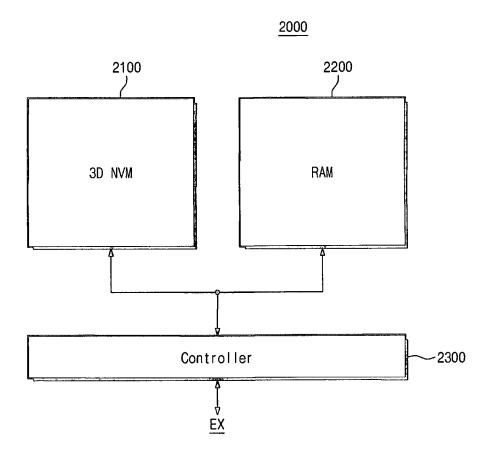

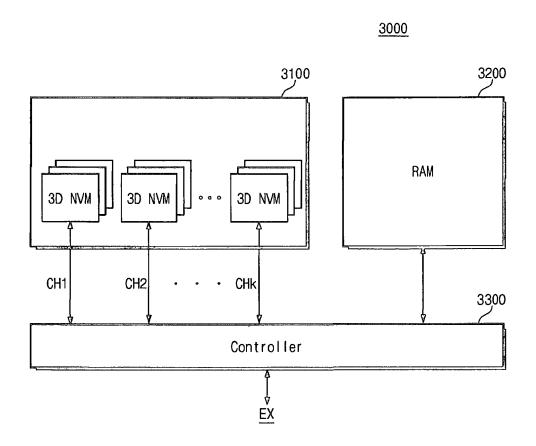

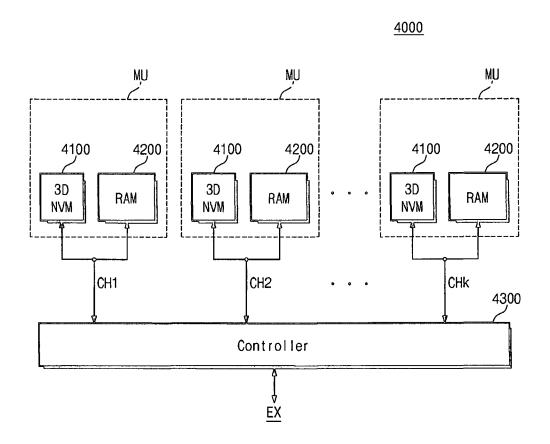

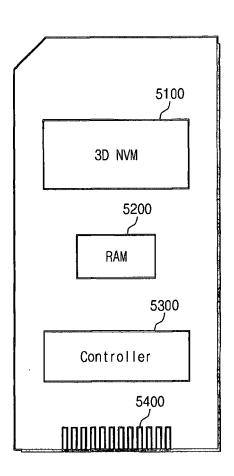

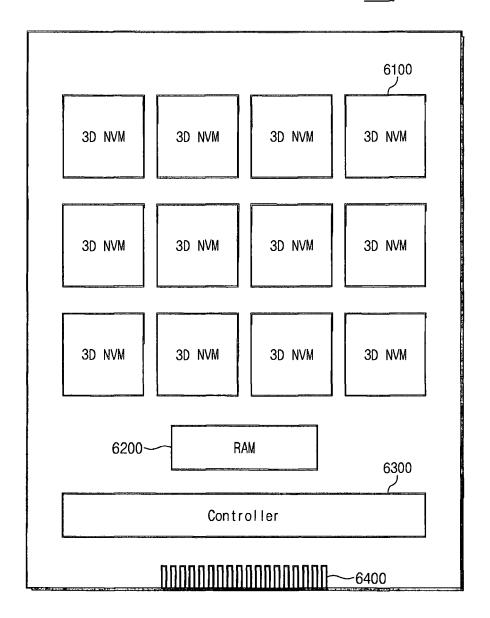

**[0033]** Die <u>Fig. 32</u>, <u>Fig. 33</u> und <u>Fig. 34</u> zeigen Blockdiagramme, die entsprechende Speichersysteme gemäß bestimmter Ausführungsformen des erfindungsgemäßen Konzepts darstellen.

**[0034]** Fig. 35 zeigt ein Diagramm, das eine Speicherkarte gemäß einer Ausführungsform des erfindungsgemäßen Konzepts zeigt.

**[0035]** Fig. 36 zeigt ein Diagramm, das ein Festkörperlaufwerk (SSD – Solid State Drive) gemäß einer Ausführungsform des erfindungsgemäßen Konzepts zeigt.

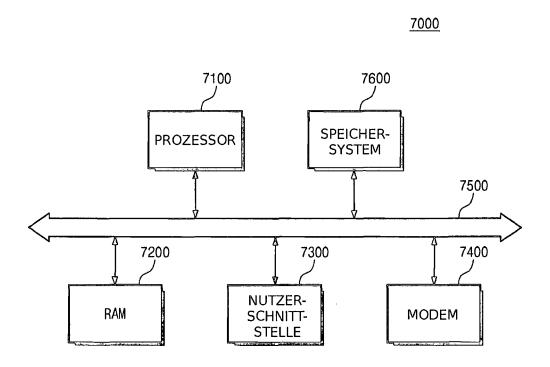

**[0036]** Fig. 37 zeigt ein Blockdiagramm, das ein Computersystem gemäß einer Ausführungsform des erfindungsgemäßen Konzepts darstellt.

### Detaillierte Beschreibung

[0037] Ausführungsformen des erfindungsgemäßen Konzepts werden im Folgenden in weiterem Detail unter Bezugnahme auf die beiliegenden Figuren beschrieben. Das erfindungsgemäße Konzept kann jedoch auf verschiedene Arten verwirklicht werden und soll nicht allein auf die dargestellten Ausführungsformen beschränkt werden. Vielmehr dienen diese Ausführungsformen als Beispiele, damit diese Beschreibung gründlich und vollständig ist, so dass das erfindungsgemäße Konzept dem Fachmann vermittelt wird. Dementsprechend werden bekannte Verfahrensschritte, Elemente und Techniken im Hinblick auf einige Ausführungsformen des erfindungsgemäßen Konzepts nicht beschrieben. Solange nicht anderweitig angemerkt, bezeichnen die gleichen Bezugszeichen durch die Beschreibung und die Figuren hindurch auch gleiche Elemente. In den Figuren können die Größen und relativen Größen von Schichten und Gebieten aus Klarheitsgründen überzeichnet dargestellt sein.

[0038] Es ist klar, dass sowohl die Ausdrücke "erster", "zweiter", "dritter", usw. im Folgenden verwendet werden, um verschiedene Elemente, Komponenten, Gebiete, Schichten und/oder Abschnitte zu beschreiben. Diese Elemente, Komponenten, Gebiete, Schichten und/oder Abschnitte nicht auf diese Ausdrücke beschränkt werden sollen. Diese Ausdrücke dienen lediglich dazu, ein Element, Komponente, Gebiet, Schicht oder Abschnitt von einem anderen Gebiet, Schicht oder Abschnitt zu unterscheiden. Das heißt, ein erstes Element, Komponente, Gebiet, Schicht oder Abschnitt wie unten diskutiert, könnte auch als ein zweites Element, Komponente, Gebiet, Schicht oder Abschnitt bezeichnet werden, ohne von der Lehre des erfindungsgemäßen Konzepts abzuweichen.

**[0039]** Räumlich relative Ausdrücke, wie "unterhalb", "unter", "unteres", "darunter", "darüber", "oberhalb"

und ähnliches werden im Folgenden verwendet, um die Beziehung eines Elements oder einer Eigenschaft zu einem anderen Element oder Eigenschaft wie in den Figuren dargestellt, leichter zu beschreiben. Es ist klar, dass räumlich relative Ausdrücke auch verschiedene Ausrichtungen in der Vorrichtung in der Verwendung oder im Betrieb zusätzlich zu der in den Figuren dargestellten Ausrichtung umfassen sollen. Beispielsweise weist die Vorrichtung, die in den Figuren umgedreht dargestellt ist, während Elemente beschrieben sind als "darunter" oder "unterhalb" oder "unter" anderer Elemente oder Eigenschaften sind dann als "darüber" oder "oberhalb" der anderen Elemente oder Eigenschaften ausgerichtet. Das heißt, beispielhafte Ausdrücke "darunter" und "unter" können beide Ausrichtungen von "darüber" oder "darunter" erfassen. Die Vorrichtung kann auch anders orientiert (90° gedreht oder in jeder anderen Orientierung) sein und die räumlich relativen Beschreibungen, wie sie im Folgenden verwendet werden, sollen dann entsprechend interpretiert werden. Zusätzlich soll auch klar sein, dass, falls eine Schicht als "zwischen" zwei Schichten beschrieben wird, das nur die eine Schicht zwischen den zwei Schichten liegen kann, oder aber auch eine oder mehrere Zwischenschichten vorhanden sein können.

[0040] Die im Folgenden verwendete Terminologie dient lediglich dazu, die speziellen Ausführungsformen zu beschreiben und nicht um das erfindungsgemäße Konzept zu beschränken. Die im Folgenden verwendeten Einzahlformen "Ein", "eines" und "der, die, das" können, solange es der Zusammenhang nicht klar anders vorgibt, auch die Pluralformen umfassen. Es ist außerdem klar, dass die Ausdrücke "umfasst" und/oder "umfassen", die im Folgenden in dieser Beschreibung verwendet werden, das Vorhandensein der genannten Eigenschaften, Zahlen, Schritte, Betriebsabläufen, Elementen und/ oder Komponenten bezeichnet, jedoch nicht das Vorhandensein zusätzlicher einer oder mehrerer anderer Eigenschaften, Zahlen, Schritte, Betriebsabläufe, Elemente, Komponenten und/oder Gruppen davon ausschließt. Der im Folgenden verwendete Ausdruck "und/oder" umfasst jede und alle Kombinationen der einen oder mehrere der entsprechend aufgeführten Ausdrücke. Auch wird der Ausdruck "beispielhaft" verwendet, um auf ein Beispiel oder eine Darstellung hinzuweisen.

[0041] Es ist klar, dass, wenn ein Element oder eine Schicht als "auf', "verbunden mit", "gekoppelt mit", oder "benachbart zu" einem anderen Element oder Schicht bezeichnet wird, es direkt auf, verbunden, gekoppelt oder benachbart zu dem anderen Element oder Schicht sein kann oder aber auch Zwischenelemente oder Zwischenschichten vorhanden sein können. Im Gegenteil dazu, falls ein Element als "direkt auf", "direkt verbunden mit", "direkt gekoppelt mit" oder "direkt benachbart zu" einem ande-

ren Element oder einer anderen Schicht bezeichnet wird, sollen keine Zwischenelemente oder Zwischenschichten vorhanden sein.

[0042] Solange nicht anders definiert, sollen alle Ausdrücke (inklusive der technischen und wissenschaftliche Ausdrücke) wie im Folgenden verwendet die gleiche Bedeutung haben, wie sie allgemein von einem Fachmann auf dem Gebiet des erfindungsgemäßen Konzepts verstanden wird. Es ist außerdem klar, dass die Ausdrücke wie sie in allgemein gebräuchlichen Wörterbüchern verwendet werden mit der Bedeutung, die konsistent mit ihrer Bedeutung im Zusammenhang mit dem Stand der Technik und/oder der vorliegenden Beschreibung zu verstehen ist und nicht in einer idealisierten oder überformalen Art zu interpretieren ist, es sei denn, es ist ausdrücklich so definiert.

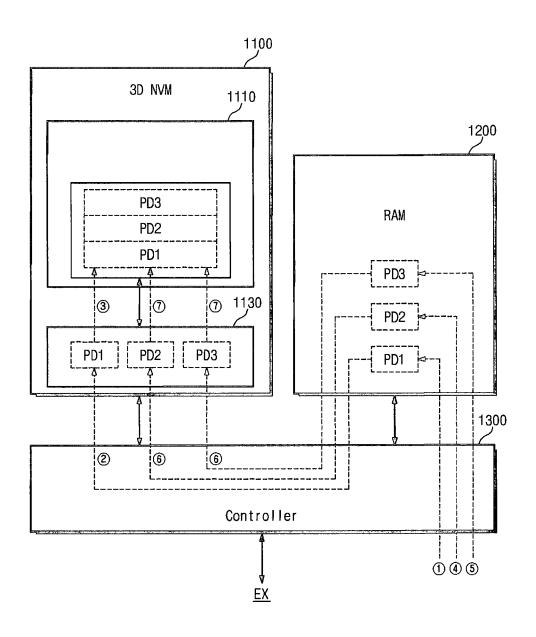

[0043] Fig. 1 zeigt ein Blockdiagramm, das allgemein ein Speichersystem gemäß einer Ausführungsform des erfinderischen Konzepts darstellt. Bezugnehmend auf Fig. 1 umfasst ein Speichersystem 1000 einen dreidimensionalen nichtflüchtigen Speicher 1100, einen Zufallzugriffsspeicher 1200 und einen Controller 1300.

[0044] Der dreidimensionale nichtflüchtige Speicher 1100 kann Steuersignale CTRL, einen Befehl CMD, und eine Adresse ADDR von dem Controller 1300 empfangen und Daten mit dem Controller 1300 austauschen. Der dreidimensionale nichtflüchtige Speicher 1100 umfasst eine Vielzahl von Speicherzellen, die in Zeilenrichtung und in Spaltenrichtung und in einer Höhenrichtung senkrecht zum Substrat angeordnet sind. Das heißt, der dreidimensionale nichtflüchtige Speicher 1100 kann eine dreidimensionale Struktur aufweisen. Der dreidimensionale Speicher 1100 kann wenigstens einen aus ROM, PROM, EPROM, EEPROM, Flashspeicher, PRAM, MRAM, ReRAM oder FRAM enthalten. Um die Beschreibung einfach zu halten, wird das erfindungsgemäße Konzept anhand eines Flashspeichers, insbesondere eines dreidimensionalen NAND Flashspeicher beschrieben. Das erfindungsgemäße Konzept ist jedoch nicht hierauf beschränkt.

[0045] Der Direktzugriffsspeicher 1200 kann Kontrollsignale CTRL, einen Befehl CMD, und eine Adresse ADDR von dem Controller 1300 empfangen und Daten mit dem Controller 1300 austauschen. Der Direktzugriffsspeicher 1200 kann wenigstens einen von DRAM, SRAM, PRAM, MRAM, RRAM oder FRAM enthalten.

[0046] Der Controller 1300 kann den dreidimensionalen nichtflüchtigen Speicher 1100 und den Direktzugriffsspeicher 1200 steuern. Der Controller 1300 kann mit einer externen Vorrichtung EX kommunizieren. Beispielsweise kann der Controller 1300 mit einer

nem externen Host kommunizieren. Der Controller **1300** kann von der externen Vorrichtung EX empfangene Daten in den dreidimensionalen nichtflüchtigen Speicher **1100** oder den Direktzugriffsspeicher **1200** programmieren und kann von dem dreidimensionalen nichtflüchtigen Speicher **1100** oder dem Direktzugriffsspeicher **1200** ausgelesene Daten an die externe Vorrichtung EX ausgeben.

[0047] Fig. 2 zeigt ein Ablaufdiagramm, das ein Programmierverfahren gemäß einer Ausbildungsform des erfindungsgemäßen Konzepts zusammenfasst. Als erstes werden Multi-Seitendaten empfangen (Silo). Die Multi-Seitendaten können Daten umfassen, die in Zeilenrichtung angeordnete Speicherzellen programmiert werden können. Die Multi-Seitendaten können zwei oder mehr Bits umfassen, die in die Speicherzelle programmiert werden. Beispielsweise können die Multi-Seitendaten ein niederwertigstes und ein hochwertigstes Bit enthalten, das in die Speicherzellen entlang der Zeilenrichtung zu programmieren ist.

**[0048]** Dann können die Multi-Bitdaten in die in Zeilenrichtung angeordneten Speicherzellen programmiert werden (S120). Die Multi-Bitdaten können gleichzeitig in die in Zeilenrichtung angeordneten Speicherzellen programmiert werden.

[0049] Fig. 3 zeigt ein Blockdiagramm, das die dreidimensionalen nichtflüchtigen Speicher 1100 aus Fig. 1 gemäß bestimmter Ausführungsformen des erfindungsgemäßen Konzepts näher darstellt. Bezugnehmend auf die Fig. 1 und Fig. 3 kann der dreidimensionale nichtflüchtige Speicher 1100 ein Speicherzellenarray 1110, einen Adressdekoder 1120, einen Seitenpuffer 1130 und eine Steuerlogik 1140 enthalten.

[0050] Das Speicherzellenarray 1110 kann mit dem Adressdekoder 1120 über Wortleitungen WL, Stringauswahlleitungen SSL, und Groundauswahlleitungen GSL und mit dem Seitenpuffer 1130 über Bitleitungen BL verbunden sein. Das Speicherzellenarray 1110 kann eine Vielzahl an Speicherblöcken BLK1 bis BLKz enthalten, von welchen jeder eine Vielzahl an Speicherzellen umfasst. In jedem der Speicherblöcke BLK1 bis BLKz können die Speicherzellen auf dem Substrat in Zeilenrichtung und Spaltenrichtung und in Höhenrichtung senkrecht zu dem Substrat angeordnet sein, so dass sich eine dreidimensionale Struktur ergibt. Jede der Speicherzellen kann zwei oder mehr Bits speichern.

[0051] Der Adressdekoder 1120 kann über Wortleitungen WL, die Stringauswahlleitungen SSL und die Groundauswahlleitungen GSL mit dem Speicherzellenarray 1110 verbunden sein. Der Adressdekoder 1120 kann in Reaktion auf die Steuerung der Steuerlogik 1140 arbeiten. Der Adressdekoder 1120 kann

von einer externen Vorrichtung eine Adresse ADDR empfangen.

[0052] Der Adressdekoder 1120 kann ausgebildet sein, um eine Zeilenadresse der eingegebenen Adresse ADDR zu dekodieren. Der Adressdekoder 1120 kann unter Verwendung der dekodierten Zeilenadresse die Wortleitungen WL, die Stringauswahlleitungen SSL und die Groundauwahlleitungen GSL auswählen. Der Adressdekoder 1120 kann geeignet sein, um eine Spaltenadresse der eingegebenen Adresse ADDR zu dekodieren. Die dekodierte Spaltenadresse DCA kann an den Seitendekoder 1130 übertragen werden. Beispielweise kann der Adressdekoder 1120 Komponenten wie beispielsweise einen Zeilendekoder, einen Spaltendekoder, einen Adresspuffer usw. enthalten.

[0053] Der Seitenpuffer 1130 kann über die Bitleitungen BL mit dem Speicherzellenarray 1110 verbunden sein. Der Seitenpuffer 1130 kann in Reaktion auf die Steuerung der Steuerlogik 1140 hin arbeiten. Der Seitenpuffer 1130 kann in Reaktion auf die dekodierte Spaltenadresse DCA die Bitlines BL auswählen.

[0054] Der Seitenpuffer 1130 kann Daten von einem Controller 1300 empfangen, um sie in ein Speicherzellarray 1110 zu schreiben. Der Seitenpuffer 1130 kann Daten von dem Speicherzellarray 1110 auslesen, um diese zu dem Controller 1300 zu übertragen. Der Seitenpuffer 1130 kann Daten von einem ersten Speichergebiet des Speicherzellenarray 1110 auslesen, um sie in ein zweites Speichergebiet des Speicherzellarrays 1110 zu schreiben. Beispielsweise kann der Seitenpuffer 1130 geeignet sein, um einen Rückkopiervorgang durchzuführen.

[0055] Der Seitenpuffer 1130 kann eine Vielzahl an Seitenpuffereinheiten PU enthalten, die entsprechend mit den Bitlines BL verbunden sind. Die Seitenpuffereinheiten PU können die Bitlines BL in einem Programmvorgang unter Spannung setzen und Spannungen der Bitlines BL in einem Lesevorgang auslesen. Die Steuerlogik 140 kann mit dem Adressdekoder 1120 und dem Seitenpuffer 1130 verbunden sein. Die Steuerlogik 1140 kann geeignet sein, um einen Gesamtbetrieb des dreidimensionalen nichtflüchtigen Speichers 1100 zu steuern. Die Steuerlogik 1140 kann in Reaktion auf Steuersignale CTRL und einem Befehl CMD wie er von einer externen Vorrichtung übertragen wird arbeiten.

[0056] Fig. 4 zeigt ein Schaltungsdiagramm, das einen Speicherblock aus der Vielzahl der Speicherblöcke, die das Speicherzellarray aus Fig. 13 bilden, näher darstellt. Bezugnehmend auf Fig. 4, umfasst ein Speicherblock Zellstrings CS11, CS12, CS 21 und CS22. Jeder der Zellstrings CS11, CS12, CS 21 und CS22 können einen Stringauswahltransistor SST, einen Groundauswahltransistor GST und Spei-

cherzellen MC1 bis MC6 die zwischen dem Stringauswahltransistor SST und dem Groundauwahltransistor GST verbunden sind, enthalten.

[0057] In den Zellstrings CS11, CS12, CS21 und CS22 sind die Controllgates der Groundauswahltransistoren GST gemeinsam mit einer Groundauswahlleitung GSL verbunden. Ein Ende der Groundauswahltransistoren GST sind entsprechend mit den Speicherzellen MC1 verbunden. Die anderen Enden der Groundauswahltransistoren GST sind gemeinsam mit einer gemeinsamen Sourceleitung CSL verbunden.

[0058] In den Zellsrtings CS11, CS12, CS21 und CS 22 können die Speicherzellen MC1 gemeinsam mit einer Wortleitung WL1 verbunden sein, die Speicherzellen MC2 können gemeinsam mit einer Wortleitung WL2 verbunden sein, die Speicherzellen MC3 können gemeinsam mit einer Wortleitung WL3 verbunden sein, die Speicherzellen MC4 können gemeinsame mit einer Wortleitung WL4 verbunden sein, die Speicherzellen MC5 können gemeinsam mit einer Wortleitung WL5 verbunden sein und die Speicherzellen MC6 können gemeinsam mit einer Wortleitung WL6 verbunden sein. Die Steuergates der Stringauswahltransistoren SST in den Zellstrings CS11 und CS 12 können mit einer Strinauswahlleitung SSL1 verbunden sein und Steuergates der Stringauswahltransistoren SST in den Zellstrings CS21 und CS22 können mit einer Stringauswahlleitung SSL2 verbunden sein.

[0059] Ein Ende der Stringauswahltransistoren SST in den Zellstrings CS11 und CS21 können mit einer Begleitung BL verbunden sein, und die anderen Enden der Stringauswahltransistoren SST in den Zellstrings CS11 und CS21 können mit den Speicherzellen MC6 verbunden sein. Ein Ende der Stringauswahltransistoren SST in den Zellstrings CS11 und CS22 können mit einer Bitleitung BL2 verbunden sein, und andere Enden der Stringauswahltransistoren SST in den Zellstrings CS12 und CS22 können mit den Speicherzellen MC6 verbunden sein. Im Folgenden werden Zeilen, Spalten und Bauhöhen kurz beschrieben. Die Richtung, in die sich die Stringauswahlleitungen SSL1 und SSL2 erstrecken, ist die Zeilenrichtung. Die Zellstrings CS11 und CS12 sind entlang der Zeilenrichtung angeordnet und bilden eine erste Zeile. Die Zellstrings CS21 und CS22 sind entlang der Zeilenrichtung angeordnet und bilden eine zweite Zeile.

**[0060]** Eine Richtung, in die sich die Bitlines BL1 und BL2 erstrecken, ist die Spaltenrichtung. Die Zellstrings CS11 und CS21 sind entlang der Spaltenrichtung angeordnet und bilden eine erste Spalte. Die Zellstrings CS21 und CS22 sind entlang der Spaltenrichtung angeordnet und bilden eine zweite Spalte.

[0061] Die Richtung von den Groundauswahltransistoren GST zu den Stringauswahltransistoren SST entspricht einer Höhe. Die Speicherzellen MC1 bis MC6 bilden eine dreidimensionale Struktur, in der sie entlang einer Zeilenrichtung und einer Spaltenrichtung angeordnet und entlang einer Höhenrichtung gestapelt sind. Speicherzellen in der gleichen Höhe sind gemeinsam mit einer Wortleitung verbunden. Speicherzellen in verschiedenen Höhen sind mit verschiedenen Wortleitungen verbunden. Stringauswahltransistoren SST in derselben Zeile können gemeinsam mit einer Stringauswahlleitung SSL1 oder SSL2, und unabhängig davon können Stringauswahltransistoren SST in verschiedenen Zeilen gemeinsam mit Stringauswahlleitungen SSL1 und SSL2 verbunden sein. Stringauswahltransistoren SST in derselben Spalte können mit derselben Bitleitung BL1 oder BL2 verbunden sein und unabhängig davon können Stringauswahltransistoren SST in verschiedenen Spalten mit verschiedenen Bitleitungen BL1 und BL2 verbunden sein.

**[0062]** Jede der Speicherzellen MC1 bis MC6 können zwei oder mehr Bits speichern.

[0063] Das heißt die Speicherzellen MC1 bis MC6 können Multilevelzellen sein.

[0064] Gemäß beispielhafter Ausführungsformen gibt es ein Beispiel, in dem der Speicherblock BLKa vier Zellstrings CS11, CS12, CS21 und CS22 enthält, wie in Fig. 4 dargestellt. Die Anzahl der Zellstrings in dem Speicherblock BLKa sind jedoch nicht auf diese Ausführungsform beschränkt. Zwei oder mehr Zellstrings können entlang einer Zeile oder Spaltenrichtung bereit gestellt sein. Ein Beispiel, in dem jeder Zellstring Textspeicherzellen MC1 bis MC6 enthält. Die Anzahl der Speicherzellen in jedem Zellstring ist jedoch nicht auf diese Ausführungsform beschränkt. Jeder Zellstring kann zwei oder mehr Speicherzellen entlang der Höhenrichtung aufweisen.

[0065] Gemäß beispielhafter Ausführungsformen ist ein Beispiel, in dem die Groundauswahltransistoren GST gemeinsam mit einer Groundauswahlleitung GSL verbunden sind, wie in Fig. 4 dargestellt. Wie jedoch bei den Stringauswahltransistoren SST kann die Struktur der Speicherblöcke BLKa auch derart geändert werden, dass die Groundauswahltransistoren GST in derselben Zeile gemeinsam mit einer Groundauswahlleitung verbunden sind und Groundauswahltransistoren GST in verschiedenen Zeilen mit verschiedenen Groundauswahlleitungen verbunden sind.

[0066] In beispielhaften Ausführungsformen ist in Fig. 4 ein Beispiel in dem jeder Zellstring einen Stringauswahltransistor SST und einen Groundauswahltransistor GST enthält dargestellt. Jeder Zellstring kann jedoch auch zwei oder mehr Stringauswahltran-

sistoren oder zwei oder mehr Groundauswahltransistoren enthalten.

**[0067]** Wenigstens eine der Speicherzellen MC1 bis MC6 in jedem Zellstring kann als Dummyspeicherzelle verwendet werden.

[0068] Fig. 5 zeigt eine perspektivische Ansicht einer möglichen Struktur, um den Speicherblock aus Fig. 4 zu realisieren. Bezugnehmend auf die Fig. 4 und Fig. 5 kann in dem Substrat 111 eine Vielzahl an gemeinsamen Sourcegebieten CSR, die sich entlang einer Zeilenrichtung erstrecken, bereitgestellt sein. Die gemeinsamen Sourcegebiete CRS können entfernt voneinander entlang einer Zeilenrichtung angeordnet sein. Die gemeinsamen Sourcegebiete CRS können gemeinsam verbunden sein, um eine gemeinsame Sourceleitung zu binden. Die gemeinsamen Sourceleitungen CSL können ein N-Typ Halbleitermaterial enthalten.

[0069] Zwischen den gemeinsamen Sourcegebieten CSR, kann entlang der Höhenrichtung (z. B. eine Richtung senkrecht zum Substrat 111) nacheinander eine Vielzahl an Isolationsmaterialien 112 und 112a bereitgestellt sein. Die Isolationsmaterialien 112 und 112a können entlang der Höhenrichtung entfernt voneinander angeordnet sein. Die Isolationsmaterialien 112 und 112a können einen Halbleiteroxidfilm als Isolationsmaterial umfassen. Das Isolationsmaterial 112a, das das Substrat 111 kontaktiert, kann eine geringere Dicke aufweisen als die anderen Isolationsmaterialien 112. Zwischen den gemeinsamen Sourcegebieten CSR, kann eine Vielzahl an Säulen PL angeordnet sein die entfernt voneinander in Zeilenrichtung und Spaltenrichtung angeordnet sein und die Vielzahl der Isolationsmaterialien 112 und 112a entlang der Föhnrichtung durchdringen. Beispielsweise können die Säulen PL das Substrat 111 durch die Isolationsmaterialien 112 und 112a hindurch kontaktieren. Jede der Säulen PL kann eine Kanalschicht 114 und ein inneres Material 115 aufweisen. Die Kanalschichten 114 können ein P-Typ Halbleitermaterial oder ein intrinsisches Halbleitermaterial aufweisen. Die inneren Materialien 115 können entsprechend ein Isolationsmaterial oder einen Luftspalt aufweisen. Zwischen den gemeinsamen Sourcegebieten CSR, sind auf freigelegten Oberflächen der Isolationsmaterialien 112 und 112a und den Säulen PL Informationsspeicherschichten 116 bereitgestellt. Die Informationsspeicherschichten 116 können durch das Einfangen oder Entladen von Ladungen Informationen speichern. Die Informationsspeicherschichten 116 können ONA (oxide-nitride-aluminum) oder ONO (oxidenitride-oxide) enthalten.

[0070] Zwischen den gemeinsamen Sourcegebieten CSR und zwischen den Isolationsmaterialien 112 und 112a können leitfähige Materialien CM1 bis CM8 auf freigelegten Oberflächen der Informationsspeicher-

schichten **116** bereitgestellt sein. Das leitfähige Material CM8 der leitfähigen Materialien CM1 bis CM8 kann durch einen Stringauswahlleitungsschnitt separiert sein. Der Stringauswahlleitungsschnitt kann sich entlang der Zeilenrichtung erstrecken, um das leitfähige Material CM8 entlang der Spaltenrichtung zu trennen. Die leitfähigen Materialien CM1 bis CM8 können ein metallisches leitfähiges Material enthalten.

[0071] Die Informationsspeicherschichten 116, die auf einer oberen Oberfläche des auf einer obersten Schicht der Isolationsmaterialien 112 und 112a angeordnetes Isolationsmaterials, kann entfernt werden. Beispielsweise können die Informationsspeicherschichten 116 die auf den Seiten gegenüber der Säulen PL von den Seiten der Isolationsmaterialien 112 und 112a angeordnet sind, entfernt werden.

[0072] Eine Vielzahl an Senken 320 kann auf der Vielzahl der jeweiligen Säulen PL angeordnet sein. Die Senken 320 können ein N-Typ Halbleitermaterial (z. B. Silizium) enthalten. Die Senken 320 können sich bis zur Oberseite der Kanalschichten 114 der Säulen PL hin erstrecken.

[0073] Die Bitleitungen BL, die sich in die Säulenrichtung erstrecken, können auf den Senken 320 bereitgestellt sein, sodass sie entlang der Zeilenrichtung voneinander beabstandet sind.

[0074] Die Bitleitungen BL können mit den Senken 320 gekoppelt sein. Gemäß beispielhafter Ausführungsformen sind die Senken 320 und die Bitleitungen BL über Kontaktstöpsel (nicht gezeigt) miteinander verbunden. Die Bitleitungen BL können entsprechend ein metallisch leitfähiges Material enthalten.

[0075] Die Vielzahl der Säulen PL können zusammen mit den Informationsspeicherschichten 116 und der Vielzahl der leitfähigen Materialien CM1 bis CM8 eine Vielzahl an Zellstrings bilden. Jede der Säulen PL kann mit den Informationsspeicherschichten 116 und benachbarten leitfähigen Materialien CM1 bis CM8 einen Zellstring bilden.

[0076] Das leitfähige Material CM1 kann als Groundauswahlleitung GSL und als Controlgates der Groundauswahltransistoren GST genutzt werden. Die Informationsspeicherschichten 116 und zu dem leitfähigen Material CM1 benachbarte Abschnitte der Kanalschichten 114 können als Sperrisolationsschicht, als Ladungsfangschicht, als Tunnelisolationsschicht und als Kanal genutzt werden.

[0077] Das leitfähige Material CM2 kann als Wortleitung WL1 und als Gatesteuerung der Speicherzellen MC1 genutzt werden. Das leitfähige Material CM3 kann als Wortleitung WL2 und als Gatesteuerung der Speicherzellen MC2 genutzt werden. Das

leitfähige Material CM4 kann als Wortleitung WL3 und als Gatesteuerung der Speicherzellen MC3 genutzt werden. Das leitfähige Material CM5 kann als Wortleitung WL4 und als Gatesteuerung der Speicherzellen MC4 genutzt werden. Das leitfähige Material CM6 kann als Wortleitung WL5 und als Gatesteuerung der Speicherzellen MC5 genutzt werden. Das leitfähige Material CM7 kann als Wortleitung WL6 und als Gatesteuerung der Speicherzellen MC6 genutzt werden.

[0078] Das leitfähige Material CM8 kann als Stringauswahlleitung SSL1 und SSL2 und als Steuergate der Stringauswahltransistoren SST genutzt werden.

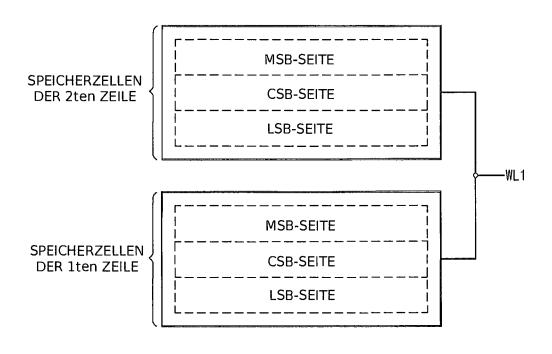

[0079] Die Speicherzellen MC1 bis MC6 können eine dreidimensionale Struktur aufweisen, um auf dem Substrat 111 entlang der Zeilenrichtung und der Spaltenrichtung angeordnet zu sein und um in einer Höhenrichtung senkrecht zum Substrat 111 gestapelt zu sein. Fig. 6 zeigt ein Diagramm, das eine mögliche Seitenstruktur für eine Gruppe von Speicherzellen, die mit einer der in Fig. 4 gezeigten Wortleitungen verbunden ist. Gemäß bestimmter Ausführungsformen ist jede der Speicherzellen MC1 bis MC6 geeignet, um ein niederwertiges Bit (LSB), ein mittelwertiges Bit (CSB) und ein höchstwertiges Bit (MSB) zu speichern. Die Anzahl der in jeder Speicherzelle gespeicherten Bits ist jedoch nicht auf drei begrenzt. Beispielsweise können andere Speicherzellen geeignet sein, um 2,4 oder mehr als 4 Bits zu speichern.

[0080] Bezugnehmend auf die Fig. 4 und Fig. 6, sind die niederwertigen Bits in den Speicherzellen MC1 die zur ersten Zeile gehören gespeichert, wobei die Speicherzellen MC1 die mit der Wortleitung WL1 verbunden sind eine LSB Seite bilden, und die in den Speicherzellen MC1 gespeicherten CSBs eine CSB Seite bilden, und die in den Speicherzellen MC1 gespeicherten MSBs eine MSB Seite bilden.

[0081] In Speicherzellen MC1 gespeicherte LSBs, die zur zweiten Zeile gehören, mit einer Wortleitung WL1 verbundene Speicherzellen MC1 bilden eine LSB Seite, in Speicherzellen MC1 gespeicherte CSBs bilden eine CSB Seite und in Speicherzellen MC1 gespeicherte MSBs bilden eine MSB Seite.

[0082] Das heißt, ein Bit das in jede der Speicherzellen in einer Zeile gespeichert ist, bildet eine einzelne Seite. Speicherzellen einer Zeile bilden eine Multiseite mit einer Vielzahl an Einzelseiten. Die Multiseite kann alle in Speicherzellen einer Zeile programmierte Einzelseiten angeben.

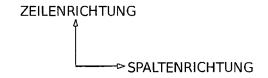

**[0083]** Fig. 7 zeigt ein Flussdiagramm, das ein Programmierverfahren gemäß einer Ausführungsform des erfindungsgemäßen Konzepts zusammenfasst. Bezugnehmend auf die Fig. 1, Fig. 3 und Fig. 7 werden Programmdaten empfangen (S210). Zum Beispiel, können die Programmdaten von einer externen

Vorrichtung EX einem Controller **1300** bereitgestellt werden.

[0084] Als Nächstes wird erfasst, ob die empfangenen Programmdaten den gesamten Daten, die in die entlang einer Zeilenrichtung angeordneten Speicherzellen programmiert sind (S220), entsprechen. In diesem Zusammenhang wird der Ausdruck "gesamte Daten" verwendet, um alle der in den Speicherzellen programmierten Daten zu bezeichnen. Das heißt, wenn eine Speicherzelle geeignet ist, um N-Bits zu speichern, umfassen die gesamten Daten alle der N-Bits, die in die Speicherzelle programmiert werden sollen. In dem angenommenen Arbeitsbeispiel umfassen die gesamten Daten LSBs, CSBs und MSBs, die in die entsprechenden Speicherzellen programmiert werden. Der Controller 1300 kann die Art der Programmdaten aufgrund der von einer externen Vorrichtung bereitgestellten entsprechenden Adresse (z. B. logische Adresse) ermitteln. Gemäß spezieller Ausführungsformen kann der Controller 1300 die Eingangsadressen in physikalische Adressen umwandeln und basierend auf der erhaltenen physikalischen Adresse die Art der Programmdaten ermitteln. Falls die Programmdaten nicht den gesamten Daten (S220 = No) entsprechen, wird ein Pufferprogrammiervorgang durchgerührt (S230). Das Pufferprogrammieren kann unter Verwendung des Direktzugriffsspeichers 1200 aus Fig. 1 durchgeführt werden. Der Pufferprogrammiervorgang wird unter Bezugnahme auf verschiedene folgende Ausführungsformen im zusätzlichen Detail beschrieben.

[0085] Falls die Programmdaten den gesamten Daten entsprechen (S220 = Ja), werden die gesamten Daten (z. B. Multi-Seitendaten) in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen ohne durch den Direktzugriffsspeicher 1200 (S240) hindurch zu gehen. Der Controller 1300 kann dann die Multi-Seitendaten zu dem dreidimensionalen nichtflüchtigen Speicher 1100 übertragen, und der dreidimensionale nichtflüchtige Speicher 1100 kann die Multi-Seitendaten zu dem Seitenpuffer 1130 laden.

[0086] Die Multi-Seitendaten, die in den Seitenpuffer 1130 geladen wurden, können dann gleichzeitig in die entlang einer Zeilenrichtung des dreidimensionalen nichtflüchtigen Speichers 1100 angeordneten Speicherzellen programmiert werden (S250). Der dreidimensionale nichtflüchtige Speicher 1100 kann gleichzeitig die geladenen Multi-Seitendaten in die entlang einer Zeilenrichtung angeordneten Speicherzellen programmieren.

**[0087]** Fig. 8 zeigt ein Diagramm eines Beispiels indem ein Speichersystem aus Fig. 1 einen Programmablauf gemäß dem Programmierverfahren aus Fig. 7 durchführt.

[0088] Bezugnehmend auf die Fig. 7 und Fig. 8 können die Programmdaten PD1, PD2 und PD3 nacheinander von einer externen Vorrichtung (EX) empfangen werden. Die Programmdaten PD1, PD2 und PD3 entsprechen Multi-Seitendaten. Beispielsweise können LSB Daten PD1, CSB Daten PD2 und MSB Daten PD3 nacheinander empfangen werden. Die gesamten Daten, die in Speicherzellen entlang einer Zeilenrichtung angeordnet sind, können empfangen werden.

[0089] Die LSB Daten PD1, CSB Daten PD2 und MSB Daten PD3 können direkt in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen werden ohne durch den Direktzugriffsspeicher 1200 hindurch zu gehen. Die LSB Daten PD1, CSB Daten PD2 und MSB Daten PD3 können direkt zu dem Seitenpuffer 1130 geladen werden und können gleichzeitig in Speicherzellen angeordnet entlang der Zeilenrichtung programmiert werden.

[0090] Fig. 9 zeigt ein Diagramm, das Spannungen darstellt, die während eines Programmiervorgangs eines dreidimensionalen nichtflüchtigen Speichers angewandt werden. In Fig. 9 bezeichnet die horizontale Achse eine Zeit T und bezeichnet eine vertikale Achse eine Spannung V. Bezugnehmend auf die Fig. 4 und Fig. 9 kann eine Programmierspannung VPGM an eine aus den Wortleitungen WL1 bis WL6 ausgewählten Wortleitung angelegt werden. Nachdem die Programmierspannung VPGM angelegt ist, werden nacheinander Verifizierungsspannungen VFY1 bis VFY7 an die ausgewählte Wortleitung angelegt. Die Verifizierungsspannungen VFY1 bis VFY7 können Spannungen entsprechen, um die Multi-Seitendaten gleichzeitig zu programmieren. Die Verifizierungsspannungen VFY1 bis VFY7 können Spannungen entsprechen, die genutzt werden, um festzustellen, ob Schwellspannungen der Speicherzellen Zielniveaus erreicht haben. Falls nach dem aufeinanderfolgenden Anlegen der Verifizierungsspannungen VFY1 bis VFY7 immer noch falsch programmierte Speicherzellen vorhanden sind, wird die Programmierspannung VPGM nochmals an die ausgewählte Wortleitung angelegt. In diesem Fall kann die Programmierspannung VPGM durch die Erhöhung ΔV erhöht werden. Danach werden die Verifizierungsspannungen VFY1 bis VFY7 nacheinander an die ausgewählte Wortleitung angelegt.

[0091] Die Programmierspannung VPGM und die Verifizierungsspannungen VFY1 bis VFY7 können iterativ angelegt werden bis die Speicherzellen programmiert sind. Ebenso kann die Programmierspannung VPGM durch die Erhöhung ΔV erhöht werden, falls immer die Programmierspannung VPGM iterativ angewandt wird. Das heißt, inkrementelles schrittweises Pulsprogrammieren wird durchgeführt.

[0092] Fig. 10 zeigt ein Diagramm, das Variationen der Speicherzellenschwellspannungen programmiert wie in den Fig. 9 dargestellten Verfahren, dargestellt. In Fig. 10 bezeichnet die horizontale Achse eine Schwellspannung und die vertikale Achse bezeichnet die Anzahl der Speicherzellen. Das heißt, Fig. 10 zeigt eine Variation der Schwellspannungsverteilungen von Speicherzellen MC.

**[0093]** Bezugnehmend auf die <u>Fig. 9</u> und <u>Fig. 10</u> können Speicherzellen mit einem Löschzustand E1 entsprechend auf einen Löschzustand E2 und Programmzustände P1 bis P7 programmiert werden.

**[0094]** Speicherzellen, die auf einen Löschzustand E2 programmiert sind (oder nicht programmiert) können programmiergesperrt sein. Speicherzellen, die auf den Programmzustand P1 programmiert sind können programmiergesperrt sein, nachdem ihre Schwellwertspannungen eine Verifizierungsspannung VFY1 erreichen.

[0095] Speicherzellen, die auf den Programmzustand P2 programmiert sind, können programmiergesperrt sein nachdem ihre Schwellwertspannungen eine Verifizierungsspannung VFY2 erreichen. Speicherzellen, die auf den Programmierzustand P3 programmiert sind, können programmiert gesperrt sein nachdem ihre Schwellspannungen eine Verifizierungsspannung VFY3 erreichen. Speicherzellen, die auf den Programmierzustand P4 programmiert sind, können programmiergesperrt sein, nachdem ihre Schwellspannung eine Verifizierungsspannung VFY4 erreicht. Speicherzellen, die auf den Programmzustand P5 programmiert sind, können programmiergesperrt sein, nachdem ihre Schwellspannungen eine Verifizierungsspannung VFY5 erreichen. Speicherzellen, die auf einen Programmierzustand P6 programmiert sind, können programmiergesperrt sein, nachdem ihre Schwellspannungen eine Verifizierungsspannung VFY6 erreichen. Speicherzellen, die auf den Programmzustand P7 programmiert sind, können programmiergesperrt sein, nachdem ihre Schwellspannung eine Verifizierungsspannung VFY7 erreicht.

[0096] Eine Kopplung kann auftreten, falls Speicherzellen von dem Löschzustand E1 auf die Programmierzustände P1 bis P7 programmiert werden. Um zu vermeiden, dass Schwellwertspannungen benachbarter Speicherzellen durch das Koppeln unbeabsichtigt geändert werden, programmieren bestimmte konventionelle NAND Flash Speicher nacheinander LSB, CSB und MSB Daten. In diesem Fall, können, da die Änderungen der Schwellspannungen erzeugt durch das einzelne Programmieren verringert werden, die Kopplungseffekte reduziert werden. Demgemäß kann die Änderung der Schwellspannungen benachbarter Speicherzellen reduziert werden.

[0097] Wie in Fig. 4 dargestellt, sind Speicherzellen auf gleicher Höhe in einem Speicherblock BL-Ka gemeinsam mit einer Wortleitung verbunden. Das heißt, eine Wortleitung wird geteilt. In diesem Fall, falls in Bezug auf eine erste Zeile von Zellstrings CS 11 und CS12 ein Programmiervorgang durchgeführt wird, kann eine zweite Zeile an Zellstrings CS21 und CS22 durch die Programmierspannung und die Überschreitungsspannung eine Belastung erfahren. Vorausgesetzt mit der Struktur aus Fig. 4, wenn zuerst LSB und dann CSB und dann MSB nacheinander programmiert werden, erhöht sich die Anzahl der Programmierschritte (NOP), die die Zielspeicherzellen erfahren exponentiell, verglichen mit ähnlichen Programmierumständen in einem planaren NAND Flash Speicher.

[0098] Im Zusammenhang mit den Ausführungsformen des erfindungsgemäßen Konzepts, können LSB, CSB und MSB Daten gleichzeitig unter Verwendung des "gleichzeitige Programmierung"-Ansatzes programmiert werden. Das heißt, die Anzahl der Programmierschritte, die auf die Speicherzellen angewandt werden, können reduziert werden. Als Ergebnis können Ermüdungserscheinungen der Speicherzellen reduziert und die Zuverlässigkeit eines Speichersystems 100 verbessert werden.

[0099] Wie in Fig. 5 dargestellt, können die Informationsspeicherschichten 116 von leitfähigen Materialien CM2 bis CM7 welche als Wortleitungen WL1 bis WL6 und als Steuergate der Speicherzellen MC1 bis MC6 genutzt werden, umgeben sein. Die leitfähigen Materialien CM2 bis CM7 können als elektromagnetische Abschirmungen dienen. Obwohl die Schwellspannungen der Speicherzellen sich ändern, können die leitfähigen Materialien CM2 bis CM7, die als elektromagnetische Abschirmungen dienen, den Einfluss des Koppelns unterdrücken. Das heißt, wie in Fig. 9 dargestellt, obwohl die Schwellspannungen der Speicherzellen stark variieren, variieren die Schwellspannungen von benachbarten Speicherzellen nicht.

[0100] Das heißt, wie in Fig. 5 dargestellt, da die leitfähigen Materialien CM2 bis CM7 als elektromagnetische Abschirmungen, die die Informationsspeicherschichten 116 der Speicherzellen MC1 bis MC6 umgeben, verwendet werden können LSB, CSB und MSB gleichzeitig programmiert werden ohne eine Schwellwertabweichung aufgrund des Koppelns zu verursachen. In einer in den Fig. 4 und Fig. 5 dargestellten Struktur eines Speicherblocks BLKa, bei der LSB, CSB und MSB gleichzeitig programmiert werden, kann die Anzahl der Programmier (NOP) Schritte, die auf die Speicherzellen angewandt werden, reduziert werden. Das Speichersystem 1000 aus Fig. 1 mit verbesserter Zuverlässigkeit kann erreicht werden, indem die Programmierdaten unter Verwendung des Direktzugriffsspeichers 1200 als Puffer gespeichert werden und die Programmierung des dreidimensionalen nichtflüchtigen Speichers **1100** gemäß einer Multi-Seiteneinheit durchgeführt wird.

[0101] Fig. 11 zeigt ein Ablaufdiagramm, das ein Pufferprogrammierverfahren unter Verwendung eines Direktzugriffsspeichers 1200 aus Fig. 1 zusammenfasst wie es auf verschiedene Ausführungsformen des erfindungsgemäßen Konzepts angewandt werden kann. Bezugnehmend gemeinsam auf die Fig. 1, Fig. 3 und Fig. 11 werden Programmdaten empfangen (S310). Die Größe der empfangenen Programmdaten kann kleiner als eine definierte Gesamtdatengröße der vorhergegangen Diskussion sein. Die Programmdaten können durch den Controller 1300 von einer externen Vorrichtung EX bereitgestellt werden.

**[0102]** Die Programmdaten werden nun in den Direktzugriffsspeicher **1200** gespeichert (S320). Der Controller **1300** wird verwendet, um die Programmdaten in dem Direktzugriffsspeicher **1200** zu speichern.

[0103] Es wird nun ermittelt, ob die in dem Direktzugriffsspeicher 1200 aufgelaufenen Daten die gesamten Daten (z. B. alle Daten, die in die entlang der Zeilenrichtung angeordneten Speicherzellen zu programmieren sind) (S330). Beispielsweise falls eine Speicherzelle N-Bits speichert, wird erfasst ob alle der N-Bits, die in die entlang einer Zeilenrichtung angeordneten Speicherzellen zu programmieren sind, erhalten wurden. Der Controller 1300 kann verwendet werden, um zu vermitteln, ob die in dem Direktzugriffsspeicher 1200 angelaufenen Daten, den gesamten Daten entsprechen.

[0104] Falls die in dem Direktzugriffsspeicher 1200 aufgelaufenen Daten den gesamten Daten (z. B. Multi-Seitendaten) entsprechen (S330 = Ja), werden die Multi-Seitendaten, die in dem Direktzugriffsspeicher 1200 aufgelaufen sind dann in den Seitenpuffer 1130 des nichtflüchtigen Speichers 1100 geladen (S340). Danach werden die in den Seitenpuffer 1130 geladenen Multi-Seitendaten gleichzeitig in die Speicherzellen des dreidimensionalen nichtflüchtigen Speichers 1100 programmiert (S350).

[0105] Nachdem die in dem Direktzugriffsspeicher angehäuften Multi-Seitendaten in die Speicherzellen des dreidimensionalen nichtflüchtigen Speichers 1100 programmiert wurden, werden gemäß der beschriebenen Ausführungsformen die Daten routinemäßig von den Direktzugriffsspeicher 1100 gelöscht.

[0106] Fig. 12 zeigt ein Diagramm das eine Ausführungsform zeigt, in der das Speichersystem aus Fig. 1 einen Programmierbetrieb gemäß dem Programmierverfahren aus Fig. 11 durchführt. Bezugnehmend auf die Fig. 11 und Fig. 12 wird der Controller 1300 verwendet, um Programmdaten PD1, PD2

und PD3 wie sie von einer externen Vorrichtung EX empfangen wurden in dem Direktzugriffsspeicher zu speichern. Die Größe der empfangenen Programmdaten PD1, PD2 und PD3 kann geringer als die der "gesamten" Multi-Seitendaten sein. In bestimmten Ausführungsformen jedoch können die Programmdaten PD1, PD2 und PD3 LSB Daten, CSB Daten und MSB Daten entsprechen, die in Speicherzellen des dreidimensionalen nichtflüchtigen Speichers 1100 die entlang einer Zeilenrichtung angeordnet sind, gespeichert werden. Die LSB, CSB und MSB Daten PD1, PD2 und PD3 können unabhängig voneinander empfangen werden und müssen nicht zur gleichen Zeit empfangen werden.

[0107] Der Controller 1300 kann verwendet werden, um LSB, CSB und MSB Daten PD1, PD2 und PD3 die unabhängig voneinander empfangen wurden in dem Direktzugriffsspeicher 1200 zu speichern. Das heißt, der Controller 1300 kann verwendet werden, um von einer externen Vorrichtung EX in dem Direktzugriffsspeicher 1200 gespeichert zu werden, sodass alle der in dem Direktzugriffsspeicher 1200 angehäuften Daten einen definierten Satz an Multi-Seitendaten bildet.

[0108] Falls die MSB Daten PD3 in dem Direktzugriffsspeicher 1200 gespeichert werden, können die Daten PD1, PD2 und PD3, die in dem Direktzugriffsspeicher 1200 angehäuft sind, den Multi-Seitendaten entsprechen. Falls die Daten PD1, PD2 und PD3, die in dem Direktzugriffsspeicher 1200 angehäuft sind den Multi-Seitendaten entsprechen, kann der Controller 1300 die Daten PD1, PD2 und PD3, die in dem Direktzugriffsspeicher 1200 angehäuft sind, an den dreidimensionalen nichtflüchtigen Speicher 1100 übertragen.

**[0109]** Die Daten PD1, PD2 und PD3, die zu den dreidimensionalen nichtflüchtigen Speicher **1100** übertragen wurden, können in den Seitenpuffer **1300** geladen werden. Danach kann der dreidimensionale nichtflüchtige Speicher **1100** die geladenen Daten PD1, PD2 und PD3 zur gleichen Zeit in Speicherzellen in einer Zeile laden.

[0110] In Fig. 12 wird ein Beispiel beschrieben, indem die von der externen Vorrichtung EX empfangenen Daten Einzelseitendaten sind. Von der externen Vorrichtung EX empfangene Daten müssen jedoch nicht auf Einzelseitendaten beschränkt sein. Falls die in den Direktzugriffsspeicher 1200 gespeicherten Daten Multi-Seitendaten entsprechen, kann der Controller 1300, die in dem Direktzugriffsspeicher 1200 akkumulierten Daten in den dreidimensionalen nichtflüchtigen Speicher 1100 programmieren unabhängig von der Größe der von der externen Vorrichtung EX empfangenen Daten.

[0111] Fig. 13 zeigt ein Diagramm, das eine andere Ausführungsform darstellt, in der ein Speichersystem aus Fig. 1 einen Programmierablauf gemäß dem Programmierverfahren aus Fig. 11 durchführt. Bezugnehmend auf die Fig. 11 und Fig. 13 werden LSB-Daten PD1 in einem Zufallzugriffsspeicher 1200 gespeichert. Während CSB-Daten PD2 in dem Direktzugriffspeicher 1200 gespeichert werden, werden die in dem Direktzugriffspeicher 1200 gespeicherten LSB-Daten PD1 in dem Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen. Während MSB-Daten PD3 in dem Direktzugriffspeicher 1200 gespeichert werden, werden die CSB-Daten PD2 die in dem Direktzugriffspeicher 1200 gespeichert sind in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen. Die in dem Direktzugriffspeicher **1200** gespeicherten MSB-Daten PD3 werden in dem Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speicher 1200 geladen. Danach werden die in dem Seitenpuffer 1130 geladenen Daten LSB, CSB, MSB, PD1, PD2 und PD3 gleichzeitig in die Speicherzellen (z. B. Speicherzellen, die entlang der Pfeilrichtung eines Speicherzellenarrays 1110 angeordnet sind) des dreidimensionalen nichtflüchtigen Speichers 1100 programmiert.

[0112] Während Seitendaten in den Direktzugriffsspeicher 1200 gespeichert werden, können Seitendaten, die in dem Direktzugriffsspeicher 1200 gespeichert sind, in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen werden. In bestimmten Ausführungsformen wird die Zeitdauer während der die Seitendaten PD1, PD2 und PD3 in den Direktzugriffsspeicher 1200 gespeichert sind und die Zeitdauer während der die Seitendaten in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 von dem Direktzugriffsspeicher 1200 geladen werden überlappen. Das heißt, es ist möglich die benötigte Gesamtzeit, die notwendig ist, um die Daten in den Seitenpuffer 1130 des dreidimensionalen nicht flüchtigen Speichers 1100 zu laden, zu reduzieren.

[0113] Fig. 14 zeigt ein Flussdiagramm, das eine andere Ausführungsform in der ein Pufferprogrammierverfahren welches dem Direktzugriffsspeicher aus Fig. 1 in Bezug auf einen dreidimensionalen nichtflüchtigen Speicher verwendet zusammengefasst. Bezugnehmend auf die Fig. 1, Fig. 3 und Fig. 14 werden Programmdaten empfangen (S410). Die Größe der empfangenen Programmdaten, kann kleiner oder gleich der Größe der entsprechenden gesamten Daten sein. Es wird wieder angenommen, dass die "gesamten Daten" die Daten sind, die in einem entlang einer Zeilenrichtung angeordneten Satz an Speicherzellen zu programmieren ist. Wie oben, können die Programmdaten von einer externen Vorrichtung EX im Controller 1300 bereitgestellt werden.

**[0114]** Es wird ermittelt, ob die empfangenen Programmdaten zusammen mit den in dem Direktzugriffsspeicher **1200** angehäuften Daten die gesamten Daten (z. B. ob die empfangenen Programmdaten und die in dem Direktzugriffsspeicher **1200** angehäuften Daten einem definierten Satz an Multi-Seitendaten entsprechen) (S420). Hier wird angenommen, dass eine Speicherzelle geeignet ist um N-Bits zu speichern. Das heißt, falls (N – 1) Bits in jede der in Zeilenrichtung angeordneten Speicherzellen, die in dem Direktzugriffsspeicher **1200** angehäuft sind, programmiert werden sollen und ein Ntes-Bit empfangen wird, wird die Erfassung als gesamte Daten (S420 = Ja) positiv erfasst.

**[0115]** Zur Wiederholung, der Controller **1300** wird verwendet, um zu erfassen, ob die gesamten Daten vorhanden sind, inklusive der in dem Direktzugriffsspeicher **1200** akkumulierten Daten und den von der externen Vorrichtung EX empfangenen Programmdaten.

[0116] Falls die in dem Zugangszugriffsspeicher 1200 angehäuften Daten und die von der externen Vorrichtung EX empfangenen Programmdaten nicht den gesamten Daten (z. B. dass die Daten nicht den definierten Multi-Seitendaten entsprechen) entsprechen (S420 = Nein), dann werden die Programmdaten lediglich in dem Direktzugriffsspeicher 1200 (S430) gespeichert. Der Controller 1300 kann verwendet werden, um die Programmdaten in dem Direktzugriffsspeicher 1200 zu speichern.

[0117] Falls jedoch die in dem Direktzugriffsspeicher 1200 akkumulierten Daten und die von der externen Vorrichtung EX empfangenen Programmdaten den Multi-Seitendaten entsprechen (S420 = Ja), werden die in dem Direktzugriffsspeicher 1200 angehäuften Daten in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen (S440). Und die empfangenen Programmdaten werden in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen (S450). Der Controller 1300 kann verwendet werden, um die in dem Direktzugriffsspeicher 1200 angehäuften Daten oder die empfangenen Programmdaten zu dem dreidimensionalen nichtflüchtigen Speicher 1100 zu übertragen. In diesem Fall werden Multi-Seitendaten in den Seitenpuffer 1130 geladen.

**[0118]** Die in den Seitenpuffer **1130** geladenen Multi-Seitendaten können gleichzeitig in die in Zeilenrichtung angeordneten Speicherzellen des Speicherzellarrays **1110** des dreidimensionalen nichtflüchtigen Speichers **1100** programmiert werden.

**[0119]** Fig. 15 zeigt ein Diagramm, das eine Ausführungsform darstellt, in welcher das Speichersystem aus Fig. 1 einen Programmiervorgang gemäß dem Programmierverfahren aus Fig. 14 geführt. Bezug-

nehmend auf die Fig. 14 und Fig. 15 können LSB-Seitendaten PD1 und CSB-Seitendaten PD2 zusammen oder unabhängig voneinander dem Controller 1300 von einer externen Vorrichtung EX bereitgestellt werden. Die LSB-Seitendaten PD1 und CSB-Seitendaten PD2, können dem Controller 1300 unabhängig von der externen Vorrichtung EX bereitgestellt werden

**[0120]** Wenn LSB-Seitendaten PD1 empfangen werden, können die Eingangsdaten und die in dem Direktzugriffsspeicher **1200** angehäuften Daten nicht den Multi-Seitendaten entsprechen. Der Controller **1300** kann daher die LSB-Seitendaten PD1 in dem Direktzugriffsspeicher **1200** speichern.

**[0121]** Wenn CSB-Seitendaten PD2 empfangen werden, können die Eingangsdaten und die in dem Direktzugriffsspeicher **1200** angehäuften Daten nicht den Multi-Seitendaten entsprechen. Der Controller **1300** kann daher die CSB-Seitendaten PD2 in dem Direktzugriffsspeicher **1200** speichern.

[0122] Wenn MSB-Seitendaten PD3 empfangen werden, können die Eingangsdaten und die in dem Direktzugriffsspeicher 1200 angehäuften Daten den Multi-Seitendaten entsprechen. Das heißt, der Controller 1300 kann die LSB- und CSB-Seitendaten PD1 und PD2, die in dem Direktzugriffsspeicher 1200 angehäuft sind, an einen dreidimensionalen nichtflüchtigen Speicher 1110 übertragen. Auch kann der Controller 1300 die MSB-Seitendaten PD3, die von der externen Vorrichtung EX eingegeben wurden, direkt an den dreidimensionalen nichtflüchtigen Speicher 1110 übertragen ohne durch den Direktzugriffsspeicher 1200 zu gehen.

[0123] Der dreidimensionale nicht flüchtige Speicher 1100 kann die Eingangsmultiseitendaten PD1, PD2 und PD3 in einen Seitenpuffer 1130 laden. Die in den Seitenpuffer 1130 geladenen Multi-Seitendaten PD1, PD2 und PD3, können gleichzeitig in entlang einer Zeilenrichtung angeordnete Speicherzellen des Speicherzellenarrays 10 programmiert werden.

[0124] Fig. 16 zeigt ein Diagramm, das eine andere Ausführungsform darstellt, in dem das Speichersystem aus Fig. 1 einen Programmiervorgang gemäß dem Programmierverfahren aus Fig. 14 durchführt. Bezugnehmend auf die Fig. 14 und Fig. 16 werden LSB-Seitendaten PD1 und CSB-Seitendaten PD2 in einer externen Vorrichtung EX unabhängig einem Controller 1300 zur Verfügung gestellt. CSB-Seitendaten PD2 und MSB-Seitendaten PD3, können in dem Controller 1300 auch zusammen von einer externen Vorrichtung bereitgestellt werden.

**[0125]** Wenn LSB-Seitendaten PD1 empfangen werden, können die Eingangsdaten und die in dem Direktzugriffsspeicher **1200** angehäuften Daten, den

Multi-Seitendaten nicht entsprechen. In dem Fall speichert der Controller **1300** die LSB-Seitendaten PD1 in dem Direktzugriffsspeicher **1200**.

[0126] Wenn die CSB-Seitendaten PD2 und MSB-Seitendaten PD3 empfangen werden, können die Eingangsdaten, die in dem Direktzugriffsspeicher 1200 angehäuften Daten, den Multi-Seitendaten entsprechen. In dem Fall beträgt der Controller 1300 die LSB-Seitendaten PD1, die in dem Direktzugriffsspeicher 1200 angehäuft sind, an einem dreidimensionalen nichtflüchtigen Speicher 1110. Der Controller 1300 kann die CSB-Seitendaten PD2 und MSB-Seitendaten PD3, die von der externen Vorrichtung EX eingegeben wurden, auch direkt an den dreidimensionalen nichtflüchtigen Speicher 1100 übertragen, ohne durch den Direktzugriffsspeicher 1200 zu gehen.

[0127] Der dreidimensionale nichtflüchtige Speicher 1300 kann die Multi-Seitendaten PD1, PD2 und PD3 in einen Seitenpuffer 1130 laden. Die Multi-Seitendaten PD1, PD2 und PD3, die in den Seitenpuffer 1130 geladen wurden, können gleichzeitig in die entlang einer Zeichenrichtung angeordneten Speicherzellen eines Speicherzellarrays 1110 programmiert werden.

[0128] Übereinstimmend in den Fig. 14, Fig. 15 und Fig. 16 beschriebenen Ausführungsformen ist der Direktzugriffsspeicher 1200 geeignet, um einen Teil der gesamten Daten (z. B. einen Teil der definierten Multi-Seitendaten) zu speichern. Das heißt, es ist möglich, die Speicherkapazität (oder Größe) des Direktzugriffsspeichers 1200, der dem Speichersystem 1000 aus Fig. 1 bereitgestellt sein muss, zu reduzieren.

**[0129]** Fig. 17 zeigt ein Ablaufdiagramm, das eine andere Ausführungsform eines Pufferprogrammierverfahren unter Verwendung des Direktzugriffsspeichers aus Fig. 1 zeigt. Bezugnehmend auf die Fig. 1, Fig. 3 und Fig. 17, werden Programmdaten empfangen (S510). Wie oben muss die Größe der empfangenen Programmdaten kleiner oder gleich der gesamten Daten sein, um in die entlang einer Zeilenrichtung angeordneten Speicherzellen programmiert werden zu können.

**[0130]** Wenigstens einmal wird erfasst, ob die empfangenen Programmdaten einen bestimmten Teil der definierten Multi-Seitendaten entspricht. In dem in **Fig. 17** dargestellten Beispiel, zum Beispiel wird erfasst, ob die empfangenen Daten den LSB-Seitendaten entsprechen (S520), und dann wird erfasst, ob die empfangenen Daten den MSB-Seitendaten entsprechen (S530). Falls die empfangenen Programmdaten den LSB-Seitendaten entsprechen (S520 = Ja), werden die Programmdaten direkt in den Seitenpuffer **1230** des dreidimensionalen nichtflüchtigen Speichers **1100** geladen, ohne durch den Direktzu-

griffsspeicher **1200** zu den (S521). Dann werden die in den Seitenpuffer **1130** geladenen LSB-Seitendaten für die entlang einer Zeilenrichtung angeordneten Speicherzellen programmiert (S520).

[0131] Wenn die empfangenen Programmdaten nicht den LSB-Seitendaten entsprechen (S520 = Nein), dann wird erfasst, ob die empfangenen Daten den MSB-Seitendaten entsprechen (S530). Falls die empfangenen Programmdaten nicht den entsprechenden MSB-Seitendaten entsprechen (S530 = Nein), dann werden, falls die eingegebenen Programmdaten den CSB-Seitendaten entsprechen, die CSB-Seitendaten derart in den Direktzugriffsspeicher 1200 gespeichert (S531).

[0132] Wenn jedoch die empfangenen Programmdaten den MSB-Seitendaten entsprechen (S530 = Ja), werden die in dem Direktzugriffsspeicher 1200 akkumulierten Daten direkt in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers geladen (S540) und die empfangenen Programmdaten werden in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1300 geladen (S550). Die Controller 1300 kann daher verwendet werden, um die in den Direktzugriffsspeichers 1200 angehäuften CSB-Daten und die von der externen Vorrichtung EX empfangen MSB-Seitendaten zu den dreidimensionalen nichtflüchtigen Speicher 1300 zu übertragen. Der dreidimensionale nichtflüchtige Speicher 1300 kann die CSB- und MSB-Seitendaten in den Seitenpuffer 1130 laden.

**[0133]** Dann können die in den Seitenpuffer **1130** geladenen CSB- und MSB-Seitendaten die entlang einer Zeilenrichtung angeordneten Speicherzellen gleichzeitig programmiert werden (S560).

[0134] Fig. 18 zeigt ein Diagramm, das ein Beispiel darstellt, in dem das Speichersystem aus Fig. 1 einen Programmiervorgang gemäß einem in Fig. 17 gezeigten Programmierverfahren duldet. Bezugnehmend auf die Fig. 17 und Fig. 18 werden MSB-Seitendaten PD1, CSB-Seitendaten, PD2 und MSB-Seitendaten PD3 einem Controller 1300 von einer externen Vorrichtung und EX unabhängig zur Verfügung gestellt.

[0135] Wenn die LSB-Seitendaten empfangen werden, kann der Controller 1300 die eingegebenen LSB-Seitendaten direkt in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1300 laden, ohne durch den Direktzugriffsspeicher 1200 hindurch zu gehen. Die in den Seitenpuffer 1130 geladenen LSB-Seitendaten PD1 können in die entlang einer Zeilenrichtung angeordneten Speicherzellen programmiert werden.

[0136] Wenn CSB-Seitendaten PD2 empfangen werden, speichert der Controller 1300 in die einge-

gebenen CSB-Seitendaten in dem Direktzugriffsspeicher **1200**.

[0137] Wenn MSB-Seitendaten PD3 empfangen werden, überträgt der Controller 1300 die in dem Direktzugriffsspeicher 1200 angehäuften CSB-Seitendaten PD2 zu dem dreidimensionalen nichtflüchtigen Speicher 1100. Der Controller 1200 kann die MSB-Seitendaten PD3 von der externen Vorrichtung EX auch direkt in dem dreidimensionalen nichtflüchtigen Speicher 1100 übertragen, ohne durch den Direktzugriffsspeicher 1200 hindurch zu treten. Der dreidimensionale nichtflüchtige Speicher 1100 kann die CSB- und MSB-Seitendaten in den Seitenpuffer 1130 anpumpen. Die in den Seitenpuffer 1130 geladenen CSB- und MSB-Seitendaten PD2 und PD3 können gleichzeitig in die entlang einer Zeilenrichtung angeordneten Speicherzellen eines Speicherzellenarrays 1110 gleichzeitig programmiert werden.

**[0138]** In den dargestellten Ausführungsformen können Einzel-Seitendaten der Multi-Seitendaten in dem Direktzugriffsspeicher **1200** gespeichert werden. Es ist dadurch möglich, die Speicherkapazität (oder Größe) des Direktzugriffsspeichers **1200** zu verringern.

**[0139]** In den dargestellten Ausführungsformen können die Programmdaten ein Teil der Einzel-Seitendaten sein und müssen nicht den gesamten Einzel-Seitendaten entsprechen. In diesem Fall kann der Controller **1300** verwendet werden, um den empfangenen Teil der Einzel-Seitendaten zu speichern bis die gesamten Einzel-Seitendaten empfangen wurden.

[0140] Zum Beispiel, wenn ein erster Teil der LSB-Daten empfangen wurde, kann der Controller 1300 verwendet werden, um den Teil der LSB-Daten in dem Zufallzugriffsspeicher 1200 zu speichern. Danach, falls die empfangenen Programmdaten und in die in dem Direktzugriffsspeicher 1200 akkumulierten Daten den LSB-Seitendatendaten entsprechen, kann der Controller 1300 die Programmdaten und die in dem Direktzugriffsspeicher 1200 angehäuften Daten in den dreidimensionalen nichtflüchtigen Speicher 1100 übertragen. Die empfangenen Programmdaten können direkt in den dreidimensionalen nichtflüchtigen Speicher 1100 übertragen werden, ohne durch den Direktzugriffsspeicher 1200 hindurch zu gehen. Der Empfang der CSB-Seitendaten und der MSB-Seitendaten können gleichzeitig behandelt wer-

[0141] Fig. 19 zeigt ein Flussdiagramm, das eine andere Ausführungsform des Pufferprogrammierens unter Verwendung des Direktzugriffsspeichers aus Fig. 1 zusammenfasst. Bezugnehmend auf die Fig. 1, Fig. 3 und Fig. 19 werden Programmdaten empfangen (S610). Wie vorher kann die Größe der empfangenen Daten kleiner oder gleich der gesam-

ten Daten sein, die entlang der Zeilenrichtung angeordneten Speicherzellen zu programmieren sind.

[0142] Es wird erfasst, ob die empfangenen Programmdaten zusammen mit dem Direktzugriffsspeicher akkumulierten Daten (kollektive Daten) einem ersten Teil der Multi-Seitendaten entsprechen (S620). Der Controller 1300 kann verwendet werden, um zu erfassen, ob die kollektiven Programmdaten einen ersten Teil der Multi-Seitendaten entsprechen. Beispielsweise kann der Controller 1300 erfassen, ob die kollektiven Programmdaten den LSB-Seitendaten entsprechen oder ob die kollektiven Programmdaten den LSB-Seitendaten und CSB-Seitendaten entsprechen.

[0143] Falls die kollektiven Programmdaten einen ersten Teil der Multi-Seitendaten (S620 = Ja) entsprechen, werden sie in dem Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1100 geladen (S630). In der in Fig. 19 dargestellten Ausführungsform können die kollektiven Programmdaten in den Seitenpuffer 1130 geladen werden, ohne durch den Direktzugriffsspeicher 1200 hindurch zu gehen. Die in den Seitenpuffer 1130 geladenen kollektiven Daten können in die Speicherzellen der entlang einer Zeilenrichtung angeordneten Speicherzellen des Speicherzellenarrays 1110 programmiert werden (S640).

[0144] Wenn jedoch die Kollektivprogrammdaten nicht dem ersten Teil der Multi-Seitendaten entsprechen (S620 = Nein), dann wird erfasst, ob die kollektiven Programmdaten einem zweiten Teil der Multi-Seitendaten entsprechen (S650). Der Controller 1300 wird wieder verwendet, um zu erfassen, ob die kollektiven Programmdaten den CSB-Seitendaten oder den MSB-Seitendaten entsprechen.

[0145] Falls die kollektiven Programmdaten den zweiten Teil der Multi-Seitendaten entsprechen (S650 = Ja), dann werden unter Verwendung der oben beschriebenen Schritte S630 und S640 der zweite Teil der Multi-Seitendaten gleichzeitig in die Speicherzellen des dreidimensionalen nichtflüchtigen Speichers 1100 programmiert.

**[0146]** Wenn jedoch die kollektiven Programmdaten nicht den zweiten Teil der Multi-Seitendaten entsprechen (S650 = Nein), dann werden die kollektiven Programmdaten in dem Direktzugriffsspeicher **1200** gespeichert (S660).

[0147] Fig. 20 zeigt ein Diagramm, das ein Beispiel darstellt, in dem das Speichersystem aus Fig. 1 einen Programmablauf gemäß dem in Fig. 19 gezeigten Programmierverfahren durchführt. Bezugnehmend auf die Fig. 19 und Fig. 20 kann ein erster Teil der Multi-Seitendaten LSB-Seitendaten PD1 und

CSB-Seitendaten PD2 sein, und ein zweiter Teil davon können MSB-Seitendaten PD3 sein.

[0148] LSB-Seitendaten PD1 und CSB-Seitendaten PD2 können nacheinander in einen Direktzugriffsspeicher 1200 geladen werden. Die LSB-Seitendaten PD1 und die CSB-Seitendaten PD2, die in dem Direktzugriffsspeicher 1200 gespeichert sind, können in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1300 geladen werden, im in die entlang einer Zeilenrichtung angeordneten Speicherzellen eines Speicherzellarrays 1110 gleichzeitig programmiert zu werden.

[0149] Danach können MSB-Seitendaten PD3 in den Direktzugriffsspeicher 1200 gespeichert werden. Die in dem Direktzugriffsspeicher 1200 gespeicherten MSB-Seitendaten PD3 können in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen 1300 geladen werden, um in die entlang einer Zeilenrichtung angeordneten Speicherzellen des Speicherzellarrays 1110 gleichzeitig programmiert zu werden. Die MSB-Seitendaten PD3 können in die gleichen Speicherzellen programmiert werden, wie die, in die die LSB- und CSB-Seitendaten PD1 und PD2 programmiert sind.

[0150] Fig. 21 zeigt ein Diagramm, das ein weiteres Beispiel darstellt, in dem ein Speichersystem aus Fig. 1 einen Programmierablauf gemäß der in Fig. 19 gezeigten Programmiermethode durchführt. Bezugnehmend auf die Fig. 19 und Fig. 21 kann ein erster Teil der Multi-Seitendaten LSB-Seitendaten PD1 sein und zweiter Teil davon können CSB-Seitendaten PD2 und MSB-Seitendaten PD3 sein.

[0151] LSB-Seitendaten PD1 können in dem Direktzugriffsspeicher 1200 gespeichert werden. Die in dem Direktzugriffsspeicher 1200 gespeicherten LSB-Seitendaten PD1 können in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1300 geladen werden, um in die entlang einer Zeilenrichtung angeordneten Speicherzellen eines Speicherzellarrays 1110 programmiert zu werden.

[0152] Danach können CSB-Seitendaten PD2 und MSB-Seitendaten PD3 in dem Direktzugriffsspeicher 1200 gespeichert werden. Die CSB-Seitendaten und MSB-Seitendaten PD3, die in dem Direktzugriffsspeicher 1200 gespeichert sind, können in den Seitenpuffer 1130 des dreidimensionalen nichtflüchtigen Speichers 1300 geladen werden, um in die entlang einer Zeilenrichtung angeordneten Speicherzellen eines Speicherzellarrays 1110 gleichzeitig programmiert zu werden. Die CSB-Seitendaten PD2 und MSB-Seitendaten PD3 können die gleichen Speicherzellen, wie die, in denen die LSB-Seitendaten PD1 programmiert sind, programmiert werden.

[0153] Wenn eine Speicherzelle N-Bitdaten speichert, d. h. wenn eine Multi-Seite N separate Datenseiten enthält, kann jede Seite der einzelnen Multi-Seiten geteilt und programmiert werden. Zum Beispiel können einzelne Seiten eines ersten Teils einer Multi-Seite in Zeilenrichtung angeordneten Speicherzellen, die gleichzeitig programmiert werden und einzelne Seiten eines zweiten Teils der Multi-Seite kann außerdem die in Zeilenrichtung angeordnete Speicherzellen gleichzeitig programmiert werden. Gemäß der vorgehend dargestellten Ausführungsformen kann die Speicherkapazität (oder Größe) des Direktzugriffsspeichers 1200 verringert werden. Das heißt, ein Ausgleich zwischen der Anzahl der Programmierschritte, die die Speicherzellen eines dreidimensionalen nichtflüchtigen Speichers 1100 erfahren und die Speicherkapazität des Direktzugriffsspeichers 1200 können ausgewertet und durchgeführt werden.

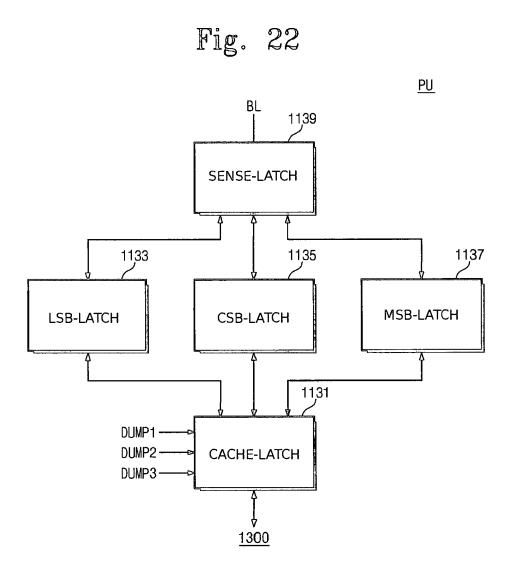

[0154] Fig. 22 ist ein Blockdiagramm das eine der Seitenpuffereinheiten aus Fig. 3 darstellt. Bezugnehmend auf Fig. 22 kann eine Seitenpuffereinheit PU ein Cache-Latch 1131, ein LSB-Latch 1133, ein CSB-Latch 1135, und ein MSB-Latch 1137, und ein Sense-Latch 1139 enthalten.

[0155] Das Cache-Latch 1131 kann mit dem Controller 1300 Daten austauschen. Das Cache-Latch 1131 reagiert auf Dump-Signale Dump1, Dump2 und Dump3, die von der Steuerlogik 1140 bereitgestellt werden.

[0156] Während des Programmierens, kann das Cache-Latch 1131 Daten von dem Controller 1300 empfangen. Wenn das Dump-Signal Dump1 aktiviert wird überträgt das Cache-Latch 1131 gespeicherte Daten zu dem LSB-Latch 1133. Wenn das Dump-Signal Dump2 aktiviert wird überträgt das Cache-Latch 1131 gespeicherte Daten zu dem CSB-Latch 1135.

[0157] Wenn das Dump-Signal Dump3 aktiviert ist überträgt das Cache-Latch 1131 gespeicherte Daten zu dem MSB-Latch 1137. Beispielsweise können LSB-Seitendaten in das LSB-Latch 1133 geladen werden, CSB-Seitendaten können auf das CSB-Latch 1135 geladen werden und MSB-Seitendaten können auf das MSB-Latch 1137 geladen werden.

[0158] Das Sense-Latch 1139 kann mit einer Bitleitung verbunden sein. Während des Programmierens kann das Sense-Latch 1139 die Bitleitung BL entsprechend der in dem LSB-, CSB- und MSB-Latch es 1133, 1135 und 1137 gespeicherten Daten unter Spannung setzen. Während der Programmierverifizierung kann das Sense-Latch 1139 die Spannung der Bitleitung BL erfassen. Beispielsweise kann das Sense-Latch 1139 das Erfassungsergebnis entsprechend der in dem LSB-, CSB- und MSB-Latch 1133, 1135 und 1137 gespeicherten Daten anpassen.

**[0159]** Fig. 23 zeigt ein Taktdiagramm das ein Beispiel an Signalen darstellt, die von einem Controller während des Programmierens an einen dreidimensionalen flüchtigen Speicher übertragen werden. Bezugnehmend auf die Fig. 1, Fig. 22 und Fig. 23 überträgt ein Controller 1300 während eines ersten Zyklus C1 einen Programmbefehl 80 h zu einem dreidimensionalen nichtflüchtigen Speicher 1100.

**[0160]** Während eines zweiten Zyklus C2, sendet der Controller **1300** eine Adresse ADDR zu dem dreidimensionalen nichtflüchtigen Speicher **1100**. Die Adresse ADDR kann entlang einer Zeilenrichtung angeordnete Speicherzellen des dreidimensionalen nichtflüchtigen Speichers **1100** bezeichnen.