(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3986571号

(P3986571)

(45) 発行日 平成19年10月3日(2007.10.3)

(24) 登録日 平成19年7月20日(2007.7.20)

(51) Int.C1.

F 1

HO 1 L 21/66 (2006.01)

HO 1 L 21/66

請求項の数 8 (全 13 頁)

(21) 出願番号 特願平6-306035

(22) 出願日 平成6年12月9日(1994.12.9)

(65) 公開番号 特開平8-162510

(43) 公開日 平成8年6月21日(1996.6.21)

審査請求日 平成13年12月6日(2001.12.6)

審判番号 不服2005-18762(P2005-18762/J1)

審判請求日 平成17年9月29日(2005.9.29)

(73) 特許権者 390020248

日本テキサス・インスツルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 小松崎 孝雄

東京都港区北青山3丁目6番12号 青山

富士ビル日本テキサス・インスツルメンツ

株式会社内

(72) 発明者 宮井 羊一

東京都港区北青山3丁目6番12号 青山

富士ビル日本テキサス・インスツルメンツ

株式会社内

最終頁に続く

(54) 【発明の名称】歩留り予測装置とその方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体チップの製造時の歩留りを予測する歩留り予測装置であって、

予め算出したノイズ粒子の粒径分布に基づいて、所定の複数個の半導体チップに付着するノイズ粒子を生成し、該生成されたノイズ粒子各々に当該ノイズ粒子が付着する半導体チップの識別番号を付与するノイズ粒子生成手段と、

前記生成されたノイズ粒子全てを1個のマスク上に配置するノイズ粒子配置手段と、

前記配置されたノイズ粒子により、マスクのパタンが欠陥となるか否かを各ノイズ粒子ごとに検出する欠陥検出手段と、

前記各ノイズ粒子ごとの欠陥検出結果と、該ノイズ粒子各々に付与された前記半導体チップ識別番号に基づいて、欠陥の生じる半導体チップの数を集計し、該集計結果より半導体チップの歩留りを算出する歩留り算出手段と、

を有する歩留り予測装置。

## 【請求項2】

前記欠陥検出手段は、前記配置されたノイズ粒子の近傍のマスクデータのみを読み出し、マスクのパタンが欠陥となるか否かを検出する

請求項1記載の歩留り予測装置。

## 【請求項3】

半導体チップの製造時の歩留りを予測する方法であって、

予め算出したノイズ粒子の粒径分布に基づいて、所定の複数個の半導体チップに付着す

10

20

るノイズ粒子を生成し、

前記生成されたノイズ粒子各々に、該ノイズ粒子が付着する半導体チップの識別番号を付与し、

前記生成されたノイズ粒子全てを1個のマスク上に配置し、

前記配置された各ノイズ粒子により、マスクのパタンが欠陥となるか否かを検出し、

前記検出結果と、前記ノイズ粒子各々に付与された前記半導体チップ識別番号に基づいて欠陥となる半導体チップの数を集計し、

該集計結果に基づいて半導体チップの歩留りを算出する、

歩留り予測方法。

**【請求項 4】**

10

前記ノイズ粒子の粒径分布を算出する段階が、

1組の欠陥密度チェックパタンを有する1組の半導体チップを選択された半導体製造現場において製造する段階と、

ノイズ粒子の粒径に対応する欠陥率を決定するために1組の半導体チップの歩留まりを分析する段階と、

1組の半導体チップの欠陥率に対応するノイズ粒子の粒径分布を求める段階と、

を有する、

請求項 3 記載の歩留り予測方法。

**【請求項 5】**

20

前記ノイズ粒子の粒径分布が粒径依存性とノイズ粒子密度とを有する、

請求項 4 記載の歩留り予測方法。

**【請求項 6】**

各欠陥密度チェックパタンが導体線間の一定の間隔を有し、

1組の欠陥密度チェックパタンが導体線間の選択された数の異なった間隔を有する、

請求項 5 記載の歩留り予測方法。

**【請求項 7】**

前記ノイズ粒子の粒径分布を算出する段階が、1組の半導体チップの欠陥密度チェックパタンを表わす歩留まり式を解く段階を更に有する、

請求項 6 記載の歩留り予測方法。

**【請求項 8】**

30

前記ノイズ粒子の粒径分布を算出する段階が、1組の半導体チップのノイズ粒子の粒径に対応する欠陥率に対する歩留まり式を帰納的に合わせ込む段階を更に有する、

請求項 7 記載の歩留り予測方法。

**【発明の詳細な説明】**

**【0001】**

**【産業上の利用分野】**

本発明は、半導体チップの製造時の歩留りを予測する歩留り予測装置とその予測方法に関する。

**【0002】**

**【従来の技術】**

40

半導体チップ（以後、ICチップと言う場合もある）の欠陥の主要な原因としては、製造プロセスにおいて、空気中に存在する浮遊粒子がチップ表面に付着し、局所的に回路欠陥が発生する現象が挙げられる。この場合、粒子が付着したときのマスクデータと、その付着した粒子の大きさ・位置を特定することができれば、欠陥の発生箇所を特定することができ、半導体チップの歩留りを計算することができる。

しかし、現実に製造環境に存在する粒子の粒径分布は流動的であり粒径ごとの存在確率を求めるることはできても、マスクにおける粒子の仮想的な付着位置を確定することは困難である。さらに、その粒子の分布と、それがICチップ製造時に引き起こす欠陥の位置関係を結び付けることは、人為的な要素や製造過程での不確定要素も加わり非常に困難である。

50

**【0003】**

そのため、これまで、半導体チップの歩留りを予測する方法としては、特開昭48-40376号公報に開示されている方法があった。これは、半導体チップのレイアウト上に任意の形状の欠陥を不規則分布に基づいて配置し、その配置された欠陥のうち、そのレイアウトにおいてクリティカルな領域に配置された欠陥の数を計数することにより、前記欠陥が欠陥半導体チップを生じせしめる確率を求める方法であった。

**【0004】**

また、本願出願人らは、より高精度に歩留りを予測するために、予め調べた製造環境の粒径分布に基づいたノイズ粒子を、仮想的に同一マスクを多数配列したパターン（仮想的なウエハ）上にランダムに配置し、前記多数のマスクのうち欠陥を生じなかったマスク数を計数することにより、半導体チップの歩留りを予測していた。10

**【0005】**

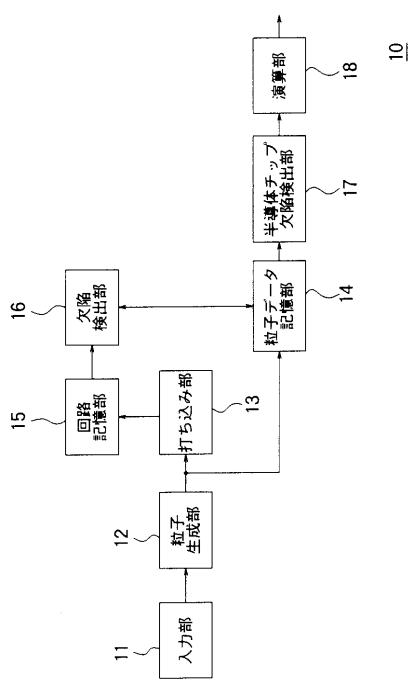

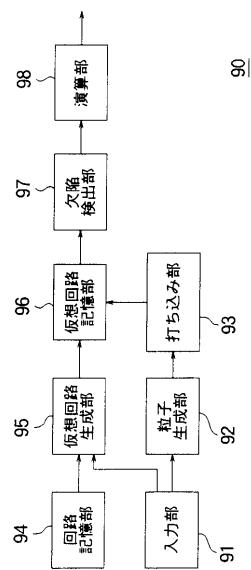

そのような方法で半導体チップの歩留りを予測する歩留り予測装置の構成について、図7を参照して説明する。

図7は、これまでの歩留り予測装置の構成を示す概略ブロック図である。

歩留り予測装置90は、入力部91、粒子生成部92、打ち込み部93、回路記憶部94、仮想回路生成部95、仮想回路記憶部96、欠陥検出部97、演算部98より構成される。

**【0006】**

歩留り予測装置90においては、入力部91より製造現場のノイズ粒子のデータと、仮想回路のデータを入力する。その入力された仮想回路のデータに基づいて、仮想回路生成部95において、ウエハにおける半導体チップの配置に基づいて回路記憶部94に記憶されているマスクデータを所定数、所定の位置に配列し、仮想的に同一マスクが多数配列されたパターン（仮想的なウエハ）を生成し、仮想回路記憶部96に記憶する。20

また、入力された製造現場のノイズ粒子のデータに基づいて、その製造現場と同様のノイズ粒子の分布を粒子生成部92で生成し、打ち込み部93で仮想回路記憶部96に記憶されている複数のマスクよりなる仮想的なウエハのパターンデータ上にランダムに配置する。

**【0007】**

次に、欠陥検出部97において、仮想回路記憶部96に記憶されているパターンの各マスクデータを順次走査し、前記ランダムに配置されたノイズ粒子がそのマスクデータ上に存在するか否か、また、存在する場合にはそのノイズ粒子により、回路パターンが欠陥となっているか否かを順次調べる。そして、前記調査結果に基づいて、演算部98において、欠陥を生じなかったマスクの全マスクに対する割合を算出し、歩留りとして出力する。30

この予測装置によれば、製造現場のノイズ粒子の状態を反映しているので、製造時の実際の値に近い歩留りを予測することができる。また、半導体チップとしての歩留りは、前記各マスクごとの処理を繰り返し行うことにより予測することができる。

**【0008】****【発明が解決しようとする課題】**

しかし、前述したマスクデータと製造現場のノイズ粒子の分布を用いて歩留りを予測する予測装置において、マスクデータを順次走査し、ノイズ粒子がそのマスクデータ上に存在するか否か、存在する場合にはそのノイズ粒子により回路パターンが欠陥となっているか否かを順次調べる処理は、マスクデータ自体が膨大なデータ量を持つことから、長時間の処理が必要になるという問題があった。40

また、そのマスクデータを統計的処理が可能な程度に多数仮想的に配置し、その多数のマスクデータ全てに対して前記走査を行い欠陥を調べることは、前記走査時間がマスク数分必要となるのに加えて、各マスクデータごとに階層化され記述されたマスクパターンのデータを1つずつ展開する処理も必要となり、一層処理時間が必要となった。

**【0009】**

また、そのような膨大なマスクデータを記憶する記憶領域が必要であり、実用的な予測装置ができなかった。50

また、処理時間を短縮し、小さな記憶領域で歩留りの予測を行うために、マスクデータを簡略化して前記処理を行う方法が取られる場合もあったが、その場合には、正確な歩留りの予測が行えないという問題もあった。

#### 【0010】

したがって、本発明の目的は、製造現場のノイズ分布に基づいて発生させたノイズ粒子を半導体チップの各マスクデータに配置させ、統計的処理により前記半導体チップの歩留りを予測する歩留り予測装置において、前記歩留り予測の処理を高速に、小さな計算資源を用いて実現することが可能な歩留り予測装置を提供することにある。

#### 【0011】

##### 【課題を解決するための手段】

10

前述したような歩留り予測装置においては、同一のマスクを多数配置した仮想的なパタンデータ（ウエハ）を使用しているために、膨大な記憶資源と処理時間が必要となっていることを考慮して、1個のマスクデータに対して、複数の半導体チップに夫々付着するノイズ粒子を対応付けて欠陥を解析することにより、多数のマスクを用いたのと同様な統計的処理が行えるようにした。

また、その1個のマスクに対する欠陥の解析を行う際にも、ノイズ粒子に基づいてマスクデータをアクセスするようにし、高速に欠陥の検出が行えるようにした。

#### 【0012】

本発明によれば、半導体チップの製造時の歩留りを予測する歩留り予測装置であって、予め算出したノイズ粒子の粒径分布に基づいて、所定の複数個の半導体チップに付着するノイズ粒子を生成し、該生成されたノイズ粒子各々に当該ノイズ粒子が付着する半導体チップの識別番号を付与するノイズ粒子生成手段と、前記生成されたノイズ粒子全てを1個のマスク上に配置するノイズ粒子配置手段と、前記配置されたノイズ粒子により、マスクのパタンが欠陥となるか否かを各ノイズ粒子ごとに検出する欠陥検出手段と、前記各ノイズ粒子ごとの欠陥検出結果と、該ノイズ粒子各々に付与された前記半導体チップ識別番号に基づいて、欠陥の生じる半導体チップの数を集計し、該集計結果より半導体チップの歩留りを算出する歩留り算出手段とを有する歩留り予測装置が提供される。

20

#### 【0013】

好ましくは、前記欠陥検出手段は、前記配置されたノイズ粒子の近傍のマスクデータのみを読み出し、マスクのパタンが欠陥となるか否かを検出する。

30

#### 【0014】

また本発明によれば、半導体チップの製造時の歩留りを予測する方法であって、予め算出したノイズ粒子の粒径分布に基づいて、所定の複数個の半導体チップに付着するノイズ粒子を生成し、

前記生成されたノイズ粒子各々に、該ノイズ粒子が付着する半導体チップの識別番号を付与し、

前記生成されたノイズ粒子全てを1個のマスク上に配置し、

前記配置された各ノイズ粒子により、マスクのパタンが欠陥となるか否かを検出し、

前記検出結果と、前記ノイズ粒子各々に付与された前記半導体チップ識別番号に基づいて欠陥となる半導体チップの数を集計し、

40

該集計結果に基づいて半導体チップの歩留りを算出する、

歩留り予測方法が提供される。

#### 【0015】

##### 【作用】

本発明の歩留り予測装置によれば、統計的処理が可能なだけの複数個の半導体チップに付着するノイズ粒子を生成し、その生成されたノイズ粒子各々にそのノイズ粒子が付着する半導体チップの識別番号を付与した上で、そのノイズ粒子全てを1個のマスク上に配置する。したがって、マスクパタンを記憶するメモリなどの計算資源は、1個のマスクに対応可能な記憶領域があればよい。

また、その配置された各ノイズ粒子に基づいて、そのノイズ粒子の近傍のマスクパタンを

50

チェックし、そのノイズ粒子が欠陥を生じせしめるか否かを順次調べていく。そして、欠陥が生ずる場合には、そのノイズ粒子に付与された半導体チップ識別番号に基づいて、どの半導体チップが欠陥を生じたかを検出する。そして、欠陥を生じていない半導体チップの数と、前記所定の半導体チップ数より半導体チップの歩留りを算出する。ノイズ粒子をキーにして欠陥のチェックを行っているので無駄がなく、処理を高速に行える。

#### 【0016】

##### 【実施例】

本発明の歩留り予測装置の一実施例を図1～図6を参照して説明する。

図1は、本実施例の歩留り予測装置の構成を示すブロック図である。

歩留り予測装置10は、入力部11、粒子生成部12、打ち込み部13、粒子データ記憶部14、回路記憶部15、欠陥検出部16、半導体チップ欠陥検出部17、演算部18を有する。

以下、各部の動作について説明する。

#### 【0017】

入力部11は、歩留り予測に必要な回路の情報、製造環境の情報、および、歩留り予測のためのパラメータを入力する入力部である。回路の情報としては、ICチップのサイズ(幅Xおよび高さY)を、製造環境の情報としては、単位面積当たりのノイズ粒子の個数D<sub>0</sub>、ノイズ粒子の分布関数の粒径依存性n、粒径条件(最大粒径、最小粒径)を、歩留り予測のためのパラメータとしては、マスク枚数をそれぞれ入力する。

なお、回路のパタンデータは、本実施例においては、予め所定の記憶手段である回路記憶部15にロードしておくものとする。

#### 【0018】

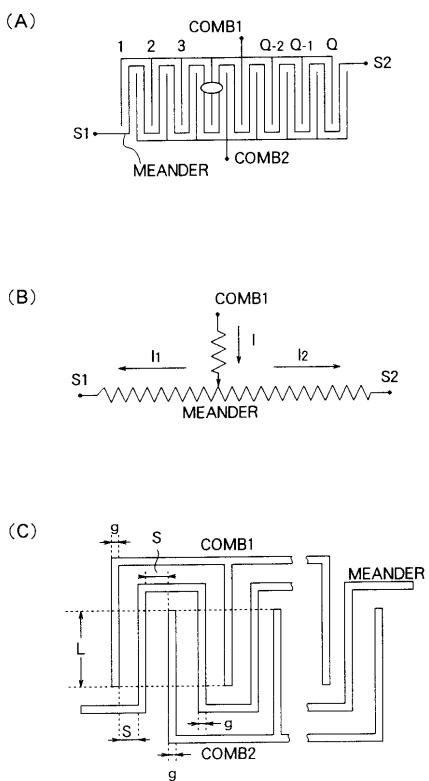

なお、前記製造環境の情報は、製造現場に存在するノイズ粒子の粒径分布D(x)を、図2(A)に示すような基本パタンがレイアウトされている欠陥密度チェック用パタンを用いて予め求めておく。

図2(A)はその欠陥密度チェック用パタンに組み込む基本パタンである。図2(A)において、2つの櫛状回路パタンCOMB1, COMB2と、蛇行回路パタンM E A N D E Rを回路パタンとして配線し、回路パタンCOMB1, COMB2を電源端子とする。

#### 【0019】

この基本パタン上にノイズ粒子が付着した場合、その付着した位置により回路パタンM E A N D E Rの両端子S1, S2から端子COMB1またはCOMB2までの配線の長さが変わるために、端子S1と端子S2で異なった電流が観測される。この電流の流れる状態を図2(B)に示す。したがって、図2(A)に示すように櫛状回路パタンCOMB1の各櫛部を端子S1側よりアドレス1～Qと表した場合、前記ノイズ粒子の付着したアドレスqは、式1で求めることができる。

#### 【0020】

##### 【数1】

$$q = (I_2 \times Q) \bigg/ (I_1 + I_2) \quad \dots (1)$$

40

但し、qは、櫛部のアドレス、

Qは、櫛の数

である。

#### 【0021】

この方法により、櫛状回路パタンCOMB1, COMB2および蛇行回路パタンM E A N D E Rの間隔を変えた種々の前記基本パタンを用いることにより、様々なサイズのノイズ

50

粒子の存在を検出できる。

そして、各サイズのノイズ粒子に対する基本パターン、即ち C O M B 1 , C O M B 2 , M E A N D E R の間隔を種々に変えた基本パターンの歩留りを解析して、帰納的に後述の歩留り式の合わせ込み ( F i t t i n g ) を行い、ノイズ粒子の粒径分布を決定するためのパラメータである単位面積当たりのノイズ粒子の個数  $D_0$  と分布関数の粒径依存性  $n$  を求める。尚、上述の基本パターンの歩留りは、ノイズ粒子が付着したものと不良品とし、ノイズ粒子が付着していないものを良品として求める。また、粒径分布  $D(x)$  を式 2 に示す。

【 0 0 2 2 】

【 数 2 】

$$D(x) = D_0 \cdot \frac{k}{x^n} \quad k = (n-1) \cdot x_0^{n-1} \quad \dots \quad (2)$$

但し、 $D_0$  は、単位面積当たりのノイズ粒子の個数、

$n$  は、粒径依存性、

$x$  は、粒径サイズ、

$x_0$  は、最小粒径

である。

【 0 0 2 3 】

歩留り式  $Y$  は、欠陥密度  $e$  とチップ面積  $A$  とから、ポアソン式  $Y = e \times p(-e \cdot A)$  を仮定し、欠陥密度  $e$  としては式 3 を使用する。

【 0 0 2 4 】

【 数 3 】

$$\lambda = D_0 \left( \frac{x_0}{s} \right)^{n-1} \cdot \frac{s(N-1)L}{n-2} \cdot \left\{ 1 - \frac{N-2}{N-1} \cdot \left( \frac{s}{2s+g} \right)^{n-2} \right\} \quad \dots \quad (3)$$

但し、 $s$  は、各配線パターン間の間隔、

$x_0$  は、最小粒径、

$n$  は、粒径依存性、

$L$  は、C O M B 1 と C O M B 2 が重なる領域の幅、

$N$  は、領域  $L$  に存在する配線パターンの総数 (図 2 (A) の場合、4

$Q-1$ ) 、

$g$  は、各配線パターンの幅

である (図 2 (C) 参照)。

【 0 0 2 5 】

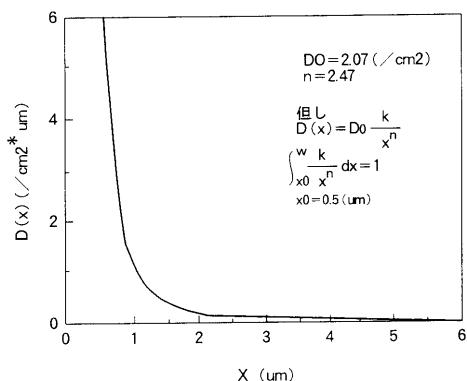

その結果、たとえば図 3 に示すような粒径分布関数が得られる。

【 0 0 2 6 】

粒子生成部 1 2 は、入力部 1 1 より入力された各パラメータに基づき、ノイズ粒子を発生する。粒子生成部 1 2 は、まず生成する粒子の数  $M$  を式 4 に基づいて決定する。

【 0 0 2 7 】

10

20

40

50

## 【数4】

$$M = X \times Y \times N_o \times D_o \quad \dots (4)$$

但し、Mは、生成粒子数、

Xは、チップ幅

Yは、チップ高さ

$N_o$ は、マスク枚数

$D_o$ は、単位面積当たりのノイズ粒子の個数

である。

10

## 【0028】

そして、その粒子の数だけ、図3に示した粒径分布曲線からノイズ粒子のサイズを決定し、乱数によりそのノイズ粒子が付着するチップの番号およびその粒子が付着するチップ内の位置を決定する。発生したノイズ粒子は、打ち込み部13に出力すると同時に、粒子データ記憶部14に記憶しておく。

20

粒子データ記憶部14は、その粒子生成部12で生成された各粒子データを記憶しておく記憶手段でありメモリで構成される。粒子データ記憶部14に記憶されている粒子データの例を図4に示す。

## 【0029】

回路記憶部15は、歩留りを求める半導体チップのマスクパターンを記憶しておく記憶手段である。回路記憶部15は、特定のメモリなどの記憶手段を用意してもよいし、演算部の記憶装置内の所定領域を割り当ててもよい。

打ち込み部13は、粒子生成部12で生成された各粒子データを、回路記憶部15に記憶されているマスクパターンデータ上に実際に配置し書き込む。

30

## 【0030】

欠陥検出部16は、粒子データ記憶部14に記憶されているノイズ粒子のデータに基づいて、回路記憶部15に記憶されているノイズ粒子が付与されたマスクパターンデータをチェックし、そのノイズ粒子によって欠陥が生じているか否かをチェックする。そして、欠陥が生じていた場合には、粒子データ記憶部14の各ノイズ粒子ごとのデータに、欠陥を引き起こしている旨を示すフラグを立てる。

## 【0031】

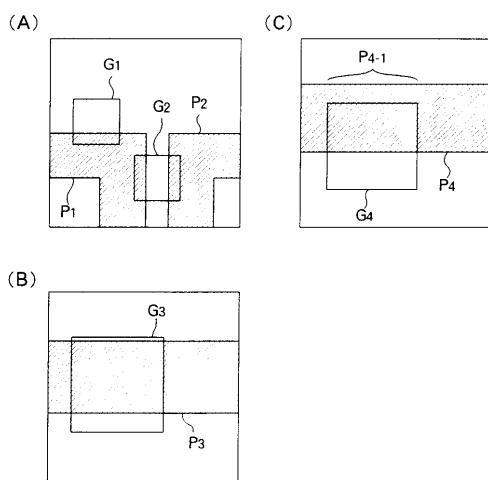

前記欠陥は、配線の短絡と断線に分けて次のように検出する。

まず、ノイズ粒子が2つ以上の配線パターンに接触している場合に、そのノイズ粒子はそれらの配線パターンを短絡させているものとして検出する。たとえば図5(A)に示すノイズ粒子G2は、配線パターンP1とパターンP2の両方に接触して存在しているので、このノイズ粒子G2は欠陥を生じせしめているものとする。また、図5(A)のノイズ粒子G1は、配線パターンP1にしか接触していないので、配線パターンを短絡させておらず、欠陥とはならない。

40

配線の断線については、ノイズ粒子が配線パターンを横断して存在している場合に、その配線パターンの断線が発生したものとする。たとえば、図5(B)に示すように、配線パターンP3にノイズ粒子G3が横断して付着している場合に、配線パターンP3は断線したものとし、ノイズ粒子G3は欠陥を引き起こしたとしてフラグが付与される。尚、図5(B)ではノイズ粒子G3が配線パターンP3を完全に横断しているが、図5(C)に示すように、ノイズ粒子が配線パターンを完全に横断せず、ノイズ粒子G4が配線パターンP4の一部分に

50

接触し、そのノイズ粒子 G 4 が接触する部分の配線パターン P 4 (具体的には、図 5 (C) の P 4 - 1 の部分) の幅が所定の幅よりも狭くなる (例えば 2 分の 1) 場合にも配線パターン P 4 は断線したものとみなす。

【 0 0 3 2 】

半導体チップ欠陥検出部 17 は、粒子データ記憶部 14 に記憶されている各ノイズ粒子ごとのデータを順次走査し、マスクパターンに欠陥を生じたノイズ粒子を検出する。そして、欠陥を生じたノイズ粒子が配置されたマスク番号を検出し、半導体チップ欠陥検出部 17 内に各マスクごとに用意されたフラグ記憶領域に、そのマスクに欠陥が生じたことを意味するフラグを付与する。全ノイズ粒子に対して前記処理を行ったら、前記フラグ記憶領域を順次走査し、欠陥を生じたマスクの数を計数し、全マスクの数とともに演算部 18 に出力する。 10

【 0 0 3 3 】

演算部 18 は、半導体チップ欠陥検出部 17 より入力された欠陥を生じたマスクの数、および、全マスクの数より歩留りを算出し出力する。

【 0 0 3 4 】

このような構成の歩留り予測装置において、歩留りが予測される動作について説明する。まず、マスクパターンのデータを回路記憶部 15 に記憶しておき、マスクのデータおよびその製造現場のデータを入力部 11 より入力する。その入力されたデータに基づいて、粒子生成部 12 で半導体チップに付着するであろうノイズ粒子が生成される。生成されたノイズ粒子のデータは、打ち込み部 13 に出力されるとともに、粒子データ記憶部 14 に記憶される。打ち込み部 13 において、回路記憶部 15 に記憶されているマスクデータ上に、そのノイズ粒子のデータを実際に配置していく。その配置が終了したら、欠陥検出部 16 において、各ノイズ粒子ごとに、そのノイズ粒子によりマスクパターンに欠陥が生じたか否かをチェックする。欠陥が生じた場合には、粒子データ記憶部 14 に記憶されている各粒子ごとのデータにフラグを付与していく。 20

【 0 0 3 5 】

次に、半導体チップ欠陥検出部 17 において、粒子データ記憶部 14 に記憶されているデータを順次走査し、欠陥を生じさせているノイズ粒子が存在した場合には、そのノイズ粒子に付与されている半導体チップ識別番号に基づいて、どの半導体チップが欠陥となつたかを調べ、半導体チップごとに用意された記憶領域にフラグを付与する。そして、その半導体チップごとに付与されたフラグをチェックし、欠陥が生じた半導体チップの数と全体の半導体チップの数を演算部 18 出力し、演算部 18 で歩留りを計算する。 30

【 0 0 3 6 】

このように、本実施例の歩留り予測装置によれば、複数の半導体チップに対して生成されたノイズ粒子を、1 個のマスクパターン上に配置し、そのマスクパターンにおいて欠陥を検出し、欠陥が生じた場合に、各ノイズ粒子に付与された半導体チップ識別番号に基づいて、どの半導体チップに欠陥が生じたかをチェックし、歩留りを算出している。

したがって、複数個のマスクパターンに対して各々行っていた処理を、1 個のマスクパターンに対する処理で行うことができる。その結果、マスクパターンを記憶する記憶領域は1 個分のマスクパターンに対応する領域でよく、また処理時間も1 個のマスクパターンに対して処理を行うのと同じ程度の処理時間でよい。尚、通常、半導体チップは複数のマスクを用いて製造されるので、それら各マスクについてノイズ粒子により欠陥が発生するか否かを検出する。 40

【 0 0 3 7 】

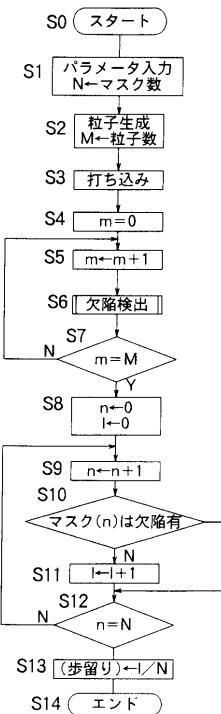

なお、本発明は、本実施例に限られるものではなく種々の変更が可能である。たとえば、本実施例として、各構成部を専用の装置で構成した歩留り予測装置を示したが、この歩留り予測装置は、マイクロプロセッサと記憶手段を有する汎用の計算機装置においても実現できる。その際の、前記マイクロプロセッサを制御するプログラムのフローチャートを図 6 に示す。

計算機装置において歩留りの予測を行った場合の処理の流れを図 6 を参照して説明する。

まず、処理をスタートしたら（ステップS0）、マスクのデータ、製造現場の条件、歩留り予測のパラメータを入力する（ステップS1）。次に、そのパラメータなどに基づいて、ノイズ粒子を生成し（ステップS2）、マスクデータ上に順次配置する（ステップS3）。

【0038】

続いて各ノイズ粒子ごとに（ステップS4～S7）、そのノイズ粒子がマスクパタンの欠陥を引き起こしているか否かをチェックする（ステップS6）。この欠陥の検出は、短絡と断線各々について調べる前述した方法で行い、欠陥を引き起こしていたノイズ粒子に対してはフラグを立てる。全てのノイズ粒子について欠陥の検出を行ったら（ステップS7）、続いて各半導体チップごとに（ステップS8～S12）、欠陥の有無を調べ（ステップS10）、欠陥のない半導体チップの数をカウントする（ステップS11）。

10

そして、全ての半導体チップについて欠陥の有無の判定を行ったら（ステップS12）、その欠陥の無い半導体チップ数と全半導体チップ数に基づいて歩留りを計算し（ステップS13）、処理を終了する。

このように、本発明の歩留り予測装置のような方法によれば、マスクパタン1個に対応する記憶領域が確保できれば歩留りの予測が可能なので、汎用の計算機装置を用いても歩留りの予測をすることができる。

【0039】

また、本発明の実施にあたって、ノイズ粒子やマスクパタンなどの条件によって、その他の処理を加えてもよい。

20

たとえば、本実施例において、複数のノイズ粒子を1個のマスク上に配置する際に、ノイズ粒子間で重なりが生じる場合がある。このような場合の重なりを検出する処理を別途加えてよい。そのような場合には、重なりを検出することにより、ノイズ粒子を、互いに重なりの無い幾つかのグループに分け、各グループごとにノイズ粒子の打ち込み（配置）、欠陥検出の処理を行うようにすることができる。そのようにすることにより、各グループごとの処理においては、全く重なりを考慮せず本実施例と同じ処理で欠陥の検出ができる。そのようにしても、各グループごとに複数回処理を行うことは、複数のマスクデータを用いて処理を行う場合に比べて、十分短い処理時間で済むため、本発明の効果に影響を与えるものではない。

【0040】

30

【発明の効果】

本発明の歩留り予測装置によれば、半導体チップに付着するであろうノイズ粒子を半導体チップの識別番号を付与した上で1個のマスク上に配置し、その配置された各ノイズ粒子に基づいて欠陥を検出し、どの半導体チップに欠陥を生じたかを検出し、歩留りを算出している。その結果、複数のマスクを適宜配置した仮想的なマスクデータを用いて歩留りを予測する場合に比べて、記憶領域などの計算資源は非常に小さくすることができた。また、1個のマスクデータを読み込み、展開し、欠陥をチェックするのみで歩留り予測が行えるので、その処理速度は著しく短くすることができた。

したがって、処理が高速で、小さな計算資源を用いて実現することができる歩留り予測装置を提供することができた。

40

【図面の簡単な説明】

【図1】本発明の第1実施例の歩留り予測装置の構成を示すブロック図である。

【図2】欠陥密度テスト用基板を示す図であり、（A）は基本パタンを示す図、（B）は端子S1と端子S2で観測される電流を模式的に示す図、（C）は基本パタンの要部の構造を示す図である。

【図3】ノイズ粒子の粒径分布関数の例を示す図である。

【図4】図1に示した歩留り予測装置の粒子データ記憶部に記憶されるデータの例を示す図である。

【図5】ノイズ粒子による欠陥の例を示す図であり、（A）は短絡している場合の例を示す図、（B）及び（C）は断線している場合の例を示す図である。

50

【図6】歩留り予測装置を計算機装置で実現した場合のフロー・チャートを示す図である。

【図7】従来の歩留り予測装置の構成を示すブロック図である。

【符号の説明】

10 ... 歩留り予測装置

11 ... 入力部

13 ... 打ち込み部

15 ... 回路記憶部

17 ... 半導体チップ欠陥検出部

90 ... 歩留り予測装置

91 ... 入力部

93 ... 打ち込み部

95 ... 仮想回路生成部

97 ... 欠陥検出部

12 ... 粒子生成部

14 ... 粒子データ記憶部

16 ... 欠陥検出部

17 ... 演算部

92 ... 粒子生成部

94 ... 回路記憶部

96 ... 仮想回路記憶部

98 ... 演算部

10

【図1】

【図2】

【図3】

【図4】

| 粒子番号 | チップ番号 | 位置座標    |        | 粒子サイズ |

|------|-------|---------|--------|-------|

|      |       | X       | Y      |       |

| 0    | 0     | 962290  | 248728 | 1880  |

| 1    | 516   | 719221  | 491617 | 1784  |

| 2    | 172   | 437426  | 525121 | 1698  |

| 3    | 987   | 1175878 | 378833 | 1618  |

| 4    | 249   | 1033870 | 584487 | 1546  |

| 5    | 445   | 1040500 | 603754 | 1488  |

| 6    | 41    | 877508  | 200488 | 1426  |

| 7    | 182   | 948781  | 584700 | 1376  |

| 8    | 971   | 1225761 | 318315 | 1330  |

| 9    | 607   | 806493  | 571104 | 1286  |

| 10   | 832   | 908401  | 13181  | 1246  |

| 11   | 109   | 822899  | 302069 | 1206  |

| 12   | 99    | 665970  | 251713 | 1170  |

| 13   | 945   | 1163191 | 354381 | 1142  |

| 14   | 21    | 1410441 | 130233 | 1114  |

| 15   | 183   | 1025990 | 42609  | 1084  |

| 16   | 30    | 235574  | 811518 | 1058  |

| 17   | 39    | 354611  | 521627 | 1030  |

| 18   | 909   | 644590  | 703341 | 1008  |

| 19   | 3     | 1170029 | 239227 | 986   |

| 20   | 449   | 357430  | 604928 | 968   |

| :    | :     | :       | :      | :     |

| :    | :     | :       | :      | :     |

| :    | :     | :       | :      | :     |

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 福原 英之

東京都港区北青山3丁目6番12号 青山富士ビル日本テキサス・インスツルメンツ株式会社内

合議体

審判長 岡 和久

審判官 正山 旭

審判官 綿谷 晶廣

(56)参考文献 特開昭63-135848(JP,A)

特開平4-61251(JP,A)