(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7172920号**

**(P7172920)**

(45)発行日 令和4年11月16日(2022.11.16)

(24)登録日 令和4年11月8日(2022.11.8)

(51)国際特許分類

|        |                  |     |        |       |         |

|--------|------------------|-----|--------|-------|---------|

| H 01 L | 29/739 (2006.01) | F I | H 01 L | 29/78 | 6 5 5 E |

| H 01 L | 29/78 (2006.01)  |     | H 01 L | 29/78 | 6 5 7 D |

| H 01 L | 21/8234(2006.01) |     | H 01 L | 29/78 | 6 5 3 A |

| H 01 L | 27/06 (2006.01)  |     | H 01 L | 29/78 | 6 5 2 J |

| H 01 L | 27/088(2006.01)  |     | H 01 L | 29/78 | 6 5 5 B |

請求項の数 5 (全14頁) 最終頁に続く

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2019-161392(P2019-161392) |

| (22)出願日  | 令和1年9月4日(2019.9.4)          |

| (65)公開番号 | 特開2021-40071(P2021-40071A)  |

| (43)公開日  | 令和3年3月11日(2021.3.11)        |

| 審査請求日    | 令和3年11月4日(2021.11.4)        |

|          |                                                               |

|----------|---------------------------------------------------------------|

| (73)特許権者 | 000004260<br>株式会社デンソー<br>愛知県刈谷市昭和町1丁目1番地                      |

| (74)代理人  | 110001128弁理士法人ゆうあい特許事務所<br>宮田 征典<br>愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内 |

| (72)発明者  | 利田 祐麻<br>愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内                            |

| (72)発明者  | 薬師川 裕貴<br>愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内                           |

| (72)発明者  | 妹尾 賢                                                          |

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

IGBT素子として機能するIGBT領域(11)と、FWD素子として機能するFWD領域(12)とを有する半導体装置であって、

第1導電型のドリフト層(31)と、前記ドリフト層の表層部に形成された第2導電型のベース層(32)と、前記IGBT領域において、前記ベース層の表層部に前記ドリフト層から離間して形成され、前記ドリフト層よりも高不純物濃度とされた第1導電型のエミッタ領域(36)と、前記IGBT領域において、前記ドリフト層のうちの前記ベース層側と反対側に形成された第2導電型のコレクタ層(43)と、前記FWD領域において、前記ドリフト層のうちの前記ベース層側と反対側に形成された第1導電型のカソード層(44)と、を有する半導体基板(30)と、

前記エミッタ領域と前記ドリフト層との間に位置する前記ベース層の表面に配置されたゲート絶縁膜(34)と、

前記ゲート絶縁膜上に配置されたゲート電極(35)と、

前記ベース層および前記エミッタ領域と電気的に接続される第1電極(41)と、

前記コレクタ層および前記カソード層と電気的に接続される第2電極(45)と、を備え、

前記IGBT領域は、第1領域(11a)と、前記第1領域と異なる第2領域(11b)とを有し、

前記エミッタ領域は、前記第1領域および前記第2領域に形成され、

前記 FWD 領域および前記 IGBT 領域の第 1 領域には、前記第 1 電極と前記第 2 電極との間に前記 FWD 素子をダイオード動作させる順バイアスが印加された際、前記第 2 領域よりも、前記第 2 電極から注入されるキャリアが抜け易くなるキャリア引抜部（32a、38、39）が形成されている半導体装置。

#### 【請求項 2】

前記 IGBT 領域は、前記 FWD 領域側に前記第 1 領域が配置されている請求項 1 に記載の半導体装置。

#### 【請求項 3】

前記 IGBT 領域および前記 FWD 領域の配列方向に沿った長さを幅とすると、

前記 IGBT 領域は、前記第 1 領域の幅が前記半導体基板の厚さ以上とされている請求項 2 記載の半導体装置。 10

#### 【請求項 4】

前記 IGBT 領域および前記 FWD 領域の配列方向に沿った長さを幅とすると、

前記 IGBT 領域は、前記第 1 領域の幅が前記 FWD 領域の幅以下とされている請求項 2 または 3 に記載の半導体装置。 2

#### 【請求項 5】

前記ベース層と前記ドリフト層との間、または前記ベース層内に形成された第 1 導電型のバリア領域（38）と、

前記ベース層に形成され、前記バリア領域と接続されると共に前記第 1 電極と接続される第 1 導電型のピラー領域（39）と、を有する前記キャリア引抜部が形成された請求項 1 ないし 4 のいずれか 1 つに記載の半導体装置。 20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、絶縁ゲート構造を有する絶縁ゲートバイポーラトランジスタ（以下では、IGBT という）素子が形成された IGBT 領域およびフリーホイールダイオード（以下では、FWD という）素子が形成された FWD 領域を有する半導体装置に関する。

##### 【背景技術】

##### 【0002】

従来より、IGBT 領域および FWD 領域を有する半導体装置において、FWD 素子のスイッチング損失を低減した半導体装置が提案されている（例えば、特許文献 1 参照）。具体的には、この半導体装置は、N<sup>-</sup>型のドリフト層を構成する半導体基板を有しており、ドリフト層上にベース層が形成されている。そして、IGBT 領域および FWD 領域では、ベース層を貫通するように複数のトレンチが形成され、各トレンチには、壁面を覆うようにゲート絶縁膜が形成されていると共に、ゲート絶縁膜上にゲート電極が形成されている。また、IGBT 領域には、トレンチと接するように、N<sup>+</sup>型のエミッタ領域が形成されている。そして、半導体基板のうちのベース層側の一面側には、ベース層およびエミッタ領域と電気的に接続される上部電極が形成されている。 30

##### 【0003】

半導体基板の一面と反対の他面側には、P 型のコレクタ層および N 型のカソード層が形成されていると共に、コレクタ層およびカソード層と電気的に接続される下部電極が形成されている。そして、半導体装置は、半導体基板の他面側にコレクタ層が形成されている領域が IGBT 領域とされ、カソード層が形成されている領域が FWD 領域とされている。 40

##### 【0004】

また、ドリフト層とベース層との間には、N 型のバリア領域が形成されている。そして、ベース層には、半導体基板の一面からバリア領域に達するようにピラー領域が形成され、ピラー領域は、上部電極とも接続されている。なお、ピラー領域は、隣合うトレンチの間にそれぞれ形成され、IGBT 領域および FWD 領域の全体に渡って形成されている。

##### 【0005】

このような半導体装置では、バリア領域およびピラー領域が形成されることにより

10

20

30

40

50

、 FWD 領域をダイオード動作させる際、正孔の注入が抑制される。このため、リカバリ電流を小さくでき、リカバリ時間を短くできる。したがって、スイッチング損失を低減できる。

**【先行技術文献】**

**【特許文献】**

**【0006】**

**【文献】特許 5919121 号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0007】**

しかしながら、本発明者らが検討したところ、上記半導体装置では、短絡耐量が低下する可能性があることが確認された。

**【0008】**

本発明は上記点に鑑み、スイッチング損失を低減しつつ、短絡耐量が低下することを抑制できる半導体装置を提供することを目的とする。

**【課題を解決するための手段】**

**【0009】**

上記目的を達成するための請求項 1 は、IGBT 素子として機能する IGBT 領域 (11) と、FWD 素子として機能する FWD 領域 (12) とを有する半導体装置であって、第 1 導電型のドリフト層 (31) と、ドリフト層の表層部に形成された第 2 導電型のベース層 (32) と、IGBT 領域において、ベース層の表層部にドリフト層から離間して形成され、ドリフト層よりも高不純物濃度とされた第 1 導電型のエミッタ領域 (36) と、IGBT 領域において、ドリフト層のうちのベース層側と反対側に形成された第 2 導電型のコレクタ層 (43) と、FWD 領域において、ドリフト層のうちのベース層側と反対側に形成された第 1 導電型のカソード層 (44) と、を有する半導体基板 (30) と、エミッタ領域とドリフト層との間に位置するベース層の表面に配置されたゲート絶縁膜 (34) と、ゲート絶縁膜上に配置されたゲート電極 (35) と、ベース層およびエミッタ領域と電気的に接続される第 1 電極 (41) と、コレクタ層およびカソード層と電気的に接続される第 2 電極 (45) と、を備えている。そして、IGBT 領域は、第 1 領域 (11a) と、第 1 領域と異なる第 2 領域 (11b) とを有し、エミッタ領域は、第 1 領域および第 2 領域に形成され、FWD 領域および IGBT 領域の第 1 領域には、第 1 電極と第 2 電極との間に FWD 素子をダイオード動作させる順バイアスが印加された際、第 2 領域よりも、第 2 電極から注入されるキャリアが抜け易くなるキャリア引抜部 (32a、38、39) が形成されている。

**【0010】**

これによれば、キャリア引抜部が形成されている FWD 領域および第 1 領域により、スイッチング損失の低減を図ることができる。また、キャリア引抜部が形成されていない第 2 領域により、短絡耐量が低下することを抑制できる。

**【0011】**

なお、各構成要素等に付された括弧付きの参照符号は、その構成要素等と後述する実施形態に記載の具体的な構成要素等との対応関係の一例を示すものである。

**【図面の簡単な説明】**

**【0012】**

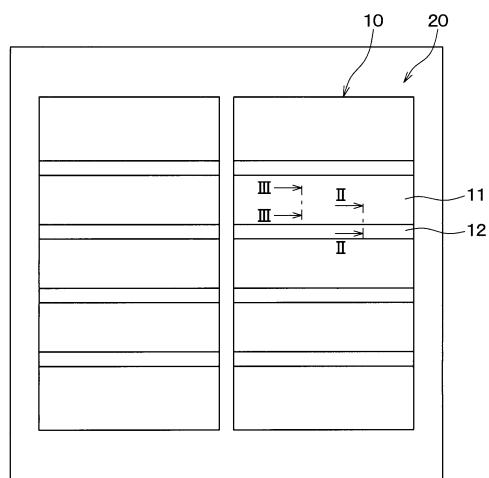

**【図 1】** 第 1 実施形態における半導体装置の平面図である。

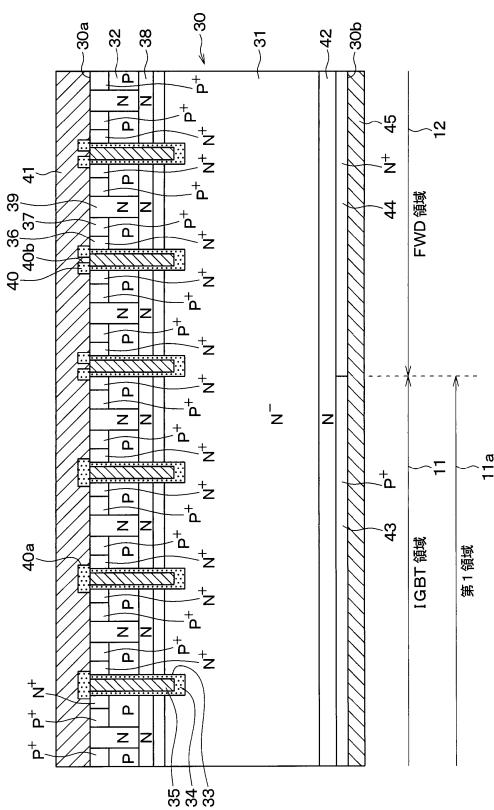

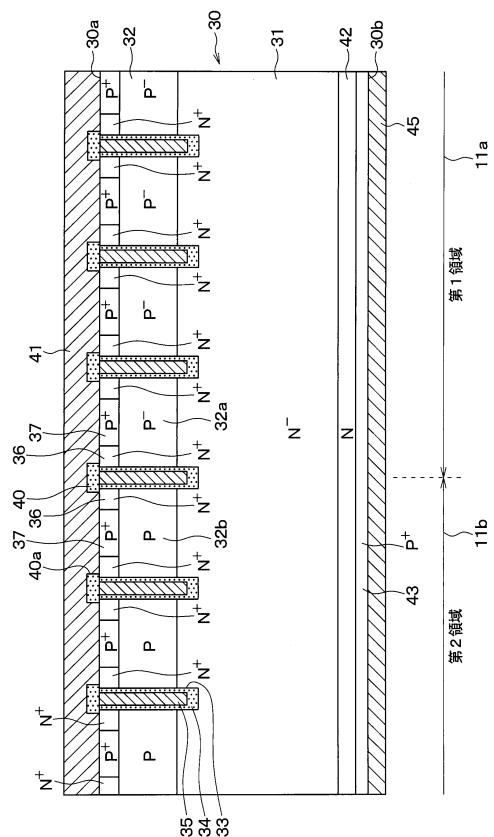

**【図 2】** 図 1 中の II - II 線に沿った断面図である。

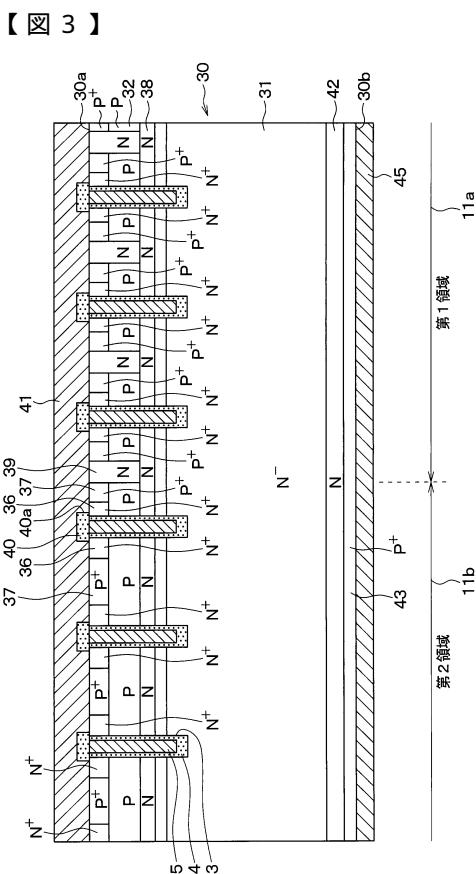

**【図 3】** 図 1 中の III - III 線に沿った断面図である。

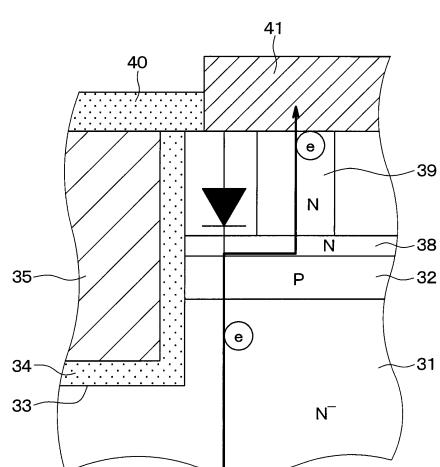

**【図 4】** ダイオード動作している際の電子の流れを示す模式図である。

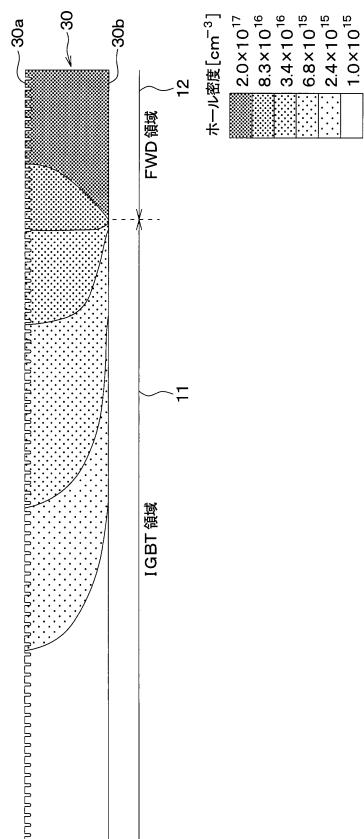

**【図 5】** ダイオード動作している際のホール密度に関するシミュレーション結果を示す図である。

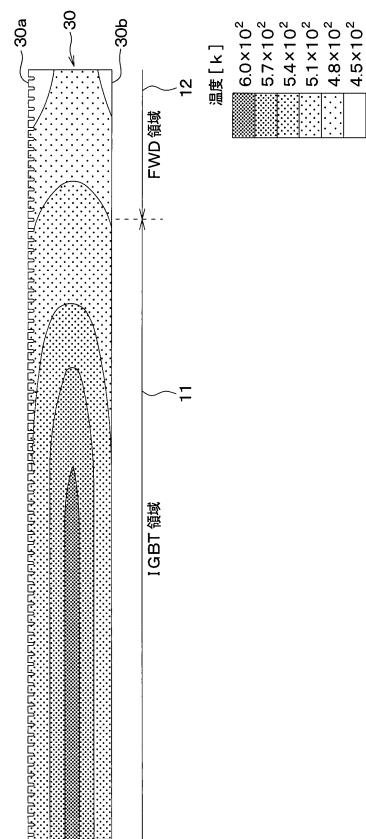

**【図 6】** 短絡電流が遮断された直後の温度分布に関するシミュレーション結果を示す図で

10

20

30

40

50

ある。

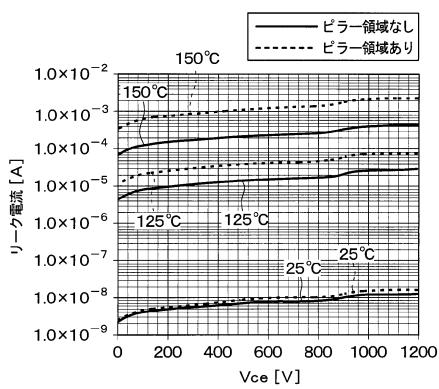

【図7】リーク電流とピラー領域の有無との関係に関するシミュレーション結果を示す図である。

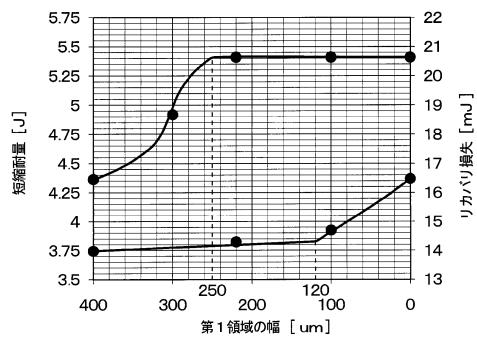

【図8】第1領域の幅と短絡耐量との関係に関する実験結果を示す図である。

【図9】第2実施形態における半導体装置の断面図である。

【発明を実施するための形態】

【0013】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

【0014】

(第1実施形態)

第1実施形態について、図面を参照しつつ説明する。なお、本実施形態の半導体装置は、例えば、インバータ、DC/DCコンバータ等の電源回路に使用されるパワースイッチング素子として利用されると好適である。

【0015】

図1に示されるように、半導体装置は、セル領域10と、当該セル領域10を囲む外周領域20とを有している。本実施形態の半導体装置は、2つのセル領域10を有している。そして、各セル領域10には、IGBT素子として機能するIGBT領域11と、IGBT領域11に隣接し、FWD素子として機能するFWD領域12とが形成されている。つまり、本実施形態の半導体装置は、同じチップ内にIGBT領域11とFWD領域12とが形成されたRC(Reverse Conductingの略)-IGBTとされている。

【0016】

本実施形態では、IGBT領域11およびFWD領域12は、各セル領域10内において、一方向に沿って交互に形成されている。つまり、IGBT領域11およびFWD領域12は、後述する半導体基板30の面方向における一方向に沿って交互に形成されている。具体的には、IGBT領域11およびFWD領域12は、それぞれ長手方向を有する矩形状の領域とされており、当該長手方向と交差する方向に沿って交互に形成されている。また、IGBT領域11およびFWD領域12は、配列方向における両端部にIGBT領域11が位置するように、交互に配列されている。

【0017】

なお、図1中では、IGBT領域11およびFWD領域12は、紙面左右方向を長手方向とする矩形状とされており、紙面上下方向に沿って交互に形成されている。以下では、IGBT領域11およびFWD領域12において、IGBT領域11とFWD領域12との配列方向を幅方向ともいい、IGBT領域11とFWD領域12との配列方向に沿った長さを幅ともいう。そして、本実施形態では、IGBT領域11は、幅が800μmとされており、FWD領域12は、幅が250μmとされている。

【0018】

以下、本実施形態の半導体装置の具体的な構成について説明する。

【0019】

半導体装置は、図2および図3に示されるように、N型のドリフト層31を構成する半導体基板30を有している。なお、本実施形態では、半導体基板30は、シリコン基板で構成されており、一面30aと他面30bとの間の長さである厚さが120μmとされている。つまり、半導体基板30は、厚さがFWD領域12の幅よりも薄くされている。そして、ドリフト層31上には、P型のベース層32が形成されている。言い換えると、半導体基板30の一面30a側には、ベース層32が形成されている。

【0020】

半導体基板30には、一面30a側からベース層32を貫通してドリフト層31に達するように複数のトレンチ33が形成されている。これにより、ベース層32は、トレンチ33によって複数個に分離されている。本実施形態では、複数のトレンチ33は、IGBT領域11およびFWD領域12にそれぞれ形成されている。また、本実施形態では、複

10

20

30

40

50

数のトレンチ 3 3 は、IGBT 領域 1 1 および FWD 領域 1 2 の配列方向と交差する方向（すなわち、図 1 中の紙面左右方向）を長手方向としてストライプ状に形成されている。なお、隣合うトレンチ 3 3 同士の間隔（すなわち、ピッチ間隔）は、例えば、 $6 \mu\text{m}$  程度とされる。

#### 【0021】

そして、各トレンチ 3 3 は、各トレンチ 3 3 の壁面を覆うように形成されたゲート絶縁膜 3 4 と、このゲート絶縁膜 3 4 の上に形成されたポリシリコン等により構成されるゲート電極 3 5 とにより埋め込まれている。これにより、トレンチゲート構造が構成されている。

#### 【0022】

なお、IGBT 領域 1 1 に形成されたトレンチ 3 3 に配置されているゲート電極 3 5 は、図示しないゲート配線を介して外周領域 2 0 に形成されたゲートパッド等と接続される。ゲートパッドは、図示しない可変抵抗を介して駆動回路と接続される。そして、このゲート電極 3 5 には、所定のパルス状のゲート電圧が印加される。FWD 領域 1 2 に形成されているトレンチ 3 3 に配置されたゲート電極 3 5 は、後述する上部電極 4 1 と電気的に接続され、所定電位に維持されるようになっている。

#### 【0023】

ベース層 3 2 の表層部には、ドリフト層 3 1 よりも高不純物濃度とされた N<sup>+</sup> 型のエミッタ領域 3 6 が形成されている。すなわち、半導体基板 3 0 の一面 3 0 a 側には、エミッタ領域 3 6 が形成されている。また、ベース層 3 2 の表層部には、ベース層 3 2 よりも高不純物濃度とされた P<sup>+</sup> 型のコンタクト領域 3 7 が形成されている。具体的には、エミッタ領域 3 6 は、ベース層 3 2 内において終端し、かつ、トレンチ 3 3 の側面に接するようにならって形成されている。また、コンタクト領域 3 7 は、エミッタ領域 3 6 と同様に、ベース層 3 2 内において終端するようにならって形成されている。

#### 【0024】

より詳しくは、エミッタ領域 3 6 は、隣合うトレンチ 3 3 間の領域において、トレンチ 3 3 の長手方向に沿ってトレンチ 3 3 の側面に接するようにならって棒状に延設され、トレンチ 3 3 の先端よりも内側で終端する構造とされている。また、コンタクト領域 3 7 は、エミッタ領域 3 6 と接するようにならって、トレンチ 3 3 の長手方向に沿って棒状に延設されている。

#### 【0025】

なお、本実施形態では、トレンチ 3 3 の壁面のうちのエミッタ領域 3 6 とドリフト層 3 1 との間に位置する部分が、エミッタ領域とドリフト層との間に位置するベース層の表面に相当する。また、図 2 および図 3 では、コンタクト領域 3 7 は、エミッタ領域 3 6 と同じ深さとされている図が示されているが、エミッタ領域 3 6 より深くまで形成されていてよい。

#### 【0026】

さらに、本実施形態では、ベース層 3 2 には、当該ベース層 3 2 をトレンチ 3 3 の深さ方向に分割するように、ドリフト層 3 1 よりも高不純物濃度とされた N 型のバリア領域 3 8 が形成されている。

#### 【0027】

そして、IGBT 領域 1 1 および FWD 領域 1 2 には、ベース層 3 2 に、半導体基板 3 0 の一面 3 0 a からバリア領域 3 8 に達するように N 型のピラー領域 3 9 が形成されている。なお、ピラー領域 3 9 は、バリア領域 3 8 とほぼ同じ不純物濃度とされており、トレンチ 3 3 の延設方向に沿って延設されている。

#### 【0028】

ここで、IGBT 領域 1 1 のうちの FWD 領域 1 2 側の領域を第 1 領域 1 1 a とし、IGBT 領域 1 1 のうちの第 1 領域 1 1 a と異なる領域を第 2 領域 1 1 b とする。本実施形態では、上記のように IGBT 領域 1 1 および FWD 領域 1 2 が配列されているため、FWD 領域 1 2 で挟まれている部分の IGBT 領域 1 1 では、第 2 領域 1 1 b は、第 1 領域 1 1 a で挟まれた構成となる。また、IGBT 領域 1 1 と FWD 領域 1 2 との配列方向の

10

20

30

40

50

両端部に位置する IGBT 領域 11 では、配列方向の端部側の領域の全体が第 2 領域 11 b となる。

#### 【 0 0 2 9 】

そして、FWD 領域 12 には、全体的にピラー領域 39 が形成されている。一方、IGBT 領域 11 では、第 1 領域 11 a のみにピラー領域 39 が形成されており、第 2 領域 11 b には、ピラー領域 39 が形成されていない。つまり、IGBT 領域 11 は、ピラー領域 39 が形成されている領域と、ピラー領域 39 が形成されていない領域とが混在した状態となっている。言い換えると、IGBT 領域 11 は、ピラー領域 39 が間引かれた構成となっている。

#### 【 0 0 3 0 】

なお、本実施形態では、バリア領域 38 およびピラー領域 39 がキャリア引抜部に相当している。また、本実施形態では、第 1 領域 11 a は、FWD 領域 12 との境界から最も離れた位置のピラー領域 39 における当該境界と反対側の部分までとされている。つまり、後述する第 1 領域 11 a の幅とは、FWD 領域 12 との境界と、境界から最も離れた位置のピラー領域 39 における当該境界と反対側の部分との間の長さのことである。

#### 【 0 0 3 1 】

半導体基板 30 の一面 30 a 上には、BPSG (Borophosphosilicate Glass の略) 等で構成される層間絶縁膜 40 が形成されている。そして、層間絶縁膜 40 上には、層間絶縁膜 40 に形成されたコンタクトホール 40 a を通じて、エミッタ領域 36、コンタクト領域 37 (すなわち、ベース層 32)、およびピラー領域 39 と電気的に接続される上部電極 41 が形成されている。つまり、層間絶縁膜 40 上には、IGBT 領域 11 においてエミッタ電極として機能し、FWD 領域 12 においてアノード電極として機能する上部電極 41 が形成されている。なお、上部電極 41 は、ベース層 32、コンタクト領域 37、およびピラー領域 39 とオーミック接合されていてもよいし、ベース層 32 およびコンタクト領域 37 とオーミック接合されると共にピラー領域 39 とショットキー接合されていてもよい。

#### 【 0 0 3 2 】

また、本実施形態では、層間絶縁膜 40 には、FWD 領域 12 において、ゲート電極 35 を露出させるコンタクトホール 40 b が形成されている。そして、上部電極 41 は、このコンタクトホール 40 b を通じてゲート電極 35 とも接続されている。これにより、FWD 領域 12 に形成されたゲート電極 35 は、上部電極 41 と同電位に維持される。本実施形態では、上部電極 41 が第 1 電極に相当している。

#### 【 0 0 3 3 】

ドリフト層 31 のうちのベース層 32 側と反対側 (すなわち、半導体基板 30 の他面 30 b 側) には、ドリフト層 31 よりも高不純物濃度とされた N 型のバッファ層 42 が形成されている。

#### 【 0 0 3 4 】

そして、IGBT 領域 11 では、バッファ層 42 を挟んでドリフト層 31 と反対側に P<sup>+</sup> 型のコレクタ層 43 が形成され、FWD 領域 12 では、バッファ層 42 を挟んでドリフト層 31 と反対側に N<sup>+</sup> 型のカソード層 44 が形成されている。つまり、IGBT 領域 11 と FWD 領域 12 とは、半導体基板 30 の他面 30 b 側に形成される層がコレクタ層 43 であるかカソード層 44 であるかによって区画されている。そして、コレクタ層 43 上の領域が IGBT 領域 11 とされ、カソード層 44 上の領域が FWD 領域 12 とされている。

#### 【 0 0 3 5 】

コレクタ層 43 およびカソード層 44 を挟んでドリフト層 31 と反対側 (すなわち、半導体基板 30 の他面 30 b) には、コレクタ層 43 およびカソード層 44 と電気的に接続される下部電極 45 が形成されている。つまり、IGBT 領域 11 においてはコレクタ電極として機能し、FWD 領域 12 においてはカソード電極として機能する下部電極 45 が形成されている。本実施形態では、下部電極 45 は、コレクタ層 43 およびカソード層 44

10

20

30

40

50

4とオーミック接合されている。また、本実施形態では、下部電極45が第2電極に相当している。

#### 【0036】

そして、上記のように構成されることにより、FWD領域12においては、ベース層32およびコンタクト領域37をアノードとし、ドリフト層31、バッファ層42、カソード層44をカソードとしてPN接合されたFWD素子が構成されている。

#### 【0037】

以上が本実施形態における半導体装置の構成である。なお、本実施形態では、N型、N<sup>+</sup>型、N<sup>-</sup>型が第1導電型に相当しており、P型、P<sup>+</sup>型が第2導電型に相当している。また、本実施形態では、上記のように構成されることにより、半導体基板30は、コレクタ層43、カソード層44、ドリフト層31、エミッタ領域36、コンタクト領域37、バリア領域38、ピラー領域39を含んだ構成となっている。10

#### 【0038】

次に、上記半導体装置の作動について説明しつつ、さらに半導体装置の詳細な構成について説明する。

#### 【0039】

IGBT領域11に形成されたIGBT素子の作動については、従来と同様である。簡単に説明すると、IGBT素子は、ゲート電極35に印加されるゲート電圧が制御されることにより、ベース層32のうちのトレンチ33と接する部分に形成されるチャネルの有無が制御される。これにより、IGBT素子は、エミッタ - コレクタ間に電流を流したり、遮断したりするスイッチング動作を行う。20

#### 【0040】

そして、FWD領域12に形成されたFWD素子は、上部電極41と下部電極45との間に順バイアスが印加されることにより、下部電極45からカソード層44に電子が注入されると共に、上部電極41からコンタクト領域37に正孔が注入されることでダイオード動作する。この際、本実施形態では、FWD領域12およびIGBT領域11の第1領域11aには、ピラー領域39が形成されている。このため、図4に示されるように、下部電極45から注入された電子は、ピラー領域39から上部電極41へと低抵抗な状態で抜ける。したがって、バリア領域38およびピラー領域39と、ベース層32との間のPN接合に順バイアスが印加され難くなり、上部電極41からの正孔の注入を低減できる。30

なお、図4では、電子を「e」として示している。

#### 【0041】

このため、上部電極41と下部電極45との間の電圧が順バイアスから逆バイアスに切り替わった際、正孔の注入が抑制されているため、リカバリ電流を小さくでき、リカバリ時間を短くできる。したがって、スイッチング損失を低減することができる。なお、本実施形態では、電子が第2電極から注入されるキャリアに相当する。

#### 【0042】

ここで、ピラー領域39がIGBT領域11およびFWD領域12の全体に渡って形成された従来の半導体装置（以下では、単に従来の半導体装置ともいう）について、本発明者らが検討した結果を図5および図6を参照しつつ説明する。40

#### 【0043】

まず、図5に示されるように、半導体装置をダイオード動作させた際、ホール濃度は、FWD領域12で高くなることが確認される。そして、IGBT領域11では、FWD領域12との境界側と反対側をIGBT領域11の幅方向における中心側（以下では、単に中心側ともいう）とすると、ホール濃度は、FWD領域12との境界側から中心側に向かって順に低くなることが確認される。これは、ダイオード動作時においては、カソード層44（すなわち、半導体基板30の他面30b）に注入される電子は、一面30a側に向かって約45°の広がりを持って拡散しながら移動するためである。つまり、IGBT領域11では、元々、FWD領域12との境界から半導体基板30の厚さ以上の部分に電子が到達し難く、ホールが注入され難い状態となっている。50

**【 0 0 4 4 】**

また、図6に示されるように、半導体装置が短絡してIGBT領域11に大電流である短絡電流が流れ、当該短絡電流が遮断された直後の温度分布は、FWD領域12との境界側から中心側に向かって高くなることが確認される。これは、IGBT領域11のうちのFWD領域12との境界側の領域では、大電流が流れたことによって発生する熱がFWD領域12側へと放熱されるためである。

**【 0 0 4 5 】**

さらに、本発明者らは、リーク電流と、ピラー領域39の有無との関係について鋭意検討を行い、図7に示す結果を得た。

**【 0 0 4 6 】**

図7に示されるように、リーク電流は、温度が高くなるほど電子が上部電極41側へと抜け易くなるために大きくなる。そして、ピラー領域39が形成されている場合には、ピラー領域39が形成されていない場合よりも電子が上部電極41側へと抜け易くなるため、リーク電流が大きくなり易いことが確認される。

**【 0 0 4 7 】**

つまり、半導体装置は、短絡時においては、IGBT領域11における中心側の領域がFWD領域12との境界側の領域より温度が高くなり易いため、この領域にピラー領域39が形成されていると、リーク電流が大きくなることによって短絡耐量が低下し易い。このため、従来の半導体装置のように、IGBT領域11およびFWD領域12の全体に渡ってピラー領域39が形成されている場合には、短絡耐量が低下する。

**【 0 0 4 8 】**

したがって、本実施形態の半導体装置では、IGBT領域11は、FWD領域12側の第1領域11aにピラー領域39が形成されており、第1領域11aと異なる第2領域11bにはピラー領域39を形成しないようにしている。このため、スイッチング損失を低減しつつ、短絡耐量を向上させることができる。

**【 0 0 4 9 】**

そして、本発明者らは、さらに、第1領域11aにおける幅について鋭意検討を行い、図8に示す実験結果を得た。なお、図8は、半導体基板30の厚さを120μmとし、FWD領域12の幅を250μmとした実験結果を示す図である。また、図8では、IGBT領域11とカソード層44との境界を基準（すなわち、図8中の第1領域の幅が0）としている。

**【 0 0 5 0 】**

図8に示されるように、リカバリ損失（すなわち、スイッチング損失）は、第1領域11aの幅が120μmまでは急峻に低下するが、120μm以上の範囲ではあまり変化しない。すなわち、リカバリ損失は、半導体基板30の厚さが120μmとされている場合、第1領域11aの幅を半導体基板30の厚さ以上としてもあまり変化しない。

**【 0 0 5 1 】**

一方、短絡耐量は、第1領域11aの幅が250μmまではほぼ一定であるが、第1領域11aの幅が250μm以上となると急峻に低下する。すなわち、短絡耐量は、FWD領域12の幅が250μmである場合、第1領域11aの幅をFWD領域12の幅以上とすると急峻に低下する。

**【 0 0 5 2 】**

このため、本実施形態では、第1領域11aの幅は、半導体基板30の厚さ以上であって、FWD領域12の幅以下となるように形成されている。

**【 0 0 5 3 】**

以上説明したように、本実施形態では、FWD領域12には、ピラー領域39が形成されている。また、IGBT領域11は、ピラー領域39が形成された第1領域11aと、ピラー領域39が形成されていない第2領域11bとを有している。このため、ピラー領域39が形成されているFWD領域12および第1領域11aにより、スイッチング損失の低減を図ることができる。また、ピラー領域39が形成されていない第2領域11bに

10

20

30

40

50

より、短絡耐量が低下することを抑制できる。

#### 【0054】

そして、本実施形態では、第1領域11aは、FWD領域12との境界側に形成されている。また、第1領域11aの幅は、半導体基板30の厚さ以上であって、FWD領域12の幅以下とされている。このため、スイッチング損失を十分に低減しつつ、短絡耐量が低下することを抑制できる。

#### 【0055】

##### (第2実施形態)

第2実施形態について説明する。本実施形態は、第1実施形態に対し、IGBT領域11の構成を変更したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

10

#### 【0056】

本実施形態では、図9に示されるように、バリア領域38およびピラー領域39は形成されていない。そして、ベース層32は、第1領域11aに位置する第1ベース層32aが、第2領域11bに位置する第2ベース層32bよりも不純物濃度が低くされている。なお、特に図示しないが、FWD領域12は、第1領域11aと同様の構成とされている。

#### 【0057】

このように、ベース層32の不純物濃度を変化させることによって上部電極41への電子の引く抜き易さを変化させた半導体装置としても、上記第1実施形態と同様の効果を得ることができる。なお、本実施形態では、第1ベース層32aがキャリア引抜部に相当する。

20

#### 【0058】

##### (他の実施形態)

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

#### 【0059】

例えば、上記各実施形態では、第1導電型をN型とし、第2導電型をP型とした例について説明したが、第1導電型をP型とし、第2導電型をN型とすることもできる。

30

#### 【0060】

また、上記各実施形態において、トレンチゲート型の半導体装置ではなく、半導体基板30の一面30a上にゲート電極35が配置されるプレーナ型の半導体装置としてもよい。

#### 【0061】

さらに、上記各実施形態において、セル領域10は、1つとされていてもよいし、3つ以上の複数とされていてもよい。また、FWD領域12は、1つのセル領域10内に1つのみ形成されるようにしてもよい。

#### 【0062】

また、上記各実施形態において、第1領域11aは、FWD領域12側に形成されていなくてもよい。さらに、第1領域11aの幅は、半導体基板10の厚さ未満とされていてもよいし、FWD領域12の幅より広くされていてもよい。このような半導体装置としても、IGBT領域11を第1領域11aと第2領域11bとを有する構成とすることにより、スイッチング損失を低減しつつ、短絡耐量が低下することを抑制できる。

40

#### 【0063】

そして、上記第1実施形態において、特に図示しないが、バリア領域38は、ドリフト層31とベース層32との間に配置されていてもよい。また、上記第1実施形態において、特に図示しないが、バリア領域38が形成されておらず、キャリア引抜部がピラー領域39のみで構成されるようにしてもよい。さらに、上記第1実施形態において、ピラー領域39の不純物濃度を変化させることにより、キャリアの引き抜き易さを変化させるようにしてもよい。この場合、例えば、第1領域11aに形成されるピラー領域39は、第2領域11bに形成されるピラー領域39よりも不純物濃度が濃くなるようにするようすればよい。

50

**【 0 0 6 4 】**

さらに、上記第1実施形態において、コンタクト領域37は、形成されていなくてもよいし、ピラー領域39と離れて形成されていてもよい。つまり、半導体装置は、ベース層32が半導体基板30の一面30aから露出する構成とされていてもよい。

**【 0 0 6 5 】**

また、上記第1、第2実施形態において、IGBT領域11とFWD領域12とは、隣接して配置されていなくてもよい。例えば、IGBT領域11とFWD領域12の間に、繋ぎ領域等の領域が配置されていてもよい。

**【 符号の説明 】****【 0 0 6 6 】**

- 1 1 IGBT領域

- 1 1 a 第1領域

- 1 1 b 第2領域

- 1 2 FWD領域

- 3 1 ドリフト層

- 3 2 ベース層

- 3 6 エミッタ領域

- 3 8 バリア領域

- 3 9 ピラー領域

- 4 1 上部電極（第1電極）

- 4 3 コレクタ層

- 4 4 カソード層

- 4 5 下部電極（第2電極）

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 4】

50

【図 5】

【図 6】

10

20

30

【図 7】

【図 8】

40

50

【図9】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

H 01 L 27/06 102 A

H 01 L 27/088 E

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 細川 博司

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 永井 昂哉

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

審査官 殿川 雅也

(56)参考文献 特開2018-073911 (JP, A)

特開2016-225345 (JP, A)

特許第5919121 (JP, B2)

特開2017-059725 (JP, A)

国際公開第2019/117248 (WO, A1)

国際公開第2010/143288 (WO, A1)

(58)調査した分野 (Int.Cl., DB名)

H 01 L 29/739

H 01 L 29/78

H 01 L 21/8234