**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>4</sup>

H04L 7/02

(45) 공고일자 1986년09월01일

(11) 공고번호 특 1986-0001258

---

|           |                |           |                |

|-----------|----------------|-----------|----------------|

| (21) 출원번호 | 특 1983-0002755 | (65) 공개번호 | 특 1984-0005634 |

| (22) 출원일자 | 1983년06월20일    | (43) 공개일자 | 1984년11월14일    |

---

|            |                                                           |

|------------|-----------------------------------------------------------|

| (30) 우선권주장 | 129139 1982년07월24일 일본(JP)                                 |

| (71) 출원인   | 파이오니아 가부시끼 가이샤 마쓰모토 세이야<br>일본국 도오쿄오도 메구로 꾸메구로 1쵸오메 4반 1고오 |

(72) 발명자

요꼬가와 후미히코

일본국 사이다마겐 도쿄로자와시 하나조노 4쵸오메 2610반지 파이오니아

가부시끼 가이샤 도쿄로자와 고오조오 내

나이또오 류우이찌

일본국 사이다마겐 도쿄로자와시 하나조노 4쵸오메 2610반지 파이오니아

가부시끼 가이샤 도쿄로자와 고오조오 내

(74) 대리인

장용식

**심사관 : 고금영 (책자공보 제1192호)**

---

**(54) 클럭 재생회로**

---

**요약**

내용 없음.

**대표도**

**도1**

**명세서**

[발명의 명칭]

클럭 재생회로

[도면의 간단한 설명]

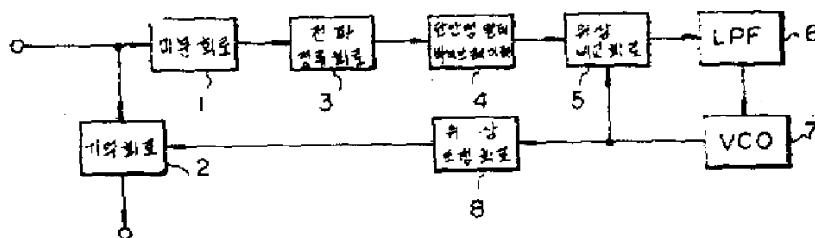

제1도는 종래의 클럭재생회로를 나타내는 블럭도.

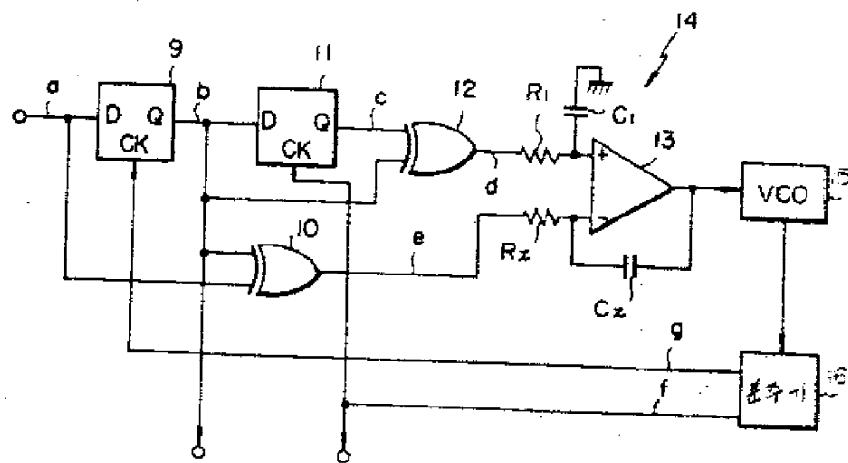

제2도는 본 발명의 한가지 실시예를 보여주는 회로 블럭도.

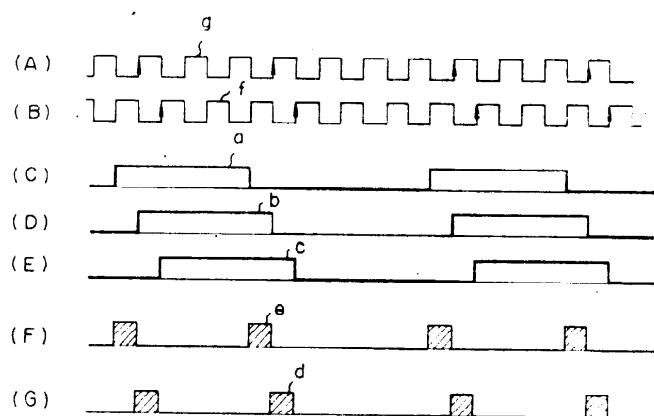

제3도 내지 제5도는 제2도의 회로의 각 상태에서의 각 출력 파형도.

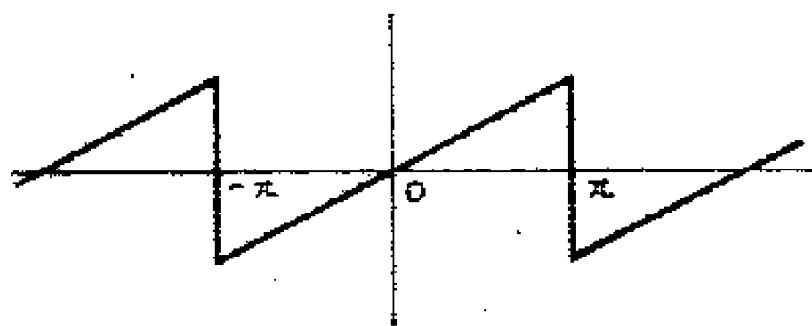

제6도는 제2도 회로에서 형성되어 있는 위상비교수단의 특성을 나타내는 그래프.

\* 도면의 주요부분에 대한 부호의 설명

9, 11 : D형 플립플립 10, 12 : 배타적논리화게이트

14 : LPF 15 : VOC

16 : 분주기

[발명의 상세한 설명]

본 발명은 클럭 재생회로에 관한 것이며, 특히 런.LENGTH 리미티드(run-length limited)변조방식에 의한 변조신호의 복조를 위한 클럭재생회로에 관한 것이다.

피시엠(pcm, 펄스부호변조)신호등의 디지털정보신호를 기록매체나 전송매체로 송출할때의 변조신호 처리방법으로서 고밀도화등을 고려하여 셀프클럭이 가능한 소위 런.LENGTH 리미티드 변조방식이 채용되고 있다. 이 런.LENGTH 리미티드 변조방식에 있어서는, 복조시에 기록매체나 전송매체로부터 얻어지는 신호로부터 복조용 클럭신호를 재생하는 것이 보통이다.

제1도는 클럭신호를 재생하는 클럭재생회로의 종래예를 나타내는 블럭도이다. 이 도면에서, 디지털 오디오디스크등의 기록매체로부터 재생된 런.LENGTH 리미티드 변조방식에 의한 변조신호로된 입력신호

가 미분회로(1) 및 D형 플립플롭(flip flop)등으로 된 기억회로(2)에 공급되고 있다.

미분회로(1)에 의해서 입력신호의 입상(立上) 에지(edge) 및 입하(立下)에지의 각각이 도래할 때마다 정의 펄스 및 부의펄스가 각각 출력되어 전파정류회로(3)에 공급된다. 전파정류회로(3)에서는 미분회로(1)에 의해서 출력된 부의 펄스의 극성이 반전되므로서 입력신호의 입상에지 및 입하에지가 도래할 때마다 정의 펄스가 얻어진다.

전파정류회로(3)의 출력은 단안정(單安定)멀티 바이브레이터(이하 단안정 멀티라고 생략한다)(4)의 트리거 입력단자에 공급된다. 단안정멀티(4)의 반전시간은, 얻어지는 재생클럭의 주기의 거의 1/2과 같은 시간으로 설정되어 있다.

이 단안정 멀티(4)의 에로서 Q출력이 위상비교회로(5)에 공급되고 있다. 위상비교기(5)는, LPF(저역 필터)(6) 및 VCO(전압제어형발진기)(7)와 함께 PLL(phase locked loop)를 형성하고 있다. 즉 VCO의 출력이 위상비교기(5)에서 단안정멀티(4)의 출력과 비교되어, 이들양신호의 주파수 및 위상에 있어서의 차에 응한 신호가 LPF(6)를 통하여 VCO(7)의 제어전압으로 된다. VCO(7)의 출력은 미분회로(1), 전파정류회로(3) 및 단안정멀티(4)에서의 신호지연시간에 의한 위상지연을 보상하기 위한 위상 조정회로(8)에 의

이상과 같이 종래의 클럭재생회로는 구성이 복잡하고 또한 단안정 멀티(4)의 반전시간을 결정하는 시한 설정용의 콘덴서 및 저항이 필요하기 때문에 IC(직접회로)화 할때에 시한설정용 콘덴서등의 외부 부착단자가 필요로되기 때문에 IC화에 적당하지 않은 결점이 있었다. 그래서 본 발명의 목적은 구성이 간단하고 시한설정용 콘덴서등을 외부에서 붙이는 단자를 필요로하지 않고 IC화에 적합한 클럭재생회로를 제공하는 것이다.

본 발명에 의한 클럭재생회로는 입력신호와 펄스발생수단으로부터 출력된 펄스에 동기시켜 입력신호의 상태를 일시 기억하는 제1 기억수단의 기억내용에 응한 신호와의 배타적 논리화를 취해서 얻은 신호의 펄스폭과, 제1 기억수단의 출력과 제1 기억수단의 출력의 상태를 상기 펄스에 동기시켜 일시 기억하는 제2기억수단과의 배타적 논리화를 취해서 얻은 신호의 펄스폭이 서로 같게 되도록 상기 펄스의 반복주파수를 제어하므로서 입력신호와 상기 펄스간의 위상차를 없애면서 상기 펄스를 재생 클럭으로해서 출력하는 구성으로 되어있다.

이하에서 본 발명의 실시예에 관하여 제2도 내지 제6도를 참조하면서 상세히 설명한다.

제2도에서 런랭스 리미티드 변조방식에 의한 변조신호로 이루어지는 입력신호(a)가 제1 기억수단으로서의 D형 플립플롭(9)의 D입력단자 및 배타적 논리화 게이트(10)의 일방의 입력단자에 공급되고 있다. D형 플립플롭(9)의 Q출력 b는 제2 기억수단으로서의 D형 플립플롭(11)의 D입력단자에 공급됨과 동시에 배타적 논리화게이트(10)의 바방의 입력단자 및 배타적 논리화게이트(12)의 일방의 입력단자에 공급되고 있다. 게이트(12)의 타방의 입력단자에는 D형 플립플롭(11)의 Q출력 C가 공급되고 있다.

게이트(12)의 출력 d는 저항 R<sub>1</sub>을 개재시켜서 연산증폭기(13)의 정상(正相)입력단자에 공급되어 있다. 연산증폭기(13)의 정상입력단자와 접지사이에는 콘덴서(C<sub>1</sub>)가 접속되어 있다.

또한 연산증폭기(13)의 역상입력단자(逆相输入端子)에는 저항 R<sub>2</sub>를 개재시켜 게이트(10)의 출력 e가 공급되고 있고, 연산증폭기(13)의 역상입력단자와 출력단자간에는 콘덴서(c<sub>2</sub>)가 접속되어 있다.

연산증폭기(13), 콘덴서(C<sub>1</sub>, C<sub>2</sub>) 및 저항 R<sub>1</sub>, R<sub>2</sub>에 의해서 2개의 입력의 차를 증폭시켜 얻은 신호의 저역성분을 추출해서 출력하는 LPF(14)가 형성되어 있고, 연산증폭기(13)에서부터 VCO(15)로 제어 전압이 공급된다. VCO(15)의 출력은 분주기(16)에 의해서 2분주된다.

그래서 분주기(16)의 π상출력 f가 D형 플립플롭(11)의 클럭에 공급됨과 동시에 복조용재생 클럭으로서 도시되지 않은 복조회로에 공급된다. 또한 분주기(16)의 0상 출력 g가 D형 플립플롭(9)의 클럭입력단자에 공급되어서 입력신호 a가 D형 플립플롭(9)에 랫치되고, 플립플롭(9)으로부터 입력신호 a를 재생클럭의 반클럭분 지연되어 얻어지는 신호가 출력되어서 상기 도시하지 않은 복조회로에 데이터 출력으로서 공급된다.

이상의 구성에 있어서 각부의 동작을 제3도 내지 제6도를 참조해서 설명한다.

D형 플립플롭(9, 11)은 클럭입력의 입상에제에서 D입력단자에 공급된 신호를 랫치시키는 것으로 한다.

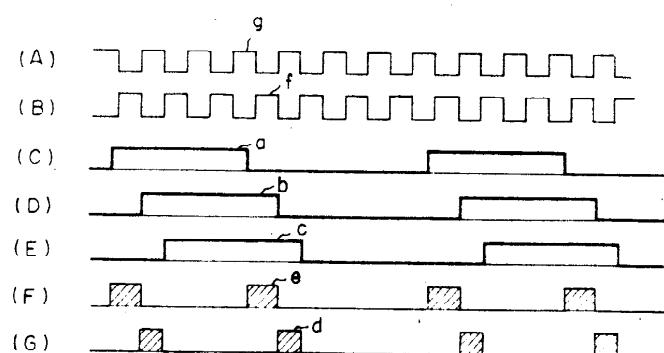

제3(a)도 내지 제3(g)도는 입력신호 a에 있어서의 입상에지 및 입하에지의 출현타이밍과 재생클럭으로서의 π상 출력 f의 입상에지의 출현 타이밍이 일치하도록 π상 출력 f의 위상이 제어되어 있는 경우의 각 신호의 파형도로서, 제3(a)도는 0상출력 g의 파형, 제3(b)도는 π상 출력 f의 파형, 제3(c)도는 입력신호 a의 파형, 제3(d)도는 D형 플립플롭(9)의 Q출력 b의 파형, 제3(e)도는 D형 플립플롭(11)의 Q출력 c의 파형, 제3(f)도는 배타적 논리화 게이트(10)의 출력 e의 파형, 제3(g)도는 배타적 논리화 게이트(12)의 출력 d의 파형동을 각각 나타낸다.

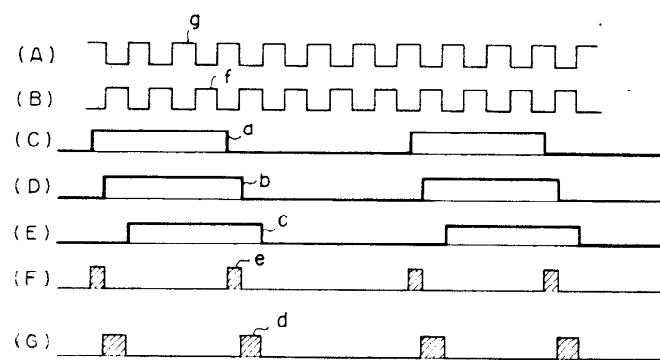

제4(a)도 내지 제4(g)도는 입력신호 a의 위상이 빨라져서 입력신호 a에서의 입상에지 및 입하에지의 출현 타이밍이 π상출력 f의 입상에지의 출현 타이밍보다 전방으로 어긋난 경우인 제3(a)도 내지 제3(g)도의 각각과 동일한 신호의 파형을 각각 나타낸다. 또한 제5(a)도 내지 제5(g)도는 입력신호 a의 위상이 늦어져서 입력신호 a에서의 입상에지 및 입상에지의 출현타이밍이 π상출력 f의 입상에지의 출현타이밍보다 후방으로 어긋난 경우인 제3(a)도 내지 제3(g)도의 각각과 동일한 신호의 파형을 각각 나타낸다.

제3도 내지 제5도에서 명백한 바와 같이 배타적 논리화게이트(10)의 출력 e는 입력신호 a의 입상 및 입하에지가 도래하는 때마다 발생하며 또한 입력신호 a와 π상 출력 f와의 위상관계 다시말하면 입

력신호 a에서의 입상에지 및 입하에지와 π상 출력의 입상에지와의 출현 타이밍간의 차에 응해서 변화하는 펄스폭을 갖는 펄스로된다.

또한 배타적 논리화게이트(12)의 출력 d는 펄스폭이 0상출력 g 및 π상출력 f의 펄스폭과 같은 펄스로된다. 그래서 입력신호 a에서의 입상에지 및 입하에지의 출현 타이밍이 π상 출현 f의 입상에지의 출현타이밍에 일치했을 때에 배타적 논리화게이트(10)의 출력 e의 펄스폭은 배타적 논리화게이트(12)의 출력 d의 펄스폭과 같게된다.

또 입력신호 a의 위상이 빨라졌을 때는 출력 e의 펄스폭을 출력 d의 펄스폭보다 넓게되고, 역으로 입력신호 a의 위상이 늦을 때에는 출력 e의 펄스폭은 출력 d의 펄스폭보다 더 좁게된다.

이상과 같이 위상정보를 포함한 배타적 논리화게이트(10)의 출력을 적분해서 얻은 신호의 직류성분의 양은 재생신호의 에지 출현확률에 의해서 변화한다. 일방 배타적논리화 게이트(12)의 출력을 적분해서 얻을 수 있는 신호는 재생신호의 에지의 출현확률에 의해서만 레벨이 변화하는 신호로 된다. 따라서 이들 배타적논리화 게이트(10, 12)의 출력 e 및 d를 차동증폭기가 포함된 LPF(14)에 공급하므로써 위상정보에 의해서만 레벨이 변화하는 신호를 얻을 수가 있다.

다시 말하면, D형 플립플롭(9, 11) 및 배타적 논리화 게이트(10, 12)는 입력신호 a와 π상출력 f와의 위상차를 검출하고 제6도에 나타낸 것과 같이 입력 위상차의 1π로부터 π까지의 범위에 이르는 변화에 대하여 출력이 직선적으로 변화하는 위상 비교수단을 형성하게 된다. 이 위상비교수단을 형성하는 D형 플립플롭(9, 11) 및 배타적 논리화 게이트(10, 12)는 LPE(14), VCO(15) 및 분주기(16)와 함께 PLL을 형성하고, π상 출력 f가 입상에지의 출현타이밍과 재생신호 a의 입상에지 및 입하에지의 출현타이밍이 일치하고 π상 출력 f의 복조용재생 클럭으로서 출력되게 된다.

이상의 동작에 있어서, D형 플립플롭(9)은 입력신호 a를 재생클럭으로 하고서 π상 출력 f에 의해서 랫치시키고 또한 D형 플립플롭(11) 및 게이트(10, 12)와 함께 재생클럭으로서의 π상 출력 f를 발생하는 PLL의 위상 비교수단을 형성하고 있으므로, 위상지연이 존재하지 않고 D형 플립플롭(9)으로부터 제1도에 있어서의 위상 조정회로(8)와 같은 회로없이도 기억회로(2)의 출력과 동등한 신호를 얻을 수 있게된다. 또한 위상비교수단을 형성하는 D형 플립플롭(9)에는 입력신호 a가 직접공급 되고 있고 제1도에서 미분회로(1), 전파정류회로(3) 및 단안정멀티(4)가 필요없게 되어 있기 때문에, 구성이 간단할 뿐 아니라 시한설정용 콘덴서등의 외부 부착용단자가 불필요하게 되어 IC화가 용이하다.

상기 실시예에서는 D형 플립플롭(9)의 출력 b가 데이터 출력으로 되고 또한 π상 출력 f가 재생클럭으로서 출력되는 것으로 했으나, D형 플립플롭(11)의 출력 C가 데이터 출력으로 되고 또한 0상출력 g가 재생클럭으로서 출력되도록 해도 좋다. 또한 상기 실시예에서는 VCO(15)의 발진주파수를 클럭주파수의 2배로 하였으나, VCO(15)의 뉴티 사이클(duty cycle)이 50%일 때는 VCO(15)의 발진주파수가 클럭주파수와 같게 되게해서 분주기(16)를 생략하는 것이 가능하다. 또한 상기 실시예에 있어서 배타적 논리화 게

이상 설명한 바와 같이 본 발명에 의한 클럭재생회로는 2개의 기억수단 및 2개의 배타적논리화 수단에 의해서 입력신호와 재생클럭과를 직접 위상비교해서 재생클럭의 위상을 제어하는 구성으로 되어 있으므로 구성이 간단하고 또한 시한설정용 콘덴서등의 외부부착용 단자가 불필요해서 IC화를 용이하게 한다.

### (57) 청구의 범위

#### 청구항 1

펄스발생수단과, 상기 펄스발생수단으로부터 출력된 펄스에 동기시켜서 입력신호(a)를 일시기억하는 제1 기억수단(9)과, 상기 펄스에 동기시켜 상기 제1 기억수단의 기억내용을 일시기억하는 제2기억수단(11)과, 상기 입력신호 및 상기 제1기억수단의 기억내용에 응한 신호의 배타적논리화를 취하는 제1배타적 논리화수단(10)과, 상기 제1 및 제2 기억수단의 각각의 기억내용을 각각 나타내는 2신호의 배타적논리화를 취하는 제2 배타적 논리화수단(12)과를 포함하며, 상기 제1 및 제2 배타적 논리화수단의 각 출력의 펄스폭이 서로 같게 되도록 상기 펄스의 반복주파수를 제어하는 것에 의해서 상기 입력신호와 상기 펄스간의 위상차를 없애면서 상기 펄스를 재생클럭으로 출력하는 것을 특징으로하는 클럭재생회로로.

#### 도면

##### 도면 1

도면2

도면3

도면4

도면5

도면6