### Demande de brevet déposée pour la Suisse et le Liechtenstein Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

# (2) FASCICULE DE LA DEMANDE A3

617 817 G

(21) Numéro de la demande: 12011/76

Kazuhiro Asano, Tokyo (JP)

(71) Requérant(s):

Kabushiki Kaisha Daini Seikosha, Tokyo (JP)

(22) Date de dépôt:

22.09.1976

(30) Priorité(s):

22.09.1975 JP 50-114548

23.09.1975 JP 50-115210

(42) Demande publiée le:

30.06.1980

(74) Mandataire: Bovard & Cie., Bern

(72) Inventeur(s):

(44) Fascicule de la demande publié le:

30.06.1980

(56) Rapport de recherche au verso

#### (54) Circuit élévateur de tension.

(57) Le circuit comprend plusieurs unités élévatrices de tension (50, 51, 52) connectées en série. Chaque unité comprend un transistor principal (55, 61, 68) et un condensateur (59, 66, 71). Les transistors principaux sont alternativement bloqués et rendus passants, de façon à faire passer la charge d'un condensateur d'une unité sur celui de l'unité suivante. Par ailleurs, des signaux impulsionnels, de phase opposée d'une unité à l'autre, sont appliqués à la borne du condensateur de chaque unité non reliée au transistor de cette unité, ceci dans toutes les unités à l'exception de la dernière dans laquelle l'autre borne du condensateur est connectée à une tension fixe (54).

Ce circuit est prévu principalement pour une montre électronique ou une calculatrice miniature.

Bundesamt für geistiges Eigentum Office fédéral de la propriété intellectuelle Ufficio federale della proprietà intellettuale

## RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de brevet No.: Patentgesuch Nr.:

12 011/76

1.1.B. Nr.:

HO 12 316

| Documents considérés comme pertinents<br>Einschlägige Dokumente |                                                                                                                                                                                       |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catégorie<br>Kategorie                                          | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile             | Revendications con-<br>cernées<br>Betrifft Anspruch<br>Nr. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0                                                               | WESCON TECHNICAL PAPERS, volume 19, no. 19, 1975 (Wescon Technical Sessions 16-19 septembre 1975) North Hollywood, USA J. KERINS "CMOS circuits for digital watches" pages 17/2 (1-4) | I, 1                                                       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                 | * Figure 5 *                                                                                                                                                                          |                                                            | Domaines techniques recherches Recherchierte Sachgebiete (INT. CL. <sup>2</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                 | FR-A-2 162 159 (K.K. DAINI SEIKOSHA)  * Figure 6 *                                                                                                                                    | I                                                          | G 04 C 3/00<br>H 02 M 3/155<br>G 04 F 5/00<br>H 03 K 5/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -                                                               |                                                                                                                                                                                       |                                                            | Catégorie des documents cités Kategorie der genanûten Dokumente: X: particulièrement pertinent von besonderer Bedeutung A: arrière-plan technologique technologischer Hintergrund O: divulgation non-écrite nichtschriftliche Offenbarung P: document intercalaire Zwischenliteratur T: théorie ou principe à la base de l'invention der Erfindung zugrunde liegende Theorien oder Grundsätze E: demande faisant interférence kollidierende Anmeldung L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument &: membre de la même famille, document correspondant Mitglied der gleichen Patentfamilie; übereinstimmendes Dokument |

Etendue de la recherche/Umfang der Recherche

Revendications ayant fait l'objet de recherches Recherchierte Patentansprüche:

ensemble

Revendications n'ayant pas fait l'objet de recherches Nicht recherchierte Patentansprüche: Raison: Grund:

Date d'achèvement de la recherche/Abschlussdatum der Recherche

Examinateur I.I.B./1.1.B Prüfer

18 juillet 1977

#### REVENDICATION

Circuit élévateur de tension comprenant une pluralité d'unités élévatrices de tension connectées en série et dont chacune comprend un condensateur et un premier transistor MOS FET, caractérisé en ce que, dans la première dite unité, ledit premier transistor MOS FET est connecté entre une borne (19) dudit condensateur de cette unité et un pôle (14) d'une source d'alimentation, de façon à connecter ce pôle à cette borne de condensateur lorsque ce premier transistor MOS FET est conducteur, tandis que, dans chacune des unités suivantes, ledit transistor MOS FET est connecté entre une borne (17) du condensateur de l'unité et la borne correspondante, connectée au transistor MOS FET du condensateur de l'unité immédiatement précédente, de façon que lorsque le transistor MOS FET d'une unité, suivant la première, est conducteur, la borne du condensateur de cette unité soit connectée avec la borne correspondante du condensateur de l'unité immédiatement précédente, chaque unité comprenant également des moyens de commutation formés d'un deuxième transistor MOS FET (3, 8) dont la source est connectée à l'autre pôle (16) de la source d'alimentation, et d'un troisième transistor MOS FET (4, 9) dont la source est connectée à ladite borne du condensateur connectée au premier transistor de l'unité, les drains des deuxième et troisième transistors MOS FET de chaque unité étant connectés entre eux et connectés également à l'électrode de commande du premier transistor MOS FET, des moyens étant établis pour appliquer aux électrodes de commande des deuxième et troisième transistors MOS FET de chaque unité un signal impulsionnel qui, par l'intermédiaire des deuxième et troisième transistors MOS FET, met alternativement le premier transistor MOS FET de chaque unité à l'état conducteur et à l'état bloqué, lesdits signaux impulsionnels appliqués à chaque unité étant tels que les premiers transistors MOS FET de chaque unité de rang pair soient conducteurs alors que ceux de chaque unité de rang impair sont bloqués, et inversement, l'autre borne du condensateur de la dernière unité étant connectée à un des pôles de la source d'alimentation, tandis que l'autre borne du condensateur de chacune des autres unités est connectée à une source de signal impulsionnel, de façon telle que, d'une unité à la suivante, il y ait inversion de phase du signal impulsionnel sur cette seconde borne de condensateur.

) ——

La présente invention concerne un circuit élévateur de tension comprenant une pluralité d'unités élévatrices de tension connectées en série et dont chacune comprend un condensateur et un premier transistor MOS FET. L'invention vise en particulier l'obtention d'un circuit élévateur de tension de petites dimensions

On connaît un circuit élévateur de tension comprenant une diode et un condensateur; ce circuit est toutefois très difficile à réaliser sous forme de circuit intégré et, de ce fait, l'espace nécessaire aux éléments du circuit élévateur de tension était une des causes principales qui empêchaient d'obtenir de petites dimensions. De plus, le coût des éléments du circuit était élevé, ce qui rendait élevé le coût d'une montre électronique ou d'une calculatrice miniature utilisant un tel circuit élévateur de tension.

Il y a lieu également de considérer deux publications antérieures qui concernent des élévateurs de tension. La première consiste en l'article de J. Kerins, intitulé «CMOS circuits for digital watches», paru dans la revue «Wescon Technical Papers», N° 19, de septembre 1975, cet article proposant, en liaison avec sa fig. 5, la mise, alternativement en série et en parallèle, de circuits comportant des transistors MOS complémentaires et des condensateurs, pour réaliser un agencement multiplicateur de tension.

L'autre publication antérieure considérée est l'exposé de demande de brevet français N° 2162159, lequel, également en

liaison avec des figures, propose un agencement analogue à celui que divulgue la première publication antérieure susmentionnée.

Selon cet art antérieur, on propose toutefois simplement un dispositif dans lequel des condensateurs sont alternativement, dans une première phase d'opération, chargés en parallèle, puis, dans une seconde phase d'opération, déchargés en série. On remarque que deux condensateurs suffisent pour tripler la tension, étant donné que la source de tension initiale est encore mise en série dans la seconde phase. Avec un tel agencement, la tension de 10 sortie est délivrée (le plus souvent avec un condensateur-tampon de sortie d'une capacité relativement importante) par plusieurs condensateurs qui sont en série les uns avec les autres. Il n'y a pas dans l'agencement de circuit lui-même un condensateur qui se charge à la tension de sortie totale. La capacité de délivrance du 15 courant de sortie est donc formée de plusieurs condensateurs en série, ce qui est désavantageux du point de vue du rapport capacité de sortie/encombrement. Le but de la présente invention est de fournir un circuit élévateur de tension du type générique précédemment défini qui soit plus avantageux que ce que connais-20 sait la technique antérieure, et qui puisse être notamment réalisé sous forme d'un circuit intégré de petites dimensions, d'une façon permettant l'insertion avantageuse du circuit élévateur de tension dans une montre électronique ou une calculatrice de petit format.

Conformément à l'invention, ce but est atteint par la présence 25 des caractères énoncés dans la revendication annexée.

On remarque que l'invention permet de réaliser un circuit élévateur de petites dimensions qui se compose seulement de condensateurs et de MOS FET, à l'exclusion de toute autre diode.

L'utilisation de plusieurs unités élévatrices de tension connectées en série permet d'obtenir une élévation de tension aussi élevée que cela est désiré, la tension de sortie d'une unité élévatrice de tension étant utilisée comme tension standard pour l'unité suivante.

Le dessin annexé illustre, à titre d'exemple, des formes d'exé-35 cution de l'objet de l'invention. Dans ce dessin:

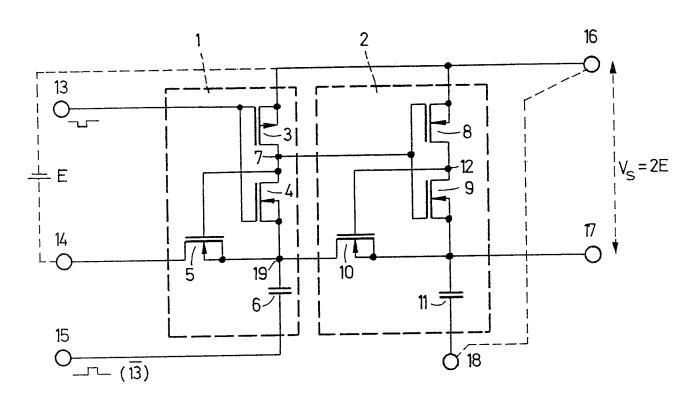

la fig. 1 représente le schéma d'une forme d'exécution du circuit élévateur de tension comprenant deux unités élévatrices de tension;

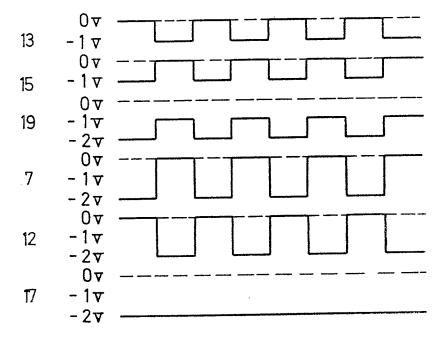

la fig. 2 est un diagramme de formes d'onde en différents 40 endroits du circuit de la fig. 1;

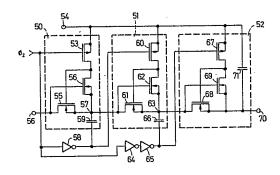

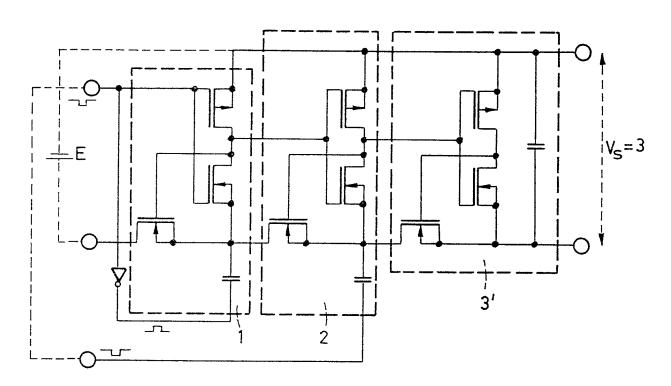

la fig. 3 représente une autre forme d'exécution d'un circuit élévateur de tension triple, qui comprend trois unités élévatrices de tension:

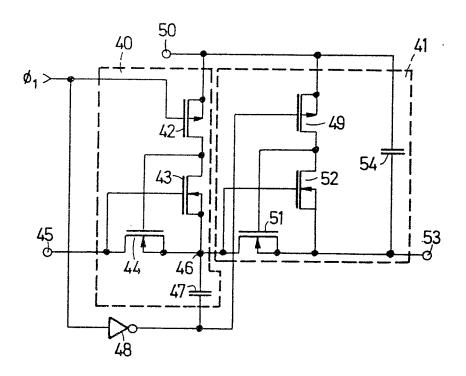

la fig. 4 représente une autre forme d'exécution d'un circuit 45 élévateur de tension à deux unités, du type particulier en question;

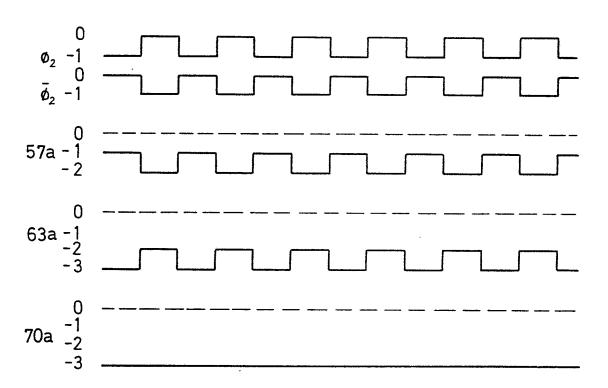

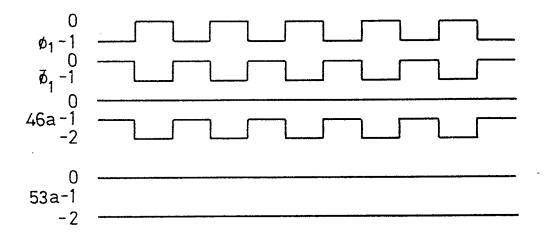

la fig. 5 est un diagramme de formes d'onde expliquant le fonctionnement du circuit de la fig. 4;

premier transistor MOS FET. L'invention vise en particulier la fig. 6 représente une autre forme d'exécution d'un circuit l'obtention d'un circuit élévateur de tension de petites dimensions. 50 élévateur de tension à trois unités du même type que celui de la fig. 4;

la fig. 7 est un diagramme de formes d'onde expliquant le fonctionnement du circuit de la fig. 6, et

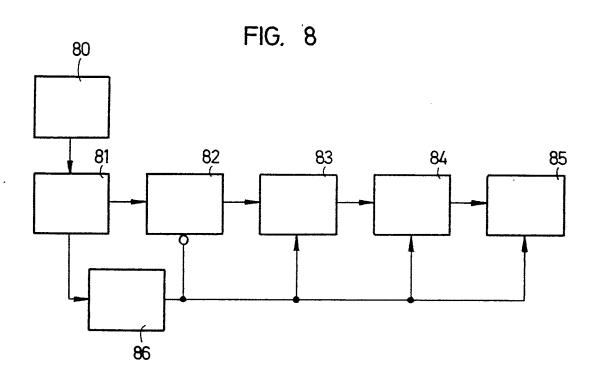

la fig. 8 est un schéma-bloc d'une montre électronique utilisant 55 un circuit élévateur de tension du type particulier en question.

Le circuit élévateur de tension représenté à la fig. 1 comprend deux unités élévatrices de tension, respectivement 1 et 2.

Sur cette figure, on voit qu'un MOS FET P 3 et un MOS FET P 4 constituent un inverseur utilisé dans l'unité élévatrice de tension 1, les grilles de ces MOS FET étant connectées en commun et les drains de ces éléments étant également connectés en commun. Les grilles sont connectées à une connexion d'entrée et les drains sont connectés à la grille d'un autre MOS FET N 5 compris dans l'unité élévatrice de tension 1.

Par ailleurs, la source du MOS FET P 3 est connectée à une connexion 16 d'amenée de tension et la source du MOS FET N 5 est connectée à la source du MOS FET N 4, en même temps qu'à une électrode d'un premier condensateur 6 également compris

dans l'unité 1. Le drain du MOS FET N 5 est connecté à une connexion d'entrée de tension 14, l'autre électrode du condensateur 6 étant connectée à une connexion d'entrée 15.

Par ailleurs, un MOS FET P 8 et un MOS FET N 9 sont utilisés pour constituer un inverseur dans l'unité élévatrice de tension 2, leurs drains étant connectés ensemble, de même que leurs grilles qui sont encore connectées à un point de circuit 7 qui constitue la connexion commune de drains des MOS FET P 3 et MOS FET N 4 de l'unité 1. La connexion commune de drains des MOS FET P 8 et MOS FET P 9 est connectée à la grille d'un second MOS FET N 10 compris dans l'unité élévatrice de tension 2.

Par ailleurs, la source du MOS FET P 8 de la seconde unité 2 est connectée à la connexion d'amenée de tension 16 et la source du MOS FET N 9 est connectée à la source du second MOS FET N 10, en même temps qu'elle est connectée à une connexion de sortie 17 et à un second condensateur 11. Le drain du second MOS FET N 10 est connecté au point 19 qui relie les sources des MOS FET N 4 et 5, de même qu'une borne du condensateur 6, dans l'unité élévatrice de tension 1. L'autre borne du second condensateur 11, compris dans la seconde unité 2, est connectée à une connexion 18 qui est une connexion d'amenée de tension si ce condensateur 11 doit jouer le rôle d'un condensateur de filtrage, mais qui pourrait être une connexion d'entrée, recevant un signal binaire, si ce condensateur devait jouer encore un rôle d'élévation 25 sateur 11 se charge lentement et finit par atteindre une tension de tension pour une unité suivante.

Les connexions 16 et 18 reçoivent la tension élevée (ou positive) d'une source de tension, tandis que la connexion d'entrée 14 reçoit la tension basse (ou négative) de cette source de tension. La connexion d'entrée 13 reçoit un signal d'entrée binaire de commande du circuit élévateur de tension; par exemple, un signal issu d'une division de la fréquence d'un circuit oscillateur peut être employé en tant que signal d'entrée sur ladite connexion d'entrée 13. La connexion d'entrée 15 reçoit un signal binaire qui est déphasé de 180° par rapport à celui qui est appliqué à la connexion d'entrée 13.

Par ailleurs, le signal de sortie, à tension plus élevée, fourni par le circuit élévateur de tension apparaît sur la connexion de sortie 17.

Pour la description que l'on va donner du fonctionnement du circuit représenté à la fig. 1, on admettra que l'on a une source de tension de 1 V, la tension sur les connexions 16 et 18 étant de 0 V et la tension sur la connexion 14 étant de -1 V. Au départ, la tension de la connexion 17 est d'approximativement -1 V provenant de la charge du condensateur 11 par les diodes parasites des MOS FET N 5 et 10; de même, la tension sur le point de connexion 19 est d'approximativement -1 V. Dans ces conditions, lorsque la tension sur la connexion d'entrée 13 devient égale à -1 V et que la tension sur la connexion d'entrée 15 devient égale à 0 V, le MOS FET P 3 devient passant, pour autant que sa tension 50 d'exécution comprenant trois unités élévatrices de tension brande seuil VTP soit inférieure à 1 V. Le MOS FET N 4 vient dans l'état bloqué, ayant sur sa grille la même tension que sur sa source.

Ainsi, la tension du point de connexion 7 est égale à 0 V et le MOS FET N 5 devient passant, sa tension de seuil VTN étant inférieure à 1 V.

D'autre part, la tension de 0 V sur le point 7 amène le MOS FET P 8 à l'état bloqué et le MOS FET N 9 à l'état passant.

Les tensions de source et de grille du MOS FET N 10 sont égales, ce qui fait que cet élément est à l'état bloqué.

Comme la tension sur la connexion d'entrée 15 est de 0 V et que le MOS FET N 5 est passant, le condensateur 6 se charge et prend entre ses bornes une tension de 1 V.

Ensuite, lorsque les signaux complémentaires sur les connexions d'entrée 13 et 15 sont inversés, le MOS FET P 3 passe à l'état bloqué, tandis que le MOS FET N 4 passe à l'état passant et que le MOS FET N 5, dont la source et la grille sont courtcircuitées par le MOS FET N 4, passe à l'état bloqué. Le conden-

sateur 6 ne peut pas se décharger soudainement, ce qui fait qu'une tension de -2 V se trouve présente sur le point 19 du fait que la tension sur la connexion d'entrée 15 est devenue égale à -1 V. Ainsi, la tension sur le point 7 devient aussi égale à -2 V et MOS FET P 8 passe à l'état passant tandis que le MOS FET N 9 passe à l'état bloqué. Une tension de 0 V se présente donc sur le point 12, ce qui rend passant le MOS FET N 10 qui transmet ainsi sur la connexion de sortie 17 et sur le second condensateur 11 la tension de -2 V du point 19, diminuée d'une légère 10 chute de tension dans le MOS FET N 10, mais d'une quantité suffisamment faible pour que la tension sur la connexion de sortie 17 soit plus basse, c'est-à-dire plus négative, plus grande en valeur absolue, que 1 V. A ce moment, le premier condensateur 6 décharge lentement la charge qu'il a emmagasinée.

Lorsque les signaux d'entrée sont de nouveau inversés et que la connexion d'entrée 13 reprend la tension de -1 V, tandis que la connexion d'entrée 15 reprend la tension de 0 V, le premier transistor 16 se charge à nouveau par l'intermédiaire du MOS FET N 5, tandis que le MOS FET N 10 est à nouveau bloqué, 20 isolant la sortie 17 qui reste à la tension précédemment acquise du fait du second condensateur 11. Les charges sont ainsi cycliquement établies dans le condensateur 6, puis transmises dans le condensateur 11.

Lorsque les opérations susmentionnées se répètent, le condendouble de celle de la source de tension, tension double qu'il délivre sur la connexion de sortie 17.

Une certaine charge se trouve connectée entre les connexions 16 et 17, mais le condensateur 11 se recharge lors des 30 opérations répétées de commutation et la tension de sortie reste constante, malgré une certaine décharge du second condensateur 11 dans la charge branchée entre les connexions 16 et 17.

La fig. 2 illustre l'évolution des niveaux de tension aux différents points du circuit de la fig. 1, les conditions de fonctionne-35 ment normal étant admises.

Dans un circuit élévateur de tension tel que celui de la fig. 1. chacun des MOS FET peut être aisément établi dans un circuit intégré logique et calculateur du genre utilisé dans les montres, notamment les montres-bracelets, les montres électroniques, et dans les petites calculatrices de poche. Seuls les condensateurs constituent des éléments additionnels indépendants, et l'encombrement du circuit élévateur de tension pour une montre électronique ou une petite calculatrice est remarquablement réduit, le coût s'en trouvant également diminué. Par ailleurs, il est 45 possible d'obtenir un fonctionnement d'élévation de tension fournissant une tension supérieure au double de la tension d'alimentation en prévoyant la connexion en série d'un plus grand nombre d'unités élévatrices de tension.

La fig. 3 montre, simplement à titre d'exemple, une forme chées en série et fournissant une tension trois fois plus élevée, ce circuit élévateur de tension de la fig. 3 se distinguant de celui de la fig. 1 par la présence d'une troisième unité élévatrice de tension 3'.

La fig. 4 représente une autre forme d'exécution d'un circuit 55 élévateur de tension, qui fournit en l'occurrence une tension double de la tension d'alimentation.

Cette forme d'exécution comprend une première unité élévatrice de tension 40 et une seconde unité élévatrice de tension 41. La première unité 40 comprend un MOS FET P 42, constituant 60 l'élément de commutation, et dont la source est connectée à un point 50 d'amenée de la tension positive de la source de tension. Une entrée d'impulsions Ø1 est appliquée à ce MOS FET P 42. Un premier MOS FET N de l'unité 40 a sa grille connectée à la connexion d'amenée de tension négative 45 à laquelle se trouve 65 également connecté le drain d'un second MOS FET N 44 de l'unité 40. Le drain du MOS FET N 43 est connecté au drain du MOS FET P 42, tandis que la source du MOS FET N 43 et la source du MOS FET N 44 sont connectées ensemble. La grille du MOS FET N 44 est reliée à la connexion commune de drains du MOS FET P 42 et du MOS FET N 43. La connexion commune de sources des MOS FET N 43 et 44 constitue un point de circuit 46 relié à un premier condensateur 47.

Un signal constituant l'inverse du signal impulsionnel d'entrée  $\emptyset_1$ , obtenu à l'aide d'un inverseur 48, est appliqué à l'autre borne de ce condensateur 47 et, par l'intermédiaire de ce dernier, au point de circuit 46.

La seconde unité élévatrice de tension 41 du circuit élévateur de tension de la fig. 4 comprend un MOS FET P 49 dont la source 10 est connectée au point 50 d'amenée de tension positive depuis la source de tension. Le signal inverse du signal  $\emptyset_1$ , provenant de l'inverseur 48, est appliqué à la grille du MOS FET P 49. La grille d'un premier MOS FET N 51 de la seconde unité élévatrice de tension 41 est connectée au drain du MOS FET P 49, auquel est connecté également le drain d'un second MOS FET N 52 de l'unité 41. Le drain du MOS FET N 51 est relié à la connexion commune 46 des deux MOS FET N 43 et 44 de la première unité 40, point de circuit auquel est également reliée la grille du MOS FET N 52. Les sources des MOS FET N 51 et 52 sont connectées ensemble et sont reliées également à une borne d'un second condensateur 54 dont l'autre borne est reliée au point d'alimentation positive 50. La connexion commune des sources des MOS FET N 51 et 52 et du condensateur 54 constitue en même temps la connexion de sortie 53 du circuit élévateur de tension, connexion de sortie sur laquelle apparaît une tension plus grande que la tension d'alimentation, par rapport à la connexion d'amenée de tension positive 50. La tension entre les points 50 et 53 est donc une tension augmentée, supérieure à celle de la source d'alimentation appliquée entre les points 50 et 45.

Les diagrammes de formes d'onde de la fig. 5 illustrent le fonctionnement du circuit de la fig. 4. Le signal impulsionnel d'entrée  $\emptyset_1$  (première courbe de la fig. 5) est appliqué à la grille du MOS FET P 42 de l'unité 40, tandis que son inverse  $\overline{\emptyset}_1$ , obtenu par l'inverseur 48 et montré à la seconde courbe de la fig. 5, est appliqué à la grille du MOS FET P 49 de la seconde unité 41, en même temps qu'il est appliqué audit condensateur 47. Dans ces conditions, si la tension du point d'alimentation positif 50 est admise à 0 V, tandis que la tension du point d'alimentation négatif 45 est de -1 V, le MOS FET P 42 devient conducteur lorsque la tension impulsionnelle d'entrée Ø1 est de -1 V. Ainsi, le MOS FET N 44 devient également passant, ce par quoi la tension sur le point 46 devient égale à -1 V. A ce moment, la tension sur l'autre borne du condensateur 47, provenant de la sortie de l'inverseur 48, est de 0 V. Ainsi, ce condensateur 47 se charge. Ensuite, lorsque la tension du signal impulsionnel d'entrée Ø1 devient 0 V, le MOS FET P 42 se bloque, le MOS FET N 43 devient passant et le MOS FET N 44 passe à l'état bloqué. Une tension de -2 V, donc une tension plus basse que la tension négative d'alimentation sur le point 45, apparaît sur le point de circuit 46 étant donné que l'autre borne du condensateur 47, reliée à la sortie de l'inverseur 48, a passé à la tension de -1 V. Ensuite, lorsque la tension impulsionnelle d'entrée Ø<sub>1</sub> change à nouveau pour prendre la valeur -1 V, le MOS FET P 42 et le MOS FET N 44 redeviennent passants et la tension sur le point de circuit 46 redevient égale à -1 V, le MOS FET N 43 étant à l'état bloqué. La courbe 46a de la fig. 5 montre l'évolution de la tension sur le point 46 du circuit de la fig. 4.

Dans la seconde unité élévatrice de tension 41, lorsque la tension du signal d'entrée inversé  $\overline{\mathcal{O}}_1$  appliquée à la grille du MOS 60 FET P 49 devient -1 V, ce MOS FET P 49 devient passant de même que le MOS FET N 51, tandis que le MOS FET N 52 se bloque. Ainsi, la tension de -2 V présente sur le point 46 est transmise sur la connexion de sortie 53. Ensuite, lorsque l'inverse  $\overline{\mathcal{O}}_1$  du signal d'entrée reprend la tension de 0 V, le MOS FET P 49 et le MOS FET N 51 redeviennent bloqués tandis que le MOS FET N 52 redevient passant. Dans ce cas, aucune alimentation électrique n'est appliquée à la connexion de sortie 53;

toutefois, cette dernière maintient la tension de -2 V du fait de la charge du condensateur 54. La dernière courbe, 53a, de la fig. 5 montre la tension sur la connexion de sortie 53, tension qui est une tension continue de -2 V.

Ainsi, il est possible d'obtenir une tension élevée égale au double de la tension d'alimentation en connectant en série les deux unités élévatrices de tension 40 et 41.

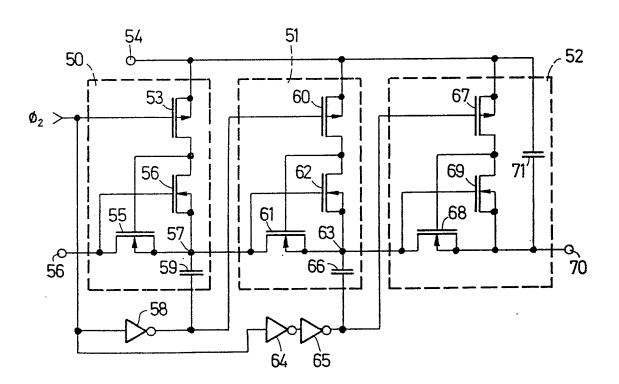

La fig. 6 représente une autre forme d'exécution d'un circuit élévateur de tension utilisant trois unités analogues à celles de la fig. 4 pour obtenir une élévation de tension de 1 à 3.

Les trois unités élévatrices de tension de cette forme d'exécution sont désignées respectivement par les signes de référence 50, 51 et 52. La première unité 50 comprend un MOS FET 53 qui forme un élément de commutation et dont la source est connectée à l'arrivée de tension positive 51 d'une source de tension standard. Un signal impulsionnel d'entrée Ø2 est appliqué à la grille de ce MOS FET P 53, la grille d'un premier MOS FET N 55 étant connectée au drain de ce MOS FET P 53 auquel est également 20 connecté le drain d'un second MOS FET N 56 de cette unité élévatrice de tension 50. Le drain du MOS FET N 55 est connecté au point 56 d'amenée de la tension négative de la source de tension standard, point auquel est également connectée la grille du MOS FET N 56. Les sources des MOS FET N 55 et 56 sont connectées en commun à un point de circuit 57 auquel est reliée également une borne d'un premier condensateur 59 dont l'autre borne reçoit l'inverse  $\emptyset_2$  du signal impulsionnel d'entrée  $\emptyset_2$ , par l'intermédiaire d'un inverseur 58.

La seconde unité élévatrice de tension 51 comprend un MOS 30 FET P 60 qui forme un élément de commutation et dont la source est connectée au point d'amenée 54 de la tension positive de la source de tension standard. L'inverse du signal impulsionnel d'entrée Ø2 est appliqué à la grille de ce MOS FET P 60, en provenance de l'inverseur 58. La grille d'un premier MOS FET N 61 de cette seconde unité 51 est connectée au drain du MOS FET P 60 auguel est connecté également le drain d'un second MOS FET N 62 de cette unité 51. Le drain du MOS FET N 61 est connecté au point 57 de connexion commune des sources des MOS FET N 55 et 56 de la première unité élévatrice de tension 50, la grille du second MOS FET N 62 de l'unité 51 étant également connectée à ce point 57. Les sources des MOS FET N 61 et 62 sont connectées ensemble sur un point 63 auquel est connectée une borne d'un second condensateur 66 dont l'autre borne reçoit le signal impulsionnel d'entrée Ø2 qui lui est appliqué par l'intermédiaire de deux inverseurs 64 et 65.

La troisième unité élévatrice de tension 52 comprend, similairement à la seconde, un MOS FET P 67 qui constitue un élément de commutation et dont la source est connectée au 50 point 54 d'amenée de la tension positive de la source de tension standard. Le signal impulsionnel sortant des deux inverseurs en cascade 64 et 65 est appliqué à la grille du MOS FET R 67 au drain duquel est connectée la grille d'un premier MOS FET N 68 de la troisième unité élévatrice de tension 52. Le drain d'un second MOS FET N 69 de cette troisième unité est également connecté au drain du MOS FET P 67. Le drain du MOS FET N 68, conjointement avec la grille du MOS FET N 69, est relié à la connexion commune 63 des MOS FET N 61 et 62 de la seconde unité. Les sources des MOS FET N 68 et 69 de la troisième unité sont connectées ensemble et sont reliées également à une connexion de sortie 70 du circuit élévateur de tension en même temps qu'à une borne d'un condensateur 71 dont l'autre borne est connectée au point 54 d'amenée de la tension positive de la source

Avec ce circuit, il est possible d'obtenir entre le point 54 d'alimentation positive et la connexion de sortie 70 une tension notablement plus élevée que la tension d'alimentation appliquée entre les points 50 et 56.

Le fonctionnement de ce circuit élévateur de la fig. 6 sera maintenant expliqué en liaison avec le diagramme de formes d'onde de la fig. 7.

Le signal impulsionnel d'entrée Ø2, représenté par la première courbe de la fig. 7, est appliqué à l'électrode de grille du MOS FET P 53 de la première unité élévatrice de tension 50. Un signal impulsionnel ayant la même phase que ce signal Ø2 est appliqué à la grille du MOS FET P 67 de la troisième unité élévatrice de tension 52, de même qu'au condensateur 66. L'inverse  $\overline{\emptyset}_2$  de ce signal d'entrée représenté par la seconde courbe de la fig. 7, et obtenu par l'inverseur 58, est appliqué à la grille du MOS FET P 60 de la seconde unité 51, de même qu'au condensateur 59 de la première unité 50.

Dans ces conditions, en admettant que la tension du point 54 d'amenée de la tension positive de la source de tension de base est de 0 V et que la tension du point 56 d'amenée de la tension négative de la source de tension de base est de -1 V, on voit qu'un signal ayant la forme représentée par la troisième courbe de la fig. 7 se trouve engendré sur ledit point de connexion 57 lorsque le 20 de temps standard fournies par le circuit diviseur de fréquence 81 signal impulsionnel d'entrée Ø2 passe séquentiellement par des créneaux de 0 V et de -1 V. Ce signal est appliqué au drain du MOS FET N 61 et à la grille du MOS FET N 62 de la seconde unité élévatrice de tension 51 lorsque la tension du signal d'entrée inverse  $\overline{Q}_2$  est de -1 V, le MOS FET P 60 et le MOS FET P 61 étant passants, tandis que le MOS FET P 62 est bloqué. A ce moment, la tension sur le point 57 est de -2 V et elle est transmise sur le point 63 qui aura également la tension de -2 V.

Lorsque la tension du signal d'entrée inverse  $\overline{\emptyset}_2$  passe au niveau 0 V, le MOS FET P 60 et le MOS FET N 61 se bloquent. tandis que le MOS FET N 62 devient passant. Au même moment, la tension à la sortie de l'inverseur 63 change de 0 V à -1 V, ce qui a pour effet, par l'intermédiaire du condensateur 66, de faire passer la tension sur le point 63 de -2 V à -3 V. L'évolution de la tension sur ce point de circuit 63 est représentée par la quatrième courbe de la fig. 7. Les changements de tension sur ce point 63 sont appliqués au drain du MOS FET N 68 et à la grille du MOS FET N 69 de la troisième unité élévatrice de tension 52 lorsque le signal d'entrée Ø2 appliqué à la grille du MOS FET P 67 présente la tension -1 V, ce qui rend passant le MOS FET P 67 et le MOS FET N 68, ce dernier transmettant alors la tension de -3 V du point de circuit 63 sur la connexion de sortie 70. Cette tension de -3 V est maintenue par le condensateur 71. Ensuite, lorsque la tension de l'impulsion d'entrée appliquée au MOS FET P 67 passe à 0 V, le MOS FET P 67 et le MOS FET N 68 se bloquent, mais la tension sur la connexion de sortie 70 se maintient à -3 V du fait du condensateur 71, comme cela est indiqué par la dernière courbe (70a) de la fig. 7.

On voit qu'il est ainsi possible d'obtenir une tension rehaussée égale à 3 fois la tension d'alimentation en connectant en série, comme le montre la fig. 6, trois unités élévatrices de tension, respectivement 50, 51 et 52.

La fig. 8 représente le schéma-bloc d'une montre électronique utilisant un circuit élévateur de tension du type particulier en question. Sur cette figure, on voit un oscillateur 80 muni d'un élément à quartz, et un circuit diviseur de fréquence 81 qui fournit un signal de base de temps à 1 Hz par division de la fréquence du signal délivré par l'oscillateur 80, ce signal à 1 Hz étant appliqué à un décaleur de niveau 82. Un signal issu de division, prélevé sur un étage approprié du diviseur de fréquence 81, est appliqué à un circuit élévateur de tension 86 en tant que signal impulsionnel d'entrée. Ce circuit élévateur de tension 86 fournit une tension plus élevée égale au triple de la tension d'alimentation standard. Cette tension plus élevée est appliquée au décaleur de niveau 82, de même qu'à un dispositif de comptage du temps 83, à un circuit de commande d'affichage 84 et à un dispositif d'affichage 85. Ledit décaleur de niveau 82 décale le niveau desdites impulsions et elles appliquent ces impulsions à niveau de tension décalé à l'agencement de comptage du temps 83. Ce dernier engendre des signaux de comptage correspondant aux informations de temps et les applique au circuit de commande d'affichage après les avoir transcodés en un système adéquat pour commander le dispositif d'affichage 85, par exemple des signaux d'affichage du type à sept segments. Le circuit de commande 84 amplifie ces signaux pour les appliquer au dispositif d'affichage 85.

La conception qui vient d'être décrite ne se limite pas aux 30 formes d'exécution qui viennent d'être décrites, et il est possible d'apporter des changements et modifications au circuit élévateur de tension en question sans sortir du cadre de cette conception particulière.

Selon cette dernière, le circuit élévateur de tension en question 35 comprend une pluralité d'unités élévatrices de tension munies de MOS FET, ce qui permet d'obtenir un agencement unitaire d'élévation de tension notablement plus petit qu'un agencement élévateur de tension classique comprenant des diodes. De plus, il est possible de monter cet agencement élévateur de tension unitaire sur une même plaquette de circuit intégré et donc dans la même «puce» qui comprend les autres éléments de la circuiterie électronique. La tension présente sur la connexion commune des sources d'un premier et d'un second MOS FET de même polarité d'une unité élévatrice de tension est utilisée en tant que tension standard pour l'unité suivante, ce qui permet d'obtenir aisément une élévation de tension aussi forte que l'on désire, en connectant une pluralité d'unités élévatrices de tension en série les unes après les autres.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7