**(19) World Intellectual Property Organization**

International Bureau

A standard linear barcode is located at the bottom of the page, spanning most of the width. It is used for document tracking and identification.

**(43) International Publication Date

23 April 2009 (23.04.2009)**

PCT

(10) International Publication Number

**WO 2009/052089 A1**

**(51) International Patent Classification:**

*H01L 51/56 (2006.01) H01L 27/32 (2006.01)*

(81) **Designated States** (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

PCT/US2008/079799

PCT/US2008/079799

**(22) International Filing Date:** 14 October 2008 (14.10.2008)

**(25) Filing Language:** English

**(26) Publication Language:** English

**(30) Priority Data:** 60/980.019 15 October 2007 (15.10.2007) US

(71) **Applicant (for all designated States except US): E.I. DU**

(74) **Applicant for all designated States except US:** LAR D C PONT DE NEMOURS AND COMPANY [US/US]; 1007 Market Street, Wilmington, Delaware 19898 (US).

(75) Inventors/Applicants (for US only): TSAI, Yaw-Ming

(75) **Inventors/Applicants (for US only):** **TSAI, Yaw-Ming**

A. [—/US]; 1423 Pacific Avenue, Santa Barbara, California 93109 (US). **STAINER, Matthew** [GB/US]; 386 Vereda Del Cielo, Goleta, California 93117-5306 (US).

(74) **Agent: LAMMING, John, H.**; E.I. du Pont de Nemours and Company, Legal Patent Records Center, 4417 Lancaster Pike, Wilmington, Delaware 19805 (US).

(84) **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

**(54) Title: BACKPLANE STRUCTURES FOR SOLUTION PROCESSED ELECTRONIC DEVICES**

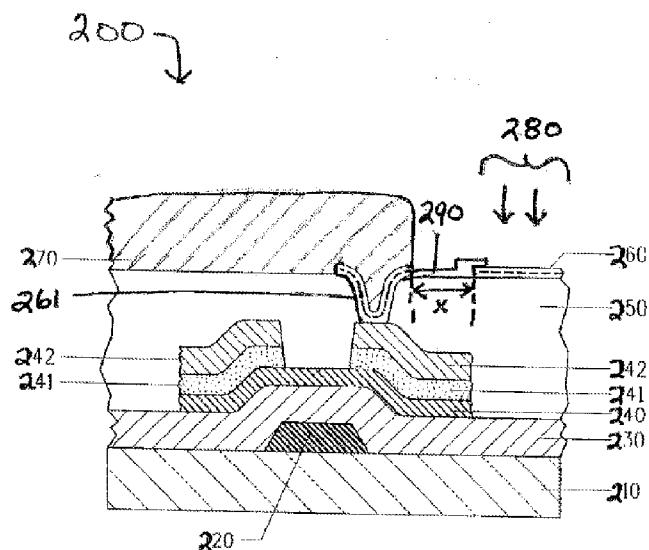

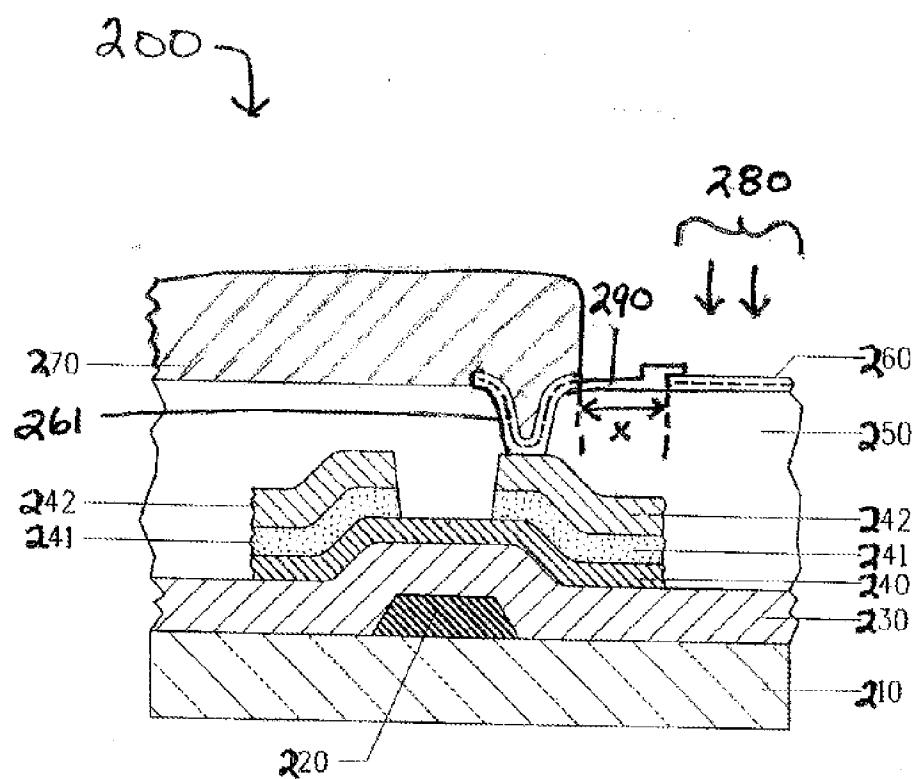

FIG. 4

**(57) Abstract:** There is provided a backplane for an organic electronic device. The backplane has a TFT substrate having a multiplicity of electrode structures thereon; a bank structure defining pixel areas over the electrode structures; and a thin layer of insulative inorganic material between the electrode structures and the bank structures. The bank structure is removed from and not in contact with the electrode structures by a distance of at least 0.1 microns.

TITLEBACKPLANE STRUCTURES FOR SOLUTION PROCESSED ELECTRONIC

DEVICES

5

BACKGROUND INFORMATIONField of the Disclosure

This disclosure relates in general to electronic devices and processes for forming the same. More specifically, it relates to backplane structures and 10 devices formed by solution processing using the backplane structures.

Description of the Related Art

Electronic devices, including organic electronic devices, continue to be more extensively used in everyday life. Examples of organic electronic devices include organic light-emitting diodes ("OLEDs"). A variety of deposition 15 techniques can be used in forming layers used in OLEDs. Liquid deposition techniques include printing techniques such as ink-jet printing and continuous nozzle printing.

As the devices become more complex and achieve greater resolution, the use of active matrix circuitry with thin film transistors ("TFTs") becomes more 20 necessary. However, surfaces of most TFT substrates are not planar. Liquid deposition onto these non-planar surfaces can result in non-uniform films. The non-uniformity may be mitigated by the choice of solvent for the coating formulation and/or by controlling the drying conditions. However, there still exists a need for a TFT substrate design that will result in improved film uniformity.

25

SUMMARY

In an embodiment, there is provided a backplane for an organic electronic device comprising:

30 a TFT substrate having a multiplicity of electrode structures thereon; a bank structure defining pixel areas over the electrode structures; wherein the bank structure is removed from and not in contact with the electrode structures by a distance of at least 0.1 microns; and

a thin layer of insulative inorganic material between the electrode structures and the bank structures.

35 There is also provided a process for forming an organic electronic device, said process comprising:

forming a backplane comprising:

5                   a TFT substrate having a multiplicity of electrode structures thereon;

and

a bank structure defining pixel areas over the electrode structures;

wherein the bank structure is removed from and not in contact with the

electrode structures by a distance of at least 0.1 microns; and

a thin layer of insulative inorganic material between the electrode

structures and the bank structures; and

depositing into at least a portion of the pixel openings a first liquid

composition comprising a first active material in a liquid medium.

10                  The foregoing general description and the following detailed description

are exemplary and explanatory only and are not restrictive of the invention, as

defined in the appended claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

15                  Embodiments are illustrated in the accompanying figures to improve

understanding of concepts as presented herein.

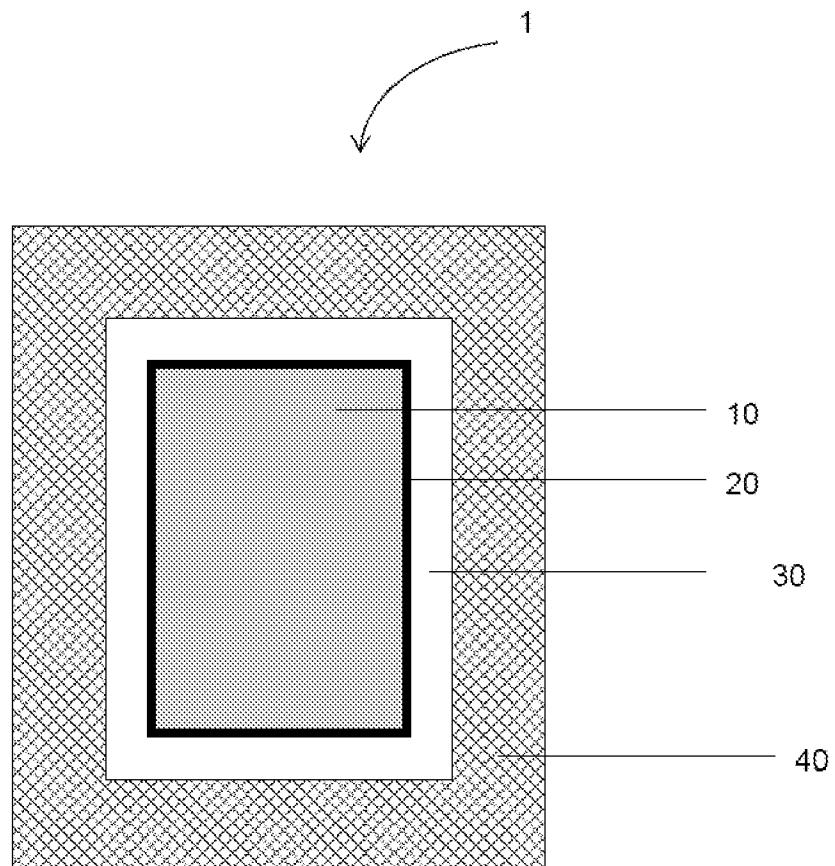

FIG. 1 includes as illustration, a schematic diagram in plan view of a pixel

area with a bank, as described herein.

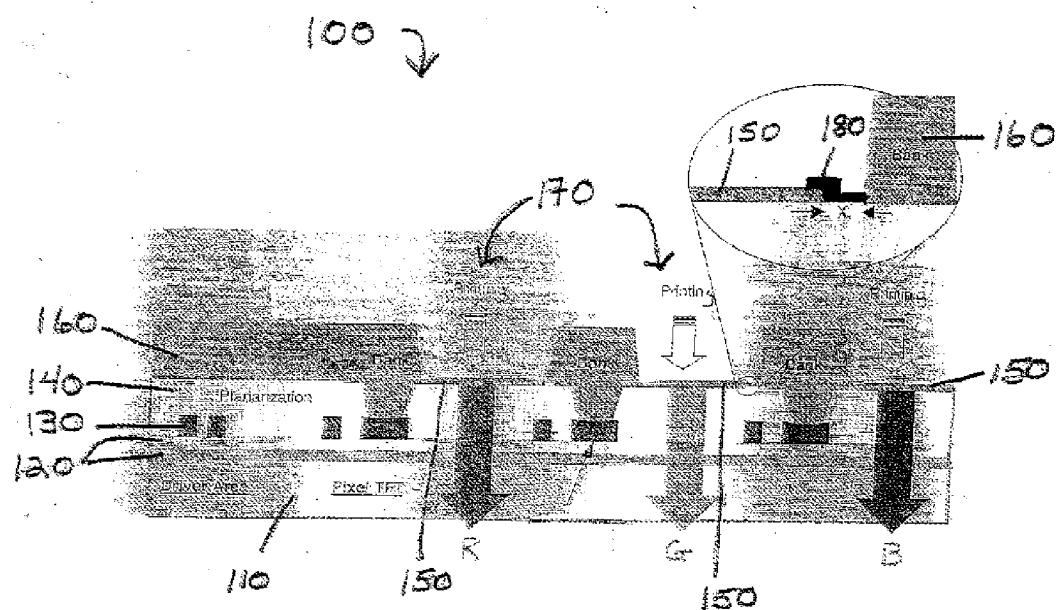

FIG. 2 includes as illustration, a schematic diagram of a cross-sectional

20                  view of a backplane as described herein.

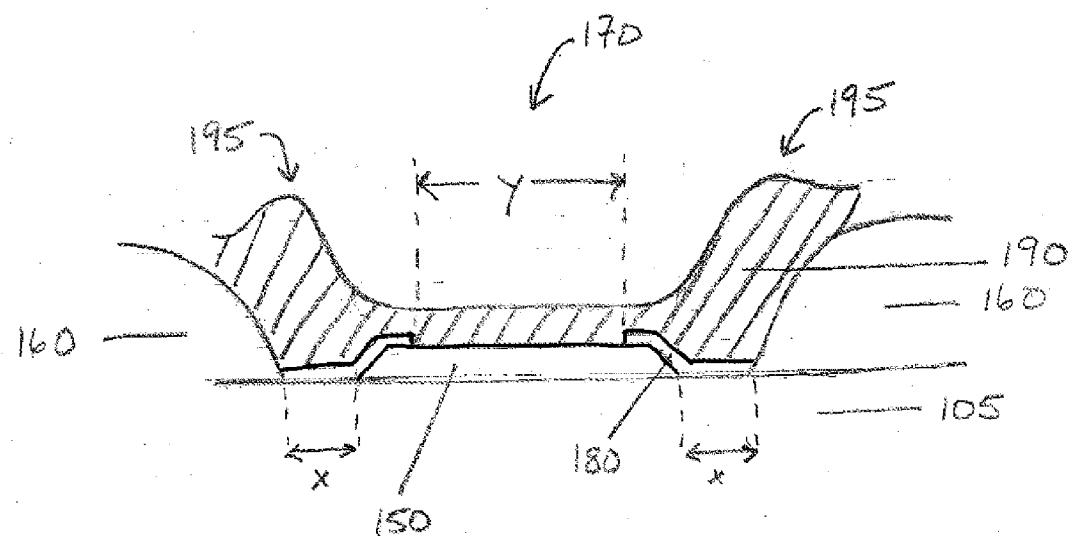

FIG. 3 includes as illustration, a schematic diagram of a cross-sectional

view of one embodiment of a new backplane as described herein containing a

layer of active organic material.

FIG. 4 includes as illustration, a schematic diagram of a cross-sectional

25                  view of another backplane as described herein.

Skilled artisans will appreciate that objects in the figures are illustrated for

simplicity and clarity and have not necessarily been drawn to scale. For

example, the dimensions of some of the objects in the figures may be

exaggerated relative to other objects to help to improve understanding of

30                  embodiments.

#### DETAILED DESCRIPTION

Many aspects and embodiments are described in this specification and

are merely exemplary and not limiting. After reading this specification, skilled

artisans will appreciate that other aspects and embodiments are possible without

35                  departing from the scope of the invention.

Other features and benefits of any one or more of the embodiments will

be apparent from the following detailed description, and from the claims. The

detailed description first addresses Definitions and Clarification of Terms followed by the Backplane, and the Process for Forming an Electronic Device.

1. Definitions and Clarification of Terms

Before addressing details of embodiments described below, some terms 5 are defined or clarified. Defined terms include their variant forms.

As used herein, the term "active" when referring to a layer or material is refers to a layer or material which electronically facilitates the operation of the device. Examples of active materials include, but are not limited to, materials which conduct, inject, transport, or block a charge, where the charge can be 10 either an electron or a hole. Examples also include a layer or material that has electronic or electro-radiative properties. An active layer material may emit radiation or exhibit a change in concentration of electron-hole pairs when receiving radiation.

The term "active matrix" is intended to mean an array of electronic 15 components and corresponding driver circuits within the array.

The term "backplane" is intended to mean a workpiece on which organic layers can be deposited to form an electronic device.

The term "circuit" is intended to mean a collection of electronic components that collectively, when properly connected and supplied with the 20 proper potential(s), performs a function. A circuit may include an active matrix pixel within an array of a display, a column or row decoder, a column or row array strobe, a sense amplifier, a signal or data driver, or the like.

The term "connected," with respect to electronic components, circuits, or portions thereof, is intended to mean that two or more electronic components, 25 circuits, or any combination of at least one electronic component and at least one circuit do not have any intervening electronic component lying between them. Parasitic resistance, parasitic capacitance, or both are not considered electronic components for the purposes of this definition. In one embodiment, electronic components are connected when they are electrically shorted to one another and 30 lie at substantially the same voltage. Note that electronic components can be connected together using fiber optic lines to allow optical signals to be transmitted between such electronic components.

The term "coupled" is intended to mean a connection, linking, or association of two or more electronic components, circuits, systems, or any 35 combination of at least two of: (1) at least one electronic component, (2) at least one circuit, or (3) at least one system in such a way that a signal (e.g., current, voltage, or optical signal) may be transferred from one to another. Non-limiting

examples of "coupled" can include direct connections between electronic components, circuits or electronic components with switch(es) (e.g., transistor(s)) connected between them, or the like.

The term "driver circuit" is intended to mean a circuit configured to control

5 the activation of an electronic component, such as an organic electronic component.

The term "electrically continuous" is intended to mean a layer, member, or structure that forms an electrical conduction path without an electrical open circuit.

10 The term "electrode" is intended to mean a structure configured to transport carriers. For example, an electrode may be an anode, a cathode. Electrodes may include parts of transistors, capacitors, resistors, inductors, diodes, organic electronic components and power supplies.

15 The term "electronic component" is intended to mean a lowest level unit of a circuit that performs an electrical function. An electronic component may include a transistor, a diode, a resistor, a capacitor, an inductor, or the like. An electronic component does not include parasitic resistance (e.g., resistance of a wire) or parasitic capacitance (e.g., capacitive coupling between two conductors connected to different electronic components where a capacitor between the

20 conductors is unintended or incidental).

The term "electronic device" is intended to mean a collection of circuits, electronic components, or combinations thereof that collectively, when properly connected and supplied with the proper potential(s), performs a function. An electronic device may include, or be part of, a system. Examples of electronic

25 devices include displays, sensor arrays, computer systems, avionics, automobiles, cellular phones, and many other consumer and industrial electronic products.

The term "insulative" is used interchangeably with "electrically insulating". These terms and their variants are intended to refer to a material, layer, member,

30 or structure having an electrical property such that it substantially prevents any significant current from flowing through such material, layer, member or structure.

The term "layer" is used interchangeably with the term "film" and refers to a coating covering a desired area. The area can be as large as an entire device or as small as a specific functional area such as the actual visual display, or as

35 small as a single sub-pixel. Films can be formed by any conventional deposition technique, including vapor deposition, liquid deposition and thermal transfer. Typical liquid deposition techniques include, but are not limited to, continuous

deposition techniques such as spin coating, gravure coating, curtain coating, dip coating, slot-die coating, spray coating, and continuous nozzle coating; and discontinuous deposition techniques such as ink jet printing, gravure printing, and screen printing.

5 The term "light-transmissive" is used interchangeably with "transparent" and is intended to mean that at least 50% of incident light of a given wavelength is transmitted. In some embodiments, 70% or more of the light is transmitted.

10 The term "liquid composition" is intended to mean an organic active material that is dissolved in a liquid medium or media to form a solution, dispersed in a liquid medium or media to form a dispersion, or suspended in a liquid medium or media to form a suspension or an emulsion.

15 The term "opening" is intended to mean an area characterized by the absence of a particular structure that surrounds the area, as viewed from the perspective of a plan view.

15 The term "organic electronic device" is intended to mean a device including one or more semiconductor layers or materials. Organic electronic devices include: (1) devices that convert electrical energy into radiation (e.g., an light-emitting diode, light emitting diode display, or diode laser), (2) devices that detect signals through electronics processes (e.g., photodetectors (e.g., 20 photoconductive cells, photoresistors, photoswitches, phototransistors, or phototubes), IR detectors, or biosensors), (3) devices that convert radiation into electrical energy (e.g., a photovoltaic device or solar cell), and (4) devices that include one or more electronic components that include one or more organic semiconductor layers (e.g., a transistor or diode).

25 The term "overlying," when used to refer to layers, members or structures within a device, does not necessarily mean that one layer, member or structure is immediately next to or in contact with another layer, member, or structure.

The term "perimeter" is intended to mean a boundary of a layer, member, or structure that, from a plan view, forms a closed planar shape.

30 The term "photoresist" is intended to mean a photosensitive material that can be formed into a layer. When exposed to activating radiation, at least one physical property and/or chemical property of the photoresist is changed such that the exposed and unexposed areas can be physically differentiated.

35 The term "structure" is intended to mean one or more patterned layers or members, which by itself or in combination with other patterned layer(s) or member(s), forms a unit that serves an intended purpose. Examples of structures include electrodes, well structures, cathode separators, and the like.

The term "TFT substrate" is intended to mean an array of TFTs and/or driving circuitry to make panel function on a base support.

The term "support" or "base support" is intended to mean a base material that can be either rigid or flexible and may be include one or more layers of one or more materials, which can include, but are not limited to, glass, polymer, metal or ceramic materials or combinations thereof.

As used herein, the terms "comprises," "comprising," "includes," "including," "has," "having" or any other variation thereof, are intended to cover a non-exclusive inclusion. For example, a process, method, article, or apparatus 10 that comprises a list of elements is not necessarily limited to only those elements but may include other elements not expressly listed or inherent to such process, method, article, or apparatus. Further, unless expressly stated to the contrary, "or" refers to an inclusive or and not to an exclusive or. For example, a condition A or B is satisfied by any one of the following: A is true (or present) and B is 15 false (or not present), A is false (or not present) and B is true (or present), and both A and B are true (or present).

Also, use of "a" or "an" are employed to describe elements and components described herein. This is done merely for convenience and to give a general sense of the scope of the invention. This description should be read to 20 include one or at least one and the singular also includes the plural unless it is obvious that it is meant otherwise.

Group numbers corresponding to columns within the Periodic Table of the elements use the "New Notation" convention as seen in the *CRC Handbook of Chemistry and Physics*, 81<sup>st</sup> Edition (2000-2001).

25 Unless otherwise defined, all technical and scientific terms used herein have the same meaning as commonly understood by one of ordinary skill in the art to which this invention belongs. Although methods and materials similar or equivalent to those described herein can be used in the practice or testing of embodiments of the present invention, suitable methods and materials are 30 described below. All publications, patent applications, patents, and other references mentioned herein are incorporated by reference in their entirety, unless a particular passage is cited. In case of conflict, the present specification, including definitions, will control. In addition, the materials, methods, and examples are illustrative only and not intended to be limiting.

35 To the extent not described herein, many details regarding specific materials, processing acts, and circuits are conventional and may be found in

textbooks and other sources within the organic light-emitting diode display, photodetector, photovoltaic, and semiconductive member arts.

2. The Backplane

There is provided herein a new backplane for an electronic device. The 5 backplane comprises:

- a TFT substrate having a multiplicity of electrode structures thereon;

- a bank structure defining pixel areas over the electrode structures; wherein the bank structure is removed from and not in contact with the electrode structures by a distance of at least 0.1 microns; and

- 10 a thin layer of insulative inorganic material between the electrode structures and the bank structures.

As used here, the term “thin”, when referring to the insulative inorganic bank structure, is intended to mean a thickness of no greater than 100 nm in the direction perpendicular to the plane of the substrate.

15 TFT substrates are well known in the electronic arts. The base support may be a conventional support as used in organic electronic device arts. The base support can be flexible or rigid, organic or inorganic. In some embodiments, the base support is transparent. In some embodiments, the base support is glass or a flexible organic film. The TFT array may be located over or 20 within the support, as is known. The support can have a thickness in the range of about 12 to 2500 microns.

The term "thin-film transistor" or "TFT" is intended to mean a field-effect transistor in which at least a channel region of the field-effect transistor is not principally a portion of a base material of a substrate. In one embodiment, the channel region of a TFT includes a-Si, polycrystalline silicon, or a combination thereof. The term "field-effect transistor" is intended to mean a transistor, whose current carrying characteristics are affected by a voltage on a gate electrode. A field-effect transistor includes a junction field-effect transistor (JFET) or a metal-insulator-semiconductor field-effect transistor (MISFET), including a metal-oxide-semiconductor field-effect transistor (MOSFETs), a metal-nitride-oxide-semiconductor (MNOS) field-effect transistor, or the like. A field-effect transistor can be n-channel (n-type carriers flowing within the channel region) or p-channel (p-type carriers flowing within the channel region). A field-effect transistor may be an enhancement-mode transistor (channel region having a different conductivity type compared to the transistor's S/D regions) or depletion-mode transistor (the transistor's channel and S/D regions have the same conductivity type).

TFT structures and designs are well known. The TFT structure usually includes gate, source, and drain electrodes, and a sequence of inorganic insulating layers, usually referred to as a buffer layer, gate insulator, and interlayer.

A planarization layer is generally present over the TFT and driver structures in the TFT substrate. The planarization layer smoothes over the rough features and any particulate material of the TFT substrate, and minimizes parasitic capacitance.

A multiplicity of electrode structures are present on the planarization layer. The electrodes may be anodes or cathodes. In some embodiments, the electrodes are pixellated. They may be formed in a patterned array of structures having plan view shapes, such as squares, rectangles, circles, triangles, ovals, and the like. Generally, the electrodes may be formed using conventional processes (e.g. deposition, patterning, or a combination thereof).

In some embodiments, the electrodes are transparent. In some embodiments, the electrodes comprise a transparent conductive material such as indium-tin-oxide (ITO). Other transparent conductive materials include, for example, indium-zinc-oxide (IZO), zinc oxide, tin oxide, zinc-tin-oxide (ZTO), elemental metals, metal alloys, and combinations thereof. In some embodiments, the electrodes are anodes for the electronic device. The electrodes can be formed using conventional techniques, such as selective

deposition using a stencil mask, or blanket deposition and a conventional lithographic technique to remove portions to form the pattern. The thickness of the electrode is generally in the range of approximately 50 to 150 nm.

The bank structure is present in a pattern over the electrodes wherein

5 there is an opening in the pixel areas where organic active material(s) will be deposited. Surrounding each pixel opening is a bank. The bank structure is formed so that the bank is not in contact with the electrode structures. The bank is removed from the electrode by at least 0.1 microns. This is shown schematically in FIG. 1. Pixel 1 has an emissive area 10. The edge of the

10 electrode in the pixel is shown as 20. The bank structure surrounding the pixel opening is shown as 40. Bank 40 is removed from the edge of the electrode by a spacing shown as 30. The distance between the electrode edge 20 and the start of bank 40 is at least 0.1 microns.

The bank structure can be inorganic or organic. The bank structure can

15 be formed using conventional techniques, such as selective deposition using a stencil mask, or blanket deposition and a conventional lithographic technique to remove portions to form the pattern.

Any organic dielectric material can be used to form the bank structure. In some embodiments, the organic material is selected from the group consisting of

20 epoxy resins, acrylic resins, and polyimide resins. Such resins are well known, and many are commercially available.

Patterning to form the organic bank structure can be accomplished using standard photolithographic techniques. In some embodiments, the bank structure is made from a photosensitive material known as a photoresist. In this

25 case, the layer can be imaged and developed to form the bank structure. The photoresist can be positive-working, which means that the photoresist layer becomes more removable in the areas exposed to activating radiation, or negative-working, which means this it is more easily removed in the non-exposed areas. In some embodiments, the material to form the bank structure is not

30 photosensitive. In this case, an overall layer can be formed, a photoresist layer can be applied over the layer, imaged, and developed to form the bank structure. In some embodiments, the photoresist is then stripped off. Techniques for imaging, developing, and stripping are well known in the photoresist art area.

The organic bank structure generally has a thickness of about 0.5 to 3

35 microns. The thickness is measured in the direction perpendicular to the plane of the TFT substrate. In some embodiments, the thickness is about 2 to 3 microns.

In some embodiments, the distance between the organic bank and the electrode is about 0.5 to 5 microns; in some embodiments, 1 to 3 microns.

Any insulative inorganic material can be used for the inorganic bank structure. In some embodiments, the inorganic material is a metal oxide or nitride. In some embodiments, the inorganic material is selected from the group consisting of silicon oxides, silicon nitrides, and combinations thereof.

5

The inorganic bank structure is generally formed by a vapor deposition process. The material can be deposited through a stencil mask to form the pattern. Alternatively, the material can be formed as a layer overall and 10 patterned using a photoresist, as described above.

The inorganic bank structure generally has a thickness of about 1000 to 4000Å. In some embodiments, the thickness is about 2000 to 3000Å. In some embodiments, the distance between the inorganic bank and the electrode is about 0.1 to 3 microns; in some embodiments, 0.5 to 2 microns.

15 Between the bank structures and the electrode structures there is provided a thin layer of insulative inorganic material. In some embodiments, this layer has a thickness of about 5 to 100 nm; in some embodiments, about 10 to 50 nm.

In some embodiments, the thin inorganic layer is present only in the gap 20 between the electrode structure and the bank structure. In some embodiments, the thin inorganic layer overlaps the edge of the electrode structure. The amount of overlap should be kept to a minimum so that the insulative material does not adversely affect electrode function.

Any insulative inorganic material can be used for the thin inorganic layer. 25 In some embodiments, the inorganic material is a metal oxide or nitride. In some embodiments, the inorganic material is selected from the group consisting of silicon oxides, silicon nitrides, and combinations thereof. The thin inorganic layer is generally formed by a vapor deposition process. The material can be deposited through a stencil mask to form the pattern. Alternatively, the material 30 can be formed as a layer overall and patterned using a photoresist, as described above.

In some embodiments, the thin inorganic layer is formed before formation 35 of the bank structure. In this case, the thin inorganic layer may underly the edge of the bank structure, after it is formed. In some embodiments, the thin inorganic layer is formed after the formation of the bank structure.

One exemplary backplane 100 is shown schematically in FIG. 2. The TFT substrate includes: glass substrate 110, inorganic insulative layers 120, and

various conductive lines 130 for gate electrodes or gate lines and source/drain electrodes or data lines. There is an organic planarization layer 140. A pixellated electrode is shown as 150. A bank structure 160 is formed over the electrode layer. The bank defines pixel openings 170, where active organic materials will be deposited to form the device. The inset has an expanded view which shows the gap "x" between the electrode 150 and the bank 160. A thin layer of insulative inorganic material 180 is present in the gap between the electrode and the bank. As shown here, the thin inorganic layer 180 slightly overlies the edge of the electrode 150. Light in the red (R), green (G) and blue (B) spectra and direction of emission are shown.

A schematic diagram of a backplane after deposition of an organic active material is shown in FIG. 3. In the backplane, there is a TFT substrate 105, which can have any type of TFTs. On the TFT substrate is electrode 150 which is surrounded by bank 160. There is a gap, x, between the bank and the electrode. The thin inorganic layer 180 is present in the gap. The organic active material is deposited from a liquid medium into pixel opening 170 to form active layer 190. It can be seen that the nonuniformities in the thickness of layer 190, shown at 195, are outside the effective emissive area, shown as "y". The active layer is substantially uniform in the effective emissive area. The advantage of forming uniform active materials in the emissive area for OLEDs is to provide uniform emission that will contribute to better color stability and better panel lifetime.

Another exemplary backplane with a-Si TFTs is shown schematically in Fig. 4 as 200. The TFT substrate includes: glass substrate 210, gate electrode or gate lines 220, gate insulator layer 230, a-Si channel 140, n<sup>+</sup> a-Si contacts 241, and source/drain metals 242. The insulative layer 230 can be made of any inorganic insulative material, as is known in the art. The conductive layers 220 and 242 can be made of any inorganic conductive materials, as is known in the art. The a-Si channel and doped n<sup>+</sup> a-Si layers are also well known in the art. Over the TFT substrate is organic planarization layer 250. The materials for the planarization layer have been discussed above. A patterned electrode 260 is formed over the planarization layer 250. There is metallization 261 for a via. The materials for the electrode have been discussed above. A bank structure 270 is formed over the electrode layer. The bank defines pixel openings 280, where active organic materials will be deposited to form the device. There is a gap "x" between the bank structure 270 and the electrode 260. A thin layer of insulative

inorganic material 290 is present in the gap between the electrode and the bank. As shown here, the thin inorganic layer 290 slightly overlies the edge of the electrode 260.

5    3. Process for Forming an Electronic Device

The backplane described herein is particularly suited to liquid deposition techniques for the organic active materials. A process for forming an organic electronic device comprises:

forming a backplane comprising:

10    a TFT substrate having a multiplicity of electrode structures thereon;

a bank structure defining pixel areas over the electrode structures,

wherein the bank structure is removed from and not in contact with

the electrode structures by a distance of at least 0.1 microns; and

a thin layer of insulative inorganic material between the electrode

15    structures and the bank structures; and

depositing into at least a portion of the pixel openings a first liquid

composition comprising a first active material in a liquid medium.

An exemplary process for forming an electronic device includes forming one or more organic active layers in the pixel wells of the backplane described

20    herein using liquid deposition techniques. In some embodiments, there is one or

more photoactive layers and one or more charge transport layers. A second

electrode is then formed over the organic layers, usually by a vapor deposition

technique. Each of the charge transport layer(s) and the photoactive layer may

include one or more layers. In another embodiment, a single layer having a

25    graded or continuously changing composition may be used instead of separate

charge transport and photoactive layers.

In some embodiments, there is provided an electronic device comprising:

(i) a backplane comprising:

a TFT substrate having a multiplicity of electrode structures thereon;

30    and

a bank structure defining pixel areas over the electrode structures,

wherein the bank structure is removed from and not in contact with

the electrode structures by a distance of at least 0.1 microns; and

a thin layer of insulative inorganic material between the electrode

35    structures and the bank structures;

(ii) a hole transport layer in at least the pixel openings;

(iii) a photoactive layer in at least the pixel openings;

- (iv) an electron transport layer in at least the pixel openings; and

- (v) a cathode.

In some embodiments, the device further comprises an organic buffer layer between the anode and the hole transport layer. In some embodiments, the 5 device further comprises an electron injection layer between the electron transport layer and the cathode. In some embodiments, one or more of the buffer layer, the hole transport layer, the electron transport layer and the electron injection layer are formed overall.

In an exemplary embodiment, the electrode in the backplane is an anode. 10 In some embodiments, a first organic layer comprising organic buffer material is applied by liquid deposition. In some embodiments, a first organic layer comprising hole transport material is applied by liquid deposition. In some embodiments, first layer comprising organic buffer material and a second layer comprising hole transport material are formed sequentially. After the organic 15 buffer layer and/or hole transport layer are formed, a photoactive layer is formed by liquid deposition. Different photoactive compositions comprising red, green, or blue emitting-materials may be applied to different pixel areas to form a full color display. After the formation of the photoactive layer, an electron transport layer is formed by vapor deposition. After formation of the electron transport layer, an 20 optional electron injection layer and then the cathode are formed by vapor deposition.

The term "organic buffer layer" or "organic buffer material" is intended to mean electrically conductive or semiconductive organic materials and may have one or more functions in an organic electronic device, including but not limited to, 25 planarization of the underlying layer, charge transport and/or charge injection properties, scavenging of impurities such as oxygen or metal ions, and other aspects to facilitate or to improve the performance of the organic electronic device. Organic buffer materials may be polymers, oligomers, or small molecules, and may be in the form of solutions, dispersions, suspensions, 30 emulsions, colloidal mixtures, or other compositions.

The organic buffer layer can be formed with polymeric materials, such as polyaniline (PANI) or polyethylenedioxythiophene (PEDOT), which are often doped with protonic acids. The protonic acids can be, for example, poly(styrenesulfonic acid), poly(2-acrylamido-2-methyl-1-propanesulfonic acid), 35 and the like. The organic buffer layer can comprise charge transfer compounds, and the like, such as copper phthalocyanine and the tetrathiafulvalene-tetracyanoquinodimethane system (TTF-TCNQ). In one embodiment, the

organic buffer layer is made from a dispersion of a conducting polymer and a colloid-forming polymeric acid. Such materials have been described in, for example, published U.S. patent applications 2004-0102577, 2004-0127637, and 2005/205860. The organic buffer layer typically has a thickness in a range of 5 approximately 20-200 nm.

The term "hole transport," when referring to a layer, material, member, or structure is intended to mean such layer, material, member, or structure facilitates migration of positive charge through the thickness of such layer, material, member, or structure with relative efficiency and small loss of charge.

10 Although light-emitting materials may also have some charge transport properties, the term "charge transport layer, material, member, or structure" is not intended to include a layer, material, member, or structure whose primary function is light emission.

Examples of hole transport materials for layer 120 have been summarized 15 for example, in Kirk-Othmer Encyclopedia of Chemical Technology, Fourth Edition, Vol. 18, p. 837-860, 1996, by Y. Wang. Both hole transporting molecules and polymers can be used. Commonly used hole transporting molecules include, but are not limited to: 4,4',4"-tris(N,N-diphenyl-amino)-triphenylamine (TDATA); 4,4',4"-tris(N-3-methylphenyl-N-phenyl-amino)-triphenylamine (MTDATA); 20 N,N'-diphenyl-N,N'-bis(3-methylphenyl)-[1,1'-biphenyl]-4,4'-diamine (TPD); 1,1-bis[(di-4-tolylamino) phenyl]cyclohexane (TAPC); N,N'-bis(4-methylphenyl)-N,N'-bis(4-ethylphenyl)-[1,1'-(3,3'-dimethyl)biphenyl]-4,4'-diamine (ETPD); tetrakis-(3-methylphenyl)-N,N,N',N'-2,5-phenylenediamine (PDA);  $\alpha$ -phenyl-4-25 N,N-diphenylaminostyrene (TPS); p-(diethylamino)benzaldehyde diphenylhydrazone (DEH); triphenylamine (TPA); bis[4-(N,N-diethylamino)-2-methylphenyl](4-methylphenyl)methane (MPMP); 1-phenyl-3-[p-(diethylamino)styryl]-5-[p-(diethylamino)phenyl] pyrazoline (PPR or DEASP); 1,2-trans-bis(9H-carbazol-9-yl)cyclobutane (DCZB); N,N,N',N'-tetrakis(4-methylphenyl)-(1,1'-biphenyl)-4,4'-diamine (TTB); N,N'-bis(naphthalen-1-yl)-N,N'-bis(phenyl)benzidine ( $\alpha$ -NPB); and porphyrinic compounds, such as copper 30 phthalocyanine. Commonly used hole transporting polymers include, but are not limited to, polyvinylcarbazole, (phenylmethyl)polysilane, poly(dioxythiophenes), polyanilines, and polypyrroles. It is also possible to obtain hole transporting polymers by doping hole transporting molecules such as those mentioned above 35 into polymers such as polystyrene and polycarbonate. The hole transport layer typically has a thickness in a range of approximately 40-100 nm.

“Photoactive” refers to a material that emits light when activated by an applied voltage (such as in a light emitting diode or chemical cell) or responds to radiant energy and generates a signal with or without an applied bias voltage (such as in a photodetector). Any organic electroluminescent (“EL”) material can

5 be used in the photoactive layer, and such materials are well known in the art. The materials include, but are not limited to, small molecule organic fluorescent compounds, fluorescent and phosphorescent metal complexes, conjugated polymers, and mixtures thereof. The photoactive material can be present alone, or in admixture with one or more host materials. Examples of fluorescent

10 compounds include, but are not limited to, naphthalene, anthracene, chrysene, pyrene, tetracene, xanthene, perylene, coumarin, rhodamine, quinacridone, rubrene, derivatives thereof, and mixtures thereof. Examples of metal complexes include, but are not limited to, metal chelated oxinoid compounds, such as tris(8-hydroxyquinolato)aluminum (Alq3); cyclometalated iridium and platinum

15 electroluminescent compounds, such as complexes of iridium with phenylpyridine, phenylquinoline, or phenylpyrimidine ligands as disclosed in Petrov et al., U.S. Patent 6,670,645 and Published PCT Applications WO 03/063555 and WO 2004/016710, and organometallic complexes described in, for example, Published PCT Applications WO 03/008424, WO 03/091688, and

20 WO 03/040257, and mixtures thereof. Examples of conjugated polymers include, but are not limited to poly(phenylenevinylenes), polyfluorenes, poly(spirofluorenes), polythiophenes, poly(p-phenylenes), copolymers thereof, and mixtures thereof. The photoactive layer 1912 typically has a thickness in a range of approximately 50-500 nm.

25 “Electron Transport” means when referring to a layer, material, member or structure, such a layer, material, member or structure that promotes or facilitates migration of negative charges through such a layer, material, member or structure into another layer, material, member or structure. Examples of electron transport materials which can be used in the optional electron transport layer

30 140, include metal chelated oxinoid compounds, such as tris(8-hydroxyquinolato)aluminum (AlQ), bis(2-methyl-8-quinolinolato)(p-phenylphenolato) aluminum (BAIq), tetrakis-(8-hydroxyquinolato)hafnium (HfQ) and tetrakis-(8-hydroxyquinolato)zirconium (ZrQ); and azole compounds such as 2-(4-biphenyl)-5-(4-t-butylphenyl)-1,3,4-oxadiazole (PBD), 3-(4-biphenyl)-4-phenyl-5-(4-t-butylphenyl)-1,2,4-triazole (TAZ), and 1,3,5-tri(phenyl-2-benzimidazole)benzene (TPBI); quinoxaline derivatives such as 2,3-bis(4-fluorophenyl)quinoxaline; phenanthrolines such as 4,7-diphenyl-1,10-

35

phenanthroline (DPA) and 2,9-dimethyl-4,7-diphenyl-1,10-phenanthroline (DDPA); and mixtures thereof. The electron-transport layer typically has a thickness in a range of approximately 30-500 nm.

As used herein, the term "electron injection" when referring to a layer, material, member, or structure, is intended to mean such layer, material, member, or structure facilitates injection and migration of negative charges through the thickness of such layer, material, member, or structure with relative efficiency and small loss of charge. The optional electron-transport layer may be inorganic and comprise BaO, LiF, or Li<sub>2</sub>O. The electron injection layer typically has a thickness in a range of approximately 20-100Å.

The cathode can be selected from Group 1 metals (e.g., Li, Cs), the Group 2 (alkaline earth) metals, the rare earth metals including the lanthanides and the actinides. The cathode a thickness in a range of approximately 300-1000 nm.

An encapsulating layer can be formed over the array and the peripheral and remote circuitry to form a substantially complete electrical device.

Note that not all of the activities described above in the general description or the examples are required, that a portion of a specific activity may not be required, and that one or more further activities may be performed in addition to those described. Still further, the order in which activities are listed are not necessarily the order in which they are performed.

In the foregoing specification, the concepts have been described with reference to specific embodiments. However, one of ordinary skill in the art appreciates that various modifications and changes can be made without departing from the scope of the invention as set forth in the claims below. Accordingly, the specification and figures are to be regarded in an illustrative rather than a restrictive sense, and all such modifications are intended to be included within the scope of invention.

Benefits, other advantages, and solutions to problems have been described above with regard to specific embodiments. However, the benefits, advantages, solutions to problems, and any feature(s) that may cause any benefit, advantage, or solution to occur or become more pronounced are not to be construed as a critical, required, or essential feature of any or all the claims.

It is to be appreciated that certain features are, for clarity, described herein in the context of separate embodiments, may also be provided in combination in a single embodiment. Conversely, various features that are, for brevity, described in the context of a single embodiment, may also be provided

separately or in any subcombination. Further, reference to values stated in ranges includes slight variations above and below such values, and the stated ranges can be used to achieve substantially the same results as values within the ranges. Also, the disclosure of these ranges is intended as a continuous range

5 including every value between the minimum and maximum average values including fractional values that can result when some of components of one value are mixed with those of different value. Moreover, when broader and narrower ranges are disclosed, it is within the contemplation of this invention to match a minimum value from one range with a maximum value from another range and

10 vice versa.

CLAIMS

What is claimed is:

1. A backplane for an organic electronic device comprising:

- a TFT substrate having a multiplicity of electrode structures thereon;

- 5 a bank structure defining pixel areas over the electrode structures; wherein the bank structure is removed from and not in contact with the electrode structures by a distance of at least 0.1 microns; and a thin layer of insulative inorganic material between the electrode structures and the bank structures.

- 10 2. The backplane of Claim 1, wherein the bank structure is an organic structure having a thickness of 0.5 to 3 microns.

- 15 3. The backplane of Claim 2, wherein the distance between the organic bank and the electrode is 0.5 to 5 microns.

4. The backplane of Claim 3, wherein the distance is 1 to 3 microns.

5. The backplane of Claim 2, wherein the bank structure comprises an 20 organic material selected from the group consisting of epoxy resins, acrylic resins, and polyimide resins.

6. The backplane of Claim 1, wherein the bank structure is an inorganic structure having a thickness of 1000 to 4000Å.

- 25 7. The backplane of Claim 6, wherein the distance between the inorganic bank and the electrode is 0.1 to 3 microns.

8. The backplane of Claim 7, wherein the distance is 0.5 to 2 microns.

- 30 9. The backplane of Claim 6, wherein the bank structure comprises an inorganic material selected from the group consisting of silicon oxides, silicon nitrides, and combinations thereof.

- 35 10. The backplane of Claim 1, wherein the thin layer of insulative inorganic material has a thickness in the range of 5 to 100 nm.

11. The backplane of Claim 10, wherein the thin layer of insulative inorganic material has a thickness in the range of 10 to 50 nm.

12. The backplane of Claim 1, wherein the thin layer of insulative inorganic material comprises a material selected from the group consisting of silicon oxides, silicon nitrides, and combinations thereof.

13. The backplane of Claim 1, wherein the thin layer of insulative inorganic material partially overlies an edge of the electrode structure.

10

14. A process for forming an organic electronic device, said process comprising:

- forming a backplane comprising:

- a TFT substrate having a multiplicity of electrode structures thereon;

- 15 a bank structure defining pixel areas over the electrode structures, wherein the bank structure is removed from and not in contact with the electrode structures by a distance of at least 0.1 microns; and

- a thin layer of insulative inorganic material between the electrode structures and the bank structures; and

- 20 depositing into at least a portion of the pixel openings a first liquid composition comprising a first active material in a liquid medium.

15. An electronic device comprising:

- (i) a backplane comprising:

- 25 a TFT substrate having a multiplicity of electrode structures thereon;

- and

- a bank structure defining pixel areas over the electrode structures, wherein the bank structure is removed from and not in contact with the electrode structures by a distance of at least 0.1 microns; and

a thin layer of insulative inorganic material between the electrode structures and the bank structures;

(ii) a hole transport layer in at least the pixel openings;

(iii) a photoactive layer in at least the pixel openings;

5 (iv) an electron transport layer in at least the pixel openings; and

(v) a cathode.

16. The device of Claim 15, further comprising an organic buffer layer between the anode and the hole transport layer.

10

17. The device of Claim 15, further comprising an electron injection layer between the electron transport layer and the cathode.

15

FIG. 1

FIG. 2

FIG. 3

FIG. 4

# INTERNATIONAL SEARCH REPORT

International application No

PCT/US2008/079799

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H01L51/56 H01L27/32

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                    | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2005/179373 A1 (KOBAYASHI HIDEKAZU [JP]) 18 August 2005 (2005-08-18)<br>paragraphs [0079], [0087] - [0089],<br>[0094], [0106], [0120], [0145]; figures<br>4a,4b,4c | 1-5,<br>10-17         |

| Y         | -----                                                                                                                                                                 | 6-9                   |

| X         | US 2007/138943 A1 (TANO TOMOKO [JP] ET AL)<br>21 June 2007 (2007-06-21)<br>paragraphs [0017] - [0034], [0083] -<br>[0086], [0102] - [0124]; figures 5,7d-7h           | 1-4,<br>10-17         |

| Y         | -----                                                                                                                                                                 | 2,5-9                 |

| X         | US 2005/008770 A1 (KAWASE TOMOMI [JP])<br>13 January 2005 (2005-01-13)<br>paragraphs [0138] - [0142]; figures 14,15<br>-----                                          | 1,10-12,<br>14-17     |

|           |                                                                                                                                                                       | -/-                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

Date of the actual completion of the international search

5 March 2009

Date of mailing of the international search report

12/03/2009

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Welter, Steve

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2008/079799 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                    | Relevant to claim No.   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| X         | EP 1 601 033 A (SAMSUNG SDI CO LTD [KR])<br>30 November 2005 (2005-11-30)<br><br>paragraphs [0032] - [0034], [0039];<br>figures 7a,7b | 1-5,<br>10-13,<br>15-17 |

| Y         | -----                                                                                                                                 | 6-9                     |

| Y         | US 2007/103062 A1 (JUNG JAE-HOON [KR] ET<br>AL) 10 May 2007 (2007-05-10)<br>paragraph [0065]; figure 2                                | 2,5-9                   |

| A         | US 2007/164670 A1 (PARK JOON-YONG [KR] ET<br>AL) 19 July 2007 (2007-07-19)<br>paragraphs [0010] - [0021], [0032] -<br>[0036]          | 1-17                    |

| A         | US 2006/273314 A1 (LEE DONG-WON [KR])<br>7 December 2006 (2006-12-07)<br>paragraphs [0028] - [0043]; figure 4c                        | 1-17                    |

|           | -----                                                                                                                                 |                         |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2008/079799

| Patent document cited in search report | Publication date | Patent family member(s) |                 |                  | Publication date                       |

|----------------------------------------|------------------|-------------------------|-----------------|------------------|----------------------------------------|

| US 2005179373                          | A1 18-08-2005    | CN 1658714 A            | JP 2005268202 A | KR 20060041919 A | 24-08-2005<br>29-09-2005<br>12-05-2006 |

|                                        |                  | TW 261479 B             |                 |                  | 01-09-2006                             |

| US 2007138943                          | A1 21-06-2007    | CN 1988136 A            | JP 2007172896 A | KR 20070065823 A | 27-06-2007<br>05-07-2007<br>25-06-2007 |

| US 2005008770                          | A1 13-01-2005    | CN 1573368 A            | JP 2004361491 A | KR 20040103768 A | 02-02-2005<br>24-12-2004<br>09-12-2004 |

|                                        |                  | TW 235853 B             |                 |                  | 11-07-2005                             |

| EP 1601033                             | A 30-11-2005     | CN 1708197 A            | JP 2005340208 A | KR 20050112456 A | 14-12-2005<br>08-12-2005<br>30-11-2005 |

|                                        |                  | US 2005263757 A1        |                 |                  | 01-12-2005                             |

| US 2007103062                          | A1 10-05-2007    | CN 1964064 A            | JP 2007134327 A | KR 20070048957 A | 16-05-2007<br>31-05-2007<br>10-05-2007 |

|                                        |                  | US 2007278942 A1        |                 |                  | 06-12-2007                             |

| US 2007164670                          | A1 19-07-2007    | CN 101000948 A          | JP 2007188883 A | KR 20070075554 A | 18-07-2007<br>26-07-2007<br>24-07-2007 |

| US 2006273314                          | A1 07-12-2006    | KR 20060125303 A        |                 |                  | 06-12-2006                             |