(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년08월20일

(11) 등록번호 10-1432150

(24) 등록일자 2014년08월13일

- (51) 국제특허분류(Int. Cl.)

*H01L 21/20* (2006.01)

(21) 출원번호 10-2009-7013965

(22) 출원일자(국제) 2007년12월11일

심사청구일자 2012년12월11일

(85) 번역문제출일자 2009년07월03일

(65) 공개번호 10-2009-0088431

(43) 공개일자 2009년08월19일

(86) 국제출원번호 PCT/US2007/087050

(87) 국제공개번호 WO 2008/073926

국제공개일자 2008년06월19일

(30) 우선권주장

11/609,590 2006년12월12일 미국(US)

(56) 선행기술조사문헌

JP2006294953 A\*

US06221742 B1

KR1020050107510 A

KR1019940004714 A

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

어플라이드 머티어리얼스, 인코포레이티드

미국 95054 캘리포니아 산타 클라라 바우어스 애브뉴 3050

(72) 발명자

예, 지유안

미국 95014 캘리포니아 쿠퍼티노 르링델 드라이브 7375 아파트먼트 38

램, 앤드류

미국 94116 캘리포니아 샌프란시스코 42 스트리트 2287

김, 이환

미국 95035 캘리포니아 밀피타스 해븐리 플래스 825

(74) 대리인

특허법인 남앤드남

전체 청구항 수 : 총 19 항

심사관 : 구본재

(54) 발명의 명칭 실리콘을 함유하는 에피택셜 층들의 형성

**(57) 요약**

본원에는 실리콘을 함유하는 에피택셜 층(epitaxial layer)들을 형성하기 위한 방법들이 개시된다. 특정 실시예들은 반도체 장치들, 예를 들어, 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET) 장치들에서의 에피택셜 층들의 형성 및 처리에 관한 것이다. 특정 실시예들에서, 에피택셜 층의 형성은 프로세스 챕버 내 기판을 실란 및 더 높은 차수의 실란과 같은 2 이상의 실리콘 소스를 포함하는 증착 가스들에 노출시키는 것을 수반한다. 실시예들은 에피택셜 층의 형성 동안에 인도펜트와 같은 도펜트 소스를 흘려 보내는 단계 및 인도펜트 없이 실리콘 소스 가스로 증착을 계속하는 단계를 포함한다.

**대 표 도 - 도1**

## 특허청구의 범위

### 청구항 1

기판 표면 상에 실리콘-함유 재료를 에피택셜하게(epitaxially) 형성하기 위한 방법으로서,

단결정 표면을 포함하는 기판을 프로세스 챔버 안으로 배치하는 단계;

상기 기판상에 제1 도핑되지 않은 층을 형성하기 위해, 실리콘 소스와 탄소 소스를 포함하고 도편트 소스는 포함하지 않는 도핑되지 않은(undoped) 증착 가스에 상기 기판을 노출시키는 단계;

상기 단결정 표면 상에 에피택셜 층을 형성하기 위해 상기 기판을 도핑된 증착 가스에 후속적으로 노출시키는 단계 – 상기 도핑된 증착 가스는 n-타입 또는 p-타입 도편트 소스 및 캐리어 가스로 구성됨 –; 및

상기 기판을 에칭 가스에 노출시키는 단계를 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 2

제1항에 있어서,

상기 도편트 소스는 인(phosphorus) 소스를 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 3

제2항에 있어서,

상기 인 소스는 포스핀을 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 4

제2항에 있어서,

상기 프로세스 챔버를 정화하는 단계를 더 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 5

제2항에 있어서,

단일 프로세스 사이클은 비도핑된 증착 단계, 도핑된 증착 단계, 에칭 가스로의 노출 단계 및 상기 프로세스 챔버를 정화하는 단계를 포함하고, 상기 프로세스 사이클은 적어도 2회 반복되는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 6

제5항에 있어서,

상기 프로세스 챔버를 정화하는 단계는 불활성 가스만을 흘려 보내는(flowing) 단계를 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 7

제2항에 있어서,

상기 에피택셜 층은 트랜지스터 제조 프로세스의 제조 단계 동안 형성되고,

상기 방법은:

기판 상에 게이트 절연체를 형성하는 단계;

상기 게이트 절연체 상에 게이트 전극을 형성하는 단계; 및

상기 기판 상에서, 상기 전극의 대향 측면들 상에 소스 및 드레인 영역들을 형성하고 상기 소스 및 드레인 영역들 사이에 채널 영역을 정하는 단계

를 더 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

#### 청구항 8

제1항에 있어서,

상기 기판을 상기 예칭 가스에 노출시킨 직후에 상기 프로세스 챕버를 정화하는 단계

를 더 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

#### 청구항 9

제8항에 있어서,

상기 예칭 가스는 염소 및 HCl을 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

#### 청구항 10

제1항에 있어서,

상기 도핑되지 않은 증착 가스에 상기 기판을 노출시키는 단계는 상기 기판을 도핑된 증착 가스에 노출시키는 단계 이후에 수행되는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

#### 청구항 11

제1항에 있어서,

상기 실리콘 소스는 모노실란 및 모노실란보다 더 높은 차수의 실란을 함께 흘려보내는 단계를 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

#### 청구항 12

제11항에 있어서,

상기 모노실란보다 더 높은 차수의 실란은 디실란, 네오펜타실란 및 이들의 혼합물로부터 선택되는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

#### 청구항 13

제11항에 있어서,

상기 모노실란보다 더 높은 차수의 실란은 네오펜타실란을 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

#### 청구항 14

제11항에 있어서,

상기 탄소 소스는 메틸실란을 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 15

제11항에 있어서,

상기 모노실란 및 모노실란보다 더 높은 차수의 실란의 비율을 조정하는 단계를 더 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 16

제11항에 있어서,

상기 실란 대 모노실란보다 더 높은 차수의 실란의 비율은 4:1을 초과하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 17

제11항에 있어서,

상기 모노실란보다 더 높은 차수의 실란은 디실란을 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 18

제17항에 있어서,

상기 모노실란 대 디실란의 비율은 5:1인,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 19

제1항에 있어서,

상기 에피택셜 층은 트랜지스터 제조 프로세스의 제조 단계 동안 형성되고,

상기 방법은:

기판 상에 게이트 절연체를 형성하는 단계;

상기 게이트 절연체 상에 게이트 전극을 형성하는 단계; 및

상기 기판 상에서, 상기 전극의 대향 측면들 상에 소스 및 드레인 영역들을 형성하고 상기 소스 및 드레인 영역들 사이에 채널 영역을 정하는 단계

를 더 포함하는,

실리콘-함유 재료를 에피택셜하게 형성하기 위한 방법.

### 청구항 20

삭제

### 청구항 21

삭제

## 명세서

### 기술 분야

[0001] 본원은 2006년 12월 12일자로 출원된 미국 특허 출원 제11/609,590호의 우선권을 주장하고, 이에 의해 상기 출

원의 개시 내용은 전체가 인용에 의해 편입된다.

[0002] 본 발명의 실시예들은 일반적으로 실리콘(silicon; 규소)을 함유하는 에피택셜 층(epitaxial layer)들의 형성 및 처리를 위한 방법 및 장치에 관한 것이다. 특정 실시예들은 반도체 장치들, 예를 들어, 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET) 장치들에서의 에피택셜 층 형성 및 처리를 위한 방법 및 장치에 관한 것이다.

## 배경 기술

[0003] MOS 트랜지스터의 채널을 통해 흐르는 전류의 양은 채널 내 캐리어들의 이동도(mobility)에 직접 비례하고, 높은 이동도의 MOS 트랜지스터들을 사용하는 것은 더 많은 전류가 흐르게 하여 결과적으로 더 빠른 회로 성능을 가능케 한다. MOS 트랜지스터의 채널 내 캐리어들의 이동도는 채널에서의 기계적 응력(mechanical stress)을 생성함으로써 증가될 수 있다. 압축 변형력(compressive strain) 하의 채널, 예를 들어, 실리콘 상에서 성장된 실리콘-게르마늄 채널 층은 pMOS 트랜지스터를 제공하기 위하여 현저히 개선된 훌륭한 이동도를 갖는다. 신장 변형력(tensile strain) 하 채널, 예를 들어, 완화된 실리콘-게르마늄(relaxed silicon-germanium) 상에서 성장된 얇은 실리콘 채널은 nMOS 트랜지스터를 제공하기 위하여 현저히 개선된 전자 이동도를 달성한다.

[0004] 신장 변형력 하 nMOS 트랜지스터 채널은 또한 하나 이상의 탄소-도핑된 실리콘 에피택셜 층들을 형성함으로써 제공될 수 있고, 이것은 pMOS 트랜지스터의 압축 변형된 SiGe 채널에 상보적일 수 있다. 그리하여, 탄소-도핑된 실리콘 및 실리콘-게르마늄 에피택셜 층들은 각각 nMOS 및 pMOS 트랜지스터들의 소스/드레인 상에서 증착될 수 있다. 소스 및 드레인 영역들은 선택적 Si 건식 에칭에 의해 평탄화되거나 리세스될 수 있다. 적절히 제조될 때, 탄소-도핑된 실리콘 에피택시로 커버된 nMOS 소스들 및 드레인들은 채널에서의 신장 변형력을 부과(impose)하고 nMOS 구동 전류를 증가시킨다.

[0005] 탄소-도핑된 실리콘 에피택시를 사용하여 리세스된 소스/드레인을 갖는 nMOS 트랜지스터들의 채널 내 개선된 전자 이동도를 달성하기 위하여, 선택적 증착을 통하여 또는 증착-후 프로세싱(post-deposition processing)에 의해 소스/드레인 상에 탄소-도핑된 실리콘 에피택셜 층을 선택적으로 형성하는 것이 바람직하다. 부가하여, 탄소-도핑된 실리콘 에피택셜 층이 채널에 신장 변형력을 유도하기 위하여 치환적인 C 원자들을 함유하는 것이 바람직하다. 더 높은 채널 신장 변형력은 탄소-도핑된 실리콘 소스 및 드레인에서의 증가된 치환적인 C 함량을 이용하여 달성될 수 있다.

[0006] 일반적으로, 서브-100 nm CMOS(상보적 금속-산화물 반도체) 장치들은 30 nm 미만의 접합 깊이(junction depth)를 요구한다. 선택적 에피택셜 증착은 종종 접합부들 내로 실리콘-함유 재료들(예를 들어, Si, SiGe 및 SiC)의 에피택셜 층들("에피층들")을 형성하기 위해 활용된다. 선택적 에피택셜 증착은 절연 영역들 상에 어떠한 성장도 갖지 않는 실리콘 모트(silicon moat)들 상에 에피층들의 성장을 허용한다. 바이폴라 장치들의 용기된 소스/드레인(elevated source/drain)들, 소스/드레인 연장부들, 콘택 플러그(contact plug)들 또는 베이스 층 증착과 같은 선택적 에피택시가 반도체 장치들 내에 사용될 수 있다.

[0007] 전형적인 선택적 에피택시 프로세스는 증착 반응 및 에칭 반응을 수반한다. 증착 프로세스 동안, 에피택셜 층은 단결정 표면 상에 형성되는 반면, 다결정 층은 적어도 이미 존재하는 다결정 층 및/또는 비정질 층과 같은 제 2 층 상에 증착된다. 증착 및 에칭 반응들은 에피택셜 층에 비해, 그리고 다결정 층에 비해 상대적으로 상이한 반응 속도(reaction rate)들로 동시에 일어난다. 그러나 증착된 다결정 층은 일반적으로 에피택셜 층보다 더 빠른 속도로 에칭된다. 따라서, 에천트 가스(etchant gas)의 농도를 변화시킴으로써, 순 선택적 프로세스(net selective process)는 에피택시 재료의 증착을 야기하고, 다결정 재료의 제한된 증착을 야기하거나 다결정 재료의 어떠한 증착도 야기하지 않는다. 예를 들어, 선택적 에피택시 프로세스는 단결정 실리콘 표면 상에 실리콘-함유 재료의 에피층의 형성을 야기할 수 있는 반면, 어떠한 증착도 스페이서 상에 남기지 않는다.

[0008] 실리콘-함유 재료들의 선택적 에피택시 증착은 예를 들어, 실리콘-함유 MOSFET(금속 산화물 반도체 전계 효과 트랜지스터) 장치들의 형성 동안에, 용기된 소스/드레인 및 소스/드레인 연장부 피쳐(feature)들의 형성 동안의 유용한 기술이 되어 왔다. 소스/드레인 연장부 피쳐들은 리세스된 소스/드레인 피쳐를 만들기 위해 실리콘 표면을 에칭함으로써 그리고 후속적으로 에칭된 표면을 실리콘 게르마늄(SiGe) 재료와 같은 선택적으로 성장된 에피층들로 충전함으로써 제조된다. 선택적 에피택시는 인-시튜 도핑(in-situ doping)으로 거의 완전한 도편트 활성화를 허용하고, 그 결과 사후 어닐링 프로세스가 생략된다. 따라서, 접합 깊이는 실리콘 에칭 및 선택적 에피택시에 의해 정확히 정해질 수 있다. 반면, 극히 얇은 소스/드레인 접합(ultra shallow source/drain junction)은 불가피하게 증가된 직렬 저항을 야기한다. 또한, 실리사이드 형성 동안 접합 소모(junction consumption)는 직렬 저항을 훨씬 더 증가시킨다. 접합 소모를 보상하기 위하여, 용기된 소스/드레인이 접합부

상에 에피택셜로 그리고 선택적으로 성장된다. 전형적으로, 용기된 소스/드레인 층은 도핑되지 않은 실리콘이다.

[0009] 그러나 현재의 선택적 에피택시 프로세스들은 소정의 결점들을 갖는다. 현재의 에피택시 프로세스들 동안 선택성을 유지하기 위하여, 선구체(precursor)들의 화학적 농도뿐만 아니라 반응 온도들이 증착 프로세스 내내 조절되고 조정되어야 한다. 충분치 않은 실리콘 선구체가 투여되면, 에칭 반응이 우세할 수 있고 전체 프로세스가 느려진다. 또한, 기판 괴쳐들의 해로운 오버-에칭이 일어날 수도 있다. 불충분한 에천트 선구체가 투여되면, 증착 반응이 우세할 수 있고, 기판 표면에 걸쳐 단결정 및 다결정 재료들을 형성하기 위해 선택성(selectivity)을 감소시킨다. 또한, 현재의 선택적 에피택시 프로세스들은 통상 약 800°C, 1,000°C 또는 그 이상과 같은 높은 반응 온도를 요구한다. 이러한 높은 온도들은 기판 표면에 대하여 있을 수 있는 제어되지 않은 질화 반응들 및 열 버짓(thermal budget) 고려들로 인하여 제조 프로세스 동안 바람직스럽지 않다. 게다가, 더 높은 프로세스 온도들에서 전형적인 선택적 Si:C 에피택시 프로세스들을 통해 통합된 대부분의 C 원자들은 Si 격자의 비-치환적(즉, 격자 간) 위치들을 점유한다. 성장 온도를 낮춤으로써, 더 높은 비율의 치환적 탄소(substitutional carbon) 레벨이 달성될 수 있으나(예를 들어, 550°C의 성장 온도에서 거의 100%), 이러한 더 낮은 온도들에서 느린 성장 속도는 장치 애플리케이션들에 바람직하지 못하고, 이러한 선택적 프로세싱은 더 낮은 온도들에서 가능하지 않을 수 있다.

[0010] 따라서, 실리콘-함유 화합물들을 선택적 도편트들로 에피택셜하게 증착하기 위한 프로세스를 가질 필요가 있다. 더구나, 상기 프로세스는 가변된 원소 농도들을 갖는 실리콘-함유 화합물들을 형성하기 위하여 다목적이어야 하는 반면, 빠른 증착 속도를 가져야 하고, 약 800°C 또는 그 이하, 바람직하게는 약 700°C 또는 그 이하와 같은 프로세스 온도를 유지하여야 한다. 이러한 방법들은 트랜지스터 장치들의 제조에 유용할 것이다.

### 발명의 상세한 설명

[0011] 본 발명의 일 실시예는 실리콘을 함유하는 에피택셜 층들을 형성 및 프로세싱하는 방법들에 관한 것이다. 다른 실시예들은 실리콘 및 탄소를 함유하는 에피택셜 층들을 포함하는 트랜지스터 장치들을 제조하는 제조 방법에 관한 것이다.

[0012] 본 발명의 일 실시예에 따라, 기판 표면 상에 실리콘-함유 재료를 에피택셜로 형성하기 위한 방법은 단결정 표면을 포함하는 기판을 프로세스 챔버 안으로 배치하는 단계; 단결정 표면 상에 에피택셜 층을 형성하기 위하여 증착 가스에 기판을 노출시키는 단계를 포함하고, 상기 증착 가스는 모노실란 및 더 높은 차수의 실란을 포함하는 실리콘 소스를 포함한다. 특정 실시예들에서, 에피택셜 막은 기판의 리세스된 부분 상에 형성된다.

[0013] 하나 이상의 실시예들에서, 상기 방법은 모노실란 및 더 높은 차수의 실란의 비율을 조정하는 단계를 더 포함한다. 특정 실시예에서, 실란 대 더 높은 차수의 실란의 비율은 4:1을 초과한다. 특정 실시예에서, 더 높은 차수의 실란은 디실란, 네오펜타실란 및 이들의 혼합물들로부터 선택된다. 하나 이상의 실시예에서, 상기 방법은 아르곤과 같은 불활성 캐리어 가스와 함께 흐를 수 있는 탄소-함유 소스, 예를 들어, 메틸실란을 흘려보내는 (flowing) 단계를 포함한다.

[0014] 특정 실시예에서, 더 높은 차수의 실란은 디실란을 포함하고, 모노실란 대 디실란의 비율은 약 5:1이다. 하나 이상의 실시예들에서, 상기 방법은 증착 가스에 기판을 노출시킨 후에 프로세스 챔버를 즉시 정화하는 단계를 포함한다. 특정 실시예들에서, 상기 방법은 에칭 가스에 기판을 노출시키는 단계를 더 포함한다. 특정 실시예에서, 상기 방법은 기판을 염소 및 HCl을 포함할 수 있는 에칭 가스에 노출시킨 직후에 프로세스 챔버를 즉시 정화하는 단계를 더 포함한다. 일 실시예에 따라, 단일 프로세스 사이클은 순차적으로 증착 단계, 에칭 가스에 노출하는 단계 및 프로세스 챔버를 정화하는 단계를 포함하고, 상기 프로세스 사이클은 적어도 2회 반복된다. 다른 실시예들에서, 상기 방법은 기판을 증착 가스에 노출하고 미리 결정된 두께를 갖는 실리콘-함유 층을 형성하기 위해 프로세스 챔버를 정화하는 프로세스를 반복하는 단계를 포함할 수 있다. 특정 실시예들에서, 네오펜타실란 소스는 프로세스 챔버로부터 약 5 피트 내에 위치할 수 있다. 일 실시예에서, 증착 가스는 봉소, 비소, 인, 알루미늄, 갈륨, 게르마늄, 탄소 및 이들의 조합으로 이루어진 그룹으로부터 선택된 원소 소스(element source)를 포함하는 도편트 화합물을 더 포함한다.

[0015] 하나 이상의 실시예들에서, 에피택셜 막은 트랜지스터 제조 프로세스의 제조 단계 동안 형성되고, 상기 방법은 기판 상에 게이트 절연물을 형성하는 단계; 게이트 절연물 상에 게이트 전극을 형성하는 단계; 및 전극의 대향 측면들 상에서 기판 상에 소스/드레인 영역들을 형성하고 소스/드레인 영역들 사이에 채널 영역을 한정(define)하는 단계를 더 포함한다.

[0016] 전술한 내용은 본 발명의 특정 특징들 및 기술적 이점들의 개요를 다소 광범위하게 기술하였다. 개시된 특정 실시예들이 본 발명의 범위 내의 다른 구조들 또는 프로세스들을 변형 또는 설계하기 위한 기반으로서 쉽게 활용될 수 있음이 당업자에게 이해되어야 한다. 또한 이러한 균등한 구성들이 첨부된 청구범위에 기술된 본 발명의 사상 및 범위로부터 벗어나지 않음이 당업자들에 의해 인식되어야 한다.

### 실시예

[0026] 본 발명의 실시예들은 일반적으로 실리콘-함유 에피택셜 층을 형성 및 처리하기 위한 방법들 및 장치를 제공한다. 특정 실시예들은 트랜지스터의 제조 동안 에피택셜 층을 형성 및 처리하기 위한 방법들 및 장치에 관한 것이다.

[0027] 본 명세서 전체에서 사용되는 바와 같이, 에피택셜 증착은 기판 상의 단일 결정 층의 증착을 언급하고, 그 결과 증착된 층의 결정 구조는 기판의 결정 구조와 매칭된다. 그리하여, 에피택셜 층 또는 막은 기판의 결정 구조와 매칭되는 결정 구조를 갖는 단일 결정 층 또는 막이다. 에피택셜 층들은 벌크 기판들 및 폴리 실리콘 층들과 구별된다.

[0028] 본 출원에서, 용어들 "실리콘-함유" 재료들, 화합물들, 막들 또는 층들은 적어도 실리콘을 함유하는 조성물을 포함하는 것으로 해석되어야 하고, 게르마늄, 탄소, 붕소, 비소, 인, 갈륨 및/또는 알루미늄을 포함할 수 있다. 금속들, 할로겐들 또는 수소와 같은 다른 원소들은 실리콘-함유 재료, 화합물, 막 또는 층 내에 보통 ppm(part per million; 백만분의 1) 농도로 포함될 수 있다. 실리콘-함유 재료들의 화합물들 또는 합금들은, 실리콘에 대해 Si, 실리콘 게르마늄에 대해 SiGe로, 실리콘 카본에 대해 Si:C로, 그리고 실리콘 게르마늄 카본에 대해 SiGeC와 같이 약자로 표현될 수 있다. 약자들은 화학양론적 관계들로 화학식들을 표현하지 않고, 실리콘-함유 재료들의 임의의 특정 환원/산화 상태를 나타내지 않는다.

[0029] 본 발명의 하나 이상의 실시예들은 일반적으로 전자 장치들의 제조 동안 기판의 단결정 표면들 상에 실리콘-함유 재료들을 선택적으로 그리고 에피택셜로 증착하는 프로세스들을 제공한다. 단결정 표면(예를 들어, 실리콘 또는 실리콘 게르마늄) 및 적어도 비정질 표면 및/또는 다결정 표면(예를 들어, 산화물 또는 질화물)과 같은 2차 표면을 포함하는 기판은 단결정 표면 상에 에피택셜 층을 형성하기 위해 에피택셜 프로세스에 노출되는 한편, 2차 표면들 상에 제한된 다결정 층을 형성하거나 어떠한 다결정 층도 형성하지 않는다. 또한 교대하는 가스 공급 프로세스로도 지칭되는 에피택셜 프로세스는 목적하는 두께의 에피택셜 층이 성장될 때까지 증착 프로세스 및 에칭 프로세스의 사이클을 반복하는 단계를 포함한다. 예시적인 교대하는 증착 및 에칭 프로세스들은 본원과 양수인이 동일하고 함께 계류 중인 미국 특허 출원 공개 제2006/0115934호로서 공개된 미국 특허 출원 제11/001,774호, "Selective Epitaxy Process With Alternating Gas Supply(교대하는 가스 공급을 가진 선택적 에피택시 프로세스)"에 개시되고, 그 전체 내용이 인용에 의해 본 명세서에 편입된다.

[0030] 하나 이상의 실시예들에서, 증착 프로세스는 적어도 실리콘 소스 및 캐리어 가스를 포함하는 증착 가스에 기판 표면을 노출시키는 단계를 포함한다. 증착 가스는 또한 도핀트 소스뿐만 아니라, 게르마늄 소스 및/또는 탄소 소스를 포함할 수 있다. 증착 프로세스 동안, 에피택셜 층은 기판의 단결정 표면 상에 형성되는 반면, 다결정/비정질 층은 절연, 비정질 및/또는 다결정 표면들과 같은 2차 표면들 상에 형성되고, 상기 절연, 비정질 및/또는 다결정 표면들은 총체적으로 "2차 표면들"로 지칭될 것이다. 후속적으로, 기판은 에칭 가스에 노출된다. 에칭 가스는 캐리어 가스 및 염소 가스 또는 염화 수소와 같은 에천트를 포함한다. 에칭 가스는 증착 프로세스 동안 증착된 실리콘-함유 재료들을 제거한다. 에칭 프로세스 동안, 다결정/비정질 층은 에피택셜 층보다 더 빠른 속도(rate)로 제거된다. 따라서 증착 및 에칭 프로세스들의 최종 결과(net result)는 단결정 표면들 상에 에피택셜 성장된 실리콘-함유 재료를 형성하는 반면, 2차 표면들 상에 다결정/비정질 실리콘-함유 재료가 있다면 2차 표면들 상의 다결정/비정질 실리콘-함유 재료의 성장을 최소화한다. 증착 및 에칭 프로세스들의 사이클은 목적하는 두께의 실리콘-함유 재료들을 얻기 위하여 필요에 따라 반복될 수 있다. 본 발명의 실시예들에 의해 증착될 수 있는 실리콘-함유 재료들은 도핀트들을 포함하는, 실리콘, 실리콘 게르마늄, 실리콘 카본, 실리콘 게르마늄 카본 및 이들의 변형물들을 포함한다.

[0031] 상기 프로세스의 일 예시에서, 에천트와 같은 염소 가스의 사용은 전체 프로세스 온도를 약 800°C 아래로 낮춘다. 일반적으로, 증착 프로세스들은 에칭 반응들보다 더 낮은 온도들에서 실시될 수 있는데, 그 이유는 에천트들이 종종 활성화되기 위해 높은 온도를 필요로 하기 때문이다. 예를 들어, 실란은 약 500°C 이하에서 실리콘을 증착하기 위해 열적으로 분해될 수 있는 반면, 염화 수소는 유효한 에천트로서 작용하기 위해 약 700°C 이상의 활성화 온도를 요구한다. 따라서 염화 수소가 프로세스 동안 사용된다면, 전체 프로세스 온도는 에천트를

활성화하기 위해 요구된 더 높은 온도에 의해 영향을 받는다. 염소는 요구된 전체 프로세스 온도를 감소시킴으로써 전체 프로세스에 기여한다. 염소는 약 500°C 만큼 낮은 온도에서 활성화될 수 있다. 따라서, 에천트로서 염소를 상기 프로세스 내로 편입시킴으로써, 전체 프로세스 온도는 에천트로서 염화 수소를 사용하는 프로세스들에 비해, 예컨대, 약 200°C 내지 300°C 만큼 현저히 감소될 수 있다. 또한, 염소는 염화 수소보다 더 빨리 실리콘-함유 재료들을 에칭한다. 따라서 염소 에천트들은 프로세스의 전체 속도를 증가시킨다.

[0032] 질소는 전형적으로, 캐리어 가스로서 아르곤 및 헬륨을 사용하는 것과 연관된 비용 고려들로 인하여 선호되는 캐리어 가스이다. 질소가 일반적으로 아르곤보다 훨씬 더 저렴하다는 사실에도 불구하고, 본 발명의 하나 이상의 실시예들에 따르면 아르곤은 선호되는 캐리어 가스이고, 특히 메틸실란이 실리콘 소스 가스인 실시예들에서 그러하다. 캐리어 가스로서 질소를 사용하는 것으로부터 일어날 수 있는 한 가지 결점은 중착 프로세스들 동안 기판 상의 재료들의 질화이다. 그러나, 높은 온도, 예컨대 800°C가 넘는 높은 온도가 이러한 방식에서 질소를 활성화하기 위해 요구된다. 따라서, 하나 이상의 실시예들에 따라, 질소는 질소 활성화 임계치 아래의 온도에서 실시되는 프로세스들에서 불활성 캐리어 가스로서 사용될 수 있다. 불활성 캐리어 가스의 사용은 중착 프로세스 동안 몇몇 속성을 갖는다. 한 가지를 들자면, 불활성 캐리어 가스는 실리콘-함유 재료의 중착 속도를 증가시킬 수 있다. 수소가 중착 프로세스 동안 캐리어 가스로서 사용될 수 있는 한편, 수소는 말단이 수소 처리된 표면(hydrogen-terminated surface)들을 형성하기 위하여 표면에 흡수되거나 반응하는 경향을 갖는다. 말단이 수소 처리된 표면은 베어 실리콘 표면(bare silicon surface)보다 훨씬 더 느리게 에피택셜 성장에 반응한다. 따라서 불활성 캐리어 가스의 사용은 중착 반응에 악영향을 주지 않음으로써 중착 속도를 증가시킨다.

[0033] 본 발명의 제 1 실시예에 따라, 중착 및 정화의 교대 단계들을 가진 블랭킷(blanket) 또는 비선택적 에피택시는 연속적 중착에 비해 더 높은 차수의 실란을 사용하여 성장된 에피택셜 막들의 개선된 결정도를 야기한다. 본 명세서에서 사용되는 바와 같이, "더 높은 차수의 실란"은 디실란 또는 더 높은 차수의 실란 선구체를 지칭한다. 몇몇 특정 실시예들에서, "더 높은 차수의 실란"은 디실란, 네오펜타실란(NPS) 또는 이들의 혼합물을 지칭한다. 예시적인 프로세스는 기판을 프로세스 챔버 안으로 로딩하는 단계 및 프로세스 챔버 내 조건들을 목적하는 온도 및 압력으로 조정하는 단계를 포함한다. 그 다음, 중착 프로세스는 기판의 단결정 표면 상에 에피택셜 층을 형성하도록 개시된다. 그 다음 중착 프로세스가 종결된다. 그 다음 에피택셜 층의 두께가 결정된다. 만약 에피택셜 층의 미리 결정된 두께가 달성된다면, 에피택셜 프로세스가 종결된다. 그러나 만약 미리 결정된 두께가 달성되지 않는다면, 중착 및 정화의 단계들은 미리 결정된 두께가 달성될 때까지 한 사이클로서 반복된다. 부가하여, 이러한 예시적인 프로세스의 세부사항들이 이하에서 기술된다.

[0034] 기판들은 패터닝되지 않거나 패터닝될 수 있다. 패터닝된 기판들은 기판 표면 안으로 또는 기판 표면 상에 형성된 전자 피쳐들을 포함하는 기판들이다. 패터닝된 기판은 보통 단결정 표면들 및 단결정이 아닌, 절연, 다결정 또는 비정질 표면들과 같은 적어도 하나의 2차 표면을 포함한다. 단결정 표면들은 보통 실리콘, 실리콘 게르마늄 또는 실리콘 카본과 같은 재료로 만들어진 중착된 단일 결정 층 또는 베어 결정질 기판을 포함한다. 다결정 또는 비정질 표면들은 산화물 또는 질화물, 특히 실리콘 옥사이드 또는 실리콘 니트라이드와 같은 절연 재료들뿐만 아니라 비정질 실리콘 표면들을 포함할 수 있다.

[0035] 기판을 프로세스 챔버 안으로 로딩한 이후에, 프로세스 챔버 내 조건들은 미리 결정된 온도 및 압력으로 조정된다. 온도는 특정 실시 프로세스로 맞추어진다. 일반적으로, 프로세스 챔버는 에피택셜 프로세스 내내 일관된 온도에서 유지된다. 그러나 소정 단계들은 가변 온도들에서 수행될 수 있다. 프로세스 챔버는 약 250°C 내지 약 1,000°C 범위의 온도에서, 예를 들어, 약 500°C 내지 약 800°C 범위의 온도에서, 더욱 상세하게 약 550°C 내지 약 750°C 범위의 온도에서 유지된다. 에피택셜 프로세스를 실시할 적절한 온도는 실리콘-함유물을 중착하기 위해 사용된 특정 선구체들에 따라 달라질 수 있다. 일 예시에서, 염소(Cl<sub>2</sub>) 가스는 보다 통상적인 에천트들을 사용하는 프로세스들보다 더 낮은 온도들에서 실리콘-함유 재료들에 대한 에천트로서 잘 작용함이 발견되었다. 따라서, 일 예시에서, 프로세스 챔버를 예열하기 위한 예시적인 온도는 약 750°C 또는 그 이하이고, 예를 들어, 약 650°C 또는 그 이하, 그리고 더욱 상세하게 약 550°C 또는 그 이하이다. 특정 일 실시예에서, 에피택셜 성장 동안의 온도는 약 560°C에서 유지된다.

[0036] 프로세스 챔버는 통상 약 0.1 Torr 내지 약 600 Torr의 압력에서, 예를 들어, 약 1 Torr 내지 약 50 Torr의 압력에서 유지된다. 상기 압력은 프로세스 단계들 동안 그리고 프로세스 단계들 사이에서 변동할 수 있으나, 일 반적으로 일정하게 유지된다. 특정 실시예에서, 압력은 중착 및 정화 동안에 약 10 Torr에서 유지된다.

[0037] 중착 프로세스 동안, 기판은 에피택셜 층을 형성하기 위하여 중착 가스에 노출된다. 기판은 약 0.5초 내지 약 30초의 시간 주기 동안, 예를 들어, 약 1초 내지 약 20초의 시간 주기 동안, 더욱 상세하게 약 5초 내지 약 10

초의 시간 주기 동안 증착 가스에 노출된다. 특정 실시예에서, 증착 단계는 약 10 내지 11초 동안 지속된다. 증착 프로세스의 특정 노출 시간은 프로세스에 사용된 온도 및 특정 선구체들뿐만 아니라 후속적인 에칭 프로세스 동안의 노출 시간과 관련하여 결정된다. 일반적으로, 기판은 에피택셜 층의 최대화된 두께를 형성하기에 충분히 오래 증착 가스에 노출된다.

[0038] 증착 가스는 적어도 실리콘 소스 및 캐리어 가스를 포함하고, 탄소 소스 및/또는 게르마늄 소스와 같은 적어도 하나의 2차 원소 소스를 포함할 수 있다. 또한 증착 가스는 봉소, 비소, 인, 갈륨 및/또는 알루미늄과 같은 도편트의 소스를 제공하도록 도편트 화합물을 더 포함할 수 있다. 대안적인 실시예에서, 증착 가스는 염화 수소 또는 염소와 같은 적어도 하나의 에婵트를 포함할 수 있다.

[0039] 실리콘 소스는 통상 약 5 sccm 내지 약 500 sccm 범위의 속도로, 바람직하게 약 10 sccm 내지 약 300 sccm 범위의 속도로, 더욱 바람직하게 약 50 sccm 내지 약 200 sccm 범위의 속도로, 예를 들어, 약 100 sccm의 속도로 프로세스 챔버 안으로 제공된다. 특정 실시예에서, 실란은 약 60 sccm으로 흐른다. 실리콘-함유 화합물들을 증착하기 위해 증착 가스에서 유용한 실리콘 소스들은 실란들, 할로겐화 실란들 및 유기실란들을 포함한다. 실란들은 실란( $\text{SiH}_4$ ) 및 디실란( $\text{Si}_2\text{H}_6$ ), 트리실란( $\text{Si}_3\text{H}_8$ ) 및 테트라실란( $\text{Si}_4\text{H}_{10}$ )뿐만 아니라 다른 것들과 같은 실험식  $\text{Si}_x\text{H}_{(2x+2)}$ 을 갖는 더 높은 차수의 실란(higer silane)을 포함한다. 할로겐화 실란들은 헥사클로로디실란( $\text{Si}_2\text{Cl}_6$ ), 테트라클로로실란( $\text{SiC}_4$ ), 디클로로실란( $\text{Cl}_2\text{SiH}_2$ ) 및 트리클로로실란( $\text{Cl}_3\text{SiH}$ )과 같은 실험식  $\text{X}'_y\text{Si}_x\text{H}_{(2x+2-y)}$ 을 가진 화합물들을 포함하고, 여기서,  $\text{X}' = \text{F}, \text{Cl}, \text{Br}$  또는  $\text{I}$ 이다. 유기실란들은 메틸실란( $(\text{CH}_3)\text{SiH}_3$ ), 디메틸실란( $(\text{CH}_3)_2\text{SiH}_2$ ), 에틸실란( $(\text{CH}_3\text{CH}_2)\text{SiH}_3$ ), 메틸디실란( $(\text{CH}_3)\text{Si}_2\text{H}_5$ ), 디메틸디실란( $(\text{CH}_3)_2\text{Si}_2\text{H}_4$ ) 및 헥사메틸디실란( $(\text{CH}_3)_6\text{Si}_2$ )과 같은 실험식  $\text{R}_y\text{Si}_x\text{H}_{(2x+2-y)}$ 을 가진 화합물들을 포함하고, 여기서,  $\text{R} = \text{메틸}, \text{에틸}, \text{프로필}$  또는  $\text{부틸}$ 이다. 유기실란 화합물들은 유리한 실리콘 소스이자, 증착된 실리콘-함유 화합물에 탄소를 포함시키는 실시예들에서 유리한 탄소 소스임이 발견되었다. 하나 이상의 실시예들에 따라, 아르곤-함유 캐리어 가스 내 메틸실란은 바람직한 실리콘-함유 소스 및 캐리어 가스 결합물이다.

[0040] 실리콘 소스는 보통 캐리어 가스와 함께 프로세스 챔버 안으로 제공된다. 캐리어 가스는 약 1 slm(standard liters per minute) 내지 약 100 slm, 예를 들어, 약 5 slm 내지 약 75 slm, 및 더욱 상세하게 약 10 slm 내지 약 50 slm, 예를 들어, 약 10 slm의 유량(flow rate)을 갖는다. 캐리어 가스들은 질소( $\text{N}_2$ ), 수소( $\text{H}_2$ ), 아르곤, 헬륨 및 이들의 조합을 포함할 수 있다. 불활성 캐리어 가스가 선호되고, 질소, 아르곤, 헬륨 및 이들의 조합을 포함한다. 캐리어 가스는 에피택셜 프로세스 동안에 사용된 선구체(들) 및/또는 프로세스 온도에 기초하여 선택될 수 있다. 보통 캐리어 가스는 증착 및 에칭의 각 단계들 내내 동일하다. 그러나 소정의 실시예들은 특정 단계들에서 상이한 캐리어 가스들을 사용할 수도 있다.

[0041] 전형적으로, 질소가 저온(예를 들어, <800°C) 프로세스들을 특징으로 하는 실시예들에서 캐리어 가스로서 활용된다. 부분적으로 에칭 프로세스의 염소 가스의 사용으로 인하여 저온 프로세스들이 액세스 가능하다. 질소는 저온 증착 프로세스를 동안에 불활성으로 남아 있다. 따라서, 질소는 저온 프로세스들 동안 증착된 실리콘-함유 재료 안으로 편입되지 않는다. 또한, 질소 캐리어 가스는 수소 캐리어 가스가 그러한 것처럼, 말단이 수소 처리된 표면들을 형성하지 않는다. 기판 표면 상에서 수소 캐리어 가스의 흡수에 의해 형성된, 말단이 수소 처리된 표면들은 실리콘-함유 층들의 성장 속도를 억제한다. 마지막으로, 저온 프로세스들은 캐리어 가스로서 질소의 경제적 이점을 가질 수 있는데, 그 이유는 질소가 수소, 아르곤 또는 헬륨보다 훨씬 더 저렴하기 때문이다. 경제적 이점에도 불구하고, 특정 실시예들에 따라서는 아르곤이 선호되는 캐리어 가스이다.

[0042] 하나 이상의 실시예들에서, 사용된 증착 가스는 또한 탄소 소스 및/또는 게르마늄 소스와 같은 적어도 하나의 2차 원소 소스를 포함한다. 탄소 소스는 실리콘 카본 재료와 같은 실리콘-함유 화합물을 형성하기 위해 실리콘 소스 및 캐리어 가스로 증착 동안 프로세스 챔버에 부가될 수 있다. 탄소 소스는 통상 약 0.1 sccm 내지 약 20 sccm 범위의 속도로, 예를 들어, 약 0.5 sccm 내지 약 10 sccm 범위의 속도로, 더욱 상세하게 약 1 sccm 내지 약 5 sccm 범위의 속도로, 예를 들어, 약 2 sccm의 속도로 프로세스 챔버 안으로 제공된다. 탄소 소스는 수소 가스에서 희석될 수 있고 300 sccm의 속도로 흐를 수 있다. 실리콘-함유 화합물들을 증착하기에 유용한 탄소 소스들은 에틸, 프로필 및 부틸의 알킨들, 알켄들, 알킬들 및 유기실란들을 포함한다. 이러한 탄소 소스들은 메틸실란( $\text{CH}_3\text{SiH}_3$ ), 디메틸실란( $(\text{CH}_3)_2\text{SiH}_2$ ), 에틸실란( $\text{CH}_3\text{CH}_2\text{SiH}_3$ ), 메탄( $\text{CH}_4$ ), 에틸렌( $\text{C}_2\text{H}_4$ ), 에타인( $\text{C}_2\text{H}_2$ ), 프로판( $\text{C}_3\text{H}_8$ ), 프로핀( $\text{C}_3\text{H}_6$ ), 부틴( $\text{C}_4\text{H}_6$ )뿐만 아니라 다른 것들을 포함한다. 에피택셜 층의 탄소 농도는 약 200 ppm 내지 약 5 원자%의 범위, 바람직하게 약 1 원자% 내지 약 3 원자%의 범위에 있고, 예를 들어, 1.5 원자%이다.

일 실시예에서, 탄소 농도는 에피택셜 층 내에서 점차적으로 변화(grade)할 수 있고, 바람직하게 에피택셜 층의 최종 부분에서보다 에피택셜 층의 시작 부분에서 더 낮은 탄소 농도를 갖도록 점차적으로 변화할 수 있다. 대안적으로, 게르마늄 소스 및 탄소 소스는 모두 실리콘 카본 또는 실리콘 게르마늄 카본 재료와 같은 실리콘-함유 화합물을 형성하기 위하여 실리콘 소스 및 캐리어 가스와 함께 증착 동안 프로세스 챔버 내로 부가될 수 있다.

[0043] 대안적으로, 게르마늄 소스는 실리콘 게르마늄 재료와 같은 실리콘-함유 화합물을 형성하기 위하여 실리콘 소스 및 캐리어 가스와 함께 증착 동안 프로세스 챔버에 부가될 수 있다. 게르마늄 소스는 통상 약 0.1 sccm 내지 약 20 sccm의 범위, 바람직하게 약 0.5 sccm 내지 약 10 sccm의 범위, 더욱 바람직하게 약 1 sccm 내지 약 5 sccm의 범위의 속도로, 예를 들어, 약 2 sccm의 속도로 프로세스 챔버 안으로 제공된다. 실리콘-함유 화합물들을 증착하기에 유용한 게르마늄 소스들은 게르만(GeH<sub>4</sub>), 더 높은 차수 게르만들(higer germane) 및 유기게르만들을 포함한다. 더 높은 차수 게르만들은 디게르만(Ge<sub>2</sub>H<sub>6</sub>), 트리게르만(Ge<sub>3</sub>H<sub>8</sub>) 및 테트라게르만(Ge<sub>4</sub>H<sub>10</sub>)뿐만 아니라 다른 것들과 같은 실험식 Ge<sub>x</sub>H<sub>(2x+2)</sub>을 가진 화합물을 포함한다. 유기게르만들은 메틸게르만((CH<sub>3</sub>)GeH<sub>3</sub>), 디메틸게르만((CH<sub>3</sub>)<sub>2</sub>GeH<sub>2</sub>), 에틸게르만((CH<sub>3</sub>CH<sub>2</sub>)GeH<sub>3</sub>), 메틸디게르만((CH<sub>3</sub>)<sub>2</sub>GeH<sub>5</sub>), 디메틸디게르만((CH<sub>3</sub>)<sub>2</sub>Ge<sub>2</sub>H<sub>4</sub>) 및 헥사메틸디게르만((CH<sub>3</sub>)<sub>6</sub>Ge<sub>2</sub>)과 같은 화합물들을 포함한다. 게르만들 및 유기게르만 화합물들이 실시예들에서 유리한 게르마늄 소스들 및 탄소 소스들임이 밝혀진 한편, 증착된 실리콘-함유 화합물들, 즉, SiGe 및 SiGeC 화합물들 내로 게르마늄 및 탄소를 편입시킨다. 에피택셜 층 내 게르마늄 농도는 약 1 원자% 내지 약 30 원자%의 범위에 있고, 예를 들어, 약 20 원자%이다. 게르마늄 농도는 에피택셜 층 내에서 점차적으로 변화할 수 있고, 바람직하게 에피택셜 층의 상부 부분보다 에피택셜 층의 하부 부분에 더 높은 게르마늄 농도를 갖도록 점차적으로 변화할 수 있다.

[0044] 증착 동안 사용된 증착 가스는 붕소, 비소, 인, 갈륨 또는 알루미늄과 같은 원소 도편트의 소스를 제공하기 위하여 적어도 하나의 도편트 화합물을 더 포함할 수 있다. 도편트들은 전자 장치에 의해 요구되는, 제어되고 목적하는 진로로의 방향성 전자 흐름과 같은 다양한 도전성 특성들을 가진 증착된 실리콘-함유 화합물들을 제공한다. 실리콘-함유 화합물들의 막들은 목적하는 도전성 특성을 달성하기 위하여 특정 도편트들로 도핑된다. 일 예시에서, 실리콘-함유 화합물은 예컨대, 약 10<sup>15</sup> 원자들/cm<sup>3</sup> 내지 약 10<sup>21</sup> 원자들/cm<sup>3</sup>의 범위의 농도로 붕소를 부가하도록 디보란(diborane)을 사용함으로써, p-타입 도핑된다. 일 예시에서, p-타입 도편트는 적어도 5×10<sup>19</sup> 원자들/cm<sup>3</sup>의 농도를 갖는다. 또 다른 예에서, p-타입 도편트는 약 1×10<sup>20</sup> 원자들/cm<sup>3</sup> 내지 약 2.5×10<sup>21</sup> 원자들/cm<sup>3</sup>의 범위에 있다. 또 다른 예에서, 실리콘-함유 화합물은 예컨대, 약 10<sup>15</sup> 원자들/cm<sup>3</sup> 내지 약 10<sup>21</sup> 원자들/cm<sup>3</sup>의 범위의 농도로 인 및/또는 비소로, n-타입 도핑된다.

[0045] 도편트 소스는 통상 증착 동안에 약 0.1 sccm 내지 약 20sccm의 범위, 예를 들어, 약 0.5 sccm 내지 약 10 sccm의 범위, 더욱 상세하게 약 1 sccm 내지 약 5 sccm의 범위의 속도로, 예를 들어, 약 2 sccm의 속도로 프로세스 챔버 안으로 제공된다. 도편트 소스로서 유용한 붕소-함유 도편트들은 보란(borane)들 및 유기보란들을 포함한다. 보란들은 보란, 디보란(B<sub>2</sub>H<sub>6</sub>), 트리보란, 테트라보란 및 펜타보란을 포함하는 반면, 알킬보란들은 실험식 R<sub>x</sub>BH<sub>(3-x)</sub>을 가진 화합물들을 포함하여, 여기서, R=메틸, 에틸, 프로필 또는 부틸이고 x=1, 2 또는 3이다. 알킬보란들은 트리메틸보란((CH<sub>3</sub>)<sub>3</sub>B), 디메틸보란((CH<sub>3</sub>)<sub>2</sub>BH), 트리에틸보란((CH<sub>3</sub>CH<sub>2</sub>)<sub>3</sub>B) 및 디에틸보란((CH<sub>3</sub>CH<sub>2</sub>)<sub>2</sub>BH)을 포함한다. 도편트들은 또한 아르신(AsH<sub>3</sub>), 포스핀(PH<sub>3</sub>) 및 예컨대, 실험식 R<sub>x</sub>PH<sub>(3-x)</sub>을 가진 알킬포스핀들을 포함할 수 있고, 여기서 R=메틸, 에틸, 프로필 또는 부틸이고, x=1, 2 또는 3이다. 알킬포스핀들은 트리메틸포스핀((CH<sub>3</sub>)<sub>3</sub>P), 디메틸포스핀((CH<sub>3</sub>)<sub>2</sub>PH), 트리에틸포스핀((CH<sub>3</sub>CH<sub>2</sub>)<sub>3</sub>P) 및 디에틸포스핀((CH<sub>3</sub>CH<sub>2</sub>)<sub>2</sub>P)을 포함한다. 알루미늄 및 갈륨 도편트 소스들은 실험식 R<sub>x</sub>MX<sub>(3-x)</sub>로 기술되는 바와 같이, 알킬화 및/또는 할로겐화 유도체들을 포함할 수 있고, 여기서, M=A1 또는 Ga이고, R=메틸, 에틸, 프로필 또는 부틸이며, X=C1 또는 F이고, x=0, 1, 2 또는 3이다. 알루미늄 및 갈륨 도편트 소스들의 예들은 트리메틸알루미늄(Me<sub>3</sub>A1), 트리에틸알루미늄(Et<sub>3</sub>A1), 디메틸알루미늄클로라이드(Me<sub>2</sub>A1Cl), 알루미늄 클로라이드(A1Cl<sub>3</sub>), 트리메틸갈륨(Me<sub>3</sub>Ga), 트리에틸갈륨(Et<sub>3</sub>Ga), 디메틸갈륨클로라이드(Me<sub>2</sub>GaCl) 및 갈륨 클로라이드(GaCl<sub>3</sub>)를 포함한다.

[0046] 하나 이상의 실시예들에 따르면, 증착 프로세스가 종료된 이후에, 프로세스 챔버는 정화 가스 또는 캐리어 가스로 씻어 낼 수 있거나, 그리고/또는 프로세스 챔버는 진공 펌프로 진공화될 수 있다. 정화 및/또는 진공 프로

세스들은 잉여 증착 가스, 반응 부산물들 및 다른 오염물들을 제거한다. 예시적인 실시예에서, 프로세스 챔버는 약 5 slm으로 캐리어 가스를 흘려보냄으로써 약 10초 동안 정화될 수 있다. 증착 및 정화의 사이클은 다수 사이클 동안 반복될 수 있다. 일 실시예에서, 증착 및 정화 사이클은 약 90회 반복된다.

[0047] 본 발명의 또 다른 양상에서, 블랭킷 또는 비선택적 증착은 높은 차수의 실란(예를 들어, 디실란 및 더 높은 차수) 소스를 사용하여 낮은 온도들에서, 예를 들어, 약 600°C 및 그 이하에서 수행된다. 이것은 증착 단계 동안 산화물 및 질화물과 같은 절연 표면들 상에서 (다결정보다는 오히려) 비정질 성장을 보조하고(비선택적 증착), 이것은 후속적인 에칭 단계에 의해 절연 표면들 상에서의 층 제거를 촉진하며 결정질 기판 상에 성장된 단일 결정 층에 대한 손상을 최소화한다.

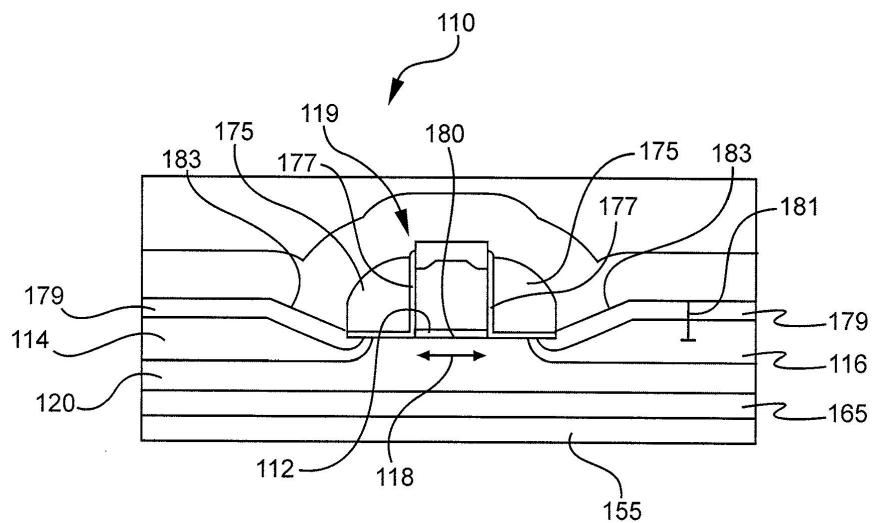

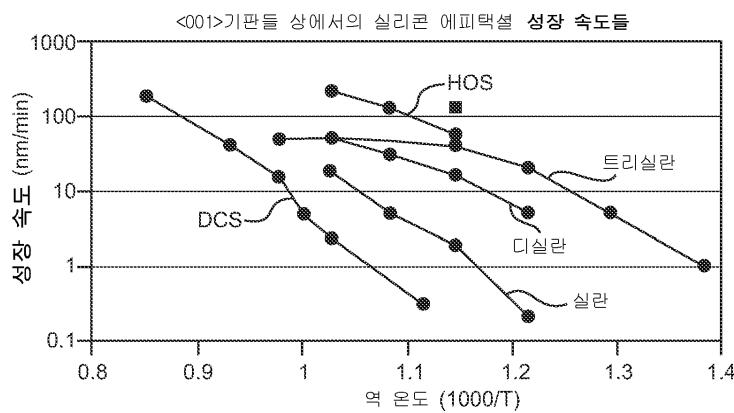

[0048] 도 1은 1000/온도의 함수로서 다양한 온도들에서 처리된 <001> 기판들 상의 실리콘에 대한 에피택셜 성장 속도들의 그래프를 보여준다. 각각의 샘플들은 약 5 내지 8 Torr 사이의 압력에서 600 내지 700°C 사이에서 처리되어, 3-5 slm 사이에서 흐르는 수소 캐리어 가스에서 전달된다. 도 1에서 "HOS"로 라벨링된 샘플은 네오펜타실란이었고, 버블러(bubbler)를 통한 수소 캐리어 가스의 혼합물에서 액체 네오펜타실란에 대한 유량은 약 20 내지 300 sccm 사이에서 가변되었다. 도 1에서 도시된 바와 같이, 더 높은 차수의 실란은 600°C에서 트리실란의 성장 속도보다 약 세 배, 디실란의 성장 속도보다 8배, 그리고 실란의 성장 속도보다 72배임을 보였다.

[0049] 디실란, 헥사클로로디실란, 트리실란 및 네오펜타실란과 같은 높은 차수의 실란을 사용하는 것은 특정 이점들을 제공한다. 기판들 상의 에피택셜 막들의 형성에 네오펜타실란을 사용하는 것은 본원과 양수인이 동일한 미국 특허 출원 공개 제2004/0224089호로 공개된 미국 출원 제10/688,797호, "Silicon-Containing Layer Deposition with Silicon Compounds(실리콘 화합물들을 가진 실리콘-함유 층 증착)"에 기술되고, 전체 내용은 본 명세서에 인용에 의해 편입된다. 네오펜타실란( $(\text{SiH}_3)_4\text{Si}$ )은 실리콘 원자에 결합된 4개의 시릴(- $\text{SiH}_3$ ) 그룹들을 포함하는 3차 실란이다. 더 높은 차수의 실란들을 사용하는 것은 더 낮은 온도에서 더 높은 증착 속도를 가능케 하고, 탄소를 포함하는 실리콘-함유 막들에 대하여 실리콘 소스 가스로서 모노-실란의 사용보다 치환적 탄소 원자들의 더 높은 편입을 가능케 한다. 캐리어 가스로서 질소를 사용하고 실리콘-카본 소스로서 메틸실란(수소에 1% 희석됨)을 사용하여 600°C의 프로세스 온도에서 실리콘 소스 가스들을 실리콘으로서 실란과 비교하여 실시된 블랭킷 증착 실험들에서, 50%의 탄소는 증착된 막들에서 치환적인 탄소였다. 그러나, 더 높은 차수의 실란들로, 디실란은 약 90%보다 더 많은 치환적 탄소를 가진 막들을 생성하였고, 네오펜타실란은 거의 100%의 치환적 탄소를 갖는 막들을 생성하였다.

[0050] 하나 이상의 실시예들에서, 프로세스 챔버에 가까이 근접하여, 예를 들어, 약 5 피트 미만 내에, 더욱 상세하게 프로세스 챔버의 약 2 또는 3 피트 미만 내에 설치된 네오펜타실란 앰풀(ampoule)을 포함하는 액체 소스 캐비닛은 실리콘 소스의 더 높은 전달 속도를 가능케 하고 결과적으로 더 높은 증착 속도를 가능케 한다.

[0051] 본 발명의 또 다른 양상은 증착 동안 네오펜타실란 및 디실란과 같은 더 높은 차수의 실란과 병류하는(co-flowing) 모노실란( $\text{SiH}_4$ )에 관한 것이다. 비록 에피택셜 증착에 적합하지만, 증착 동안 더 높은 차수의 실란들을 사용하는 프로세스들은 일반적으로 모노실란을 사용하는 프로세스들에 비해 비등각성(non-conformal) 성장을 보여준다. 더욱 상세하게, 더 높은 차수의 실란들은 측벽과 같은 수직 평면들 상에서의 증착보다 리세스된 영역들의 바닥 및 게이트의 상부와 같은 수평 표면들 상에 더 두꺼운 증착을 생성하는 경향이 있다. 이러한 비등각성 성장은 선택성을 달성하기 위해 게이트 상부 상에 있는 원치 않는 증착을 예방할 때, 측벽이 오버 에칭되어, 언더컷(undercut)으로서 지칭될 수 있는 것을 야기하는 문제점을 유도할 수 있다. 반면, 소스 가스로서  $\text{SiH}_4$ 를 활용하는 프로세스들은 등각성 성장을 나타내는 경향이 있다. 더 높은 차수의 실란이 모노실란과 병류하는 것은 특히 더 낮은 증착 온도들에서 막 속성들의 맞춤(tailoring)을 가능케 한다. 더 높은 차수 실란 및 모노실란의 비율(예를 들어, 각각의 소스의 유량을 가변시킴으로써)은 증착 프로세스에 의해 형성된 에피택셜 층의 형태(morphology)를 조율하기 위해 사용될 수 있다. 예를 들어, 모노실란 대 더 높은 차수의 실란의 유량이 적어도 약 4:1이 되도록 비율을 조정하는 것은 모노실란 대 더 높은 차수의 실란의 비율이 더 낮았던 프로세스에 비해 유리한 결과들을 제공한 것으로 보였다. 더욱 상세하게, 모노실란 및 디실란이 기판의 리세스된 영역에 대해 약 2.4:1의 비율로 흐른 프로세스 실행 및 모노실란 및 디실란이 약 4:1의 비율로 흐른 프로세스 실행이 비교되었다. 4:1의 비율로 흐른 것으로부터 획득된 샘플은 2.4:1의 비율로 흐른 것으로부터 획득된 샘플보다 더 매끄러운 형태를 야기하였다. 그리하여, 적어도 약 4:1, 그리고 소정의 실시예들에서 약 5:1의 모노실란 대 더 높은 차수의 실란의 비율들은 에피택셜 막들의 형태를 개선하기 위해 사용될 수 있다.

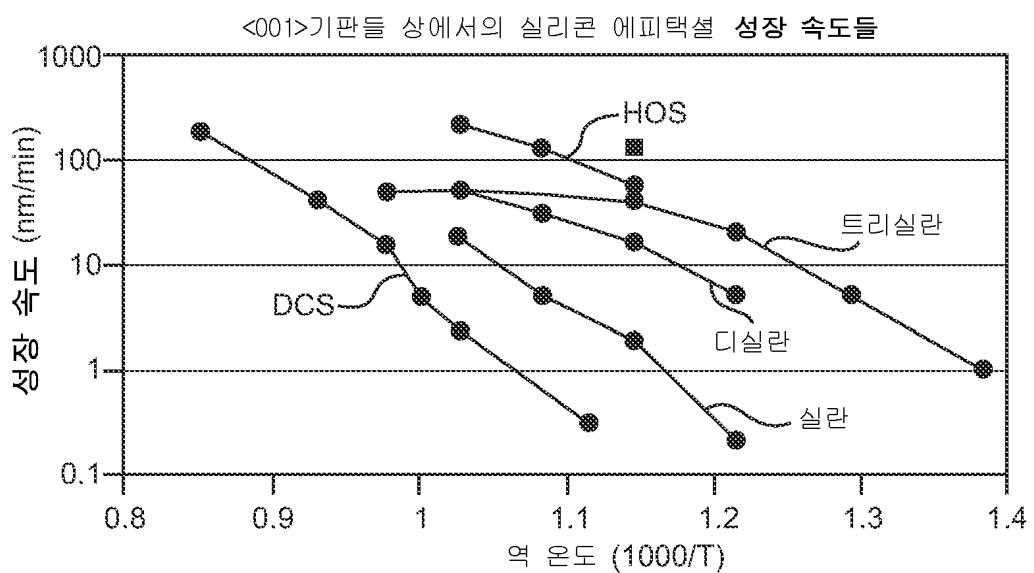

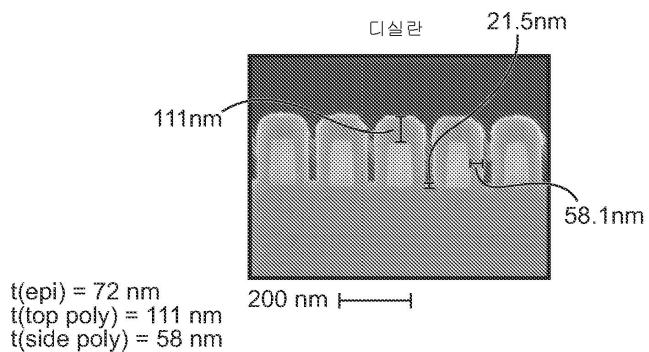

[0052] 도 2A는 절연 구조 상에 에피택셜 막을 증착하기 위하여 실리콘 소스로서 실란을 사용하는 탄소를 함유하는 실

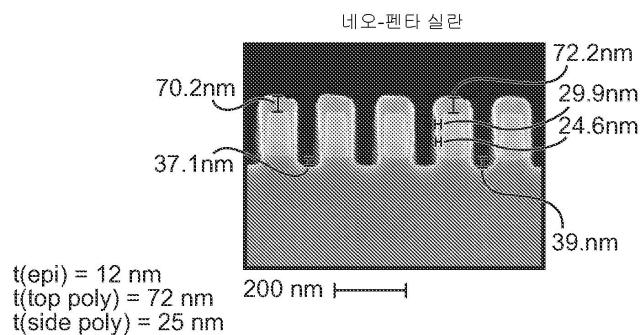

리콘 막의 등각성을 보여준다. 절연 구조들 상에 증착된 막의 스캐닝 전자 마이크로사진인 도 2A에 도시된 바와 같이, 막의 상부 표면은 51 nm인 반면, 막의 측면 표면은 53 nm인 것으로 도시된다. 도 2B는 절연 구조 상에 에피택셜 막을 증착하기 위하여 실리콘 소스로서 디실란을 사용하는 탄소를 함유하는 실리콘 막의 등각성을 보여준다. 도 2B에 도시된 바와 같이, 막의 상부 표면은 111 nm 두께인 반면, 막의 측면 표면은 58 nm 두께이다. 도 2C는 절연 구조 상에 에피택셜 막을 증착하기 위하여 실리콘 소스로서 네오펜타실란을 사용하는 탄소를 함유하는 실리콘 막의 등각성을 보여준다. 도 2C에 도시된 바와 같이, 막의 상부 표면은 72 nm 두께인 반면, 막의 측면 표면은 25 nm 두께이다. 그리하여, 더 높은 차수의 실란들을 사용하는 것에 있어서는, 더 낮은 온도들에서 더 빠른 증착을 제공하나 등각성 성장이 문제가 될 수 있는 트레이드오프가 존재한다.

[0053] 실리콘-함유 에피택셜 막들을 형성하기 위하여 실리콘 소스들로서 병류하는  $\text{SiH}_4$  및 더 높은 차수의 실란을 부가함으로써, 리세스된 영역 측벽들 상의 성장이 제어될 수 있고, 결과적으로 측벽이 후속적인 프로세싱 동안에 언더컷으로부터 보호될 수 있다고 여겨진다. 측벽 성장에 부가하여, 더 높은 차수 실란이 실란( $\text{SiH}_4$ )과 병류하는 것은 높은 차수 실란들을 단독으로 사용하는 프로세스들에 의해 달성된 막 품질을 개선하는 것으로 여겨진다. 동일한 프로세스 조건들 하에서, 더 높은 차수의 실란들을 활용하는 프로세스들로부터  $\text{SiH}_4$ 를 제거하는 것은 더 높은 혼탁도(haziness) 및 더 불량한 막 결정도를 가진 막들을 생성하였다. 본 발명의 실시예들이 특정 동작 이론에 의해 한정되도록 의도되지는 않지만, 더 높은 차수의 실란과 함께 실란을 활용하는 프로세스에서, 실란은 네오펜타실란과 같은 더 큰 분자들로부터 비정질화의 내재 장력(intrinsic tension)을 보상하도록 더 작은 분자들을 제공하는 것으로 보인다.

[0054] 본 발명의 또 다른 양상은 Si:C 막들의 선택적 에피택셜 증착 또는 인 시튜 인 도핑을 위한 방법들에 관한 것이다. 일반적으로, 실리콘 증착 동안의 인 시튜 인 도핑은 성장 속도를 감소시키고 결정 막의 에칭 속도를 증가시키며, 따라서 선택성을 달성하는 것을 어렵게 만든다. 즉, 절연 표면들 상에서의 어떠한 성장도 없이 기판의 결정 표면들 상의 결정 성장을 달성하는 것은 어렵다. 또한, 인 시튜 인 도핑은 에피택셜 막들의 결정도를 저하시키는 경향이 있다.

[0055] 특정 실시예들에서, 전술한 하나 이상의 문제들은 델타 도핑(delta doping)으로 지칭될 수 있는 것에 의해 회피된다. 즉, 오직 도편트 가스, 예를 들어, 인 도편트 가스, 예를 들어,  $\text{PH}_3$  및 캐리어 가스가 도핑되지 않은 증착 이후에 흐른다. 인 도편트 가스는 도핑되지 않은 증착 단계 직후에, 또는 후속적인 에칭 단계 직후에, 또는 정화 단계 직후에, 또는 에칭 및 정화 양쪽 단계 직후에 흐를 수 있다. 에칭 및/또는 정화 단계는 높은 품질 막을 달성하기에 필요한 만큼 반복될 수 있다. 하나 이상의 실시예들에서, 도핑되지 않은 층의 형성 동안 캐리어 가스 및 포스핀과 같은 도편트 소스만을 흘려보내는 것을 수반한다. 이러한 방식으로 처리함으로써, 전술한 하나 이상의 바람직하지 못한 효과들이 회피된다. 예를 들어, 기판 표면 상에 실리콘-함유 재료를 에피택셜로 형성하기 위한 방법은 프로세스 챔버 안으로 단결정 표면을 포함하는 기판을 배치하는 단계 및 그 후에 기판을 도핑되지 않은 증착 가스에 노출시키는 단계를 포함할 것이고, 상기 도핑되지 않은 증착 가스는 기판 상에 제 1 비도핑 층을 형성하기 위하여 실리콘 소스, 선택적 탄소 소스, 및 무 도편트 소스를 포함한다. 그 이후에, 기판은 도핑된 증착 가스에 순차적으로 노출되고, 여기서 증착 가스는 제 1 비도핑 층 상에 도핑된 층을 형성하기 위하여 도편트 소스 및 캐리어 가스를 포함한다. 하나 이상의 실시예들에서, 기판은 단결정 표면 상에 에피택셜 층을 형성하기 위하여 도핑되지 않은 증착 가스에 더 노출될 수 있고, 여기서 상기 증착 가스는 도핑된 층 상에 제 2 비도핑 층을 형성하기 위하여 실리콘 소스, 탄소 소스 및 무 도편트 소스를 포함한다. 그와 같은 프로세스의 예에서, 막들은 약 560°C의 성장 온도 및 10 Torr의 성장 압력에서, 5 slm으로 흐르는 질소 캐리어 가스에서 120 sccm으로 흐르는 NPS를 흘려 보내고, 150 sccm으로 실란을 흘려 보내고, 626 sccm으로 메틸실란(Ar에서 1% 회석됨)을 흘려 보내고, 포스핀(수소에서 1% 회석됨)을 흘려 보냄으로써 제 1 증착 단계를 사용하여 구성되었다. 제 1 증착 단계는 약 15초 동안 실시되었다. 다음, 제 2 증착 단계는 단지 캐리어 가스 내 포스핀만을 흘려 보냄으로써 실시되었다. 제 2 증착 단계는 약 3초 동안 10 Torr의 압력 및 약 560°C의 온도에서 실시되었다. 포스핀 가스(수소에서 1% 포스핀 회석됨)는 5 slm으로 흐르는 질소 캐리어 가스와 함께 15 sccm으로 흘러 들어왔다. 그 다음, 에칭 단계는 70 sccm에서 흐르는 염소, 5 slm에서 흐르는 질소 및 300 sccm에서 흐르는 HCl을 사용하여, 약 14.5 Torr의 압력 및 약 560°C의 온도에서 실시되었다. 에칭 단계는 약 7초 동안 실시되었다. 다음, 정화 단계는 8초 동안 동일 온도 및 압력에서 실시되었고, 그 동안 단지 질소 가스만이 5 slm으로 흘러 들어왔다. 이러한 방식의 프로세싱은 선택적 에피택시 동안 선택성을 개선하는 것으로 예상된다.

[0056] 다른 실시예들에서, 도핑된/도핑되지 않은 층들의 스택이 에칭에 앞서 형성되고, 이것은 도핑된 SiC 에피택시 막의 직접 에칭(direct etching)을 차단한다. 그리하여, 본 발명의 실시예들에 따라, 증착은 에칭에 앞서, 적

어도 두 단계로, 도핑된 증착, 그 다음 도핑되지 않은 증착으로 일어난다. 그리하여, 프로세스의 일 실시예의 단일 사이클은 전술한 바와 같이, 도핑된 증착, 그 다음 도핑되지 않은 증착, 그 다음 에칭, 그 다음 정화를 포함한다. 특정 예로서, 막들은 약 560°C의 성장 온도 및 10 Torr의 성장 압력에서 5 sNm으로 흐르는 질소 캐리어 가스에서, 5 sNm의 N<sub>2</sub>와 함께 운반된 120 sccm으로 흐르는 NPS를 흘려 보내고, 150 sccm으로 실란을 흘려 보내며, 626 sccm으로 메틸실란(Ar에서 1% 희석됨)을 흘려 보내고, 포스핀(수소에서 1% 희석됨)을 흘려 보냄으로써 구성되었다. 포스핀을 포함하는 제 1 증착 단계는 약 5초 동안 실시되었다. 그 다음, 제 2 증착 단계는 도핑된 층을 씌우기 위하여 포스핀을 흘려보내지 않고 실시되었다. 그 다음, 에칭 단계는 70 sccm으로 흐르는 염소, 5 sNm으로 흐르는 질소 및 300 sccm으로 흐르는 HCl로 약 14.5 Torr의 압력, 약 560°C의 온도에서 실시되었다. 에칭 단계는 약 7초 동안 실시되었다. 다음, 정화 단계는 8초 동안 동일한 온도 및 압력에서 실시되었고, 그 동안 단지 질소 가스만이 5 sNm으로 흘려 들어왔다. 물론, 다른 변형예들이 본 발명의 범위 내에 있다. 예를 들어, 증착 단계 다음에는 단지 에칭 단계 또는 정화 단계만이 뒤따를 수 있거나, 대안적으로, 에칭 단계 또는 정화 단계가 고품질 막을 얻기 위해 필요한 만큼 반복될 수 있다.

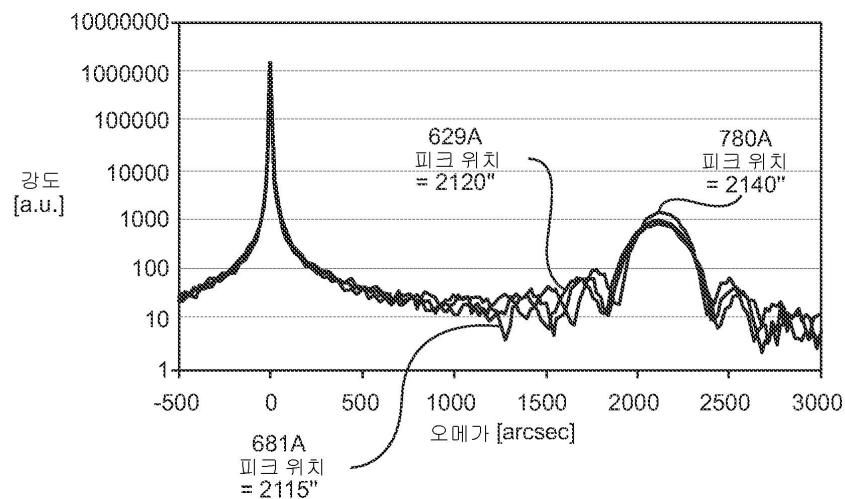

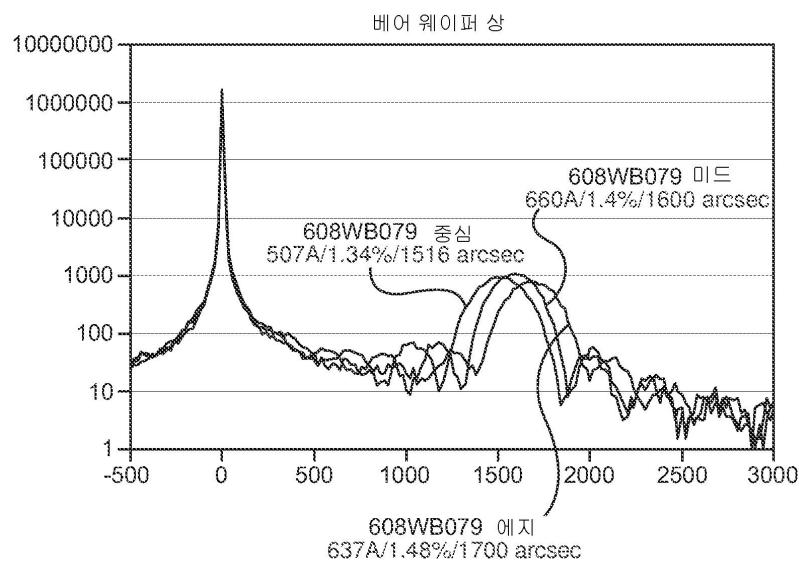

[0057]

본 발명의 다른 실시예들에 따라, 증착 및 정화의 교대 단계들이 실리콘-함유 막 성장 프로세스 동안 사용된다. 도 3은 증착 및 정화의 교대 단계들로 성장된 비선택적 Si:C 에피택시의 고해상도 X-레이 회절 스펙트럼을 보여준다. 그것은 2% 치환적 탄소 농도를 보여준다. 도 4는 증착, 에칭 및 정화의 교대 단계들로 성장된 막들의 고해상도 X-레이 회절 그래프를 보여준다. 도 4는 탄소 농도의 약 1.3 내지 약 1.48 원자 퍼센트를 보여준다. 막들은 약 560°C의 성장 온도 및 10 Torr의 성장 압력에서 5 sNm으로 흐르는 질소 캐리어 가스에서, 120 sccm으로 N<sub>2</sub>와 함께 운반된 네오펜타실란(NPS)을 흘려 보내고, 150 sccm으로 실란을 흘려 보내고, 626 sccm으로 메틸실란(Ar에서 1% 희석됨)을 흘려 보내고, 포스핀(수소에서 1% 희석됨)을 흘려 보냄으로써 구성되었다. 증착은 약 15초 동안 실시되었다. 그 다음, 에칭 단계는 70 sccm으로 흐르는 염소, 5 sNm으로 흐르는 질소 및 300 sccm으로 흐르는 HCl로 약 14.5 Torr의 압력, 약 560°C의 온도에서 실시되었다. 에칭 단계는 약 7초 동안 실시되었다. 다음, 정화 단계는 8초 동안 동일한 온도 및 압력에서 실시되었고, 그 동안 단지 질소 가스만이 5 sNm으로 흘려 들어왔다.

[0058]

다른 실시예들에서, 도핑된/도핑되지 않은 층들의 스택이 에칭에 앞서 형성되고, 이것은 도핑된 SiC 에피택시 막의 직접 에칭을 차단한다. 그리하여, 본 발명의 실시예들에 따라, 증착은 에칭에 앞서, 적어도 두 단계로, 도핑된 증착, 그 다음 도핑되지 않은 증착으로 일어난다. 그리하여, 프로세스의 일 실시예의 단일 사이클은 전술한 바와 같이, 도핑된 증착, 그 다음 도핑되지 않은 증착, 그 다음 에칭, 그 다음 정화를 포함한다. 특정 예로서, 막들은 약 560°C의 성장 온도 및 10 Torr의 성장 압력에서 5 sNm으로 흐르는 질소 캐리어 가스에서, 120 sccm으로 N<sub>2</sub>와 함께 운반된 NPS 유량을 흘려 보내고, 150 sccm으로 실란을 흘려 보내고, 626 sccm으로 메틸실란(Ar에서 1% 희석됨)을 흘려 보내고, 포스핀(수소에서 1% 희석됨)을 흘려 보냄으로써 구성되었다. 포스핀을 포함하는 제 1 증착 단계는 약 5초 동안 실시되었다. 그 다음, 제 2 증착 단계는 포스핀-도핑된 층을 씌우기 위해 포스핀을 흘려보내지 않고 실시되었다. 그 다음, 에칭 단계는 70 sccm으로 흐르는 염소, 5 sNm으로 흐르는 질소 및 300 sccm으로 흐르는 HCl로 약 14.5 Torr의 압력, 약 560°C의 온도에서 실시되었다. 에칭 단계는 약 7초 동안 실시되었다. 다음, 정화 단계는 8초 동안 동일한 온도 및 압력에서 실시되었고, 그 동안 단지 질소 가스만이 5 sNm으로 흘려 들어왔다.

[0059]

하나 이상의 실시예에 따라, 상기 방법들은 순차적인 순서를 따르나, 상기 프로세스가 본 명세서에서 기술된 정확한 단계들로 제한되는 것은 아니다. 예를 들어, 다른 프로세스 단계들이 프로세스 시퀀스의 순서가 유지되는 한, 단계들 사이에 삽입될 수 있다. 에피택셜 증착의 개별 단계들이 이제 하나 이상의 실시예들에 따라 기술될 것이다.

[0060]

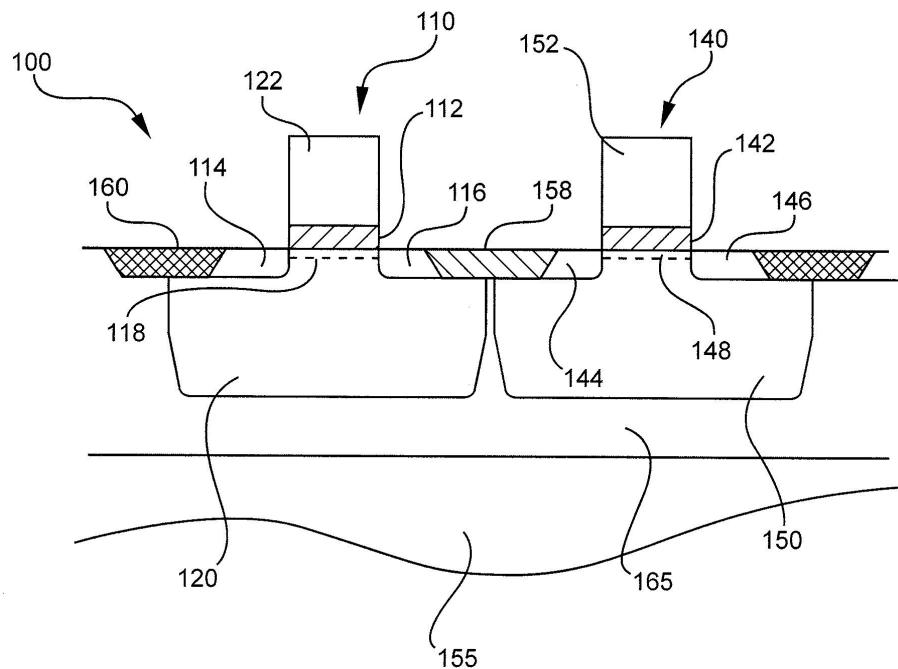

본 발명의 하나 이상의 실시예들은 상보적 금속 산화물 반도체(CMOS) 집적-회로 장치들을 형성하는 데 있어 특히 유용하고 그러한 맥락에서 기술될 것이다. 다른 장치들 및 응용예들 또한 본 발명의 범위 내에 있다. 도 5는 전형적인 CMOS 장치에서 FET 쌍의 단면도의 부분들을 도시한다. 장치(100)는 NMOS 장치 및 PMOS 장치의 소스/드레인 영역들, 게이트 절연물 및 게이트 전극을 제공하기 위해 웰(well)들을 형성한 이후의 반도체 기판을 포함한다. 상기 장치(100)는 단일 결정 실리콘 성장 및 트렌치 에칭에 의한, 그리고 트렌치 개구부들에서의 절연물 성장 또는 증착에 의한 얇은 트렌치 분리 구조(shallow trench isolation structure)들의 형성과 같은 종래의 반도체 프로세스들을 사용하여 형성될 수 있다. 이러한 여러 구조들을 형성하기 위한 세부적인 절차들은 본 명세서에서 더 기술되지 않는다.

[0061]

장치(100)는 p-타입 재료로 도핑된 반도체 기판(155), 예를 들어, 실리콘 기판, 기판(155) 상의 p-타입 에피택셜 실리콘 층(165), 에피택셜 층(165)에 정의된 p-타입 웰 영역(120)과 n-타입 웰 영역(150), p-웰(120)에 정

의된 n-타입 트랜지스터(NMOS FET)(110) 및 n-웰(150)에 정의된 p-타입 트랜지스터(PMOS FET)(140)를 포함한다. 제 1 분리 영역(isolation region)(158)은 NMOS(110) 및 PMOS(140) 트랜지스터들을 전기적으로 분리하고, 제 2 분리 영역(160)은 기판(155) 상의 다른 반도체 장치들로부터 트랜지스터들(110 및 140)의 쌍을 전기적으로 분리한다.

[0062] 본 발명의 하나 이상의 실시예들에 따라, NMOS 트랜지스터(110)는 게이트 전극(122), 제 1 소스 영역(114) 및 드레인 영역(116)을 포함한다. NMOS 게이트 전극(122)의 두께는 크기조정 가능(scalable)하고 장치 성능에 대한 고려 사항들에 기초하여 조정될 수 있다. NMOS 게이트 전극(122)은 N-타입 장치의 일 함수에 대응하는 일 함수를 갖는다. 소스 및 드레인 영역들은 게이트 전극(122)의 대향 측면들 상에 있는 n-타입 영역들이다. 채널 영역(118)은 소스 영역(114)과 드레인 영역(116) 사이에 개입된다. 게이트 절연 층(112)은 채널 영역(118) 및 게이트 전극(122)을 분리한다. NMOS 게이트 전극(122) 및 절연 층을 형성하기 위한 프로세스들은 당업계에 알려져 있고 본 명세서에서는 더 논의하지 않는다.

[0063] 하나 이상의 실시예들에 따라, PMOS 트랜지스터(140)는 게이트 전극(152), 소스 영역(144) 및 드레인 영역(146)을 포함한다. PMOS 게이트 전극(152)의 두께는 크기조정 가능하고 장치 성능에 대한 고려 사항들에 기초하여 조정될 수 있다. PMOS 게이트 전극(152)은 P-타입 장치의 일 함수에 대응하는 일 함수를 갖는다. 소스 및 드레인 영역들은 게이트 전극(152)의 대향 측면들 상에 있는 p-타입 영역들이다. 채널 영역(148)은 소스 영역(144)과 드레인 영역(146) 사이에 개입된다. 게이트 절연물(142)은 채널 영역(148) 및 게이트 전극(152)을 분리한다. 절연물(142)은 채널 영역(148)으로부터 게이트 전극(152)을 전기적으로 절연한다. 도 5에 도시되고 바로 앞서 언급된 트랜지스터들(110 및 140)의 구조들은 단지 예시적이고, 재료들, 충들 등에서의 여러 변형예들이 본 발명의 범위 내에 있음이 이해될 것이다.

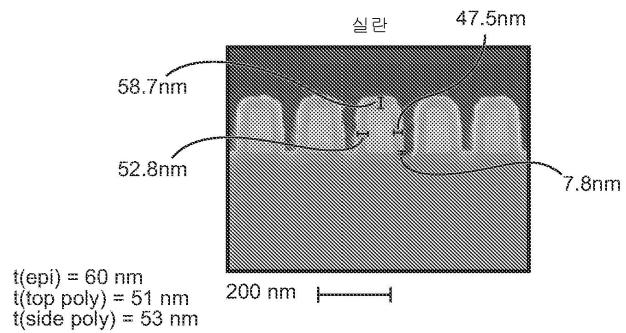

[0064] 이제 도 6을 참조하면, 도 6은 스페이서들, 소스/드레인 영역들 위의 충들, 예를 들어, 실리사이드 충들의 형성 및 에치 스톱(etch stop)의 형성 이후의 도 5의 NMOS 장치(110)에 대한 부가적인 세부사항들에 대한 도면을 보여준다. 도 5에 도시된 PMOS 장치가 이하에서 더 상세히 기술될 NMOS 장치의 채널에 유도된 응력에 영향을 주도록 수치들 및/또는 조성에서 조정될 수 있는 유사한 스페이서들 및 충들을 포함할 수 있음이 이해될 것이다. 그러나, 예시의 목적을 위하여, 단지 NMOS 장치만이 상세히 도시되고 기술된다.

[0065] 도 6은 게이트(119) 둘레에 편입된 적합한 절연 재료로 형성될 수 있는 스페이서들(175)을 도시한다. 오프셋 스페이서들(177) 또한 제공될 수 있고, 각각의 스페이서들(175)을 둘러싼다. 스페이서들(175 및 177)의 형태, 크기 및 두께를 형성하기 위한 프로세스는 당업계에 알려져 있고, 본 명세서에서 더 상세히 기술되지 않는다. 금속 실리사이드 충(179)은 소스 영역(114) 및 드레인 영역(116) 위에 형성될 수 있다. 실리사이드 충(179)은 스퍼터링 또는 PVD(물리적 기상 증착)와 같은 임의의 적합한 프로세서에 의해 니켈, 티타늄 또는 코발트와 같은 적합한 금속으로 형성될 수 있다. 실리사이드 충(179)은 하부에 놓인 표면들의 부분들 안으로 확산할 수 있다. 드레인 영역(116)의 융기는 화살표(181)에 의해 도시되고, 이것은 기판 표면(180)으로부터 실리사이드 충(179) 까지의 거리로서 표현된다. 소스 드레인 영역의 패짓(facet)(183)은 각이 진 표면으로서 도시된다. 당업자에 의해 이해되는 바와 같이, 전술한 예시적인 장치는 본 명세서에서 기술된 방법들에 따라 더 수정될 수 있는 Si:C 에피택셜 충을 갖는 소스/드레인 또는 소스/드레인 연장부를 포함하도록 변형될 수 있다.

[0066] 본 명세서를 통해 지칭되는 "하나의 실시예", "특정 실시예들", "하나 이상의 실시예들" 또는 "일 실시예"는 그러한 실시예와 관련하여 기술된 특정 특징, 구조, 재료 또는 특성이 본 발명의 적어도 하나의 실시예에 포함됨을 의미한다. 그러므로, 본 명세서를 통해 여러 곳에서 언급된 "하나 이상의 실시예들에서", "특정 실시예들에서", "하나의 실시예에서" 또는 "일 실시예에서"와 같은 문구들은 반드시 본 발명의 동일한 실시예를 지칭하는 것은 아니다. 부가하여, 특정 특징들, 구조들, 재료들 또는 특성들이 하나 이상의 실시예들에서 임의의 적합한 방식으로 결합될 수 있다. 상기 방법의 기재 순서는 제한으로 간주되지 않아야 하며, 방법들은 기술된 동작들을 순서를 달리하여 또는 생략하거나 추가하여 사용할 수 있다.

[0067] 전술한 설명은 제한적인 것이 아니라, 예시적인 것으로 의도됨을 이해되어야 한다. 다수의 다른 실시예들이 전술한 설명을 숙지한 당업자에게 자명할 것이다. 따라서 본 발명의 범위는 첨부된 청구범위를 참조하여, 이러한 청구범위가 부여하는 전체 범위의 균등물들 따라 결정되어야 한다.

## 도면의 간단한 설명

[0017] 본 발명의 앞서 언급된 특징들이 상세히 이해될 수 있는 방식으로, 앞서 간단히 요약된 본 발명의 보다 특정한 기술이 실시예들을 참조하여 이루어질 수 있고, 소정의 실시예들은 첨부 도면에 도시된다. 그러나 첨부 도면들

은 본 발명의 전형적인 실시예들을 단지 예시할 뿐이고 따라서 본 발명의 범위를 제한하는 것으로 간주되지 않아야 하며, 본 발명에 대하여 다른 균등하게 유효한 실시예들을 인정할 수 있다.

[0018] 도 1은 여러 실리콘 선구체들에 대하여 1000/온도에 대한 에피택셜 성장 속도(growth rate)의 그래프이다;

[0019] 도 2A는 실란 소스에 의한 Si 기판 상의 Si:C 에피택셜 성장 및 절연 구조들의 등각성(conformality)을 보여주는 SEM 사진이다;

[0020] 도 2B는 디실란 소스에 의한 Si 기판 상의 Si:C 에피택셜 성장 및 절연 구조들의 등각성을 보여주는 SEM 사진이다;

[0021] 도 2C는 네오펜타실란 소스에 의한 Si 기판 상의 Si:C 에피택셜 성장 및 절연 구조들의 등각성을 보여주는 SEM 사진이다;

[0022] 도 3은 증착 및 정화의 교대 단계들로 에피택시 성장된 비선택적 Si:C의 고 해상도 X-레이 회절 스팩트럼이다;

[0023] 도 4는 증착, 에칭 및 정화의 교대 단계들로 에피택시 성장된 선택적 Si:C의 고해상도 X-레이 회절 스팩트럼이다;

[0024] 도 5는 본 발명의 일 실시예에 따라 전계 효과 트랜지스터 쌍의 단면도이다;

[0025] 도 6은 본 장치 상에 형성된 부가 층들을 갖는 도 5에 도시된 PMOS 전계 효과 트랜지스터의 단면도이다.

## 도면

### 도면1

## 도면2A

## 도면2B

## 도면2C

## 도면3

## 도면4

도면5

도면6