(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5295250号

(P5295250)

(45) 発行日 平成25年9月18日(2013.9.18)

(24) 登録日 平成25年6月21日(2013.6.21)

(51) Int.Cl.

H01L 33/58 (2010.01)

F 1

H01L 33/00 430

請求項の数 21 (全 12 頁)

(21) 出願番号 特願2010-526157 (P2010-526157)

(86) (22) 出願日 平成20年9月12日 (2008.9.12)

(65) 公表番号 特表2010-541222 (P2010-541222A)

(43) 公表日 平成22年12月24日 (2010.12.24)

(86) 國際出願番号 PCT/DE2008/001533

(87) 國際公開番号 WO2009/039829

(87) 國際公開日 平成21年4月2日 (2009.4.2)

審査請求日 平成23年6月30日 (2011.6.30)

(31) 優先権主張番号 102007046744.5

(32) 優先日 平成19年9月28日 (2007.9.28)

(33) 優先権主張国 ドイツ(DE)

(31) 優先権主張番号 102008005345.7

(32) 優先日 平成20年1月21日 (2008.1.21)

(33) 優先権主張国 ドイツ(DE)

(73) 特許権者 599133716

オスラム オプト セミコンダクターズ

ゲゼルシャフト ミット ベシュレンクテ

ル ハフツング

Osram Opto Semiconductors GmbH

ドイツ連邦共和国、93055 レーゲン

スブルグ、ライプニッツシュトラーゼ 4

Leibnizstrasse 4, D

-93055 Regensburg,

Germany

(74) 代理人 100061815

弁理士 矢野 敏雄

(74) 代理人 100099483

弁理士 久野 琢也

最終頁に続く

(54) 【発明の名称】半導体ベースの素子、半導体ベースの素子の収容部材、ならびに、半導体ベースの素子の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

収容部材(12)の組み込み位置への実装のために、

第1の表面(2)と該第1の表面(2)の反対側の第2の表面(3)とを有するガラス基板(1)と、

前記第1の表面(2)に収容された、発光特性を有する半導体素子(5)と、

前記ガラス基板(1)の前記第1の表面(2)上でそのコーナー領域に配置された実装用基部(10)と

を有する、

半導体ベースの素子において、

前記実装用基部(10)は、前記半導体ベースの素子の全体が該実装用基部(10)を通して前記組み込み位置に支持されるように構成されており、

前記第1の表面(2)の一部の領域のみが前記半導体素子(5)によって覆われてあり、

前記第1の表面(2)の残りの領域は鏡(8)によって覆われていることを特徴とする半導体ベースの素子。

## 【請求項 2】

前記第2の表面(3)に光学素子(11)が収容されている、請求項1記載の半導体ベースの素子。

## 【請求項 3】

前記第1の表面(2)と前記発光特性を有する前記半導体素子(5)とのあいだに変換

10

20

層(4)が配置されている、請求項1または2記載の半導体ベースの素子。

**【請求項4】**

前記光学素子(11)は、フレネルレンズの形態を有しているか、または、光学的ディフューザとして構成されている、請求項2記載の半導体ベースの素子。

**【請求項5】**

前記第1の表面(2)のうち前記鏡(8)によって覆われていない中央領域は、前記鏡(8)によって覆われていない変換層(4)によってコーティングされている、請求項3記載の半導体ベースの素子。

**【請求項6】**

前記変換層(4)は円形に成形されており、透明な前記ガラス基板(1)は正方形の基本形状を有している、請求項5記載の半導体ベースの素子。 10

**【請求項7】**

前記半導体素子(5)は前記ガラス基板(1)の前記第1の表面(2)から遠いほうの面に少なくとも2つの電気コンタクト面(7)を有する、請求項1から6までのいずれか1項記載の半導体ベースの素子。

**【請求項8】**

前記半導体素子(5)は、前記第1の表面(2)の中央に位置しており、かつ、前記実装用基部(10)に包囲されている、請求項7記載の半導体ベースの素子。

**【請求項9】**

前記ガラス基板(1)は前記半導体ベースの素子を支持している、請求項1から8までのいずれか1項記載の半導体ベースの素子。 20

**【請求項10】**

前記半導体素子(5)は、前記ガラス基板(1)を除いた厚さが20μm以下の薄膜発光ダイオードである、請求項1から9までのいずれか1項記載の半導体ベースの素子。

**【請求項11】**

前記半導体素子(5)のうち前記ガラス基板(1)から遠いほうの主表面上に、前記半導体素子(5)内で形成される電磁放射の少なくとも一部を前記ガラス基板(1)の方向へ反射させて戻す反射層が被着されているかまたは形成されている、請求項10記載の半導体ベースの素子。

**【請求項12】**

前記光学素子(10)は、経時劣化および温度に対して安定なシリコーンから形成される層内に埋め込まれている、請求項2記載の半導体ベースの素子。 30

**【請求項13】**

請求項1から12までのいずれか1項記載の半導体ベースの素子に対する収容部材(12)において、

半導体ベースの素子のコンタクト面(7)に電気的に接続されている、収容部の2つの電気コンタクト(13)と、実装用基部(10)を収容した基部収容部(14)とが設けられており、

前記基部収容部(14)は電気的に中性であり、前記2つの電気コンタクト(13)に電気的に接続されていない 40

ことを特徴とする半導体ベースの素子に対する収容部材。

**【請求項14】**

請求項1から12までのいずれか1項記載の半導体ベースの素子の製造方法であって、ガラス基板(1)を用意するステップ、および、

該ガラス基板(1)の第1の表面(2)上に半導体素子(5)を被着するステップを有する

ことを特徴とする半導体ベースの素子の製造方法。

**【請求項15】**

前記第1の表面(2)上に鏡面層(8)を被着する、請求項14記載の半導体ベースの素子の製造方法。 50

**【請求項 16】**

前記ガラス基板(1)の第2の表面(3)に光学素子(11)を被着する、請求項14または15記載の半導体ベースの素子の製造方法。

**【請求項 17】**

前記ガラス基板の前記第1の表面(2)と前記半導体素子(5)とのあいだに変換層(4)を被着する、請求項14から16までのいずれか1項記載の半導体ベースの素子の製造方法。

**【請求項 18】**

鏡面層(8)をフォト技術によって制御されるスパッタリングプロセスまたは蒸着プロセスによって被着するか、および／または、変換層(4)をプリンティングプロセスまたはスクリーンプリンティングプロセスによって被着する、請求項14から17までのいずれか1項記載の半導体ベースの素子の製造方法。 10

**【請求項 19】**

前記ガラス基板(1)の前記第1の表面(2)上にめっきプロセスにより少なくとも1つの実装用基部(10)を被着する、請求項14から18までのいずれか1項記載の半導体ベースの素子の製造方法。

**【請求項 20】**

前記光学素子(11)を経時劣化および温度に対して安定な層内へ組み込む、請求項16から19までのいずれか1項記載の半導体ベースの素子の製造方法。 20

**【請求項 21】**

前記経時劣化および温度に対して安定な層をシリコーンから形成する、請求項20記載の半導体ベースの素子の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本願は、独国出願第102007046744.5号および独国出願第102008005345.7号の優先権を主張するものであり、その開示内容は参照によって本願に取り込まれるものとする。

**【0002】**

本発明は、発光特性を有する半導体ベースの素子、当該の半導体ベースの素子の収容部材、ならびに、当該の半導体ベースの素子の製造方法に関する。 30

**【0003】**

半導体をベースとした発光特性を有する素子は例えば発光ダイオードである。これは、たいてい、プラスティックと金属との接合体またはセラミックから成るケーシング内に発光特性を有する半導体素子が実装されまたは埋め込まれるように構成されている。半導体ベースの素子の製造プロセスにおいて、半導体素子ははんだ付け過程または接着過程によってケーシング内に実装される。

**【0004】**

発光特性を有する半導体素子、例えば薄膜発光ダイオードは、垂直方向に電流の流れる半導体素子と水平方向に電流の流れる半導体素子とで区別される。垂直方向に電流の流れる半導体素子では、半導体ベースの素子の実装面が個々の電気コンタクトとして構成される。第2の電気コンタクトは半導体素子の発光面側に配置される。当該の第2の電気コンタクトは通常ボンディングワイヤによって接続される。水平方向に電流の流れる半導体素子は、半導体素子の実装面上に2つの電気コンタクトが形成されるように構成される。 40

**【0005】**

特に、垂直方向に電流の流れる半導体素子では、第1の電気コンタクトと第2の電気コンタクトとが半導体素子の延在する主平面の面法線の方向で見て上下に重なり合って並んでいる。水平方向に電流の流れる半導体素子では、第1の電気コンタクトおよび第2の電気コンタクトまたはこれらのコンタクトの領域が主平面を上から見たとき横方向に隣り合って並んでいる。 50

**【 0 0 0 6 】**

有利には、電流の流れは垂直方向または水平方向のみに限定されない。垂直方向に電流の流れる半導体素子では、有利には、横方向への電流の広がりが生じる。水平方向に電流の流れる半導体素子では、半導体素子内の電流は、主平面の面法線に対して平行な成分を少なくともところどころに有する。

**【 0 0 0 7 】**

半導体素子そのものの構造とは無関係に、ケーシング内に、透明樹脂または他の封止材料による注型成形によって、半導体素子が付加的に外部影響から保護される。半導体素子の静電気に対する安定化および機械的負荷に対する保護は、半導体素子を包囲するケーシングによって行われる。こうして半導体素子の保護および支持が達成される。カバーとなるケーシングを用いると、発光特性を有する半導体ベースの素子に対して、半導体素子そのものの大きさをいちじるしく上回る寸法が生じる。このことは、素子の微細化の妨げとなる。

10

**【 0 0 0 8 】**

したがって、本発明の課題は、さらなる微細化の可能な、発光特性を有する半導体ベースの素子を提供することである。

**【 0 0 0 9 】**

この課題は、独立請求項の特徴部分に記載された特徴を有する、半導体ベースの素子、半導体ベースの素子の収容部材ならびに半導体ベースの素子の製造方法により解決される。本発明の有利な実施形態および改善形態は、各従属請求項に記載されている。特許請求の範囲の開示内容は参照によって本明細書に明示的に含まれるものとする。

20

**【 図面の簡単な説明 】****【 0 0 1 0 】**

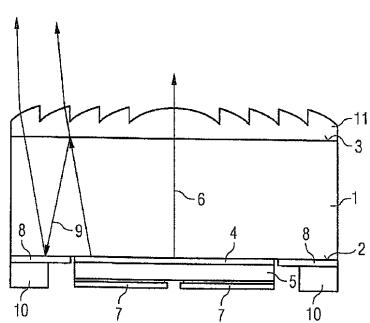

【図1】半導体ベースの素子の第1の実施例の断面図である。

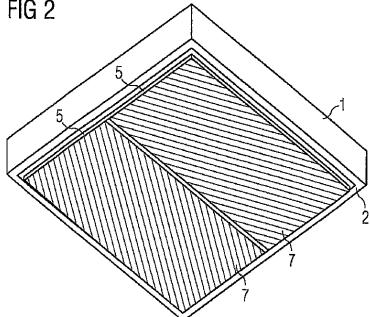

【図2】半導体ベースの素子の第2の実施例の斜視図である。

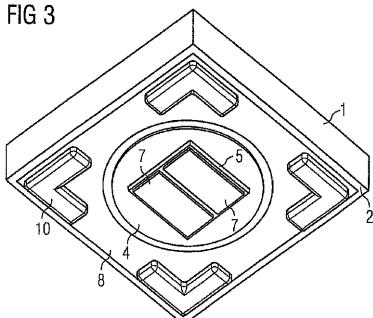

【図3】半導体ベースの素子の第1の実施例の第1の方向からの斜視図である。

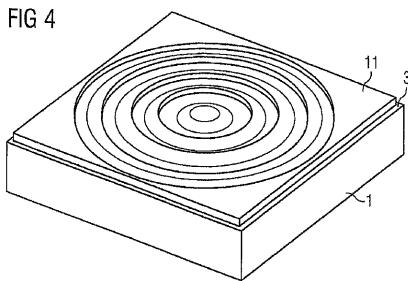

【図4】半導体ベースの素子の第1の実施例の第2の方向からの斜視図である。

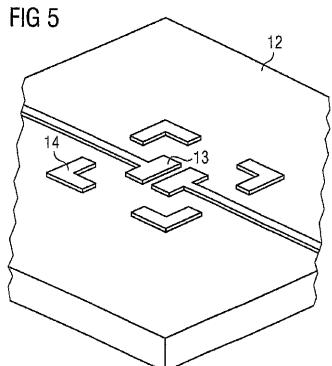

【図5】第1の実施例の半導体ベースの素子に対する収容部材の一部の斜視図である。

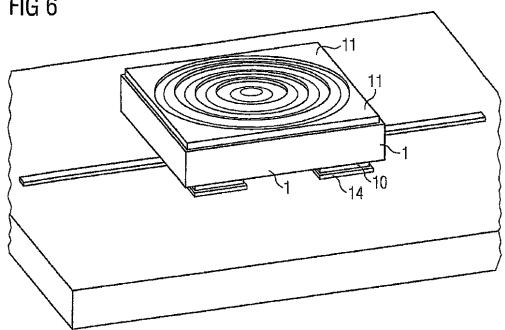

【図6】第1の実施例の半導体ベースの素子を収容部材に収容した様子を示す斜視図である。

30

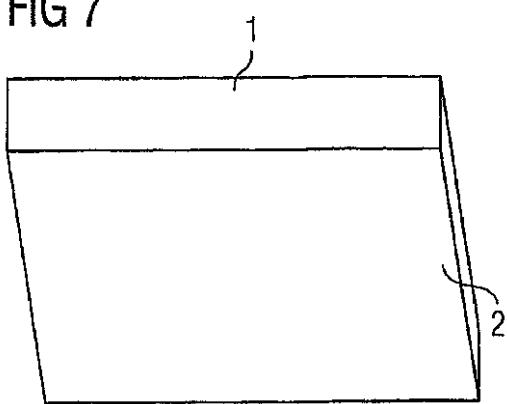

【図7】第1の実施例の半導体ベースの素子を製造する製造方法の第1のステップを示す図である。

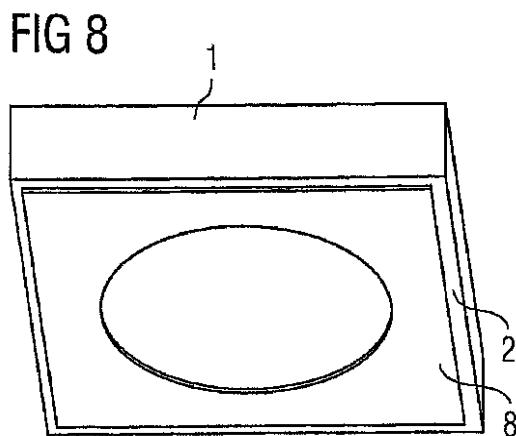

【図8】第1の実施例の半導体ベースの素子を製造する製造方法の第2のステップを示す図である。

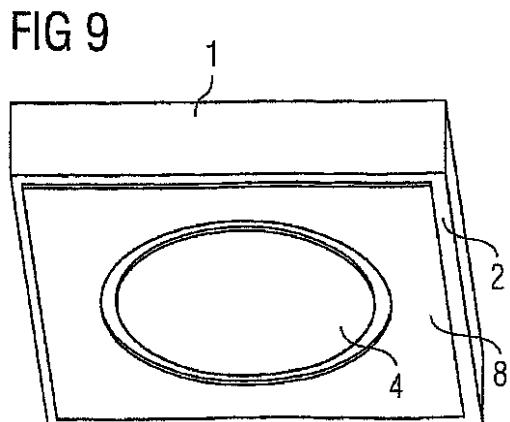

【図9】第1の実施例の半導体ベースの素子を製造する製造方法の第3のステップを示す図である。

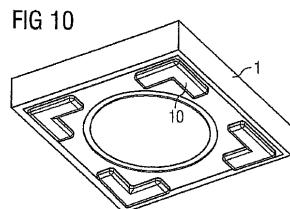

【図10】第1の実施例の半導体ベースの素子を製造する製造方法の第4のステップを示す図である。

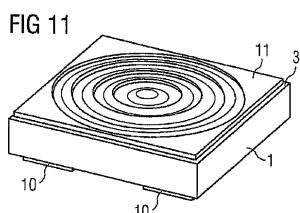

【図11】第1の実施例の半導体ベースの素子を製造する製造方法の第5のステップを示す図である。

40

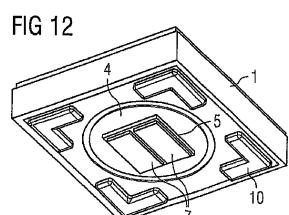

【図12】第1の実施例の半導体ベースの素子を製造する製造方法の第6のステップを示す図である。

**【 0 0 1 1 】**

発光特性を有する半導体ベースの素子にはガラス基板が設けられている。発光特性を有する半導体ベースの素子はオプトエレクトロニクス半導体チップなどの発光半導体素子を含む。半導体素子は特に半導体層列、例えば光形成のための活性領域を含むエピタキシ半導体層列を備える。例えば、活性領域にはp n接合部、ダブルヘテロ構造および/または量子井戸構造が含まれる。

**【 0 0 1 2 】**

ガラス基板は主として相互に平行に対向する2つの表面を有している。ガラス基板の第

50

1の表面には発光特性を有する半導体素子が配置されている。半導体素子はガラス基板の第1の表面に配置され、光の放射方向はガラス基板の内部へ向かう方向となる。放射方向とは半導体素子が駆動中に電磁放射を放出する方向のことであり、特に、半導体素子の主平面に対して垂直方向に延在する。有利には、ガラス基板は半導体素子に対する支持部材を形成している。

#### 【0013】

有利な実施形態によれば、半導体素子はほぼ正方形の基本形状を有する。ここでは、半導体素子のエッジ長さは約3mmである。別の実施形態では、半導体素子のエッジ長さは約0.85mmである。さらに別の実施形態では、半導体素子の横寸法はガラス基板の横寸法に等しい。

10

#### 【0014】

別の有利な実施形態においては半導体素子が薄膜発光ダイオードとして構成されている。水平方向に電流の流れる半導体素子、特に薄膜発光ダイオードにおいて、ガラス基板は支持部材として特に有利である。なぜなら、特に薄膜発光ダイオードでは、製造プロセス中に成長基板が分離されるからである。成長基板は、製造プロセス中、半導体素子の支持部材として機能する。成長基板は製造プロセス中に分離されるため、支持機能を担当する代替の部材が必要となる。ガラス基板は支持機能だけでなく、半導体素子を機械的負荷から保護する機能も有する。

#### 【0015】

この種の薄膜発光ダイオードの原理については、例えばI. Schnitzer et.al., Appl.Phys.Lett.63 (16), 18.Oct.1993の2174頁～2176頁に記載されており、この文献を本願の参考文献とする。また、欧州公開第0905797号明細書および国際公開第02/13281号明細書に薄膜発光ダイオードの例が記載されており、これらの開示内容は参照によって本願に含まれるものとする。

20

#### 【0016】

薄膜発光ダイオードは、ガラス基板が用いられない場合、約20μmより小さい厚さを有し、特に10μmより小さい厚さを有する。有利には、薄膜発光ダイオードから成長基板が取り除かれる。この"成長基板が取り除かれる"とは、場合一によって半導体層列の成長のために使用される成長基板が構造体から除去されるかまたは少なくとも非常に薄くされることを意味する。とりわけ、この成長基板は、それ自体でも、また半導体構造のエピタキシ層列を伴っても、片持梁式の保持が不可能となるほど薄くされている。きわめて薄い成長基板の残留部は特に成長基板の機能には適さない。薄膜発光ダイオードは混合構造を有する少なくとも1つの面を備えた少なくとも1つの半導体層を含む。理想的な場合にはこの混合構造によりエピタキシャル層列内にほぼエルゴード的な光分布が生じる。つまりこの光分布は有利には可能な限りエルゴード的な確率分散特性を有している。

30

#### 【0017】

別の有利な実施形態では、薄膜発光ダイオードの光形成を行う半導体層列（特にエピタキシ層列）のうちガラス基板から遠いほうの面に、この半導体層列で形成された電磁放射の少なくとも一部をガラス基板の方向へ反射して戻す反射層が被着されるかまたは形成される。

40

#### 【0018】

半導体層列のガラス基板に面した側には、当該の半導体素子を形成する際に、電気端子面、電気コンタクトまたは電気コンタクト面は設けられない。有利には、半導体素子はガラス基板の第1の表面から遠いほうの面にn側のコンタクトおよびp側のコンタクトに対する2つの電気コンタクト面を有する。

#### 【0019】

別の実施形態によれば、ガラス基板の第2の表面上に光学素子が配置される。したがって、半導体素子で形成された光はガラス基板の内部および光学素子を通って放出される。光学素子により、発光半導体素子の利用目的と光学素子の光学特性とに応じて、種々の機能が達成される。例えばレンズとして構成された光学素子により、光束が形成される。ま

50

た、光学ディフューザとして構成された光学素子により、放出された光が分散される。半導体ベースの素子の利用の形態に応じて、種々の特性を形成することができる。形成された半導体ベースの素子の寸法は任意にスケーリング可能である。必要な幅および高さは主として所望の光学特性に基づいて定められる。

#### 【0020】

半導体ベースの素子から放出される光およびその混合光について、あらかじめ定められた光色またはあらかじめ定められた波長を形成するために、本発明の別の有利な実施形態によれば、発光半導体素子とガラス基板の第1の表面とのあいだに変換層が配置されている。変換層はその内部を通り抜ける光の少なくとも一部の波長を変換する。したがって、それぞれの色調は半導体素子の発光のみによっては実現することはできない。例えば、青色光を放出する半導体素子を黄色変換層と組み合わせることにより、簡単かつ低コストに白色光を形成することができる。10

#### 【0021】

本発明の別の有利な実施形態によれば、ガラス基板の第1の表面は半導体素子の収容に必要な面積よりも大きく構成されており、付加的に少なくとも1つの実装用基部を設けることができる。実装用基部は、半導体素子の厚さの全体を均等にし、ガラス基板および半導体ベースの素子に作用する機械的負荷を吸収して実装位置へ逃がすことのできる材料厚さを有する。組み込まれた状態において、半導体素子は機械的負荷から完全に保護される。有利な実施形態によれば、組み込まれていない状態においても、半導体素子は摩耗負荷に対して幾分かは保護される。20

#### 【0022】

発光特性を有する半導体ベースの素子の有利な実施形態によれば、光散乱損失を回避するために、半導体素子によって覆われていない表面が鏡によって覆われる。当該の鏡は、有利な実施形態では、ガラス基板の第1の表面のうち半導体素子によって覆われていない領域のみを覆うように直接に被着される。したがって、製造技術的な例外を除けば、ガラス基板上には発光面または光反射面が形成されることになる。ここで、発光面は半導体素子により形成され、光反射面は鏡により形成される。

#### 【0023】

さらに、前述した方式で形成される半導体ベースの素子を収容する収容ユニット（以下では収容部材と略する）も設けられる。30

#### 【0024】

収容部材は結線可能に構成された2つの電気コンタクトを有する。したがって、電気信号ないし電気エネルギーを、収容部材に収容された半導体ベースの素子へ供給可能である。半導体素子のコンタクトの寸法および面積に等しい電気コンタクトが形成される。導電性接着剤またははんだでの接着により、半導体素子と収容部材とのあいだの電気的接触が形成される。コンタクトは上部に少なくとも1つの実装用基部を収容可能な少なくとも1つの基部収容部によって包囲されている。基部収容部は電気的にニュートラルであり、電気コンタクトとの接続を形成していない。

#### 【0025】

さらに本発明は半導体ベースの素子の製造方法に関する。本発明の製造方法は次のステップを含む。40

#### 【0026】

第1のステップで、ガラス基板が用意される。続く第2のステップで、半導体素子がガラス基板の第1の表面に被着され、光学素子がガラス基板の第2の表面に被着される。

#### 【0027】

本発明の製造方法は複数のガラス基板に対して同時に適用される。この場合、複数の半導体ベースの素子を並列に形成するためのガラスウェハが設けられる。この場合、本発明の製造方法は、ガラスウェハ全体にわたって形成される複数の半導体ベースの素子を個別化するステップを含む。

#### 【0028】

10

20

30

40

50

本発明の有利な実施形態によれば、発光特性を有する半導体ベースの素子は、あらかじめ定められた波長の光または混合光、例えば白色光を放出するように製造される。例えば、公知の半導体プラスティックのみによっては形成できない波長を得るために、有利な実施形態として、半導体素子の被着前にガラス基板の第1の表面上に変換層が被着される。有利には、この場合、プリンティングプロセスまたはスクリーンプリンティングプロセスが用いられる。

#### 【0029】

平面的な広がりがガラス基板の第1の表面より小さい半導体素子に対しては、フォト技術によって制御されるスパッタリングプロセスまたは蒸着プロセスにより、鏡面層が被着される。ガラス基板の第1の表面は、フォト技術、特にフォトリソグラフィプロセスによって前処理されるので、半導体素子および場合により被着される変換層によって覆われていない領域のみをスパッタリングプロセスまたは蒸着プロセスによって処理することができる。10

#### 【0030】

ガラス基板の第2の表面に配置される光学素子は、経時劣化および温度に対して安定な層、有利にはシリコーンから形成される層に埋め込まれる。

#### 【0031】

以下に本発明を図1～図12に示した種々の実施例に即して詳細に説明する。

#### 【0032】

全図を通して、同じ機能を有する要素には同じ参照番号を付してある。図および図示した要素の互いの大きさの比は縮尺通りではないことに注意されたい。むしろ、個々の要素のなかには、理解および／または説明を容易にするために意図的に拡大して表示したものがある。20

#### 【0033】

図1には、従来の方式で光を形成する、発光特性を有する半導体ベースの素子の第1の実施例が示されている。支持部材として透明なガラス基板1が設けられている。当該のガラス基板1は第1の表面2および第2の表面3を有する。第1の表面2には変換層4が被着されており、その上に半導体素子5が被着されている。半導体素子5は発光特性を有しており、変換層4の上に配置されている。形成される光の放射方向6は変換層4からガラス基板1の内部を通る方向である。30

#### 【0034】

有利には、半導体素子5は薄膜発光ダイオードとして構成され、ガラス基板1から遠いほうの表面に少なくとも2つの電気コンタクト面7を有する。この電気コンタクト面7を介して半導体素子5に電気エネルギーが供給される。半導体素子5は、図1の実施例では、ガラス基板1の第1の表面2の全体を覆ってはいない。ガラス基板1の第1の表面2の残りの領域は鏡8によって覆われている。鏡8は、反射により第1の表面2の方向へ戻る散乱光成分9を再び放射方向6へ配向し、第2の表面3へ到達させる機能を有する。これにより光散乱損失が低減される。

#### 【0035】

第1の表面2の外縁には実装用基部10が取り付けられており、この実装用基部10により半導体ベースの素子を収容部内に安定に固定することができる。実装用基部10は、半導体ベースの素子の全体が当該の実装用基部10によって組み込み位置で支持されるように構成される。こうして半導体素子5での機械的負荷は回避される。40

#### 【0036】

ガラス基板1の第2の表面3の上には光学素子11が被着される。この実施例では、光学素子11はフレネルレンズである。フレネルレンズの形態の光学素子11により、光束が形成される。しかし、半導体ベースの素子はこの実施例には限定されず、他の特性を有する光学素子、例えば光学ディフューザなどを適用することもできる。これらの適用は、半導体ベースの素子の利用目的に合わせて調整可能である。

#### 【0037】

10

20

30

40

50

図2には発光特性を有する半導体ベースの素子の第2の実施例が示されている。ここでは、半導体素子5はガラス基板1の第1の表面2のほぼ全面にわたって設けられている。図2の実施例では、ガラス基板1の第1の表面2の平面的な広がりが半導体素子5の平面的広がりにほぼ相応している。図1の第1の実施例とは異なり、図2の第2の実施例では、実装用基部10または鏡8の配置は必要ない。

#### 【0038】

図3には、第1の実施例の半導体ベースの素子を第1の方向から見た斜視図が示されている。当該の斜視図の観察方向は、下から第1の表面2を見る方向である。

#### 【0039】

第1の表面2には、半導体素子5、変換層4、鏡8および実装用基部10が配置されている。ガラス基板1の第1の表面2の中央には円形の区画が存在しており、ここに変換層4が配置され、その上の中央に半導体素子5が配置されている。半導体素子5は組み込み位置で電気エネルギーを受け取るための導電性のコンタクト面7を有している。円形の変換層4を包囲するように鏡8が被着されており、光散乱損失が回避される。

10

#### 【0040】

ガラス基板1は有利には正方形の基本形状を有しており、第1の表面2の各コーナーに少なくとも1つの実装用基部10を有する。実装用基部10により、半導体ベースの素子は組み込み位置に固定される。この場合、組み込み位置で半導体ベースの素子に作用する機械的な力は実装用基部10を介して外部へ逃がされるので、半導体素子5は機械的負荷から保護される。図3に示されている半導体ベースの素子はほぼ正方形の基本形状を有しており、ほぼ3mmのエッジ長さおよびほぼ0.85mmの厚さを有する。これらの外部寸法は限定的なものではない。前述した個々の半導体ベースの素子の寸法は光学特性への要求のみにしたがって定められる。

20

#### 【0041】

図4には、図1および図3に示されている第1の実施例の半導体ベースの素子を第2の方向から見た斜視図が示されている。ここでの観察方向は、上からガラス基板1の第2の表面3を見る方向である。ガラス基板1の第2の表面3の上には光学素子11が収容されている。この実施例では、光学素子11はレンズである。特に有利には、レンズはフレネルレンズである。

#### 【0042】

30

図5には、図1、図3、図4の半導体ベースの素子に対する収容部が示されている。ここでは、配線板12上に少なくとも2つの導電性のコンタクト面13が配置されている。これらのコンタクトおよびこれに接続された導体路を介して半導体素子5に電気信号または電気エネルギーが供給される。したがって、半導体素子5の電気コンタクト7は半導体ベースの素子が実装された状態で接続される。半導体ベースの素子および収容部は上下に重ね合わされ、これにより、半導体素子5の電気コンタクト7は収容部の電気コンタクト面13と協働して機能する。収容部には、半導体ベースの素子の実装用基部10と協働する基部収容部14が配置されている。したがって、電気コンタクト面13は収容部の中央に置かれて基部収容部14によって包囲されている。ここで、各実装用基部10は接着プロセスまたははんだ付けプロセスまたはその他の力による接合プロセスによって基部収容部14上に固定される。

40

#### 【0043】

図6には、半導体ベースの素子が収容部に配置されている様子が斜視図で示されている。この図から、各実装用基部10が各基部収容部14の上に配置されることが見て取れる。

#### 【0044】

図7～図12には本発明の第1の実施例の半導体ベースの素子を製造する製造方法の各ステップが示されている。

#### 【0045】

図7には正方形の基本形状を有する透明なガラス基板1が示されている。このガラス基

50

板1の形状は、個々の半導体ベースの素子の形状に応じたものである。特に、半導体素子の横寸法はガラス基板の横寸法に等しい。

【0046】

発光特性を有する半導体ベースの素子を製造する最適な製造方法の前提として、1つのガラスウェハ上の複数のガラス基板を同時に処理することが挙げられる。この場合、ガラスウェハは製造方法のうちあらかじめ定められた部分ステップにおいて個別化され、個々の半導体素子が形成される。本発明の製造方法をより良く理解してもらうために、個々の要素について説明する。

【0047】

図8に示されているように、ガラス基板1から出発して、スパッタリングプロセスまたは蒸着プロセスにより、鏡8を形成する鏡面層がガラス基板1の第1の表面2上に被着される。このステップはフォトリソグラフィプロセスを前提としており、鏡面層によってコーティングされない表面領域が定められる。10

【0048】

続いて、図9に示されているように、ガラス基板1の第1の表面2のうち例えば所定の部分領域の上に、変換層4が被着される。変換層4はプリンティングプロセスまたはスクリーンプリンティングプロセスによって被着される。第1の表面2のうち、鏡8によって覆われていない中央の領域が変換層4によってコーティングされる。鏡8は変換層4によつては覆われない。20

【0049】

続いて、図10に示されているように、例えばフォトリソグラフィプロセスによって支援されるめっきプロセスによって、実装用基部10がガラス基板1の各コーナーに被着される。実装用基部10は例えば鏡8の縁領域に被着される。

【0050】

さらに、図11に示されているように、次のステップにおいて、第2の表面3に光学素子11が設けられる。光学素子11は、ここでは、経時劣化および温度に対して安定となるように、例えばシリコーンから形成される層に埋め込まれる。

【0051】

図12の次のステップでは、半導体素子5が変換層4上に被着される。半導体素子5は薄膜発光ダイオードとして構成されており、電気コンタクト面7を含む。この電気コンタクト面は、当該の半導体素子に電気エネルギーを供給する接続部を形成するものである。さらなるステップにおいて薄膜発光ダイオードがガラス基板1上に配置される。30

【図1】

FIG 1

【図2】

FIG 2

【図3】

FIG 3

【図4】

FIG 4

【図5】

FIG 5

【図7】

FIG 7

【図6】

FIG 6

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(74)代理人 100112793

弁理士 高橋 佳大

(74)代理人 100128679

弁理士 星 公弘

(74)代理人 100135633

弁理士 二宮 浩康

(74)代理人 100114890

弁理士 アインゼル・フェリックス=ラインハルト

(72)発明者 イエルク ゾルク

ドイツ連邦共和国 レーゲンスブルク ゴツラートシュトラーセ 12

(72)発明者 シュテファン グルーバー

ドイツ連邦共和国 バート アブバッハ ヴァイクザー ヴェーク 10

審査官 佐藤 俊彦

(56)参考文献 特開2001-077430 (JP, A)

特開平09-199626 (JP, A)

特表平11-509687 (JP, A)

特開2000-022222 (JP, A)

特開2004-341446 (JP, A)

特開2005-303285 (JP, A)

特開2000-135814 (JP, A)

特開2007-095855 (JP, A)

特開平02-155671 (JP, A)

特開平08-072307 (JP, A)

特開平04-159519 (JP, A)

特開昭63-262259 (JP, A)

Scnitzer et al, "30 % external quantum efficiency from surface textured, thin-film light-emitting diodes", Applied Physics Letters, 1993年 8月 9日, vol.63, no.16, p 2174-2176

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64