(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6170221号

(P6170221)

(45) 発行日 平成29年7月26日(2017.7.26)

(24) 登録日 平成29年7月7日(2017.7.7)

(51) Int.Cl.

H01L 29/786 (2006.01)

F 1

|      |       |      |

|------|-------|------|

| H01L | 29/78 | 616T |

| H01L | 29/78 | 618B |

| H01L | 29/78 | 617K |

| H01L | 29/78 | 618C |

請求項の数 3 (全 23 頁)

(21) 出願番号 特願2016-185090 (P2016-185090)

(22) 出願日 平成28年9月23日 (2016.9.23)

(62) 分割の表示 特願2015-875 (P2015-875) の分割

原出願日 平成22年9月21日 (2010.9.21)

(65) 公開番号 特開2016-213513 (P2016-213513A)

(43) 公開日 平成28年12月15日 (2016.12.15)

審査請求日 平成28年9月26日 (2016.9.26)

(31) 優先権主張番号 特願2009-218816 (P2009-218816)

(32) 優先日 平成21年9月24日 (2009.9.24)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 高橋 圭

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 伊藤 良明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上の第1の導電層と、

前記第1の導電層上の酸化物半導体層と、

前記酸化物半導体層上の、前記第1の導電層と重畳しない領域を有する第2の導電層と

、

前記酸化物半導体層上および前記第2の導電層上の絶縁層と、

前記絶縁層上の、前記第1の導電層および前記第2の導電層と重畳しない領域を有する第3の導電層と、

を有し、

前記第1の導電層は、上面からみて前記第2の導電層の外周を囲うように配置された領域を有し、

前記第3の導電層は、上面からみて前記第2の導電層と前記第1の導電層との間に配置された領域を有し、

前記酸化物半導体層は、パターニングされており、

前記酸化物半導体層の端部は、上面からみて前記第1の導電層の外周よりも内側に配置され、且つ、前記第2の導電層の外周よりも外側に配置されていることを特徴とする半導体装置。

## 【請求項 2】

基板上の第1の導電層と、

10

20

前記第1の導電層上の酸化物半導体層と、

前記酸化物半導体層上の、前記第1の導電層と重畠しない領域を有する第2の導電層と

、前記酸化物半導体層上および前記第2の導電層上の絶縁層と、

前記絶縁層上の、前記第1の導電層および前記第2の導電層と重畠しない領域を有する第3の導電層と、

を有し、

前記第1の導電層は、上面からみて前記第2の導電層の外周を囲うように配置された領域を有し、

前記第3の導電層は、上面からみて前記第2の導電層と前記第1の導電層との間に配置された領域を有し、

前記酸化物半導体層は、パターニングされており、

前記酸化物半導体層の端部は、上面からみて前記第1の導電層の外周よりも内側に配置され、且つ、前記第3の導電層の外周よりも外側に配置されていることを特徴とする半導体装置。

【請求項3】

請求項1又は2において、

前記第1の導電層はソース電極またはドレイン電極の一方としての機能を有し、

前記第2の導電層はソース電極またはドレイン電極の他方としての機能を有し、

前記第3の導電層はゲート電極としての機能を有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

開示する発明の技術分野は、半導体装置およびその作製方法に関するものである。

【背景技術】

【0002】

金属酸化物は多様に存在し、さまざまな用途に用いられている。酸化インジウムはよく知られた材料であり、液晶ディスプレイなどで必要とされる透明電極材料として用いられている。

【0003】

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては、例えば、酸化タンクステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このような金属酸化物をチャネル形成領域に用いた薄膜トランジスタが既に知られている（例えば、特許文献1乃至特許文献4、非特許文献1等参照）。

【0004】

ところで、金属酸化物には、一元系酸化物のみでなく多元系酸化物も知られている。例えば、ホモガス相を有する  $In_xGa_3(ZnO)_m$  (m:自然数) は、In、GaおよびZnを有する多元系酸化物半導体として知られている（例えば、非特許文献2乃至非特許文献4等参照）。

【0005】

そして、上記のような  $In_xGa_3(ZnO)_m$  系酸化物で構成される酸化物半導体も、薄膜トランジスタのチャネル形成領域に適用可能であることが確認されている（例えば、特許文献5、非特許文献5および非特許文献6等参照）。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭60-198861号公報

【特許文献2】特開平8-264794号公報

【特許文献3】特表平11-505377号公報

【特許文献4】特開2000-150900号公報

10

20

30

40

50

【特許文献 5】特開 2004-103957 号公報

【非特許文献】

【0007】

【非特許文献 1】M. W. Prins, K. O. Grosse-Holz, G. Muller, J. F. M. Cilleissen, J. B. Giesbers, R. P. Weening, and R. M. Wolf、「A ferroelectric transparent thin-film transistor」、Appl. Phys. Lett.、17 June 1996、Vol. 68 p. 3650-3652

【非特許文献 2】M. Nakamura, N. Kimizuka, and T. Mohri、「The Phase Relations in the  $In_2O_3$ - $Ga_2ZnO_4$ -ZnO System at 1350」、J. Solid State Chem.、1991、Vol. 93, p. 298-315 10

【非特許文献 3】N. Kimizuka, M. Isobe, and M. Nakamura、「Syntheses and Single-Crystal Data of Homologous Compounds,  $In_2O_3(ZnO)_m$  ( $m = 3, 4$ , and  $5$ ),  $InGaO_3(ZnO)_3$ , and  $Ga_2O_3(ZnO)_m$  ( $m = 7, 8, 9$ , and  $16$ ) in the  $In_2O_3$ - $ZnGa_2O_4$ -ZnO System」、J. Solid State Chem.、1995、Vol. 116, p. 170-178 20

【非特許文献 4】中村真佐樹、君塚昇、毛利尚彦、磯部光正、「ホモロガス相、 $InFeO_3$  ( $ZnO$ ) $m$  ( $m$  : 自然数) とその同型化合物の合成および結晶構造」、固体物理、1993年、Vol. 28、No. 5、p. 317-327

【非特許文献 5】K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono、「Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor」、SCIENCE、2003、Vol. 300、p. 1269-1272

【非特許文献 6】K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono、「Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors」、NATURE、2004、Vol. 432 p. 488-492 30

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところで、パワー MOSFETなどの大電力用途の半導体装置には、高耐圧、高変換効率、高速スイッチングなどの特性が必要となる。現在、これらの半導体装置の半導体材料としてはシリコンが採用されているが、上述の観点から、さらなる特性の向上が可能な新たな半導体材料が求められている。 40

【0009】

上述の諸特性を向上させる可能性がある半導体材料としては、例えば、炭化シリコンを挙げることができる。炭化シリコンは、Si-C結合の原子間距離が約0.18nmと短く、結合エネルギーが高く、シリコンと比較して約3倍と大きなエネルギー・ギャップを有するため、半導体装置の耐圧向上、電力損失の低減などに有利であることが知られている。

【0010】

ところが、炭化シリコンは、その性質上溶融させることができないため、シリコンウェハを製造する際に用いられるチョクラルスキー法 (CZ法) などの生産性の高い方法を用いて製造することができないという問題がある。また、炭化シリコンには、マイクロパイ 50

プと呼ばれる欠陥の問題が存在する。これらの問題から、炭化シリコンを用いた半導体装置の実用化は遅れている。

【0011】

上述に鑑み、開示する発明の一態様では、生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。または、新たな半導体材料を用いた新たな構造の半導体装置を提供することを目的の一とする。または、当該半導体装置を用いた電力用回路を提供することを目的の一とする。または、このような半導体装置の好適な作製方法を提供することを目的の一とする。

【課題を解決するための手段】

【0012】

開示する発明の一態様は、酸化物半導体材料を用いて耐圧（例えばドレイン耐圧）を向上させた半導体装置である。特に、表層部に結晶領域を有する酸化物半導体層を用いた半導体装置である。

【0013】

また、開示する発明の一態様は、上述の半導体装置の作製方法である。

【0014】

例えば、本発明の一態様は、基板上の第1の導電層と、第1の導電層を覆う酸化物半導体層と、酸化物半導体層上の、第1の導電層と重畠しない領域の第2の導電層と、酸化物半導体層および第2の導電層を覆う絶縁層と、絶縁層上の、少なくとも第1の導電層および第2の導電層と重畠しない領域を含む領域の第3の導電層と、を有する半導体装置である。

【0015】

また、本発明の別の一態様は、基板上の第1の導電層と、第1の導電層を覆い、上方の表層部に結晶領域を有する酸化物半導体層と、酸化物半導体層上の、第1の導電層と重畠しない領域の第2の導電層と、酸化物半導体層および第2の導電層を覆う絶縁層と、絶縁層上の、少なくとも第1の導電層および第2の導電層と重畠しない領域を含む領域の第3の導電層と、を有する半導体装置である。

【0016】

また、本発明の別の一態様は、基板上の酸化物半導体層と、酸化物半導体層上の、第1の導電層と、酸化物半導体層上の、第1の導電層と重畠しない領域の第2の導電層と、酸化物半導体層、第1の導電層、および、第2の導電層を覆う絶縁層と、絶縁層上の、少なくとも第1の導電層および第2の導電層と重畠しない領域を含む領域の第3の導電層と、を有する半導体装置である。

【0017】

また、本発明の別の一態様は、基板上の、上方の表層部に結晶領域を有する酸化物半導体層と、酸化物半導体層上の、第1の導電層と、酸化物半導体層上の、第1の導電層と重畠しない領域の第2の導電層と、酸化物半導体層、第1の導電層、および、第2の導電層を覆う絶縁層と、絶縁層上の、少なくとも第1の導電層および第2の導電層と重畠しない領域を含む領域の第3の導電層と、を有する半導体装置である。

【0018】

上記において、酸化物半導体層の結晶領域以外の領域は非晶質とすることが好適である。また、酸化物半導体層の結晶領域は、 $In_2Ga_2ZnO_7$ の結晶を含んでいることが望ましい。また、酸化物半導体層は、 $In-Ga-Zn-O$ 系の酸化物半導体材料を含んでいることが望ましい。

【0019】

また、上記において、第3の導電層は、その一部が第2の導電層と重畠していることが望ましい。また、上記において、第1の導電層はソース電極またはドレイン電極の一方として、第2の導電層はソース電極またはドレイン電極の他方として、第3の導電層はゲート電極として、それぞれ機能させることが可能である。

【0020】

10

20

30

40

50

また、本発明の別の一態様は、上記の半導体装置を有し、半導体装置の第3の導電層に入力されるパルス信号に応じてそのオン状態とオフ状態とを変化させ、これによって出力電圧を変化させる電力用回路である。

【0021】

また、本発明の一態様は、基板上に、第1の導電層を形成し、第1の導電層を覆うように、酸化物半導体層を形成し、酸化物半導体層に熱を加えて、酸化物半導体層の上方の表層部に結晶領域を形成し、酸化物半導体層上の第1の導電層と重畠しない領域に、第2の導電層を形成し、酸化物半導体層および第2の導電層を覆うように、絶縁層を形成し、絶縁層上の、少なくとも第1の導電層および第2の導電層と重畠しない領域を含む領域に、第3の導電層を形成する、半導体装置の作製方法である。

10

【0022】

また、本発明の別の一態様は、基板上に、酸化物半導体層を形成し、酸化物半導体層に熱を加えて、酸化物半導体層の上方の表層部に結晶領域を形成し、酸化物半導体層上に、第1の導電層を形成し、酸化物半導体層上の第1の導電層と重畠しない領域に、第2の導電層を形成し、酸化物半導体層、第1の導電層、および、第2の導電層を覆うように、絶縁層を形成し、絶縁層上の、少なくとも第1の導電層および第2の導電層と重畠しない領域を含む領域に、第3の導電層を形成する、半導体装置の作製方法である。

【0023】

上記において、結晶領域の形成は、酸化物半導体層が500以上となるように熱を加えることにより行なうことが望ましい。また、酸化物半導体層の形成は、In-Ga-Zn-O系のターゲットを用いたスパッタリング法により行なうことが望ましい。

20

【0024】

また、上記において、第3の導電層は、その一部が第2の導電層と重畠するように形成されることが望ましい。

【0025】

なお、本明細書等において、「上」の表現は、直上であることを限定するものではない。例えば、「基板上」と表現する場合には、基板表面から見て上部にあることを意味する。つまり、「上」の表現は、他の構成要素を間に有する構造を含む趣旨で用いる。

【発明の効果】

【0026】

30

開示する発明の一態様では、生産性が高く、エネルギーギャップの大きい酸化物半導体層を用いて半導体装置を形成している。これにより、大電力用に好適な、耐圧（例えばドレイン耐圧等）の高い半導体装置を得ることができる。

【0027】

また、開示する発明の一態様では、表層部に結晶領域を有する酸化物半導体層を用いている。これにより、耐圧をさらに向上させた半導体装置を得ることができる。

【0028】

また、開示する発明の一態様により、上述の半導体装置の好適な作製方法が提供される。

【図面の簡単な説明】

【0029】

40

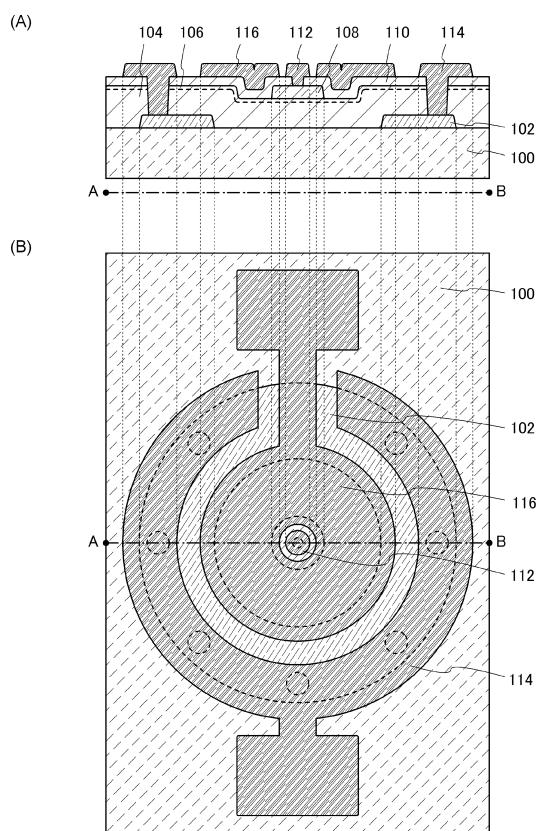

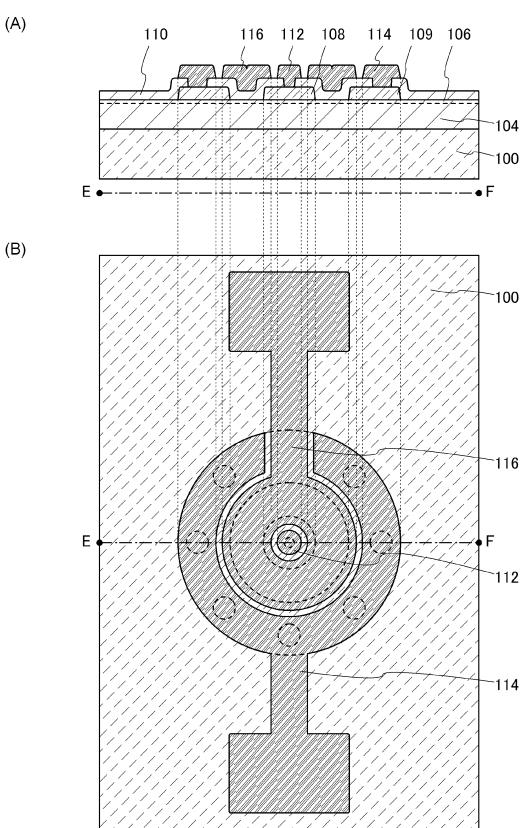

【図1】半導体装置の構成を説明する断面図および平面図である。

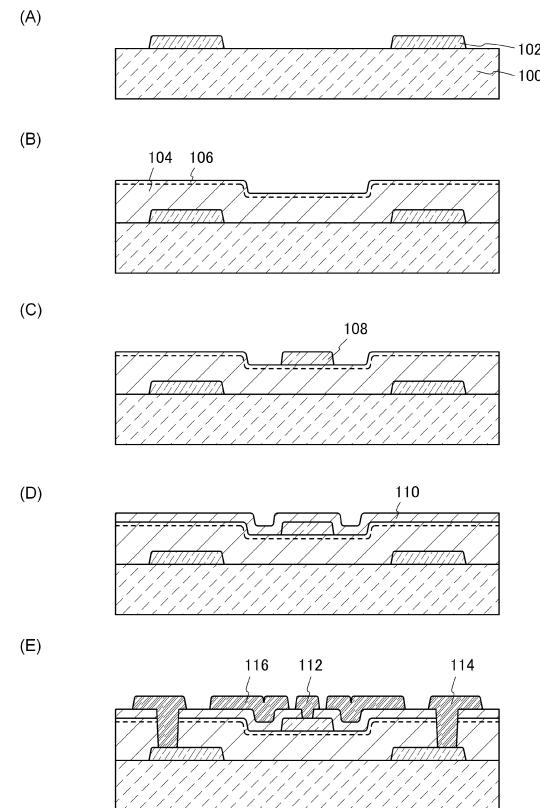

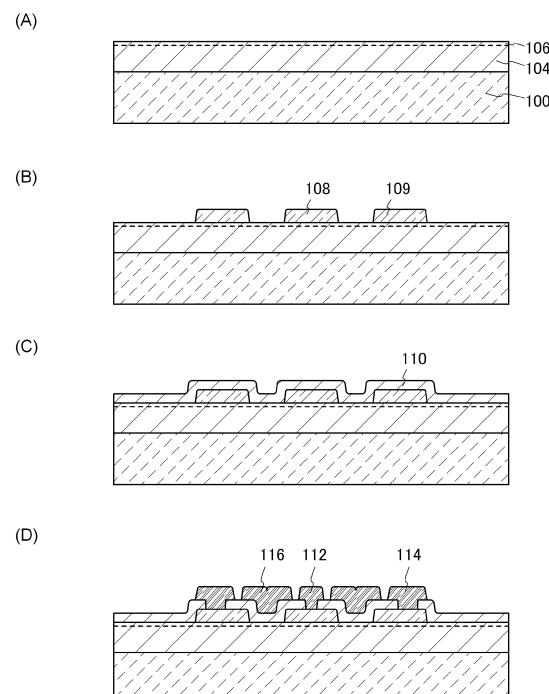

【図2】半導体装置の作製方法について説明する断面図である。

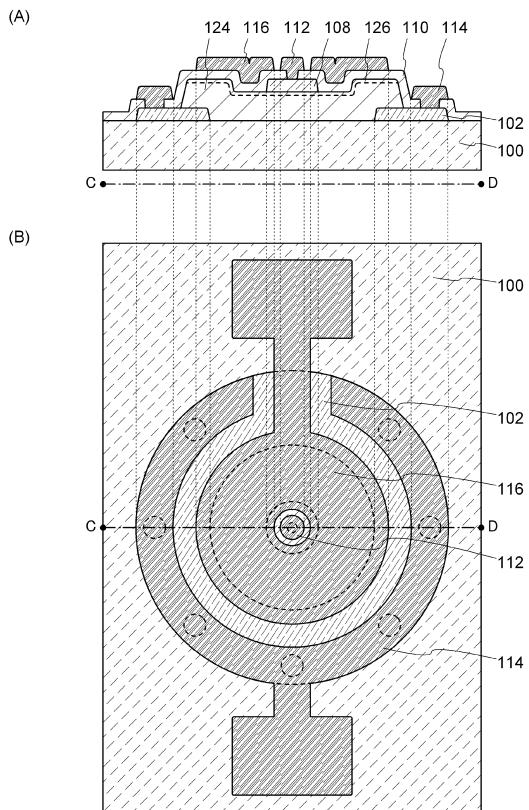

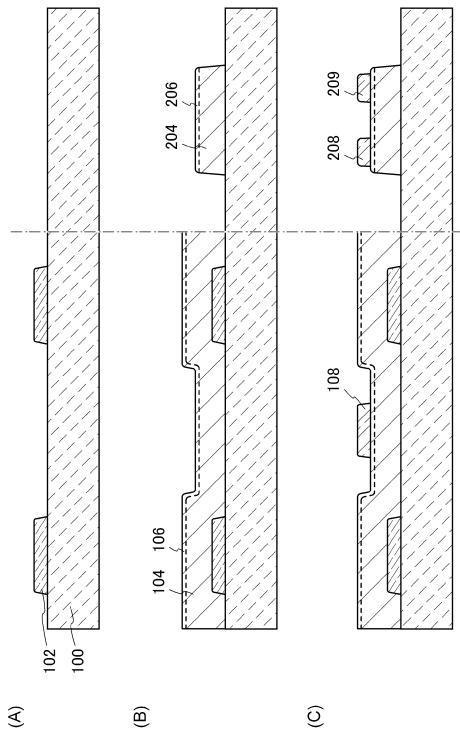

【図3】半導体装置の構成を説明する断面図および平面図である。

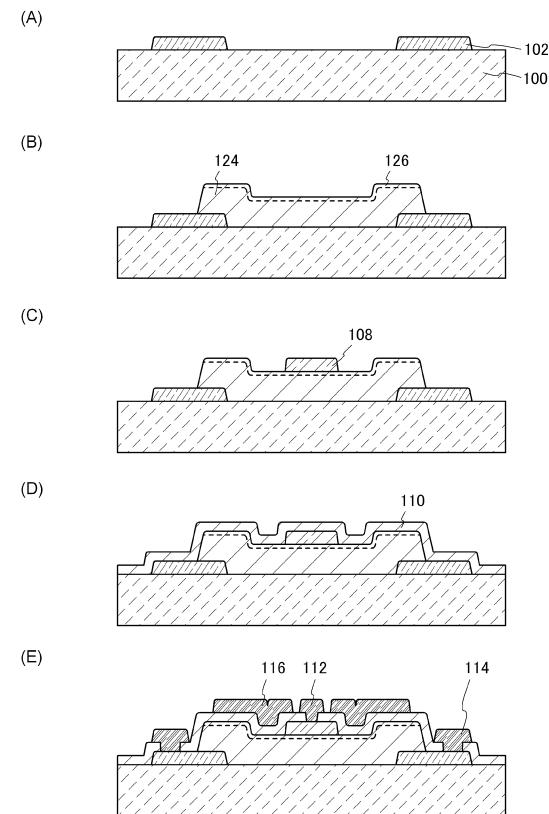

【図4】半導体装置の作製方法について説明する断面図である。

【図5】半導体装置の構成を説明する断面図および平面図である。

【図6】半導体装置の作製方法について説明する断面図である。

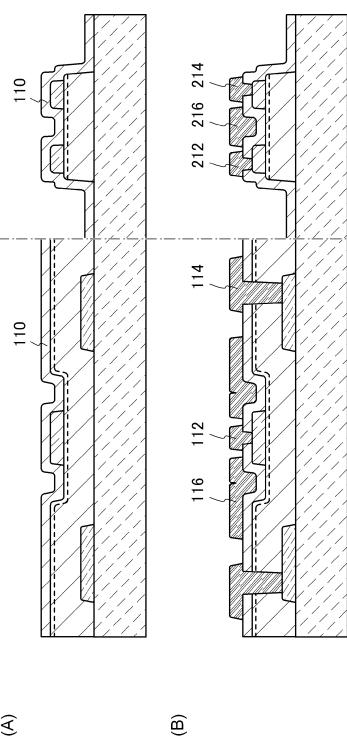

【図7】半導体装置の作製方法について説明する断面図である。

【図8】半導体装置の作製方法について説明する断面図である。

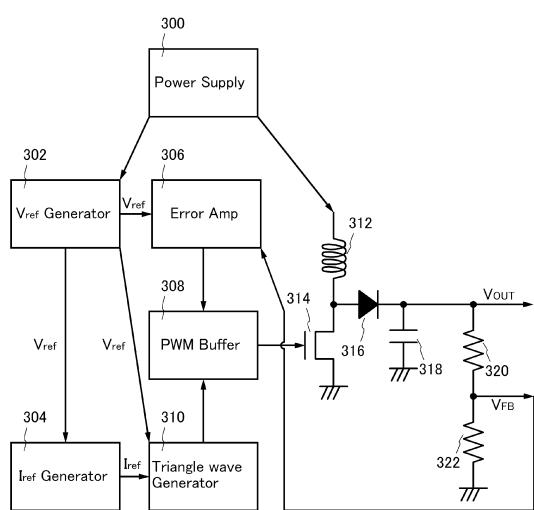

【図9】DC-DCコンバータの構成の一例を示す図である。

【図10】DC-DCコンバータを構成する回路の出力波形の一例を示す図である。

50

【図11】インバータを備えた太陽光発電システムの一例を示す図である。

【発明を実施するための形態】

【0030】

以下、実施の形態について、図面を用いて詳細に説明する。ただし、発明は以下に示す実施の形態の記載内容に限定されず、本明細書等において開示する発明の趣旨から逸脱することなく形態および詳細を様々に変更し得ることは当業者にとって自明である。また、異なる実施の形態に係る構成は、適宜組み合わせて実施することが可能である。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を用い、その繰り返しの説明は省略する。

【0031】

10

(実施の形態1)

本実施の形態では、半導体装置およびその作製方法の一例について、図1および図2を参考して説明する。なお、以下では、半導体装置としてパワーMOS(MIS)FETを例に挙げて説明する。

【0032】

<半導体装置の概略>

図1には、半導体装置の構成の一例を示す。図1(A)は断面図、図1(B)は平面図に相当する。また、図1(A)は、図1(B)のA-B線における断面に対応している。なお、平面図においては、理解の容易のために一部の構成要素を省略している。

【0033】

20

図1に示す半導体装置は、基板100、ソース電極またはドレイン電極の一方として機能する導電層102、酸化物半導体層104、酸化物半導体層104中の結晶領域106、ソース電極またはドレイン電極の他方として機能する導電層108、ゲート絶縁層として機能する絶縁層110、導電層108と電気的に接続される導電層112、導電層102と電気的に接続される導電層114、ゲート電極として機能する導電層116、などを含む。

【0034】

ここで、酸化物半導体層104は、エネルギーギャップの大きい酸化物半導体材料を含む半導体層である。半導体装置にエネルギーギャップの大きい酸化物半導体材料を用いることで、半導体装置の耐圧(例えば、ドレイン耐圧)が向上する。

30

【0035】

結晶領域106は、酸化物半導体層104の表層部(上層)に相当し、酸化物半導体層104の一部が結晶化した領域である。当該結晶領域106を有することで、半導体装置の耐圧(例えば、ドレイン耐圧)をさらに向上させることができる。なお、酸化物半導体層104の結晶領域106以外の領域は、非晶質の領域であることが望ましいが、結晶粒を含む非晶質の領域であっても良いし、微結晶の領域であっても良い。

【0036】

平面的には、ソース電極またはドレイン電極の他方として機能する導電層108や導電層108と電気的に接続される導電層112の周囲に、ゲート電極として機能する導電層116が配置され、さらにその周囲には、ソース電極またはドレイン電極の一方として機能する導電層102や、導電層102と電気的に接続される導電層114が配置される(図1(B)参照)。

40

【0037】

つまり、ソース電極またはドレイン電極の一方として機能する導電層102と、ソース電極またはドレイン電極の他方として機能する導電層108とは、重畠しない。ここで、「重畠しない」とは、平面図において互いに重なる領域を有しないことを言う。本明細書の他の記載においても同様とする。

【0038】

また、ゲート電極として機能する導電層116は、導電層102および導電層108と重畠しない領域を含む領域に設けられる。つまり、導電層116の少なくとも一部は、導電

50

層 102 および導電層 108 とは重畠しない。一方、導電層 116 の他の一部は、導電層 102 または導電層 108 と重畠していても良い。

【0039】

なお、図1では、導電層 108 および導電層 112 を中央に配置し、その周囲に導電層 116、導電層 102、および、導電層 114 を配置する構成としているが、半導体装置のレイアウトはこれに限定されない。各構成要素の配置は、半導体装置の機能を害さない範囲において適宜変更することができる。

【0040】

導電層 108 と電気的に接続される導電層 112 は、外部配線等との電気的接続を実現するための端子として機能するが、導電層 108 と外部配線等とを直接接続することができれば、導電層 112 は形成しなくとも良い。導電層 114 についても同様である。なお、図1においては、導電層 112 と電気的に接続される外部配線等は示していない。

10

【0041】

以下、図1(A)および図1(B)を参照して、本実施の形態に係る半導体装置の構成の詳細について説明する。

【0042】

<基板>

基板 100 としては、絶縁基板、半導体基板、金属基板などが採用される。また、これらの表面を絶縁材料などで被覆した基板を採用することもできる。なお、基板 100 は酸化物半導体層の加熱に耐えうる程度の耐熱性を有することが望ましい。

20

【0043】

絶縁基板には、ガラス基板や石英基板などがある。また、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン樹脂、アクリル樹脂、エポキシ樹脂などの有機材料を含む絶縁基板を採用することもできる。有機材料を含む絶縁基板を採用する場合にはプロセス中の最高温度に耐えうる絶縁基板を選択することが求められる。

【0044】

半導体基板の代表例は、シリコン基板(シリコンウェハ)である。シリコン基板のグレードには複数あるが、表面がある程度平坦なものであれば、廉価なものを用いても良い。例えば、純度 6N (99.9999%) ~ 7N (99.99999%) 程度のシリコン基板を適用することもできる。

30

【0045】

金属基板は、アルミニウム基板や銅基板が代表的である。これらの金属基板を用いる場合には、絶縁性を確保するために、表面に絶縁層を形成しても良い。金属基板は熱伝導性が高いため、発熱量の大きいパワーMOSFETなどの大電力用半導体装置の基板として好適である。

【0046】

<酸化物半導体層>

酸化物半導体層 104 を構成する半導体材料の一例としては、 $InMO_3 (ZnO)_m$  ( $m > 0$ ) で表記されるものがある。ここで、Mは、ガリウム(Ga)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)、コバルト(Co)などから選ばれた一の金属元素または複数の金属元素を示す。例えば、Mとして Ga が選択される場合には、Gaのみの場合の他に、Ga と Ni や、Ga と Fe など、Ga 以外の上記金属元素が選択される場合を含む。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素として Fe、Ni その他の遷移金属元素、または該遷移金属の酸化物が含まれているものがある。本明細書等においては、上記酸化物半導体のうち、Mとして少なくともガリウムを含むものを In-Ga-Zn-O 系酸化物半導体と呼ぶこととする。

40

【0047】

上記 In-Ga-Zn-O 系の酸化物半導体材料は、無電界時の抵抗が十分に高く、オフ電流を十分に小さくすることができ、また、エネルギーギャップが大きい(ワイドギャップである)ため、パワーMOSFETなどの大電力用半導体装置には好適である。

50

## 【0048】

なお、酸化物半導体層104を構成する半導体材料の別の例としては、例えば、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体材料などがある。

## 【0049】

酸化物半導体層104（結晶領域106を除く）は、非晶質構造であることが望ましいが、非晶質構造中に結晶粒を含む構造や、微結晶構造などであっても良い。また、その厚さは、目的とする耐圧などの特性に応じて適宜設定することができる。具体的には、例えば、100nm乃至10μm程度とすることができる。

10

## 【0050】

結晶領域106は、結晶粒が配列した構造を有するのが好適である。例えば、In-Ga-Zn-O系の酸化物半導体材料を用いて酸化物半導体層104を形成する場合には、結晶領域106は、 $In_2Ga_2ZnO_7$ の結晶粒が所定の方向に配列した領域とする。中でも、 $In_2Ga_2ZnO_7$ 結晶のc軸が基板平面（または、酸化物半導体層表面）に対して垂直な方向となるように結晶粒を配列させる場合には、半導体装置の耐圧を大きく向上させることができると好適である。すなわち、c軸方向と比較して、b軸方向（またはa軸方向）は、より高い耐圧を有すると言えることができる。これは、 $In_2Ga_2ZnO_7$ の誘電率の異方性に起因するものと考察される。なお、 $In_2Ga_2ZnO_7$ の結晶は、a軸(a-axis)およびb軸(b-axis)に平行なレイヤーの積層構造を含むように構成される。つまり、 $In_2Ga_2ZnO_7$ のc軸とは、 $In_2Ga_2ZnO_7$ の結晶を構成するレイヤーに垂直な方向をいう。

20

## 【0051】

なお、上記半導体装置において、結晶領域106は必須の構成要素ではない。酸化物半導体材料を用いることで十分な耐圧を確保できる場合には、結晶領域106を設けなくとも良い。

## 【0052】

## &lt;絶縁層&gt;

ゲート絶縁層として機能する絶縁層110を構成する絶縁材料は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化タンタルなどから選択することが可能である。また、これらの材料の複合材料を採用しても良い。絶縁層110は、これらの絶縁材料を用いた層の単層構造としても良いし、積層構造としても良い。なお、一般にMOSFETとは、金属-酸化物-半導体による電界効果型トランジスタを言うが、開示する発明の半導体装置に用いる絶縁層を、酸化物に限定する必要はない。

30

## 【0053】

なお、本明細書等において、酸化窒化物とは、その組成において、窒素よりも酸素の含有量（原子数）が多いものを示し、例えば、酸化窒化シリコンとは、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、シリコンが25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれるものと定義する。また、窒化酸化物とは、その組成において、酸素よりも窒素の含有量（原子数）が多いものを示し、例えば、窒化酸化シリコンとは、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、シリコンが25原子%以上35原子%以下、水素が10原子%以上25原子%以下の範囲で含まれるものと定義する。但し、上記範囲は、ラザフォード後方散乱法（RBS: Rutherford Backscattering Spectrometry）や、水素前方散乱法（HFS: Hydrogen Forward scattering Spectrometry）を用いて測定した場合のものである。また、構成元素の含有比率の合計は100原子%を超えない。

40

## 【0054】

## &lt;導電層&gt;

50

導電層 102 は、例えば、ドレイン電極として機能し、導電層 108 は、ソース電極として機能し、導電層 116 は、ゲート電極として機能する。導電層 112 および導電層 114 は、外部配線等との電気的接続を実現するための端子として機能するが、これらは必須の構成要素ではない。

【0055】

上記の導電層を構成する導電材料は、アルミニウム、銅、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウムなどの金属材料、またはこれらの金属材料を主成分とする合金材料、またはこれらの金属材料を成分とする窒化物などから選択することができる。他にも、酸化インジウム、酸化インジウム酸化スズ合金、酸化インジウム酸化亜鉛合金、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどの透光性を有する酸化物導電材料などを採用することが可能である。導電層は、これらの導電材料を用いた層の単層構造としても良いし、積層構造としても良い。

10

【0056】

ソース電極として機能する導電層 108 は、酸化物半導体層 104 と、その上方で接しており、ドレイン電極として機能する導電層 102 は、酸化物半導体層 104 と、その下方で接している。また、ゲート電極として機能する導電層 116 は、絶縁層 110 上に設けられており、酸化物半導体層 104 中に電界を生じさせる。

【0057】

なお、ソースおよびドレインの別は便宜的なものに過ぎず、半導体装置を構成する各構成要素の機能が上記称呼に限定して解釈されるものではない。ソースおよびドレインの機能は、半導体装置の動作に従って入れ替わることがあるためである。

20

【0058】

以下、本実施の形態に係る半導体装置の動作について簡単に説明する。

【0059】

<半導体装置の動作>

電子をキャリアとする n 型半導体装置の場合、通常動作時には、ソース電極として機能する導電層 108 が負にバイアスされ、ドレイン電極として機能する導電層 102 が正にバイアスされる。

【0060】

ソース電極として機能する導電層 108 と、ドレイン電極として機能する導電層 102 との間には、十分な厚さの酸化物半導体層 104 が介在している。また、酸化物半導体層 104 は、ワイドギャップかつ無電界時の抵抗が十分に高い酸化物半導体材料で構成されている。このため、導電層 108 が負にバイアスされ、導電層 102 が正にバイアスされた状態において、ゲート電極として機能する導電層 116 にバイアスを印加しない場合、または、負バイアスを印加する場合には、ごく僅かな電流しか流れない。

30

【0061】

ゲート電極として機能する導電層 116 に正バイアスを印加すると、酸化物半導体層 104 の、導電層 116 と重なる領域の絶縁層 110 との界面付近に負の電荷（電子）が誘起されてチャネルが形成される。これにより、ソース電極として機能する導電層 108 とドレイン電極として機能する導電層 102 との間に電流が流れる。

40

【0062】

開示する発明の一態様では、半導体材料として酸化物半導体を用いているため、半導体装置の耐圧（ドレイン耐圧等）を向上させることができる。これは、酸化物半導体のエネルギーギャップが、一般的な半導体材料のエネルギーギャップと比較して大きいことによる。

【0063】

また、結晶粒が所定の方向に配列した結晶領域 106 を有することにより、さらに半導体装置の耐圧を高めることができる。例えば、酸化物半導体層 104 に  $In - Ga - Zn - O$  系の酸化物半導体材料を用いる場合、 $In_2Ga_2ZnO_7$  の c 軸が基板平面（または、酸化物半導体層表面）に対して垂直な方向となるように結晶粒を配列させることにより

50

、半導体装置の耐圧を高めることができる。

【0064】

<作製工程>

図1に示した半導体装置の作製工程について、図2を用いて説明する。

【0065】

まず、基板100上に導電層102を形成する(図2(A)参照)。基板100の詳細に

10

関しては、上記<基板>の項を参照できる。

【0066】

導電層102は、上記<導電層>の項で示した導電材料を含む導電膜を、スパッタリング

10

法や真空蒸着法などの方法で基板100上に形成した後、フォトリソグラフィ法によるレジストマスクを用いたエッチング処理によって不要な部分を除去することで形成される。エッチング処理は、ウェット処理としても良いし、ドライ処理としても良い。なお、導電層102上に形成される各構成要素の被覆性を向上させるため、当該エッチング処理は、導電層102の側面と、導電層102の底面とのなす角が、鋭角となるように行なうことが望ましい。

【0067】

導電層102を、低抵抗導電材料であるアルミニウムや銅などでなる層と、高融点導電材料であるモリブデン、チタン、クロム、タンタル、タンゲステン、ネオジム、スカンジウムなどでなる層の積層構造とする場合には、導電性と耐熱性とを両立させることができ

20

ため好適である。例えば、アルミニウムとモリブデンの二層構造、銅とモリブデンの二層構造、銅と窒化チタンの二層構造、銅と窒化タンタルの二層構造、窒化チタンとモリブデンの二層構造などを適用することができる。また、アルミニウム、アルミニウムとシリコンの合金、アルミニウムとチタンの合金、アルミニウムとネオジムの合金などを、タンゲステン、窒化タンゲステン、窒化チタン、チタンなどで挟んだ構造の三層構造を適用することもできる。

【0068】

次に、導電層102を覆うように、結晶領域106を含む酸化物半導体層104を形成する(図2(B)参照)。なお、結晶領域106を有しない酸化物半導体層104を形成しても良い。

【0069】

酸化物半導体層104は、上記<酸化物半導体層>の項で示した酸化物半導体材料を用いて形成される。また、酸化物半導体層104は、アルゴンをはじめとする希ガス雰囲気下、酸素雰囲気下、希ガスと酸素の混合雰囲気下におけるスパッタリング法などにより形成することができる。スパッタリング法において、 $SiO_2$ を2重量%以上10重量%以下含むターゲットを用いることにより、酸化物半導体層104中に $SiO_x$ ( $X > 0$ )を含ませて酸化物半導体層104の結晶化を抑制することができる。当該方法は、非晶質構造の酸化物半導体層104を得たい場合に有効である。

【0070】

例えば、In、Ga、およびZnを含む酸化物半導体成膜用ターゲット(In:Ga:Zn = 1:1:0.5 [atom%]、In:Ga:Zn = 1:1:1 [atom%]、In:Ga:Zn = 1:1:2 [atom%]の組成比を有するターゲットなど)を用い、基板とターゲットとの間の距離を100mm、圧力を0.6Pa、直流電力を0.5kW、雰囲気を酸素(酸素流量比率100%)雰囲気とすることで、酸化物半導体層104として、In-Ga-Zn-O系の非晶質酸化物半導体層を得ることができる。なお、電源としてパルス直流電源を用いる場合には、成膜時のごみを低減することができる、また、膜厚分布を均一化することができるため好適である。

【0071】

酸化物半導体層104の厚さは、上記<酸化物半導体層>の項で説明したように、目的とする耐圧などの特性に応じて適宜設定することができる。例えば、100nm乃至10μm程度とすればよい。

10

20

30

40

50

## 【0072】

結晶領域106は、酸化物半導体層104を形成した後の熱処理によって形成される。なお、当該熱処理によって、酸化物半導体層104中のH<sub>2</sub>、H、OHなどが脱離するため、当該熱処理を脱水化処理または脱水素化処理と呼んでも良い。

## 【0073】

上記熱処理には、高温の不活性ガス（窒素や希ガスなど）を用いたRTA（Rapid Thermal Anneal）処理を適用することができる。ここで、熱処理の温度は500以上とすることが好適である。熱処理温度の上限は特に限定しないが、基板100の耐熱温度の範囲内とする必要がある。また、熱処理の時間は、1分以上10分以下とすることが好適である。例えば、650で3分～6分程度のRTA処理を行うと良い。上述のようなRTA処理を適用することで、短時間に熱処理を行うことができるため、基板100に対する熱の影響を小さくすることができる。つまり、熱処理を長時間行う場合と比較して、熱処理温度の上限を引き上げることが可能である。なお、当該熱処理は、上記のタイミングで行うことには限らず、他の工程の前後などにおいて行うこともできる。また、当該熱処理は、一回に限らず、複数回行っても良い。

10

## 【0074】

また、上記熱処理において、処理雰囲気中には、水素（水を含む）などが含まれないことが望ましい。例えば、熱処理装置に導入する不活性ガスの純度を、6N（99.9999%、即ち不純物濃度が1ppm以下）以上、好ましくは、7N（99.99999%、即ち不純物濃度が0.1ppm以下）以上とする。

20

## 【0075】

上記熱処理によって、酸化物半導体層104の表層部は結晶化し、結晶粒が配列された構成の結晶領域106が形成される。酸化物半導体層104のその他の領域は、非晶質構造、非晶質と微結晶が混合した構造、または微結晶構造のいずれかとなる。なお、結晶領域106は酸化物半導体層104の一部であり、酸化物半導体層104には、結晶領域106が含まれる。

## 【0076】

なお、上記熱処理の後には、酸化物半導体層104中に水素（水を含む）を混入させないことが重要である。このためには、少なくとも、熱処理およびその後の降温過程において、大気暴露しないことが必要になる。これは、例えば、熱処理およびその後の降温過程を同一雰囲気において行うことで実現される。もちろん、降温過程の雰囲気を熱処理雰囲気と異ならせててもよい。この場合、降温過程の雰囲気を、例えば、酸素ガス、N<sub>2</sub>Oガス、超乾燥エア（露点が-40以下、好ましくは-60以下）などの雰囲気とすることができます。

30

## 【0077】

次に、酸化物半導体層104上の導電層102と重畠しない領域に、導電層108を形成する（図2（C）参照）。

## 【0078】

導電層108は、導電層102と同様に形成することができる。すなわち、導電層108は、スパッタリング法や真空蒸着法などの方法で導電膜を形成した後、レジストマスクを用いたエッチング処理によって不要な部分を除去することで形成される。エッチング処理は、ウェット処理としても良いし、ドライ処理としても良いが、酸化物半導体層104の表層部に結晶領域106を形成した場合には、当該結晶領域106がエッチング処理によって除去されないようにする必要がある。

40

## 【0079】

例えば、導電層108にチタンなどの導電材料を用いる場合には、過酸化水素水や加熱塩酸をエッチャントに用いたウェットエッチング処理を適用すると良い。このように、酸化物半導体材料に対する導電層108を構成する導電材料のエッチング選択性が十分に高い条件でエッチング処理を行うことで、表層部の結晶領域106を残存させることができる。

50

## 【0080】

次に、酸化物半導体層104および導電層108を覆うように、絶縁層110を形成する（図2（D）参照）。

## 【0081】

絶縁層110は、上記＜絶縁層＞の項で示した絶縁材料などを用いて形成することができる。形成方法としては、CVD法（プラズマCVD法を含む）、スパッタリング法などがある。なお、絶縁層110の厚さは、半導体装置の特性に応じて適宜設定することができるが、10nm以上1μm以下とするのが好適である。

## 【0082】

その後、絶縁層110を選択的に除去して、導電層102または導電層108に達する開口を形成した後に、導電層108と電気的に接続する導電層112、導電層102と電気的に接続する導電層114、および、導電層116を形成する（図2（E）参照）。

10

## 【0083】

絶縁層110の除去は、レジストマスクを用いたエッチング処理によって行うことができる。エッチング処理は、ウェット処理としても良いし、ドライ処理としても良い。

## 【0084】

導電層112、導電層114、および、導電層116は、他の導電層などと同様に形成することができる。すなわち、導電層112、導電層114、および、導電層116は、スパッタリング法や真空蒸着法などの方法で導電膜を形成した後、レジストマスクを用いたエッチング処理によって不要な部分を除去することで形成される。エッチング処理は、ウェット処理としても良いし、ドライ処理としても良い。

20

## 【0085】

以上により、いわゆるパワーMOSFETと呼ばれる半導体装置を作製することができる。本実施の形態で示したように、半導体層に酸化物半導体材料を用いることで、半導体装置の耐圧向上などが実現される。特に、結晶領域を有する酸化物半導体層を用いることで、半導体装置の耐圧を一層向上させることができる。また、酸化物半導体層は、スパッタリング法などの生産性の高い方法を用いて形成されるため、半導体装置の生産性を高め、製造コストを抑制することができる。

## 【0086】

本実施の形態に示す構成、方法などは、他の実施の形態と適宜組み合わせて用いることができる。

30

## 【0087】

## （実施の形態2）

本実施の形態では、半導体装置およびその作製方法の別の一例について、図3および図4を参照して説明する。なお、本実施の形態において説明する半導体装置は、多くの点で先の実施の形態に係る半導体装置と共通している。このため、共通する部分については省略し、主として相違点について説明する。

## 【0088】

## &lt;半導体装置の概略&gt;

図3には、半導体装置の構成の別の一例を示す。図3（A）は断面図、図3（B）は平面図に相当する。また、図3（A）は、図3（B）のC-D線における断面に対応している。

40

## 【0089】

図3に示す半導体装置の構成要素は、図1に示す半導体装置と同様である。つまり、基板100、ソース電極またはドレイン電極の一方として機能する導電層102、酸化物半導体層124、酸化物半導体層124中の結晶領域126、ソース電極またはドレイン電極の他方として機能する導電層108、ゲート絶縁層として機能する絶縁層110、導電層108と電気的に接続される導電層112、導電層102と電気的に接続される導電層114、ゲート電極として機能する導電層116、などを含む。

## 【0090】

50

図1に示す半導体装置との相違点は、酸化物半導体層104がパターニングされている点である。当該構成を採用する場合であっても、図1に示す半導体装置と同様に動作し、同様の効果を得ることができる。

#### 【0091】

<作製工程>

半導体装置の作製工程も、基本的には図2に示すものと同様である。以下、図4を参照して簡単に説明する。

#### 【0092】

まず、基板100上に導電層102を形成する(図4(A)参照)。詳細については、先の実施の形態を参酌できる。

10

#### 【0093】

次に、導電層102の一部を覆うように、結晶領域126を含む酸化物半導体層124を形成する(図4(B)参照)。酸化物半導体層124の形成方法は、先の実施の形態と同様であるが、本実施の形態における酸化物半導体層124は、導電層102の一部を覆う態様で形成されている点において、先の実施の形態に係る酸化物半導体層104とは異なっている。

#### 【0094】

本実施の形態における酸化物半導体層124は、先の実施の形態に示す方法などに従って酸化物半導体層104(結晶領域106を含む)を形成した後に、当該酸化物半導体層104をパターニングすることで得ることができる。パターニングは、レジストマスクを用いたエッチング処理によって行うことが可能である。エッチング処理は、ウェット処理としても良いし、ドライ処理としても良いが、結晶領域126が残存する態様で行うのが好適である。

20

#### 【0095】

次に、酸化物半導体層124上の導電層102と重畠しない領域に、導電層108を形成する(図4(C)参照)。詳細については、先の実施の形態を参酌できる。

#### 【0096】

次に、酸化物半導体層124および導電層108を覆うように、絶縁層110を形成する(図4(D)参照)。絶縁層110の詳細についても、先の実施の形態を参酌できる。

30

#### 【0097】

その後、絶縁層110を選択的に除去して、導電層102または導電層108に達する開口を形成した後に、導電層108と電気的に接続する導電層112、導電層102と電気的に接続する導電層114、および、導電層116を形成する(図4(E)参照)。詳細については、先の実施の形態を参酌できる。

#### 【0098】

以上により、いわゆるパワーMOSFETと呼ばれる半導体装置を作製することができる。本実施の形態に示す構成、方法などは、他の実施の形態と適宜組み合わせて用いることができる。

#### 【0099】

(実施の形態3)

40

本実施の形態では、半導体装置およびその作製方法の別の一例について、図5および図6を参照して説明する。なお、本実施の形態において説明する半導体装置は、多くの点で先の実施の形態に係る半導体装置と共通している。このため、共通する部分については省略し、主として相違点について説明する。

#### 【0100】

<半導体装置の概略>

図5には、半導体装置の構成の別の一例を示す。図5(A)は断面図、図5(B)は平面図に相当する。また、図5(A)は、図5(B)のE-F線における断面に対応している。

#### 【0101】

50

図5に示す半導体装置は、先の実施の形態に示す半導体装置における導電層102を、導電層109に置き換えたものに相当する。すなわち、図5に示す半導体装置は、基板100、酸化物半導体層104、酸化物半導体層104中の結晶領域106、ソース電極またはドレイン電極の一方として機能する導電層109、ソース電極またはドレイン電極の他方として機能する導電層108、ゲート絶縁層として機能する絶縁層110、導電層108と電気的に接続される導電層112、導電層109と電気的に接続される導電層114、ゲート電極として機能する導電層116、などを含む。

#### 【0102】

導電層109は、導電層108と同一の層で形成される。導電層102を導電層109で置き換えたことにより、すべての導電層が酸化物半導体層104上に設けられることになる。また、これにより、酸化物半導体層104表面の平坦性が向上する。

10

#### 【0103】

当該構成を採用する場合には、先の実施の形態において示す半導体装置とは異なり、酸化物半導体層104の表層部、すなわち、結晶領域106にのみキャリアが流れる。本実施の形態が示す半導体装置は、結晶粒が所定の方向に配列した結晶領域106を有することにより、さらに半導体装置の耐圧を高めることができる。例えば、酸化物半導体層104に $In - Ga - Zn - O$ 系の酸化物半導体材料を用いる場合、 $In_2Ga_2ZnO_7$ のc軸が基板平面（または、酸化物半導体層表面）に対して垂直な方向となるように結晶粒を配列させることにより、半導体装置における電流の方向が $In_2Ga_2ZnO_7$ のb軸方向（またはa軸方向）となる。このため、結晶領域106に起因する半導体装置の耐圧を高める効果はより顕著なものとなる。

20

#### 【0104】

##### <作製工程>

作製工程は、導電層102を形成しない点、導電層108と同様の工程で導電層109を形成する点、を除き図2や図4に示すものと同様である。以下、図6を参照して簡単に説明する。

#### 【0105】

まず、基板100上に酸化物半導体層104を形成する（図6（A）参照）。酸化物半導体層104の形成等に関する詳細については、先の実施の形態を参照できる。

30

#### 【0106】

次に、酸化物半導体層104上に導電層108および導電層109を形成する（図6（B）参照）。導電層109は導電層108と同様に形成することができる。ここで、導電層108および導電層109は、分離された状態で形成する点に留意すべきである。導電層108の形成等に関する詳細については、先の実施の形態を参照できる。

#### 【0107】

次に、酸化物半導体層104、導電層108、導電層109を覆うように、絶縁層110を形成する（図6（C）参照）。絶縁層110の詳細についても、先の実施の形態を参照できる。

#### 【0108】

その後、絶縁層110を選択的に除去して、導電層108または導電層109に達する開口を形成した後に、導電層108と電気的に接続する導電層112、導電層109と電気的に接続する導電層114、および、導電層116を形成する（図6（D）参照）。詳細については、先の実施の形態を参照できる。

40

#### 【0109】

以上により、いわゆるパワーMOSFETと呼ばれる半導体装置を作製することができる。本実施の形態に示す構成、方法などは、他の実施の形態と適宜組み合わせて用いることができる。

#### 【0110】

##### （実施の形態4）

本実施の形態では、いわゆるパワーMOSFETと、薄膜トランジスタとを、同一の基板

50

上に同様の工程で作製する方法の一例について、図7および図8を参照して説明する。なお、以下では、パワーMOSFETとして、図1に示す半導体装置を形成する場合を例に挙げて説明する。

【0111】

本実施の形態に示す半導体装置の作製工程は、図2に、薄膜トランジスタの作製工程が付加されたものに相当する。つまり、基本的な作製工程は図2に示すものと同様である。なお、パワーMOSFETと薄膜トランジスタとでは、要求される特性が異なるのが一般的であり、その大きさなどは要求に応じて適宜設定することが望ましい。この点、図7および図8においてはパワーMOSFETと薄膜トランジスタを同程度の大きさで示しているが、これは理解の容易のためであり、現実の大きさの関係を規定するものではない。

10

【0112】

まず、基板100上に導電層102を形成する(図7(A)参照)。詳細については、先の実施の形態を参酌できる。

【0113】

次に、導電層102を覆うように、結晶領域106を含む酸化物半導体層104を形成すると共に、薄膜トランジスタの構成要素である、結晶領域206を含む酸化物半導体層204を形成する(図7(B)参照)。酸化物半導体層104および酸化物半導体層204は、先の実施の形態に示す方法などに従って酸化物半導体層(結晶領域を含む)を形成した後に、当該酸化物半導体層をパターニングすることで得られる。パターニングは、レジストマスクを用いたエッチング処理によって行うことが可能である。エッチング処理は、ウェット処理としても良いし、ドライ処理としても良いが、結晶領域が残存する態様で行うのが好適である。

20

【0114】

次に、酸化物半導体層104上の導電層102と重畠しない領域に導電層108を形成すると共に、酸化物半導体層204上に導電層208および導電層209を形成する(図7(C)参照)。ここで、導電層208は薄膜トランジスタのソース電極またはドレイン電極の一方として、導電層209は薄膜トランジスタのソース電極またはドレイン電極の他方として機能する。導電層208および導電層209の作製工程は、導電層108の作製工程と同様である。導電層108の作製工程の詳細は、先の実施の形態を参酌できる。

30

【0115】

次に、酸化物半導体層104、導電層108、酸化物半導体層204、導電層208、および導電層209を覆うように、絶縁層110を形成する(図8(A)参照)。絶縁層110は、薄膜トランジスタのゲート絶縁層としても機能する。絶縁層110の作製工程の詳細は、先の実施の形態を参酌できる。

【0116】

その後、絶縁層110を選択的に除去して、導電層102、導電層108、導電層208、または導電層209に達する開口を形成した後に、導電層108と電気的に接続する導電層112、導電層102と電気的に接続する導電層114、導電層116、導電層208と電気的に接続する導電層212、導電層209と電気的に接続する導電層214、導電層216、を形成する(図8(B)参照)。導電層212、導電層214、導電層216の作製工程は、導電層112、導電層114、導電層116の作製工程と同様である。詳細については、先の実施の形態を参酌できる。

40

【0117】

以上により、パワーMOSFETと薄膜トランジスタを、同一の基板上に同様の工程で作製することができる。

【0118】

本実施の形態に示す方法などによって、パワーMOSFETと薄膜トランジスタを、同一の基板上に同様の工程で作製することができる。これにより、各種集積回路と、電力用回路とを同一基板上に形成することが可能である。

【0119】

50

なお、本実施の形態では、パワーMOSFETの酸化物半導体層104と、薄膜トランジスタの酸化物半導体層204とを、同一の工程で形成する場合を示したが、パワーMOSFETと薄膜トランジスタとでは酸化物半導体層の厚さへの要求が異なる場合がある。このため、酸化物半導体層104と酸化物半導体層204とは、異なる工程で作り分けても良い。具体的には、酸化物半導体層の作製工程を二段階に分け、第1段階において酸化物半導体層104または酸化物半導体層204の一方を作製し、第2段階において酸化物半導体層104または酸化物半導体層204の他方を作製する方法や、厚い酸化物半導体層をエッチング処理などで選択的に薄くして、酸化物半導体層104と酸化物半導体層204とを作製する方法、などがある。

## 【0120】

10

絶縁層110に関しても同様のことがいえ、パワーMOSFETと薄膜トランジスタとでその厚さが異なるように作り分けても良い。具体的には、絶縁層の作製工程を二段階に分け、第1段階において酸化物半導体層104上の絶縁層または酸化物半導体層204上の絶縁層の一方を作製し、第2段階において酸化物半導体層104上の絶縁層または酸化物半導体層204上の絶縁層の他方を作製する方法や、厚い絶縁層をエッチング処理などで選択的に薄くして、酸化物半導体層104上の絶縁層と酸化物半導体層204上の絶縁層とを作製する方法、などがある。

## 【0121】

本実施の形態に示す構成、方法などは、他の実施の形態と適宜組み合わせて用いることができる。

20

## 【0122】

## (実施の形態5)

本実施の形態では、開示する発明に係る半導体装置を用いた回路の一例について、図9および図10を参照して説明する。なお、以下では、電力用回路（電力変換用回路など）の一例であるDC-DCコンバータについて説明する。

## 【0123】

DC-DCコンバータは、直流電圧を、別の直流電圧に変換する回路である。DC-DCコンバータの変換方式としては、リニア方式やスイッチング方式が代表的であるが、スイッチング方式のDC-DCコンバータは変換効率に優れるため、電子機器の省電力化に好適である。ここでは、スイッチング方式、特にチョッパ方式のDC-DCコンバータについて説明する。

30

## 【0124】

図9に示すDC-DCコンバータは、電源300、リファレンス電圧生成回路302、リファレンス電流生成回路304、エラーアンプ306、PWMバッファ308、三角波生成回路310、コイル312、パワーMOSFET314、ダイオード316、コンデンサ318、抵抗320、抵抗322などを含む。なお、ここでは、パワーMOSFET314として、n型のパワーMOSFETを用いる。

## 【0125】

リファレンス電圧生成回路302は、各種リファレンス電圧（ $V_{ref}$ ）を生成する。また、リファレンス電流生成回路304は、リファレンス電圧生成回路302で生成されたリファレンス電圧（ $V_{ref}$ ）を利用して、リファレンス電流（ $I_{ref}$ ）やバイアス電流を生成する。

40

## 【0126】

エラーアンプ306は、リファレンス電圧生成回路302からのリファレンス電圧（ $V_{ref}$ ）とフィードバック電圧（ $V_{FB}$ ）の差を積分して、PWMバッファ308に出力する。三角波生成回路310は、リファレンス電圧（ $V_{ref}$ ）およびリファレンス電流（ $I_{ref}$ ）から三角波を生成して、PWMバッファ308に出力する。

## 【0127】

PWMバッファ308は、エラーアンプ306からの出力と、三角波生成回路310からの三角波とを比較して、パルス信号をパワーMOSFET314に出力する。

50

## 【0128】

PWMバッファ308からのパルス信号が高電位の場合には、n型のパワーMOSFET314はオン状態となり、ダイオード316の入力側の電位は接地電位（低電位）となる。このため、パルス信号が高電位の期間においては、出力電圧（ $V_{OUT}$ ）は徐々に減少する。

## 【0129】

一方、PWMバッファ308からのパルス信号が低電位の場合には、n型のパワーMOSFET314はオフ状態となり、ダイオード316の入力側の電位は上昇する。このため、パルス信号が低電位の期間において、出力電圧（ $V_{OUT}$ ）は徐々に増大する。

## 【0130】

PWMバッファ308からのパルス信号に起因する上記出力電圧（ $V_{OUT}$ ）の変化はごく僅かなものであるから、DC-DCコンバータを採用することで、出力電圧を略一定に保つことができる。

## 【0131】

なお、上記DC-DCコンバータにおいて、コイル312は、パワーMOSFET314のスイッチングに起因する電流の変化を緩和するために設けられている。また、コンデンサ318は、出力電圧（ $V_{OUT}$ ）の急激な変動を抑制するために設けられている。さらに、抵抗320および抵抗322は、出力電圧（ $V_{OUT}$ ）からフィードバック電圧（ $V_{FB}$ ）を生成するために設けられている。

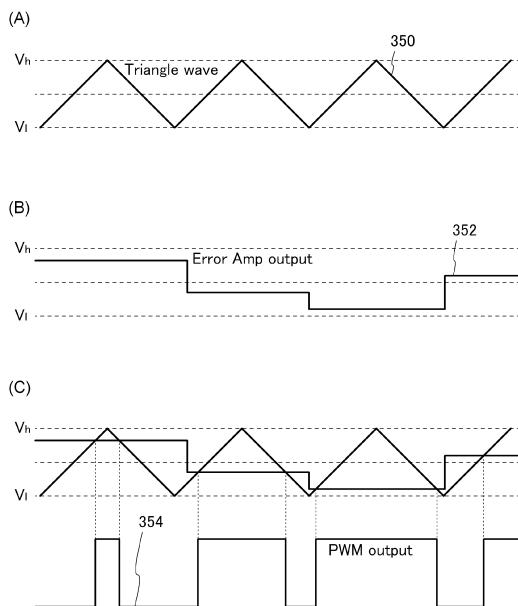

## 【0132】

図10には、DC-DCコンバータを構成する回路の出力波形の一例を示す。

## 【0133】

図10（A）には、三角波生成回路310から出力される三角波350を、図10（B）には、エラーアンプ306からの出力波形352を、それぞれ示す。

## 【0134】

図10（C）には、PWMバッファ308で生成されるパルス信号354を示す。三角波350および出力波形352がPWMバッファ308に入力されると、PWMバッファ308はこれらを比較して、パルス信号354を生成する。そして、当該パルス信号354はパワーMOSFET314に出力され、出力電圧（ $V_{OUT}$ ）が決定される。

## 【0135】

以上に示したように、開示する発明に係るパワーMOSFETをDC-DCコンバータに適用することが可能である。開示する発明に係るパワーMOSFETは耐圧が高く、これを用いたDC-DCコンバータの信頼性を高めることができる。また、開示する発明に係るパワーMOSFETは製造コストが抑制されているため、これを用いたDC-DCコンバータの製造コストも抑制される。このように、開示する発明に係る半導体装置を電子回路に用いることで、信頼性の向上、製造コストの低減などのメリットを享受できる。

## 【0136】

なお、本実施の形態において示したDC-DCコンバータは、開示する発明の半導体装置を用いた電力用回路の一例に過ぎず、開示する発明の半導体装置をその他の回路に用いることは、当然に可能である。本実施の形態に示す構成、方法などは、他の実施の形態と適宜組み合わせて用いることができる。

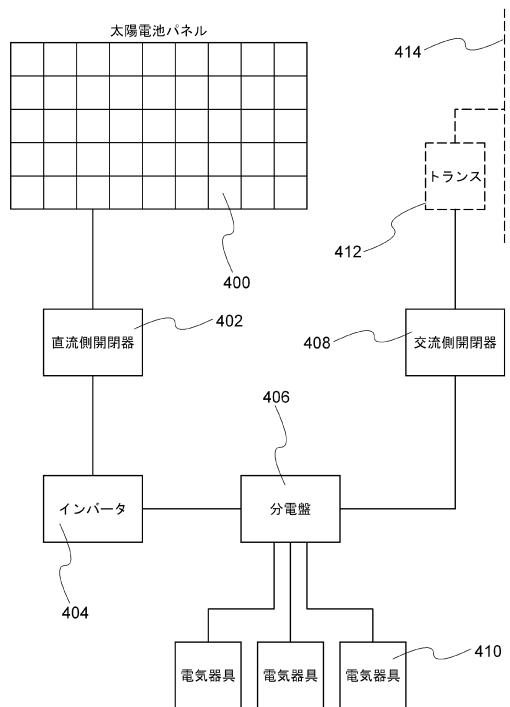

## 【0137】

## (実施の形態6)

本実施の形態では、開示する発明の半導体装置を用いて構成されるインバータを備えた太陽光発電システムの一例について、図11を参照して説明する。なお、ここでは、住宅等に設置される太陽光発電システムの構成の一例について示す。

## 【0138】

図11に示す住宅用の太陽光発電システムは、太陽光発電の状況に応じて、電力の供給方式を変更するシステムである。例えば、晴天時など太陽光発電が行われる状況においては、太陽光発電により生じた電力を家庭内で消費し、また、余剰電力は電力会社からの配電

10

20

30

40

50

線 4 1 4 に供給する。一方、太陽光発電による電力が不足する夜間や雨天時には、配電線 4 1 4 から電気の供給を受けて、それを家庭内で消費する。

【 0 1 3 9 】

図 1 1 に示す住宅用の太陽光発電システムは、太陽光を電力（直流電力）に変換する太陽電池パネル 4 0 0 や、その電力を直流から交流に変換するインバータ 4 0 4 などを含む。インバータ 4 0 4 から出力される交流電力は、各種の電気器具 4 1 0 を動作させる電力として使用される。

【 0 1 4 0 】

余分な電力は、配電線 4 1 4 を通じて家庭外に供給される。すなわち、当該システムを利用して電力の売却が可能である。直流開閉器 4 0 2 は、太陽電池パネル 4 0 0 とインバータ 4 0 4 との接続または遮断を選択するために設けられている。また、交流開閉器 4 0 8 は、配電線 4 1 4 と接続されるトランス 4 1 2 と、分電盤 4 0 6 との接続または遮断を選択するために設けられている。

【 0 1 4 1 】

上記のインバータに、開示する発明の半導体装置を適用することで、信頼性が高く、安価な太陽光発電システムを実現することができる。

【 0 1 4 2 】

本実施の形態に示す構成、方法などは、他の実施の形態と適宜組み合わせて用いることができる。

【 符号の説明 】

【 0 1 4 3 】

|       |                 |    |

|-------|-----------------|----|

| 1 0 0 | 基板              | 20 |

| 1 0 2 | 導電層             |    |

| 1 0 4 | 酸化物半導体層         |    |

| 1 0 6 | 結晶領域            |    |

| 1 0 8 | 導電層             |    |

| 1 0 9 | 導電層             |    |

| 1 1 0 | 絶縁層             |    |

| 1 1 2 | 導電層             |    |

| 1 1 4 | 導電層             | 30 |

| 1 1 6 | 導電層             |    |

| 1 2 4 | 酸化物半導体層         |    |

| 1 2 6 | 結晶領域            |    |

| 2 0 4 | 酸化物半導体層         |    |

| 2 0 6 | 結晶領域            |    |

| 2 0 8 | 導電層             |    |

| 2 0 9 | 導電層             |    |

| 2 1 2 | 導電層             |    |

| 2 1 4 | 導電層             |    |

| 2 1 6 | 導電層             | 40 |

| 3 0 0 | 電源              |    |

| 3 0 2 | リファレンス電圧生成回路    |    |

| 3 0 4 | リファレンス電流生成回路    |    |

| 3 0 6 | エラーアンプ          |    |

| 3 0 8 | PWM バッファ        |    |

| 3 1 0 | 三角波生成回路         |    |

| 3 1 2 | コイル             |    |

| 3 1 4 | パワー M O S F E T |    |

| 3 1 6 | ダイオード           |    |

| 3 1 8 | コンデンサ           | 50 |

|       |         |

|-------|---------|

| 3 2 0 | 抵抗      |

| 3 2 2 | 抵抗      |

| 3 5 0 | 三角波     |

| 3 5 2 | 出力波形    |

| 3 5 4 | パルス信号   |

| 4 0 0 | 太陽電池パネル |

| 4 0 2 | 直流開閉器   |

| 4 0 4 | インバータ   |

| 4 0 6 | 分電盤     |

| 4 0 8 | 交流開閉器   |

| 4 1 0 | 電気器具    |

| 4 1 2 | トランス    |

| 4 1 4 | 配電線     |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開2007-173820(JP, A)

米国特許出願公開第2007/0141789(US, A1)

特開2006-352087(JP, A)

米国特許出願公開第2006/0263576(US, A1)

特開昭63-205963(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 786