(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4545250号

(P4545250)

(45) 発行日 平成22年9月15日(2010.9.15)

(24) 登録日 平成22年7月9日(2010.7.9)

(51) Int.Cl.

HO4N 7/32 (2006.01)

F 1

HO4N 7/137

Z

請求項の数 5 (全 16 頁)

(21) 出願番号 特願平11-197286

(22) 出願日 平成11年7月12日(1999.7.12)

(65) 公開番号 特開2000-50284(P2000-50284A)

(43) 公開日 平成12年2月18日(2000.2.18)

審査請求日 平成18年7月11日(2006.7.11)

(31) 優先権主張番号 114568

(32) 優先日 平成10年7月13日(1998.7.13)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78729 テキサス州

オースチン ウエスト パーマー レー

ン 7700

(74) 代理人 100116322

弁理士 桑垣 衡

(72) 発明者 デビッド・ジェイ・ホウキンス

アメリカ合衆国テキサス州オースチン、ス

モキー・ヒル・ロード6904

(72) 発明者 ブルース・エー・オウガスティン

アメリカ合衆国イリノイ州レイク・イン・

ザ・ヒルズ、バーハーバー・ドライブ46

35

最終頁に続く

(54) 【発明の名称】動きベクトルの格納および読出を用いることによりビデオ信号を符号化および解読するための方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ビデオ信号の解読および符号化に用いられる動きベクトルを格納および読出する装置であつて：

複数の格納要素を有するメモリであつて、前記複数の格納要素の第1要素がビデオ・フレームのマクロブロックに関して第1動きベクトルを格納し、前記マクロブロックはビデオ・フレームを表す複数のマクロブロックの1つであり、さらに前記複数の格納要素の第2要素が前記マクロブロックに関する第2動きベクトルを格納し、前記第1動きベクトルおよび第2動きベクトルが同一のマクロブロックに関して格納されており、前記第1動きベクトルおよび前記第2動きベクトルが、ビデオ・アーチファクト除去のための動きベクトル予測子計算およびオーバラップブロック動き補償の両方の間で共有される、前記メモリ；および

前記メモリに結合され、前記メモリ内で動きベクトルが格納される場所を制御するアドレス発生回路構成；

を具備し、前記メモリおよび前記アドレス発生回路構成が集積回路形式でハードウェア部品として実現され、

前記メモリは第1集合の動きベクトルと第2集合の動きベクトルを格納し、

前記第1集合の動きベクトルは第1の複数のマクロブロックの上部分に対応する複数の第1動きベクトルを含み、前記複数の第1動きベクトルは、現行のマクロブロックの処理に必要な第1動きベクトルのみを含むものであり、

10

20

前記第2集合の動きベクトルは、前記第1の複数のマクロブロックの下部分と、第2の複数のマクロブロックの下部分とに対応する複数の第2動きベクトルを含み、

前記第1集合の動きベクトルが前記第2集合の動きベクトルよりも少ない格納要素をメモリ内で占有することを特徴とする装置。

【請求項2】

前記メモリに応答する予測子計算機をさらに具備することを特徴とする請求項1記載の装置。

【請求項3】

ビデオ信号の解読および符号化に用いられる動きベクトルを格納および読出する方法であって：

メモリを設ける段階；

複数のマクロブロックに対応する第1集合の動きベクトルと第2集合の動きベクトルを受信する段階であって、前記第1集合の動きベクトルは、第1の複数のマクロブロックの上部分を表す複数の第1および第2動きベクトルを含み、前記複数の第1動きベクトルは、現行のマクロブロックの処理に必要な第1および第2動きベクトルのみを含むものであり、前記第2集合の動きベクトルは、前記第1の複数のマクロブロックの下部分と、第2の複数のマクロブロックの下部分とを表す複数の第3および第4動きベクトルを含み、各第1動きベクトルは、各マクロブロック内の左上ブロックであるブロック1を表し、各第2動きベクトルは各マクロブロック内の右上ブロックであるブロック2を表し、各第3動きベクトルは各マクロブロック内の左下ブロックであるブロック3を表し、各第4動きベクトルは各マクロブロック内の右下ブロックであるブロック4を表し、前記複数のマクロブロックがビデオ・フレームの一部分を表す、前記複数の動きベクトルを受信する段階；および

前記第1集合の動きベクトルを前記メモリの第1部分に格納し、前記第2集合の動きベクトルを前記メモリの第2部分に格納する段階；

を具備し、前記第1集合の動きベクトルが前記第2集合の動きベクトルよりも少ない格納要素をメモリ内で占有することを特徴とする方法。

【請求項4】

ビデオ信号をデコードするための装置であって：

ビデオ信号を受けるビットストリーム・デコーダ；

前記ビットストリーム・デコーダに応答する動きベクトル格納および読出モジュールであって、該動きベクトル格納および読出モジュールは複数のマクロブロックを表す第1集合の動きベクトル及び第2集合の動きベクトルを格納するメモリを含み、前記複数のマクロブロックは前記ビデオ信号の一部を表し、前記メモリにおける前記第1及び第2の集合の動きベクトルの一部は少なくとも1つの所定のマクロブロック内の複数のブロックを表し、前記少なくとも1つの所定のマクロブロックは前記ビデオ信号の一部を表し、前記第1集合の動きベクトルは、第1の複数のマクロブロックの上部分に対応する複数の動きベクトルを含み、前記上部分に対応する複数の動きベクトルは、現行のマクロブロックの処理に必要な上部分に対応する動きベクトルのみを含むものであり、前記第2集合の動きベクトルは、前記第1の複数のマクロブロックの下部分と、第2の複数のマクロブロックの下部分とに対応する複数の動きベクトルを含み、前記第1集合の動きベクトルが前記第2集合の動きベクトルよりも少ないメモリを必要とする、前記動きベクトル格納および読出モジュール；

前記ビットストリーム・デコーダに応答する変換をベースとした圧縮モジュール；

前記動きベクトル格納および読出モジュールに応答する動き補償ユニット；および

前記動き補償ユニットおよび変換をベースとした圧縮モジュールに応答する合成器；

を具備することを特徴とするビデオ信号をデコードするための装置。

【請求項5】

ビデオ信号をエンコードするための装置であって：

動き推定モジュール；

10

20

30

40

50

前記動き推定モジュールに応答する動きベクトル格納および読み出モジュールであって、該動きベクトル格納および読み出モジュールはマクロブロックに対応する第1集合の動きベクトルと第2集合の動きベクトルとを格納するメモリを含み、前記マクロブロックは前記ビデオ信号の一部を表し、前記メモリにおける前記第1及び第2集合の動きベクトルの一部は少なくとも1つの所定のマクロブロック内の複数のブロックを表し、前記少なくとも1つの所定のマクロブロックは前記ビデオ信号の一部を表し、前記第1集合の動きベクトルは、第1の複数のマクロブロックの上部分に対応する複数の動きベクトルを含み、前記上部分に対応する複数の動きベクトルは、現行のマクロブロックの処理に必要な上部分に対応する動きベクトルのみを含むものであり、前記第2集合の動きベクトルは、前記第1の複数のマクロブロックの下部分と、第2の複数のマクロブロックの下部分とに対応する複数の動きベクトルを含み、前記第1集合の動きベクトルは前記第2集合の動きベクトルよりも少ないメモリを必要とする、前記動きベクトル格納および読み出モジュール；

前記動きベクトル格納および読み出モジュールに応答する動き補償ユニット；

前記動き補償ユニットに応答する変換をベースとした圧縮モジュール；および

前記変換をベースとした圧縮モジュールに応答するビットストリーム・エンコーダ；

を具備することを特徴とするビデオ信号をエンコードするための装置。

【発明の詳細な説明】

【0001】

【産業上の利用分野】

本発明は、一般にビデオ通信に関し、さらに詳しくは、ビデオ画像の圧縮および圧縮解除に関する。

【0002】

【従来の技術および発明が解決しようとする課題】

事業用および家庭用に用いられる多くのビデオ電話およびビデオ会議装置は、現在の電話網に固有の帯域幅上の制約により高い圧縮比を必要とする。この要望に応えて、低ビット速度ビデオ通信に関するH.263国際規格(H.263 International Standard for Low Bit Rate Video Communications)が開発された。この規格は、直ちにビデオ産業に採用された。H.263国際規格には、高度予測モード(APM: Advanced Prediction Mode)と呼ばれる任意の技術の実行が含まれる。APMは、動きの推定中に導入されるアーチファクトを排除することによりビデオ画像が大幅に改善する。APMの欠点は、ハードウェア内に組み込むのが極めて困難で非効率的なことである。その結果、高度予測モードが最初に実現されたのはソフトウェア内のみであった。

【0003】

ビデオを圧縮するH.263技術の1つは、動き推定(motion estimation)を用いることである。動き推定は、実際の画素の代わりに動きベクトルをデコーダに送ることによりビデオを処理する。デコーダは、この動きベクトルを取り込み、それを用いて前に解読されたフレームから動きベクトルが指示するデータのブロックにアクセスすることで現行のフレームを再生する。H.263 APMモードにおいては、それぞれ $8 \times 8$ ブロックの画素の代わりに1つの動きベクトルを送ればよい。APMオプションは、それぞれ $8 \times 8$ ブロックを表す動きベクトルを周辺ブロックの動きベクトルで平均化することを求める。これにより、動き推定プロセス中に導入されるブロック化アーチファクトが軽減される。残念ながら、周辺のマクロブロックから動きベクトルを平均化することは、いくつかの理由から、メモリにおいてもハードウェアにおいても集約的になることがわかっている。第1に、周辺ブロックから動きベクトルを読み出すには、RAM内に多数の動きベクトルを格納しなければならないことになる。現行のブロック上に動きベクトルを読み出しなければならないということは、動きベクトルの行全体を格納することが必要となり、これは極めてメモリ集約的になる。第2に、H.263規格は、2つの別々の関数に関して動きベクトルを格納および読み出すことを必要とするものとAPMモードを定義する：すなわち、オーバラップブロック動き補償(OBMC: Overlapped

10

20

30

40

50

Block Motion Compensation) および予測子計算 (predictor calculation) である。これらの関数は、容易に合成されない。なぜなら、OBMC 関数は解読時間の 1 マクロブロック分だけ予測子関数より遅延するためである。これにより、2 つの関数は異なる時間フレーム内で動作することを強いられる。第 3 に、OBMC も予測子計算も、それぞれ 4 つの異なるアドレス・パターンを必要とする。従って、必要なアドレス化スキームは 8 個になる。しかし、アドレス化スキームのうち線形順序のものは 1 つもなく、容易にアドレス化可能な他のパターンのものもない。

#### 【0004】

上記の問題のために、H.263 規格で定義される APM モードのハードウェアを効率的に実行することは極めて困難である。APM モードをソフトウェアで実行することは、この機能を実現するために必要とされる大量のメモリおよびシステム資源の使用可能性のために有利である。しかし、ソフトウェアの実行には、実行速度がはるかに遅く、ハードウェア実行により得られるフレーム速度と画像の品質が犠牲になるという欠点がある。

#### 【0005】

##### 【実施例】

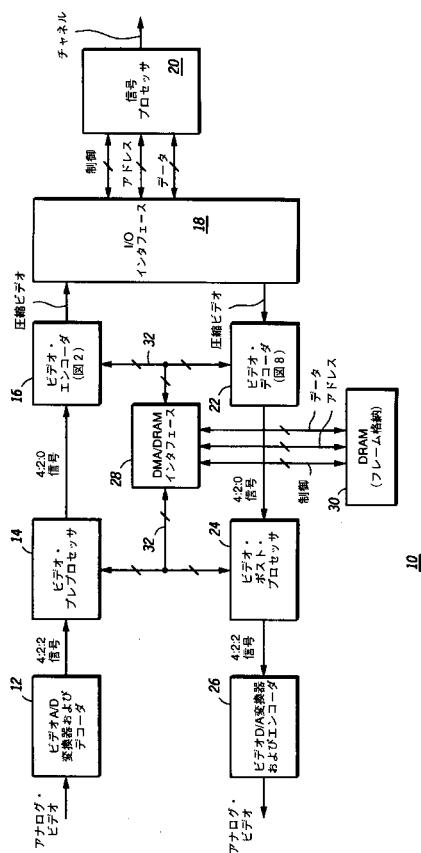

図 1 には、本発明の好適な実施例によるビデオ・コデック (エンコーダ / デコーダ 10) 装置のブロック図を示す。本発明は、上記の問題点を克服し、APM を効率的にシリコン内に実現することを可能にする。ビデオ A - D 変換器およびデコーダ 12 は、アナログ・ビデオ信号を受信する入力と、4 : 2 : 2 のビデオ・フォーマットの信号を提供する出力とを有する。4 : 2 : 2 信号は、ビデオ・プレプロセッサ 14 の入力に接続され、プレプロセッサ 14 は 4 : 2 : 0 のビデオ・フォーマットの信号を提供する。ビデオ・プレプロセッサ 14 の出力はビデオ・エンコーダ 16 の入力に接続される。エンコーダ 16 については図 2 で詳細に説明する。ビデオ・エンコーダ 16 は、圧縮されたビデオ・ビットストリームを入力 / 出力 (I / O) インタフェース回路 18 に提供する。I / O インタフェース 18 は、制御、アドレスおよびデータ・バスを介して信号プロセッサ 20 に結合される。I / O インタフェース 18 は、被圧縮ビデオ・ビットストリームを信号プロセッサ 20 で利用される特定種類の信号プロセッサとインターフェースする。I / O インタフェース 18 は、被圧縮ビデオ・ビットストリームをビデオ・デコーダ 22 に与えるビデオ・デコーダ 22 の入力にも結合される。ビデオ・デコーダ 22 の出力は、ポスト・プロセッサ 24 の入力に接続される。ビデオ・デコーダ 22 の出力は 4 : 2 : 0 のビデオ・フォーマットである。ポスト・プロセッサ 24 の出力は、4 : 2 : 2 のビデオ・フォーマットで、ビデオ D - A 変換器およびエンコーダ 26 の入力に接続される。ビデオ D - A 変換器およびエンコーダ 26 の出力は、アナログ・ビデオ出力を提供する。またさらに、直接メモリ・アクセス (DMA : direct memory access) / ダイナミック・ランダム・アクセス・メモリ (DRAM : dynamic random access memory) インタフェース回路 28 が図示される。DMA / DRAM インタフェース回路 28 は、内部バス 32 を介して、ビデオ・プレプロセッサ 14、ビデオ・エンコーダ 16、ビデオ・デコーダ 22 およびポスト・プロセッサ 24 の各々に結合される。DMA / DRAM インタフェース回路 28 は、制御、アドレスおよびデータ・バスを介して DRAM 30 に結合される。ビデオ・コデック 10 は、アナログ・ビデオ信号を受信し、それをビデオ A - D 変換器およびデコーダ 12 とビデオ・プレプロセッサ 14 とを介して 2 つの異なるビデオ・フォーマットに変換し、4 : 2 : 0 信号をビデオ・エンコーダに与えるよう機能し、ビデオ・エンコーダが信号を被圧縮ビデオ・ビットストリームに圧縮する働きをする。被圧縮ビデオ・ビットストリームは、信号プロセッサ 20 により利用され、信号プロセッサ 20 はホストとして機能して被圧縮ビデオ・ビットストリームをチャネルに与えて送信する。どのタイプのチャネルが用いられるかにより、信号プロセッサ 20 は被圧縮ビデオ・ビットストリームをアナログ・フォーマットに変換するか、あるいはデジタル・フォーマットのままにする。I / O インタフェース 18 も被圧縮ビデオ・ビットストリームを提供する機能を果たすが、この被圧縮ビデオ・ビットストリームは信号プロセッサ 20 を介してチャネル上で、ビデオ・デコーダ 22 により受信される。ビデオ・デコ

10

20

30

40

50

ダ22は、ビデオ・ビットストリームを、ポスト・プロセッサ24が用いる4:2:0のビデオ・フォーマットに圧縮解除する。ポスト・プロセッサ24は、4:2:0のフォーマットを、ビデオD/A変換器26により用いられる4:2:2のフォーマットに変換する。ビデオD/A変換器26は、従来のテレビジョンまたはビデオ・モニタが受け入れることのできるアナログ出力を提供する。ビデオ・コデック10の形式は、図示される如く実質的には従来通りである。言い換えると、既存の集積回路製品を用いて、ビデオA-D変換器およびデコーダ12、ビデオ・プレプロセッサ14、ポスト・プロセッサ24およびビデオD-A変換器およびエンコーダ26を実現することができる。しかし、ビデオ・エンコーダ16およびビデオ・デコーダ22の実行例と効率性は、用途により変わる。本発明が扱うのは、ビデオ・エンコーダ16およびビデオ・デコーダ22の特定の実行例である。

10

## 【0006】

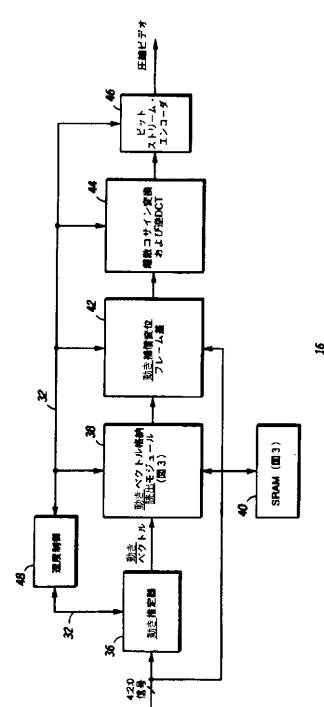

図2には、図1のビデオ・エンコーダ16の詳細なブロック図を示す。ビデオ・エンコーダ16は、一般に、4:2:0のビデオ・フォーマットでビデオ信号を受信する入力を有する動き推定器回路36によって構成される。動き推定器36の出力は、ベクトル格納読み出モジュール38に複数の動きベクトルを提供する。モジュール38は、動き補償および変位フレーム差回路42の入力に接続される出力を有する。動き補償および変位フレーム差回路42の出力は、離散コサイン変換および逆離散コサイン変換(DCT: Discrete Cosine Transform / IDT: Inverse Discrete Cosine Transform)回路44またはモジュールの入力に接続される。一般に、IDT/DCT回路44は、ウェーブレットまたは離散コサイン変換などの圧縮/圧縮解除アルゴリズムに基づき変換を実行する。離散コサイン変換および逆DCT回路44の出力は、被圧縮ビデオ出力ビットストリームを提供するビットストリーム・エンコーダ46の入力に接続される。速度制御回路48は、これも図1に図示される内部バス32を介して、動き推定器36、動き補償および変位フレーム差回路42および離散コサイン変換および逆DCT回路44の各々に接続される。

20

## 【0007】

動作中は、ビデオ・エンコーダ16は、前回のフレームの画素情報から現行フレームの動き推定を実行することにより機能する。動き推定器36が、複数の動きベクトルを提供する。この動きベクトルは、前回のフレームと現行のフレームとの間の8×8画素ブロックの変位を表す。動きベクトル格納読み出モジュール38が動きベクトルを受信する。図3に関連してさらに説明されるが、モジュール38はH.263国際規格などのビデオ規格において高度予測モードを実現するために必要とされる動きベクトルを読み出および格納する働きをする。モジュール38がこのような動きベクトルを読み出されると、モジュール38はその出力において2種類の動きベクトルを動き補償および変位フレーム差回路42に提供する。提供される第1種類の動きベクトルがオーバラップブロック動き補償に用いられる。提供される第2種類の動きベクトルは、前回のフレーム再構築および動き補償に用いられる動きベクトルである。動き補償および変位差フレーム回路42は、これら2種類の動きベクトルを取り入れ、2つの関数を実行する: すなわち、変位フレーム差および動き補償である。動き補償関数は、上記の2種類の動きベクトルを用いて、遠隔のデコーダの解読を複製する。動き補償関数は、バス32を介して動き推定器36に関して再構築される基準フレームを提供する。このフレームは、前フレームまたは再構築フレームとも呼ばれ、遠隔デコーダにより解読されるものの正確な複製である。これがビデオ・エンコーダ16が次のフレームを符号化する際に動き推定の基準フレームとして動き推定器36により用いられる。変位フレーム差関数は、当初の(基準)フレームから動き推定されるフレームを差し引き、その差を離散コサイン変換および逆DCT回路44に与える。DCT / IDCT 44の出力と動き推定器36からの動きベクトルとがビットストリーム・エンコーダ46に与えられる。ビットストリーム・エンコーダ46は、H.263に準じてデータを配列し、圧縮されたビデオ・ビットストリーム出力をチャネルに提供する。チ

30

40

50

ヤネル上に送付されるだけでなく、D C T / I D C T 回路 4 4 の圧縮出力は、同じ D C T / I D C T 回路 4 4 の逆変換関数を用いて圧縮解除される。この圧縮解除された出力は、次にバス 3 2 を介して、同じ 動き 補償および変位フレーム差回路 4 2 に送られる。この情報は、変位差フレーム関数により用いられ、その前の減算を取り消し、動き 推定器 3 6 の基準フレームを再度作成する。これはチャネルの他端で遠隔デコーダにより解読されるものの正確な複製である。

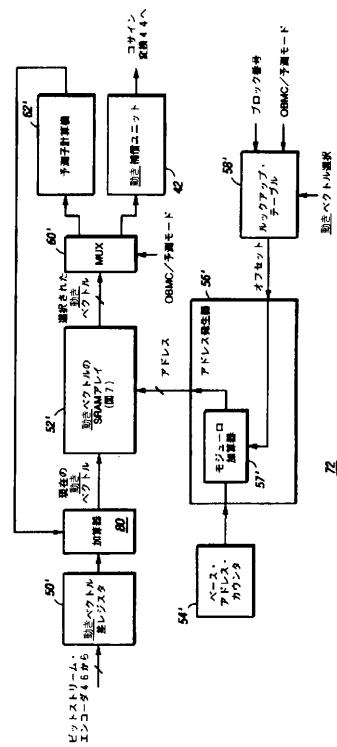

【 0 0 0 8 】

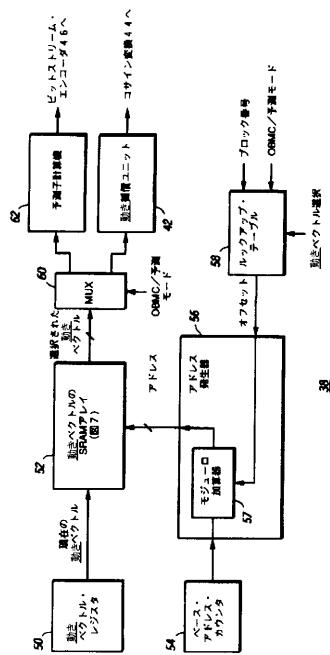

図 3 には、本発明による図 2 の 動きベクトル格納読出 モジュール 3 8 を示す。動きベクトル・レジスタ 5 0 は、現在の 動きベクトルを 動きベクトル S R A M アレイ 5 2 に提供する出力を有する。この 動きベクトル S R A M アレイ 5 2 は、より一般的には 動きベクトルを格納する複数の格納要素と呼ばれる。ベース・アドレスを生成するベース・アドレス・カウンタ 5 4 がアドレス発生器 5 6 に接続される。アドレス発生器 5 6 は、ルックアップ・テーブル 5 8 からオフセット値を受信する第 2 入力を有する。ルックアップ・テーブル 5 8 は、プロック番号を受信する第 1 入力を有する。プロック番号は、多くのビデオ規格で定義されるマクロプロック内の 4 つの可能なプロックのうちの 1 つを表す。ルックアップ・テーブル 5 8 は、H . 2 6 3 国際規格に必要な O B M C または予測子計算モードのいずれか一方を実現するための O B M C / 予測子モード信号を受信する第 2 入力を有する。ルックアップ・テーブル 5 8 は、所望の 動きベクトル (左, 上, 右上, 右, 下) を選択する第 3 入力を有する。これについては図 5 および図 6 において詳細に説明する。状態装置は 4 つの可能な選択肢 (左, 上, 右上, 右下) を循環し、新しいマクロプロックが符号化されると最初に戻ってリセットされる。モジユーロ加算器 5 7 は、ルックアップ・テーブル 5 8 からオフセット値を受信する第 1 入力と、ベース・アドレス・カウンタ 5 4 からベース・アドレスを受信する第 2 入力と、動きベクトルの S R A M アレイ 5 2 に接続されるアドレスを提供する出力を有する。S R A M アレイ 5 2 は、選択された 動きベクトルを乗算器回路 6 0 に与える出力を有する。乗算器 6 0 は、予測子計算機回路 6 2 の入力に接続される第 1 出力を有する。乗算器 6 0 は、O B M C / 予測モード制御信号に応答して機能する。この信号は、ルックアップ・テーブル 5 8 において適切なオフセット値を選択する際にも用いられる。乗算器 6 0 は、動き 補償ユニット 4 2 の入力に接続される第 2 出力を有する。動き 補償ユニット 4 2 は、図 2 に図示される D C T / I D C T 回路 4 4 に信号を提供する出力を有する。動きベクトル格納読出 モジュール 3 8 の動作を説明する前に、図 4 ないし図 6 について説明する。

【 0 0 0 9 】

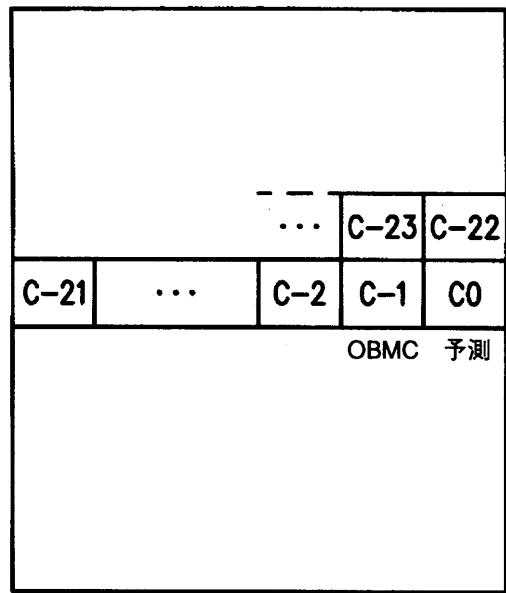

図 4 に、タイプ共通中間フォーマット ( C I F ) のビデオ・フレーム内の 1 行のマクロプロック・レイアウトを示す。マクロプロック・レイアウトは複数の行のマクロプロックを有する。図面の便宜上、1 行のマクロプロックのみを詳細に示す。各行は 2 2 個のマクロプロックを有し、それぞれに C 0 ~ C - 2 1 とラベルが付けられる。図示される形式では、マクロプロック C 0 は現行のマクロプロックを時間的に示す。マクロプロック C 0 のすぐ上にはマクロプロック C - 2 2 があり、これは時間領域において、過去の 2 2 個のマクロプロックからのマクロプロックである。ハードウェアおよびメモリを最大に節約するためには、O B M C および予測子関数のために用いられるメモリを共有および合成することが必要である。O B M C 関数は、予測子関数に関して、時間にして 1 マクロプロック分だけ遅延しなければならない。この事実により、O B M C 関数はマクロプロック C - 1 で動作 (動きベクトルの格納および 読出) を行うことになり、一方予測子関数はマクロプロック C 0 で動作する。O B M C 関数をマクロプロック C - 1 まで遅延させることができ、O B M C 関数が動作するマクロプロックのすぐ右側 (図 6 について詳細に説明する) の 動きベクトルを 読出する必要がある O B M C 要件のために必要である。O B M C 関数がマクロプロック C 0 で動作すると、「右側」の 動きベクトルをマクロプロック C + 1 から 読出しなければならない。これは 1 ブロックだけ将来のマクロプロックであり、まだ使用可能になつていない。図 5 および図 6 についてさらに説明するように、O B M C および予測子関数の「上の」マクロプロックから 動きベクトルを 読出することも必要である。「上」の 動き

10

20

30

40

50

ベクトルは、O B M C 関数に関しては 2 3 マクロブロック分だけ過去において処理されたものであり、予測子関数に関しては 2 2 マクロブロック分だけ過去に処理されたものであることに注目することが重要である。このため、2 4 個 ( C 0 ~ C - 2 3 ) のマクロブロックの 動きベクトルを格納することが必要になる。

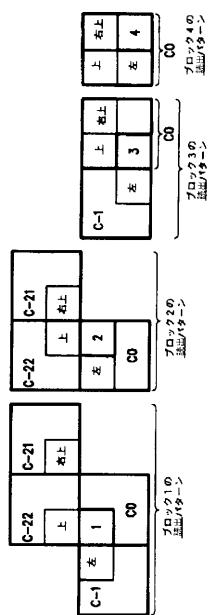

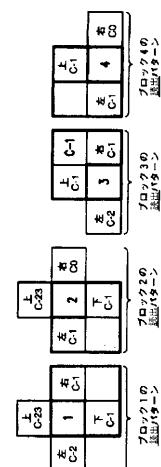

#### 【 0 0 1 0 】

図 5 および図 6 においては次のような命名法を採用する：16 × 16 画素マクロブロックを表す大きな正方形が 4 個のより小さな 8 × 8 画素ブロックに分割される。8 × 8 画素ブロックの各々は、それに関連する自身の 動きベクトルを有する。4 個の 8 × 8 画素ブロックは、当技術では通常「ブロック」と呼ばれるが、ブロック 1, 2, 3, 4 と番号が振られる。ブロック 1 はマクロブロックの左上隅であり、ブロック 2 が右上隅、ブロック 3 が左下隅、ブロック 4 が右下隅である。マクロブロックの処理とは、そのマクロブロックの符号化または解読を指す。図 5 および図 6 における「C - 1」の名前は、1 マクロブロック分だけ過去に処理されたマクロブロックを指す。同様に、マクロブロック「C - 2 1」は、2 1 マクロブロック分だけ過去に処理されたマクロブロックを指す。「C 0」は現在処理中のマクロブロックを指す。図 5 においては、マクロブロック C 0 内でブロック 1 について 読み出すべき動きベクトル は左、上および右上であることに注目することが重要である。左 動きベクトル はマクロブロック C - 1 内のブロック 2 のものである。上 動きベクトル はマクロブロック C - 2 2 内のブロック 3 のものである。右上 動きベクトル はマクロブロック C - 2 1 内のブロック 3 のものである。現在処理中のマクロブロック内のブロック 2 に関する 読み出パターン は次のようになる：左 動きベクトル が現在処理中のブロック ( C 0 ) のブロック 1 である。上 動きベクトル はマクロブロック C - 2 2 のブロック 4 である。右上 動きベクトル はマクロブロック C - 2 1 のブロック 3 である。現在処理中のマクロブロック内のブロック 3 に関する 読み出パターン もブロック 1, 2, 3, 4 とは異なる。現行ブロック内のブロック 3 の 読み出パターン は次のようになる：左 動きベクトル がマクロブロック C - 1 のブロック 4 である。上 動きベクトル は現在処理中のマクロブロック ( C 0 ) のブロック 1 であり、右上 動きベクトル は現在処理中のマクロブロック ( C 0 ) のブロック 2 である。現在処理中のマクロブロック内のブロック 4 については、左 動きベクトル が現行マクロブロック C 0 内のブロック 3 である。上 動きベクトル は現行マクロブロック C 0 のブロック 1 であり、右上 動きベクトル は現行マクロブロック C 0 内のブロック 2 である。この場合も、ブロック 1, 2, 3, 4 に関する 読み出パターン が互いに異なることに注目することが重要である。これらのパターンは、H . 2 6 3 規格において定義される。

#### 【 0 0 1 1 】

本発明は、O B M C 関数の 動きベクトル の 読み出 にも対応する。この関数も同様にマクロブロック内の各ブロックについて別々の 読み出パターン を有する。O B M C 関数は、マクロブロック内の各ブロックについて左、上、右および下 動きベクトル を 読み出 する必要がある。この場合も、右に 動きベクトル を 読み出 する要件は現行のマクロブロックの右の 動きベクトル がまだ処理されていないために困難であることに注目することが重要である。右 動きベクトル を 読み出 するためには、O B M C 関数を 1 マクロブロック分だけ時間的に遅延させることが必要である。従って、O B M C 関数は、予測子関数より 1 マクロブロック分だけ後にくるマクロブロック C - 1 で動作する。O B M C 関数の 読み出パターン は次のようになる：ブロック 1 については、左 動きベクトル がマクロブロック C - 2 のブロック 2 である。上 動きベクトル がマクロブロック C - 2 3 のブロック 3 である。右 動きベクトル はマクロブロック C - 1 のブロック 2 であり、下 動きベクトル はマクロブロック C - 1 のブロック 3 である。処理中の同じ O B M C 動きベクトル 内のブロック 2 については、左 動きベクトル がマクロブロック C - 1 内のブロック 1 である。上 動きベクトル はマクロブロック C - 2 3 のブロック 4 である。右 動きベクトル はマクロブロック C 0 のブロック 1 であり、下 動きベクトル はマクロブロック C - 1 のブロック 4 である。O B M C 関数のブロック 3 については、左 動きベクトル がマクロブロック C - 2 のブロック 4 である。上 動きベクトル はマクロブロック C - 1 のブロック 1 である。右 動きベクトル はマクロブロック C - 1

10

20

30

40

50

のブロック 4 であり、下動きベクトルはマクロブロック C - 1 のブロック 3 である。O B M C マクロブロック C - 1 のブロック 4 については、左動きベクトルがマクロブロック C - 1 のブロック 3 である。上動きベクトルはマクロブロック C - 1 のブロック 2 である。右動きベクトルはマクロブロック C 0 のブロック 3 であり、下動きベクトルはマクロブロック C - 1 のブロック 4 である。

#### 【 0 0 1 2 】

図 3 に戻り、動きベクトル格納読出モジュール 3 8 は次のように機能する。図 5 および図 6 について上述される O B M C および予測子モードの両方の 8 個のアドレス化スキームのオフセットがルックアップ・テーブル 5 8 を介して提供される。ルックアップ・テーブル 5 8 は、その入力としてマクロブロック内のブロック番号 ( 1 , 2 , 3 , 4 ) と、必要な動きベクトル ( 右、左など ) と、動きベクトル読出の適切なオフセットを選択するための関数モード ( O B M C / 予測子 ) とを取り入れる。

#### 【 0 0 1 3 】

実行される最初のモードは予測モードである。予測モードを実行するには、図 5 を参照する。図 5 は、H . 2 6 3 国際規格により定義される 4 つのマクロブロック構造を示す。各マクロブロックはマクロブロック内に  $8 \times 8$  ブロックを表す 4 つの動きベクトルを有する。予測モードについては、H . 2 6 3 国際規格はマクロブロックに含まれる 4 つのブロックの各々に関して左、上および右上動きベクトルの読出を必要とする。各ブロックの左、上および右上動きベクトルの読出パターンは、マクロブロック内の個々のブロック 1 , 2 , 3 , 4 に関して異なる。パターンを実現するために、カウンタ 5 4 がゼロから 5 3 までの間の数値をアドレス発生器 5 6 に提供する。アドレス発生器 5 6 は、カウンタの出力に 2 を掛けてベース・アドレスを得る。この実行例で 2 を掛ける乗算が必要とされるのは、2 つの動きベクトルが各計数において格納されるためである。ルックアップ・テーブル 5 8 はブロック番号、モードおよび動きベクトル選択に基づきオフセット値を出力する。モジューロ加算器 5 7 は、ルックアップ・テーブル 5 8 が与えるオフセット値をカウンタ 5 4 が与えるベース・アドレスに加算する。その和が S R A M アレイ 5 2 との通信においてポインタとして用いられるアドレスとなる。このアドレスは、H . 2 6 3 規格の読出パターンにより適切な左、上および右上動きベクトルを読出するために用いられる。S R A M アレイ 5 2 内でアドレス指定される左、上および右上動きベクトルが、S R A M アレイ 5 2 により乗算器 6 0 ( M u x ) を介して選択的に出力される。選択される動きベクトルは予測子計算機 6 2 に与えられる。予測子計算機 6 2 は、選択される上、右上および左動きベクトルのメジアン ( 中央値 ) を計算するよう機能する。それに由来するメジアンは、通常「予測子」と呼ばれ、ビットストリーム・エンコーダ 4 6 に提供される。ここで予測子を動き推定器 3 6 により提供される動きベクトルから減じる。その結果、当技術では「差」と呼ばれるが、差がチャネル上に送付される。予測子計算機 6 2 の実行例は当技術では周知である。

#### 【 0 0 1 4 】

O B M C モードにおいては、ルックアップ・テーブル 5 8 が H . 2 6 3 規格に準拠する O B M C 用動きベクトル読出パターン ( 図 6 ) に従うオフセット値を提供する。アドレス発生器 5 6 は、予測子計算に関する上記の説明と同様に機能して、アドレスが S R A M アレイ 5 2 にアドレスが送られ、アレイ 5 2 は、選択した動きベクトルを乗算器 6 0 に送る。乗算器 6 0 から、O B M C 動きベクトルが動き補償ユニット 4 2 に乗算器 6 0 を介して与えられる。動き補償ユニットは O B M C 動きベクトルを利用して動き推定器のために再構築フレームを構築する。

#### 【 0 0 1 5 】

マクロブロックの上部の動きベクトル、すなわちブロック 1 , 2 はマクロブロック C - 2 を超えてセーブする必要がないことに注目すると、R A M において大幅な節約を実現することができることを理解頂きたい。これを理解するには、図 6 のブロック 1 ( O B M C 関数 ) を参照されたい。図 6 は、上半分または部分 ( T - x ) の動きベクトルの集合が必要とされる最後のときがマクロブロック C - 1 内のブロック 1 の左動きベクトルの読出の

10

20

30

40

50

ためであることを示す。従って、下半分または部分動きベクトル(B - x)の集合のみがマクロブロックC - 2の後は必要になる。これは、「上」動きベクトルを得るために、処理中のマクロブロック上のマクロブロックからの下半分または部分動きベクトルのみが必要となるからである。

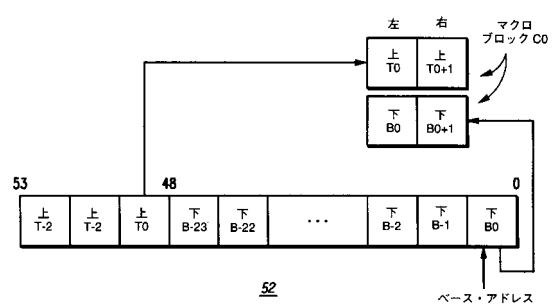

#### 【0016】

図7には、S R A Mアレイ52の1つの形態に関するメモリ割当の例が示される。図示される形態においては、27個の半マクロブロックのうち複数のものが提供され、各半マクロブロックまたは部分にはマクロブロックの下または上動きベクトルが含まれる。メモリ・レイアウトにおいては、24個の下半分のマクロブロックと、3個の上半分のマクロブロックとがある。マクロブロックの上半分はマクロブロックのブロック1, 2の動きベクトルを格納する。マクロブロックの下半分は、マクロブロックのブロック3, 4の動きベクトルを格納する。さらに詳しくは、48個のアドレス位置が下動きベクトルに割り付けられ、6個のアドレス位置が上動きベクトルに割り付けられる。この割付は、下動きベクトルは23マクロブロック分の時間格納する必要があり、上動きベクトルは3マクロブロック分の時間しか格納する必要がないという事実に対応する。図7で用いられる命名法は次の通りである：B0は現在処理中のマクロブロックを表し、現在解読中の下動きベクトル(ブロック3, 4)が格納される場所である。B-1は、1マクロブロック分だけ過去に処理されたマクロブロックの下動きベクトルが格納される場所である。同様に、T0は現行のマクロブロックの上動きベクトル(ブロック1, 2)が格納される場所であり、T-1は1マクロブロック分だけ過去に処理されたマクロブロックの上動きベクトルが格納される場所である。これはスライディング／相対アドレス指定スキームであり、絶対的なアドレス指定ではないことに留意することが重要である。B0, B-1マクロブロックは絶対アドレス・スキームの場合のように絶対アドレス0および絶対アドレス2にコード化されることはない。ベース・アドレスは常にB0の左動きベクトル(現在処理中のマクロブロックの下動きベクトル)を指示することに留意されたい。これは、2に図3のベース・アドレス・カウンタ54内の値を掛けることにより計算されるのと同じベース・アドレスである。カウンタが進み、新しいマクロブロックの処理を開始すると、上動きベクトルT0が古くなり上動きベクトルT-1になることに留意することが重要である。新しい上動きベクトルT0が下動きベクトルB-23を書き換える。同様に、新しい下動きベクトルB0は古い上動きベクトルT-2を書き換える。このように、下動きベクトルは常に上動きベクトルを書き換え、上動きベクトルは常に下動きベクトルを書き換える。上および下の動きベクトルに割り付けられる格納場所が2つの異なるタイムラインを形成することにも注目されたい。

#### 【0017】

上記の概念の例を以下に示す。この例では、カウンタの現在値が5のときS R A Mアレイ52のベース・アドレス10は現行マクロブロックの下動きベクトルが格納される場所であることを示す。現行マクロブロックの上動きベクトルは常にカウンタより6アドレス分だけ先に、この例ではアドレス16に格納されることになる。その理由は、図7のメモリ割付を注意深く見るとわかる。現行の計数は常にB0を指示し、T0のスライディング・アドレス空間は6をモジューロ加算してT0に統合すると得られる。次のマクロブロックを処理して、計数が6に進むと、全部が1マクロブロックだけ「古くなる」。ベース・アドレス10は過去1マクロブロックからの下動きベクトルを含み、ベース・アドレス12は新しい現行のマクロブロックの下動きベクトルを含む。ベース・アドレス12がマクロブロックC - 2(C - 2は上動きベクトルT-2および下動きベクトルB-2を含むマクロブロックである)の上動きベクトルを以前は含んだことに留意することが重要である。カウンタが6に進んだときに、3マクロブロック時間の間しか格納する必要のないT-2動きベクトルが終了し、下動きベクトルB0が代わりに書き込まれた。

#### 【表1】

例:

| カウンタ値 5 = ベース・アドレス 10 |     |     |     |     |     |     |             |

|-----------------------|-----|-----|-----|-----|-----|-----|-------------|

| ベース・アドレス              |     |     |     |     |     |     |             |

| 0 . . . 4             | 6   | 8   | 10  | 12  | 14  | 16  | 18 . . . 52 |

|                       | B-2 | B-1 | B0  | T-2 | T-1 | T0  | B-23        |

| カウンタ値 6 = ベース・アドレス 12 |     |     |     |     |     |     |             |

| ベース・アドレス              |     |     |     |     |     |     |             |

| 0 . . . 4             | 6   | 8   | 10  | 12  | 14  | 16  | 18 . . . 52 |

|                       | B-3 | B-2 | B-1 | B0  | T-2 | T-1 | T0          |

要するに、動きベクトル格納読出モジュール 3 8 全体の動作が次の例に基づき説明される：ベース・アドレス・カウンタ 5 4 が 6 の値を有するとすると、それが指す実際のアドレスは 1 2 になる。これは、各ベース・アドレス位置に 2 つの動きベクトルが含まれるためである。従って、実際のアドレス 1 2 が、B 0 の左動きベクトルが格納される場所となる。ルックアップ・テーブル 5 8 の入力が：ブロック番号 = 1 , O B M C / 予測モード = O B M C であるとする。するとブロック C - 1 の左、上、右および下 O B M C 動きベクトルは次のように読出される：

【表 2】

| MV選択 | 位置   | LUTアウト | ベース・アドレス | 最終アドレス |

|------|------|--------|----------|--------|

| 左    | T-2  | +3     | 12       | 15     |

| 上    | B-23 | +8     | 12       | 20     |

| 右    | T-1  | +5     | 12       | 17     |

| 下    | B-1  | -2     | 12       | 10     |

10

20

上記の例においては、図 6 を用いて、ブロック 1 の O B M C 左動きベクトルがマクロブロック C - 2 の右上ブロック、メモリ位置 T - 2 にあることがわかる。図 7 または上記の例を用いて、オフセットを決定することができる。この場合、T - 2 の右動きベクトルは、3 をモジュー口加算することにより得られる。同様に、図 6 では、右動きベクトルがメモリ・セグメント T - 1 の右側にあり、上動きベクトルはメモリ・セグメント B - 2 3 の左側にあり、下動きベクトルはメモリ・セグメント B - 1 の左側にあることがわかる。

【0018】

本発明の装置および方法が符号化動作に関して説明されたので、解読動作における本発明の使用を説明する。図 1 のデコーダ部分は、ビデオ D - A 変換器およびエンコーダ 2 6 , ポスト・プロセッサ 2 4 およびビデオ・デコーダ 2 2 を含む。

30

40

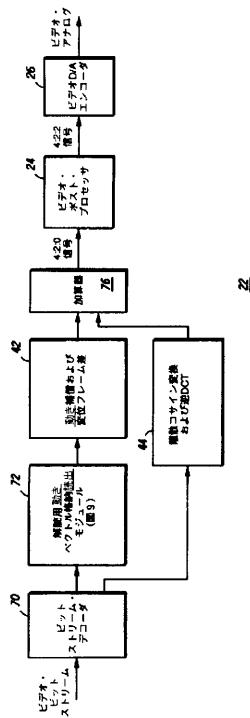

【0019】

図 8 には、ビデオ・デコーダ 2 2 の詳細が図示される。ビデオ・ビットストリームがビットストリーム・デコーダ 7 0 に入力として与えられる。ビットストリーム・デコーダ 7 0 は、解読用動きベクトル格納読出モジュール 7 2 の入力に接続される第 1 出力を有する。ビットストリーム・デコーダ 7 0 の第 2 出力は、図 2 に関連して前述された離散コサイン変換および逆 D C T 4 4 の入力に接続される。解読用動きベクトル格納読出モジュール 7 2 の出力が、図 2 に関して前述された動き補償回路 4 2 に接続される。動き補償回路 4 2 の出力は加算器 7 6 と呼ばれる合成器回路の第 1 入力に接続される。離散コサイン変換および逆 D C T 4 4 の出力は加算器 7 6 の第 2 入力に接続される。加算器 7 6 の出力は、ビデオ・フォーマット 4 : 2 : 0 で信号を提供する。ポスト・プロセッサ 2 4 の出力は、

50

ビデオ D / A エンコーダ 2 6 の入力に接続される。ポスト・プロセッサ 2 4 はビデオ・フォーマット 4 : 2 : 2 で信号を提供する。ビデオ D / A エンコーダ 2 6 の出力は、図 1 に図示されるのと同じ信号であるビデオ・アナログ信号を提供する。

【 0 0 2 0 】

動作中、デジタル・ビデオ信号がビットストリーム・デコーダ 7 0 に入力され、デコーダ 7 0 は動きベクトル差と画素データとをビデオ・ビットストリームから分離する。動きベクトル差は解読用動きベクトル格納読出モジュール回路 7 2 に送られる。これについては図 9 にさらに説明する。解読回路 7 2 の出力動きベクトルが動き補償回路 4 2 に送られる。動き補償が実行されると、次に、それに由来する画素が離散コサイン変換および逆 D C T 回路 4 4 からの出力と加算器 7 6 により加算される。ビットストリーム・デコーダ 7 0 により提供される画素データが離散コサイン変換および逆 D C T 4 4 により処理され、変換ベース圧縮解除を実行する。離散コサイン変換および逆 D C T 回路 4 4 の出力は、第 2 入力として加算器 7 6 に与えられる。加算器 7 6 は 4 : 2 : 0 のビデオ・フォーマットで信号をポスト・プロセッサ 2 4 に送り、ポスト・プロセッサ 2 4 がデジタル - アナログ変換に先立って後処理を実行する。D / A 変換が実行され、ビデオ・アナログ出力信号を提供する。

【 0 0 2 1 】

図 9 には、本発明による図 8 の解読用動きベクトル格納読出モジュール回路 7 2 が図示される。図 3 に関連する同じ要素に対する同じ参照番号が図 9 でも用いられるが、図示されるハードウェア実行例に関して容易に複製される類似の回路構成を示すためにダッシュ ( ' ) が付けられる。言い換えると、動き補償ユニット 4 2 などのように同一番号を持つ要素にダッシュが用いられない場合は、同一の要素を図 3 と図 9 の機能の間で容易に時間的に共有することができる。図 3 と図 9 との間の類似性の結果として、注目すべき主要な差は加算器回路 8 0 が追加されたことである。回路 8 0 は動きベクトルレジスタ 5 0 ' から出力を受け取る第 1 入力と、予測子計算機 6 2 ' から出力を受け取る第 2 入力を有する。加算器 8 0 の出力は、完全な動きベクトル ( 予測子および差の和 ) を与え、これは動きベクトルの S R A M アレイ 5 2 ' により格納されるために用いられる。解読用動きベクトル格納読出モジュール回路 7 2 の動作は、図 2 の動きベクトル格納読出モジュール 3 8 の動作と類似であり、前述された。従って、解読用動きベクトル格納読出モジュール回路 7 2 の動作の詳細説明は繰り返さない。類似の動作に対する顕著な違いは、解読モードにある動きベクトル差レジスタ 5 0 ' が、図 3 のレジスタ 5 0 が格納する完全な動きベクトルではなく、実際には動きベクトル差を格納することである。さらに、動きベクトルは図 3 と同様に動きベクトルの S R A M アレイ 5 2 ' に格納しなければならない。S R A M アレイ 5 2 ' に格納するために動きベクトルを得るには、予測子計算機 6 2 ' からの予測子に、動きベクトルレジスタ 5 0 ' からの動きベクトル差を加えて、動きベクトルの S R A M アレイ 5 2 ' 内に格納する動きベクトルを得なければならない。これらの動きベクトルの格納が、第 2 マクロブロックに対応する第 2 群の動きベクトルを形成する。

【 0 0 2 2 】

以上、動きベクトルを効率的に読出および格納する改善されたビデオ動画システムおよび方法が提供されたことは明らかである。メモリに動きベクトルを格納する方法は、各々がビデオ信号の部分を表す第 1 マクロブロックに対応する 4 つの動きベクトルを受信する段階によって構成される。第 1 および第 2 動きベクトルは第 1 マクロブロックの上部分に対応し、第 3 および第 4 動きベクトルはマクロブロックの下部分に対応する。第 1 および第 2 動きベクトルはメモリの第 1 部分に格納され、第 3 および第 4 動きベクトルがメモリの第 2 部分に格納される。本発明は、動きベクトルの S R A M アレイ 5 2 , 5 2 ' を実現するために必要なメモリ量を大幅に軽減する。たとえば、1 つの動きベクトルにつき 2 バイトがあるとすると、ビデオ・コデックのデコーダ部分が O B M C および予測子関数を実行するには 1 9 2 バイトの R A M 格納部が必要になる。1 9 2 は次のように計算される：

[( 2 4 マクロブロック ) ( 4 動きベクトル / マクロブロック ) ( 2 バイト / 動きベクトル ) ] = 1 9 2

10

20

30

40

50

192 バイトのRAMは必要とされる最小RAMサイズのように見えるが、本発明により大幅な節約がなされる。特に、本発明は図4に示されるマクロブロックC-2を超えてセーブする必要のないマクロブロックの上の動きベクトルをセーブまたは格納することを避ける。言い換えると、各マクロブロックC-3, C-4, C-5 ~ C-23の2つの上ブロックがなくなる（格納されない）。この空間節約方法により、メモリ・サイズ要件は次のようになる：

[ ( 下動きベクトル用の 24 マクロブロック ) ( 2 動きベクトル / マクロブロック ) ] = 48 下動きベクトル

( 上動きベクトル用の 3 マクロブロック ) ( 2 動きベクトル / マクロブロック ) = 6 上動きベクトル

総バイト = [ ( 48 + 6 ) 動きベクトル ] [ 動きベクトル毎 2 バイト ] = 108 バイト

予測子およびO B M C 関数はビデオ・コデックのエンコーダおよびデコーダ側で実行しなければならぬので、総合的な節約分は 2 ( 108 ) 対 2 ( 192 ) となる。この例では、本発明を用いることにより、上記の以前の計算の 384 バイトに対し 216 バイトのサイズの節約（約 44 % の節約）となる。本発明を H D T V 用 M P E G - 4 と共に用いると、水平解像度がさらに増すために節約分ははるかに大きくなる。本件に開示される本発明のメモリ割付法を用いることにより、マクロブロックC-2後のブロック1, 2を無くすために複雑なアドレス指定法は必要ない。本発明により、H.263 規格のO B M C および予測子関数が追加のアドレス指定用ハードウェアを追加せずに同じRAMを共有することができる。必要なハードウェアが軽減されるので、シリコン領域、コストおよび消費電力がすべて削減され、結果としてソフトウェアによる実行に匹敵し、さらにはそれよりも有利なビデオ・コデックのハードウェアによる実行が可能になる。

### 【 0023 】

当業者には、本発明の範囲から逸脱せずに修正および変形が可能であることを理解頂けよう。たとえば、「メモリ」という用語が説明される部分で種々の電子的メモリを実現することができる事が理解頂けよう。本発明の方法を実現するために種々の論理ゲート構造を利用することができる。従って、本発明は添付の請求項の範囲に入るこれらすべての変形および修正を包含するものである。

### 【 図面の簡単な説明 】

【 図 1 】 本発明で用いられるビデオ通信システムをブロック図に示す。

30

【 図 2 】 本発明によるビデオ・エンコーダをブロック図に示す。

【 図 3 】 本発明による図 2 の 動きベクトル格納読出回路構成 をブロック図に示す。

【 図 4 】 共通中間フォーマット ( C I F : Common Intermediate Format ) サイズ・フレーム内の 1 行のマクロブロック・レイアウトを等角図に示す。

【 図 5 】 H.263 規格による予測子計算のための 動きベクトル読出パターン を示す。

【 図 6 】 H.263 規格による O B M C 関数のための 動きベクトル読出パターン を示す。

【 図 7 】 図 3 の S R A M アレイに関するメモリの割付を示す。

【 図 8 】 本発明による図 1 のシステムで用いるビデオ・デコーダ・ブロック図である。

【 図 9 】 図 8 の解読機能用 動きベクトル格納読出回路構成 をブロック図に示す。

40

### 【 符号の説明 】

10 ビデオ・コデック

12 ビデオ A / D 変換器およびデコーダ

14 ビデオ・プレプロセッサ

16 ビデオ・エンコーダ ( 図 2 )

18 I / O インタフェース

20 信号プロセッサ

22 ビデオ・デコーダ ( 図 8 )

24 ビデオ・ポスト・プロセッサ

26 ビデオ D / A 変換器およびエンコーダ

50

28 DMA / DRAM インタフェース

30 DRAM (フレーム格納)

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【 図 5 】

【 四 6 】

【圖 7】

【 义 8 】

【 図 9 】

---

フロントページの続き

審査官 川崎 優

(56)参考文献 欧州特許出願公開第00838956 (EP, A1)

Nachtergaele, L., Catthoor, F., Kapoor, B., Janssens, S., Moolenaar, D., Low-power data transfer and storage exploration for H.263 videodecoder system, IEEE Journal on Selected Areas in Communications, 1998年 1月, Vol.16, No. 1, P.120-129

(58)調査した分野(Int.Cl., DB名)

H04N 7/26-50