(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4671494号

(P4671494)

(45) 発行日 平成23年4月20日(2011.4.20)

(24) 登録日 平成23年1月28日(2011.1.28)

(51) Int.Cl.

F 1

|            |           |            |         |

|------------|-----------|------------|---------|

| GO6F 3/041 | (2006.01) | GO6F 3/041 | 3 3 0 E |

| GO6F 3/042 | (2006.01) | GO6F 3/042 | J       |

| GO9F 9/00  | (2006.01) | GO9F 9/00  | 3 6 6 A |

| GO9F 9/30  | (2006.01) | GO9F 9/30  | 3 3 8   |

| HO1L 27/32 | (2006.01) | GO9F 9/30  | 3 6 5 Z |

請求項の数 7 (全 38 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2000-376766 (P2000-376766)  |

| (22) 出願日  | 平成12年12月12日 (2000.12.12)      |

| (65) 公開番号 | 特開2002-182839 (P2002-182839A) |

| (43) 公開日  | 平成14年6月28日 (2002.6.28)        |

| 審査請求日     | 平成19年12月3日 (2007.12.3)        |

前置審査

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

審査官 山崎 慎一

最終頁に続く

(54) 【発明の名称】情報装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

表示部兼入力部にEL素子と、光電変換素子とを有する画素を複数有する情報装置の駆動方法であって、

前記複数の画素各々は、第1トランジスタと、第2トランジスタとを有し、

前記第1トランジスタのソースとドレインの一方は第1配線と電気的に接続され、

前記第1トランジスタのソースとドレインの他方は前記第2トランジスタのゲートと電気的に接続され、

前記第2トランジスタのソースとドレインの一方は第2配線と電気的に接続され、

前記第2トランジスタのソースとドレインの他方は前記EL素子と電気的に接続され、

1フレーム期間は複数のサブフレーム期間を有し、

前記複数のサブフレーム期間のそれぞれは、アドレス期間とサステイン期間とを有し、

前記情報装置をイメージセンサとして用いる際に、前記複数のサブフレーム期間の全てのサステイン期間において、前記複数の画素の全ての前記EL素子を発光させることによつて読みとり対象物体に光を照射し、

前記読みとり対象物体において反射した光を前記複数の画素の前記光電変換素子に入力し、

前記光電変換素子に入力された光を電気信号に変換して読み出すことによつて、前記読みとり対象物体の表面の情報を得ることを特徴とする情報装置の駆動方法。

## 【請求項 2】

10

20

請求項 1 において、

前記複数の画素各々は、第3トランジスタと、第4トランジスタと、第5トランジスタとを有し、

前記第3トランジスタのゲートは前記光電変換素子と電気的に接続され、

前記第3トランジスタのソースは導通状態となった前記第4トランジスタを介して第3配線と電気的に接続され、

前記光電変換素子は導通状態となった前記第5トランジスタを介して第4配線と電気的に接続されていることを特徴とする情報装置の駆動方法。

【請求項 3】

請求項 1 または 2 において、

10

前記光電変換素子は、フォトダイオードであることを特徴とする情報装置の駆動方法。

【請求項 4】

請求項 3 において、

前記フォトダイオードは、アノード電極と、カソード電極と、前記アノード電極と前記カソード電極との間に挟まれた光電変換層とを有することを特徴とする情報装置の駆動方法。

【請求項 5】

請求項 4 において、

前記光電変換層は、有機材料又は非晶質半導体によって構成されることを特徴とする情報装置の駆動方法。

20

【請求項 6】

請求項 1 乃至 請求項 5 のいずれか一において、

前記読みとり対象物体の表面の情報は、生体情報であることを特徴とする情報装置の駆動方法。

【請求項 7】

請求項 6 において、

前記生体情報は、掌紋又は指紋であることを特徴とする情報装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

30

本発明は、ペン等によって情報を入力する機能を有する情報装置に関する。特に、表示装置の画面上でペン入力の操作を行う情報装置に関する。表示装置としては、特に E L 素子を用いた E L 表示装置に関する。また、この情報装置を有する携帯情報装置に関する。

【0002】

なお、本明細書において、E L 素子とは、一重項励起子からの発光（蛍光）及び三重項励起子からの発光（燐光）の両方を利用するものを示すとする。

【0003】

【従来の技術】

携帯情報装置において、小型化及び操作性の面から、ペン入力方式の携帯情報装置の需要が高まっている。ペン入力方式は、専用の、もしくは任意のペン等を用い、表示画面にペン先を接触させる、もしくは近付けることによって、情報の入力を行う方式のことである。

40

【0004】

つまり、表示画面上のペン先が指し示した位置に対応する情報の入力を行う。表示画面は、ペン入力画面も兼ねる。このペン入力方式では、ペン入力画面上で、ペンが指し示した位置を特定する必要がある。ペン入力方式の手法には、抵抗膜式や光学式等がある。

【0005】

始めに、抵抗膜式について説明する。

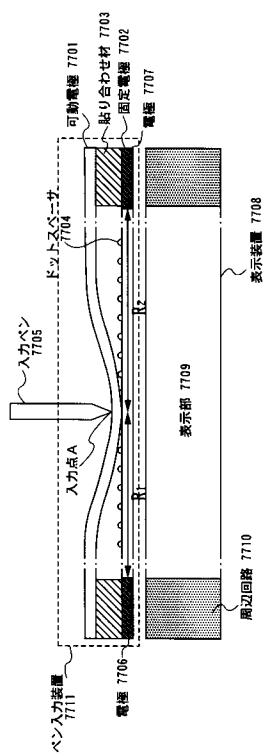

【0006】

図 7 は、抵抗膜式のペン入力装置の構造を示す模式図である。なお、ペン入力装置 771

50

1は、表示装置7708の上部に形成されている。表示装置7708は、表示部7709と周回路7710を有する。

【0007】

ペン入力装置7711において、可動電極7701と固定電極7702は、ドットスペース7704を挟んで、貼り合わせ材7703によって約100～300μmの間隔で互いに平行に接続されている。ここで、ペン入力装置7711を介して、表示装置7708の表示部7709に映し出される画像を見る能够るように、可動電極7701及び固定電極7702は、透光性を有する導電材料で形成されている。透光性を有する導電材料としては、一般に、酸化インジウム・スズ(ITO)膜が用いられる。

【0008】

抵抗膜式では、ペン入力装置7711上の入力ペン7705で指示した位置(図7中、入力点A)において、可動電極7701と固定電極7702は接する。このとき、入力点Aの位置を、2つの位置検出用の電極7706及び7707からの抵抗R1及びR2の比として読み取る方式である。

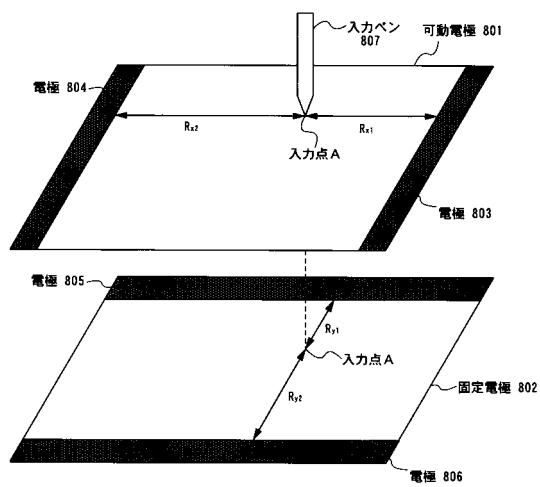

【0009】

具体的に、位置の読み取りを行う際の例を図8に示す。入力ペン807によって、入力点Aにおいて、可動電極801側より圧力を加えて、固定電極802と接触させる。ここで、可動電極801の2つの電極803と804間に電圧をかけ、可動電極801内部に電位の勾配を発生させる。このときの入力点Aの電位VAを測定することによって、電極803と電極804から入力点Aまでの抵抗値Rx1及びRx2を知ることができる。ここで、可動電極801の膜質が均一であるとすると、この抵抗値Rx1及びRx2は、電極803と804それぞれから入力点Aまでの距離に比例する。

【0010】

同様に今度は、固定電極802の2つの電極805と806間に電圧を加えて、固定電極802内部に電位の勾配が発生する。このときの入力点Aの電位VAを知ることで、電極805と電極806から入力点Aまでの抵抗値Ry1及びRy2を知ることができる。ここで、固定電極802の膜質が均一であるとすると、この抵抗値Ry1及びRy2は、電極805と806それぞれからA点までの距離に比例する。こうして、入力点Aの位置を知ることができる。

【0011】

なお、入力点Aの位置を測定するための、入力点Aの電位の測定方法は、上記構成に限らず、いろいろな方法を用いることができる。

【0012】

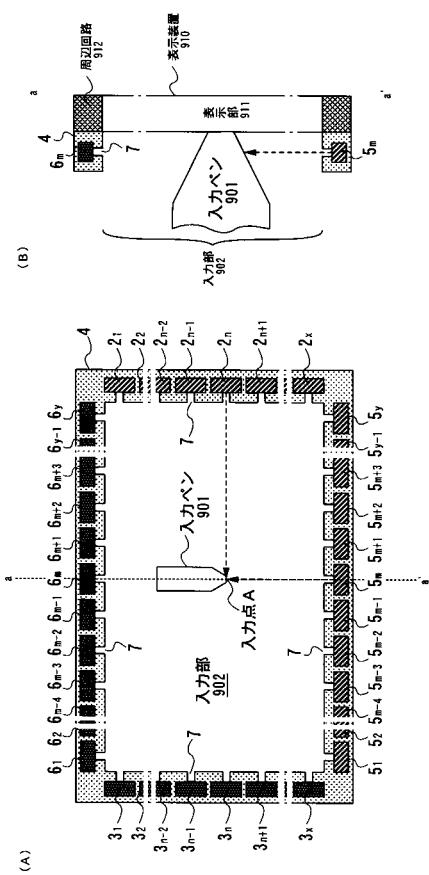

次に、光学式のペン入力装置について説明する。図9(A)に、この方式のペン入力装置の上面模式図を示す。

【0013】

入力部902に、入力用ペン901のペン先が触れるとき、触れた位置を検出する。この位置検出の動作について説明する。

【0014】

入力部902の周りには、右辺部に、x-1個の発光ダイオード(以下、LEDという)2<sub>1</sub>～2<sub>x</sub>が配置され、左辺部に、x-1個のフォトトランジスタ(以下、PTという)3<sub>1</sub>～3<sub>x</sub>が、LED2<sub>1</sub>～2<sub>x</sub>と対向するように配置され、枠4に埋設されている。

【0015】

一方、下辺部に、y-1個のLED5<sub>1</sub>～5<sub>y</sub>が配置され、上辺部に、y-1個のPT6<sub>1</sub>～6<sub>y</sub>が、LED5<sub>1</sub>～5<sub>y</sub>と対向するように配置され、枠4に埋設されている。

【0016】

そして、LED2<sub>1</sub>～2<sub>x</sub>とPT3<sub>1</sub>～3<sub>x</sub>は、x-1本の水平方向のタッチ入力ラインを形成し、LED5<sub>1</sub>～5<sub>y</sub>とPT6<sub>1</sub>～6<sub>y</sub>は、y-1本の垂直方向のタッチ入力ラインを形成する。

【0017】

10

20

30

40

50

ここで、タッチ入力ラインとは、向かい合う一対のLEDとPTにおいて、LEDから発した光がPTに入力される時に通過する経路のことである。

【0018】

なお、 $3_1 \sim 3_x$ 及び $6_1 \sim 6_y$ として、PTを用いたが、PTに限らず、光を電気信号に変換する、光電変換素子であれば自由に用いることができる。

【0019】

LED $2_1 \sim 2_x$ 及び $5_1 \sim 5_y$ それぞれから放射され、PT $3_1 \sim 3_x$ 及び $6_1 \sim 6_y$ にそれぞれ入射される光の指向性を高めるため、各素子が埋設された枠4の前方に、円孔状のスリット7がそれぞれ形成されている。

【0020】

図9(B)は、図9(A)のa~a'の断面図である。表示装置910がペン入力装置の下部に形成されている。表示装置910は、表示部911及び周辺回路912によって構成されている。抵抗膜式とは異なり、表示部911に映し出される画像を直接見ることが可能である。

【0021】

再び、図9(A)を参照する。

【0022】

上記構成のペン入力装置において、水平光のタッチ入力ライン及び垂直方向のタッチ入力ラインそれぞれを同時に、対向するLEDとPTの対について一対ずつ端から順に発光及び受光を行わせる(以下、スキャンという)。

【0023】

ここで、入力ペン901で入力部902内的一点を指示示す。今、図9(A)中の入力点Aを指示示したとする。このとき、入力点Aに対応する2本のタッチ入力ライン $2_n \sim 3_n$ 及び $5_m \sim 6_m$ の間で光が遮断され、入力ペン901が触れた位置Aが認識される。

【0024】

【発明が解決しようとする課題】

抵抗膜式は、情報入力の度に、可動電極を機械的に変形させる必要がある。このため、繰り返しの変形により、可動電極が疲労し、破壊する可能性がある。これは耐久性の上で問題となる。

【0025】

また、破壊にまで至らないとしても、繰り返しの変形や、作製上の過程で、マイクロメートルオーダーの微小なクラックが形成された場合において、ITO膜の導電性が均一でなくなるため、ペン入力の位置の検出精度に問題が発生する。

【0026】

加えて、可動電極及び固定電極の、2枚の電極を介して、表示装置の画像を読み取ることになる。このとき、透明電極の透過率は100%ではないため、表示装置からの光が減衰し画像の輝度が落ちるといった画面の視認性の問題が発生する。そのため、画像の輝度を上げようとして表示装置の発光を強くしなくてはならず、装置の消費電力の増加が問題となる。

【0027】

また、外部から応力がかかり、可動電極及び固定電極の、2つの電極間の距離が $40 \mu m$ 以下になると、2つの電極間での反射光の干渉の効果により、ニュートンリングが現れるといった問題もある。

【0028】

さらに、2枚の電極を平行に配置したコンデンサ構造のため、バッテリー電源使用の際、消耗が大きいという問題がある。これは、低消費電力が望まれる携帯情報機器において重大な問題である。

【0029】

一方、光学式のペン入力装置では、抵抗膜式のように薄膜を繰り返し変形させる必要は無く、機械的な耐久性の問題は無い。また、透明電極を介して、表示装置を見ることになら

10

20

30

40

50

ず、画面の視認性の上で問題も少ない。

【0030】

しかし、発光素子が発した光が、その対となる受光素子にまっすぐに受光されない場合、たとえ、入力ペン等である位置を指示したとしても、認識されない可能性がある。

【0031】

また、表示装置上に、発光素子と受光素子の列やスリット等を形成する必要があるため、小型化が難しいという問題がある。

【0032】

【課題を解決するための手段】

そこで、本発明のペン入力機能を有する情報装置では、表示装置の画素に、EL（エレクトロルミネッセンス）素子と光電変換素子の両方を配置し、ペン先が発光するペンによって情報入力を行う。 10

【0033】

EL素子は、自発光型素子であり、主にEL表示装置に用いられている。EL表示装置とは、有機EL表示装置（OLED：Organic EL Display）又は有機ライトエミッティングダイオード（OLED：Organic Light Emitting Diode）ともいう。

【0034】

EL素子は、一対の電極（陽極と陰極）の間にEL層が挟まった構造となっている。EL層は通常、積層構造となっている。代表的には、コダック・イーストマンカンパニーのTangらが提案した「正孔輸送層／発光層／電子輸送層」という積層構造が挙げられる。この構造は発光効率が極めて高いことが知られている。 20

【0035】

また他にも、電極上に、「正孔注入層／正孔輸送層／発光層／電子輸送層」と積層したものや、「正孔注入層／正孔輸送層／発光層／電子輸送層／電子注入層」と積層した構造のものでも良い。また、発光層に蛍光性色素等をドーピングしても良い。

【0036】

本明細書において、一対の電極間に設けられる全ての層を指してEL層と呼ぶ。よって上述した正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等は、すべてEL層に含まれる。上記構成のEL層に一対の電極から所定の電圧を印加する。それによって、発光層においてキャリアの再結合が起こって発光する。 30

【0037】

光電変換素子としては、フォトダイオード等を用いることができる。本明細書においてフォトダイオードとは、カソード電極と、アノード電極と、カソード電極とアノード電極の間に光電変換層を有している。

【0038】

なお、フォトダイオードはこの構成に限らず、p型半導体層とn型半導体層の間に、i型（真性）半導体層からなる光電変換層を有する、PIN構造のものであっても良い。また、p型半導体層と、n型半導体層からなるPN型のフォトダイオードであっても良い。

【0039】

また、光電変換素子として、有機物から構成される光電変換層等を有するものを用いても良い。 40

【0040】

フォトダイオードは、カソード電極とアノード電極の間（フォトダイオードの電極間と呼ぶことにする）に逆バイアス電圧を印加した後、光を照射すると、光によって生じたキャリアによって、電極間の電圧が低下する。このとき、照射された光の強度が高いほど、この電圧が低下する量も大きい。これを利用して、フォトダイオードに光が照射された場合の電圧と、照射されなかった場合の電圧を比較することで、光を電気信号として検出する。

【0041】

EL素子とフォトダイオードとは、同一基板上にマトリクス状に形成され、そして同じく 50

マトリクス状に設けられた薄膜トランジスタ（TFT）にを用いて、EL素子とフォトダイオードのそれぞれの動作を制御する。

【0042】

これによって、表示画像の輝度を損なわず、また鮮明な画像を表示し、耐久性に優れ、小型化可能で、精度の良い、低消費電力のペン入力機能を有する情報装置が得られる。

【0043】

以下に、本発明の情報装置の構成について記載する。

【0044】

本発明によって、

複数の画素を有する情報装置において、

10

入力用ペンを有し、

前記複数の画素はそれぞれEL素子と光電変換素子とを有し、

前記入力ペンは、光線を発し、

前記光線が、前記光電変換素子に入力されることにより情報入力を行うことを特徴とする情報装置が提供される。

【0045】

前記EL素子と前記光電変換素子とは、同一基板上に形成されていることを特徴とする情報装置であってもよい。

【0046】

前記光電変換素子は、フォトダイオードであることを特徴とする情報装置であってもよい

20

。

【0047】

本発明によって、

複数の画素を有する情報装置において、

EL表示用ソース信号線駆動回路と、EL表示用ゲート信号線駆動回路と、複数のEL表示用ソース信号線と、複数のEL表示用ゲート信号線と、複数の電源供給線と、入力ペンとを有し、

前記EL表示用ソース信号線駆動回路は、前記複数のEL表示用ソース信号線に信号を出力し、

前記EL表示用ゲート信号線駆動回路は、前記複数のEL表示用ゲート信号線に信号を出力し、

30

前記複数の画素は、それぞれEL表示部とセンサ部とを有し、

前記EL表示部と前記センサ部とは、同一基板上に形成され、

前記EL表示部は、スイッチング用TFTと、EL駆動用TFTと、EL素子とを有し、前記スイッチング用TFTのゲート電極は、前記複数のEL表示用ゲート信号線のうちの一本に接続され、

前記スイッチング用TFTのソース領域とドレイン領域とは、一方は、前記複数のEL表示用ソース信号線のうちの一本と接続され、もう一方は、前記EL駆動用TFTのゲート電極に接続され、

前記EL駆動用TFTのソース領域とドレイン領域とは、一方は、前記複数の電源供給線のうちの一本に接続され、もう一方は、前記EL素子に接続され、

40

前記センサ部は、フォトダイオードを有し、

前記入力ペンは、光線を発し、

前記光線が前記フォトダイオードに入力されることにより情報入力を行うことを特徴とする情報装置が提供される。

【0048】

本発明によって、

複数の画素を有する情報装置において、

センサ用ソース信号線駆動回路と、センサ用ゲート信号先駆回路と、複数のセンサ用出力配線と、複数のセンサ用ゲート信号線と、複数のリセット用ゲート信号線と、複数のセン

50

サ用電源線と、入力ペンとを有し、

前記センサ用ソース信号線駆動回路は、前記複数のセンサ用出力配線から信号を読み取り、

前記センサ用ゲート信号線駆動回路は、前記複数のセンサ用ゲート信号線と、複数のリセット用ゲート信号線に信号を出力し、

前記複数の画素は、それぞれE L表示部とセンサ部とを有し、

前記E L表示部と前記センサ部とは、同一基板上に形成され、

前記センサ部は、選択用TFTと、バッファ用TFTと、リセット用TFTと、フォトダイオードとを有し、

前記選択用TFTのゲート電極は、前記複数のセンサ用ゲート信号線のうちの1本に接続され、

前記選択用TFTのソース領域とドレイン領域とは、一方は、前記複数のセンサ用出力配線のうちの1つに接続され、もう一方は、前記バッファ用TFTのソース領域もしくはドレイン領域のどちらか一方に接続され、

前記バッファ用TFTのソース領域とドレイン領域とで、前記選択用TFTと接続されていない側は、前記複数のセンサ用電源線のうちの1つに接続され、

前記バッファ用TFTのゲート電極は、前記フォトダイオード及び前記リセット用TFTのソース領域もしくはドレイン領域に接続され、

前記リセット用TFTのソース領域もしくはドレイン領域で、前記バッファ用TFTと接続されていない側は、前記複数のセンサ用電源線のうちの1つに接続され、

前記リセット用TFTのゲート電極は、前記複数のリセット用ゲート信号線のうちの1つに接続され、

前記E L表示部は、E L素子を有し、

前記入力ペンは光線を発し、

前記光線が前記フォトダイオードに入力されることにより情報入力をを行うことを特徴とする情報装置が提供される。

#### 【0049】

本発明によって、

複数の画素を有する情報装置において、

E L表示用ソース信号線駆動回路と、E L表示用ゲート信号線駆動回路と、センサ用ソース信号線駆動回路と、センサ用ゲート信号先駆回路と、複数のE L表示用ソース信号線と、複数のE L表示用ゲート信号線と、複数の電源供給線と、複数のセンサ用出力配線と、複数のセンサ用ゲート信号線と、複数のリセット用ゲート信号線と、複数のセンサ用電源線と、入力ペンとを有し、

前記E L表示用ソース信号線駆動回路は、前記複数のE L表示用ソース信号線に信号を出力し、

前記E L表示用ゲート信号線駆動回路は、前記複数のE L表示用ゲート信号線に信号を出力し、

前記センサ用ソース信号線駆動回路は、前記複数のセンサ用出力配線から信号を読み取り、

前記センサ用ゲート信号線駆動回路は、前記複数のセンサ用ゲート信号線と、複数のリセット用ゲート信号線に信号を出力し、

前記複数の画素は、E L表示部とセンサ部とを有し、

前記E L表示部と前記センサ部とは、同一基板上に形成され、

前記E L表示部は、スイッチング用TFTと、E L駆動用TFTと、E L素子とを有し、前記スイッチング用TFTのゲート電極は、前記複数のE L表示用ゲート信号線のうちの一本に接続され、

前記スイッチング用TFTのソース領域とドレイン領域とは、一方は、前記複数のE L表示用ソース信号線のうちの一本と接続され、もう一方は、前記E L駆動用TFTのゲート電極に接続され、

10

20

30

40

50

前記 E L 駆動用 TFT のソース領域とドレイン領域とは、一方は、前記複数の電源供給線のうちの一本に接続され、もう一方は、前記 E L 素子に接続され、

前記センサ部は、選択用 TFT とバッファ用 TFT と、リセット用 TFT とフォトダイオードとを有し、

前記選択用 TFT のゲート電極は、前記複数のセンサ用ゲート信号線のうちの 1 本に接続され、

前記選択用 TFT のソース領域とドレイン領域とは、一方は、前記複数のセンサ用出力配線のうちの 1 つに接続され、もう一方は、前記バッファ用 TFT のソース領域もしくはドレイン領域のどちらか一方に接続され、

前記バッファ用 TFT のソース領域とドレイン領域とで、前記選択用 TFT と接続されていない側は、前記複数のセンサ用電源線のうちの 1 つに接続され、

前記バッファ用 TFT のゲート電極は、前記フォトダイオード及び前記リセット用 TFT のソース領域もしくはドレイン領域に接続され、

前記リセット用 TFT のソース領域もしくはドレイン領域で、前記バッファ用 TFT と接続されていない側は、前記複数のセンサ用電源線のうちの 1 つに接続され、

前記リセット用 TFT のゲート電極は、前記複数のリセット用ゲート信号線のうちの 1 つに接続され、

前記入力ペンは、光線を発し、

前記光線が前記フォトダイオードに入力されることにより情報入力をを行うことを特徴とする情報装置が提供される。

#### 【 0 0 5 0 】

前記光線は、レーザー光であることを特徴とする情報装置であってもよい。

#### 【 0 0 5 1 】

前記光線は、紫外光または近紫外光であることを特徴とする情報装置であってもよい。

#### 【 0 0 5 2 】

前記 E L 表示用ソース信号線駆動回路と E L 表示用ゲート信号駆動回路とは、前記 E L 表示部及び前記センサ部が形成された基板と同一基板上に形成されていることを特徴とする情報装置であってもよい。

#### 【 0 0 5 3 】

前記センサ用ソース信号線駆動回路とセンサ用ゲート信号駆動回路とは、前記 E L 表示部及び前記センサ部が形成された基板と同一基板上に形成されていることを特徴とする情報装置であってもよい。

#### 【 0 0 5 4 】

前記 E L 表示用ソース信号線駆動回路と、 E L 表示用ゲート信号駆動回路と、前記センサ用ソース信号線駆動回路と、センサ用ゲート信号駆動回路とは、前記 E L 表示部及び前記センサ部が形成された基板と同一基板上に形成されていることを特徴とする情報装置であってもよい。

#### 【 0 0 5 5 】

前記フォトダイオードは、アノード電極と、カソード電極と、前記アノード電極と前記カソード電極との間に挟まれた光電変換層とを有することを特徴とする情報装置であってもよい。

#### 【 0 0 5 6 】

前記光電変換層は、有機材料によって構成されていることを特徴とする情報装置であってもよい。

#### 【 0 0 5 7 】

前記フォトダイオードは、p 型半導体層と、n 型半導体層と、前記 p 型半導体層と前記 n 型半導体層の間に挟まれた光電変換層とを有することを特徴とする情報装置であってもよい。

#### 【 0 0 5 8 】

前記光電変換層は、非晶質半導体によって構成されることを特徴とする情報装置であって

10

20

30

40

50

もよい。

【0059】

前記 E L 素子が発した光は、被写体の表面に照射され、

前記被写体の表面に照射された光が、前記被写体の表面によって反射され、

前記被写体の表面によって反射された光が、前記光電変換素子に入力されることにより、前記被写体の表面の情報が、画像として入力されることを特徴とする情報装置であってもよい。

【0060】

前記被写体の表面の情報は、生体情報であることを特徴とする情報装置であってもよい。

【0061】

前記生体情報は、掌紋であることを特徴とする情報装置であってもよい。

10

【0062】

前記生体情報は、指紋であることを特徴とする情報装置であってもよい。

【0063】

前記情報装置は、携帯情報端末、PDA であってもよい。

【0064】

【発明の実施の形態】

本発明の実施の形態について説明する。

【0065】

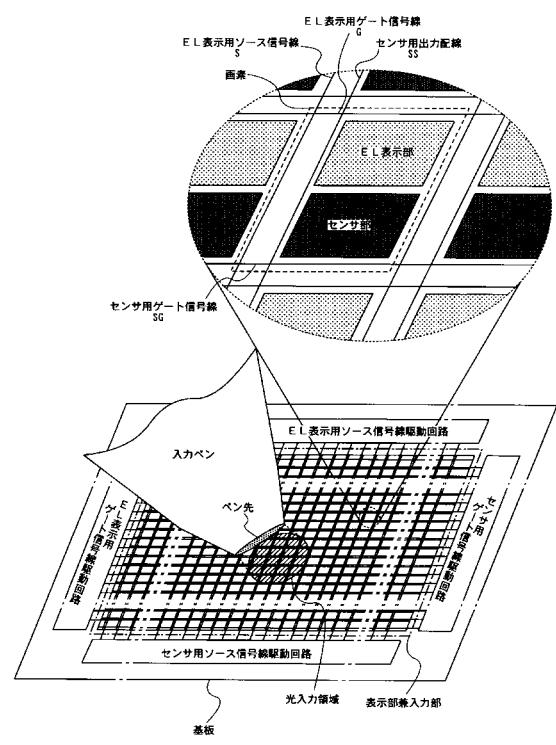

図1に本発明のペン入力機能を有する情報装置の模式図を示す。

20

【0066】

本実施の形態では、ペン先が発光する入力ペンによって、表示部兼入力部内部を示すことによって情報を入力する手法について説明する。ここで、表示部兼入力部において各画素は、E L 素子を有する E L 表示部と、光電変換素子を有するセンサ部とにより構成されている。これらの E L 表示部とセンサ部は、表示部兼入力部の周囲に配置された、E L 表示用ソース信号線駆動回路、E L 表示用ゲート信号線駆動回路、センサ用ソース信号線駆動回路、センサ用ゲート信号線駆動回路からの信号によって駆動される。

【0067】

ここで、表示部兼入力部が形成された基板と同じ基板上に、各駆動回路（E L 表示用ソース信号線駆動回路、E L 駆動用ゲート信号線駆動回路、センサ用ソース信号線駆動回路、センサ用ゲート信号線駆動回路）が形成されている。

30

【0068】

E L 表示用ソース信号線駆動回路からの信号は、E L 表示用ソース信号線 S によって各画素の E L 表示部に伝達され、E L 表示用ゲート信号線駆動回路からの信号は、E L 表示用ゲート信号線 G によって各画素の E L 表示部に伝達される。

【0069】

センサ用ソース信号線駆動回路は、センサ用出力配線 S S によって各画素のセンサ部の信号を読み取り、センサ用ゲート信号線駆動回路は、センサ用ゲート信号線 S G によって各画素のセンサ部に信号を伝達する。

【0070】

40

なお、図1において、各画素に配線される E L 素子用の電源線（電源供給線）や、センサ用の電源線やリセット用信号線（リセット用ゲート信号線）等は図示していない。

【0071】

表示部兼入力部において各画素は、E L 表示部において表示を行う。

【0072】

同時に、入力ペンのペン先が発光し光線が発し、ペン先が指示した付近のセンサ部（光入力領域）に、光が入力される。こうして、入力ペンが指示した位置が認識される。

【0073】

次に、表示部兼入力部の具体的な回路構成について説明する。

【0074】

50

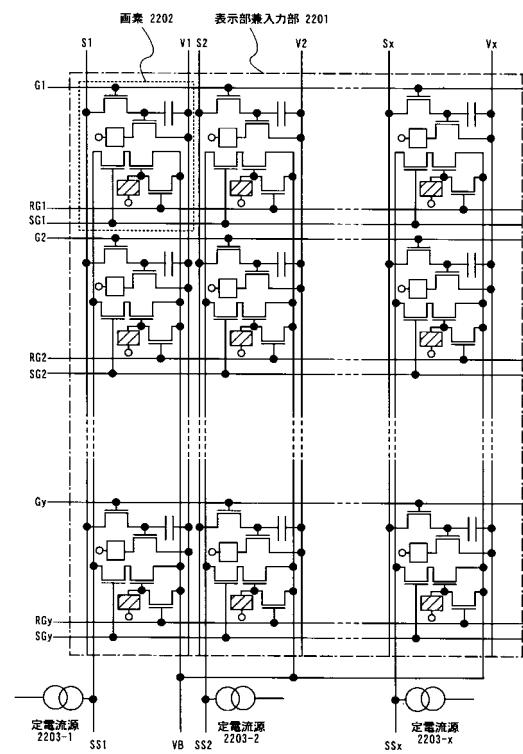

図2は、表示部兼入力部の回路構成の例を示した図である。

【0075】

表示部兼入力部2201は、EL表示用ソース信号線S1～Sxと、EL表示用ゲート信号線G1～Gyと、電源供給線V1～Vxと、センサ用出力配線SS1～SSxと、センサ用ゲート信号線SG1～SGyと、リセット用ゲート信号線RG1～RGyと、センサ用電源線VBを有する。

【0076】

表示部兼入力部2201は、複数の画素2202を有している。複数の画素2202はそれぞれ、EL表示用ソース信号線S1～Sxのうちの一本と、EL表示用ゲート信号線G1～Gyのうちの一本と、電源供給線V1～Vxのうちの一本と、センサ用出力配線SS1～SSxのうちの一本と、センサ用ゲート信号線SG1～SGyのうちの一本と、リセット用ゲート信号線RG1～RGyのうちの一本と、センサ用電源線VBを有する。

10

【0077】

センサ用出力配線SS1～SSxはそれぞれ、定電流源2203-1～2203-xに接続されている。

【0078】

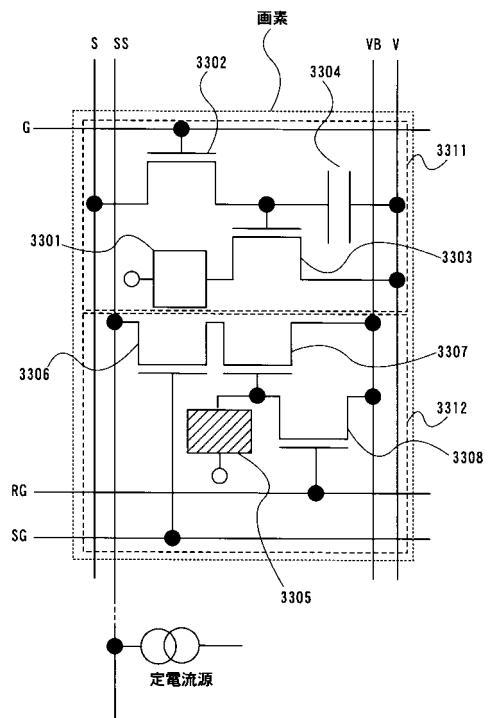

図3に、図2の画素2202の詳しい構成を示す。なお、EL表示用ソース信号線Sは、EL表示用ソース信号線S1～Sxのうちいずれか1つを示す。EL表示用ゲート信号線Gは、EL駆動用ゲート信号線G1～Gyのいずれか1つを示す。電源供給線Vは、電源供給線V1～Vxのいずれか1つを示す。センサ用出力配線SSは、センサ用出力配線SS1～SSxのうちいずれか1つを示す。センサ用ゲート信号線SGは、センサ用ゲート信号線SG1～SGyのうちいずれか1つを示す。

20

【0079】

画素は、EL表示部3311とセンサ部3312を有している。

【0080】

EL表示部3311は、EL素子3301、スイッチング用TFT3302、EL駆動用TFT3303、コンデンサ3304によって構成されている。なお、コンデンサ3304は、必ずしも設ける必要はない。

【0081】

スイッチング用TFT3302のゲート電極は、EL表示用ゲート信号線Gに接続され、ソース領域とドレイン領域とは、一方はEL表示用ソース信号線Sに接続され、もう一方は、コンデンサ3304の一方の電極及びEL駆動用TFT3303のゲート電極に接続されている。コンデンサ3304のもう一方の電極は、電源供給線Vに接続されている。EL駆動用TFT3303のソース領域とドレイン領域とは、一方は電源供給線Vに接続され、もう一方はEL素子3301に接続されている。

30

【0082】

EL素子3301の陽極と陰極で、EL駆動用TFT3303のソース領域もしくはドレイン領域と接続されている側が画素電極となり、EL駆動用TFT3303のソース領域もしくはドレイン領域と接続されていない側が対向電極となる。

40

【0083】

センサ部3312は、フォトダイオード3305、選択用TFT3306、バッファ用TFT3307、リセット用TFT3308によって構成されている。

【0084】

フォトダイオード3305の構成としては、本実施の形態では、アノード電極とカソード電極の間に光電変換層を挟んだショットキー型のものを用いる。

【0085】

フォトダイオードに入射した光は、光電変換層に吸収されキャリアを形成する。この光によって形成されたキャリアの量は、光電変換層に吸収された光の量に依存する。

【0086】

ここでは光を電気信号に変換する光電変換素子として、上記構成のフォトダイオードを用

50

いたが、これに限らず、PIN型や、PN型のフォトダイオードや、アバランシェダイオード等を用いることもできる。

【0087】

なお、PIN型のフォトダイオードは、p型半導体層と、n型半導体層と、p型半導体層とn型半導体層の間に挟まれたi型(真性)半導体層によって構成される。ここで、i型半導体層は、光電変換層とも呼ばれる。

【0088】

またこれらのフォトダイオードが有する光電変換層として、非晶質シリコン膜(アモルファスシリコン膜)等の非晶質半導体を用いることで、光電変換層での光の吸収率を高くすることができる。

10

【0089】

また、光電変換素子として、有機物から構成される光電変換層等を有するものを用いても良い。

【0090】

選択用TFT3306のゲート電極は、センサ用ゲート信号線SGに接続され、ソース領域とドレイン領域とは、一方はセンサ用出力配線SSと接続され、もう一方は、バッファ用TFT3307のソース領域もしくはドレイン領域と接続されている。バッファ用TFT3307のソース領域とドレイン領域で、選択用TFT3306と接続されていない側は、センサ用電源線VBと接続されている。リセット用TFT3308のゲート電極はリセット用ゲート信号線RGに接続され、ソース領域とドレイン領域とは、一方はセンサ用電源線VBと接続され、もう一方は、バッファ用TFT3307のゲート電極及びフォトダイオード3305に接続されている。

20

【0091】

センサ用電源線VBは、一定電位(基準電位)に保たれている。センサ用出力配線SSは、定電流源に接続されている。

【0092】

なお、EL表示用ソース信号線駆動回路、センサ用のソース信号線駆動回路、EL表示用ゲート信号線駆動回路、センサ用ゲート信号線駆動回路は、公知の構成の回路を用いればよい。

30

【0093】

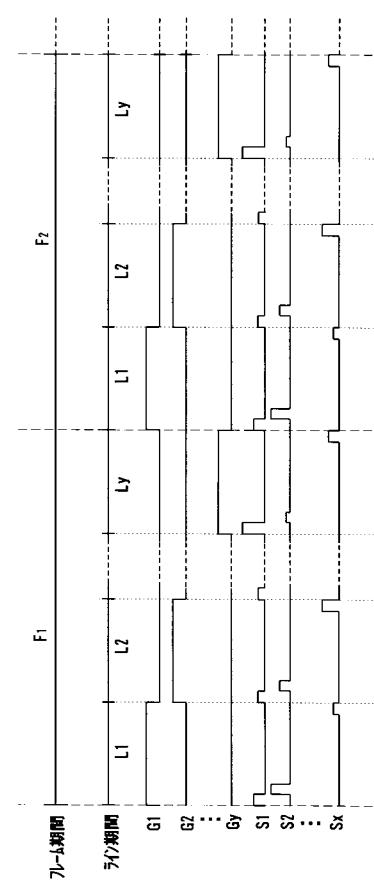

上記構成の表示部兼画素部の動作方法について、図2及び図3の回路図と、図17及び図18のタイミングチャートを用いて説明する。

【0094】

まず、EL表示部の動作方法について、図2及び図3と、図17を用いて説明する。

【0095】

なお、ここでは、ソース信号線S1～Sxにアナログの信号を入力し、表示を行う方式(以下、アナログ方式と呼ぶ)について説明する。

【0096】

ここで、スイッチング用TFT3302及びEL駆動用TFT3303は、nチャネル型TFTであるとするが、スイッチング用TFT3302及びEL駆動用TFT3303は、それぞれnチャネル型TFTでもpチャネル型TFTでもどちらでも良い。ただし、EL素子3301の陽極が画素電極となる場合、EL駆動用TFT3303は、pチャネル型TFTであることが望ましく、逆に、EL素子3301の陰極が画素電極となる場合には、EL駆動用TFT3303は、nチャネル型TFTであることが望ましい。

40

【0097】

はじめ、EL表示用ゲート信号線G1に入力された信号により、EL表示用ゲート信号線G1に接続された全てのスイッチング用TFT3302が、導通状態になる。

【0098】

ある一本のEL表示用ゲート信号線が選択されている期間を、1ライン期間と呼び、特に、EL表示用ゲート信号線G1が選択されている期間を第1のライン期間L1と呼ぶ。こ

50

のライン期間 L 1 の間に、E L 表示用ソース信号線 S 1 ~ S x に順にアナログ信号が入力される。E L 表示用ソース信号線に入力されたアナログ信号電圧は、コンデンサ 3 3 0 4 及び E L 駆動用 T F T 3 3 0 3 のゲート電極に印加される。E L 駆動用 T F T 3 3 0 3 は、そのゲート電極に印加されたこのアナログ信号電圧に対応するソース・ドレイン間電流を、電源供給線 V より E L 素子 3 3 0 1 に流す。この電流に応じた輝度で E L 素子 3 3 0 1 は発光する。

#### 【 0 0 9 9 】

次に、E L 表示用ゲート信号線 G 2 が選択され、E L 表示用ゲート信号線 G 2 に接続された全てのスイッチング用 T F T 3 3 0 2 が導通状態になる。こうして、第 2 のライン期間 L 2 が始まる。この後、E L 表示用ソース信号線 S 1 ~ S x に順に信号電圧が入力される。この信号電圧が、E L 駆動用 T F T 3 3 0 3 のゲート電極に印加され、そのゲート電極に印加されたこのアナログ信号電圧に対応するソース・ドレイン間電流を、電源供給線 V より E L 素子 3 3 0 1 に流す。この電流に応じた輝度で E L 素子 3 3 0 1 は発光する。

10

#### 【 0 1 0 0 】

上記動作を、すべての E L 表示用ゲート信号線 G 1 ~ G y について繰り返し、1 フレーム期間 F 1 が終了する。その後、第 2 のフレーム期間 F 2 が始まる。この動作を繰り返すことによって、画像を表示する。

#### 【 0 1 0 1 】

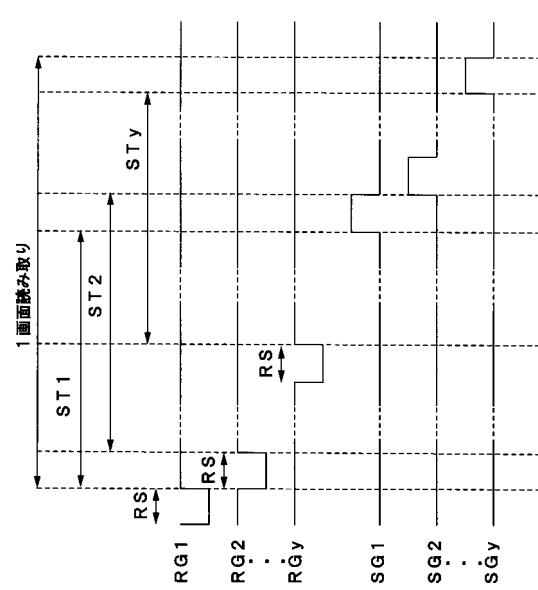

次に、センサ部の動作方法について、図 2 及び図 3、図 1 8 を用いて説明する。

#### 【 0 1 0 2 】

20

ここで、リセット用 T F T 3 3 0 8 は n チャネル型 T F T とし、バッファ用 T F T 3 3 0 7 は p チャネル型 T F T とし、選択用 T F T 3 3 0 6 は n チャネル型 T F T としたが、リセット用 T F T 3 3 0 8 、バッファ用 T F T 3 3 0 7 及び選択用 T F T 3 3 0 6 はそれぞれ、n チャネル型 T F T でも p チャネル型 T F T でもどちらでも良い。なお、リセット用 T F T 3 3 0 8 とバッファ用 T F T 3 3 0 7 の極性は逆の方が望ましい。

#### 【 0 1 0 3 】

始め、リセット用ゲート信号線 R G 1 の信号により、リセット用ゲート信号線 R G 1 に接続された全てのリセット用 T F T 3 3 0 8 は、導通状態にある。このとき、リセット用ゲート信号線は、選択されているということにする。なお、他のリセット用ゲート信号線 R G 2 ~ R G y に接続されたすべてのリセット用 T F T 3 3 0 8 は、すべて非導通状態にある。このとき、センサ用電源線 V B の電位は、リセット用 T F T 3 3 0 8 を介して、バッファ用 T F T 3 3 0 7 のゲート電極に印加される。こうして、バッファ用 T F T 3 3 0 7 のソース領域は、センサ用電源線 V B の電位（基準電位）から、バッファ用 T F T 3 3 0 7 のソース領域とゲート領域の電位差を差し引いた電位に保たれている。こうしてフォトダイオード 3 3 0 5 の電極間には、逆バイアスの電圧が印加される。

30

#### 【 0 1 0 4 】

このとき、センサ用ゲート信号線 S G 1 の信号によって、センサ用ゲート信号線 S G 1 に接続された全ての選択用 T F T 3 3 0 6 は、非導通状態にある。本明細書において、リセット用ゲート信号線が選択されている期間をリセット期間 R S と呼ぶこととする。

#### 【 0 1 0 5 】

40

次に、リセット用ゲート信号線 R G 1 の信号が変化し、リセット用ゲート信号線 R G 1 に接続された全てのリセット用 T F T 3 3 0 8 が非導通状態になる。このときリセット用ゲート信号線は、非選択であるということにする。すると、フォトダイオード 3 3 0 5 に光が照射されていると、フォトダイオード 3 3 0 5 の電極間に電流が流れ、リセット期間中に印加された電極間の逆バイアス電圧が、低くなる。この後、センサ用ゲート信号線 S G 1 に入力される信号によって、センサ用ゲート信号線 S G 1 に接続された全ての選択用 T F T 3 3 0 6 が導通状態になる。

#### 【 0 1 0 6 】

リセット用ゲート信号線が非選択の状態になり、同じラインの画素に対応する選択用 T F T が選択されるまでの期間をサンプリング期間 S T と呼ぶこととする。特に、リセット用

50

ゲート信号線 R G 1 が非選択になり、選択用ゲート信号線 S G 1 が選択されるまでの期間を第 1 のサンプリング期間 S T 1 と呼ぶことにする。

【 0 1 0 7 】

サンプリング期間 S T 1 において、時間の経過と共に、フォトダイオード 3 3 0 5 の電極間の逆バイアス電圧が小さくなる。この逆バイアス電圧の低下する度合は、フォトダイオード 3 3 0 5 の光電変換層に照射された光の強度に依存する。ここで、フォトダイオード 3 3 0 5 のバッファ用 T F T 3 3 0 7 のゲート電極と接続されていない側の電極は、一定の電位に保たれている。よって、フォトダイオード 3 3 0 5 のバッファ用 T F T 3 3 0 7 のゲート電極に接続されている側の電位が低下する。

【 0 1 0 8 】

この電位の低下は、バッファ用 T F T 3 3 0 7 のゲート電極の電位を低下させる。

10

【 0 1 0 9 】

ここで、バッファ用 T F T 3 3 0 7 のソース領域は、それぞれ、選択用 T F T 3 3 0 6 のドレイン・ソース間を介して定電流源 2 2 0 3 - 1 ~ 2 2 0 3 - x に接続されているので、バッファ用 T F T 3 3 0 7 は、ソースフォロワとして働く。そのため、バッファ用 T F T 3 3 0 7 のゲート・ソース間電圧は、常に等しく保たれる。そのため、フォトダイオード 3 3 0 5 の電極間の電位の変化によって、バッファ用 T F T 3 3 0 7 のゲート電極の電位が変化すると、同じ分の電位だけ、バッファ用 T F T 3 3 0 7 のソース領域の電位も変化する。サンプリング期間 S T 1 の後、センサ用ゲート信号線 S G 1 が選択され、このソース領域の電位の変化は、センサ用出力配線 S S 1 ~ S S x に出力される。

20

【 0 1 1 0 】

その後、センサ用ゲート信号線 S G 1 は、非選択の状態になる。

【 0 1 1 1 】

一方、リセット用ゲート信号線 R G 1 が非選択の状態になると、リセット用ゲート信号線 R G 2 が選択される。リセット用ゲート信号線 R G 2 に接続された全てのリセット用 T F T 3 3 0 8 が導通状態となり、第 2 ライン目のリセット期間 R S が始まる。この後、リセット用ゲート信号線 R G 2 が非選択の状態になり、第 2 ライン目のサンプリング期間 S T 2 が始まる。なお、第 1 のサンプリング期間 S T 1 と第 2 のサンプリング期間 S T 2 は、始まる時間は異なるが、長さは同じである。

30

【 0 1 1 2 】

第 2 のサンプリング期間 S T 2 でも同様に、各画素のセンサ部において、入力された光の強度に応じて、フォトダイオードの電極間の逆バイアス電圧が低下する。第 2 のサンプリング期間 S T 2 の後、センサ用ゲート信号線 S G 2 の信号によって、センサ用ゲート信号線 S G 2 に接続された全ての選択用 T F T 3 3 0 6 が導通状態となり、フォトダイオード 3 3 0 5 の電極間の電位の変化は、バッファ用 T F T 3 3 0 7 のゲート電極に入力され、バッファ用 T F T 3 3 0 7 のソース領域の電位の変化となって、センサ用出力配線 S S 1 ~ S S x に出力される。

【 0 1 1 3 】

その後、センサ用ゲート信号線 S G 2 が非選択の状態となる。

40

【 0 1 1 4 】

上記動作を、全てのセンサ用ゲート信号線 S G 1 ~ S G y について繰り返し、表示部兼入力部 2 2 0 1 の画素全部のセンサ部 3 3 1 2 に入力された信号の情報を読み取る。

【 0 1 1 5 】

この様に、E L 表示部は、画像の表示を行う。また同時に、センサ部において、入力ペンのペン先から発した光を検出し、入力ペンのペン先が指示した位置を特定することができる。

【 0 1 1 6 】

【 実施例 】

以下に本発明の実施例について記述する。

【 0 1 1 7 】

50

**[実施例 1]**

本実施例では、実施の形態において述べた構造の情報装置を実際に作製した場合について説明する。

**【0118】**

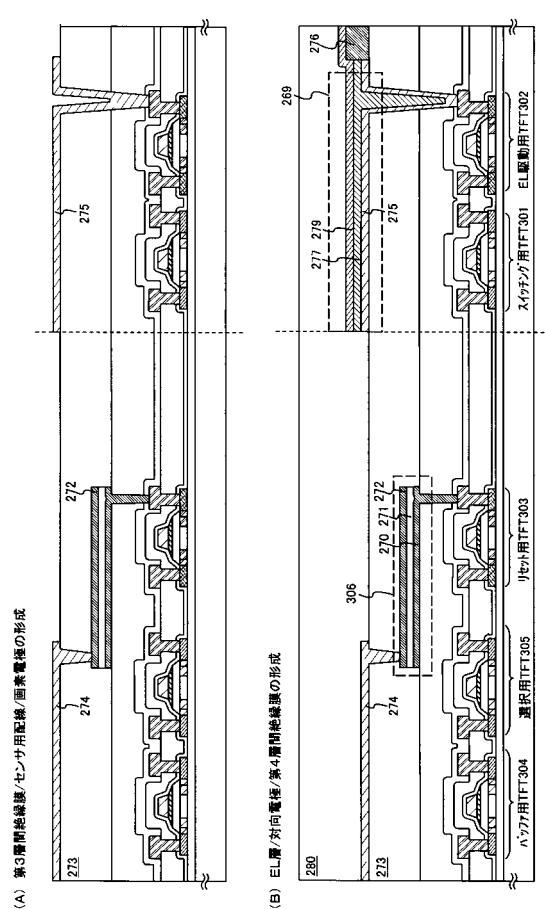

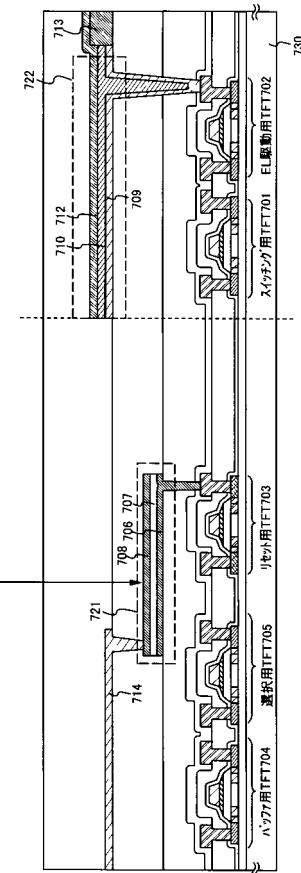

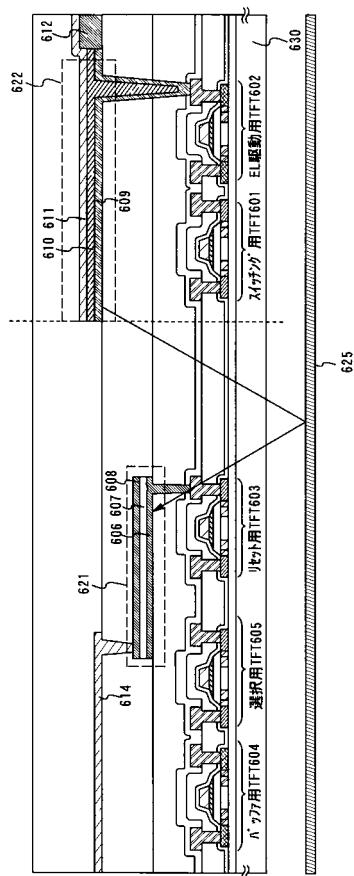

本実施例では、本発明の情報装置の断面図について、図15を用いて説明する。

**【0119】**

601はスイッチング用TFT、602はEL駆動用TFT、603はリセット用TFT、604はバッファ用TFT、605は選択用TFTである。

**【0120】**

また、606はアノード電極、607は光電変換層、608はカソード電極である。アノード電極606、光電変換層607、カソード電極608とによって、フォトダイオード621が形成される。614はセンサ用配線であり、カソード電極608と外部の電源とを電気的に接続している。また、フォトダイオード621のアノード電極606とリセット用TFT603のドレイン領域とは電気的に接続されている。10

**【0121】**

ここで、フォトダイオード621のアノード電極606は、透光性を有する材料で形成されている。

**【0122】**

また609は画素電極（陽極）、610はEL層、611は対向電極（陰極）である。画素電極（陽極）609と、EL層610と、対向電極（陰極）611とでEL素子622が形成される。なお612はバンクであり、隣り合う画素同士のEL層610を区切っている。20

**【0123】**

ここで、EL素子622の画素電極609は、透光性を有する材料で形成されている。

**【0124】**

図15に示した構成の情報装置において、EL素子622は、基板630の方向に光を放射する。

**【0125】**

624は入力ペンであり、入力ペン624のペン先発光部623から発した光は、フォトダイオード621に入射する。本実施例では、入力ペン624による入力を基板630のTFTが形成されていない側から行う。なお、このペン入力を行う側は、EL素子622の光の放射側にあたり、EL素子622によって表示される画像を視認しながら情報の入力を行う。30

**【0126】**

なお、入力ペン624のペン先発光部623から発する光は、指向性が高いものが好ましい。そのため、ペン先発光部623からレーザー光を発するような入力ペン624を用いるのが好ましい。

**【0127】**

また、入力ペン624のペン先発光部623から発する光として、波長の短い光、つまりエネルギーの高い光を用いるのが好ましい。例えば、紫外や近紫外の光を用いるのが好ましい。なお、本明細書中で、近紫外の光とは、紫色及び青色の可視光も含むものとする。よって、紫外発光ダイオードや近紫外発光ダイオード等を有し、ペン先発光部623からそれらの発光ダイオードの光が照射される構造の入力ペン624を用いるのが好ましい。40

**【0128】**

この様なエネルギーの高い光を用いることで、入力ペン624によってフォトダイオード等の光電変換素子に入力され電気信号に変換された信号を、外光等のノイズの信号と比較して大きくすることができる。そのため、より信頼性の高いペン入力操作を行うことができる。

**【0129】**

本実施例において、スイッチング用TFT601、リセット用TFT603、選択用TFT50

T 6 0 5 は全て n チャネル型 TFT である。また EL 駆動用 TFT 6 0 2 、バッファ用 TFT 6 0 4 は p チャネル型 TFT である。なお、本発明はこの構成に限定されない。よってスイッチング用 TFT 6 0 1 、EL 駆動用 TFT 6 0 2 、バッファ用 TFT 6 0 4 、選択用 TFT 6 0 5 、リセット用 TFT 6 0 3 は、n チャネル型 TFT と p チャネル型 TFT のどちらでも良い。

【 0 1 3 0 】

ただし本実施例のように、EL 駆動用 TFT 6 0 2 のソース領域またはドレイン領域が EL 素子 6 2 2 の陽極 6 0 9 と電気的に接続されている場合、EL 駆動用 TFT 6 0 2 は p チャネル型 TFT であることが望ましい。また逆に、EL 駆動用 TFT 6 0 2 のソース領域またはドレイン領域が EL 素子 6 2 2 の陰極と電気的に接続されている場合、EL 駆動用 TFT 6 0 2 は n チャネル型 TFT であることが望ましい。 10

【 0 1 3 1 】

また、本実施例のように、フォトダイオード 6 2 1 のアノード電極 6 0 6 がリセット用 TFT 6 0 3 と電気的に接続されている場合、リセット用 TFT 6 0 3 は n チャネル型 TFT 、バッファ用 TFT 6 0 4 は p チャネル型 TFT であることが望ましい。逆にフォトダイオード 6 2 1 のカソード電極がリセット用 TFT 6 0 3 と接続され、センサ用配線 6 1 6 がアノード電極と接続されている場合、リセット用 TFT 3 0 3 は p チャネル型 TFT 、バッファ用 TFT 3 0 4 は n チャネル型 TFT であることが望ましい。

【 0 1 3 2 】

【実施例 2 】 20

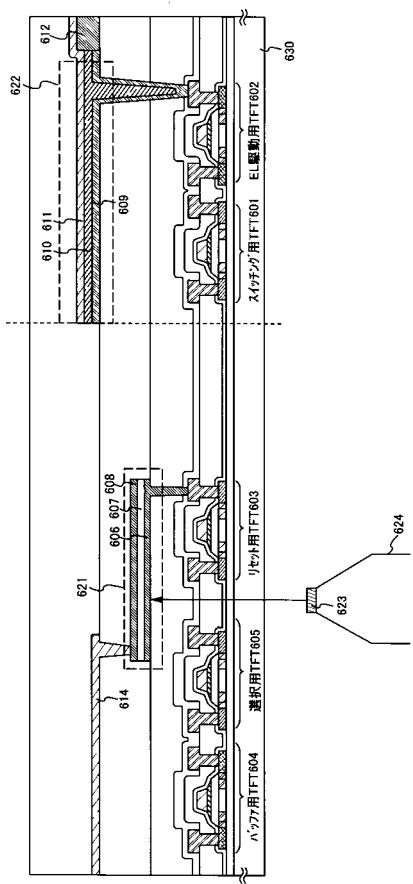

本実施例では、実施例 1 において述べた構造の情報装置において、EL 素子の発光の方向が異なる例について図 16 を用いて説明する。

【 0 1 3 3 】

図 16 に本実施例の情報装置の断面図を示す。7 0 1 はスイッチング用 TFT 、7 0 2 は EL 駆動用 TFT 、7 0 3 はリセット用 TFT 、7 0 4 はバッファ用 TFT 、7 0 5 は選択用 TFT である。

【 0 1 3 4 】

また、7 0 6 はカソード電極、7 0 7 は光電変換層、7 0 8 はアノード電極である。カソード電極 7 0 6 、光電変換層 7 0 7 、アノード電極 7 0 8 とによって、フォトダイオード 7 2 1 が形成される。7 1 4 はセンサ用配線であり電気的に、アノード電極 7 0 8 と外部の電源とを接続している。また、フォトダイオード 7 2 1 のカソード電極 7 0 6 とリセット用 TFT 7 0 3 のドレイン領域とは電気的に接続されている。 30

【 0 1 3 5 】

ここで、フォトダイオード 7 2 1 のアノード電極 7 0 8 は、透光性を有する材料で形成されている。

【 0 1 3 6 】

また 7 0 9 は画素電極（陰極）、7 1 0 は EL 層、7 1 2 は対向電極（陽極）である。画素電極（陰極）7 0 9 と、EL 層 7 1 0 と、対向電極（陽極）7 1 2 とで EL 素子 7 2 2 が形成される。なお 7 1 3 はバンクであり、隣り合う画素同士の EL 層 7 1 0 を区切っている。 40

【 0 1 3 7 】

ここで、EL 素子 7 2 2 の対向電極 7 1 2 は、透光性を有する材料で形成されている。

【 0 1 3 8 】

図 16 に示した構成の情報装置において、EL 素子 7 2 2 は、基板 7 3 0 とは逆の方向に光を放射する。

【 0 1 3 9 】

7 2 4 は入力ペンであり、入力ペン 7 2 4 のペン先発光部 7 2 3 から発した光は、フォトダイオード 7 2 1 に入射する。本実施例では、入力ペン 7 2 4 による情報の入力を、基板 7 3 0 の TFT が形成されている側から行う。なお、このペン入力を行う側は、EL 素子 7 2 2 の光の放射側にあたり、EL 素子 7 2 2 によって表示される画像を視認しながら情 50

報の入力を行う。

【0140】

なお、入力ペン724のペン先発光部723から発する光は、指向性が高いものが好ましい。そのため、ペン先発光部723からレーザー光を発するような入力ペン724を用いるのが好ましい。

【0141】

また、入力ペン624のペン先発光部623から発する光として、波長の短い光、つまりエネルギーの高い光を用いるのが好ましい。例えば、紫外や近紫外の光を用いるのが好ましい。なお、本明細書中で、近紫外の光とは、紫色及び青色の可視光も含むものとする。よって、紫外発光ダイオードや近紫外発光ダイオード等を有し、ペン先発光部623からそれらの発光ダイオードの光が照射される構造の入力ペン624を用いるのが好ましい。

10

【0142】

この様なエネルギーの高い光を用いることで、入力ペン624によってフォトダイオード等の光電変換素子に入力され電気信号に変換された信号を、外光等のノイズの信号と比較して大きくすることができる。そのため、より信頼性の高いペン入力操作を行うことができる。

【0143】

本実施例において、スイッチング用TFT701、EL駆動用TFT702、バッファ用TFT704、選択用TFT705は全てnチャネル型TFTである。またリセット用TFT703はpチャネル型TFTである。なお本発明はこの構成に限定されない。よってスイッチング用TFT701、EL駆動用TFT702、バッファ用TFT704、選択用TFT705、リセット用TFT703は、nチャネル型TFTとpチャネル型TFTのどちらでも良い。

20

【0144】

ただし本実施例のように、EL駆動用TFT702のソース領域またはドレイン領域がEL素子722の陰極709と電気的に接続されている場合、EL駆動用TFT702はnチャネル型TFTであることが望ましい。また逆に、EL駆動用TFT702のソース領域またはドレイン領域がEL素子722の陽極712と電気的に接続されている場合、EL駆動用TFT702はpチャネル型TFTであることが望ましい。

【0145】

30

また、本実施例のように、フォトダイオード721のカソード電極706がリセット用TFT703と電気的に接続されている場合、リセット用TFT703はpチャネル型TFT、バッファ用TFT704はnチャネル型TFTであることが望ましい。逆にフォトダイオード721のアノード電極がリセット用TFT703と接続され、センサ用配線714がカソード電極と接続されている場合、リセット用TFT703はnチャネル型TFT、バッファ用TFT704はpチャネル型TFTであることが望ましい。

【0146】

[実施例3]

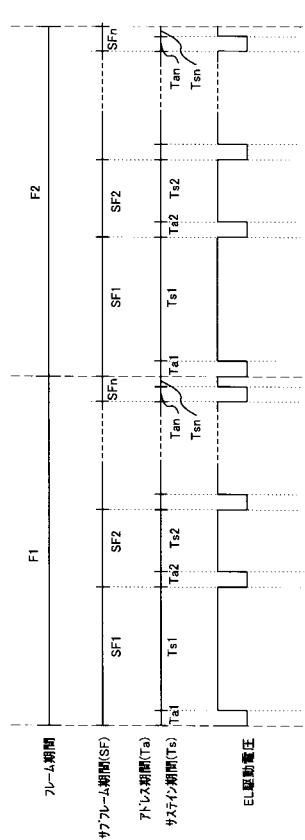

本実施例では、実施の形態で示したのとは異なる、表示部兼入力部の動作方法について説明する。なお、画素部兼入力部の構成は、実施の形態で示したものと同じであり図2及び図3を参照し説明は省略する。また、本実施例のセンサ部の動作方法も実施の形態で示したものと同じであり、図18を参照する。本実施例のEL表示部の動作方法を示すタイミングチャートを図5に示す。

40

【0147】

まず、1フレーム期間(F)をN個のサブフレーム期間(SF1～SFN)に分割する。階調数が多くなるにつれて1フレーム期間におけるサブフレーム期間の数も増える。なおエリアセンサのセンサ部が画像を表示する場合、1フレーム期間(F)とは、表示部兼入力部の全ての画素のEL表示部が1つの画像を表示する期間を指す。

【0148】

本実施例の場合、フレーム期間は1秒間に60以上設けることが好ましい。1秒間に表示

50

される画像の数を 60 以上にすることで、視覚的にフリック等の画像のちらつきを抑えることが可能になる。

【 0149 】

サブフレーム期間はアドレス期間 (T<sub>a</sub>) とサステイン期間 (T<sub>s</sub>) とに分けられる。アドレス期間とは、1 サブフレーム期間中、全ての画素にデジタルビデオ信号を入力する期間である。なおデジタルビデオ信号とは、画像情報を有するデジタルの信号である。サステイン期間（点灯期間とも呼ぶ）とは、アドレス期間において画素に入力されたデジタルビデオ信号によって、EL 素子を発光又は非発光の状態にし、表示を行う期間を示している。なおデジタルビデオ信号とは、画像情報を有するデジタルの信号を意味する。

【 0150 】

S<sub>F</sub>1 ~ S<sub>F</sub>N が有するアドレス期間 (T<sub>a</sub>) をそれぞれ T<sub>a</sub>1 ~ T<sub>a</sub>N とする。S<sub>F</sub>1 ~ S<sub>F</sub>N が有するサステイン期間 (T<sub>s</sub>) をそれぞれ T<sub>s</sub>1 ~ T<sub>s</sub>N とする。

【 0151 】

電源供給線 (V<sub>1</sub> ~ V<sub>x</sub>) の電位は所定の電位（電源電位）に保たれている。

【 0152 】

まずアドレス期間 T<sub>a</sub>において、EL 素子 3301 対向電極の電位は、電源電位と同じ高さに保たれている。

【 0153 】

次に EL 表示用ゲート信号線 G<sub>1</sub> に入力される信号によって、EL 表示用ゲート信号線 G<sub>1</sub> に接続されている全てのスイッチング用 T<sub>FT</sub>3302 が導通状態になる。次に、EL 表示用ソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) にデジタルビデオ信号が入力される。デジタルビデオ信号は「0」または「1」の情報を有しており、「0」と「1」のデジタルビデオ信号は、一方が H<sub>i</sub>、一方が L<sub>o</sub> の電圧を有する信号である。

【 0154 】

そして EL 表示用ソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) に入力されたデジタルビデオ信号は、導通状態のスイッチング用 T<sub>FT</sub>3302 を介して、EL 駆動用 T<sub>FT</sub>3303 のゲート電極に入力される。

【 0155 】

次に EL 表示用ゲート信号線 G<sub>1</sub> に接続されている全てのスイッチング用 T<sub>FT</sub>3302 が非導通状態になり、EL 表示用ゲート信号線 G<sub>2</sub> に入力されるゲート信号によって、EL 表示用ゲート信号線 G<sub>2</sub> に接続されている全てのスイッチング用 T<sub>FT</sub>3302 が導通状態になる。次に、EL 表示用ソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) にデジタルビデオ信号が入力される。EL 表示用ソース信号線 (S<sub>1</sub> ~ S<sub>x</sub>) に入力されたデジタルビデオ信号は、導通状態のスイッチング用 T<sub>FT</sub>3302 を介して、EL 駆動用 T<sub>FT</sub>3303 のゲート電極に入力される。

【 0156 】

上述した動作を EL 表示用ゲート信号線 G<sub>y</sub> まで繰り返し、全ての画素の EL 駆動用 T<sub>FT</sub>3303 のゲート電極にデジタルビデオ信号が入力され、アドレス期間が終了する。

【 0157 】

アドレス期間 T<sub>a</sub> が終了すると同時にサステイン期間 T<sub>s</sub> となる。サステイン期間において、全てのスイッチング用 T<sub>FT</sub>3302 はオフの状態になる。サステイン期間において、全ての EL 素子 3301 の対向電極の電位は、電源電位が画素電極に与えられたときに EL 素子 3301 が発光する程度に、電源電位との間に電位差を有する高さになる。

【 0158 】

本実施例では、デジタルビデオ信号が「0」の情報を有していた場合、EL 駆動用 T<sub>FT</sub>3303 は非導通状態になる。よって EL 素子 3301 の画素電極は対向電極の電位に保たれたままである。その結果、「0」の情報を有するデジタルビデオ信号が入力された画素において、EL 素子 3301 は発光しない。

【 0159 】

逆にデジタルビデオ信号が「1」の情報を有していた場合、EL 駆動用 T<sub>FT</sub>3303 は

10

20

30

40

50

導通状態になる。よって電源電位がEL素子3301の画素電極に与えられる。その結果、「1」の情報を有するデジタルビデオ信号が入力された画素が有するEL素子3301は発光する。

【0160】

このように、画素に入力されるデジタルビデオ信号の有する情報によって、EL素子が発光または非発光の状態になり、画素は表示を行う。

【0161】

サステイン期間が終了すると同時に、1つのサブフレーム期間が終了する。そして次のサブフレーム期間が出現し、再びアドレス期間に入り、全画素にデジタルビデオ信号を入力したら、再びサステイン期間に入る。なお、サブフレーム期間S F 1 ~ S F Nの出現する順序は任意である。 10

【0162】

以下、残りのサブフレーム期間においても同様の動作を繰り返し、表示を行う。N個のサブフレーム期間が全て終了したら、1つの画像が表示され、1フレーム期間が終了する。1フレーム期間が終了すると次のフレーム期間のサブフレーム期間が出現し、上述した動作を繰り返す。

【0163】

本発明において、N個のサブフレーム期間がそれぞれ有するアドレス期間(T a 1 ~ T a N)の長さは全て同じである。またN個のサステイン期間T s 1、...、T s Nの長さの比は、 $T s 1 : T s 2 : T s 3 : \dots : T s (N - 1) : T s N = 2^0 : 2^{-1} : 2^{-2} : \dots : 2^{-(N-2)} : 2^{-(N-1)}$ で表される。 20

【0164】

各画素の階調は、1フレーム期間においてどのサブフレーム期間を発光させるかによって決まる。例えば、N=8のとき、全部のサステイン期間で発光した場合の画素の輝度を100%とすると、T s 1とT s 2において画素が発光した場合には75%の輝度が表現でき、T s 3とT s 5とT s 8を選択した場合には16%の輝度が表現できる。

【0165】

上記のように画素のEL素子を発光させて、画像表示を行う手法をデジタル方式とよぶことにする。

【0166】

次に、センサ部の動作方法について、図2及び図3、図18を用いて説明する。 30

【0167】

ここで、リセット用T F T 3308はnチャネル型T F Tとし、バッファ用T F T 3307はpチャネル型T F Tとし、選択用T F T 3306はnチャネル型T F Tとしたが、リセット用T F T 3308、バッファ用T F T 3307及び選択用T F T 3306はそれぞれ、nチャネル型T F Tでもpチャネル型T F Tでもどちらでも良い。なお、リセット用T F T 3308とバッファ用T F T 3307の極性は逆の方が望ましい。

【0168】

始め、リセット用ゲート信号線R G 1の信号により、リセット用ゲート信号線R G 1に接続された全てのリセット用T F T 3308は、導通状態にある。このとき、リセット用ゲート信号線は、選択されているということにする。なお、他のリセット用ゲート信号線R G 2 ~ R G yに接続されたすべてのリセット用T F T 3308は、すべて非導通状態にある。このとき、センサ用電源線V Bの電位は、リセット用T F T 3308を介して、バッファ用T F T 3307のゲート電極に印加される。こうして、バッファ用T F T 3307のソース領域は、センサ用電源線V Bの電位(基準電位)から、バッファ用T F T 3307のソース領域とゲート領域の電位差を差し引いた電位に保たれている。こうしてフォトダイオード3305の電極間には、逆バイアスの電圧が印加される。 40

【0169】

このとき、センサ用ゲート信号線S G 1の信号によって、センサ用ゲート信号線S G 1に接続された全ての選択用T F T 3306は、非導通状態にある。本明細書において、リセ 50

ット用ゲート信号線が選択されている期間をリセット期間 R S と呼ぶことにする。

【 0 1 7 0 】

次に、リセット用ゲート信号線 R G 1 の信号が変化し、リセット用ゲート信号線 R G 1 に接続された全てのリセット用 T F T 3 3 0 8 が非導通状態になる。このときリセット用ゲート信号線は、非選択であるということにする。すると、フォトダイオード 3 3 0 5 に光が照射されていると、フォトダイオード 3 3 0 5 の電極間に電流が流れ、リセット期間中に印加された電極間の逆バイアス電圧が、低くなる。この後、センサ用ゲート信号線 S G 1 に入力される信号によって、センサ用ゲート信号線 S G 1 に接続された全ての選択用 T F T 3 3 0 6 が導通状態になる。

【 0 1 7 1 】

リセット用ゲート信号線が非選択の状態になり、同じラインの画素に対応する選択用 T F T が選択されるまでの期間をサンプリング期間 S T と呼ぶことにする。特に、リセット用ゲート信号線 R G 1 が非選択になり、選択用ゲート信号線 S G 1 が選択されるまでの期間を第 1 のサンプリング期間 S T 1 と呼ぶことにする。

【 0 1 7 2 】

サンプリング期間 S T 1 において、時間の経過と共に、フォトダイオード 3 3 0 5 の電極間の逆バイアス電圧が小さくなる。この逆バイアス電圧の低下する度合は、フォトダイオード 3 3 0 5 の光電変換層に照射された光の強度に依存する。ここで、フォトダイオード 3 3 0 5 のバッファ用 T F T 3 3 0 7 のゲート電極と接続されていない側の電極は、一定の電位に保たれている。よって、フォトダイオード 3 3 0 5 のバッファ用 T F T 3 3 0 7 のゲート電極に接続されている側の電位が低下する。

【 0 1 7 3 】

この電位の低下は、バッファ用 T F T 3 3 0 7 のゲート電極の電位を低下させる。

【 0 1 7 4 】

ここで、バッファ用 T F T 3 3 0 7 のソース領域は、それぞれ、選択用 T F T 3 3 0 6 のドレイン・ソース間を介して定電流源 2 2 0 3 - 1 ~ 2 2 0 3 - x に接続されているので、バッファ用 T F T 3 3 0 7 は、ソースフォロワとして働く。そのため、バッファ用 T F T 3 3 0 7 のゲート・ソース間電圧は、常に等しく保たれる。そのため、フォトダイオード 3 3 0 5 の電極間の電位の変化によって、バッファ用 T F T 3 3 0 7 のゲート電極の電位が変化すると、同じ分の電位だけ、バッファ用 T F T 3 3 0 7 のソース領域の電位も変化する。サンプリング期間 S T 1 の後、センサ用ゲート信号線 S G 1 が選択され、このソース領域の電位の変化は、センサ用出力配線 S S 1 ~ S S x に出力される。

【 0 1 7 5 】

その後、センサ用ゲート信号線 S G 1 は、非選択の状態になる。

【 0 1 7 6 】

一方、リセット用ゲート信号線 R G 1 が非選択の状態になると、リセット用ゲート信号線 R G 2 が選択される。リセット用ゲート信号線 R G 2 に接続された全てのリセット用 T F T 3 3 0 8 が導通状態となり、第 2 ライン目のリセット期間 R S が始まる。この後、リセット用ゲート信号線 R G 2 が非選択の状態になり、第 2 ライン目のサンプリング期間 S T 2 が始まる。なお、第 1 のサンプリング期間 S T 1 と第 2 のサンプリング期間 S T 2 は、始まる時間は異なるが、長さは同じである。

【 0 1 7 7 】

第 2 のサンプリング期間 S T 2 でも同様に、各画素のセンサ部において、入力された光の強度に応じて、フォトダイオードの電極間の逆バイアス電圧が低下する。第 2 のサンプリング期間 S T 2 の後、センサ用ゲート信号線 S G 2 の信号によって、センサ用ゲート信号線 S G 2 に接続された全ての選択用 T F T 3 3 0 6 が導通状態となり、フォトダイオード 3 3 0 5 の電極間の電位の変化は、バッファ用 T F T 3 3 0 7 のゲート電極に入力され、バッファ用 T F T 3 3 0 7 のソース領域の電位の変化となって、センサ用出力配線 S S 1 ~ S S x に出力される。

【 0 1 7 8 】

10

20

30

40

50

その後、センサ用ゲート信号線 SG2 が非選択の状態となる。

【0179】

上記動作を、全てのセンサ用ゲート信号線 SG1 ~ SGy について繰り返し、表示部兼入力部 2201 の画素全部のセンサ部 3312 に入力された信号の情報を読み取る。

【0180】

こうして、入力ペンのペン先の位置を特定することができる。

【0181】

なお本実施例は、実施例 1 ~ 実施例 2 と自由に組み合わせることが可能である。

【0182】

[実施例 4]

10

本発明の情報装置において、入力ペンによって情報の入力を行うだけではなく、イメージセンサとしても用いることができる。

【0183】

図 20 は、本発明の情報装置をイメージセンサとして用いた場合の模式図である。

【0184】

情報装置の表示部兼入力部の回路構成は、実施の形態と同様であるので、説明はここでは省略する。また、図 20 の模式図において、図 15 と同様の部分は、同じ符号を用いて示し説明は省略する。

【0185】

また、表示部兼入力部を駆動する方法は、実施の形態や、実施例 3 で示した手法と同様の手法を用いることができるので、説明は、ここでは省略する。

20

【0186】

本発明の情報装置の表示部兼入力部の、ペン入力を行う側に、読みとりたい物体（読みとり対象物体：625）を近づける。ここで、実施の形態や、実施例 3 等で示したのと同様の手法で、各画素の EL 素子 622 を発光させる。この EL 素子 622 の発光を用いて、読みとり対象物体 625 に光を照射する。つまり、各画素の EL 素子 622 は、読みとり対象物体 625 の情報を読みとるための照明装置として用いられる。

【0187】

そのため、本発明の情報装置をイメージセンサとして用いる際は、各画素の EL 素子の発光輝度は、全て同じにするのが望ましい。

30

【0188】

つまり、実施の形態において示したような、アナログ方式によって各画素の EL 素子を駆動する場合は、全ての画素に、EL 用ソース信号線より入力されるアナログの信号を、等しくする。

【0189】

一方、実施例 3 に示したような、デジタル方式によって、各画素の EL 素子を駆動させる場合は、全ての画素が、1 フレーム期間内に同じ長さの時間だけ発光するようとする。なお、できる限り連続的に光を照射するために、全ての画素の EL 素子が、1 フレーム期間内の全てのサスティン期間において発光するように設定するのが望ましい。

【0190】

40

こうして、読みとり対象物体 625 に照射された光は、読みとり対象物体 625 表面で反射され、各画素のセンサ部のフォトダイオード 621 に入力される。この入力された光が電気信号に変換され、センサ用駆動回路（センサ用ソース信号線駆動回路、センサ用ゲート信号線駆動回路）によって読み出され、読みとり対象物体 625 の表面の情報が、画像として得られる。

【0191】

ここで、本実施例では、実施例 1 に示した構成の情報装置を用いて説明を行ったが、実施例 2 において図 16 で示した構成の情報装置を用い、表示部兼画素部の形成された基板の、TFT が形成された側から、読み取り対象物体を近づけて、読み取り対象物体表面の情報を読み取ることもできる。

50

## 【0192】

なお、本実施例は、実施例1～実施例3と自由に組み合わせて実施することが可能である。

## 【0193】

## [実施例5]

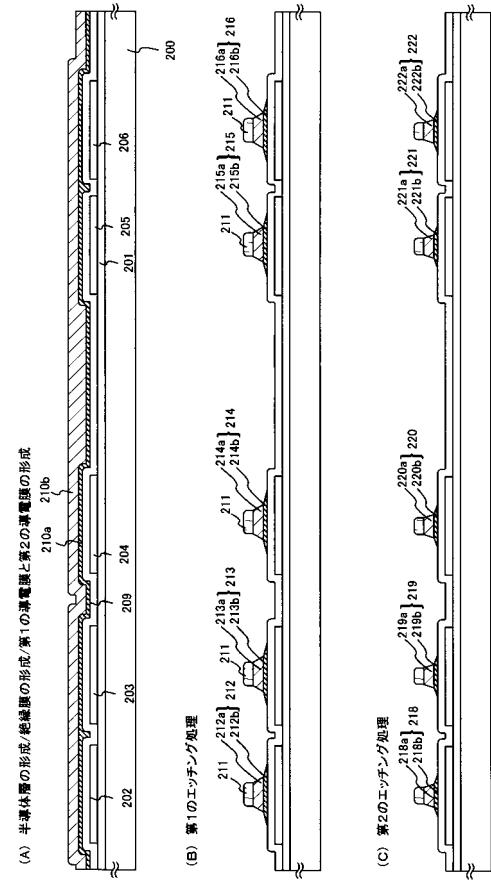

本発明の情報装置の表示部兼入力部の作製方法について、図10～図14を用いて説明する。

## 【0194】

まず、図10(A)において、本実施例ではコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミニノホウケイ酸ガラスなどのガラスからなる基板200を用いる。なお、基板200としては、透光性を有する基板であれば限定されず、石英基板を用いてもよく、また、ガラス基板、セラミック基板等を用いてもよい。また、本実施例の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

10

## 【0195】

また基板200としては、ステンレス基板を用いてもよい。しかし、ステンレス基板は、透明ではないため、EL素子が発する光が基板200とは反対側に放射される場合のみ有効である。

## 【0196】

次に基板200を覆うように、基板200上に酸化珪素からなる絶縁膜を形成する。絶縁膜は、酸化珪素膜、窒化珪素膜または酸化窒化珪素膜を用いることができる。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化珪素膜を250～800nm(好ましくは300～500nm)、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化珪素膜を250～800nm(好ましくは300～500nm)の厚さに積層して形成しても良い。ここでは酸化珪素からなる絶縁膜を単層構造とし、0.5～1.5μmの厚さに形成した。なお絶縁膜の材料は酸化珪素に限定されない。

20

## 【0197】

次にCMP法で該絶縁膜を研磨することで平坦化絶縁膜201が形成される。CMP法は公知の方法で行うことが可能である。酸化膜の研磨では、一般的に100～1000nmの研磨剤を、PH調整剤等の試薬を含む水溶液に分散させた固液分散系のスラリーが用いられる。本実施例では、水酸化カリウムが添加された水溶液に、塩化珪素ガスを熱分解して得られるフュームドシリカ粒子を20wt%分散したシリカスラリー(PH=10～11)を用いる。

30

## 【0198】

平坦化絶縁膜201形成後、平坦化絶縁膜201上に半導体層202～206を形成する。半導体層202～206は、非晶質構造を有する半導体膜を公知の手段(スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜した後、公知の結晶化処理(レーザー結晶化法、熱結晶化法、またはニッケルなどの触媒を用いた熱結晶化法等)を行って得られた結晶質半導体膜を所望の形状にパターニングして形成する。この半導体層202～206の厚さは25～80nm(好ましくは30～60nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくは珪素またはシリコンゲルマニウム(Si<sub>x</sub>Ge<sub>1-x</sub>(X=0.0001～0.02))合金などで形成すると良い。本実施例では、プラズマCVD法を用い、55nmの非晶質珪素膜を成膜した後、ニッケルを含む溶液を非晶質珪素膜上に保持させた。この非晶質珪素膜に脱水素化(500、1時間)を行った後、熱結晶化(550、4時間)を行い、さらに結晶化を改善するためのレーザーアーチル処理を行って結晶質珪素膜を形成した。そして、この結晶質珪素膜をフォトリソグラフィ法を用いたパターニング処理によって、半導体層202～206を形成した。

40

## 【0199】

また、半導体層202～206を形成した後、TFTのしきい値を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。

50

## 【0200】

また、レーザー結晶化法で結晶質半導体膜を作製する場合には、パルス発振型または連続発光型のエキシマレーザーやYAGレーザー、YVO<sub>4</sub>レーザーを用いることができる。これらのレーザーを用いる場合には、レーザー発振器から放射されたレーザー光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宜選択するものであるが、エキシマレーザーを用いる場合はパルス発振周波数300Hzとし、レーザーエネルギー密度を100～400mJ/cm<sup>2</sup>(代表的には200～300mJ/cm<sup>2</sup>)とする。また、YAGレーザーを用いる場合にはその第2高調波を用いパルス発振周波数30～300kHzとし、レーザーエネルギー密度を300～600mJ/cm<sup>2</sup>(代表的には350～500mJ/cm<sup>2</sup>)とすると良い。そして幅100～1000μm、例えば400μmで線状に集光したレーザー光を基板全面に渡って照射し、この時の線状レーザー光の重ね合わせ率(オーバーラップ率)を50～98%として行えばよい。

## 【0201】

次いで、半導体層202～206を覆うゲート絶縁膜209を形成する。ゲート絶縁膜209はプラズマCVD法またはスパッタ法を用い、厚さを40～150nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により110nmの厚さで酸化窒化珪素膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成した。勿論、ゲート絶縁膜は酸化窒化珪素膜に限定されるものでなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。

## 【0202】

また、酸化珪素膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO<sub>2</sub>とを混合し、反応圧力40Pa、基板温度300～400とし、高周波(13.56MHz)電力密度0.5～0.8W/cm<sup>2</sup>で放電させて形成することができる。このようにして作製される酸化珪素膜は、その後400～500の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

## 【0203】

次いで、図10(A)に示すように、ゲート絶縁膜209上に膜厚20～100nmの第1の導電膜210aと、膜厚100～400nmの第2の導電膜210bとを積層形成する。本実施例では、膜厚30nmのTaN膜からなる第1の導電膜210aと、膜厚370nmのW膜からなる第2の導電膜210bを積層形成した。TaN膜はスパッタ法で形成し、Taのターゲットを用い、窒素を含む雰囲気内でスパッタした。また、W膜は、Wのターゲットを用いたスパッタ法で形成した。その他に6フッ化タンゲステン(WF<sub>6</sub>)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W膜中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。従って、本実施例では、高純度のW(純度99.9999%)のターゲットを用いたスパッタ法で、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9～20μcmを実現することができた。

## 【0204】

なお、本実施例では、第1の導電膜210aをTaN、第2の導電膜210bをWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、リン等の不純物元素をドーピングした多結晶珪素膜に代表される半導体膜を用いてもよい。また、AgPdCu合金を用いてもよい。また、第1の導電膜をタンタル(Ta)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化チタン(TiN)膜で形成し、第2の導電膜をW膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をAl膜とする組み合わせ、第1の導電膜を窒化タンタル(TaN)膜で形成し、第2の導電膜をCu膜とする組み合わせとしてもよい。

## 【0205】

10

20

30

40

50

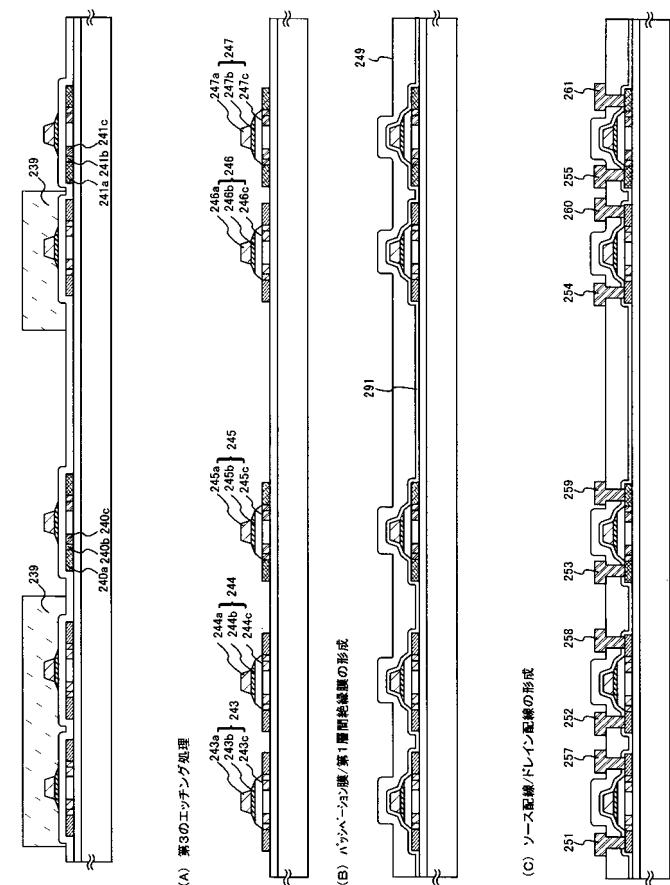

次に、フォトリソグラフィ法を用いてレジストからなるマスク 211を形成し、電極及び配線を形成するための第1のエッティング処理を行う(図10(B))。第1のエッティング処理では第1及び第2のエッティング条件で行う。本実施例では第1のエッティング条件として、ICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッティング法を用い、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25/25/10(ccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを行った。ここでは、松下電器産業(株)製のICPを用いたドライエッティング装置(Model E645-ICP)を用いた。基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッティング条件によりW膜をエッティングして第1の導電層の端部をテーパー形状とする。第1のエッティング条件でのWに対するエッティング速度は200.39nm/min、TaNに対するエッティング速度は80.32nm/minであり、TaNに対するWの選択比は約2.5である。また、この第1のエッティング条件によって、Wのテーパー角は、約26°となる。

#### 【0206】

上記第1のエッティング処理では、レジストからなるマスク 211の形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15~45°とすればよい。こうして、第1のエッティング処理により第1の導電層と第2の導電層から成る第1の形状の導電層212~216(第1の導電層212a~216aと第2の導電層212b~216b)を形成する。217はゲート絶縁膜であり、第1の形状の導電層212~216で覆われない領域は20~50nm程度エッティングされ薄くなった領域が形成される。

#### 【0207】

次いで、レジストからなるマスクを除去せずに第2のエッティング処理を行う(図10(C))。ここでは、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25/25/10(ccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッティング処理でのWに対するエッティング速度は124.62nm/min、TaNに対するエッティング速度は20.67nm/minであり、TaNに対するWの選択比は6.05である。従って、W膜が選択的にエッティングされる。この第2のエッティングによりWのテーパー角は70°となった。この第2のエッティング処理により第2の導電層218b~222bを形成する。一方、第1の導電層218a~222aは、ほとんどエッティングされず、第1の導電層218a~222aが形成される。223はゲート絶縁膜であり、第2の形状の導電層218~222で覆われない領域は20~50nm程度エッティングされ薄くなった領域が形成される。

#### 【0208】

第1の導電層218aと第2の導電層218bとで形成された電極は、後の工程で形成されるnチャネル型のバッファ用TFTとなり、第1の導電層219aと第2の導電層219bとで形成された電極は、後の工程で形成されるnチャネル型の選択用TFTとなる。同様に、第1の導電層220aと第2の導電層220bとで形成された電極は、後の工程で形成されるpチャネル型のリセット用TFTとなり、第1の導電層221aと第2の導電層221bとで形成された電極は、後の工程で形成されるnチャネル型のスイッチング用TFTとなり、第1の導電層222aと第2の導電層222bとで形成された電極は、後の工程で形成されるpチャネル型のEL駆動用TFTとなる。

#### 【0209】

次いで、第1のドーピング処理を行って図11(A)の状態を得る。ドーピングは第2の導電層218b~222bを不純物元素に対するマスクとして用い、第1の導電層218a~222aのテーパー部下方の半導体層に不純物元素が添加されるようにドーピングする。本実施例では、不純物元素としてP(リン)を用い、ドーズ量3.5×10<sup>12</sup>atoms/

10

20

30

40

50

cm<sup>3</sup>、加速電圧 90 k e V にてプラズマドーピングを行った。こうして第 1 の導電層と重ならない低濃度不純物領域 224a ~ 228a と、第 1 の導電層と重なる低濃度不純物領域 224b ~ 228b を自己整合的に形成する。低濃度不純物領域 224b ~ 228b へ添加されたリン (P) の濃度は、 $1 \times 10^{17} \sim 1 \times 10^{18}$  atoms/cm<sup>3</sup> であり、且つ、第 1 の導電層 218a ~ 222a のテーパー部の膜厚に従って緩やかな濃度勾配を有している。なお、第 1 の導電層 218a ~ 222a のテーパー部と重なる半導体層において、第 1 の導電層 218a ~ 222a のテーパー部の端部から内側に向かって、若干不純物濃度が低くなっているものの、ほぼ同程度の濃度である。

#### 【0210】

そして、レジストからなるマスク 231 を形成し、第 2 のドーピング処理を行い、半導体層に n 型を付与する不純物元素を添加する (図 11 (B))。ドーピング処理はイオンドープ法、若しくはイオン注入法で行えれば良い。イオンドープ法の条件はドーズ量を  $1 \times 10^{13} \sim 5 \times 10^{15}$  atoms/cm<sup>3</sup> とし、加速電圧を 60 ~ 100 k e V として行う。本実施例ではドーズ量を  $1.5 \times 10^{15}$  atoms/cm<sup>3</sup> とし、加速電圧を 80 k e V として行った。n 型を付与する不純物元素として 15 族に属する元素、典型的にはリン (P) または砒素 (As) を用いるが、ここではリン (P) を用いた。この場合、導電層 218 ~ 222 が n 型を付与する不純物元素に対するマスクとなり、自己整合的に高濃度不純物領域 232a ~ 236a、第 1 の導電層と重ならない低濃度不純物領域 232b ~ 236b、第 1 の導電層と重なる低濃度不純物領域 232c ~ 236c が形成される。高濃度不純物領域 232a ~ 236a には  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup> の濃度範囲で n 型を付与する不純物元素を添加する。

#### 【0211】

なお p チャネル型の半導体膜が形成される半導体膜には、図 11 (B) に示した第 2 のドーピング処理により n 型の不純物をドーピングする必要はないため、マスク 231 を半導体層 204、206 上に完全に覆うように形成し、n 型の不純物がドーピングされないようにしても良い。逆にマスク 231 を半導体層 204、206 上に設けず、第 3 のドーピング処理において半導体層の極性を p 型に反転させても良い。

#### 【0212】

次いで、レジストからなるマスク 231 を除去した後、新たにレジストからなるマスク 239 を形成して第 3 のドーピング処理を行う。この第 3 のドーピング処理により、p チャネル型 TFT の活性層となる半導体層に前記一導電型 (n 型) とは逆の導電型 (p 型) を付与する不純物元素が添加された不純物領域 240a ~ 240c、241a ~ 241c を形成する (図 11 (C))。第 1 の導電層 220b、222b を不純物元素に対するマスクとして用い、p 型を付与する不純物元素を添加して自己整合的に不純物領域を形成する。本実施例では、不純物領域 240a ~ 240c、241a ~ 241c はジボラン (B<sub>2</sub>H<sub>6</sub>) を用いたイオンドープ法で形成する。なお、この第 3 のドーピング処理の際には、n チャネル型 TFT を形成する半導体層はレジストからなるマスク 239 で覆われている。第 1 のドーピング処理及び第 2 のドーピング処理によって、不純物領域 240a、240b、240c にはそれぞれ異なる濃度でリンが添加されているが、そのいずれの領域においても p 型を付与する不純物元素の濃度が  $2 \times 10^{20} \sim 2 \times 10^{21}$  atoms/cm<sup>3</sup> となるようにドーピング処理することにより、p チャネル型 TFT のソース領域およびドレイン領域として機能するために何ら問題は生じない。

#### 【0213】

次いで、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ファーネスアニール炉を用いる熱アニール炉で行う。熱アニール法としては、酸素濃度が 1 P P m 以下、好ましくは 0.1 P P m 以下の窒素雰囲気中で 400 ~ 700、代表的には 500 ~ 550 で行えればよく、本実施例では 550、4 時間の熱処理で活性化処理を行った。なお、熱アニール法の他に、レーザーアニール法、またはラピッドサーマルアニール法 (R T A 法) などを適用することができる。

#### 【0214】

10

20

30

40

50

50

また、第1の層間絶縁膜を形成した後に活性化処理を行ってもよい。ただし、配線に用いた配線材料が熱に弱い場合には、本実施例のように配線等を保護するため層間絶縁膜（シリコンを主成分とする絶縁膜、例えば窒化珪素膜）を形成した後で活性化処理を行うことが好ましい。

【0215】

さらに、3～100%の水素を含む雰囲気中で、300～550で1～12時間の熱処理を行い、半導体層を水素化する工程を行う。本実施例では、水素を約3%含む窒素雰囲気中で410、1時間の熱処理を行った。この工程は熱的に励起された水素により半導体膜の不対結合手を水素終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる。）を用いることもできる。

10

【0216】

また、パッシベーション膜を形成した後に水素化する工程を行ってもよい。

【0217】

以上までの工程でそれぞれの半導体層に不純物領域が形成される。

【0218】

次いで、レジストからなるマスク239を除去し、第3のエッティング処理を行う。本実施例では導電層218～222をマスクとして用いて、ゲート絶縁膜をエッティング処理する。

【0219】

第3のエッティング処理により、ゲート絶縁膜243c～247cが、第2の導電層243b～247bの下方に形成される（図12（A））。

20

【0220】

次いで、基板200を覆うように、パッシベーション膜291を形成する（図12（B））。パッシベーション膜291は、酸化珪素膜、窒化珪素膜または酸化窒化珪素膜を用いることができる。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化珪素膜を250～800nm（好ましくは300～500nm）、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化珪素膜を250～800nm（好ましくは300～500nm）の厚さに積層して形成してもよい。本実施例では酸化窒素からなるパッシベーション膜291を、単層構造とし、0.5～1.5μmの厚さで形成した。

【0221】

30

次いで、第1層間絶縁膜249を形成する。プラズマCVD法またはスパッタ法を用い、厚さを100～200nmとして珪素を含む絶縁膜で形成する。本実施例では、プラズマCVD法により膜厚150nmの酸化窒化珪素膜を形成した。勿論、第1層間絶縁膜249は酸化窒化珪素膜に限定されるものなく、他の珪素を含む絶縁膜を単層または積層構造として用いても良い。次いで、各不純物領域232a、233a、235a、238、240a、241a、242に達するコンタクトホールを形成するためのパターニングを行う。

【0222】

次いで、ソース配線251～255、ドレイン配線257～261を形成する（図12（C））。なお、本実施例では、この配線の材料としては、AlまたはAgを主成分とする膜、またはそれらの積層膜等の反射性の優れた材料を用いることが望ましい。

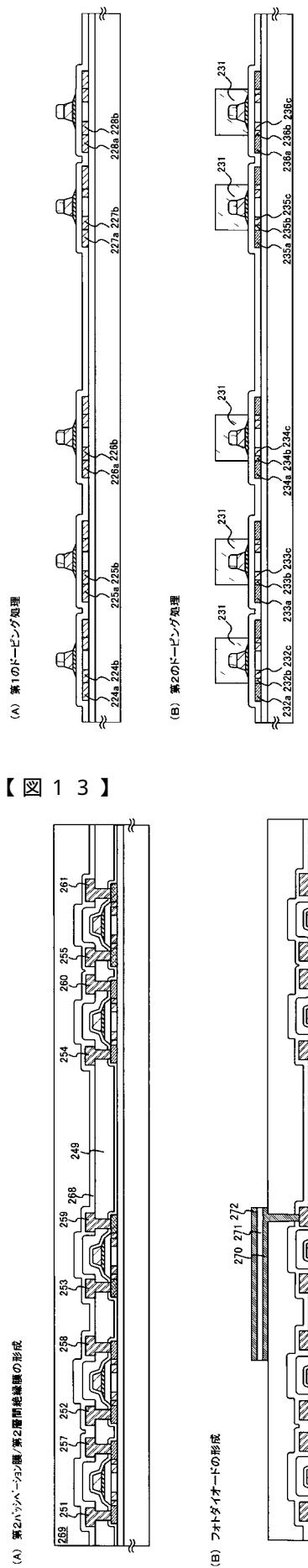

40

【0223】

次に、図13（A）に示すように50～500nm（代表的には200～300nm）の厚さで第2パッシベーション膜268を形成する。本実施例では第2パッシベーション膜268として300nm厚の窒化酸化珪素膜を用いる。これは窒化珪素膜で代用しても良い。なお、窒化酸化珪素膜の形成に先立ってH<sub>2</sub>、NH<sub>3</sub>等水素を含むガスを用いてプラズマ処理を行うことは有効である。

【0224】

次に、有機樹脂からなる第2層間絶縁膜269を形成する。有機樹脂としてはポリイミド、ポリアミド、アクリル、BCB（ベンゾシクロブテン）等を使用することができる。特

50

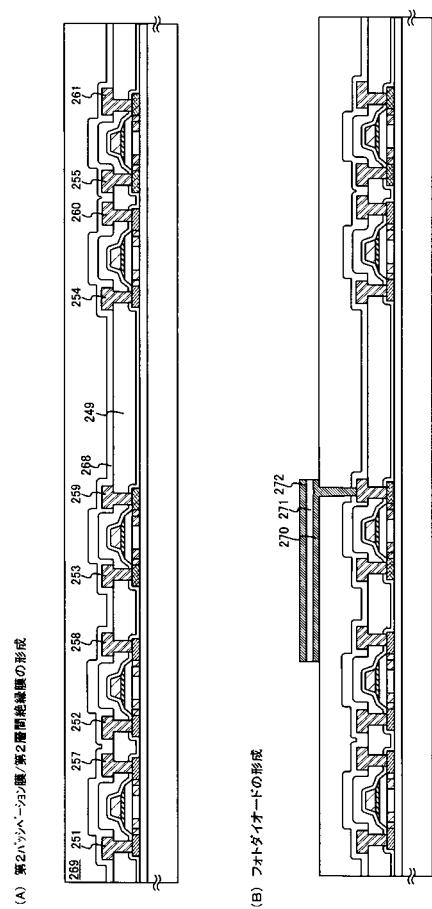

に、第2層間絶縁膜269は平坦化の意味合いが強いので、平坦性に優れたアクリルが好み。本実施例ではTFTによって形成される段差を十分に平坦化しうる膜厚でアクリル膜を形成する。好ましくは1～5μm(さらに好ましくは2～4μm)とすれば良い。

#### 【0225】

次に、第2層間絶縁膜269及び第2パッセーション膜268にドレイン配線259に達するコンタクトホールを形成し、ドレイン配線259に接するようにフォトダイオードのカソード電極270を形成する。本実施例では、カソード電極270としてスパッタ法によって形成したアルミニウム膜を用いたが、その他の金属、例えばチタン、タンタル、タンゲステン、銅を用いることができる。また、チタン、アルミニウム、チタンでなる積層膜を用いてもよい。

10

#### 【0226】

次に、水素を含有する非晶質珪素膜を基板全面に成膜した後にパターニングし、光電変換層271を形成する。次に、基板全面に透明導電膜を形成する。本実施例では透明導電膜として厚さ200nmのITOをスパッタ法で成膜する。透明導電膜をパターニングし、アノード電極272を形成する。(図13(B))

#### 【0227】

次に、図14(A)に示すように第3層間絶縁膜273を形成する。第3層間絶縁膜273として、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の樹脂を用いることで、平坦な表面を得ることができる。本実施例では、第3層間絶縁膜273として厚さ0.7μmのポリイミド膜を基板全面に形成した。

20

#### 【0228】

次に、第3層間絶縁膜273、第2層間絶縁膜269及び第2パッセーション膜268にドレイン配線261に達するコンタクトホールを形成し、画素電極275を形成する。また第3層間絶縁膜273に、アノード電極272に達するコンタクトホールを形成し、センサ用配線274を形成する。本実施例ではアルミニウム合金膜(1wt%のチタンを含有したアルミニウム膜)を300nmの厚さに形成し、パターニングを行ってセンサ用配線274及び画素電極275を同時に形成する。

#### 【0229】

次に、図14(B)に示すように、樹脂材料でなるバンク276を形成する。バンク276は1～2μm厚のアクリル膜またはポリイミド膜をパターニングして形成すれば良い。バンク276はソース配線254上に沿って形成しても良いし、ゲート配線(図示せず)上に沿って形成しても良い。なおバンク276を形成している樹脂材料に顔料等を混ぜ、バンク276を遮蔽膜として用いても良い。

30

#### 【0230】

次に、発光層277を形成する。具体的には、発光層277となる有機EL材料をクロロフォルム、ジクロロメタン、キシレン、トルエン、テトラヒドロフラン等の溶媒に溶かして塗布し、その後、熱処理を行うことにより溶媒を揮発させる。こうして有機EL材料でなる被膜(発光層)が形成される。

#### 【0231】

なお、本実施例では一画素しか図示されていないが、カラー表示を行う情報装置を作製する場合は、このとき同時に赤色に発光する発光層、緑色に発光する発光層及び青色に発光する発光層が形成される。本実施例では、赤色に発光する発光層としてシアノポリフェニレンビニレン、緑色に発光する発光層としてポリフェニレンビニレン、青色に発光する発光層としてポリアルキルフェニレンを各々50nmの厚さに形成する。また、溶媒としては1,2-ジクロロメタンを用い、80～150のホットプレートで1～5分の熱処理を行って揮発させる。

40

#### 【0232】

本実施例ではEL層を発光層でなる1層構造とするが、その他に正孔注入層、正孔輸送層、電子注入層、電子輸送層等を設けても構わない。このように組み合わせは既に様々な例が報告されており、そのいずれの構成を用いても構わない。

50

## 【0233】

発光層277を形成したら、対向電極として透明導電膜でなる陽極279を120nmの厚さに形成する。本実施例では、酸化インジウムに10~20wt%の酸化亜鉛を添加した透明導電膜を用いる。成膜方法は、発光層277を劣化させないように室温で蒸着法により形成することが好ましい。

## 【0234】

陽極279を形成したら、図14(B)に示すように第4層間絶縁膜280を形成する。第4層間絶縁膜280として、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の樹脂を用いることで、平坦な表面を得ることができる。本実施例では、第4層間絶縁膜280として厚さ0.7μmのポリイミド膜を基板全面に形成した。

10

## 【0235】

こうして図14(B)に示すような構造のセンサ基板が完成する。なお、バンク276を形成した後、第4層間絶縁膜280を形成するまでの工程をマルチチャンバー方式(またはインライン方式)の薄膜形成装置を用いて、大気開放せずに連続的に処理することは有効である。

## 【0236】

以上の様にして、バッファ用TFT304、選択用TFT305、リセット用TFT303、フォトダイオード306、スイッチング用TFT301、EL駆動用TFT302及びEL素子269を同一基板上に形成することができる。

20

## 【0237】

なお、各駆動回路(EL表示用ソース信号線駆動回路、EL表示用ゲート信号線駆動回路、センサ用ソース信号線駆動回路、センサ用ゲート信号線駆動回路)を構成するTFTも、上記作製工程によって同様に作製することができる。こうして、表示部兼入力部と同一基板上に各駆動回路を形成することができる。

## 【0238】

なお本実施例は、実施例1~実施例4と自由に組み合わせることが可能である。

## 【0239】

## [実施例6]

本実施例では、本発明を用いて情報装置を作製した例について、図6を用いて説明する。

30

## 【0240】

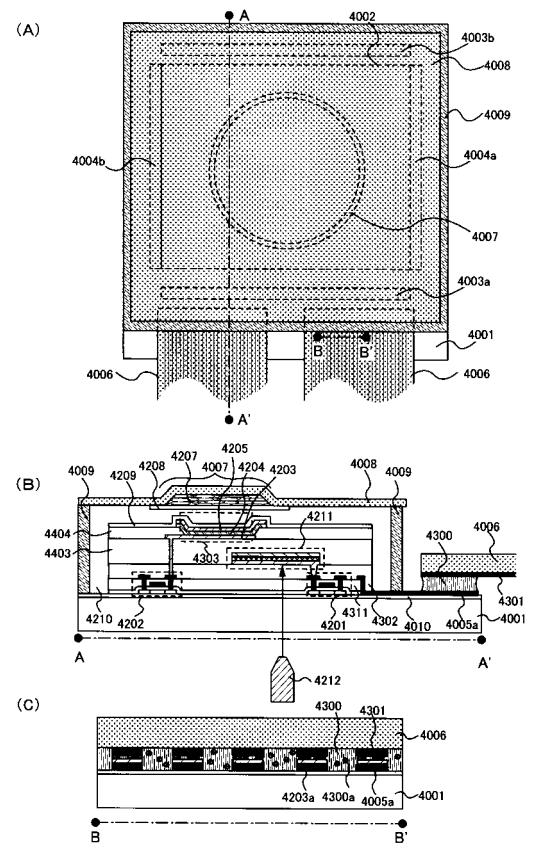

図6(A)は、TFT基板をシーリング材によって封止することによって形成された情報装置の上面図であり、図6(B)は、図6(A)のA-A'における断面図、図6(C)は図6(A)のB-B'における断面図である。

## 【0241】

同一基板4001上に設けられた表示部兼入力部4002と、センサ用およびEL素子用のソース信号線駆動回路4003a、bと、センサ用およびEL素子用のゲート信号線駆動回路4004a、bとを囲むようにして、シール材4009が設けられている。また表示部兼入力部4002と、センサ用およびEL素子用のソース信号線駆動回路4003a、bと、センサ用およびEL素子用のゲート信号線駆動回路4004a、bとの上にシーリング材4008が設けられている。よって表示部兼入力部4002と、センサ用およびEL素子用のソース信号線駆動回路4003a、bと、センサ用およびEL素子用の第1及び第2のゲート信号線駆動回路4004a、bとは、基板4001とシール材4009とシーリング材4008とによって、充填材4210で密封されている。

40

## 【0242】

また基板4001上に設けられた表示部兼入力部4002と、センサ用およびEL素子用のソース信号線駆動回路4003a、bと、センサ用およびEL素子用のゲート信号線駆動回路4004a、bとは、複数のTFTを有している。図6(B)では代表的に、下地膜4010上に形成された、画素部兼入力部4002に含まれるリセット用TFT(フォトダイオードに逆バイアス電圧をかけるためのTFT)4201及びEL駆動用TFT(EL素子への電流を制御するTFT)4202、フォトダイオード4211を図示した。

50

## 【0243】

本実施例では、リセット用 TFT4201 には公知の方法で作製された n チャネル型 TFT が用いられ、EL 駆動用 TFT4202 には公知の方法で作製された p チャネル型 TFT が用いられる。また、表示部兼入力部 4002 には EL 駆動用 TFT4202 のゲートに接続された保持容量（図示せず）が設けられる。

## 【0244】

リセット用 TFT4201、EL 駆動用 TFT4202 上には第 1 層間絶縁膜（平坦化膜）4311 が形成される。次に第 2 層間絶縁膜（平坦化膜）4302 が形成され、その上にフォトダイオード 4211 が形成される。次に第 3 層間絶縁膜 4403 が形成され、その上に EL 駆動用 TFT4202 のドレインと電気的に接続する画素電極（陽極）4203 が形成される。画素電極 4203 としては仕事関数の大きい透明導電膜が用いられる。透明導電膜としては、酸化インジウムと酸化スズとの化合物、酸化インジウムと酸化亜鉛との化合物、酸化亜鉛、酸化スズまたは酸化インジウムを用いることができる。また、前記透明導電膜にガリウムを添加したものを用いても良い。

10

## 【0245】

そして、画素電極 4203 の上には絶縁膜 4404 が形成され、絶縁膜 4404 は画素電極 4203 の上に開口部が形成されている。この開口部において、画素電極 4203 の上には EL（エレクトロルミネッセンス）層 4204 が形成される。EL 層 4204 は公知の有機 EL 材料または無機 EL 材料を用いることができる。また、有機 EL 材料には低分子系（モノマー系）材料と高分子系（ポリマー系）材料があるがどちらを用いても良い。

20

## 【0246】

EL 層 4204 の形成方法は公知の蒸着技術もしくは塗布法技術を用いれば良い。また、EL 層の構造は正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層を自由に組み合わせて積層構造または単層構造とすれば良い。

## 【0247】

EL 層 4204 の上には遮光性を有する導電膜（代表的にはアルミニウム、銅もしくは銀を主成分とする導電膜またはそれらと他の導電膜との積層膜）からなる陰極 4205 が形成される。また、陰極 4205 と EL 層 4204 の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、EL 層 4204 を窒素または希ガス雰囲気で形成し、酸素や水分に触れさせないまま陰極 4205 を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式（クラスター・ツール方式）の成膜装置を用いることで上述のような成膜を可能とする。そして陰極 4205 は所定の電圧が与えられている。

30

## 【0248】

以上のようにして、画素電極（陽極）4203、EL 層 4204 及び陰極 4205 からなる EL 素子 4303 が形成される。そして EL 素子 4303 を覆うように、絶縁膜 4302 上に保護膜 4209 が形成されている。保護膜 4209 は、EL 素子 4303 に酸素や水分等が入り込むのを防ぐのに効果的である。

## 【0249】

4005 は電源供給線に接続された引き回し配線であり、EL 駆動用 TFT4202 のソース領域に電気的に接続されている。引き回し配線 4005 はシール材 4009 と基板 4001 との間を通り、異方導電性フィルム 4300 を介して FPC4006 が有する FPC 用配線 4301 に電気的に接続される。

40

## 【0250】

シーリング材 4008 としては、ガラス材、金属材（代表的にはステンレス材）、セラミックス材、プラスチック材（プラスチックフィルムも含む）を用いることができる。プラスチック材としては、FRP（Fiberglass-Reinforced Plastics）板、PVF（ポリビニルフルオライド）フィルム、マイラーフィルム、ポリエスチルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルを PVF フィルムやマイラーフィルムで挟んだ構造のシートを用いることもできる。

50

## 【0251】

但し、E L 素子からの光の放射方向がカバー材側に向かう場合にはカバー材は透明でなければならない。その場合には、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透明物質を用いる。

## 【0252】

また、充填材4103としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができ、PVC(ポリビニルクロライド)、アクリル、ポリイミド、エポキシ樹脂、シリコン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)を用いることができる。本実施例では充填材として窒素を用いた。

10

## 【0253】

また充填材4210を吸湿性物質(好ましくは酸化バリウム)もしくは酸素を吸着しうる物質にさらしておくために、シーリング材4008の基板4001側の面に凹部4007を設けて吸湿性物質または酸素を吸着しうる物質4207を配置する。そして、吸湿性物質または酸素を吸着しうる物質4207が飛び散らないように、凹部カバー材4208によって吸湿性物質または酸素を吸着しうる物質4207は凹部4007に保持されている。なお凹部カバー材4208は目の細かいメッシュ状になっており、空気や水分は通し、吸湿性物質または酸素を吸着しうる物質4207は通さない構成になっている。吸湿性物質または酸素を吸着しうる物質4207を設けることで、E L 素子4303の劣化を抑制できる。

20

## 【0254】

図6(C)に示すように、画素電極4203が形成されると同時に、引き回し配線4005上に接するように導電性膜4203aが形成される。

## 【0255】

また、異方導電性フィルム4300は導電性フィラー4300aを有している。基板4001とFPC4006とを熱圧着することで、基板4001上の導電性膜4203aとFPC4006上のFPC用配線4301とが、導電性フィラー4300aによって電気的に接続される。

## 【0256】

なお、本実施例は、実施例1～実施例5と自由に組み合わせて実施することが可能である。

30

## 【0257】

## [実施例7]

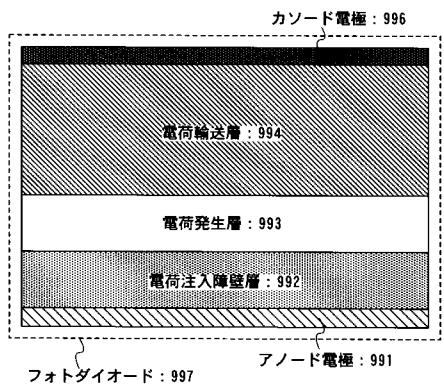

本実施例では、本発明の情報装置の光電変換素子を、有機物を用いて作製した例について説明する。

## 【0258】

光電変換素子として、フォトダイオードを例に説明する。

## 【0259】

フォトダイオードの光電変換層として、有機物を用いる。具体的には、アゾ顔料、ペリレンのような多環式化合物、フタロシアニン顔料、イオン性色素などを用いることができる。なお、ここでは光電変換層を、電荷発生層と呼ぶ事にする。

40

## 【0260】

また、電荷発生層のほかに、電荷注入障壁層や、電荷輸送層等を設けることもできる。

## 【0261】

電荷輸送層としては、ヒドラゾン誘導体、スチルベンゼン誘導体、トリファニルアミン誘導体等の低分子化合物、ポリシラン誘導体等の高分子材料を利用することができる。

## 【0262】

この様な電荷輸送層を設けることで、フォトダイオードの光応答特性を向上させることができる。

## 【0263】

50

また、電荷注入障壁層としては、共重合ナイロン等を用いることができる。

【0264】

この様な、電荷注入障壁層と電荷発生層と電荷輸送層の積層構造を有するフォトダイオードを作製する手法について図19を用いて説明する。

【0265】

ITO膜のアノード電極991を形成し、その上に電荷注入障壁層992、電荷発生層993、電荷輸送層994、カソード電極996の順に形成する。

【0266】

ここでは、電荷注入障壁層992としては、共重合ナイロン層を塗布する。

【0267】

その後、アゾ顔料をバインダ樹脂に分散し塗布することで、電荷発生層993を形成する。

【0268】

次に、ヒドラゾン誘導体をバインダ樹脂に分散し、塗布することで、電荷輸送層994を形成する。

【0269】

最後に、アルミニウムでカソード電極996を形成し、フォトダイオード997が完成する。

【0270】

なお、フォトダイオードの構成はこれに限定されない。電荷注入障壁層や電荷輸送層は必ずしも設定する必要はない。

【0271】

また、アノード電極、カソード電極、電荷注入障壁層、電荷発生層、電荷輸送層等は、上記材料に限らず、公知の材料を自由に用いる事ができる。

【0272】

半導体等の無機物を用いたフォトダイオードに比べて、有機物を用いたものは、大面積のフォトダイオードが作製可能であり、また柔軟性に富み、加工性に優れるといった利点がある。

【0273】

なお、本実施例は、実施例1～実施例6と自由に組み合あわせて実施する事が可能である。

【0274】

[実施例8]

本実施例では、本発明の情報装置を応用した電子機器について説明する。本発明の情報装置を応用する例として、携帯情報端末(PDA、携帯電話または電子書籍等)などが挙げられる。

【0275】

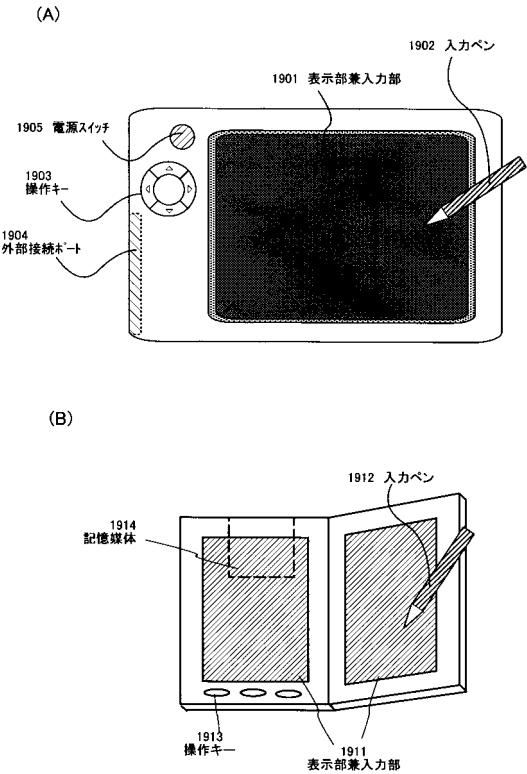

図4(A)は、PDAの模式図である。表示部兼入力部1901と入力ペン1902、操作キー1903、外部接続ポート1904及び電源スイッチ1905を有する。本発明の情報装置はPDAの表示部兼入力部1901に用いることができる。

【0276】

図4(B)は、電子書籍の模式図である。表示部兼入力部1911と入力ペン1912、操作キー1913及び記録媒体1914を有する。本発明の情報装置は電子書籍の表示部兼入力部1911に用いることができる。

【0277】

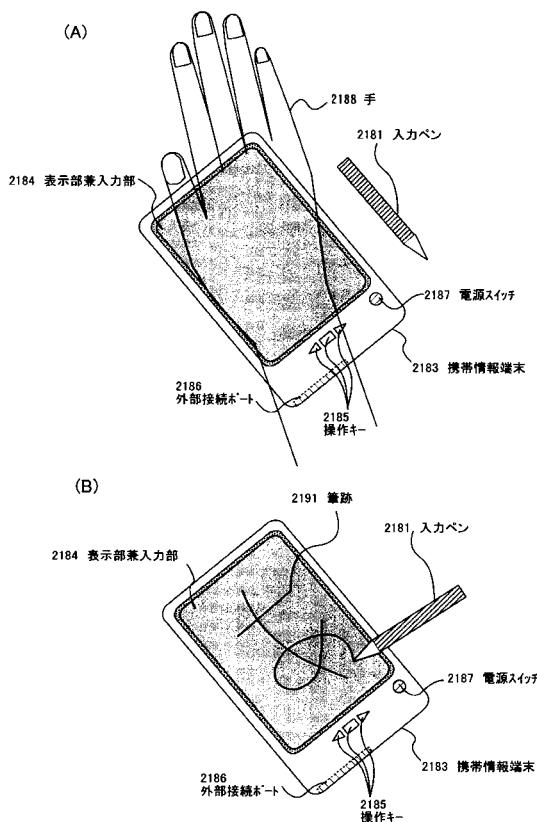

図21(A)及び図21(B)は、本発明の情報装置を、本人認証作業の機能を有する携帯情報端末に応用した例である。

【0278】

ここで、本人認証作業とは、予め登録されている情報と、その後入力された情報とを比較して、この2つの情報が、同じ人物を指し示すものかどうかを判断する機能のことをいう

10

20

30

40

50

とする。

【0279】

図21(A)に携帯情報端末2183を示す。この携帯情報端末2183は、入力ペン2181、表示部兼入力部2184、操作キー2185、外部接続ポート2186、電源スイッチ2187等を有する。

【0280】

実施例4において示した、表示部兼入力部2184をイメージセンサとして用いる手法を用い、手2188を、表示部兼入力部2184上に置いて、掌紋を読み取る。

【0281】

この読み取った掌紋を、個人を識別する情報(個人情報)として用いて、認証作業を行うことができる。

10

【0282】

なお、認証作業に用いる個人情報は、掌紋のみに限らず、指紋等の生体情報を自由に用いることができる。

【0283】

また、これらの、認証のための個人情報は、自由に組み合わせて用いることができる。

【0284】

また、図21(B)は、図21(A)で示したのと同じ構成の携帯情報装置であるが、異なる方法で本人認証作業を行う場合について説明する。

20

【0285】

ここでは、入力ペン2181によって、表示部兼入力部2184に入力した筆跡2191の情報を、認証作業に用いる。

【0286】

なお、ペン入力によって入力された、筆跡などの個人情報と、イメージセンサによって入力された、掌紋、指紋などの個人情報を、自由に組み合わせて、本人認証の作業を行う携帯情報端末に応用することもできる。

【0287】

本発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1~7のどのような組み合わせからなる構成を用いても実現することができる。

30

【発明の効果】

従来の抵抗膜式や光学式のペン入力機能を有する情報装置では、画像の視認性、装置の耐久性、精度や小型化、消費電力等の問題があった。

【0288】

本発明のペン入力機能を有する情報装置は、表示装置の画素に、EL素子と光電変換素子の両方を配置し、ペン先が発光するペンによって、光電変換素子に光を入力することによって情報入力を行う。これによって、表示画像の輝度を損なわず、また鮮明な画像を表示し、耐久性に優れ、小型化可能で、精度の良い、ペン入力機能を有する情報装置が得られる。

【図面の簡単な説明】

40

【図1】 本発明の情報装置の模式図。

【図2】 本発明の光センサの上面及び断面の模式図。

【図3】 本発明の情報装置のイメージセンサ付表示パネルの画素部の回路図。

【図4】 本発明の情報装置を応用した電子機器の図。

【図5】 本発明の情報装置の駆動のタイミングチャートを示す図。

【図6】 本発明の情報装置の上面図及び断面図。

【図7】 従来の抵抗膜式ペン入力装置の構造を示す図。

【図8】 従来の抵抗膜式ペン入力装置の構造を示す図。

【図9】 従来の光学式ペン入力装置の構造を示す図。

【図10】 本発明の情報装置の作製工程を示す図。

50

- 【図11】 本発明の情報装置の作製工程を示す図。

- 【図12】 本発明の情報装置の作製工程を示す図。

- 【図13】 本発明の情報装置の作製工程を示す図。

- 【図14】 本発明の情報装置の作製工程を示す図。

- 【図15】 本発明の情報装置の断面図。

- 【図16】 本発明の情報装置の断面図。

- 【図17】 本発明の情報装置の駆動のタイミングチャートを示す図。

- 【図18】 本発明の情報装置の駆動のタイミングチャートを示す図。

- 【図19】 本発明の情報装置の光電変換素子の構成を示す図。

- 【図20】 本発明の情報装置の断面図。

- 【図21】 本発明の情報装置を応用した電子機器の図。 10

【図1】

【図2】

【図3】

【 図 4 】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

(A) 半導体層の形成/絶縁膜の形成/第1の導電層と第2の導電層の形成

【 図 1 1 】

## 【図12】

### 【 図 1 3 】

### 【図14】

【 図 1 5 】

【 図 1 6 】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(51)Int.Cl. F I

H 01H 35/00 (2006.01) H 01H 35/00 K

H 01H 35/00 C

(56)参考文献 特開平11-326954 (JP, A)

特開平11-194321 (JP, A)

特開2000-323662 (JP, A)

特開平03-205783 (JP, A)

特開平05-110055 (JP, A)

特開平05-020712 (JP, A)

特開平11-025257 (JP, A)

特開昭61-084055 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 3/041

G06F 3/042

G09F 9/00

G09F 9/30

H01H 35/00

H01L 27/32