### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2007/0114649 A1

Partridge et al.

May 24, 2007 (43) Pub. Date:

### (54) LOW PROFILE STACKING SYSTEM AND **METHOD**

(75) Inventors: Julian Partridge, Austin, TX (US); James W. Cady, Austin, TX (US);

James Wilder, Austin, TX (US); David L. Roper, Austin, TX (US); James Douglas Wehrly JR., Austin, TX (US)

Correspondence Address:

FISH & RICHARDSON P.C. P.O BOX 1022 Minneapolis, MN 55440-1022 (US)

(73) Assignee: Staktek Group L.P., a Texas Limited Partnership

(21) Appl. No.: 11/626,318

(22) Filed: Jan. 23, 2007

#### Related U.S. Application Data

(60) Division of application No. 11/011,469, filed on Dec. 14, 2004, now Pat. No. 7,180,167, which is a division of application No. 10/457,608, filed on Jun. 9, 2003, which is a continuation-in-part of application No. 10/005,581, filed on Oct. 26, 2001, now Pat. No. 6,576,992.

#### **Publication Classification**

(51) Int. Cl. H01L 23/02 (2006.01)

(57)**ABSTRACT**

The present invention provides a system and method that mounts integrated circuit devices onto substrates and a system and method for employing the method is stacked modules. The contact pads of a packaged integrated circuit device are substantially exposed. A solder past that includes higher temperature solder paste alloy is applied to a substrate or to the integrated circuit device to be mounted. The integrated circuit device is positioned to contact the contacts of the substrate. Heat is applied to create high temperature joints between the contacts of the substrate and the integrated circuit device resulting in a device-substrate assembly with high temperature joints. The formed joints are less subject to re-melting in subsequent processing steps. The method may be employed in devising stacked module constructions such as those disclosed herein as preferred embodiments in accordance with the invention. Typically, the created joints are low in profile.

# LOW PROFILE STACKING SYSTEM AND METHOD

#### RELATED APPLICATIONS

[0001] The present application is a division of application Ser. No. 11/011,469, filed Dec. 14, 2004, pending, which is a division of application Ser. No. 10/457,608, filed Jun. 9, 2003, which is a continuation-in-part of U.S. patent application Ser. No. 10/005,581, filed Oct. 26, 2001, all of which are hereby incorporated by reference.

#### TECHNICAL FIELD

[0002] The present invention related to mounting integrated circuit devices on substrates and to mounting integrated circuits on substrates employed in stacked modules.

#### BACKGROUND OF THE INVENTION

[0003] A variety of methods are used to mount integrated circuit devices to substrates such as PWBs and flex circuitry. Solder paste is selectively applied to the integrated circuit device or substrate to which the IC is to be attached. The device and substrate are exposed to reflow temperatures of approximately 220° C. The device is, consequently, soldered to the substrate.

[0004] Typically, however, the formed solder joints will re-melt during subsequent processing. Common tin-lead solders start to melt as 183° C. and, when exposed to such temperatures and higher, the exposed joint may re-melt and become unreliable.

[0005] What is needed, therefore, is a technique and system for mounting integrated circuit devices on substrates that provide an efficient and readily implemented technique to create structures that reliably withstand subsequent exposure to typical tin-lead solder melting point temperatures.

#### SUMMARY OF THE INVENTION

[0006] The present invention provides a system and method that mounts integrated circuit devices onto substrates and a system and method for employing the method in stacked modules. The contact pads of a packaged integrated circuit device are substantially exposed. A solder past that includes higher temperature solder paste alloy is applied to a substrate or the contacts of the packaged device. The integrated circuit device is positioned to contact the contacts of the substrate with the higher temperature solder alloy paste between. Heat is applied to create high temperature joints between the contacts of the substrate and the integrated circuit device resulting in a device-substrate assembly with high temperature joints. The formed joints are less subject to re-melting in subsequent processing steps. The method may be employed in devising stacked module constructions such as those disclosed herein as preferred embodiments in accordance with the invention. Typically, the created joints are low in profile. In a method in accordance with the present invention, a first solder used to construct a stacked module has a higher melting point than a second solder used to populate a board with that module.

#### BRIEF DESCRIPTION OF THE DRAWINGS

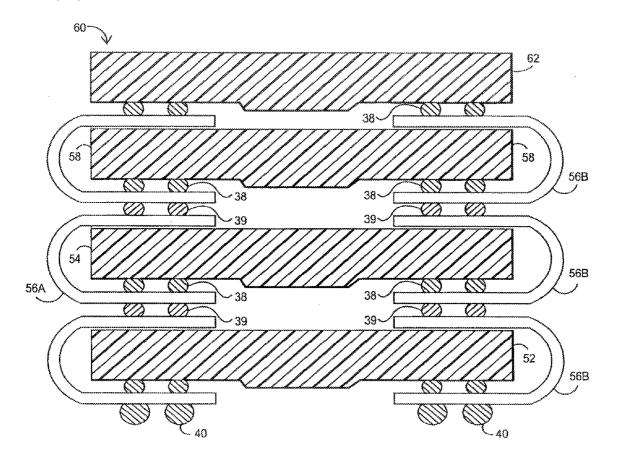

[0007] FIG. 1 depicts a typical prior art packaged integrated circuit device.

[0008] FIG. 2 depicts the device of FIG. 1 from which the solder ball contacts have been removed.

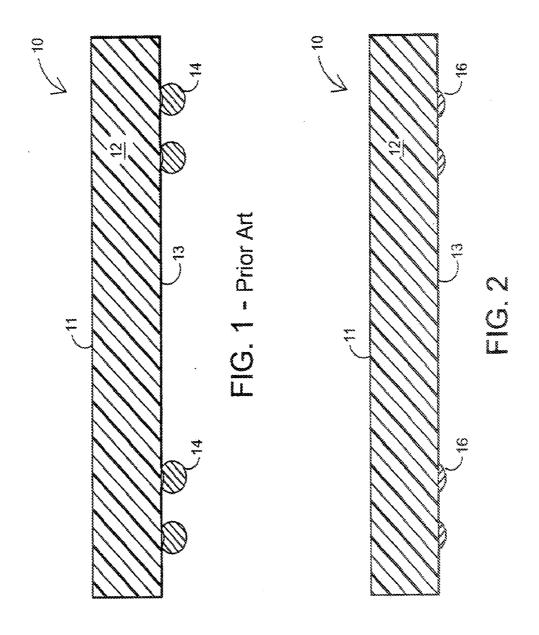

[0009] FIG. 3 depicts a set of substrate contacts upon which a high temperature solder paste has been applied in accordance with a preferred embodiment of the present invention.

[0010] FIG. 4 depicts portions of two flexible circuit connectors prepared for mounting of an integrated circuit device in accordance with a preferred embodiment of the present invention.

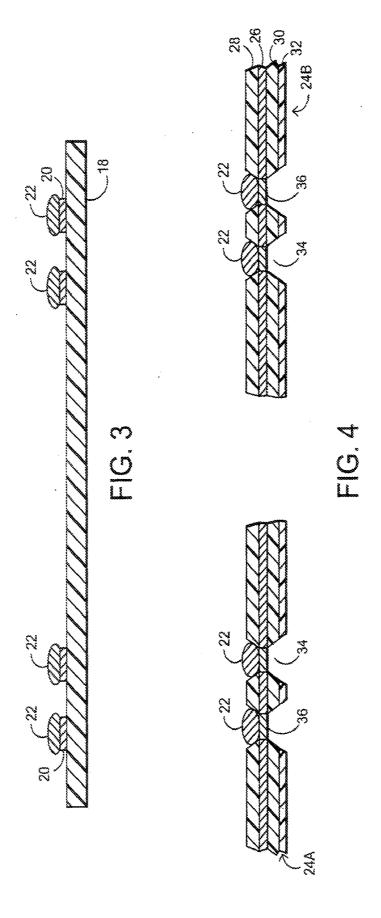

[0011] FIG. 5 depicts a device-substrate assembly in accordance with a preferred embodiment of the present invention.

[0012] FIG. 6 depicts a two-high integrated circuit module mounted to the two flexible circuit connectors depicted in FIG. 4 in accordance with a preferred embodiment of the present invention.

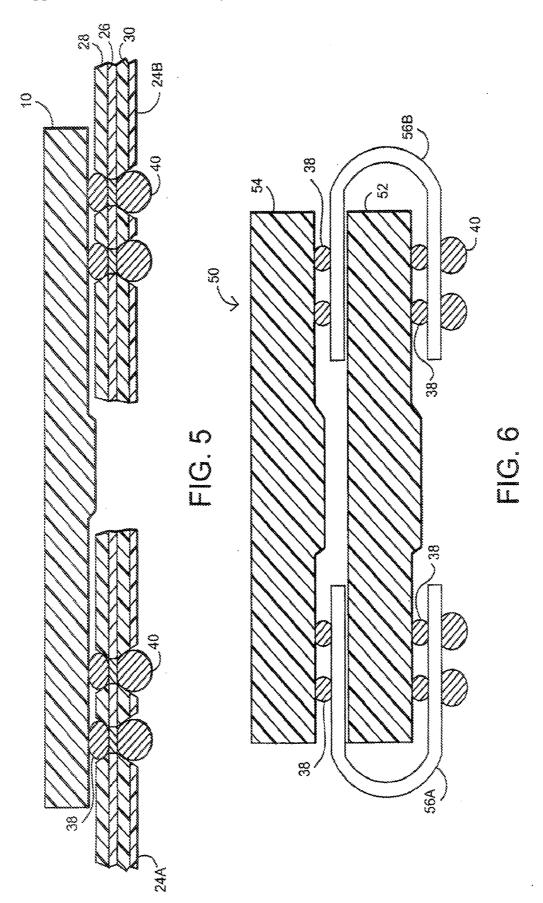

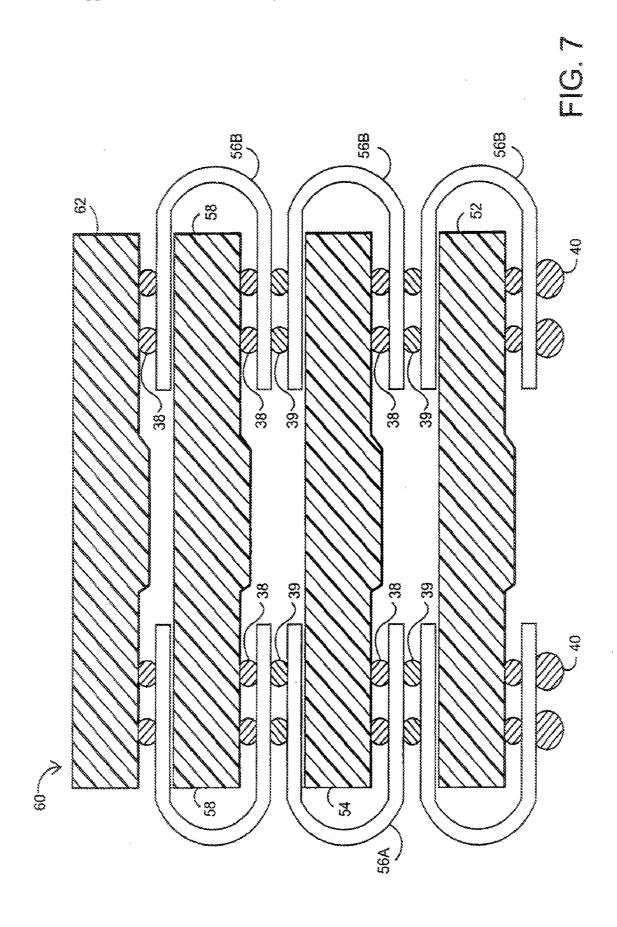

[0013] FIG. 7 depicts a four-high stacked module devised in accordance with a preferred embodiment of the present invention.

# DESCRIPTION OF PREFERRED EMBODIMENTS

[0014] FIG. 1 depicts an exemplar integrated circuit device 10 having upper surface 11 and lower surface 13. Device 10 is an example of one type of the general class of devices commonly known in the art as chip-scale-packaged integrated circuits ("CSPs"). The present invention may employed with a wide variety of integrated circuit devices and is not, as those of skill in the art will understand, limited to devices having the profile depicted in FIG. 1. Further, although its preferred use is with plastic-bodied CSP devices, the invention provides advantages in mounting a variety of packaged integrated circuit devices in a wide variety of configurations including leaded and CSP topologies.

[0015] Exemplar integrated circuit device 10 may include one or more integrated circuit die and body 12 and a set of contacts 14. The illustrated integrated circuit device 10 has CSP ball contacts 14 arrayed along surface 13 of its body 12. Typically, when integrated circuit device 10 is a CSP device, CSP ball contacts 14 are, as depicted, balls that are a mixture of tin and lead with common relative composition of 63% tin and 37% lead. Such contacts typically have a melting point of about 183° C. Other contacts are sometimes found along a planar surface of integrated circuit devices and such other contacts may also be treated in accordance with the present invention where the opportunity may also be treated in accordance with the present invention where the opportunity arises as will be understood after gaining familiarity with the present disclosure.

[0016] In the depiction of FIG. 2, CSP ball contacts 14 have been removed, leaving CSP pads 16 arrayed along lower surface 13. CSP pads 16 will typically exhibit a residual thin layer of tin/lead mixture after removal of CSP ball contacts 14. As those of skill will know, CSPs may be received without attached balls and the process and structures described herein will then not require "removal" of balls. Further, embodiments of the present invention may be

implemented with CSPs already bearing ball contacts comprised of high temperature solders.

[0017] FIG. 3 depicts exemplar substrate 18 on which are disposed contacts 20. Substrate 18 is depicted as a rigid board such as a PWB or PCB such as are known in the art. In accordance with a preferred embodiment of the present invention, a solder paste 22 is applied to substrate contacts 20. In accordance with an alternative preferred embodiment of the invention, solder paste 22 is applied to the CSP pads 16 and not the substrate contacts 20. However, as those skilled will recognize, solder paste 22 may applied to both substrate contacts 20 and CSP pads 16 (or a set of contacts of other configuration when devices that are not CSP are used in accordance with the invention.) As those of skill understand, solder paste is a mixture of solder particles and flux

[0018] Two or more of the elements lead, tin, silver, copper, antimony, or indium may be employed in a variety of combinations to devise a solder to be employed in solder paste 22 in accordance with the present invention. Therefore, in accordance with preferred embodiments of the present invention, a solder alloy employed in solder paste 22 exhibits a melting point equal to or greater than 235° C. and, preferably between 235° C. and 312° C. The alloy chosen should not have a melting point so high that the IC package is adversely affected, but it should also not be so low as to remelt during board assembly operations.

[0019] Some market participants are starting to implement lead-free solders. Such lead-free solders will typically have melting points higher than those found in lead inclusive solders. Typically, those who use lead-free solders to populate boards with stacked modules will, for example, employ temperatures up to 240° C. in the process of attachment of stacked modules to boards. Consequently, a HT joint implemented with a lead-free alloy will, in conformity with preferred embodiments of the present invention, exhibit a melting point greater than those lead-free solders used to populate boards. Consequently, a preferred implementation of the HT joints of the present invention will have a melting point range of between 245° C. and 265° C. The lead-free solder alloy employed in such HT joints will be comprised of at least two of the following elements: tin, silver, copper, or indium.

[0020] Preferably, an alloy used as a solder in the present invention will melt over a narrow temperature range. Disintegration of the module during board attachment or population will be less likely if the melt range is narrow. Most preferably, the top of the melting point range of the solder used in board attachment should be exceeded by 15° C. by the melting point of the solder used to manufacture the stacked module although in the case of lead-free solder, this is reduced to ameliorate issues that could arise from exposure of the package to high temperatures.

[0021] The following combinations have been found to exhibit the following melting points, and the below recited combinations are merely a representative, but not exhaustive, list of examples of solder alloys appropriate for use in the present invention. As those of skill will recognize, these examples are instructive in selecting other preferred particular combinations of lead, tin, silver copper, antimony, and indium that are readily employed to advantage in the present invention so as to arrive at alloys of at least two of the

following solder elements: lead, tin, silver, copper, antimony, and indium that have in their combined mixture, a preferred melting point between 235° C. to 312° C. inclusive.

- [0022] a. A combination of 95% Sn and 5% Sb melts over a range of 235° C. to 240° C.

- [0023] b. A combination of 83% Pb and 10% Sb and 5% Sn and 2% Ag melts over a range of 237° C. to 247° C.

- [0024] c. A combination of 85% Pb and 10% Sb and 5% Sn melts over a range of 245° C. to 255° C.

- [0025] d. A combination of 90% Pb and 10% Sb melts over a range of 252° C. to 260° C.

- [0026] e. A combination of 92.5% Pb, 5% Sn and 2.5% Ag melts over a range of 287° C. to 296° C.

- [0027] f. A combination of 90% Pb and 10% Sn melts over a range of 275° C. to 302° C.

- [0028] g. A combination of 95% Pb and 5% Sn melts over a range of 275° C. to 302° C.

- [0029] h. A combination of 75% Pb and 25% Indium melts over a range of 240° C. to 260° C.

[0030] Those of skill will note that solder alloys or mixtures may also be employed in embodiments of the present invention that exhibit melting points lower than 235° C., as would be exhibited for example with a 97% Sn and a 3% Sb alloy, but preferred embodiments will employ solder mixtures or alloys that melt between 235° C. and 312° C. inclusive.

[0031] FIG. 4 depicts portions of two flexible circuit connectors 24A and 24B prepared for mounting of a device 10 in accordance with a preferred embodiment of the present invention. Exemplar flex circuits 24A and 24B may be simple flex circuitry or may exhibit the more sophisticated designs of flex circuitry such as those that would be constructed in accordance with the detailed descriptions provided in U.S. patent application Ser. No. 10/005,581 which has been made part of this application by incorporation by reference. For clarity of exposition, depicted flex circuits 24A and 24B exhibit a single conductive layer 26 and a first outer layer 28. Conductive layer 26 is supported by substrate layer 30, which, in a preferred embodiment, is a polymide. Outer layer 32 resides along the lower surface of the flex circuits 24A and 24B. Optional outer layers 28 and 32, when present, are typically a covercoat or solder mask material. Windows 34 are created through outer layer 32 and intermediate layer 30 to expose flex contacts 36.

[0032] As depicted in FIG. 4, solder paste 22 is applied to flex contacts 36 which are demarked at the level of conductive layer 26. Solder paste 22 may also alternatively or in addition, be applied to the CSP pads 16 of a CSP. Windows 34 provide openings through which module contacts may be disposed in a later stacked module assembly step. Those of skill will recognize that the method of the present invention is applicable to a wide variety of substrates including solid PWB's, rigid flex, and flexible substrates such as flexible circuits, for example, and the substrate employed can be prepared in accordance with the present invention in a manner appropriate for the intended application. Where the invention is employed with rigid substrates such as a PWB,

multilayer strategies and windowing in substrate layers are techniques which are useful in conjunction with the present invention, but not essential.

[0033] FIG. 5 depicts a device-substrate assembly in accordance with a preferred embodiment of the present invention as may be employed in the construction of a low profile stacked module. The features depicted in FIG. 5 are not drawn to scale, and show various features in an enlarged aspect for purposes of illustration. As shown, integrated circuit device 10 is disposed upon flex circuits 24A and 24B which have been, in a preferred embodiment of the method of the present invention, previously prepared as shown in earlier FIG. 4. Module contacts 40 have been appended to flex circuits 24A and 24B to provide connective facility for the device-flex combination whether as part of a stacked module or otherwise.

[0034] High temperature joints contacts 38 ("HT joints") are formed by the melting of the lead alloy in previously applied solder paste 22 and the application of a selected heat range appropriate for the solder mixtures identified previously. Thus, HT joints 38 will, after solidification, typically not re-melt unless exposed subsequently to such temperature ranges. The temperature range applied in this step of assembly will not typically be subsequently encountered in a later assembly operation such as, for example, the application of a stacked module to a DIMM board. Consequently, in one embodiment, the present invention is articulated as a stacked module having HT joints that is appended to a DIMM board with traditional lower melting point solder.

[0035] FIG. 6 depicts a two-high stacked module devised in accordance with a preferred embodiments of the present invention. Stacked module 50 shown in FIG. 6 includes lower integrated circuit device 52 and upper integrated circuit device 54. A stacked module 50 may be devised in accordance with the present invention that includes more than two packaged integrated circuit devices. Flex circuits 56A and 56B are depicted connecting lower integrated circuit device 52 and upper integrated circuit device 54. Those of skill will also recognize that module 50 may be implemented with a single flexible circuit connector. Further, the flexible circuit connectors employed in accordance with the invention may exhibit one or more conductive layers. Flex circuits 56A and 56B may be any circuit connector structure that provides connective facility between two integrated circuits having a contact array. Those of skill will note that flexible circuits 56A and 56B may exhibit single conductive layers (such as, for example, the flexible circuit connectors earlier illustrated herein and identified for descriptive purposes as flex circuits 24A and 24B in FIG. 5) or may exhibit multiple conductive layers. examples of other preferred flexible circuit structures are found in U.S. application Ser. No. 10/005,581 which has been incorporated by reference and those of skill will readily appreciate how a variety of circuit structures may be employed in preferred embodiments. Further, the connective structures used to connect lower integrated circuit 52 with upper integrated circuit 54 need not literally be flexible circuit connectors but may be flexible in portions and rigid in other protions.

[0036] HT contacts 38 are employed in the preferred embodiment of FIG. 6 to provide connective facility between the respective integrated circuits and contacts borne

by the flex circuits 56A and 56B. Preferably, HT joints 38 will exhibit a height dimension smaller than that of CSP ball contacts 14 shown earlier as part of typical CSPs in FIG. 1. As those of skill will recognize, HT joints 38 are depicted in a scale that is enlarged relative to joint sizes that would typically be encountered in actual practice of preferred modes of the invention. Thus, module 50 will preferably present a lower profile that stacked modules created employing typical CSP contacts 14 on each of the constituent integrated circuit packages employed in a stacked module 50.

[0037] FIG 7 depicts module 60 as having lower integrated circuit element 52, upper IC element 54, 3rd IC element 58, and 4<sup>th</sup> IC element 62. When the present invention is employed between flex circuits in stacking multiple levels of CSPs, as for example in FIG. 7, some embodiments will present HT contacts that have minimal heights that do not cause appreciable separation between the flex circuitry associated IC 52 and IC 54, for example, or between IC 54 and IC 62, for example. For such embodiments, the apparent height for illustrated HT joints 39, particularly, that lie between respective layers of flex circuitry pairs 56A and 56B are also shown but, as in other embodiments, the invention may be implemented with a variety of substrates including single flex circuits in place of the depicted pair and with flexible circuits that have one or plural conductive layers.

[0038] As shown, the HT joints provide connections between integrated circuit devices and substrates and the overall profile of module 60 is reduced by use of the present invention that provides advantages in subsequent processing steps such as for example, affixation of module 60 to DIMM boards, for example.

[0039] To construct a stacked module in accordance with a preferred embodiment of the present invention, if present, ball contact 14 are removed from a CSP leaving CSP contacts 16 that typically exhibit a residual layer of solder. A high temperature solder paste composed from a lead alloy or mixture that has a preferable melting point equal to or higher that 235° C. and preferably less than 312° C. is applied to substrate contacts 20 of a substrate such as a flexible circuit and/or the substrate contacts to which it is to be mounted. The CSP is positioned to place the CSP pads 16 and substrate contacts 22 in appropriate proximity. Heat is applied sufficient to melt the lead solder alloy of solder paste 22 thus forming HT joints 38. The flexible circuit is positioned to place portions of the flexible circuit connector between the first CSP and a second CSP that is connected to the substrate with HT joints created using the process described for creating HT joints.

[0040] In understanding the present invention, it may be helpful to articulate the relative melting points in terms of variables to illustrate the relationships between the HT joints used to construct a stacked module and the solders used to populate a board with such HT joint-implemented stacked module. In use in board population, the present invention will provide a stacked high module that is assembled using the HT joints that exhibit melting point ranges between X and Y degrees where X is less that Y. Attachment of the stacked module to a board is then implemented with a solder having a melting point between A and B degrees where A and B are less that X.

- [0041] Although the present invention has been described in detail, it will be apparent to those skilled in the art that the invention may be embodied in a variety of specific forms and that various changes, substitutions and alterations can be made without departing from the spirit and scope of the invention. The described embodiments are only illustrative and not restrictive and the scope of the invention is, therefore, indicated by the following claims.

- 1. A high temperature joint in a stacked circuit module in which a first integrated circuit element is disposed above a second integrated circuit element, the high temperature joint comprising:

- an alloy comprised of lead and antimony having the proportion of no more that 95% tin and at least 5% antimony, the alloy having a melting point between 235° C. to 260° C.

- 2. A high temperature joint in a stacked circuit module in which a first integrated circuit element is disposed above a second integrated circuit element, the high temperature joint comprising:

- an alloy comprised of lead and tin, the alloy having a melting point between 275° C. 312° C.

- **3**. A high temperature joint in a stacked circuit module in which a first integrated circuit element is disposed above a second integrated circuit element, the high temperature joint comprising:

- an alloy comprised of lead, the alloy having a melting point of between 235 $^{\circ}$  C. and 312 $^{\circ}$  C.

\* \* \* \* \*