## MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102009901727315 |

|------------------------------|-----------------|

| Data Deposito                | 28/04/2009      |

| Data Pubblicazione           | 28/10/2010      |

Classifiche IPC

Titolo

DISPOSITIVO E METODO DI PROTEZIONE DA DISTURBI PER UN SEGNALE DIGITALE

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"DISPOSITIVO E METODO DI PROTEZIONE DA DISTURBI PER UN

SEGNALE DIGITALE"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MI)

Inventori: CAULI Arber, PRANDI Luciano, CAMINADA Carlo

\* \* \*

La presente invenzione si riferisce ad un dispositivo e a un metodo di protezione da disturbi per un segnale digitale.

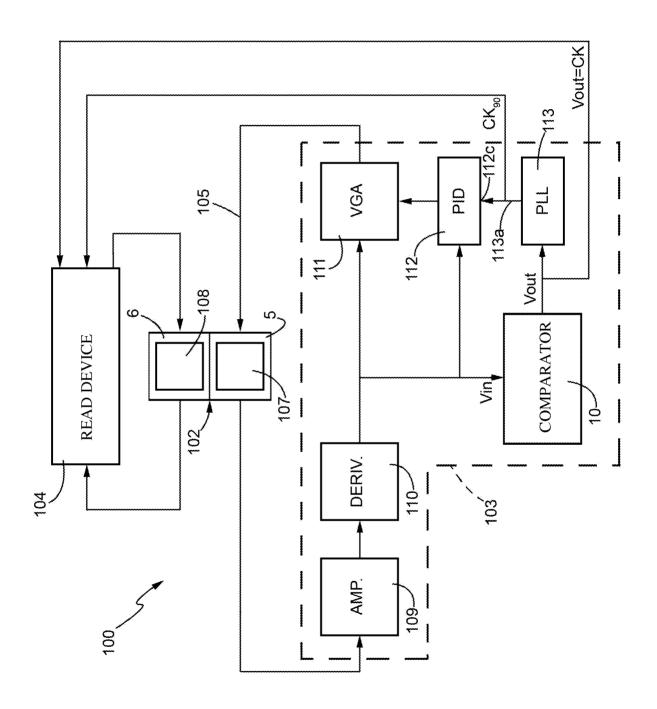

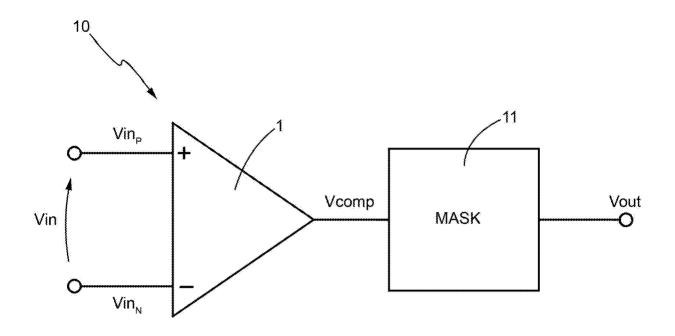

La figura 1 mostra un comparatore 1 differenziale a tempo continuo, di tipo noto. Il comparatore 1 è configurato per accettare in ingresso un segnale di ingresso analogico Vin e fornire in uscita un segnale di comparazione Vcomp, di tipo binario, che può assumere un valore logico alto Vcomp $_{\rm H}$  (uno logico) o basso Vcomp $_{\rm L}$  (zero logico) sulla base del segnale di ingresso analogico Vin. Più in dettaglio, il comparatore 1 riceve su un ingresso invertente e su un ingresso non invertente il segnale di ingresso analogico Vin. In uso, il comparatore 1 compara il segnale di tensione Vin $_{\rm P}$  presente sull'ingresso non invertente con il segnale di tensione Vin $_{\rm N}$  presente

sull'ingresso invertente, e fornisce in uscita il segnale di comparazione Vcomp secondo la seguente formula (1):

$$\begin{cases} Vcomp = Vcomp_{L} & se & Vin_{P} < Vin_{N} \\ Vcomp = Vcomp_{H} & se & Vin_{P} > Vin_{N} \end{cases}$$

(1)

Risulta chiaro che, mentre i segnali di tensioni  $Vin_P$  e  $Vin_N$  sono segnali analogici, il segnale di comparazione Vcomp è di tipo binario, poiché assume alternativamente il valore logico alto  $Vcomp_H$  o il valore basso  $Vcomp_L$ . Definendo il segnale di ingresso analogico Vin come segnale differenziale  $Vin=Vin_P-Vin_N$  le equazioni della formula (1) possono essere espresse secondo la seguente formula (2):

$$\begin{cases} Vcomp = Vcomp_{L} & se & Vin < 0 \\ Vcomp = Vcomp_{H} & se & Vin > 0 \end{cases}$$

(2)

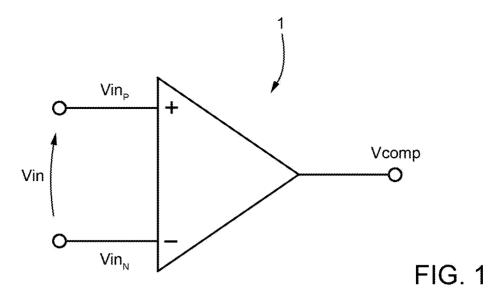

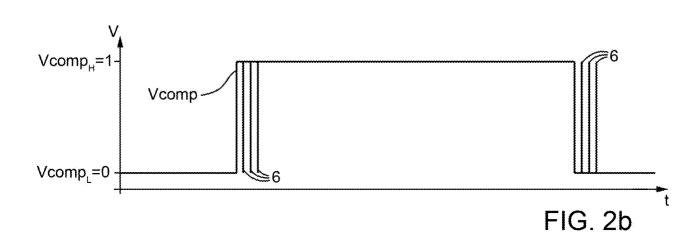

La figura 2a mostra un segnale di ingresso analogico Vin di tipo sinusoidale, rappresentato mostrando i segnali di tensione  $Vin_P$  e  $Vin_N$  agli ingressi del comparatore 1, oscillante entro i valori di tensione (-Vs, ..., +Vs), mentre la figura 2b mostra il segnale di comparazione Vcomp, che assumere il valore logico  $Vcomp_H=1$  o  $Vcomp_L=0$  secondo le equazione espresse dalla formula (2).

Il segnale di ingresso analogico Vin comprende generalmente una componente di segnale utile ed una componente di disturbo. La componente di disturbo può essere a sua volta scomposta in una componente di rumore elettronico e in una componente di disturbo impulsivo, ad esempio causata da accoppiamenti capacitivi, spesso associati a strutture a capacità commutate (circuiti di

tipo "switched capacitor"), che causano picchi di tensione brevi ed improvvisi (chiamati "glitch"), generalmente di tipo periodico, in corrispondenza di commutazioni di segnali digitali propri delle strutture a capacità commutate.

Come mostrato nelle figure 2a e 2b, la presenza di numerosi disturbi impulsivi 5 (ad esempio i glitch) in rapida successione tra loro nel segnale di ingresso analogico Vin può causare rispettive commutazioni di disturbo 6 spurie e indesiderate, anch'esse in rapida successione tra loro, del segnale di comparazione Vcomp del comparatore 1.

Tali commutazioni di disturbo 6 possono causare un funzionamento non corretto di un sistema in cui il comparatore 1 è implementato. Ad esempio, se il segnale di tensione di uscita del comparatore 1 viene utilizzata come ingresso di un circuito PLL ("phase locking loop") ad esempio di un circuito di feedback che opera in modo sincrono, tali commutazioni di disturbo potrebbero inficiare il funzionamento corretto del circuito PLL e di conseguenza dell'intero sistema.

Scopo della presente invenzione è fornire un dispositivo e un metodo di protezione da disturbi per un segnale digitale che superi gli inconvenienti dell'arte nota.

Secondo la presente invenzione vengono realizzati un dispositivo e un metodo di protezione da disturbi per un segnale digitale come definito nelle rivendicazioni 1 e 9.

Per una migliore comprensione dell'invenzione, ne viene ora descritta una forma di realizzazione preferita, a puro titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

- la figura 1 mostra un comparatore di tipo noto;

- le figure 2a e 2b mostrano rispettivamente un segnale differenziale in ingresso al e in uscita dal comparatore di figura 1;

- la figura 3 mostra un dispositivo comparatore secondo la presente invenzione;

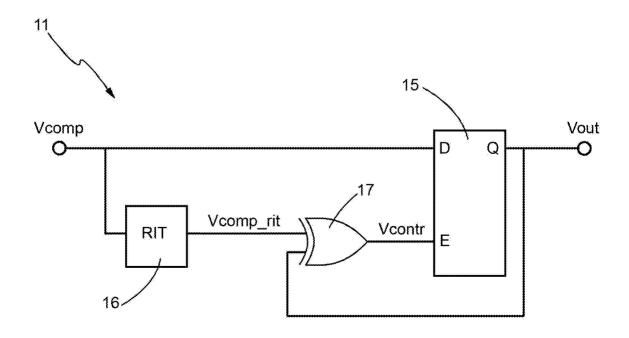

- la figura 4 mostra un circuito di protezione da segnali di disturbo del dispositivo comparatore di figura 3:

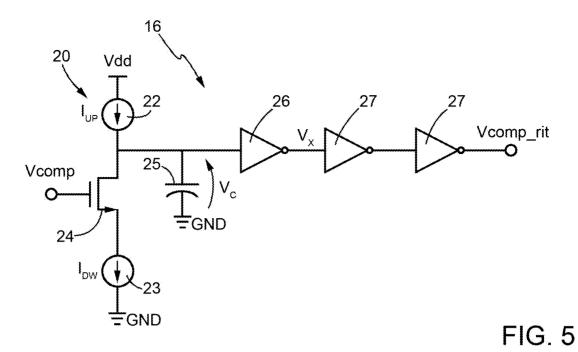

- la figura 5 mostra un circuito di ritardo di segnali interni al circuito di protezione di figura 4;

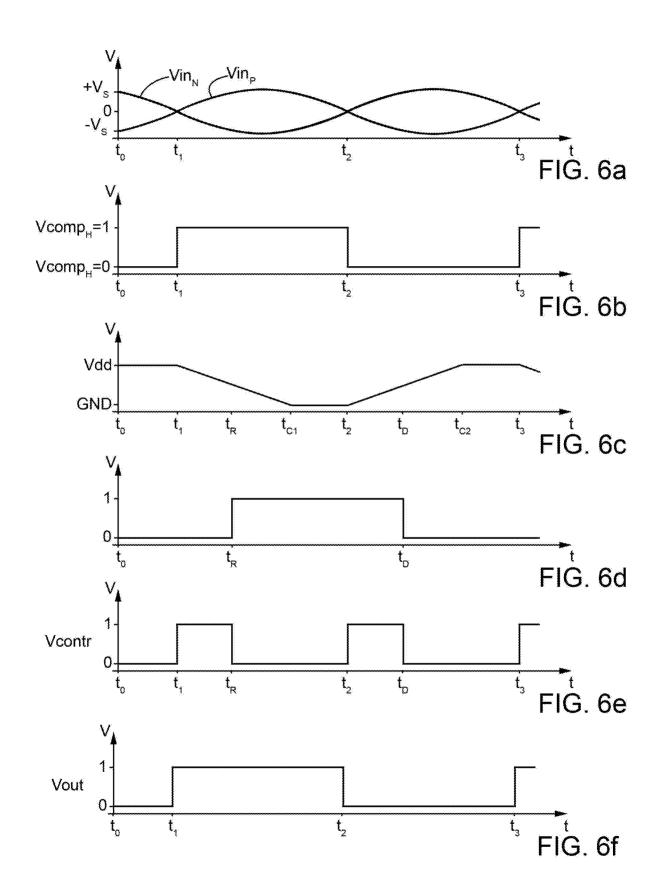

- le figure 6a-6f mostrano forme d'onda di segnali in ingresso al, interni al e generati dal dispositivo comparatore di figura 3 in assenza di segnali di disturbo;

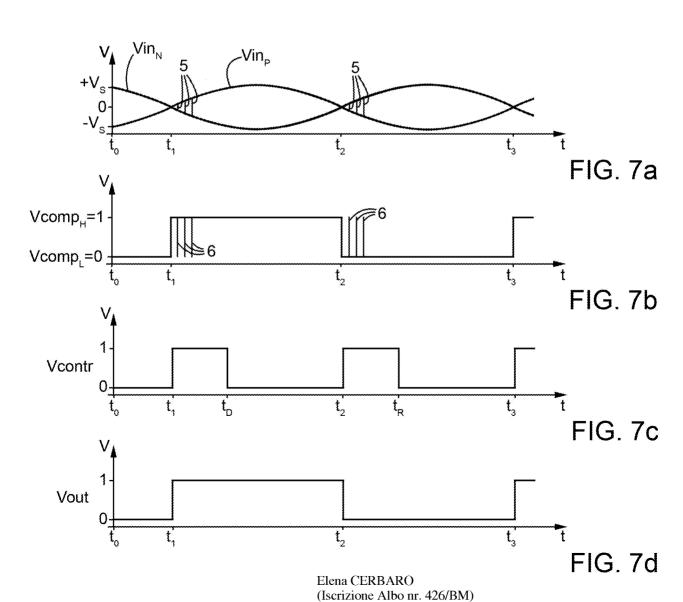

- le figure 7a-7d mostrano forme d'onda di segnali in ingresso al, interni al e generati dal dispositivo comparatore di figura 3 in presenza di segnali di disturbo;

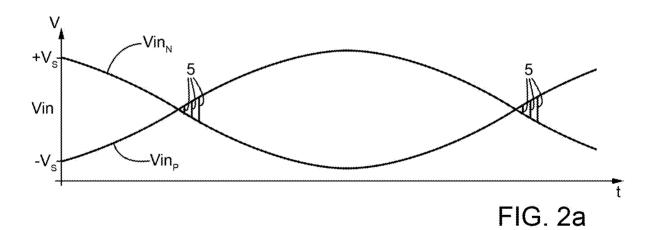

- la figura 8 mostra un sistema microelettromeccanico in cui il dispositivo comparatore di figura 3 può essere implementato.

La figura 3 mostra un dispositivo comparatore 10 comprendente un comparatore 1, ad esempio del tipo descritto con riferimento alla figura 1, ed un circuito di protezione 11, configurato per ricevere in ingresso un segnale digitale, eventualmente con segnali di disturbo ad esso sovrapposti, (come ad esempio i disturbi impulsivi 5 mostrati in figura 2b) e generare un segnale di uscita utile Vout simile al segnale in ingresso ma privo di commutazioni di disturbo 6 in rapida successione tra loro. In generale, il segnale di uscita utile Vout generato dal circuito di protezione 11 possiede lo stesso periodo e lo stesso duty-cycle del segnale di comparazione Vcomp, ingresso al circuito di protezione 11. Casi particolari, in cui il duty-cycle e/o il periodo del segnale di uscita utile Vout potrebbero variare rispetto a quelli del segnale di comparazione Vcomp saranno meglio illustrati nel seguito.

Più in dettaglio, il circuito di protezione 11 riceve in ingresso il segnale di comparazione Vcomp generato dal comparatore 1 che, come detto descritto con riferimento alle figure 2a, 2b, può essere soggetto a commutazioni di disturbo 6, e genera in uscita un segnale di uscita utile

Vout privo di commutazioni di disturbo 6 in rapida successione tra loro. Il circuito di protezione infatti, opera una mascheratura del segnale di comparazione Vcomp generato dal comparatore 1 al fine di evitare che commutazioni di disturbo 6 presenti nel di segnale comparazione Vcomp causino rispettive commutazioni di disturbo nel segnale di uscita utile Vout. La mascheratura è attivata quando viene rilevata una prima commutazione del segnale di comparazione Vcomp ed ha una durata di mascheratura Tmask.

funzionamento normale, cioè in assenza di il circuito di protezione 11 sostanzialmente trasparente ed il segnale di comparazione Vcomp è riprodotto in uscita, realizzando il segnale di uscita utile Vout. Un primo fronte di commutazione del di comparazione Vcomp segnale causa una rispettiva commutazione del segnale di uscita utile Vout. Quindi, in seguito a tale primo fronte di commutazione, con un ritardo minimo, intrinseco ai componenti elettronici utilizzati (generalmente di pochi nanosecondi), viene attivata mascheratura. In questo caso, il circuito di protezione 11 disaccoppia il proprio ingresso dalla propria uscita, e mantiene, per un tempo pari alla durata di mascheratura Tmask, il segnale di uscita utile Vout all'ultimo valore acquisito dal segnale di comparazione Vcomp in seguito al rilevamento del fronte di commutazione, indipendentemente da eventuali ulteriori fronti di commutazione dal segnale di comparazione Vcomp. In questo modo, durante l'intera durata di mascheratura Tmask, eventuali commutazioni di disturbo 6 del segnale di comparazione Vcomp non generano rispettive commutazioni del segnale di uscita utile Vout. Al termine della durata di mascheramento Tmask la fase di mascheratura termina, il segnale di uscita utile Vout sull'uscita del circuito di protezione 11 riproduce nuovamente il segnale di comparazione Vcomp e il circuito di protezione 11 rimane in attesa di un successivo fronte di commutazione del segnale di comparazione Vcomp. Tale successivo fronte di commutazione, analogamente a quanto descritto relativamente al primo fronte di commutazione, comanda una rispettiva commutazione del segnale di uscita utile Vout e quindi, con un ritardo dato dai componenti elettronici utilizzati, viene nuovamente attivata mascheratura. Il circuito di protezione 11 disaccoppia nuovamente il proprio ingresso dalla propria uscita, e mantiene il segnale di uscita utile Vout all'ultimo valore acquisito per l'intera durata di mascheratura Tmask.

La durata di Tmask è condizionata dalla durata del periodo del segnale in ingresso al circuito di protezione 11 (il segnale di comparazione Vcomp nella forma di realizzazione descritta). Ad esempio, si può dimensionare

la durata di mascheratura Tmask secondo la seguente formula (3):

$$Tmask < T_{SEM}, (3)$$

dove  $T_{\text{SEM}}$  è il semiperiodo più breve del periodo del segnale di ingresso analogico Vin (uguale, a meno di commutazioni di disturbo 6, al semiperiodo più breve del periodo del segnale di comparazione Vcomp).

Supponendo che il segnale di comparazione Vcomp abbia un duty-cycle del 50% (semiperiodi di uquale durata), dimensionando la durata di mascheratura Tmask inferiore a metà del periodo del segnale di Vin, si riesce ad ottenere una protezione da eventuali disturbi garantendo comunque la rilevazione del fronte di commutazione (salita/discesa) del segnale di comparazione Vcomp (supponendo assenza disturbi nell'intervallo compreso tra la fine della durata di mascheratura Tmask ed il fronte di commutazione del segnale di comparazione Vcomp).

Nel caso in cui il duty-cycle del segnale di comparazione Vcomp sia diverso dal 50%, la rilevazione del fronte di commutazione è garantito dimensionando la durata di mascheratura Tmask in modo tale che sia inferiore al semiperiodo del segnale di comparazione Vcomp avente durata minore.

La figura 4 mostra una possibile implementazione del

circuito di protezione 11. Secondo questa forma realizzazione, il circuito di protezione 11 comprende un di memoria, ad esempio elemento un flip-flop configurato per accettare su un ingresso D di dati di comparazione Vcomp, su ingresso E segnale un di abilitazione ("enable") un segnale di abilitazione generare su un'uscita Q il segnale di uscita utile Vout; un elemento di ritardo 16, configurato per accettare ingresso il segnale di comparazione Vcomp e per generare in uscita un segnale di ingresso digitale ritardato Vcomp rit, in particolare ritardato di un tempo pari alla durata di mascheratura Tmask desiderata; e una porta logica 17, più precisamente un XOR, configurata per accettare su un primo ingresso il segnale di ingresso digitale ritardato Vcomp rit, su un secondo ingresso il segnale di uscita utile Vout generato dal flip-flop 15, e per generare in uscita un segnale di controllo mascheratura Vcontr, di tipo digitale, fornito sull'ingresso di abilitazione E del flipflop 15.

In questo modo, l'uscita Vcomp\_rit dell'elemento di ritardo 16 e l'uscita Vout del flip-flop 15 controllano, attraverso la porta logica 17 XOR, il funzionamento del flip-flop 15 stesso. Infatti, quando il segnale di controllo mascheratura Vcontr è basso (zero logico), si ha che il segnale di uscita utile Vout corrisponde al segnale

di comparazione Vcomp, a meno di un ritardo introdotto dal flip-flop 15, e quindi la mascheratura è disattivata; al contrario, quando il segnale di controllo mascheratura Vcontr è alto (uno logico), la mascheratura è attiva e il flip-flop 15 mantiene il segnale di uscita utile Vout al valore definito dallo stato precedentemente acquisito.

La figura 5 mostra uno schema circuitale dell'elemento di ritardo 16, secondo una possibile forma di realizzazione.

L'elemento di ritardo 16 comprende una pompa di carica 20, di tipo noto, collegata all'ingresso dell'elemento di ritardo e configurata per essere comandata dal segnale di comparazione Vcomp.

pompa di carica 20 è mostrata secondo rappresentazione schematica, е comprende un generatore di corrente 22, collegato ad una tensione di alimentazione Vdd (di valore opportuno, ad esempio compresa tra 2 V e 5 V) e configurato per generare una corrente Iup; un secondo generatore di corrente 23, collegato ad un terminale di terra GND (ad esempio posto a 0 V) configurato per generare una corrente Idw, ad esempio pari a 2. Iup; ed un interruttore 24, ad esempio un transistore MOSFET a canale N, comandato in conduzione o interdizione mediante il segnale di comparazione Vcomp, avente un primo terminale di conduzione collegato al primo generatore di corrente 22 ed un secondo terminale di conduzione collegato al secondo generatore di corrente 23.

Il primo terminale di conduzione dell'interruttore elettronico 24 è inoltre collegato ad un primo morsetto di un condensatore 25, a sua volta collegato tramite un secondo morsetto al terminale di terra GND. Inoltre, il primo terminale di conduzione dell'interruttore elettronico 24 è collegato ad un invertitore 26. Ulteriori invertitori 27, ad esempio dello stesso tipo dell'invertitore 26, possono opzionalmente essere collegati in serie all'invertitore 26 per ottenere in uscita dal blocco di ritardo un segnale con fronti di salita e di discesa più ripidi. L'uscita della serie degli invertitori 26 e 27 forma il segnale di ingresso digitale ritardato Vcomp rit.

In uso, quando la tensione di comparazione Vcomp commuta verso  $Vcomp_L$ , l'interruttore elettronico 24 è comandato in interdizione e il condensatore 25 è caricato dalla corrente Iup, fino a che la tensione sul condensatore 25 raggiunge un valore di tensione  $Vc\approx Vdd$ . Viceversa, quando la tensione di comparazione Vcomp commuta verso  $Vcomp_H$ , l'interruttore elettronico 24 è comandato in conduzione e il condensatore 25 si scarica con una corrente data da Idw-Iup, fino a che la tensione sul condensatore 25 raggiunge un valore di tensione  $Vc\approx GND$ .

La mascheratura ha inizio quando il condensatore 25

comincia a caricarsi/scaricarsi, e perdura fino a quando la tensione Vc aumentando/diminuendo attraversa la soglia di inversione dell'invertitore 26 (e degli ulteriori invertitori 27 se presenti). La mascheratura pertanto si attiva sia sul fronte di salita sia sul fronte di discesa della tensione di comparazione Vcomp. Secondo la forma di realizzazione mostrata, la durata di mascheratura Tmask è definita dal valore di capacità C del condensatore 25, dalla corrente Iup e dal valore della tensione di soglia di inversione Vth dell'invertitore 26, secondo la seguente formula (4):

$$Tmask = \frac{C}{Iup} \cdot Vth . \tag{4}$$

La durata di mascheratura Tmask è dunque intrinsecamente definita dal tempo di carica/scarica del condensatore 25 fino al raggiungimento della tensione di soglia di inversione Vth dell'inverter 26 (e degli ulteriori invertitori 27 se presenti).

Le figure 6a-6f e 7a-7d mostrano un esempio di variazione temporale dei segnali coinvolti durante la mascheratura. La mascheratura interviene sempre, sia in presenza di glitch o altri disturbi sia in assenza di essi. Le figure 6a-6f mostrano un caso in cui la mascheratura interviene in assenza di glitch e disturbi in genere. Un esempio di mascheratura in presenza di glitch e disturbi è descritto con riferimento alle figure 7a-7d.

Con riferimento alle figure 6a-6f e 7a-7d, i ritardi intrinseci del flip-flop 15 e della porta logica 17 non vengono considerati per semplicità di descrizione.

La figura 6a mostra il segnale di ingresso analogico Vin secondo una rappresentazione differenziale, mostrando i segnali di tensione  $Vin_P$  e  $Vin_N$  presenti su rispettivi ingressi non invertente e invertente del comparatore 1 di figura 3. Nell'esempio di figura 6a, il segnale di ingresso analogico Vin è di tipo sinusoidale, idealmente compreso nell'intervallo di valori di tensione (-Vs, ..., +Vs). Risulta chiaro che tale segnale di ingresso analogico Vin può essere di tipo diverso da quello mostrato, e può essere compreso in un intervallo di valori di tensione qualsiasi, a seconda delle necessità.

La figura 6b mostra il segnale di comparazione Vcomp generato in uscita dal comparatore 1 di figura 3. segnale di comparazione Vcomp è un'onda quadra, con dutycycle del 50% e frequenza uguale alla frequenza del segnale di ingresso analogico Vin. Essendo il segnale comparazione Vcomp un segnale digitale, la figura 6b mostra una rappresentazione ideale in cui il segnale Vcomp un valore di zero logico Vcomp<sub>L</sub> e un valore di uno logico Vcomp<sub>H</sub>. Risulta anche in questo caso chiaro che lo zero logico e l'uno logico possono essere implementati mediante opportuni valori di tensione, a seconda delle necessità.

Nel seguito, quando non diversamente specificato, il segnale di ingresso analogico Vin è inteso come segnale di ingresso differenziale  $Vin=Vin_P-Vin_N$  in ingresso al comparatore 1 di figura 3.

Con riferimento congiunto alle figure 6a e 6b, nell'intervallo temporale t0-t1, il segnale di ingresso analogico Vin è negativo. Pertanto, con riferimento alla formula (2), il segnale di comparazione Vcomp ha valore logico basso, pari a Vcomp<sub>L</sub>=0. Con riferimento alla figura 5, l'interruttore 24 è comandato in interdizione e il condensatore 25, caricandosi, sviluppa una tensione ai suoi capi pari a Vc≈Vdd. La figura 6c mostra l'andamento della tensione Vc sul condensatore 25 (supposto, per semplicità di descrizione, già parzialmente carico all'istante t0).

Nell'istante temporale t1, il segnale di ingresso analogico Vin è pari a zero ( $Vin_P=Vin_N$ ) e, negli istanti temporali successivi a t1, il segnale di ingresso analogico Vin assume valore positivo. Il segnale di comparazione Vcomp commuta da livello logico basso a livello logico alto, assumendo il valore  $Vcomp_H=1$ . In particolare, con riferimento congiunto alla figura 5, il valore in tensione effettivo di VcompH deve essere tale da comandare l'interruttore 24 in conduzione e consentire uno scaricamento progressivo del condensatore 25. Ad esempio è possibile associare all'uno logico il valore di 3.5 V...

Come mostrato in figura 6c, il condensatore 25 inizia a scaricarsi all'istante temporale t1 (la tensione Vc ai sui capi decresce) e risulta completamente scarico all'istante temporale tc1.

Quando, in un istante temporale tR compreso tra gli istanti temporali t1 e tc1, la tensione Vc ai capi del condensatore 25 scaricandosi raggiunge la tensione di soglia di inversione Vth dell'invertitore 26 (e degli inverter 27 se presenti), il circuito di ritardo 16 genera in uscita, figura 6d, il segnale di ingresso digitale ritardato Vcomp rit.

Durante l'intervallo temporale t1-tR i segnali in ingresso alla porta logica 17 non posseggono lo stesso valore logico. Infatti, come mostrato nelle figure 6b, 6d e 6f, il segnale di comparazione Vcomp con valore logico alto causa all'istante temporale t1 una commutazione ad un valore logico alto del segnale di uscita utile Vout, mentre il segnale Vcomp\_rit mantiene un valore logico basso. Gli ingressi della porta logica 17, di tipo XOR, assumono pertanto valore logico diverso. Il segnale di controllo mascheratura Vcontr generato dalla porta logica 17 è dunque un segnale con valore logico alto.

Il segnale di controllo mascheratura Vcontr sull'ingresso di abilitazione  $\underline{E}$  del flip-flop 15 (il segnale invertito non è mostrato in figura), in modo tale

che un segnale di controllo mascheratura Vcontr alto comandi il flip-flop 15 in uno stato di memoria. Il segnale di uscita utile Vout sull'uscita  $\underline{Q}$  mantiene l'ultimo valore logico acquisito indipendentemente dal valore assunto dal segnale di comparazione Vcomp sull'ingresso dati D.

Quindi, quando il segnale di controllo mascheratura Vcontr presente sull'ingresso  $\underline{E}$  di attivazione del flipflop 15 viene mantenuto a livello logico alto, l'uscita  $\underline{Q}$  del latch conserva il proprio stato indipendentemente dal valore assunto dal segnale di comparazione Vcomp sull'ingresso  $\underline{D}$ . Al contrario, quando il segnale di controllo mascheratura Vcontr sull'ingresso  $\underline{E}$  viene commuta a livello logico basso, il segnale sull'uscita  $\underline{Q}$  assume il valore logico del segnale di comparazione Vcomp presente sull'ingresso  $\underline{D}$ .

Durante l'intervallo t1-tR, cioè finché il segnale di controllo mascheratura Vcontr è mantenuto al valore logico alto, il flip-flop 15 genera un segnale di uscita utile Vout avente un valore logico alto, indipendentemente dalle variazioni del segnale di comparazione Vcomp.

Quando, all'istante temporale tR, il segnale di ingresso digitale ritardato Vcomp\_rit assume valore logico alto, il segnale di controllo mascheratura Vcontr assume valore logico basso. L'uscita del flip-flop 15 commuterà pertanto alla successiva commutazione del segnale di

comparazione Vcomp.

Nell'istante temporale t2, il segnale di ingresso analogico Vin è nuovamente pari a zero ( $Vin_P=Vin_N$ ), mentre negli istanti temporali successivi a t2 assume valore negativo. Il segnale di comparazione Vcomp commuta all'istante temporale t2 da livello logico alto a livello logico basso, assumendo il valore Vcomp<sub>L</sub> e causando una rispettiva commutazione del segnale di uscita utile Vout.

Con riferimento alla figura 5, il valore Vcomp<sub>L</sub> deve essere tale da comandare l'interruttore 24 in interdizione e consentire il caricamento del condensatore 25 (ad esempio Vcomp<sub>L</sub> può essere pari a 0 V). Come mostrato in figura 6c, il condensatore 25 inizia a caricarsi all'istante temporale t2 (la tensione Vc ai sui capi cresce) e risulta completamente carico all'istante temporale tc2.

Quando la tensione Vc ai capi del condensatore 25 caricandosi raggiunge la tensione di soglia di inversione Vth dell'invertitore 26 (e degli invertitori 27 se presenti), in un istante temporale tD compreso tra gli istanti temporali t2 e tc2, il segnale di ingresso digitale ritardato Vcomp\_rit generato dal circuito di ritardo 16 assume valore logico basso.

Nell'intervallo temporale compreso tra t2 e tD il segnale di controllo mascheratura Vcontr generato dalla porta logica 17, di tipo XOR, è nuovamente un segnale con

valore logico alto, in quanto, in tale intervallo temporale, il segnale di uscita utile Vout ha valore logico basso, mentre il segnale Vcomp rit ha valore logico alto.

Quindi, durante l'intervallo t2-tD, il flip-flop 15 genera in uscita un valore logico basso, indipendentemente dalle variazioni del segnale di comparazione Vcomp. Il flip-flop 15 è comandato in uno stato di memoria e mantiene il segnale di uscita utile Vout fisso all'ultimo valore logico assunto (in questo caso un valore logico basso).

All'istante temporale tD la tensione Vc raggiunge la tensione di soglia di inversione Vth dell'invertitore 26 (e degli invertitori 27 se presenti) ed il segnale di ingresso digitale ritardato Vcomp\_rit assume valore logico basso. Di conseguenza, anche il segnale di controllo mascheratura Vcontr assume valore logico basso, terminando la mascheratura. Il segnale di uscita utile Vout generato dal flip-flop 15 può pertanto commutare alla successiva commutazione del segnale di comparazione Vcomp.

La durata di mascheratura Tmask è pertanto definita dal tempo di scaricamento e caricamento del condensatore 25, cioè dagli intervalli temporali t1-tR e t2-tD, rispettivamente.

La figura 6f mostra il segnale di uscita utile Vout, generato dal flip-flop 15 secondo quanto descritto con riferimento alle figure 6a-6e. Il segnale di uscita utile

Vout risulta essere disaccoppiato dal segnale di comparazione Vcomp durante gli intervalli temporali t1-tR e t2-tD, e segue le variazioni del segnale di comparazione Vcomp al di fuori di tali intervalli temporali.

Quindi, all'istante temporale t3 il segnale di ingresso differenziale Vin è nuovamente pari a zero e le fasi descritte con riferimento alle figure 6a-6f si ripetono.

Le figure 7a-7d mostrano un esempio in cui disturbi (ad esempio forti glitch differenziali) presenti sul segnale di tensione in ingresso Vin (figura 7a) causano commutazioni non desiderate del segnale di ingresso digitale (figura 7b) generato dal comparatore 1 di figura 3.

Il circuito di protezione 11 opera come già descritto con riferimento alle figure 6a-6f.

Come si può notare dalla figura 7c, che mostra il segnale di controllo mascheratura Vcontr, la durata di mascheratura Tmask è superiore alla durata di disturbi che si verificano in seguito al passaggio attraverso lo zero del segnale di ingresso analogico Vin. In questo modo, il segnale utile di uscita Vout è insensibile alla presenza di tali disturbi e coincide con il segnale utile di uscita Vout che si avrebbe in assenza di disturbi sul segnale di ingresso analogico Vin.

Come espresso dalla formula (4), la durata di mascheratura Tmask dipende dalla corrente Iup, dal valore di capacità C del condensatore 25 e dalla tensione di soglia di inversione Vth. Quest'ultima, in particolare, può variare in funzione del valore di tensione di alimentazione Vdd (ad esempio, nel caso di inverter di tipo CMOS, la tensione di soglia di inversione Vth è pari a Vdd/2). Per ottenere durate di mascheratura Tmask uguali sia al fronte positivo di commutazione del segnale di comparazione Vcomp che a quello negativo, è preferibile garantire che il condensatore 25 si carichi/scarichi completamente.

Un modo per dimensionare i vari parametri che determinano Tmask secondo le formule (3) e (4) può essere il seguente. Si considera il valore di tensione di tensione di soglia Vth massima (definita in fase di progetto, ad esempio, nel caso di inverter CMOS in cui Vth=Vdd/2, considerando il valore di tensione di alimentazione Vdd massimo) e di frequenza del segnale di comparazione Vcomp massima prevista (periodo del segnale di comparazione Vcomp minimo), per i quali infatti il tempo di caricamento (e scaricamento) del condensatore 25 è maggiore. Inoltre si considerano dei valori nominali di corrente Iup e Idw ragionevolmente piccoli, per limitare i consumi. Infine, sulle base delle considerazioni precedenti, si definisce un valore nominale di capacità C del condensatore 25.

Il dispositivo comparatore 10 può essere ad esempio utilizzato in circuiti di pilotaggio di strutture microelettromeccaniche, in cui una massa mobile deve essere eccitata e continuamente mantenuta in oscillazione a una pulsazione propria di risonanza, come ad esempio un giroscopio microintegrato. Ciò non si deve tuttavia considerare limitativo, in quanto l'invenzione può essere sfruttata in tutti i casi in cui risulti vantaggioso mascherare segnali di disturbo sovrapposti ad un segnale digitale generato da un convertitore, da un comparatore o altro dispositivo.

Ad esempio, il dispositivo comparatore 10 può essere utilizzato in un giroscopio microintegrato del descritto nel brevetto US 7,305,880 e descritto brevemente nel seguito con riferimento alla figura 8. Qui, un sistema microintegrato 100, esempio un ad giroscopio microintegrato, comprende una microstruttura realizzata in tecnologia MEMS, un dispositivo di pilotaggio 103 e un dispositivo di lettura 104, alloggiati su un supporto (non mostrato). La microstruttura 102 è provvista di un sistema di attuazione 5 e di un sensore inerziale 6, includenti rispettive masse mobili. Più precisamente, il sistema di attuazione 5 comprende una massa di pilotaggio 107, oscillante attorno a una posizione di riposo secondo un proprio grado di libertà, mentre il sensore inerziale 6 comprende una massa di rilevamento 108, meccanicamente collegata alla massa di pilotaggio 107 mediante molle (qui non mostrate), in modo da essere trascinata in movimento quando la massa di pilotaggio 107 viene eccitata. Inoltre, la massa di rilevamento 108 è relativamente mobile rispetto alla massa di pilotaggio 107 secondo un ulteriore grado di libertà.

Il dispositivo di pilotaggio 103 comprende, ad esempio un amplificatore 109, uno stadio derivatore 110, un circuito amplificatore a guadagno variabile o circuito VGA 111 ("Variable Gain Amplifier"), un controllore 112 e un circuito ad aggancio di fase o circuito PLL 113 ("Phase Locked Loop").

Il circuito PLL 113 ha ingressi collegati alle uscite dello stadio derivatore 110 attraverso il dispositivo comparatore 10, e un'uscita 113a, collegata a un ingresso di temporizzazione 112c del controllore 112. Il dispositivo comparatore 10 riceve in ingresso un segnale di ingresso analogico Vin in uscita dallo stadio derivatore, ad esempio un segnale sinusoidale con frequenza pari a 4.6kHz, e fornisce in uscita al circuito PLL 113 un segnale di uscita Vout, di tipo binario (in particolare un segnale a onda quadra che assume due valori logici, uno alto e uno basso). Il segnale di uscita Vout ha qui la funzione di primo segnale di temporizzazione ("clock") CK. Il primo segnale

di temporizzazione ("clock") CK, insieme con un secondo segnale di temporizzazione CK<sub>90</sub>, sfasato di 90° e prelevato sull'uscita del circuito PLL 113, è fornito al dispositivo di lettura 104, allo scopo di sincronizzare le operazioni di pilotaggio e lettura della microstruttura 102.

Inoltre, il dispositivo di pilotaggio 103 opera sul guadagno e sulla fase complessivi dell'anello di retroazione di pilotaggio 105, in modo da mantenere la massa di pilotaggio 107 costantemente in oscillazione ad una pulsazione di risonanza  $\omega_{\text{R}}$ .

il mantenimento Risulta quindi chiaro come sincronismo per le operazioni di pilotaggio e lettura della microstruttura 102 sia essenziale per il funzionamento del giroscopio microintegrato 100. Come descritto con riferimento alle figure 2a e 2b, segnali di disturbo potrebbero infatti generare una pluralità di indesiderate sul commutazioni primo segnale di temporizzazione CK; in questo caso, il circuito PLL 113 perdere il sincronismo, sganciandosi potrebbe dalla frequenza di oscillazione della massa di pilotaggio 107 che verrebbe quindi eccitata ad una frequenza diversa da quella di risonanza.

Risulta evidente dalla descrizione del circuito di protezione 11 che il segnale di controllo mascheratura Vcontr (e quindi la mascheratura di eventuali commutazioni

del segnale di comparazione Vcomp) viene attivato da un qualsiasi cambiamento di stato logico del segnale di comparazione Vcomp, cioè dal passaggio da un valore logico basso ad uno alto e viceversa indipendentemente dal fatto che tale cambiamento di stato logico sia causato da un evento di disturbo presente sul segnale di ingresso analogico Vin o da una effettiva variazione di stato logico.

In presenza di forti disturbi sul segnale di ingresso analogico Vin, precedenti al passaggio per lo zero del segnale di ingresso analogico Vin, (ad esempio, con riferimento alla figura 7b, precedenti all'istante temporale t1 e/o t2 ma fuori dall'intervallo di mascheratura tR-t1 e/o tD-t2), può accadere che la mascheratura venga attivata da una commutazione di errore generata da un disturbo e non dall'effettiva commutazione del segnale.

Tali disturbi sono generalmente glitch sistematici, tali da causare uno spostamento ("shift") temporale del segnale di comparazione Vcomp. Ciò causa un anticipo sistematico del segnale di uscita utile Vout che viene a trovarsi non più in fase con il segnale di ingresso analogico Vin. Tale spostamento temporale, poiché sistematico, è calibrabile digitalmente per consentire il ripristino della sincronia.

Con particolare riferimento al giroscopio di figura 8, il segnale di uscita utile Vout è fornito in ingresso a un circuito PLL. In questo caso, un eventuale rumore di jitter può essere comunque compensato dal circuito PLL stesso che, sulla base delle proprie specifiche, è in grado di recuperare il sincronismo.

In alternativa, metodi e circuiti di compensazione aggiuntivi possono essere implementati per compensare tale variazione del duty-cycle.

Da un esame delle caratteristiche del dispositivo e del metodo di protezione da disturbi di un segnale digitale realizzati secondo la presente invenzione sono evidenti i vantaggi che essa consente di ottenere.

Ad esempio, la presente invenzione consente di eliminare problemi di sincronismo derivanti da commutazioni multiple in rapida successione derivanti da segnali di disturbo, specialmente nel caso di glitch che si verificano in architetture a capacità commutate.

Inoltre, la mascheratura dei disturbi viene effettuata senza la necessità di segnali digitali generati esternamente al circuito comparatore 10 da un opportuno circuito digitale dedicato al controllo della mascheratura. Risulta infine chiaro che al dispositivo e metodo di protezione da disturbi di un segnale digitale qui descritti ed illustrato possono essere apportate modifiche e varianti

senza per questo uscire dall'ambito protettivo della presente invenzione, come definito nelle rivendicazioni allegate.

Ad esempio il circuito di ritardo 16 e la porta logica 17 possono essere realizzati in forma integrata totalmente digitale, ad esempio implementando un software comprendente un blocco contatore (non mostrato), configurato per ricevere in ingresso il segnale di comparazione Vcomp e fornire in uscita il segnale di controllo mascheratura Vcontr, avente un fronte di salita comandato dal fronte di salita del segnale di comparazione Vcomp ed un fronte di discesa comandato dal blocco contatore stesso.

## RIVENDICAZIONI

1. Metodo di protezione da disturbi di un segnale digitale (Vcomp) generato da un comparatore (1), comprendente le fasi di:

generare un segnale di uscita (Vout) commutante da un primo a un secondo stato logico ad una prima commutazione di stato logico del segnale digitale (Vcomp);

rilevare un cambiamento dal primo al secondo stato logico del segnale di uscita (Vout);

inibire ulteriori commutazioni del segnale di uscita (Vout) per un primo intervallo di tempo dopo detto cambiamento dal primo al secondo stato logico.

- 2. Metodo secondo la rivendicazione 1, in cui la fase di inibire comprende mantenere il segnale di uscita (Vout) al secondo livello logico durante detto primo intervallo di tempo (Tmask).

- 3. Metodo secondo la rivendicazione 1 o 2, comprendente, dopo il primo intervallo di tempo, le fasi di:

commutare il segnale di uscita (Vout) dal secondo al primo stato logico al rilevamento di una seconda commutazione di stato logico del segnale digitale (Vcomp);

rilevare un cambiamento dal secondo al primo stato logico del segnale di uscita (Vout); e

inibire ulteriori commutazioni del segnale di uscita

(Vout) per un secondo intervallo di tempo dopo detto cambiamento dal secondo al primo stato logico.

- 4. Metodo secondo la rivendicazione 3, in cui la fase di inibire ulteriori commutazioni del segnale di uscita (Vout) per un secondo intervallo di tempo comprende mantenere il segnale di uscita (Vout) al primo livello logico durante detto secondo intervallo di tempo (Tmask).

- 5. Metodo secondo la rivendicazione 3 o 4, in cui detto segnale digitale è un segnale periodico avente un semiperiodo, detti primo e secondo intervallo di tempo (Tmask) avendo una durata inferiore a detto semiperiodo del segnale digitale (Vcomp).

- 6. Metodo secondo una qualsiasi delle rivendicazioni 3-5, in cui la fase di rilevare un cambiamento dal primo al secondo stato logico del segnale di uscita comprende:

prelevare detto segnale di uscita (Vout);

generare un segnale di verifica (Vcomp\_rit) ritardato

rispetto a detto segnale digitale;

confrontare detto segnale di uscita (Vout) con il segnale di verifica (Vcomp rit); e

generare un segnale di controllo inibizione (Vcontr) abilitante un ulteriore cambiamento di stato logico di detto segnale di uscita solo dopo il rilevamento di una commutazione di stato logico di detto segnale di verifica.

7. Metodo secondo la rivendicazione 6, in cui detta

fase di generare un segnale di verifica (Vcomp\_rit)

comprende:

inviare detto segnale digitale (Vcomp) ad un ingresso di controllo di un interruttore (24);

comandare rispettivamente la carica e la scarica di un condensatore (25) da parte dell'interruttore (24);

abilitare la generazione del segnale di verifica (Vcomp\_rit) al raggiungimento di un valore di carica del condensatore (25).

- 8. Metodo secondo la rivendicazione 6 o 7, in cui detta fase di confrontare comprende eseguire un'operazione logica di XOR tra il segnale di uscita (Vout) ed il segnale di verifica (Vcomp rit).

- 9. Dispositivo comparatore (10) comprendente un comparatore (1), configurato per generare un segnale digitale (Vcomp), e un circuito di protezione (11), il circuito di protezione (11) comprendendo:

mezzi generatori di segnale (15), configurati per generare un segnale di uscita (Vout) commutante da un primo a un secondo stato logico al rilevamento di commutazioni di stato logico del segnale digitale (Vcomp);

mezzi di rilevamento cambiamento stato (16, 17), configurati per rilevare un cambiamento dal primo al secondo stato logico del segnale di uscita (Vout); e

mezzi di inibizione commutazione (15), configurati per

inibire la commutazione del segnale di uscita (Vout) per un intervallo di tempo (Tmask) dopo detto cambiamento dal primo al secondo stato logico.

- 10. Dispositivo secondo la rivendicazione 9, in cui detti mezzi di inibizione commutazione (15) comprendono mezzi di memoria (15), configurati per mantenere il segnale di uscita (Vout) in detto secondo stato logico durante detto intervallo di tempo (Tmask).

- 11. Dispositivo secondo la rivendicazione 9 o 10, in cui detti mezzi di rilevamento commutazione (16, 17) comprendono:

mezzi di ritardo (16), configurati per ricevere il segnale digitale (Vcomp) e generare un segnale di verifica ritardato rispetto al segnale digitale; e

mezzi di confronto (17), configurati per confrontare detto segnale di uscita (Vout) con il segnale di verifica (Vcomp\_rit) e generare un segnale di controllo inibizione (Vcontr) abilitante un ulteriore cambiamento di stato logico di detto segnale di uscita solo dopo il rilevamento di una commutazione di stato logico di detto segnale di verifica.

12. Dispositivo secondo la rivendicazione 11, in cui i mezzi di memoria comprendono un flip-flop (15) di tipo D, avente un ingresso di abilitazione (E) configurato per ricevere il segnale di controllo (Vcontr), un ingresso dati

(D) configurato per ricevere il segnale digitale (Vcomp) ed un'uscita (Q) configurata per generare il segnale di uscita (Vout); e i mezzi di confronto (17) comprendono una porta logica XOR, avente un primo ingresso collegato ad una uscita dei mezzi di ritardo (16), un secondo ingresso collegato all'uscita del flip-flop (15) ed un'uscita collegata all'ingresso di abilitazione (E) del flip-flop (15).

13. Dispositivo secondo la rivendicazione 11 o 12, in cui i mezzi di ritardo (16) comprendono:

una pompa di carica (20), includente un interruttore (24) avente un terminale di controllo collegato ad un'uscita del comparatore, un primo terminale di conduzione collegato ad una prima linea a potenziale di riferimento (Vdd) ed un secondo terminale di conduzione collegato ad una seconda linea a potenziale di riferimento (GND);

un condensatore (25) avente un primo morsetto collegato al primo terminale di conduzione dell'interruttore ed un secondo morsetto collegato alla seconda linea a potenziale di riferimento (GND); e

almeno un elemento a soglia (26), avente un ingresso collegato al primo morsetto del condensatore (25) ed un'uscita collegata ai mezzi di confronto (17).

14. Sistema microelettromeccanico risonante comprendente una microstruttura (102), avente una massa

(107) liberamente oscillabile; e un dispositivo di pilotaggio (103), accoppiato a detta massa (107) per mantenere detta massa (107) in oscillazione, in cui detto dispositivo di pilotaggio (103) comprende:

un amplificatore differenziale di lettura (109);

uno stadio di attuazione e controllo (111, 112, 113), includente un circuito PLL (113) e configurato per pilotare detta massa (107); e

un dispositivo comparatore (10) secondo una qualsiasi delle rivendicazioni 9-13, collegato fra detto amplificatore differenziale di lettura (109) e il circuito PLL (113) di detto stadio di attuazione e controllo (111, 112, 113).

15. Sistema microelettromeccanico secondo la rivendicazione 14 costituente un giroscopio.

p.i.: STMICROELECTRONICS S.R.L.

Elena CERBARO

FIG. 3

FIG. 4

Elena CERBARO (Iscrizione Albo nr. 426/BM)

FIG. 8