(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5869135号

(P5869135)

(45) 発行日 平成28年2月24日(2016.2.24)

(24) 登録日 平成28年1月15日(2016.1.15)

(51) Int.Cl.

F 1

|                   |                  |      |       |      |

|-------------------|------------------|------|-------|------|

| <b>G06F 13/36</b> | <b>(2006.01)</b> | G06F | 13/36 | 310E |

| <b>G06F 13/38</b> | <b>(2006.01)</b> | G06F | 13/38 | 340A |

| <b>G06F 13/28</b> | <b>(2006.01)</b> | G06F | 13/38 | 350  |

|                   |                  | G06F | 13/28 | 310Z |

請求項の数 20 (全 16 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-533274 (P2014-533274)  |

| (86) (22) 出願日 | 平成23年9月30日 (2011.9.30)        |

| (65) 公表番号     | 特表2014-531685 (P2014-531685A) |

| (43) 公表日      | 平成26年11月27日 (2014.11.27)      |

| (86) 國際出願番号   | PCT/US2011/054394             |

| (87) 國際公開番号   | W02013/048477                 |

| (87) 國際公開日    | 平成25年4月4日 (2013.4.4)          |

| 審査請求日         | 平成26年5月13日 (2014.5.13)        |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 593096712<br>インテル コーポレイション<br>アメリカ合衆国 95054 カリフォルニア州 サンタクララ ミッション カレッジ ブールバード 2200 |

| (74) 代理人  | 100107766<br>弁理士 伊東 忠重                                                             |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                                                             |

| (74) 代理人  | 100091214<br>弁理士 大貫 進介                                                             |

| (72) 発明者  | マーゴ、ウィリアム、アール、<br>アメリカ合衆国 51822-9228<br>イリノイ州 シャンペーン コブルフィールド ロード 1603             |

最終頁に続く

(54) 【発明の名称】コプロセッサのためのダイレクトI/Oアクセス

## (57) 【特許請求の範囲】

## 【請求項 1】

リモートダイレクトメモリーアクセス (R D M A ) デバイスと；

中央処理装置 (C P U ) とメモリーを有する周辺機器と；

前記 R D M A デバイスと前記周辺機器に対して通信可能に接続されたホストコントローラーと、を含み、

前記ホストコントローラーは、

前記ホストコントローラーの中に含まれ、前記周辺機器のメモリー又は前記 R D M A デバイスのメモリーのうちの一つに対してマップされた仮想アドレスにおけるアクセリクエストメッセージに係る通知を受け取り；

前記 R D M A デバイスの前記メモリーに対してマップされた仮想アドレスにおける前記アクセリクエストメッセージの受け取りに応じて、前記周辺機器からの前記 R D M A デバイスのメモリーに対する前記アクセリクエストメッセージに基づき、R D M A アクセスリクエストを前記 R D M A デバイスに対して伝送し、前記 R D M A アクセスリクエストメッセージは仮想アドレス R D M A パラメーターを含み；かつ

前記周辺機器の前記メモリーに対してマップされた仮想アドレスにおける前記アクセリクエストメッセージの受け取りに応じて、アクセスリクエストメッセージを前記周辺機器の前記メモリーに対して伝送する、

ように構成されており、

前記 R D M A デバイスは、リクエストの完了後、前記周辺機器のメモリーにマップされ

た仮想アドレスに対して完了メッセージを送付し、前記仮想アドレスは、前記完了メッセージを保管するための完了キューを表している、

ことを特徴とするシステム。

**【請求項 2】**

前記 R D M A アクセスリクエストは、R D M A 読み出しリクエストを有し、

前記ホストコントローラーは、さらに；

前記 R D M A デバイスからの前記周辺機器によりリクエストされたデータを受け取り、かつ、

前記周辺機器の前記メモリーに対して、前記データを含んでいるデータメッセージを

伝送する、

請求項 1 に記載のシステム。

**【請求項 3】**

前記 R D M A アクセスリクエストは、R D M A 書き込みリクエストを有し、

前記ホストコントローラーは、さらに；

前記周辺機器のメモリーからの前記 R D M A デバイスによりリクエストされたデータを受け取り、かつ、

前記 R D M A デバイスに対して、前記データを含んでいるデータメッセージを伝送する、

請求項 1 に記載のシステム。

**【請求項 4】**

前記周辺機器の前記 C P U は、複数のプロセッサコアのうちの一つ、または、前記周辺機器の中に含まれているマルチコアプロセッサを有する、

請求項 1 に記載のシステム。

**【請求項 5】**

前記周辺機器と前記 R D M A デバイスは、周辺コンポーネント相互接続エクスプレス ( P C I e ) リンクを介して、前記ホストコントローラーに対して通信可能に接続されている、

請求項 1 に記載のシステム。

**【請求項 6】**

前記 R D M A デバイスと前記ホストコントローラーは、P C I e ルートポートを介して通信可能に接続されている、

請求項 5 に記載のシステム。

**【請求項 7】**

前記周辺機器は、グラフィックサブシステムを有し、かつ

前記 C P U は、グラフィックプロセッサユニット ( G P U ) を有する、

請求項 1 に記載のシステム。

**【請求項 8】**

前記アクセスリクエストメッセージは、インフィニバンド仕様に準じている、

請求項 1 に記載のシステム。

**【請求項 9】**

前記アクセスリクエストメッセージは、R D M A コンソーシアム仕様に準じている、

請求項 1 に記載のシステム。

**【請求項 10】**

リモートダイレクトメモリーアクセス ( R D M A ) デバイスのメモリーと周辺機器のメモリーのうちの一つに対してマップされた仮想アドレスにおけるアクセスリクエストメッセージに係る通知を受け取るステップであり、前記周辺機器は、さらに、中央処理装置 ( C P U ) とメモリーを有するステップと；

前記 R D M A デバイスの前記メモリーに対してマップされた仮想アドレスにおける前記アクセスリクエストメッセージの受け取りに応じて：

R D M A パラメーターとして前記 R D M A デバイスの前記メモリーに対してマップさ

10

20

30

40

50

れた前記仮想アドレスを利用するステップと；

前記周辺機器からの前記R D M Aデバイスのメモリーに対する前記アクセシリクエストメッセージに基づき、R D M Aアクセシリクエストを前記R D M Aデバイスに対して伝送するステップであり、前記R D M Aアクセシリクエストメッセージは仮想アドレスR D M Aパラメーターを含んでいるステップと；

前記周辺機器の前記メモリーに対してマップされた仮想アドレスにおける前記アクセシリクエストメッセージの受け取りに応じて、

アクセシリクエストメッセージを前記周辺機器の前記メモリーに対して伝送するステップと、を含み、

前記R D M Aデバイスは、リクエストの完了後、前記周辺機器のメモリーにマップされた仮想アドレスに対して完了メッセージを送付し、前記仮想アドレスは、前記完了メッセージを保管するための完了キューを表している、

ことを特徴とする方法。

#### 【請求項11】

前記R D M Aアクセシリクエストは、R D M A読み出しリクエストを有し、

前記方法は、さらに；

前記R D M Aデバイスからの前記周辺機器によりリクエストされたデータを受け取るステップと、

前記周辺機器の前記メモリーに対して、前記データを含んでいるデータメッセージを伝送するステップと、を含む、

請求項10に記載の方法。

#### 【請求項12】

前記R D M Aアクセシリクエストは、R D M A書き込みリクエストを有し、

前記方法は、さらに；

前記周辺機器のメモリーからの前記R D M Aデバイスによりリクエストされたデータを受け取るステップと、

前記R D M Aデバイスに対して、前記データを含んでいるデータメッセージを伝送するステップと、を含む、

請求項10に記載の方法。

#### 【請求項13】

前記周辺機器の前記C P Uは、複数のプロセッサコアのうちの一つ、または、前記周辺機器の中に含まれているマルチコアプロセッサを有する、

請求項10に記載の方法。

#### 【請求項14】

前記周辺機器と前記R D M Aデバイスは、周辺コンポーネント相互接続エクスプレス(P C I e)リンクを介して、ホストコントローラーに対して通信可能に接続されている、

請求項10に記載の方法。

#### 【請求項15】

前記R D M Aデバイスと前記ホストコントローラーは、P C I eルートポートを介して通信可能に接続されている、

請求項14に記載の方法。

#### 【請求項16】

前記周辺機器は、グラフィックサブシステムを有し、かつ

前記C P Uは、グラフィックプロセッサユニット(G P U)を有する、

請求項10に記載の方法。

#### 【請求項17】

リモートダイレクトメモリーアクセス(R D M A)デバイスに対して通信可能に接続された第1の相互接続リンクと；

中央処理装置(C P U)とメモリーを有する周辺機器に対して通信可能に接続された第2の相互接続リンクと；

10

20

30

40

50

ホストコントローラーと、を含み、

前記ホストコントローラーは、

前記ホストコントローラーの中に含まれ、前記周辺機器のメモリー又は前記R D M Aデバイスのメモリーのうちの一つに対してマップされた仮想アドレスにおけるアクセスリクエストメッセージに係る通知を受け取り；

前記R D M Aデバイスの前記メモリーに対してマップされた仮想アドレスにおける前記アクセスリクエストメッセージの受け取りに応じて、前記周辺機器からの前記R D M Aデバイスのメモリーに対する前記アクセスリクエストメッセージに基づき、R D M Aアクセスリクエストを前記R D M Aデバイスに対して伝送し、前記R D M Aアクセスリクエストメッセージは仮想アドレスR D M Aパラメーターを含み；かつ

前記周辺機器の前記メモリーに対してマップされた仮想アドレスにおける前記アクセスリクエストメッセージの受け取りに応じて、アクセスリクエストメッセージを前記周辺機器の前記メモリーに対して伝送し、

前記R D M Aデバイスは、リクエストの完了後、前記周辺機器のメモリーにマップされた仮想アドレスに対して完了メッセージを送付し、前記仮想アドレスは、前記完了メッセージを保管するための完了キューを表している、

ことを特徴とする装置。

#### 【請求項18】

前記R D M Aアクセスリクエストは、R D M A読み出しリクエストを有し、

前記ホストコントローラーは、さらに；

前記R D M Aデバイスからの前記周辺機器によりリクエストされたデータを受け取り、かつ、

前記周辺機器の前記メモリーに対して、前記データを含んでいるデータメッセージを伝送する、

請求項17に記載の装置。

#### 【請求項19】

前記R D M Aアクセスリクエストは、R D M A書き込みリクエストを有し、

前記ホストコントローラーは、さらに；

前記周辺機器のメモリーからの前記R D M Aデバイスによりリクエストされたデータを受け取り、かつ、

前記R D M Aデバイスに対して、前記データを含んでいるデータメッセージを伝送する、

請求項17に記載の装置。

#### 【請求項20】

前記第1および第2の相互接続リンクのそれぞれは、周辺コンポーネント相互接続エクスプレス(P C I e)リンクを有しており、かつ、

前記装置は、さらに、前記R D M Aデバイスに対して通信可能に接続されたルートポートを含んでいる、

請求項17に記載の装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明の実施例は、一般的に、コンピューターデバイスに適用される。より特定的には、周辺機器のためのメモリーアクセス管理に関する。

#### 【背景技術】

#### 【0002】

コンピューターシステムは、ネットワーク又はバス構成といった相互接続構造を介してお互いに接続されている種々のデバイスを含んでいる。これらのデバイスは、典型的にはローカルメモリーを有しており、コンピューター環境の中で処理速度と適応性を提供するために複数のデバイスが並行して動作される。

10

20

30

40

50

**【0003】**

リモートダイレクトメモリーアクセス( R D M A )は、ネットワークインターフェイスカード( N I C )の機能であり、コンピューターデバイスが、別のコンピューターデバイスのメモリーの情報にアクセスできるようにする。特に、R D M A技術を介して、コンピューターデバイスは、ホストオペレーティングシステム( O S )を巻き込むことなく、別のコンピューターデバイスのメモリーから情報を読み出すことができる。別のコンピューターデバイスのメモリーに情報を書き込むことも同様である。

**【0004】**

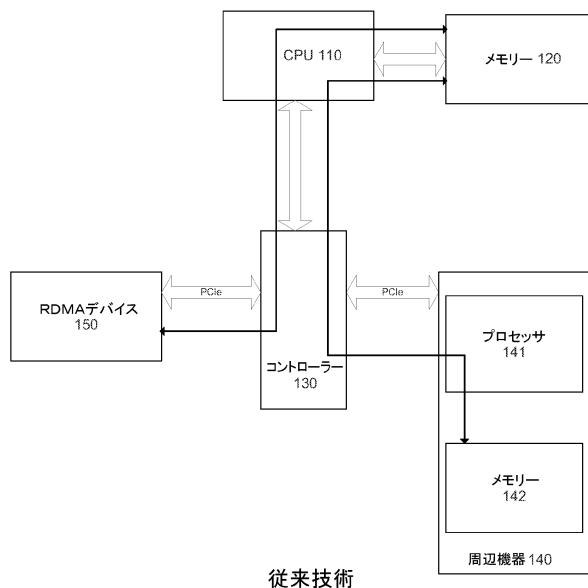

図1は、C P Uとメモリーの複合物を有している周辺機器を含んだ従来技術に係るシステムを図示している。システム100は、システムC P U110、システムメモリー120、周辺機器コントローラー130、周辺機器140、および、R D M Aデバイス150を含んでいる。周辺機器140は、プロセッサ141及びメモリー142を含んでいる。周辺機器140及びR D M Aデバイス150は、「ピア( " p e e r " )」デバイスとして参照されてよい。10

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

周辺機器140は、R D M A150の中に保管されているデータにアクセスする必要があり、その逆もまた同様である。現在、インフィニバンド( I n f i n i B a n d )仕様又はR D M Aコンソーシアム仕様、等といった多くの相互接続構造規格の実施は、ピアデバイスが、別のピアデバイスのアドレス空間において保管されているデータに直接的にアクセスすることをできなくしている。20

**【0006】**

現在のソリューションは、ピアデバイスが、リクエストされたデータを共通に利用可能なメモリーに対して書き込むことを要求する。この説明図においては、システムメモリー120であり、相互接続性構造に接続されたあらゆる周辺機器によってアクセス可能である。しかしながら、そうしたデータ転送のために共通のシステムメモリーを使用することは時間の浪費であり、処理のオーバーヘッドを増加させるものである。さらに、共通システムのメモリーを使用することは、周辺機器の処理動作を遅くしてしまう。30

**【課題を解決するための手段】****【0007】**

本発明の実施例は、ホストと、C P U及びメモリーの複合体を含む周辺機器(代替的には、ここにおいてプロセッサアドインカードとして言及されるもの)との間で、リモートダイレクトメモリーアクセス( R D M A )デバイスハードウェアを共有することができるシステム、装置、および、方法を説明する。本発明の実施例は、プロセッサアドインカード( a d d - i n c a r d )とR D M Aデバイスとの間でのピアツ-ピア( p e e r - t o - p e e r )のデータ転送のための周辺コンポーネント相互接続エクスプレス( P C I e )といった相互接続ハードウェアを利用する。ホストシステムは、メモリー及びレジスターをR D M Aデバイスに対して、及び/又は、R D M Aデバイスからマップするためのモジュール又はロジックを含んでよい。これにより、ホストシステムのI / Oオペレーティングシステムと同時に、アドインカードのプロセッサ上のユーザーモードアプリケーションに対して、または、アプリケーションから直接的に実行されるべきI / Oをできるようになっている。40

**【図面の簡単な説明】****【0008】**

以降の記述は、本発明の具体化に係る実施例によって与えられる例解を有する図面の説明を含んでいる。図面は、例示として理解されるべきであり、本発明を限定するものとして理解されるべきではない。ここにおいて使用されるように、一つまたはそれ以上の「実施例」は、本発明に係る少なくとも一つの実施に含まれる所定の機能、構成、または、特性を表しているものとして理解されるべきである。このように、ここにおいて表れている50

「一つの実施例において」または「代替的な実施例において」といったフレーズは、本発明に係る種々の具体化及び実施を説明するものであり、必ずしも全てが同一の実施例を参照する必要はない。しかしながら、それらはお互いに排他的であることも要しない。

【図1】図1は、CPU及びメモリーの複合体を有する周辺機器を含む従来技術のシステムを示している。

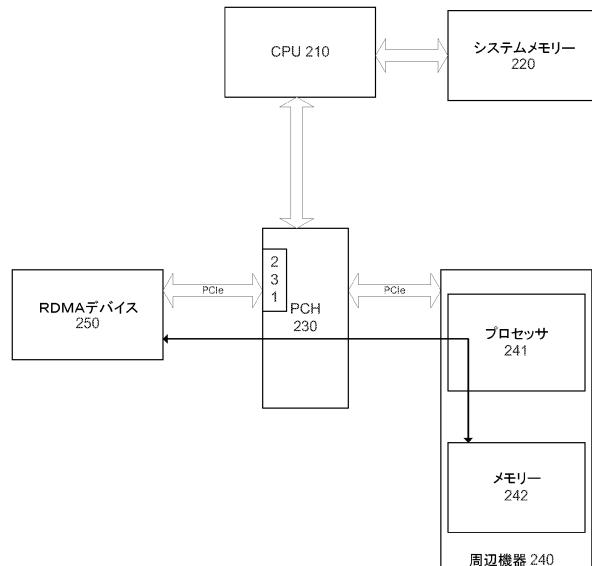

【図2】図2は、本発明の一つの実施例に従ったロックダイヤグラムである。

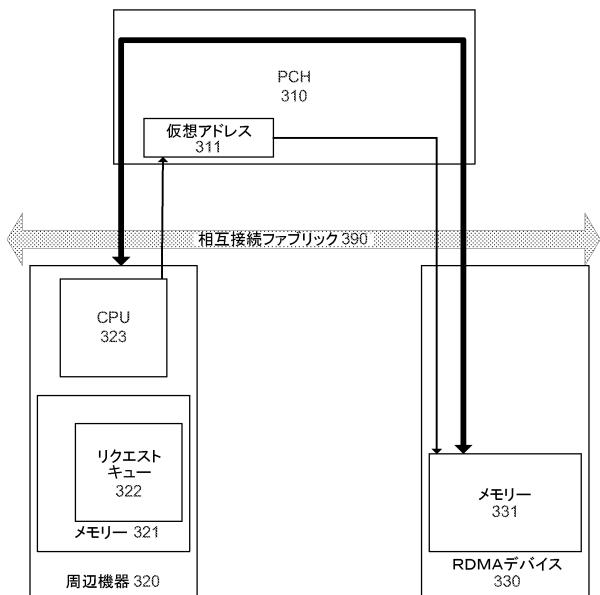

【図3】図3は、本発明の一つの実施例に従ったシステムコンポーネントのロックダイヤグラムである。

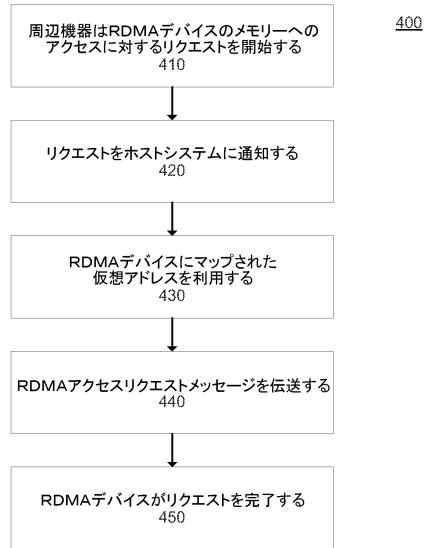

【図4】図4は、本発明の一つの実施例に従ったプロセスのフローチャートである。

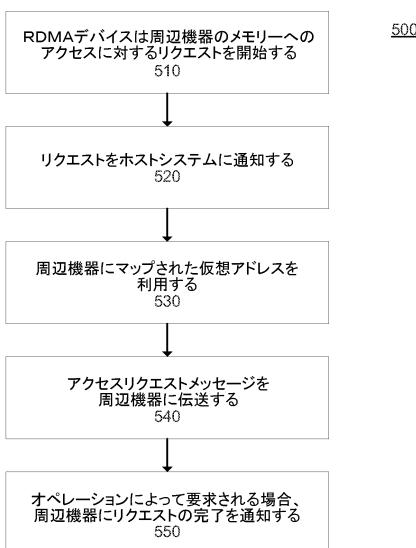

【図5】図5は、本発明の一つの実施例に従ったプロセスのフローチャートである。

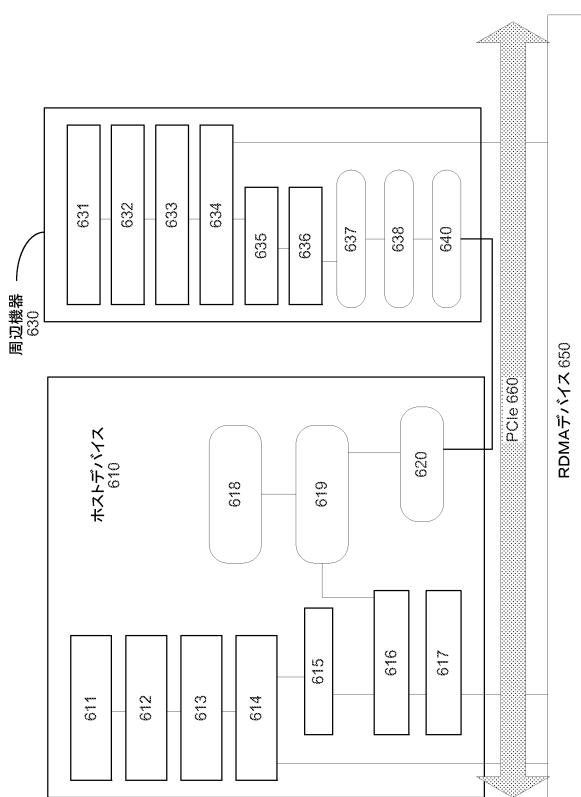

【図6】図6は、本発明の一つの実施例に従ったホストとアドインカードモジュールのロックダイヤグラムである。

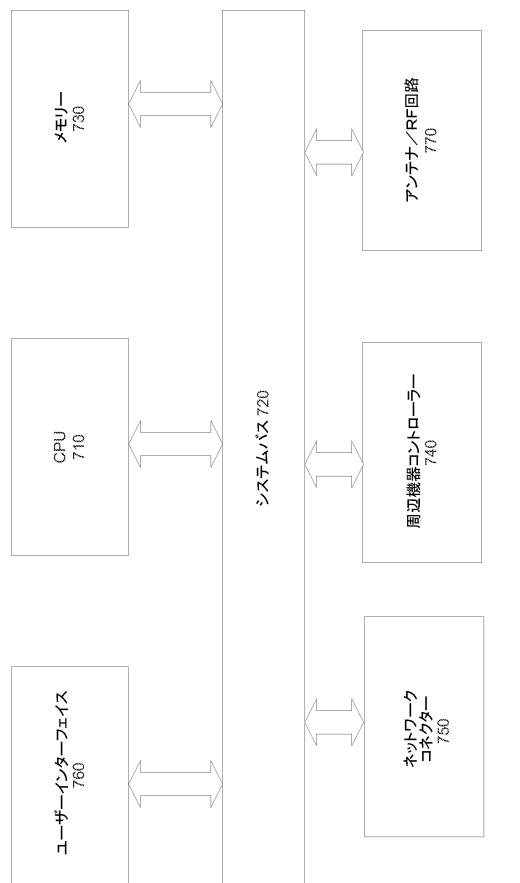

【図7】図7は、本発明の一つの実施例を利用するシステムのロックダイヤグラムである。

#### 【0009】

所定の詳細及び実施例に係る説明が後に続く。図面の説明を含むものであり、図面は以降に記述される実施例のいくつか又は全てを表している。他の可能性のある具体化、または、ここにおいて表される本発明の概念に係る実施例の説明も同様に後に続く。本発明の実施例の概要が以下に提供され、図面に関してより詳細な説明が続く。

#### 【発明を実施するための形態】

#### 【0010】

本発明の具体例を利用するプロセッサアドインカードの実施例は、グラフィックプロセッサユニット(GPU)を有するグラフィックプロセッササブシステムと、高度に並列なアプリケーションのパフォーマンスを改善するための複数の小さく、低消費電力なプロセッサコア又はマルチコアプロセッサを有するプロセッサアドインカードを含んでいる。異種混在(heterogeneous)が加速されたコンピューター環境においては、しかしながら、共通で、規格ベースのプログラミング及びコミュニケーションモデルを提供することは難しいと証明されている。このことは、クラスター(cluster)において特に真実であり、全てのプロセッサからの効率的なコミュニケーションメカニズムを有することが望ましい。プロセッサが、プライマリーシステムのCPUであるか、アドインカードのコプロセッサコアであるかにかかわらずである。共通で、規格ベースのプログラミングモデルは、アプリケーションの開発とメインテナンスを簡素化するだけでなく、システムを使用するためのより大きな適応性を与えてシステムのパフォーマンスの全ての利点を得ることができる。

#### 【0011】

クラスターは、一般的に、お互いに密接に動作するようにリンク又は相互接続されたコンピューターシステムのグループを参照するものである。それらは、多くの観点で一つのコンピューターを形成するようにリンク等されている。クラスターは、一般的に、単独のコンピューターによって提供されるものよりも大幅に改善されたパフォーマンス及び/又は可用性を提供する。クラスターは、また、典型的には、同等な速度と可用性のある単独のコンピューターよりも、コスト効率が良い。

#### 【0012】

大規模なクラスターシステムの構築に対する重要な見地は、相互接続である。相互接続は、システムの全てを一緒に接続する「ファブリック("fabric")」を含んでよい。システムをファブリックに対してインターフェイスするホストアダプターも同様である。クラスターは、インフィニバンド仕様又はRDMAコンソーシアム仕様と調和した相互接続を利用してよい。インフィニバンドは、本来高性能コンピューターにおいて使用されたスイッチファブリックコミュニケーションリンク(switted fabric communication link)であり、スケーラビリティと同様に、サービス品質とフェイルオーバー機能を提供する。インフィニバンド相互接続は、一般的に、よ

10

20

30

40

50

り小さなレイテンシー ( latency ) 、より高いバンド幅、および、改善された信頼性を提供する。

#### 【 0 0 1 3 】

インフィニバンドといった R D M A アーキテクチャーは、メッセージ受渡しオペレーティングシステムのレイテンシーを削減し、かつ、バンド幅を増加させることによって、高パフォーマンスコンピューティング ( H P C ) クラスター・アプリケーションのパフォーマンス改善において、非常に成功してきた。R D M A アーキテクチャーは、カーネルバイパス ( k e r n e l - b y p a s s ) 、ダイレクトデータ配置を通じて、ネットワークインターフェイスをアプリケーションに対して大変近くに移動することによってパフォーマンスを改善し、かつ、アプリケーションの要求に合せるように I / O オペレーティングシステムをより広くコントロールすることができる。10

#### 【 0 0 1 4 】

R D M A アーキテクチャーは、ハードウェアにおいて、プロセス分離、保護、および、アドレス変換をすることができる。このアーキテクチャーは、ホストとコプロセッサ・アプリケーションが分離されたアドレスドメインにおいて実行されるコプロセッサ・コア環境に対して相性がいい。しかしながら、従来技術においては、取り付けられたプロセッサ（つまり、プロセッサ・アドインカード）に対して R D M A の利益は利用可能ではなかった。本発明の実施例は、R D M A アーキテクチャーの利益を取り付けられたプロセッサに対して直接的に提供し、図 1 に示すようなソリューションに対する必要性を取り除く。図 1 では、取り付けられたプロセッサに係る内外のコミュニケーションは、ホストメモリーの中への追加のデータコピーを招くことを要し、実質的に、メッセージレイテンシーと達成可能なバンド幅の両方に影響を与えている。20

#### 【 0 0 1 5 】

図 2 は、本発明の一つの実施例に従ったシステムのブロックダイヤグラムである。システム 200 は、システム C P U 210 、システムメモリー 220 、プラットフォーム・コントローラー・ハブ ( P C H ) 230 、周辺機器 240 、および、R D M A デバイス 250 を含んでいる。この実施例において、周辺機器 240 は、プロセッサ・アドインカードであり、プロセッサ 241 とメモリー 242 を含んでいる。周辺機器 240 と R D M A デバイス 250 は、「ピア ( " p e e r " ) 」デバイスとして参照されてよい。

#### 【 0 0 1 6 】

周辺機器 240 は、R D M A デバイス 250 の中に保管されているデータにアクセスをリクエストし得る。周辺機器が、P C I e リンクを介して P C H 230 と通信可能に接続されているものと示されている一方で、R D M A デバイスは、P C I e ルートポート 231 を介して P C H 130 に対して動作可能に接続されているものと示されている。この実施例において、周辺機器 240 は、P C H を含んでおらず、従って、ホスト・チャネル・アダプター / ネットワーク・インターフェイス・コントローラー ( H C A / N I C ) カードを R D M A デバイス 250 に専念させる能力を有していない（しかしながら、P C H 又はオンボードの R D M A デバイスを伴う内部 P C I e バスを含んでいる周辺機器も、また、以下に説明される本発明の実施例を利用し得ることが理解されるべきである）。P C I e 相互接続は、単独では、ピアデバイスが、別のピアデバイスのアドレス空間の中に保管されているデータにアクセスするようにはできない。3040

#### 【 0 0 1 7 】

本発明の実施例は、システム 200 、 P C H 230 、および、周辺機器 240 に含まれているロジック及び/又はモジュールについて説明する。周辺機器が、R D M A デバイス 250 の中に含まれているデータに対して直接的にアクセスできるようにするものである。つまり、システムメモリー 220 は、図 1 のシステム 100 といった従来技術のソリューションにおいて必要とされたように必要とされない。リクエストされたデータをホストメモリーの中に受け取るための、ホストメモリーに対する必要性を取り除くことによって、本発明の実施例は、著しく、メッセージレイテンシーを減少させ、達成可能なバンド幅を増加させる。50

## 【0018】

図3は、本発明の一つの実施例に従ったシステムコンポーネントのブロックダイヤグラムである。この実施例において、PCH310、周辺機器320、および、RDMA330は、システムバス390（ここにおいては、代替的にイントラノード（intra-node）バスとして参照される）を介してお互いに通信可能に接続されている。周辺機器320は、図2に係る機器240と類似のものであり、RDMAデバイス330を専念させる能力を有していない。

## 【0019】

この実施例において、周辺機器320のメモリー321はリクエストキュー（queue）322を含んでいる。リクエストキューは、RDMAデバイス330のメモリー331に向けて指示されたリクエストを保管している。周辺機器のCPU323は、リクエストキューがメモリー331へのアクセスに対する未解決のリクエストを有していることを、RDMAデバイス330に通知する。一つの実施例において、RDMAデバイス330は、キュー322の中に未解決のリクエストがいくらかでもある場合に通知される。他の実施例において、RDMAデバイス330は、キュー322の中の未解決のリクエストの数量が閾値を超えた場合に通知される。

## 【0020】

CPU323は、PCH310の中に含まれる仮想アドレス311に対して書き込むことによって、未解決のリクエストについてRDMAデバイス350に通知する。仮想アドレスは、RDMAデバイスのメモリー331に対してマップされたメモリーである。未解決のリクエストは、実行されるべきオペレーションを記述することができる。つまり、send、receive、write、read、atomic compare/exchange、atomic fetch/add、等である。このように、本発明の実施例は、周辺機器320からホストシステムのPCH310への「プロキシー（"proxy"）」リクエストに対して記述されてよい。

## 【0021】

図4は、本発明の一つの実施例に従ったプロセスのフローチャートである。ここにおいて説明されるように、フローチャートは、種々のプロセス動作のシーケンスに係る実施例を提供する。所定のシーケンス又は順序において示されてはいるが、別に指定がなければ、動作の順序は変更することができる。従って、図示された実施例は、単なる例示として理解されるべきであり、図示されたプロセスは、異なる順序で実行することができ、いくつかの動作は並行に実行され得る。加えて、一つまたはそれ以上の動作は、本発明に種々の実施例において除外することができる。従って、全ての動作が、それぞれの実施において必要とされるわけではない。他のプロセスフローも可能である。

## 【0022】

プロセス400は、プロセッサコアとメモリーを有する周辺機器による、RDMAデバイスのメモリーへのアクセスに対するリクエストを受け取るオペレーションを含んでいる、410。そのリクエストは、周辺機器のメモリーにおけるキューの中に保管されてよい。いくつかの実施例において、周辺機器は複数のプロセッサコアを含んでおり、それぞれのプロセッサコアに対して分離されたキューを維持している。

## 【0023】

周辺機器は、PCHの中に含まれている仮想アドレスに対してデータを送付することによって、キューの中のアクセスリクエストメッセージをRDMAデバイスに通知する、420。その仮想アドレスは、PCHの中に含まれており、RDMAデバイスのメモリーにマップされている。PCHは、RDMAデバイスにマップされた仮想アドレスを利用する、430。そして、RDMAデバイスのメモリーに対してRDMAアクセスリクエストメッセージを伝送する、440。そのRDMAアクセスリクエストメッセージは、周辺機器の中にキューされたアクセスリクエストメッセージに基づくものである。

## 【0024】

RDMAデバイスは、RDMAアクセスリクエストメッセージの受け取りに応じて、周

10

20

30

40

50

辺機器からのリクエストを完了する、450。いくつかの実施例において、R D M Aデバイスは、P C Hの中に含まれ、かつ、周辺機器のメモリーにマップされている仮想アドレスに対して完了メッセージを送付する。その仮想アドレスは、完了メッセージを保管するための完了キューを表してよい。例えば、R D M AアクセスリクエストメッセージがR D M A読み出しリクエストを有する場合、周辺機器によってリクエストされたデータを含んでいるデータメッセージが、P C Hを介して周辺機器に対して送付される。R D M AアクセスリクエストメッセージがR D M A書き込みリクエストを有する場合、P C Hは、書き込まれるべきデータを含んでいるデータメッセージをR D M Aデバイスに対して伝送する。いくつかの実施例において、R D M A動作の完了は、R D M Aデバイスによって完了メッセージがいつ送付されるかを決定するものではない。例えば、インフィニバンド仕様は、リクエストは、それらが投稿された順序で実行されることを要求する。先の全てのR D M A動作が完了するまで、周辺機器は完了メッセージを受け取らないことを意味するものである。

#### 【0025】

図5は、本発明の一つの実施例に従ったプロセスのフローチャートである。プロセス500は、周辺機器（プロセッサコアも含んでいる）のメモリーへのアクセスに対するリクエストを受け取るオペレーションを含んでいる、510。そのリクエストは、R D M Aデバイスのメモリーにおけるキューの中に保管されてよい。

#### 【0026】

R D M Aデバイスは、P C Hの中に含まれている仮想アドレスに対してデータを送付することによって、キューの中のアクセスリクエストメッセージをホストシステムに通知する、520。その仮想アドレスは、周辺機器のメモリーにマップされている。P C Hは、アクセスリクエストメッセージパラメーターとして、R D M Aデバイスにマップされた仮想アドレスを利用する、530。そして、周辺機器のメモリーに対してアクセスリクエストメッセージを伝送する、540。そのアクセスリクエストメッセージは、R D M Aデバイスの中にキューされたアクセスリクエストメッセージに基づいて、周辺機器に対して伝送される。

#### 【0027】

周辺機器は、P C Hからのアクセスリクエストメッセージの受け取りに応じて、R D M Aデバイスからのリクエストを完了する。例えば、アクセスリクエストメッセージが読み出しリクエストを有する場合、R D M Aデバイスによってリクエストされたデータを含んでいるデータメッセージが、P C Hを介してR D M Aデバイスに対して送付される。アクセスリクエストメッセージが書き込みリクエストを有する場合、R D M Aデバイスは、P C Hを介して、書き込まれるべきデータを含んでいるデータメッセージを周辺機器に対して伝送する。R D M Aデバイスは、R D M A動作及び/又はパラメーターのタイプに応じて、P C Hの中に含まれ、かつ、周辺機器のメモリーにマップされている仮想アドレスに対して完了メッセージを送付する、550。その仮想アドレスは、完了メッセージを保管するための完了キューを表してよい。

#### 【0028】

図6は、本発明の一つの実施例に従ったホストとプロセッサアドインカードモジュールのブロックダイヤグラムである。上述のように、本発明の実施例は、インフィニバンド仕様（例えば、規格リリース1.0.a、2001年7月19日発行）に準じた相互接続を利用してよい。インフィニバンドは、本来高性能コンピューターにおいて使用されるスイッチファブリックコミュニケーションリンクであり、スケーラビリティと同様に、サービス品質とフェイルオーバー機能を提供する。インフィニバンド相互接続は、一般的に、より小さなレイテンシー、より高いバンド幅、および、改善された信頼性を提供する。インフィニバンドは、コンピューターシステムのコンポーネントの中、および、コンピューターの中で情報を移動する方法を提供する。インフィニバンドは、コンピューターのC P Uが、非常に高いパフォーマンスでI/Oデバイス及び他のC P Uと直接的にコミュニケーションできるようにする。インフィニバンド技術は、あらゆるネットワークに係るデータ

10

20

30

40

50

センターのバックエンド( *b a c k e n d* )を対象としている。ネットワークインフラストラクチャーのフロントエンド及びミドルエンドは、典型的には、従来のイーサネット( 登録商標 )( *E t h e r n e t* )技術を含んでいる。別の言葉で言えば、インフィニバンド及びイーサネット技術は、両方とも同一のホストによって使用され得るものである。

#### 【 0 0 2 9 】

ホスト 610 と周辺機器カード 630 は、種々のインフィニバンドモジュール( 以下に説明される )を含むように示されており、PCIe 相互接続 660 を介して RDMA デバイス 650 と通信可能に接続されている。以下に説明するように、RDMA デバイス 650 によって受け取られる RDMA メッセージは、RDMA コンソーシアム仕様( 例えば、RDMA プロトコル規格( バージョン 1.0 )、2002 年 10 月 21 日発行 )に準じてよい。RDMA コンソーシアムの RDMA プロトコルは、TCP / IP プロトコルにおける TCP 層の上で規定されている。従って、RDMA 動作は、プロトコルスタックのトップから送信器側のボトムまで進み、次に、プロトコルスタックを越えて受信器側のトップまで進む。本発明の実施例によって利用される RDMA プロトコルは、基本の TCP / IP 処理ハードウェアを構築することを含んでよい。パケットを受け取り、TCP / IP を停止し、TCP / IP を通してアプリケーションに対してパケットを処理し、そして、データ及びメモリーに書き込むためのアプリケーション層でのアドレスを抽出することである。RDMA プロトコルは、データ転送をより効率的にする( 特により大きなデータペイロードに対して )ことによって、パケットをメモリーにコピーすることができる( そして、その後にデータペイロードをメモリーにコピーする )。

10

20

#### 【 0 0 3 0 】

この実施例において、ホスト 610 上のモジュールと周辺機器 630 はお互いにコミュニケーションし、PCIe 相互接続 660 をわたり RDMA デバイス 650 に対して直接的なアクセスを有している。モジュールは、RDMA デバイスのリソースを管理するために PCIe 相互接続 660 をわたりプロキシオペレーションに対するスプリットドライバー( *s p l i t - d e r i v e r* )モデルを使用する。

#### 【 0 0 3 1 】

ホスト 610 は、インフィニバンドベースのソフトウェアコミュニケーションスタックを含むように図示されている。メッセージパッシングインターフェイス( MPI )アプリケーション 611 、 RDMA API であるユーザーモードダイレクトアクセスプロバイダーライブラリー( u D A P L ) 612 、 IB バーブ( *v e r b* )( つまり、機能 )ライブラリー 613 、ベンダーライブラリー 614 、 IB ユーバーブ( *u v e r b* ) 635 、および、 IB コア 636 を含んでいる。ホストと周辺機器は、さらに、以下に説明されるモジュールとして実行される本発明の実施例を利用する。

30

#### 【 0 0 3 2 】

ホスト 610 は、IB プロキシーデーモン( *d a e m o n* ) 618 を含んでいる。IB プロキシーデーモンは、ホストユーザー モードのアプリケーションであり、基底にあるベンダードライバー 617 に対するコール( *c a l l* )のために IB プロキシーサーバー 619( 以下に説明される )に対してユーザー モードプロセスコンテクスト( *c o n t e x t* )を提供する。ユーザー モードプロセスコンテクストは、ベンダードライバー 617 を変更することなく RDMA デバイス 650 のメモリーの仮想アドレスマッピングを実行するために使用され得る。

40

#### 【 0 0 3 3 】

ホスト 610 は、さらに、IB プロキシーサーバー 619 を含んでおり、IB プロキシーサーバーはホストカーネルモジュールを有している。この実施例において、その IB プロキシーサーバーは、コミュニケーションと周辺機器 630( 以下に説明される )の IB プロキシクライアント 638 のためのコマンドサービスを提供する。この実施例において、IB プロキシーサーバー 619 は、クライアント接続をリスン( *l i s t e n* )し、RDMA デバイスの追加、除去、および、イベント通知メッセージをリレーする。IB プロキシーサーバー 619 は、さらに、IB プロキシクライアント 638 のために IB コ

50

アレイヤー 616 に対するカーネルモード I B バープコールを開始して、その結果を戻すことができる。

【0034】

周辺機器 630 は、I B プロキシークライアント 638 を含んでおり、I B プロキシークライアントはカーネルモジュールを有している。その I B プロキシークライアントは、ホスト 610 上でカーネルモード I B バープを実行するために、ベンダープロキシードライバー 637（以下に説明される）に対してプログラミングインターフェイスを提供する。インターフェイスは、さらに、コマンドのフォーマット及びコミュニケーションの実行に係る詳細を抽出し得る。I B プロキシークライアント 638 は、所定のデバイスの追加、除去、および、ベンダープロキシードライバー 637 へのイベント通知に対するコールバック（call back）を呼び出す。10

【0035】

周辺機器 630 は、さらに、ベンダープロキシードライバー 637 を含んでおり、ベンダープロキシードライバーはカーネルモジュールを有している。所定の R D M A デバイスをサポートするために異なるベンダープロキシードライバーが使用されてよい。そのベンダープロキシードライバーそれぞれは、R D M A のデバイスの追加、除去、および、所定の P C I e ドライバーからのイベント通知を I B プロキシークライアント 638 に登録し得る。ベンダープロキシードライバー 637 は、カーネルモード I B バープコールを実行するために、I B プロキシークライアント 638 によって提供されるプログラミングインターフェイスを使用してよい。そのベンダープロキシードライバーは、さらに、ベンダーライブラー 634 とホスト 610 上のベンダードライバー 617 との間で共有されるあらゆるプライベートデータの解釈及び変換を取り扱う。20

【0036】

この実施例において、ホスト 610 と周辺機器 630 の両方は、シンメトリックコミュニケーションインターフェイス（S C I F）モジュール 620 と 640 を、それぞれに含んでいる。その S C I F モジュールは、シングルプラットフォームの中でイントラノード（intra-node）コミュニケーションのためのメカニズムを提供する。S C I F は、ホスト 610 と周辺機器 630 との間で対称な A P I を提供する一方で、P C I e にわたるコミュニケーション（および、関連する周辺機器ハードウェアのコントロール）の詳細を抽出する。30

【0037】

上述のモジュールに加えて、本発明の実施例は、I B コアレイヤー 616 におけるコールを利用して、ベンダーライブラー 614 及び 634 とベンダードライバー 617 との間でプライベートデータを転送する。メモリーを R D M A デバイス 650 に対してマッピングすることも同様である。

【0038】

上記の「バープ（"verb"）」（つまり、機能）は、R D M A デバイス 650 に向けた P D M A オペレーションを実行する。バープは、特権クラスと非特権クラスに分類されてよい。特権バープは、典型的に R D M A ハードウェアのリソースを割り当て、管理するために使用され、ベンダードライバー 617 によって実施される。周辺機器 630 上で稼働しているアプリケーションのために、これらの特権バープが、ベンダープロキシサーバー 637 を通じてホスト 610 上のベンダードライバー 617 に対してフォワードされる。一旦、ハードウェアが割り当てられ開始されると、非特権バープは、カーネルをバイパスし、リソース割り当ての最中にアプリケーションアドレス空間の中にマップされたメモリーを使用して、ユーザー モードからハードウェアに対する直接的なアクセスを許可する。同様に、R D M A デバイスは、キューにアクセスすることができ、プロセスアドレス空間へ、または、プロセスアドレス空間から直接的にデータ転送を実行することができる。このように、本発明の実施例は、周辺機器 630 上のクライアントプロセスを、まるでホスト 610 上の別の「ユーザー モード」プロセスであるかのようにする。40

【0039】

50

従って、上記のモジュールにより、ホスト 610 は、R D M A デバイス 650 のメモリーにアクセスするための、周辺機器 630 のプロセッサコアからのアクセスリクエストメッセージに係る通知を受け取ることができる。その通知は、ホスト 610 及び R D M A デバイス 650 のメモリーにマップされたメモリー（例えば、図 3 に示されるように）の中に含まれる仮想アドレスにおいて受け取られる。ホストデバイス 610 は、そのアクセスリクエストメッセージに基づいて、R D M A デバイスに対して R D M A アクセスリクエストを転送する。ここで、リクエストは仮想アドレス R D M A パラメーターを含んでいる。従って、データリクエストのタイプが何であれ、アクセスリクエストメッセージは、例えば、`send`、`receive`、`write`、`read`、`atomic compare / exchange`、`atomic fetch / add`、等を含んでいる。データリクエストは、R D M A デバイス 650 に対して、周辺機器 630 からというよりむしろ、まるでホスト 610 上の「ユーザー モード」から生じたものであるように見える。

10

#### 【0040】

図 7 は、本発明の一つの実施例を利用するシステムのブロックダイヤグラムである。システム 700 は、サーバープラットフォームを記述しているが、例えば、以下のものに含まれてのよい。デスクトップコンピューター、ラップトップコンピューター、タブレットコンピューター、ネットブック、ノートブックコンピューター、パーソナルデジタルアシスタント（PDA）、サーバー、ワークステーション、携帯電話、モバイルコンピューター機器、インターネット機器、MP3 又はメディアプレーヤー、または、あらゆる他のタイプのコンピューター デバイス、である。

20

#### 【0041】

システム 700 は、システムバス 720 を介して、データを交換するためのプロセッサ 710、ユーザーインターフェイス 760、システムメモリー 730、周辺機器コントローラー 740、および、ネットワークコネクター 750 を含んでいる。その周辺機器コントローラーは、周辺機器及び R D M A デバイスとコミュニケーション可能に接続され、上記の本発明の実施例のいずれかに従ってデバイ患者関連情報の I/O リクエストを管理する。

#### 【0042】

システム 700 は、さらに、システム 700 の種々のエレメントによって処理されるべき信号を送信及び受信するためのアンテナと R F 回路 770 を含んでいる。上記のアンテナは、指向性アンテナ又は無指向性アンテナであってよい。ここにおいて使用されるように、無指向性アンテナという用語は、少なくとも一平面において実質的に均一なパターンを有するあらゆるアンテナを参照するものである。例えば、いくつかの実施例において、アンテナは、ダイポール（dipole）アンテナ、または、四分の一波長（quarter wave）アンテナといった、無指向性アンテナであってよい。例えば、いくつかの実施例において、アンテナは、パラボラアンテナ、パッチアンテナ、または、ハムアンテナといった、指向性アンテナであってもよい。いくつかの実施例において、システム 700 は、複数の物理的なアンテナを含んでよい。

30

#### 【0043】

ネットワークコネクター 750 から離れているように示されているが、他の実施例において、アンテナ及び R F 回路 770 は、無線インターフェイスを含んでよいことが理解されるべきである。無線インターフェイスは、これらに限定されるわけではないが、IEEE 802.11 規格及び関連ファミリー規格、Home Plug AV (HPAV)、ウルトラワイドバンド（UWB）、Bluetooth（登録商標）、WiMax、または、無線通信プロトコルの他の形式に従って動作するものである。

40

#### 【0044】

ここにおいて、プロセス、サーバー、または、ツールとして説明され、上記に参照された種々のコンポーネントは、説明された機能を実行するための手段であってよい。ここにおいて説明されたそれぞれのコンポーネントは、ソフトウェア又はハードウェア、または、これらの組み合わせを含んでいる。それぞれ及び全てのコンポーネントは、ソフトウェ

50

アモジュール、ハードウェアモジュール、特定用途ハードウェア（例えば、アプリケーション所定のハードウェア、A S I C、D S P、等）、エンベッドコントローラー、ハードワイヤード回路、ハードウェアロジック、等として実施されてよい。ソフトウェアコンテンツ（例えば、データ、インストラクション、コンフィグレーション）は、固定で有形なコンピューター又はマシンで読み取り可能な媒体を含む製品を介して提供されてよい。実行され得るインストラクションを表すコンテンツを提供するものである。コンテンツは、結果として、ここにおいて説明された種々の機能／動作のコンピューターによる実行を生じる。

## 【0045】

コンピューターで読み取り可能な固定記録媒体は、コンピューター（例えば、計算機器、電子システム、等）によってアクセス可能な形式で情報を提供（つまり、保管及び/又は送信）するあらゆるメカニズムを含んでいる。記録可能／記録不能媒体（例えば、読み出し専用メモリー（R O M）、ランダムアクセスメモリー（R A M）、磁気ディスク記録媒体、光記録媒体、フラッシュメモリーデバイス、等）といったものである。コンテンツは、直接的に実行可能な（「オブジェクト」又は「実行可能」形式）ソースコード、または、異なるコード（「デルタ」又は「パッチ」コード）であってよい。コンピューターで読み取り可能な固定記録媒体は、また、ストレージ又はデータベースを含んでよく、そこからコンテンツをダウンロードすることができる。コンピューターで読み取り可能な媒体は、また、販売時又は引き渡し時に、媒体上にコンテンツが保管されているデバイス又はプロダクトを含んでよい。従って、コンテンツが保管されたデバイスを引き渡すこと、または、コミュニケーション媒体にわたるダウンロードのためにコンテンツを提供することは、ここにおいて説明されたようなコンテンツを伴う製品を提供することとして理解されてよい。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

700

---

フロントページの続き

- (72)発明者 ウッドラフ, ロバート, ジェイ .

アメリカ合衆国 97106 オレゴン州 バンクス ノースウェスト グランドビュー 139

83

- (72)発明者 リー, デイヴィッド, エム .

アメリカ合衆国 97229 オレゴン州 ポートランド ノースウェスト クレストビュー ウ

エイ 2203

- (72)発明者 ディヴィス, アーリン, アール .

アメリカ合衆国 97148 オレゴン州 ヤムヒル ノースイースト コーヴ オーチャード

ロード 23190

- (72)発明者 ヘフティ, マーク, ショーン

アメリカ合衆国 97007 オレゴン州 アロハ サウスウェスト ハート ロード 1856

0

- (72)発明者 コフマン, ジェリー, エル .

アメリカ合衆国 97124 オレゴン州 ヒルズボロ ノースイースト 11ス コート 31

53

審査官 寺谷 大亮

(56)参考文献 米国特許第07711793(US, B1)

米国特許出願公開第2004/0034725(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 13 / 36

G 06 F 13 / 28

G 06 F 13 / 38