(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4817924号

(P4817924)

(45) 発行日 平成23年11月16日(2011.11.16)

(24) 登録日 平成23年9月9日(2011.9.9)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| HO 1 L 23/02 | (2006.01) |

| HO 1 L 23/12 | (2006.01) |

| HO 1 L 23/04 | (2006.01) |

| HO 1 P 3/08  | (2006.01) |

| HO 1 L       | 23/02     |

| HO 1 L       | 23/12     |

| HO 1 L       | 23/04     |

| HO 1 P       | 3/08      |

請求項の数 5 (全 9 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2006-91162 (P2006-91162)    |

| (22) 出願日  | 平成18年3月29日 (2006.3.29)        |

| (65) 公開番号 | 特開2007-266417 (P2007-266417A) |

| (43) 公開日  | 平成19年10月11日 (2007.10.11)      |

| 審査請求日     | 平成21年2月27日 (2009.2.27)        |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100083806<br>弁理士 三好 秀和                |

| (74) 代理人  | 100100712<br>弁理士 岩▲崎▼ 幸邦              |

| (74) 代理人  | 100100929<br>弁理士 川又 澄雄                |

| (74) 代理人  | 100108707<br>弁理士 中村 友之                |

| (74) 代理人  | 100095500<br>弁理士 伊藤 正和                |

| (74) 代理人  | 100101247<br>弁理士 高橋 俊一                |

最終頁に続く

(54) 【発明の名称】半導体パッケージ

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体素子が設置されたベース基板と、

前記ベース基板上に設けられ前記半導体素子を覆い、前記ベース基板側の端部に開口部を有する覆い部材と、

第1表面及び前記第1表面の反対面である第2表面を有し、前記第2表面を前記ベース基板に向けて前記開口部を塞ぐように前記ベース基板上に設けられ、前記第1表面における前記覆い部材の内部に位置する領域に第1高周波信号線を有し、前記第2表面に前記第1高周波信号線に電気的に接続する第2高周波信号線を有する接栓基板と、

前記第2高周波信号線と前記ベース基板との間に空間を形成して前記ベース基板を前記第2高周波信号線から離間させるように、前記ベース基板に形成された凹部と、

を備え、

前記第1高周波信号線と前記ベース基板は第1マイクロストリップ線路部を構成し、

前記第2高周波信号線と前記ベース基板は第2マイクロストリップ線路部を構成し、

前記第1マイクロストリップ線路部のインピーダンスと前記第2マイクロストリップ線路部のインピーダンスは同じであることを特徴とする半導体パッケージ。

## 【請求項 2】

半導体素子が設置された表面及び前記表面の反対面を有するベース基板と、

前記ベース基板の前記表面上に設けられ前記半導体素子を覆い、前記ベース基板側の端部に開口部を有する覆い部材と、

第1表面及び前記第1表面の反対面である第2表面を有し、前記第2表面を前記ベース基板に向けて前記開口部を塞ぐように前記ベース基板上に設けられ、前記第1表面における前記覆い部材の内部に位置する領域に第1高周波信号線を有し、前記第2表面に前記第1高周波信号線に電気的に接続する第2高周波信号線を有する接栓基板と、

前記ベース基板の前記反対面を含む仮想面と前記第2高周波信号線との間に空間を形成して前記ベース基板を前記第2高周波信号線から離間させるように、前記ベース基板に形成された切欠部と、

を備え、

前記第1高周波信号線と前記ベース基板は第1マイクロストリップ線路部を構成し、

前記仮想面と前記第2高周波信号線が第2マイクロストリップ線路部を構成する場合、前記第1マイクロストリップ線路部のインピーダンスと前記第2マイクロストリップ線路部のインピーダンスが同じになるように前記第2高周波信号線の幅が設定されていることを特徴とする半導体パッケージ。

### 【請求項3】

前記第2高周波信号線の幅は前記第1高周波信号線の幅よりも大きいことを特徴とする請求項1又は2記載の半導体パッケージ。

### 【請求項4】

前記第2マイクロストリップ線路部分のベース基板は前記第1マイクロストリップ線路部分のベース基板よりも薄いことを特徴とする請求項1記載の半導体パッケージ。

### 【請求項5】

前記第1マイクロストリップ線路部分のベース基板の厚さは、前記第1マイクロストリップ線路部のインピーダンスと前記第2マイクロストリップ線路部のインピーダンスが同じになるように設定されていることを特徴とする請求項2記載の半導体パッケージ。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体パッケージに関し、特に、半導体素子を気密封止する半導体パッケージに関する。

#### 【背景技術】

#### 【0002】

高周波半導体素子等の半導体素子を有する半導体パッケージは、様々な高周波機器に用いられている（例えば、特許文献1参照）。この半導体パッケージは、半導体素子が設置されたベース基板と、ベース基板上に設けられ半導体素子を囲む枠体と、枠体上に設けられた蓋体と、枠体に貫通させてベース基板上に設けられた接栓基板とを備えており、半導体素子を気密封止するパッケージ（気密封止パッケージ）である。

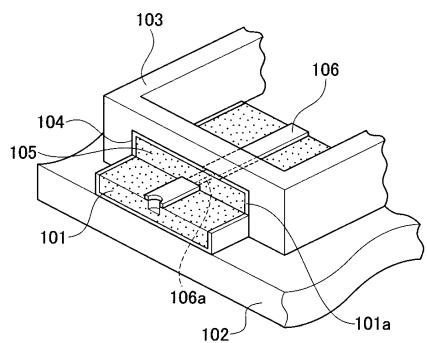

#### 【0003】

例えば、図7に示すように、接栓基板101はベース基板102上に設けられている。この接栓基板101は、誘電体により形成されており、枠体であるフレーム103に形成された開口部104を塞ぐ基板である。接栓基板101は、開口部104を塞ぐための凸部105を有しており、この接栓基板101の表面には、凸部105を貫通する高周波信号線106が設けられている。接栓基板101の周面には、Wペーストを塗布し焼結することにより形成された外枠101aが設けられている。この外枠101aとフレーム103とがAgを用いてろう付けされ、気密封止パッケージが形成されている。

#### 【0004】

高周波信号線106の貫通部分が三導体部（ストリップ線路部）106aとして機能し、その他の部分がマイクロストリップ線路部として機能する。なお、高周波信号線106の三導体部106aは、マイクロストリップ線路部とのインピーダンス整合を取るため、マイクロストリップ線路部に比べ細く形成されている（図7参照）。

#### 【特許文献1】特開2001-35948号公報

#### 【発明の開示】

10

20

30

40

50

## 【発明が解決しようとする課題】

## 【0005】

しかしながら、現在、半導体パッケージの高電力化が進んでおり、高周波信号線106の幅が狭くなると、高周波信号の挿入損失が増加してしまい、さらに、その許容電流が低くなるため、高周波信号線106の三導体部106aが溶融してしまうことがある。

## 【0006】

本発明は、上記に鑑みてなされたものであり、その目的は、高電力化による高周波信号線の溶融を抑え、高周波信号の挿入損失の増加を防止することができる半導体パッケージを提供することである。

## 【課題を解決するための手段】

10

## 【0007】

本発明の実施の形態に係る第1の特徴は、半導体パッケージにおいて、半導体素子が設置されたベース基板と、前記ベース基板上に設けられ前記半導体素子を覆い、前記ベース基板側の端部に開口部を有する覆い部材と、第1表面及び前記第1表面の反対面である第2表面を有し、前記第2表面を前記ベース基板に向けて前記開口部を塞ぐように前記ベース基板上に設けられ、前記第1表面における前記覆い部材の内部に位置する領域に第1高周波信号線を有し、前記第2表面に前記第1高周波信号線に電気的に接続する第2高周波信号線を有する接栓基板と、前記第2高周波信号線と前記ベース基板との間に空間を形成して前記ベース基板を前記第2高周波信号線から離間させるように、前記ベース基板に形成された凹部と、を備え、前記第1高周波信号線と前記ベース基板は第1マイクロトリップ線路部を構成し、前記第2高周波信号線と前記ベース基板は第2マイクロトリップ線路部を構成し、前記第1マイクロトリップ線路部のインピーダンスと前記第2マイクロトリップ線路部のインピーダンスは同じであることである。

20

本発明の実施の形態に係る第2の特徴は、半導体パッケージにおいて、半導体素子が設置された表面及び前記表面の反対面を有するベース基板と、前記ベース基板の前記表面上に設けられ前記半導体素子を覆い、前記ベース基板側の端部に開口部を有する覆い部材と、第1表面及び前記第1表面の反対面である第2表面を有し、前記第2表面を前記ベース基板に向けて前記開口部を塞ぐように前記ベース基板上に設けられ、前記第1表面における前記覆い部材の内部に位置する領域に第1高周波信号線を有し、前記第2表面に前記第1高周波信号線に電気的に接続する第2高周波信号線を有する接栓基板と、前記ベース基板の前記反対面を含む仮想面と前記第2高周波信号線との間に空間を形成して前記ベース基板を前記第2高周波信号線から離間させるように、前記ベース基板に形成された切欠部と、を備え、前記第1高周波信号線と前記ベース基板は第1マイクロトリップ線路部を構成し、前記仮想面と前記第2高周波信号線が第2マイクロトリップ線路部を構成する場合、前記第1マイクロトリップ線路部のインピーダンスと前記第2マイクロトリップ線路部のインピーダンスが同じになるように前記第2高周波信号線の幅が設定されていることである。

30

## 【発明の効果】

## 【0008】

本発明によれば、高電力化による高周波信号線の溶融を抑え、高周波信号の挿入損失の増加を防止することができる半導体パッケージを提供することができる。

40

## 【発明を実施するための最良の形態】

## 【0009】

## (第1の実施の形態)

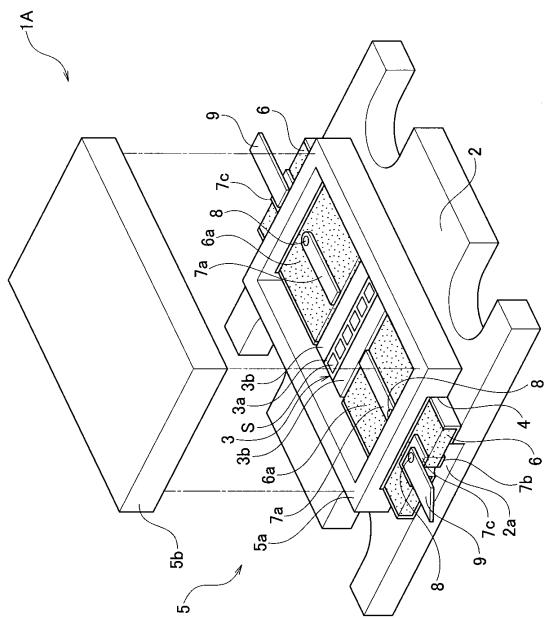

本発明の第1の実施の形態について図1ないし図4を参照して説明する。

## 【0010】

図1ないし図3に示すように、本発明の第1の実施の形態に係る半導体パッケージ1Aは、ベース基板2と、そのベース基板2上に設けられ複数の半導体素子Sを有する半導体搭載部3と、ベース基板2に設けられ各半導体素子Sを覆い、ベース基板2側の端部に開口部4を有する覆い部材5と、開口部4を塞ぐようにベース基板2上に設けられ、第1表

50

面 6 a の覆い部材 5 の内部に位置する領域に第 1 高周波信号線 7 a を有し、第 1 表面の反対面である第 2 表面 6 b ( 図 3 参照 ) に第 1 高周波信号線 7 a に電気的に接続する第 2 高周波信号線 7 b を有する接栓基板 6 とを備えている。

【 0 0 1 1 】

半導体搭載部 3 は、各半導体素子 S と、それらの半導体素子 S を支持するマウント部 3 a と、そのマウント部 3 a 上に各半導体素子 S の両側にそれぞれ位置付けられて設けられた 2 つの整合コンデンサ 3 b とから構成されている。これらの整合コンデンサ 3 b は、ワイヤボンディング等により各半導体素子 S に電気的に接続されている。

【 0 0 1 2 】

覆い部材 5 は、枠状に形成されベース基板 2 上に設けられた枠体であるフレーム 5 a と、そのフレーム 5 a 上に設けられた蓋体である蓋部材 5 b とから構成されている。この覆い部材 5 は、その内部に半導体搭載部 3 を収容して気密封止する。フレーム 5 a には、2 つの開口部 4 が対向させて設けられている。これらの開口部 4 はベース基板 2 側の端部に位置付けられている。

【 0 0 1 3 】

接栓基板 6 は、所定の誘電率を有する誘電体により板状に形成された基板であり、フレーム 5 a の開口部 4 を塞ぐ部材として機能する。この接栓基板 6 の第 1 表面 6 a には、第 1 高周波信号線 7 a がフレーム 5 a 内に位置付けられて設けられており、さらに、第 3 高周波信号線 7 c がフレーム 5 a 外に位置付けられて設けられている。また、接栓基板 6 の第 2 表面 6 b ( 図 3 参照 ) である裏面には、第 2 高周波信号線 7 b が設けられている。

【 0 0 1 4 】

第 1 高周波信号線 7 a 、第 2 高周波信号線 7 b 及び第 3 高周波信号線 7 c は、高周波信号が通過する伝送線路である。これらの第 1 高周波信号線 7 a 、第 2 高周波信号線 7 b 及び第 3 高周波信号線 7 c は、接栓基板 6 にそれぞれ設けられた複数のスルーホール配線 8 により接続されている。

【 0 0 1 5 】

第 1 高周波信号線 7 a は、接栓基板 6 におけるフレーム 5 a の内部の内端部から対向する外部の外端部に向かってフレーム 5 a に接触しないようにその手前まで設けられている。この第 1 高周波信号線 7 a は整合コンデンサ 3 b に電気的に接続されている。また、第 3 高周波信号線 7 c は、フレーム 5 a の近傍から接栓基板 6 の外端部まで設けられている。第 2 高周波信号線 7 b は、各スルーホール配線 8 を介して第 1 高周波信号線 7 a と第 3 高周波信号線 7 c とを電気的に接続している。これらの第 1 高周波信号線 7 a 、第 2 高周波信号線 7 b 及び第 3 高周波信号線 7 c は、例えば W 厚膜又は C u 厚膜、N i メッキ及び A u メッキ等により形成されている。また、各スルーホール配線 8 は、気密封止のためブラインドスルーホールとなるように形成されている。

【 0 0 1 6 】

第 3 高周波信号線 7 c には、第 3 高周波信号線 7 c を半導体パッケージ 1 A の外部に引き出すリード線 9 が設けられている。このリード線 9 は、第 3 高周波信号線 7 c に電気的に接続されている。

【 0 0 1 7 】

ベース基板 2 は、板状に形成された基板であり、接栓基板 6 の第 2 表面 6 b である裏面を支持している。このベース基板 2 は、例えば銅等の放熱性が高い材料により、第 2 高周波信号線 7 b から離間するように形成されている。すなわち、ベース基板 2 には、その第 2 高周波信号線 7 b に対向し第 2 高周波信号線 7 b から離間する凹部 2 a が設けられている。これにより、接栓基板 6 がベース基板 2 上に設けられた場合、ベース基板 2 が第 2 高周波信号線 7 b に接触することが防止される。

【 0 0 1 8 】

凹部 2 a は、第 2 高周波信号線 7 b に対向する領域を含み第 2 高周波信号線 7 b より大きい領域のベース基板 2 の一部分を取り除くように形成されている。この凹部 2 a により、第 2 高周波信号線 7 b とベース基板 2 との間には、空間が設けられている。この空間は

10

20

30

40

50

空気により満たされており、空気層が形成されている。

#### 【0019】

以上説明したように、本発明の第1の実施の形態によれば、接栓基板6の第2表面6bに第2高周波信号線7bを設け、その第2表面6b上の第2高周波信号線7bから離間するようにベース基板2を形成することにより、フレーム5aの下方を通過する第2高周波信号線7bはマイクロストリップ線路部として機能する。このとき、第2高周波信号線7bの下方の空気層が誘電体となるので(1>2)、第1高周波信号線7a及び第3高周波信号線7cと第2高周波信号線7bとのインピーダンス整合を取るために、第2高周波信号線7bの幅W2を第1高周波信号線7a及び第3高周波信号線7cの幅W1に比べて広くする必要がある。これにより、第2高周波信号線7bの許容電流は増加することになり、高電力化による第2高周波信号線7bの溶融が抑えられるので、高周波信号の挿入損失の増加を防止することができる。10

#### 【0020】

さらに、第2高周波信号線7bに対向する部分のベース基板2の厚さが薄くなるので、リード線9を通過する際の高周波信号の回り込みの発生を抑えることが可能になり、高周波特性を向上させることができる。このとき、ベース基板2は部分的に薄くなるだけであり、ベース基板2が全体的に薄くなることは防止されるので、ベース基板2の機械的な強度を維持することができる。

#### 【0021】

また、ベース基板2は、第2高周波信号線7bに対向し第2高周波信号線7bから離間する凹部2aを有していることから、簡単な構成により、フレーム5aの下方を通過する第2高周波信号線7bをマイクロストリップ線路部として構成することができ、さらに、ベース基板2を第2高周波信号線7bから離間するように容易に形成することができる。20

#### 【0022】

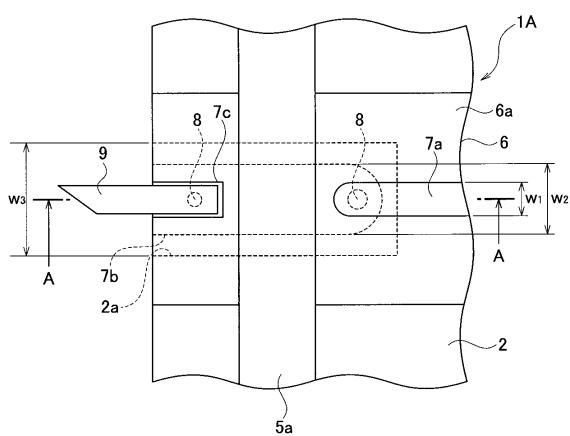

ここで、図2に示すように、第1高周波信号線7aの幅をW1とし、第2高周波信号線7bの幅をW2とし、凹部2aの幅をW3とし、図3に示すように、接栓基板6の誘電率を $\epsilon_1$ とし、空気の誘電率を $\epsilon_2$ とし、接栓基板6の厚さをt1とし、凹部2aの深さ、すなわち空気層の厚さをt2とした場合、特性インピーダンスを50Ωに設定して半導体パッケージ1Aを設計すると、図4に示す実施例のように、各種の設計値が求められる。なお、図4に示す比較例では、図7に示す従来の半導体パッケージを用いる。30

#### 【0023】

図4に示すように、実施例では、高周波信号線(第2の高周波信号線7b)の幅W2は0.644mmであり、比較例では、高周波信号線(三導体部106a:図7参照)の幅は0.148mmである。さらに、実施例では、地導体の幅は凹部2aの幅W3となり、3.0mmであり、比較例では、地導体の幅は無限大(ベース基板102の幅:図7参照)となる。このように半導体パッケージ1Aによれば、ストリップ線路の線路幅より格段に幅広に高周波信号線を設計することが可能になるので、接栓部の許容電流を大きくすることができ、加えて、第3高周波信号線7cの幅がW1以上W2以下の範囲で設計可能になるので、リード線9の取付け強度を増加させることができる。さらに、空気層の厚さt2の分だけ地導体の幅を短くすることが可能になり、良好な高周波特性を得ることができる。40

#### 【0024】

##### (第2の実施の形態)

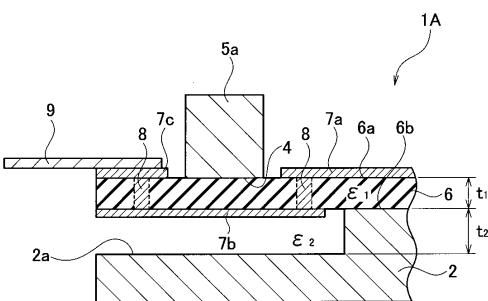

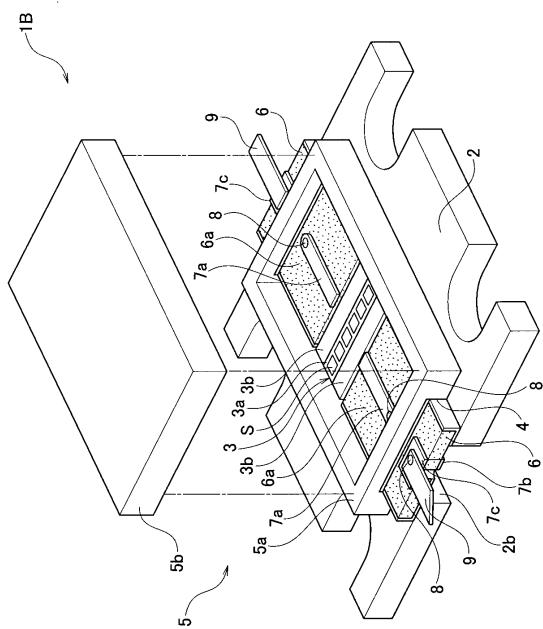

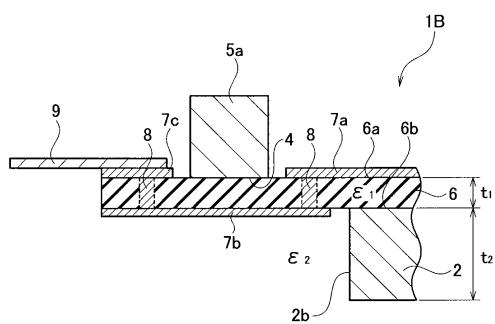

本発明の第2の実施の形態について図5及び図6を参照して説明する。

#### 【0025】

第2の実施の形態では、第1の実施の形態と異なる部分について説明する。なお、第1の実施の形態で説明した部分と同一部分は同一符号で示し、その説明は省略する。

#### 【0026】

図5及び図6に示すように、本発明の第2の実施の形態に係る半導体パッケージ1Bが備えるベース基板2には、第1の実施の形態に係る凹部2aに代えて、第2高周波信号線50

7 b から離間する切欠部 2 b が設けられている。これにより、接栓基板 6 がベース基板 2 上に設けられた場合、ベース基板 2 が第 2 高周波信号線 7 b に接触することが防止される。

#### 【 0 0 2 7 】

切欠部 2 b は、第 2 高周波信号線 7 b に対向する領域を含み第 2 高周波信号線 7 b より大きい領域を有するベース基板 2 の一部分を切り欠くように形成されている。この切欠部 2 b により、第 2 高周波信号線 7 b に対向する位置にベース基板 2 が存在しなくなる。

#### 【 0 0 2 8 】

以上説明したように、本発明の第 2 の実施の形態によれば、第 1 の実施の形態と同様な効果を得ることができる。さらに、切欠部 2 b をベース基板 2 に設けることによって、第 2 高周波信号線 7 b に対向する位置にベース基板 2 が存在しなくなるので、第 1 の実施の形態に比べ、リード線 9 を通過する際の高周波信号の回り込みの発生をより確実に抑えることができる。また、リード線 9 を第 2 高周波信号線 7 b に直接接続することも可能になり、この場合には、第 3 高周波信号線 7 c を不要とすることができる。

#### 【 0 0 2 9 】

また、ベース基板 2 は、第 2 高周波信号線 7 b から離間する切欠部 2 b を有していることから、簡単な構成により、フレーム 5 a の下方を通過する第 2 高周波信号線 7 b をマイクロストリップ線路部として構成することができ、さらに、ベース基板 2 を第 2 高周波信号線 7 b から離間するように容易に形成することができる。

#### 【 0 0 3 0 】

##### ( 他の実施の形態 )

なお、本発明は、前述の実施の形態に限るものではなく、その要旨を逸脱しない範囲において種々変更可能である。

#### 【 0 0 3 1 】

例えば、前述の実施の形態においては、各種の数値を挙げているが、それらの数値は例示であり、限定されるものではない。

#### 【 0 0 3 2 】

また、前述の実施の形態においては、スルーホール配線 8 により接栓基板 6 の第 1 表面 6 a 上の第 3 高周波信号線 7 c に第 2 高周波信号線 7 b を電気的に接続し、第 3 高周波信号線 7 c にリード線 9 を接続しているが、これに限るものではなく、例えば、第 3 高周波信号線 7 c を設けずに、第 2 高周波信号線 7 b にリード線 9 を接続するようにしてもよい。

#### 【 図面の簡単な説明 】

#### 【 0 0 3 3 】

【 図 1 】本発明の第 1 の実施の形態に係る半導体パッケージの概略構成を分解して示す分解斜視図である。

【 図 2 】図 1 に示す半導体パッケージの一部を示す平面図である。

【 図 3 】図 2 の A - A 線断面図である。

【 図 4 】特性インピーダンスを 50 Ω に設定した場合の半導体パッケージの各種設計値を示す説明図である。

【 図 5 】本発明の第 2 の実施の形態に係る半導体パッケージの概略構成を分解して示す分解斜視図である。

【 図 6 】図 4 に示す半導体パッケージの一部を示す断面図である。

【 図 7 】先行技術に係る半導体パッケージの一部を示す斜視図である。

#### 【 符号の説明 】

#### 【 0 0 3 4 】

1 A , 1 B ... 半導体パッケージ、2 ... ベース基板、4 ... 開口部、5 ... 覆い部材、6 ... 接栓基板、6 a ... 第 1 表面、6 b ... 第 2 表面、7 a ... 第 1 高周波信号線、7 b ... 第 2 高周波信号線、S ... 半導体素子

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

|                          | 実施例        | 比較例   |

|--------------------------|------------|-------|

| 接栓基板の誘電率 $\varepsilon_1$ | 9.0        | 9.0   |

| 接栓基板の厚さ $t_1$ (mm)       | 0.4        | 0.4×2 |

| 空気層の厚さ $t_2$ (mm)        | 0.5        | —     |

| 高周波信号線の幅(mm)             | 0.644(=W2) | 0.148 |

| 地導体の幅(mm)                | 3.0(=w3)   | 無限大   |

【図5】

【図6】

【図7】

---

フロントページの続き

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 山本 文朗

神奈川県横浜市磯子区新磯子町33番地 株式会社東芝 生産技術センター内

審査官 日比野 隆治

(56)参考文献 特開平05-121913(JP, A)

特開平11-074396(JP, A)

特開2001-035948(JP, A)

特開2003-249596(JP, A)

特開2001-144222(JP, A)

実開平03-090503(JP, U)

実開昭63-115228(JP, U)

(58)調査した分野(Int.Cl., DB名)

H01L 23/02

H01L 23/04

H01L 23/12

H01P 3/08