(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5063066号

(P5063066)

(45) 発行日 平成24年10月31日(2012.10.31)

(24) 登録日 平成24年8月17日(2012.8.17)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 27/12  | (2006.01) | HO1L 27/12 | B    |

| HO1L 21/02  | (2006.01) | GO6K 19/00 | H    |

| GO6K 19/07  | (2006.01) | GO6K 19/00 | K    |

| GO6K 19/077 | (2006.01) | HO1L 21/56 | R    |

| HO1L 21/56  | (2006.01) | HO1L 29/78 | 619A |

請求項の数 11 (全 33 頁) 最終頁に続く

(21) 出願番号

特願2006-262010 (P2006-262010)

(22) 出願日

平成18年9月27日 (2006.9.27)

(65) 公開番号

特開2007-123859 (P2007-123859A)

(43) 公開日

平成19年5月17日 (2007.5.17)

審査請求日 平成21年9月3日 (2009.9.3)

(31) 優先権主張番号 特願2005-288141 (P2005-288141)

(32) 優先日 平成17年9月30日 (2005.9.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100108741

弁理士 渡邊 順之

(72) 発明者 渡邊 了介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

基板の一方の面上に複数の素子群を形成し、

前記複数の素子群を覆うように絶縁膜を形成し、

前記複数の素子群において隣り合う2つの素子群間の領域に設けられた前記絶縁膜に開口部を選択的に形成して前記基板を露出させ、

前記絶縁膜および前記開口部を覆うように第1のフィルムを設け、

前記基板を除去して前記素子群を露出させ、

前記露出した素子群の表面を覆うように第2のフィルムを設け、

前記絶縁膜が露出しないように前記複数の素子群の間を切断することを特徴とする半導

10

体装置の作製方法。

## 【請求項2】

基板の一方の面上に下地膜を形成し、

前記下地膜上に複数の素子群を形成し、

前記複数の素子群を覆うように絶縁膜を形成し、

前記複数の素子群において隣り合う2つの素子群間の領域に設けられた前記絶縁膜に開口部を選択的に形成して前記基板または前記下地膜を露出させ、

前記絶縁膜および前記開口部を覆うように第1のフィルムを設け、

前記基板を除去して前記下地膜を露出させ、

前記露出した下地膜の表面を覆うように第2のフィルムを設け、

前記絶縁膜が露出しないように前記複数の素子群の間を切斷することを特徴とする半導体装置の作製方法。

【請求項 3】

基板の一方の面上に複数の素子群を形成し、

前記複数の素子群を覆うように絶縁膜を形成し、

前記複数の素子群において隣り合う 2 つの素子群間の領域に設けられた前記絶縁膜に開口部を選択的に形成して前記基板を露出させ、

前記絶縁膜および前記開口部を覆うように第 1 のフィルムを設け、

前記基板の他方の面から前記基板を薄膜化し、

前記薄膜化した基板を化学反応処理により除去して前記素子群を露出させ、

前記露出した素子群の表面を覆うように第 2 のフィルムを設け、

前記絶縁膜が露出しないように前記複数の素子群の間を切斷することを特徴とする半導体装置の作製方法。

【請求項 4】

基板の一方の面上に下地膜を形成し、

前記下地膜上に複数の素子群を形成し、

前記複数の素子群を覆うように絶縁膜を形成し、

前記複数の素子群において隣り合う 2 つの素子群間の領域に設けられた前記絶縁膜に開口部を選択的に形成して前記基板または前記下地膜を露出させ、

前記絶縁膜および前記開口部を覆うように第 1 のフィルムを設け、

前記基板の他方の面から前記基板を薄膜化し、

前記薄膜化した基板を化学反応処理により除去して前記下地膜を露出させ、

前記露出した下地膜の表面を覆うように第 2 のフィルムを設け、

前記絶縁膜が露出しないように前記複数の素子群の間を切斷することを特徴とする半導体装置の作製方法。

【請求項 5】

請求項 3 または請求項 4 において、

前記基板の薄膜化は、研削処理、研磨処理の一方または両方により行うことを特徴とする半導体装置の作製方法。

【請求項 6】

請求項 3 乃至請求項 5 のいずれか一項において、

前記化学反応処理は、前記薄膜化した基板を薬液に浸すことにより行うことを特徴とする半導体装置の作製方法。

【請求項 7】

請求項 2 または請求項 4 において、

前記下地膜を、窒化物で形成することを特徴とする半導体装置の作製方法。

【請求項 8】

請求項 1 乃至請求項 7 のいずれか一項において、

前記開口部は、レーザ光を照射することにより形成することを特徴とする半導体装置の作製方法。

【請求項 9】

請求項 1 乃至請求項 8 のいずれか一項において、

前記基板として、ガラス基板を用いることを特徴とする半導体装置の作製方法。

【請求項 10】

請求項 1 乃至請求項 9 のいずれか一項において、

前記第 1 のフィルムの材料として、前記絶縁膜の材料より弾性率が低い材料を用いることを特徴とする半導体装置の作製方法。

【請求項 11】

請求項 1 乃至請求項 10 のいずれか一項において、

前記第 1 のフィルムの材料として、ポリプロピレン、ポリエチレン、ビニル、ポリフッ

10

20

30

40

50

化ビニル、又はポリ塩化ビニルを用い、

前記第2のフィルムの材料として、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、又はポリ塩化ビニルを用いることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の作製方法に関し、特に支持基板上にトランジスタ等の半導体素子を形成した後に当該支持基板を除去する半導体装置の作製方法に関する。

【背景技術】

【0002】

10

近年、ガラス等の剛性を有する基板上に半導体素子を形成することによって、LCD、有機ELディスプレイなどのディスプレイ、及びフォトセンサー、太陽電池などの光電変換素子等の用途としての半導体装置等の開発が盛んに行われている。また、他にも、非接触でデータを送受信する半導体装置（RFIDタグ（Radio Frequency Identification）タグ、IDタグ、ICタグ、ICチップ、無線タグ、電子タグ、無線チップともよばれる）の開発が盛んに進められている。また、最近では、フィルム状のディスプレイや紙に漉き込んだ半導体装置等のフレキシブルなデバイスが求められており、半導体装置の薄膜化が重要な鍵を握っている。

【0003】

20

半導体装置の薄膜化を実現するために、例えば、あらかじめ薄膜化した基板を用いる方法があるが、この場合、基板の反り等の問題や、素子を扱う際に、応力の反り、ハンドリングの困難性、リソグラフィーや印刷工程における位置ずれ等の問題が生じる。そのため、一般的に、基板に半導体素子を作製した後に当該基板を薄膜化または除去する方法が用いられている。

【0004】

例えば、基板の薄膜化または除去する方法として、研削処理や研磨処理、または化学反応によるウェットエッチングで支持基板（ガラス基板）を除去する技術がある（例えば、特許文献1参照）。

【特許文献1】特開2002-87844号公報

【発明の開示】

30

【発明が解決しようとする課題】

【0005】

しかしながら、半導体素子が形成された基板を研削処理または研磨処理によって除去する場合、装置の精度と研磨の面内均一性の限界により薄膜化の限界があり、全面を厚さ50μm以下にすることは難しく、基板を除去することは困難であった。また、基板に研削処理および研磨処理を行った場合、当該基板上に設けられた半導体素子に応力が加わることにより半導体素子が破損する恐れがある。これは、基板が薄くなればなるほど、半導体素子へ加わる応力が顕著となるため、研削処理または研磨処理によって基板を除去することは困難であった。

【0006】

40

また、半導体素子が形成された基板を化学処理により除去する場合、歩留まり高く均一に基板のみを除去することは非常に難しく、処理に非常に時間がかかるという問題があった。

【0007】

本発明は上記問題を鑑み、支持基板上に半導体素子を設けた後に当該支持基板の薄膜化または除去を行う場合であっても、半導体素子の損傷を防ぎ且つ処理速度を向上させた半導体装置の作製方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の半導体装置の作製方法は、基板の一方の面上に複数の素子群を形成し、複数の

50

素子群を覆うように絶縁膜を形成し、複数の素子群において隣り合う2つの素子群間の領域に位置する絶縁膜に選択的に開口部を形成して基板を露出させ、絶縁膜および開口部を覆うように第1のフィルムを形成し、基板を除去して素子群を露出させ、露出した素子群の表面を覆うように第2のフィルムを形成し、絶縁膜が露出しないように複数の素子群の間を切断することを特徴としている。

#### 【0009】

また、本発明の半導体装置の他の作製方法は、基板の一方の面上に下地膜を形成し、下地膜上に複数の素子群を形成し、複数の素子群を覆うように絶縁膜を形成し、複数の素子群において隣り合う2つの素子群間の領域に位置する絶縁膜に選択的に開口部を形成して基板または下地膜を露出させ、絶縁膜および開口部を覆うように第1のフィルムを形成し、基板を除去して下地膜を露出させ、露出した下地膜の表面を覆うように第2のフィルムを形成し、絶縁膜が露出しないように複数の素子群の間を切断することを特徴としている。

10

#### 【0010】

また、本発明の半導体装置の他の作製方法は、上記構成において、基板の除去を、基板の他方の面から当該基板を薄膜化した後に、薄膜化した基板を化学反応を用いた化学処理（化学反応処理（以下、単に「化学処理」とも記す））により除去することを特徴としている。なお、基板の薄膜化は、物理的手段又は物理的手段と化学的手段を併用した方法を用いることができ、例えば、研削処理、研磨処理の一方または両方を用いることができる。化学処理は、例えば、薄膜化した基板を薬液に浸すことによって、当該薄膜化した基板に化学反応を起こさせることにより行うことができる。

20

#### 【発明の効果】

#### 【0011】

本発明により、半導体素子が形成された基板の除去を行う場合であっても、当該半導体素子にダメージを与えることを防ぐことができる。その結果、半導体装置の処理速度を向上させることが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0012】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用い説明を省略する場合がある。

30

#### 【0013】

##### (実施の形態1)

本実施の形態では、本発明の半導体装置の作製方法の一例に関して図面を参照して説明する。

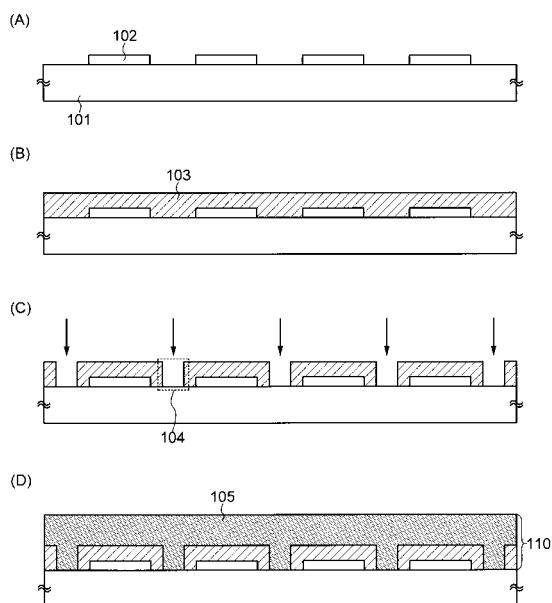

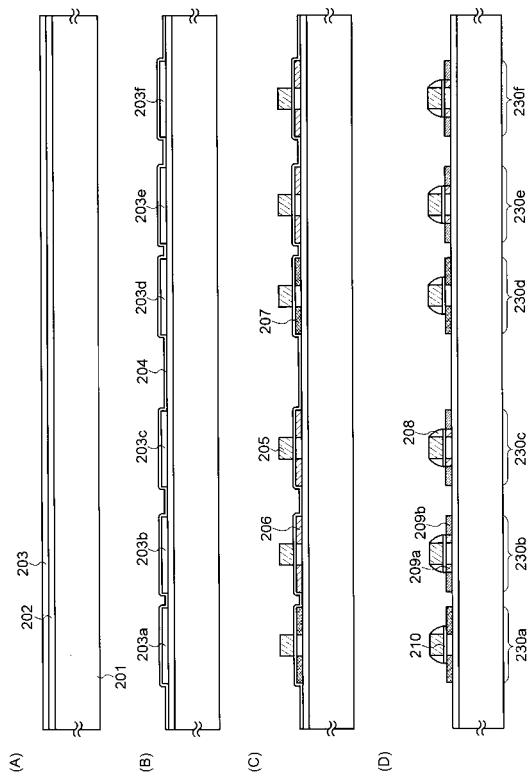

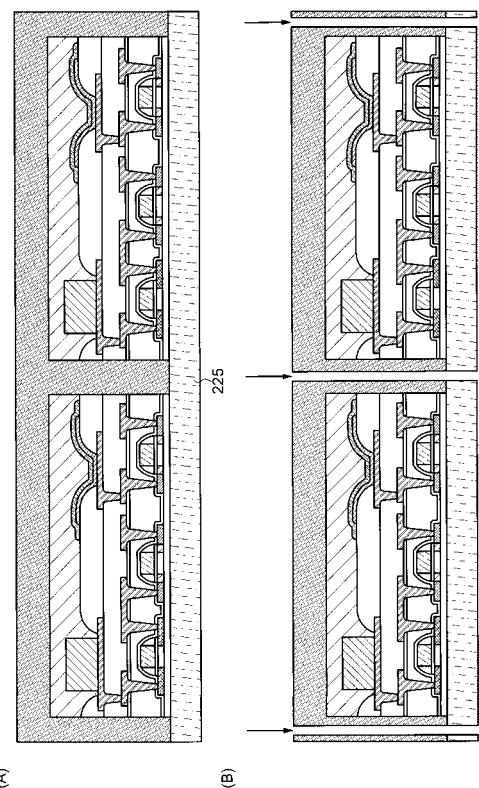

#### 【0014】

まず、基板101上に素子群102を形成する（図1（A））。本実施の形態では、基板101上に半導体装置を構成する素子群102を複数設ける。素子群102を基板101上に複数形成することにより、1枚の基板から複数の半導体装置を作製することができるため好ましい。

40

#### 【0015】

基板101としては、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶縁膜を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとよい。このような基板101であれば、その面積や形状に大きな制限はないため、基板101として、例えば、1辺が1メートル以上であって、矩形状のものを用いれば、生産性を格段に向上させることができる。また、他にも、Si等の半導体基板を用いてもよい。

50

## 【0016】

素子群102としては、例えば、トランジスタやダイオード等の半導体素子から構成されている。トランジスタとしては、ガラス等の剛性を有する基板上に形成された半導体膜をチャネルとして利用する薄膜トランジスタ(TFT)、Si等の半導体基板上に当該基板をチャネルとして利用する電界効果型トランジスタ(FET)または有機材料をチャネルとして利用する有機TFT等で設けることができる。また、ダイオードとしては、可変容量ダイオード、ショットキーダイオードまたはトンネルダイオード等の各種ダイオードを適用することができる。本発明では、これらのトランジスタやダイオード等を用いることによって、CPU、メモリ、マイクロプロセッサまたは温度センサー、湿度センサーまたはバイオセンサー等の各種センサー等のありとあらゆる集積回路を設けることができる。10

また、素子群102は、トランジスタ等の半導体素子に加えてアンテナを有する形態もとりうる。素子群102にアンテナを設けた半導体装置は、アンテナで発生した交流の電圧を用いて動作を行い、またアンテナに印加する交流の電圧を変調することによって、非接触で外部機器(リーダ/ライタ)とデータの送受信を行うことが可能となる。なお、アンテナは、トランジスタを有する集積回路とともに形成してもよいし、集積回路とは別個に形成した後に電気的に接続するように設けてもよい。

## 【0017】

次に、素子群102を覆うように絶縁膜103を形成する(図1(B))。絶縁膜103は、複数の素子群102の上方及び素子群と素子群の間に設けられ、素子群102の保護膜として機能する。20

## 【0018】

絶縁膜103としては、酸化珪素(SiO<sub>x</sub>)膜、窒化珪素(SiN<sub>x</sub>)膜、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)膜等の酸素または窒素を有する絶縁膜、DLC(ダイヤモンドライクカーボン)膜等の炭素を含む膜や、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。なお、シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。30

## 【0019】

次に、絶縁膜103に選択的に開口部104を形成する(図1(C))。開口部104は、複数の素子群102の間(ここでは、隣接する素子群102同士の間)にレーザ光を照射したり、フォトリソグラフィ法を用いたりすることによって選択的に形成する。なお、開口部104は、素子群102を避けた部分に形成し、ここでは、素子群と素子群の間にレーザ光を照射することにより線状に形成する。従って、開口部104の形成により素子群102が露出しないことが好ましい。

## 【0020】

次に、絶縁膜103および開口部104を覆うようにフィルム105を形成する(図1(D))。フィルム105を設けることにより、基板101から素子群102、絶縁膜103およびフィルム105からなる層(以下、「素子形成層110」と記す)を分離した際に、応力により素子形成層110が変形することを防ぐことができる。また、ここでは、開口部104の一部又は全部を充填するようにフィルム105を形成することが好ましい。40

## 【0021】

フィルム105としては、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、纖維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルム等を利用することができる。また、50

フィルムは、加熱処理および加圧処理が行われることにより被処理物に接着されるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、または最外層に設けられた層（接着層ではない）を加熱処理によって溶かし、加圧により接着する。また、フィルムの表面には接着層が設けられていてもよいし、接着層が設けられていなくてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。また、封止後に内部への水分等の侵入を防ぐために封止するフィルムにシリカコートを行うことが好ましく、例えば、接着層とポリエステル等のフィルムとシリカコートを積層させたシート材を利用することができる。従って、これらのフィルムの接着層が開口部 104 の一部又は全部を充填するように設けられる。

## 【0022】

また、接着層としてホットメルト接着剤を用いることができる。ホットメルト接着剤は、水や溶剤を含まず、室温では固体で不揮発性の熱可塑性材料からなり、溶融状態で塗布し冷却することにより物と物を接着する化学物質である。また、接着時間が短く、無公害、安全で衛生的、省エネルギーであり、低コストであるといった利点を有する。ホットメルト接着剤は常温で固体であるため、あらかじめフィルム状、纖維状に加工したもの、またはポリエステル等のベースフィルム上にあらかじめ熱可塑性樹脂を含む接着層を形成してフィルム状にしたものを用いることができる。ここでは、ポリエチレンテレフタレートからなるベースフィルム上にホットメルトフィルムを形成したフィルムを用いる。ホットメルトフィルムは、ベースフィルムよりも軟化点の低い樹脂からなっており、加熱することによってホットメルトフィルムのみが溶融してゴム状になり被接着物と接着し、冷却すると硬化する。ホットメルトフィルムとしては、例えばエチレン・酢酸ビニル共重合体（EVA）系、ポリエステル系、ポリアミド系、熱可塑性エラストマー系、ポリオレフィン系等を主成分としたフィルムを用いることができる。

## 【0023】

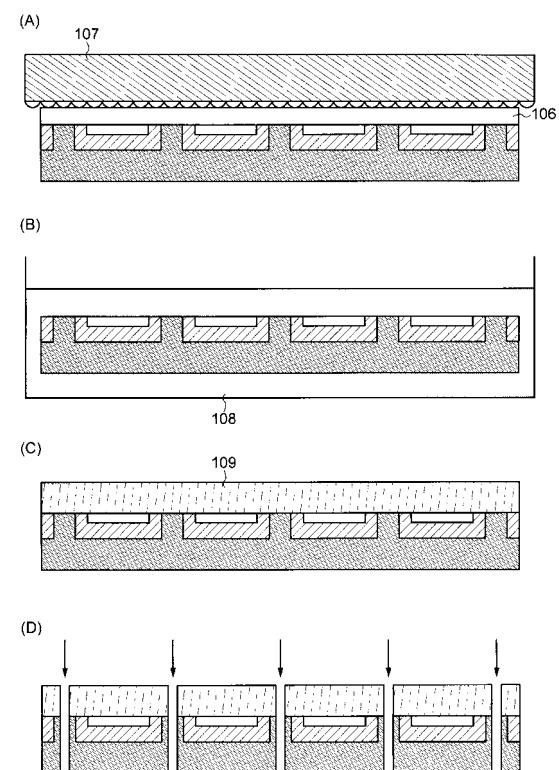

次に、基板 101 を薄膜手段 107 により薄膜化する（図 2（A））。ここでは、素子群 102 が形成された基板 101 の面と反対側の面（裏面）から基板 101 の薄膜化を行うことによって、基板 101 を薄膜化して基板 106 とする。基板 101 を薄膜化する場合には、後の工程（化学処理によるエッティング）での処理時間を短縮するためできるだけ薄くすることが好ましいが、基板 101 が薄くなるにつれて素子形成層 110 に応力が加わり破損しやすくなる。そのため、基板 106 の厚さが 5 μm ~ 50 μm、好ましくは 5 μm ~ 20 μm、より好ましくは 5 μm ~ 10 μm とする。

## 【0024】

薄膜手段 107 としては、物理的手段又は物理的手段と化学的手段を併用した方法を用いることができ、例えば、研削処理、研磨処理等を用いることができる。研削処理は、砥石の粒子を用いて被処理物の表面（ここでは、基板 101 の裏面）を削り取り平滑にする。研磨処理は、研磨布紙や研磨砥粒等の研磨材を用いて被処理物の表面を塑性的平滑作用または摩擦的みがき作用によって平滑にする。研削処理、研磨処理を行う場合に純水や研磨溶液等を用いることができる。また、研磨処理としては、C M P (Chemical Mechanical Polishing) を用いてもよい。

## 【0025】

本実施の形態では、基板 101 の裏面に研削処理を行い、その後さらに基板 101 の裏面に研磨処理を行うことによって基板 101 を薄膜化し、基板 106 とする。なお、研削処理、研磨処理の一方のみを行っても良い。基板 101 に研削処理、研磨処理の一方または両方を行う場合にはできるだけ基板 101 を薄くすることが好ましいが、基板 101 が薄くなるにつれて素子形成層 110 に応力が生じやすくなり、クラック等により破損する恐れがでてくる。

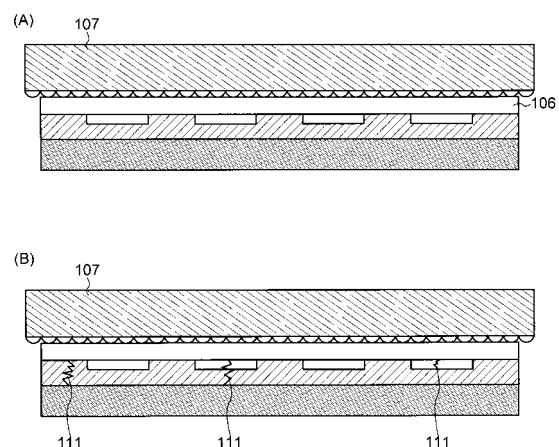

## 【0026】

一般に、図 4 に示すように、開口部 104 を設けずに素子群 102 の上方に絶縁膜 103 およびフィルム 105 を形成して基板 101 に研削処理や研磨処理を行う場合（図 4（A））、素子形成層 110 に応力が生じた場合には素子群 102 や絶縁膜 103 にクラッ

10

20

30

40

50

ク 1 1 1 が生じる（図 4（B））。

【0027】

一方、本実施の形態で示す作製方法では、基板 101 に研削処理や研磨処理を行う前の段階で複数の素子群 102 の間（ここでは隣り合う素子群 102 の間）に開口部 104 を形成し、当該開口部にフィルム 105 を設けた構造となっている。そのため、研削処理や研磨処理により素子形成層 110 に応力が発生した場合に素子群 102 や絶縁膜 103 に加わる応力が分散され素子群 102 にクラックが生じにくくなるという利点がある。また、応力が生じた場合に、開口部 104 に設けられたフィルム 105 に選択的に応力が加われば効果的に素子群 102 の破損を抑制することができる。そのため、素子群 102 を覆う絶縁膜 103 とフィルム 105 の材料を考慮し、例えば、フィルム 105 を素子群 102 や絶縁膜 103 に比較して曲がりやすい物質で形成することが好ましい。10

【0028】

フィルム 105 に用いる物質としては、素子群 102 や絶縁膜 103 と比較して曲がりやすい性質を有する物質であればよく、例えば、弾性を示す物質や塑性を有する物質を用いることができる。なお、フィルム 105 として、弾性を示す物質を用いる場合には、フィルム 105 に用いる物質の弾性率（応力 / ひずみの比）を絶縁膜 103 に用いる物質の弾性率より低くなるように設ける。また、フィルム 105 として塑性を有する物質を用いる場合には、絶縁膜 103 に用いる物質より塑性を有するように設ける。なお、ここでいう弾性とは、外力によって形や体積に変化を生じた物体が、力を取り去ると再びもとの状態に回復する性質をいう。また、ここでいう塑性とは、外力によって変形しやすく、力を取り去ってもひずみが残る性質をいう。20

【0029】

また、絶縁膜 103 やフィルム 105 としてガラス転移温度を有する高分子等の有機化合物を用いる場合には、フィルム 105 に用いる物質のガラス転移点を絶縁膜 103 に用いる物質のガラス転移より低くするように設ける。ガラス転移点が低い物質は、ガラス転移点が高い物質と比較して粘弾性が高くなるため、ガラス転移点が低い物質とガラス転移点が高い物質とを設けた場合、応力が加わった際にガラス転移点が低い物質に選択的に大きいひずみが生じるため、絶縁膜 103 に覆われている素子群 102 の破損を抑制することができる。

【0030】

次に、薄膜化された基板 106 に化学処理を行うことにより基板 106 を除去する（図 2（B））。化学処理は、薬液を用いて被処理物に化学エッティングを行う。ここでは、薬液 108 に基板 106 および素子形成層 110 を浸すことによって、基板 106 のエッティングを行う。薬液 108 は基板を除去できるものであればよく、例えば、基板 101 としてガラス基板を用いる場合には、薬液 108 として弗化水素酸を含む溶液を用いることが好ましい。なお、フィルム 105 は、薬液 108 と反応しにくい材料を用いることが好ましい。また、基板 101 と素子群 102 の間に薬液 108 と反応しにくい材料で下地膜を形成しておいてもよい。基板 101 としてガラス基板を用い、ガラス基板を弗化水素酸に浸して除去する場合には、下地膜として窒化物で設けることが好ましく、例えば、窒化珪素（SiNx）膜、酸化窒化珪素（SiOxNy）（x > y）膜、窒化酸化珪素（SiN<sub>x</sub>O<sub>y</sub>）（x > y）膜等の窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。30

【0031】

なお、上記工程において、基板 101 を研削処理および研磨処理により除去してもよいが、基板 101 が薄膜化した状態で研削処理または研磨処理を行う場合、均一に薄膜化するのが難しく、また、素子形成層 110 に応力が生じて破損する確率が高くなる。一方、研削処理および研磨処理を行わずに化学処理を用いて基板 101 を除去してもよいが、この場合、基板 101 の除去に時間を要し処理速度の低下が懸念される。また、素子形成層 110 を長時間薬液に浸しておくことによって、素子形成層に悪影響を及ぼす恐れもある。

## 【0032】

そのため、本発明では、基板101を除去する際に、一度研削処理、研磨処理等を行い、ある程度基板を薄膜化した後に、化学処理を用いて薄膜化された基板の除去を行う。従って、素子形成層に加わる応力等を抑制し、且つ処理速度の向上を図ることができる。

## 【0033】

次に、素子形成層110の一方の面（基板101が除去された面）にフィルム109を形成して、素子形成層110に封止処理を行う（図2（C））。

## 【0034】

フィルム109としては、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、ポリ塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム（ポリエステル、ポリアミド、無機蒸着フィルム、紙類等）と接着性合成樹脂フィルム（アクリル系合成樹脂、エポキシ系合成樹脂等）との積層フィルム等を利用することができます。また、フィルムは、加熱処理および加圧処理が行われることにより被処理物に接着されるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、または最外層に設けられた層（接着層ではない）を加熱処理によって溶かし、加圧により接着する。また、フィルムの表面には接着層が設けられていてもよいし、接着層が設けられていてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。また、封止後に内部への水分等の侵入を防ぐために封止するフィルムにシリカコートを行うことが好ましく、例えば、接着層とポリエステル等のフィルムとシリカコートを積層させたシート材を利用することができます。10 20

## 【0035】

また、接着層としてホットメルト接着剤を用いることができる。ホットメルト接着剤は、水や溶剤を含まず、室温では固体で不揮発性の熱可塑性材料からなり、溶融状態で塗布し冷却することにより物と物を接着する化学物質である。また、接着時間が短く、無公害、安全で衛生的、省エネルギーであり、低コストであるといった利点を有する。ホットメルト接着剤は常温で固体であるため、あらかじめフィルム状、繊維状に加工したもの、またはポリエステル等のベースフィルム上にあらかじめ熱可塑性樹脂を含む接着層を形成してフィルム状にしたもの用いることができる。ここでは、ポリエチレンテレフタレートからなるベースフィルム上にホットメルトフィルムを形成したフィルムを用いる。ホットメルトフィルムは、ベースフィルムよりも軟化点の低い樹脂からなっており、加熱することによってホットメルトフィルムのみが溶融してゴム状になり被接着物と接着し、冷却すると硬化する。ホットメルトフィルムとしては、例えばエチレン・酢酸ビニル共重合体（EVA）系、ポリエステル系、ポリアミド系、熱可塑性エラストマー系、ポリオレフィン系等を主成分としたフィルムを用いることができる。30

## 【0036】

次に、素子形成層110およびフィルム109を切断して、基板101上に設けられた複数の素子群を個々の素子群に分断する（図2（D））。この際に、絶縁膜103が露出せずに、フィルム105およびフィルム109が露出するように分断することが好ましい。これは、絶縁膜103が露出すると絶縁膜103に水分や不純物元素が混入し素子群102の特性が悪化するためである。40

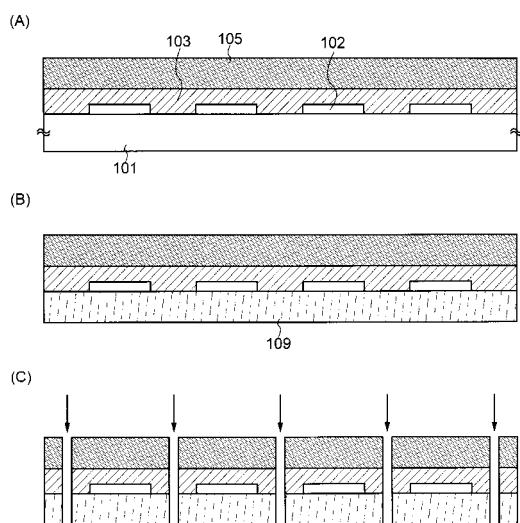

## 【0037】

一般に、図3（A）～（C）に示すように、開口部104を設けずに素子群102の上方に絶縁膜103およびフィルム105を形成して（図3（A））、基板101を除去してフィルム109を形成した（図3（B））後に、基板101上に設けられた複数の素子群を個々の素子群に分断した場合（図3（C））、側面において絶縁膜103が露出した構造となってしまう。一方、本実施の形態で示す作製方法を用いて得られた半導体装置は、基板101を除去する前の段階で複数の素子群102の間に開口部104を形成し、当該開口部にフィルム105を設けた構造とするため、図2（D）に示すように個々の素子に分断した場合に素子群102および絶縁膜103をフィルム105およびフィルム109で覆った構造とすることができます。より具体的には、絶縁膜103とフィルム109に50

より素子群 102 が露出せずに覆われており、且つフィルム 105 とフィルム 109 により絶縁膜 103 が露出せずに覆われた構造となっている。その結果、素子群 102 や絶縁膜 103 に水分や不純物元素が混入することを抑制し、半導体装置の信頼性を向上させることができる。

#### 【0038】

以上の工程により、半導体装置を形成することができる。

#### 【0039】

##### (実施の形態 2 )

本実施の形態では、上記実施の形態とは異なる半導体装置の作製方法について図面を参照して説明する。具体的には、薄膜トランジスタ、記憶素子およびアンテナを含む本発明の半導体装置の作製方法について、図面を参照して説明する。10

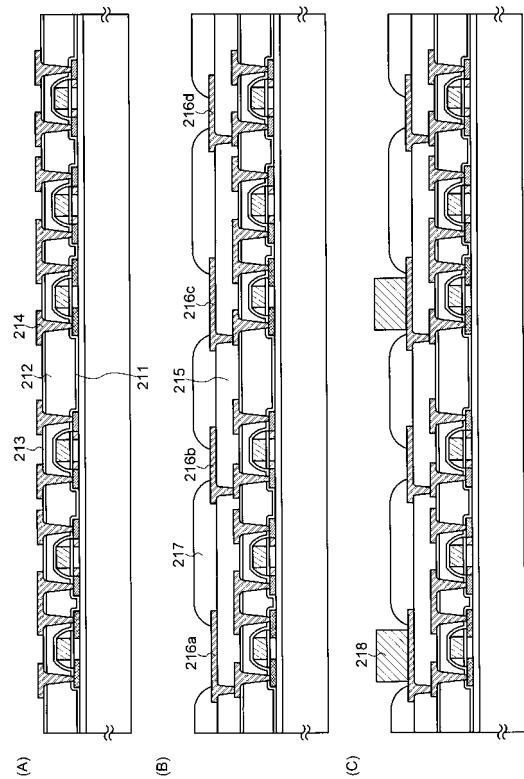

#### 【0040】

まず、基板 201 の一表面に下地となる絶縁膜 202 を形成し、当該絶縁膜 202 上に半導体膜 203 を形成する(図 5(A))。なお、絶縁膜 202 および半導体膜 203 は、連続して形成することができる。

#### 【0041】

基板 201 は、ガラス基板、石英基板、金属基板やステンレス基板の一表面に絶縁膜を形成したもの、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとい。このような基板 201 であれば、その面積や形状に大きな制限はないため、基板 201 として、例えば、1 辺が 1 メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。また、他にも、Si 等の半導体基板を用いてもよい。20

#### 【0042】

絶縁膜 202 は、CVD 法やスパッタ法等により、酸化珪素(SiO<sub>x</sub>)膜、窒化珪素(SiN<sub>x</sub>)膜、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x > y)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x > y)膜等の酸素または窒素を有する絶縁膜の単層構造、またはこれらの積層構造で設けることができる。下地となる絶縁膜が 2 層構造の場合、例えば、1 層目として窒化酸化珪素膜を形成し、2 層目として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜が 3 層構造の場合、1 层目として酸化珪素膜を形成し、2 层目として窒化酸化珪素膜を形成し、3 层目として酸化窒化珪素膜を形成するとよい。または、1 层目として酸化窒化珪素膜を形成し、2 层目として窒化酸化珪素膜を形成し、3 层目として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜は、基板 201 からの不純物の侵入を防止するプロッキング膜として機能する。30

#### 【0043】

半導体膜 203 としては、非晶質(アモルファス)半導体またはセミアモルファス半導体(SAS)で形成することができる。また多結晶半導体膜を用いていても良い。SAS は、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第 3 の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、0.5 ~ 20 nm の結晶領域を観測することができ、珪素を主成分とする場合にはラマンスペクトルが 520 cm<sup>-1</sup> よりも低波数側にシフトしている。X 線回折では珪素結晶格子に由来するとされる(111)、(220) の回折ピークが観測される。未結合手(ダンギングボンド)を終端させるために水素またはハロゲンを少なくとも 1 原子% またはそれ以上含ませている。SAS は、珪素を含む気体をグロー放電分解(CVD)して形成する。珪素を含む気体としては、SiH<sub>4</sub>、その他にも Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いることが可能である。また GeF<sub>4</sub> を混合させても良い。この珪素を含む気体を H<sub>2</sub>、または、H<sub>2</sub> と He、Ar、Kr、Ne から選ばれた一種または複数種の希ガス元素で希釈してもよい。希釈率は 2 ~ 1000 倍の範囲とし、圧力は概略 0.1 Pa ~ 133 Pa の範囲、電源周波数は 1 MHz ~ 120 MHz、好ましくは 13 MHz ~ 60 MHz、基板加熱温度は 300 以下とすることができます。膜中の不純物元素として、酸素、窒素、炭素などの大気成分の不純物は 1 × 10<sup>-2</sup> atoms/cm<sup>3</sup>40

以下とすることが望ましく、特に、酸素濃度は  $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下とする。ここでは、スパッタ法、CVD法等を用いてシリコン(Si)を主成分とする材料(例えばSi<sub>x</sub>Ge<sub>1-x</sub>等)を用いて25~200nm(好ましくは30~150nm)の厚さで非晶質半導体膜を形成する。

#### 【0044】

次に、非晶質半導体膜203をレーザ結晶化法、RTA又はファーネスアーナー炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法などの結晶化法により結晶化して、結晶質半導体膜を形成する。また、結晶化の方法として、他にも、DCバイアスを印加して熱プラズマを発生することにより、当該熱プラズマを半導体膜に作用させることによって半導体膜の結晶化を行うことも可能である。そして、得られた結晶質半導体膜を所望の形状にエッチングして、結晶質の半導体膜203a~203fを形成し、当該半導体膜203a~203fを覆うようにゲート絶縁膜204を形成する(図5(B))。

#### 【0045】

半導体膜203a~203fの作製工程の一例を以下に簡単に説明すると、まず、プラズマCVD法を用いて、膜厚66nmの非晶質半導体膜を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体膜上に保持させた後、非晶質半導体膜に脱水素化の処理(500、1時間)と、熱結晶化の処理(550、4時間)を行って結晶質半導体膜を形成する。その後、必要に応じてレーザ光を照射し、フォトリソグラフィ法を用いることによって結晶質の半導体膜203a~203fを形成する。

#### 【0046】

レーザ結晶化法で結晶質半導体膜を形成する場合、連続発振型のレーザビーム(CWレーザビーム)やパルス発振型のレーザビーム(パルスレーザビーム)を用いることができる。ここで用いることができるレーザビームは、Arレーザ、Krレーザ、エキシマレーザなどの気体レーザ、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。このときレーザのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度(好ましくは0.1~10MW/cm<sup>2</sup>)が必要である。そして、走査速度を10~2000cm/sec程度として照射する。なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、Arイオンレーザ、またはTi:サファイアレーザは、連続発振をさせることができあり、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザビームを発振させると、半導体膜がレーザによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得ることができる。

#### 【0047】

また、結晶化を助長する金属元素を用いて非晶質半導体膜の結晶化を行うと、低温で短時間の結晶化が可能となるうえ、結晶の方向が揃うという利点がある一方、金属元素が結晶質半導体膜に残存するためにオフ電流が上昇し、特性が安定しないという欠点がある。

10

20

30

40

50

そこで、結晶質半導体膜上に、ゲッタリングサイトとして機能する非晶質半導体膜を形成するとよい。ゲッタリングサイトとなる非晶質半導体膜には、リンやアルゴンの不純物元素を含有させる必要があるため、好適には、アルゴンを高濃度に含有させることができ可能なスパッタ法で形成するとよい。その後、加熱処理（R T A法やファーネスアニール炉を用いた熱アニール等）を行って、非晶質半導体膜中に金属元素を拡散させ、続いて、当該金属元素を含む非晶質半導体膜を除去する。そうすると、結晶質半導体膜中の金属元素の含有量を低減又は除去することができる。

## 【0048】

ゲート絶縁膜204は、CVD法やスパッタ法等により、珪素の酸化物又は珪素の窒化物を含む膜を、単層又は積層して形成する。具体的には、酸化珪素を含む膜、酸化窒化珪素を含む膜、窒化酸化珪素を含む膜を、単層又は積層して形成する。10

## 【0049】

また、ゲート絶縁膜204は、半導体膜203a～203fに対し高密度プラズマ処理を行い、表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素（NO<sub>2</sub>）、アンモニア、窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル（OHラジカルを含む場合もある）や窒素ラジカル（NHラジカルを含む場合もある）によって、半導体膜の表面を酸化又は窒化することができる。20

## 【0050】

このような高密度プラズマを用いた処理により、1～20nm、代表的には5～10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜（結晶性シリコン、或いは多結晶シリコン）を直接酸化（若しくは窒化）するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの結晶粒界でも半導体膜の酸化が強くされることがないため、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相反応することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。20

## 【0051】

ゲート絶縁膜は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それにプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。30

## 【0052】

また、半導体膜に対し、連続発振レーザ若しくは10MHz以上の周波数で発振するレーザビームを照射しながら一方向に走査して結晶化させて得られた半導体膜203a～203fは、そのビームの走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向（チャネル形成領域が形成されたときにキャリアが流れる方向）に合わせてトランジスタを配置し、上記ゲート絶縁膜を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高いトランジスタ（TFT）を得ることができる。40

## 【0053】

次に、ゲート絶縁膜204上に、第1の導電膜と第2の導電膜とを積層して形成する。第1の導電膜は、プラズマCVD法やスパッタ法等により、20～100nmの厚さで形成する。第2の導電膜は、プラズマCVD法やスパッタ法等により、100～400nmの厚さで形成する。第1の導電膜と第2の導電膜は、タンタル（Ta）、タングステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ニオブ（Nb）等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結50

晶珪素に代表される半導体材料により形成する。第1の導電膜と第2の導電膜の組み合わせの例を挙げると、窒化タンタル(TaN)膜とタングステン(W)膜、窒化タングステン(WN)膜とタングステン膜、窒化モリブデン(MoN)膜とモリブデン(Mo)膜等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、第1の導電膜と第2の導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

#### 【0054】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、ゲート電極として機能する導電膜(以下、「ゲート電極205」と記す)を形成する。ここでは、ゲート電極205は、上述したいずれかの材料を積層して設けた構造となっている。

10

#### 【0055】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成して、半導体膜203b、203c、203e、203fに、イオンドープ法又はイオン注入法により、N型を付与する不純物元素を低濃度に添加して、N型不純物領域206を形成する。N型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。

#### 【0056】

次に、フォトリソグラフィ法によりレジストからなるマスクを形成して、半導体膜203a、203dに、P型を付与する不純物元素を添加して、P型不純物領域207を形成する。P型を付与する不純物元素は、例えばボロン(B)を用いる。(図5(C))

20

#### 【0057】

次に、ゲート絶縁膜204とゲート電極205を覆うように、絶縁膜を形成する。絶縁膜は、プラズマCVD法やスパッタ法等により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。次に、絶縁膜を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、ゲート電極205の側面に接する絶縁膜208(サイドウォールともよばれる)を形成する。また、絶縁膜208の作製と同時に、ゲート絶縁膜204がエッチングされた絶縁膜210が形成される。絶縁膜208は、後にLDD(Lightly Doped drain)領域を形成する際のドーピング用のマスクとして用いる。

30

#### 【0058】

次に、フォトリソグラフィ法により形成したレジストからなるマスクと、絶縁膜208をマスクとして用いて、半導体膜203b、203c、203e、203fにN型を付与する不純物元素を添加して、第1のN型不純物領域209a(LDD領域ともよぶ)と、第2のN型不純物領域209bとを形成する。第1のN型不純物領域209aが含む不純物元素の濃度は、第2のN型不純物領域209bの不純物元素の濃度よりも低い。上記工程を経て、N型の薄膜トランジスタ230b、230c、230e、230fと、P型の薄膜トランジスタ230a、230dが完成する(図5(D))。

40

#### 【0059】

なお、LDD領域を形成するためには、ゲート電極を2層以上の積層構造として、当該ゲート電極をテーパー状に設けるようにエッチングしたり異方性エッチング等を行って、当該ゲート電極を構成する下層の導電膜をマスクとして用いる手法と、サイドウォールの絶縁膜をマスクとして用いる手法がある。前者の手法を採用して形成された薄膜トランジスタは、ゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた構造となっているが、この構造は、ゲート電極をテーパー状に設けるようにエッチングしたり異方性エッチングを利用するため、LDD領域の幅を制御することが難しく、エッチング工程が良好に行われなければ、LDD領域を形成することが出来ない場合がある。一方、後者のサイドウォールの絶縁膜をマスクとして用いる手法は、前者の手法と比較すると、LDD領域の幅の制御が容易であり、また、LDD領域を確実に形成することができる。

50

**【0060】**

続いて、薄膜トランジスタ 230a～230f を覆うように、絶縁膜を単層又は積層して形成する(図6(A))。薄膜トランジスタ 230a～230f を覆う絶縁膜は、SOG法、液滴吐出法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シリコサン等の有機材料等により、単層又は積層で形成する。例えば、薄膜トランジスタ 230a～230f を覆う絶縁膜が3層構造の場合、1層目の絶縁膜 211 として酸化珪素を含む膜を形成し、2層目の絶縁膜 212 として樹脂を含む膜を形成し、3層目の絶縁膜 213 として窒化珪素を含む膜を形成するとよい。

**【0061】**

10

なお、絶縁膜 211～213 を形成する前、または絶縁膜 211～213 のうちの1つまたは複数の薄膜を形成した後に、半導体膜の結晶性の回復や半導体膜に添加された不純物元素の活性化、半導体膜の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザアニール法又はRTA法などを適用するとよい。

**【0062】**

次に、フォトリソグラフィ法により絶縁膜 211～213 を選択的にエッチングして、半導体膜 203a～203f を露出させるコンタクトホールを形成する。続いて、コンタクトホールを充填するように、導電膜を形成し、当該導電膜をパターン加工して、ソースドレイン配線として機能する導電膜 214 を形成する。

**【0063】**

20

導電膜 214 は、CVD法やスパッタリング法等により、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジウム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜 214 は、例えば、バリア膜とアルミニウムシリコン(A1-Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(A1-Si)膜と窒化チタン(TiN)膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜 214 を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができることができる。

30

**【0064】**

40

次に、導電膜 214 を覆うように、絶縁膜 215 を形成する(図6(B))。絶縁膜 215 は、SOG法、液滴吐出法またはスクリーン印刷法やグラビア印刷法等の印刷法を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁膜 215 は、好適には、0.75 μm～3 μm の厚さで形成する。

**【0065】**

続いて、フォトリソグラフィ法により絶縁膜 215 をエッチングして、薄膜トランジスタ 230a、230c、230d、230f における導電膜 214 を露出させるコンタクトホールを形成する。続いて、コンタクトホールを充填するように、導電膜を形成する。導電膜は、プラズマCVD法やスパッタ法等を用いて、導電性材料により形成する。次に、導電膜をパターン加工して、導電膜 216a～216d を形成する。なお、導電膜 216b、216d は、後に形成される記憶素子が含む一対の導電膜のうちの一方の導電膜となる。従って、好適には、導電膜 216b、216d は、チタン、又はチタンを主成分と

50

する合金材料若しくは化合物材料により、単層又は積層で形成するとよい。チタンは、抵抗値が低いため、記憶素子のサイズの縮小につながり、高集積化を実現することができる。また、導電膜 216a～216dを形成するためのフォトリソグラフィ工程においては、下層の薄膜トランジスタ 230a～230fにダメージを与えないために、ウェットエッチング加工を行うとよく、エッチング剤にはフッ化水素(HF)又はアンモニア過水を用いるとよい。

#### 【0066】

次に、導電膜 216a～216dの端部を覆うように、絶縁膜 217を形成する。絶縁膜 217は、SOG法、液滴吐出法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁膜 217は、好適には、0.75μm～3μmの厚さで形成する。

10

#### 【0067】

次に、導電膜 216a、216cに接し、アンテナとして機能する導電膜 218を形成する(図6(C))。導電膜 218は、CVD法、スパッタリング法、印刷法、液滴吐出法、印刷法等を用いて、導電性材料により形成する。好ましくは、導電膜 218は、アルミニウム(Al)、チタン(Ti)、銀(Ag)、銅(Cu)、金(Au)から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。具体的には、導電膜 218は、スクリーン印刷法により、銀を含むペーストを用いて形成し、その後、50～350度の加熱処理を行って形成する。なお、加熱処理の際に圧力をかけて加熱すると特性のよいアンテナを得ることができるため好ましい。また、他にも、スパッタリング法によりアルミニウム膜を形成し、当該アルミニウム膜をパターン加工することにより形成する。アルミニウム膜のパターン加工は、ウェットエッチング加工を用いるとよく、ウェットエッチング加工後は200～300度の加熱処理を行うとよい。

20

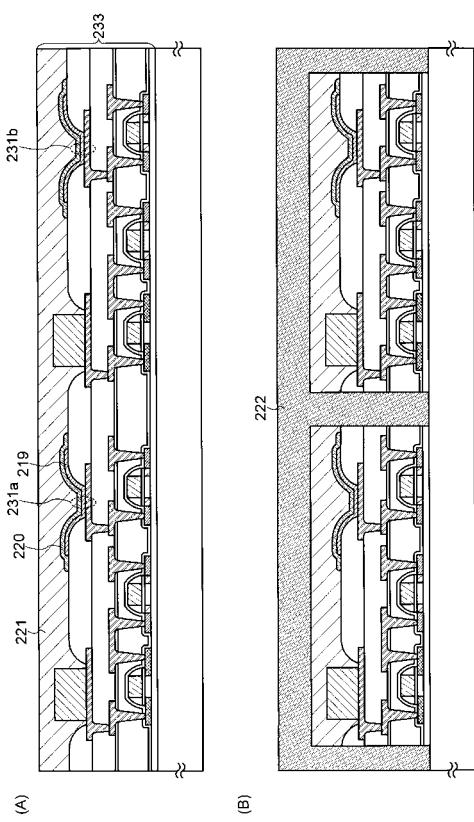

#### 【0068】

次に、導電膜 216b、216dに接するように記憶素子として機能する有機化合物層 219を形成する(図7(A))。記憶素子としては、電気的作用、光学的作用又は熱的作用等により、その性質や状態が変化する材料を用いることができる。例えば、ジュール熱による溶融、絶縁破壊等により、その性質や状態が変化し、下部電極と、上部電極とが短絡(ショート)することができる材料を用いればよい。そのため記憶素子に用いる層(ここでは有機化合物層)の厚さは、5nmから100nm、好ましくは10nmから60nmとするとよい。

30

#### 【0069】

ここでは、有機化合物層 219は、液滴吐出法、スピンドル法、蒸着法等により形成する。続いて、有機化合物層 219に接するように、導電膜 220を形成する。導電膜 220は、スパッタ法やスピンドル法、液滴吐出法、蒸着法等により形成する。

#### 【0070】

以上の工程を経て、導電膜 216bと有機化合物層 219と導電膜 220との積層体からなる記憶素子部 231aおよび導電膜 216dと有機化合物層 219と導電膜 220との積層体からなる記憶素子部 231bが完成する。

40

#### 【0071】

なお、上記の作製工程では、有機化合物層 219の耐熱性が強くないため、アンテナとして機能する導電膜 218を形成する工程の後に、有機化合物層 219を形成する工程を行うことを特徴とする。

#### 【0072】

有機化合物層に用いる有機材料としては、例えば、4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル(略称:-NPD)や4,4'-ビス[N-(3-メチルフェニル)-N-フェニル-アミノ]-ビフェニル(略称:TPD)や4,4',4'''-トリス(N,N-ジフェニル-アミノ)-トリフェニルアミン(略称:TDATA)、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニル

-アミノ] -トリフェニルアミン(略称: M T D A T A)や4 , 4' -ビス( N - (4 -(N , N -ジ-m -トリルアミノ)フェニル) - N - フェニルアミノ)ビフェニル(略称: D N T P D)などの芳香族アミン系(即ち、ベンゼン環 - 窒素の結合を有する)の化合物、ポリビニルカルバゾール(略称: P V K)やフタロシアニン(略称: H 2 P c)、銅フタロシアニン(略称: C u P c)、バナジルフタロシアニン(略称: V O P c)等のフタロシアニン化合物等を用いることができる。これら材料は、正孔輸送性の高い物質である。

### 【 0 0 7 3 】

また、他にも有機材料として、例えばトリス(8 - キノリノラト)アルミニウム(略称: A l q<sub>3</sub>)、トリス(4 - メチル - 8 - キノリノラト)アルミニウム(略称: A l m q<sub>3</sub>)、ビス(10 - ヒドロキシベンゾ[ h ] - キノリナト)ベリリウム(略称: B e B q<sub>2</sub>)、ビス(2 - メチル - 8 - キノリノラト) - 4 - フェニルフェノラト - アルミニウム(略称: B A l q)等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる材料や、ビス[2 - (2 - ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称: Z n (B O X)<sub>2</sub>)、ビス[2 - (2 - ヒドロキシフェニル)ベンゾチアゾラト]亜鉛(略称: Z n (B T Z)<sub>2</sub>)などのオキサゾール系、チアゾール系配位子を有する金属錯体などの材料も用いることができる。これら材料は、電子輸送性が高い物質である。

### 【 0 0 7 4 】

さらに、金属錯体以外にも、2 - (4 - ビフェニリル) - 5 - (4 - t e r t - プチルフェニル) - 1 , 3 , 4 - オキサジアゾール(略称: P B D)、1 , 3 - ビス[5 - (4 - t e r t - プチルフェニル) - 1 , 3 , 4 - オキサジアゾール - 2 - イル]ベンゼン(略称: O X D - 7)、3 - (4 - t e r t - プチルフェニル) - 4 - フェニル - 5 - (4 - ビフェニリル) - 1 , 2 , 4 - トリアゾール(略称: T A Z)、3 - (4 - t e r t - プチルフェニル) - 4 - (4 - エチルフェニル) - 5 - (4 - ビフェニリル) - 1 , 2 , 4 - トリアゾール(略称: p - E t T A Z)、バソフェナントロリン(略称: B P h e n)、バソキュプロイン(略称: B C P)等の化合物等を用いることができる。

### 【 0 0 7 5 】

また、有機化合物層は単層構造であっても、積層構造であってもよい。積層構造の場合、上記材料から選び、積層構造することができる。また上記有機材料と、発光材料とを積層してもよい。発光材料として、4 - ジシアノメチレン - 2 - メチル - 6 - [2 - (1 , 1 , 7 , 7 - テトラメチルジュロリジン - 9 - イル)エテニル] - 4 H - ピラン(略称: D C J T)、4 - ジシアノメチレン - 2 - t - プチル - 6 - [2 - (1 , 1 , 7 , 7 - テトラメチルジュロリジン - 9 - イル)エテニル] - 4 H - ピラン、ペリフランテン、1 , 4 - ビス[2 - (10 - メトキシ) - (1 , 1 , 7 , 7 - テトラメチルジュロリジン - 9 - イル)エテニル] - 2 , 5 - ジシアノベンゼン、N , N' - ジメチルキナクリドン(略称: D M Q d)、クマリン6、クマリン545T、トリス(8 - キノリノラト)アルミニウム(略称: A l q<sub>3</sub>)、9 , 9' - ビアントリル、9 , 10 - ジフェニルアントラセン(略称: D P A)や9 , 10 - ジ(2 - ナフチル)アントラセン(略称: D N A)、2 , 5 , 8 , 11 - テトラ - t - プチルペリレン(略称: T B P)等がある。

### 【 0 0 7 6 】

また、上記発光材料を分散してなる層を用いてもよい。発光材料を分散してなる層において、母体となる材料としては、9 , 10 - ジ(2 - ナフチル) - 2 - t e r t - プチルアントラセン(略称: t - B u D N A)等のアントラセン誘導体、4 , 4' - ビス( N - カルバゾリル)ビフェニル(略称: C B P)等のカルバゾール誘導体、ビス[2 - (2' - ヒドロキシフェニル)ピリジナト]亜鉛(略称: Z n p p<sub>2</sub>)、ビス[2 - (2' - ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称: Z n B O X)などの金属錯体等を用いることができる。また、トリス(8 - キノリノラト)アルミニウム(略称: A l q<sub>3</sub>)、9 , 10 - ジ(2 - ナフチル)アントラセン(略称: D N A)、ビス(2 - メチル - 8 - キノリノラト) - 4 - フェニルフェノラト - アルミニウム(略称: B A l q)等を用いることができる。

10

20

30

40

50

## 【0077】

このような有機材料は、熱的作用等によりその性質を変化させるため、ガラス転移温度( $T_g$ )が50から300、好ましくは80から120であるとよい。

## 【0078】

また、有機材料や発光材料に金属酸化物を混在させた材料を用いてもよい。なお金属酸化物を混在させた材料とは、上記有機材料又は発光材料と、金属酸化物とが混合した状態、又は積層された状態を含む。具体的には複数の蒸着源を用いた共蒸着法により形成された状態を指す。このような材料を有機無機複合材料と呼ぶことができる。

## 【0079】

例えは正孔輸送性の高い物質と、金属酸化物を混在させる場合、当該金属酸化物にはバナジウム酸化物、モリブデン酸化物、ニオブ酸化物、レニウム酸化物、タンクス滕酸化物、ルテニウム酸化物、チタン酸化物、クロム酸化物、ジルコニウム酸化物、ハフニウム酸化物、タンタル酸化物を用いると好ましい。10

## 【0080】

また電子輸送性の高い物質と、金属酸化物を混在させる場合、当該金属酸化物にはリチウム酸化物、カルシウム酸化物、ナトリウム酸化物、カリウム酸化物、マグネシウム酸化物を用いると好ましい。

## 【0081】

有機化合物層には、電気的作用、光学的作用又は熱的作用により、その性質が変化する材料を用いればよいため、例えは光を吸収することによって酸を発生する化合物(光酸発生剤)をドープした共役高分子を用いることもできる。共役高分子として、ポリアセチレン類、ポリフェニレンビニレン類、ポリチオフェン類、ポリアニリン類、ポリフェニレンエチニレン類等を用いることができる。また、光酸発生剤としては、アリールスルホニウム塩、アリールヨードニウム塩、 $\sigma$ -ニトロベンジルトシレート、アリールスルホン酸 $p$ -ニトロベンジルエステル、スルホニルアセトフェノン類、Fe-アレン錯体PF6塩等を用いることができる。20

## 【0082】

なお、ここでは、記憶素子部231a、231bとして、有機化合物材料を用いた例を示したが、これに限られない。例えは、結晶状態と非晶質状態の間で可逆的に変化する材料や第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料等の相変化材料を用いることができる。また、非晶質状態から結晶状態にのみ変化する材料を用いることも可能である。30

## 【0083】

結晶状態と非晶質状態の間で可逆的に変化する材料とは、ゲルマニウム(Ge)、テルル(Te)、アンチモン(Sb)、硫黄(S)、酸化テルル(TeO<sub>x</sub>)、スズ(Sn)、金(Au)、ガリウム(Ga)、セレン(Se)、インジウム(In)、タリウム(Tl)、コバルト(Co)及び銀(Ag)から選択された複数を有する材料であり、例えは、Ge-Te-Sb-S、Te-TeO<sub>2</sub>-Ge-Sn、Te-Ge-Sn-Au、Ge-Te-Sn、Sn-Se-Te、Sb-Se-Te、Sb-Se、Ga-Se-Te、Ga-Se-Te-Ge、In-Se、In-Se-Tl-Co、Ge-Sb-Te、In-Se-Te、Ag-In-Sb-Te系材料が挙げられる。また、第1の結晶状態と第2の結晶状態の間で可逆的に変化する材料とは、銀(Ag)、亜鉛(Zn)、銅(Cu)、アルミニウム(Al)、ニッケル(Ni)、インジウム(In)、アンチモン(Sb)、セレン(Se)及びテルル(Te)から選択された複数を有する材料であり、例えは、Ag-Zn、Cu-Al-Ni、In-Sb、In-Sb-Se、In-Sb-Teが挙げられる。この材料の場合、相変化は2つの異なる結晶状態の間で行われる。また、非晶質状態から結晶状態にのみ変化する材料とは、テルル(Te)、酸化テルル(TeO<sub>x</sub>)、パラジウム(Pd)、アンチモン(Sb)、セレン(Se)及びビスマス(Bi)から選択された複数を有する材料であり、例えは、Te-TeO<sub>2</sub>、Te-TeO<sub>2</sub>-Pd、Sb<sub>2</sub>Se<sub>3</sub>/Bi<sub>2</sub>Te<sub>3</sub>が挙げられる。4050

## 【0084】

次に、記憶素子部231a、231b、アンテナとして機能する導電膜218を覆うように、SOG法、スピンドルコート法、液滴吐出法または印刷法等により、保護膜として機能する絶縁膜221を形成する。絶縁膜221は、 DLC(ダイヤモンドライクカーボン)などの炭素を含む膜、窒化珪素を含む膜、窒化酸化珪素を含む膜、有機材料により形成し、好ましくはエポキシ樹脂により形成する。

## 【0085】

次に、上記実施の形態で示したように、薄膜トランジスタ230a～230f、アンテナとして機能する導電膜218、記憶素子部231aおよび231b等を有する素子形成層233に選択的に開口部を形成し、当該素子形成層233および開口部を充填するようにフィルム222を形成する(図7(B))。

10

## 【0086】

フィルム222としては、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、ポリ塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルム等を利用することができます。また、フィルムは、加熱処理および加圧処理が行われることにより被処理物に接着されるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、または最外層に設けられた層(接着層ではない)を加熱処理によって溶かし、加圧により接着する。また、フィルムの表面には接着層が設けられていてもよいし、接着層が設けられていなくてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。また、封止後に内部への水分等の侵入を防ぐために封止するフィルムにシリカコートを行うことが好ましく、例えば、接着層とポリエステル等のフィルムとシリカコートを積層させたシート材を利用することができます。

20

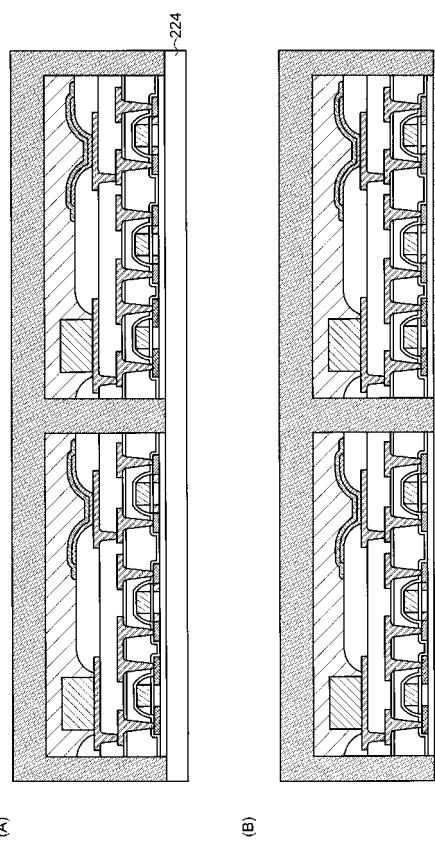

## 【0087】

次に、基板201に研削処理、研磨処理の一方又は両方を行うことにより基板201を薄膜化して基板224とする(図8(A))。ここでは、基板201の素子形成層233が形成されていない面(裏面)に研削処理を行い、その後さらに基板201の裏面に研磨処理を行うことによって基板201を薄膜化し、基板224とする。基板201に研削処理または研磨処理を行う場合にはできるだけ基板201を薄くすることが好ましいが、基板201が薄くなるにつれて素子形成層233に応力が加わりやすくなるため、基板224の厚さが5μm～50μm、好ましくは5μm～20μm、より好ましくは5μm～10μmとする。

30

## 【0088】

次に、化学処理により、基板224を除去する(図8(B))。化学処理として、薬液を用いて被処理物に化学エッチングを行う。ここでは、薬液に基板224および素子形成層233を浸すことによって、基板224のエッチングを行う。薬液は基板を除去できるものであればよく、例えば、基板201としてガラス基板を用いる場合には、薬液として弗化水素酸を含む溶液を用いることが好ましい。なお、フィルム222は、薬液と反応しにくい材料を用いることが好ましく、ここでは、エポキシ樹脂を含む絶縁膜で形成する。また、基板201が除去された後に、絶縁膜202が直接薬液に触れるため、絶縁膜202として薬液に耐性のある材料を用いることが好ましく、例えば、絶縁膜202を2層構造で設け、1層目として窒化酸化珪素膜を形成し、2層目として酸化窒化珪素膜を形成するとよい。

40

## 【0089】

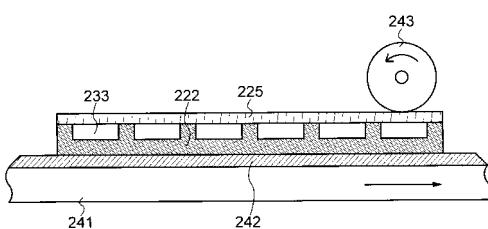

次に、素子形成層233の面にフィルム225を設けることによって封止処理を行う(図9(A))。封止処理は、図16に示すように、素子形成層233の一方の面(基板201が除去された面)に、フィルム225を設け、ローラー243を用いてフィルム225を素子形成層233に接着させる。

## 【0090】

50

封止に用いるフィルム 225 としては、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、ポリ塩化ビニルなどからなるフィルム、繊維質な材料からなる紙、基材フィルム（ポリエステル、ポリアミド、無機蒸着フィルム、紙類等）と接着性合成樹脂フィルム（アクリル系合成樹脂、エポキシ系合成樹脂等）との積層フィルム等を利用することができます。また、フィルムは、加熱処理および加圧処理が行われることにより被処理物に接着されるものであり、加熱処理と加圧処理を行う際には、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層（接着層ではない）を加熱処理によって溶かし、加圧により接着する。また、フィルム 225 の表面には接着層が設けられていてもよいし、接着層が設けられていてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。また、封止後に内部への水分等の侵入を防ぐために封止するシート材にシリカコートを行うことが好ましく、例えば、接着層とポリエステル等のフィルムとシリカコートを積層させたシート材を利用することができる。10

#### 【0091】

例えば、フィルム 225 として、ポリエチレンテレフタレート等のベースフィルム上に熱可塑性樹脂等を含むホットメルト接着剤を設けたフィルムを用いることができる。ホットメルト接着剤は、常温で個体であるが熱を加えることにより溶解するため、素子形成層 233 の表面にホットメルト接着剤を有するフィルムを設け、その後ローラー 243 で加熱処理および加圧処理を行うことによって、素子形成層 233 の封止を行うことができる。なお、ローラー 243 で加熱処理を行う場合には十分にホットメルト接着剤が溶解する温度で行う必要がある。そのため、ステージ 241 にアルミ等の金属を用いる場合には、ローラー 243 で発生した熱がステージ 241 に奪われ十分にホットメルト接着剤が溶解しない恐れがある。そのため、ステージ 241 と被処理物との間にシリコンゴム 242 等の断熱材料を設けることが好ましい。20

#### 【0092】

また、フィルム 222、フィルム 225 として、静電気等を防止する帯電防止対策を施したフィルム（以下、帯電防止フィルムと記す）を用いることもできる。帯電防止フィルムとしては、帯電防止可能な材料を樹脂中に分散させたフィルム、及び帯電防止可能な材料が貼り付けられたフィルム等が挙げられる。帯電防止可能な材料が設けられたフィルムは、片面に帯電防止可能な材料を設けたフィルムであってもよいし、両面に帯電防止可能な材料を設けたフィルムであってもよい。さらに、片面に帯電防止可能な材料が設けられたフィルムは、帯電防止可能な材料が設けられた面をフィルムの内側になるように層に貼り付けてもよいし、フィルムの外側になるように貼り付けてもよい。なお、帯電防止可能な材料はフィルムの全面、あるいは一部に設けてあればよい。ここでの帯電防止可能な材料としては、金属、インジウムと錫の酸化物（ITO）、両性界面活性剤や陽イオン性界面活性剤や非イオン性界面活性剤等の界面活性剤用いることができる。また、他にも帯電防止材料として、側鎖にカルボキシル基および 4 級アンモニウム塩基をもつ架橋性共重合体高分子を含む樹脂材料等を用いることができる。これらの材料をフィルムに貼り付けたり、練り込んだり、塗布したりすることによって帯電防止フィルムとすることができる。帯電防止フィルムで封止を行うことによって、商品として取り扱う際に、外部からの静電気等によって半導体素子に悪影響が及ぶことを抑制することができる。3040

#### 【0093】

なお、フィルム 225 で素子形成層 233 の封止処理を行った後に、必要であればフィルム 222 を覆うように封止を行ってもよい。

#### 【0094】

次に、素子形成層 233、フィルム 222 およびフィルム 225 を切断して、個々の素子に分断する（図 9（B））。なお、この際に、素子形成層 233 が露出せずに、フィルム 222 およびフィルム 225 が露出するように分断することが好ましい。このように、素子形成層 233 をフィルム 222 およびフィルム 225 で完全に覆うことによって、外部から不純物元素や水分が薄膜トランジスタ等の半導体素子に混入することを抑制し、信50

頼性の高い半導体装置を得ることができる。

【0095】

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。つまり、上記実施の形態で示した材料や形成方法は、本実施の形態でも組み合わせて利用することができるし、本実施の形態で示した材料や形成方法も上記実施の形態でも組み合わせて利用することができる。

【0096】

(実施の形態3)

本実施の形態では、上記実施の形態で示した作製方法を用いて得られた半導体装置の使用形態の一例について説明する。具体的には、非接触でデータのやりとりが可能である半導体装置の適用例に関して図面を参照して以下に説明する。非接触でデータのやりとりが可能である半導体装置は利用の形態によっては、RFID (Radio Frequency Identification) タグ、IDタグ、ICタグ、ICチップ、RFタグ (Radio Frequency) 、無線タグ、電子タグまたは無線チップともよばれる。

10

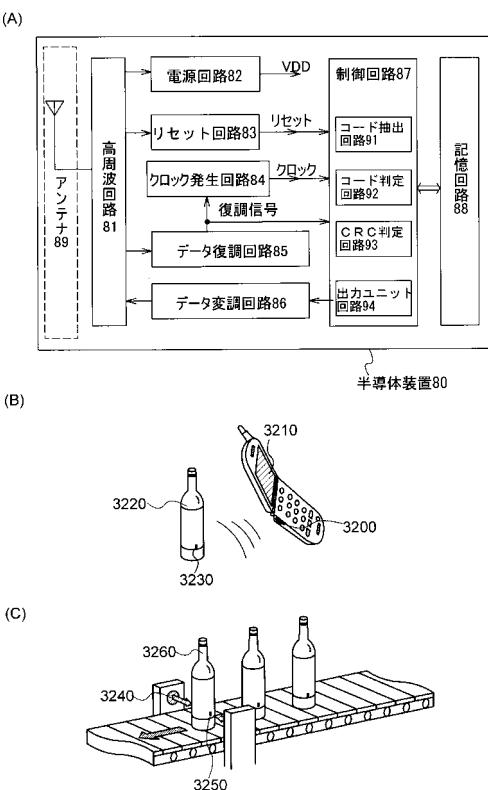

【0097】

半導体装置80は、非接触でデータを交信する機能を有し、高周波回路81、電源回路82、リセット回路83、クロック発生回路84、データ復調回路85、データ変調回路86、他の回路の制御を行う制御回路87、記憶回路88およびアンテナ89を有している(図10(A))。高周波回路81はアンテナ89より信号を受信して、データ変調回路86より受信した信号をアンテナ89から出力する回路であり、電源回路82は受信信号から電源電位を生成する回路であり、リセット回路83はリセット信号を生成する回路であり、クロック発生回路84はアンテナ89から入力された受信信号を基に各種クロック信号を生成する回路であり、データ復調回路85は受信信号を復調して制御回路87に出力する回路であり、データ変調回路86は制御回路87から受信した信号を変調する回路である。また、制御回路87としては、例えばコード抽出回路91、コード判定回路92、CRC判定回路93および出力ユニット回路94が設けられている。なお、コード抽出回路91は制御回路87に送られてきた命令に含まれる複数のコードをそれぞれ抽出する回路であり、コード判定回路92は抽出されたコードとリファレンスに相当するコードとを比較して命令の内容を判定する回路であり、CRC回路は判定されたコードに基づいて送信エラー等の有無を検出する回路である。

20

【0098】

また、記憶回路としては1つに限定されず、複数設けてもよく、SRAM、フラッシュメモリ、ROMまたはFRAM等や上記実施の形態で示した有機化合物層を記憶素子部に用いたものを用いることができる。

【0099】

次に、本発明の非接触でデータの交信が可能な半導体装置の動作の一例について説明する。まず、アンテナ89により無線信号が受信される。無線信号は高周波回路81を介して電源回路82に送られ、高電源電位(以下、VDDと記す)が生成される。VDDは半導体装置80が有する各回路に供給される。また、高周波回路81を介してデータ復調回路85に送られた信号は復調される(以下、復調信号)。さらに、高周波回路81を介してリセット回路83およびクロック発生回路84を通った信号及び復調信号は制御回路87に送られる。制御回路87に送られた信号は、コード抽出回路91、コード判定回路92およびCRC判定回路93等によって解析される。そして、解析された信号にしたがって、記憶回路88内に記憶されている半導体装置の情報が出力される。出力された半導体装置の情報は出力ユニット回路94を通じて符号化される。さらに、符号化された半導体装置80の情報はデータ変調回路86を通じて、アンテナ89により無線信号に載せて送信される。なお、半導体装置80を構成する複数の回路においては、低電源電位(以下、VSS)は共通であり、VSSはGNDとすることができます。

30

【0100】

40

50

このように、リーダ／ライタから半導体装置80に信号を送り、当該半導体装置80から送られてきた信号をリーダ／ライタで受信することによって、半導体装置のデータを読み取ることが可能となる。

#### 【0101】

また、半導体装置80は、各回路への電源電圧の供給を電源（バッテリー）を搭載せず電磁波により行うタイプとしてもよいし、電源（バッテリー）を搭載して電磁波と電源（バッテリー）により各回路に電源電圧を供給するタイプとしてもよい。

#### 【0102】

上記実施の形態で示した構成を用いることによって、折り曲げることが可能な半導体装置を作製することが可能となるため、曲面を有する物体に貼り付けて設けることが可能となる。10

#### 【0103】

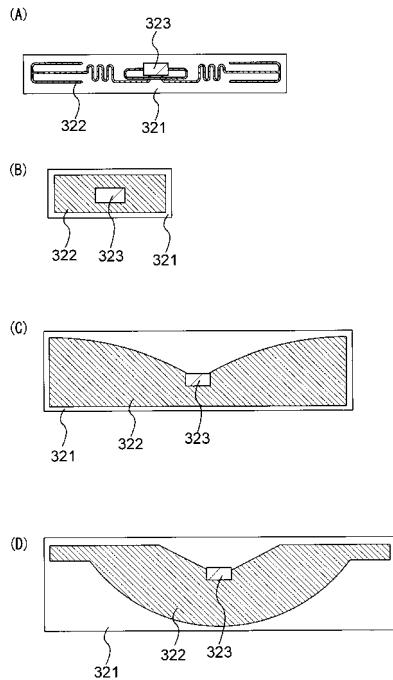

次に、可撓性を有し、非接触でデータのやりとりが可能な半導体装置の使用形態の一例について説明する。表示部3210を含む携帯端末の側面には、リーダ／ライタ3200が設けられ、品物3220の側面には半導体装置3230が設けられる（図10（B））。品物3220が含む半導体装置3230にリーダ／ライタ3200をかざすと、表示部3210に品物の原材料や原産地、生産工程ごとの検査結果や流通過程の履歴等、更に商品の説明等の商品に関する情報が表示される。また、商品3260をベルトコンベアにより搬送する際に、リーダ／ライタ3240と、商品3260に設けられた半導体装置3250を用いて、該商品3260の検品を行うことができる（図10（C））。このように、システムに半導体装置を活用することで、情報の取得を簡単に行うことができ、高機能化と高付加価値化を実現する。また、上記実施の形態で示したように、曲面を有する物体に貼り付けた場合であっても、半導体装置に含まれるトランジスタ等の損傷を防止し、信頼性の高い半導体装置を提供することが可能となる。20

#### 【0104】

また、上述した非接触データのやりとりが可能である半導体装置における信号の伝送方式は、電磁結合方式、電磁誘導方式またはマイクロ波方式等を用いることができる。伝送方式は、実施者が使用用途を考慮して適宜選択すればよく、伝送方式に伴って最適なアンテナを設ければよい。

#### 【0105】

例えば、半導体装置における信号の伝送方式として、電磁結合方式または電磁誘導方式（例えば13.56MHz帯）を適用する場合には、磁界密度の変化による電磁誘導を利用するため、アンテナとして機能する導電膜を輪状（例えば、ループアンテナ）、らせん状（例えば、スパイラルアンテナ）に形成する。30

#### 【0106】

また、半導体装置における信号の伝送方式として、マイクロ波方式（例えば、UHF帯（860～960MHz帯）、2.45GHz帯等）を適用する場合には、信号の伝送に用いる電磁波の波長を考慮してアンテナとして機能する導電膜の長さ等の形状を適宜設定すればよく、例えば、アンテナとして機能する導電膜を線状（例えば、ダイポールアンテナ（図12（A）））、平坦な形状（例えば、パッチアンテナ（図12（B）））またはリボン型の形状（図12（C）、（D））等に形成することができる。また、アンテナとして機能する導電膜の形状は線状に限られず、電磁波の波長を考慮して曲線状や蛇行形状またはこれらを組み合わせた形状で設けてよい。40

#### 【0107】

アンテナとして機能する導電膜は、CVD法、スパッタ法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム（Al）、チタン（Ti）、銀（Ag）、銅（Cu）、金（Au）、白金（Pt）ニッケル（Ni）、パラジウム（Pd）、タンタル（Ta）、モリブデン（Mo）から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層構造又は積層構造で形成する。50

## 【0108】

例えば、スクリーン印刷法を用いてアンテナとして機能する導電膜を形成する場合には、粒径が数 nm から数十 μm の導電体粒子を有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀 (A g)、金 (A u)、銅 (C u)、ニッケル (N i)、白金 (P t)、パラジウム (P d)、タンタル (T a)、モリブデン (M o) およびチタン (T i) 等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、珪素樹脂等の有機樹脂が挙げられる。また、導電膜の形成にあたり、導電性のペーストを押し出した後に焼成することが好ましい。例えば、導電性のペーストの材料として、銀を主成分とする微粒子（例えば粒径 1 nm 以上 1 0 0 nm 以下）を用いる場合、150 ~ 300 の温度範囲で焼成することにより硬化させて導電膜を得ることができる。また、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよく、この場合は粒径 20 μm 以下の微粒子を用いることが好ましい。はんだや鉛フリーはんだは、低コストであるといった利点を有している。10

## 【0109】

また、上述した材料以外にも、セラミックやフェライト等をアンテナに適用してもよいし、他にもマイクロ波帯において誘電率および透磁率が負となる材料（メタマテリアル）をアンテナに適用することも可能である。20

## 【0110】

また、電磁結合方式または電磁誘導方式を適用する場合であって、アンテナを備えた半導体装置を金属に接して設ける場合には、当該半導体装置と金属との間に透磁率を備えた磁性材料を設けることが好ましい。アンテナを備えた半導体装置を金属に接して設ける場合には、磁界の変化に伴い金属に渦電流が流れ、当該渦電流により発生する反磁界によって、磁界の変化が弱められて通信距離が低下する。そのため、半導体装置と金属との間に透磁率を備えた材料を設けることにより金属の渦電流を抑制し通信距離の低下を抑制することができる。なお、磁性材料としては、高い透磁率を有し高周波損失の少ないフェライトや金属薄膜を用いることができる。30

## 【0111】

また、アンテナを設ける場合には、1枚の基板上にトランジスタ等の半導体素子とアンテナとして機能する導電膜を直接作り込んで設けてもよいし、半導体素子とアンテナとして機能する導電膜を別々の基板上に設けた後に、電気的に接続するように貼り合わせることによって設けてもよい。

## 【0112】

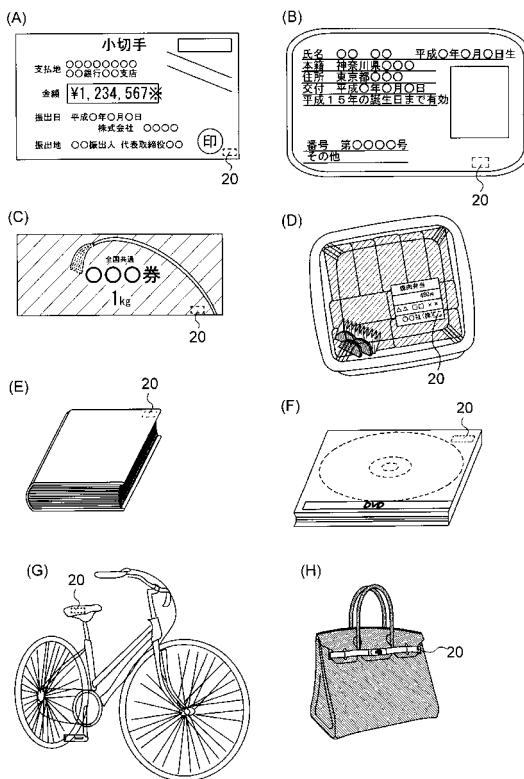

なお、上述した以外にも可撓性を有する半導体装置の用途は広範にわたり、非接触で対象物の履歴等の情報を明確にし、生産・管理等に役立てる商品であればどのようなものにも適用することができる。例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して図 1 1 を用いて説明する。40

## 【0113】

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するものの（金券）、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指す（図 1 1 ( A )）。証書類とは、運転免許証、住民票等を指す（図 1 1 ( B )）。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す（図 1 1 ( C )）。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指す（図 1 1 ( D )）。書籍類とは、書物、本等を指す（図 1 1 ( E )）。記録媒体とは、D V D ソフト、ビデオテープ等を指す（図 1 1 ( F )）。乗物類とは、自転車等の車両、船舶等を指す（図 1 1 ( G )）。身の回り品とは、鞄、眼鏡等を指す（図 1 1 ( H )）。食品類とは、食料品、飲料等を指す。衣類と50

は、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、E L表示装置、テレビジョン装置（テレビ受像機、薄型テレビ受像機）、携帯電話機等を指す。

#### 【0114】

紙幣、硬貨、有価証券類、証書類、無記名債券類等に半導体装置を設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、生活用品類、電子機器等に半導体装置を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等に半導体装置を設けることにより、偽造や盗難の防止、薬品類ならば、薬の服用の間違いを防止することができる。半導体装置の設け方としては、物品の表面に貼ったり、物品に埋め込んだりして設ける。例えば、本ならば紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。可撓性を有する半導体装置を用いることによって、紙等に設けた場合であっても、上記実施の形態で示した構造を有する半導体装置を用いて半導体装置を設けることにより、当該半導体装置に含まれる素子の破損等を防止することができる。10

#### 【0115】

このように、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類に半導体装置を設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にセンサーを備えた半導体装置を埋め込むことによって、生まれた年や性別または種類等はもちろん現在の体温等の健康状態を容易に管理することが可能となる。20

#### 【0116】

なお、本実施の形態は、上記実施の形態と自由に組み合わせて行うことができる。つまり、上記実施の形態で示した材料や形成方法は、本実施の形態でも組み合わせて利用することができるし、本実施の形態で示した材料や形成方法も上記実施の形態でも組み合わせて利用することができる。30

#### 【0117】

##### （実施の形態4）

本実施の形態では、上記実施の形態で示した作製方法を用いて得られた半導体装置の使用形態の一例について説明する。具体的には、表示手段を有する半導体装置に関して図面を参照して説明する。

#### 【0118】

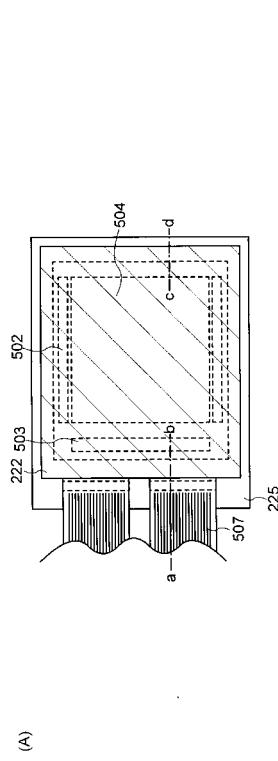

まず、表示手段として、画素部に発光素子を設けた場合に関する図13を参照して説明する。なお、図13(A)は本発明の半導体装置の一例を示す上面図を示しており、図13(B)は図13(A)をa-b間とc-d間で切断した断面図を示している。

#### 【0119】

図13(A)に示すように、本実施の形態で示す半導体装置は、フィルム225(フィルム状の基板)上に設けられた走査線駆動回路502、信号線駆動回路503および画素部504等を有している。また、画素部504をフィルム225と共に挟むようにフィルム222(フィルム状の基板)が設けられている。走査線駆動回路502、信号線駆動回路503および画素部504には、フィルム225上に上記実施の形態で示したいずれかの構造を有する薄膜トランジスタが設けられている。40

#### 【0120】

走査線駆動回路502および信号線駆動回路503は、外部入力端子となるFPC507からビデオ信号、クロック信号、スタート信号、リセット信号等を受け取る。また、ここではFPC(flexible printed circuit)しか図示されていないが、このFPCにはプリント配線基板が取り付けられていても良い。また、ここでは50

信号線駆動回路 503 または走査線駆動回路 502 を構成する薄膜トランジスタとして、上記実施の形態で示したように、薄膜トランジスタを積層させた構造とすることができる。薄膜トランジスタを積層させて設けることによって、信号線駆動回路 503 または走査線駆動回路 502 が占有する面積を小さくすることができるため、画素部 504 の面積を広く形成することが可能となる。

#### 【0121】

図 13 (B) は、図 13 (A) の a - b 間と c - d 間の断面の模式図を示しており、ここでは、フィルム 225 上に信号線駆動回路 503 と画素部 504 に含まれる薄膜トランジスタが設けられている場合を示している。信号線駆動回路 503 は、上記実施の形態で示したいずれかの構造を有する n 型の薄膜トランジスタ 510a と p 型の薄膜トランジスタ 510b とを組み合わせた CMOS 回路が形成されている。10

#### 【0122】

走査線駆動回路 502 や信号線駆動回路 503 等の駆動回路を形成する薄膜トランジスタは、CMOS 回路、PMOS 回路もしくはNMOS 回路で形成しても良い。また、本実施の形態では、フィルム 225 上に走査線駆動回路 502 や信号線駆動回路 503 等の駆動回路を形成したドライバー一体型を示すが、必ずしもその必要はなく、フィルム 225 上ではなく外部に形成することもできる。

#### 【0123】

また、画素部 504 は、発光素子 516 と当該発光素子 516 を駆動するための薄膜トランジスタ 511 とを含む複数の画素により形成されている。薄膜トランジスタ 511 は、上記実施の形態で示したいずれかの構造を有する薄膜トランジスタを適用することができる。また、ここでは、薄膜トランジスタ 511 のソースまたはドレイン領域に接続されている導電膜 214 に接続するように第 1 の電極 513 が設けられ、当該第 1 の電極 513 の端部を覆うように絶縁膜 217 が形成されている。絶縁膜 217 は、複数の画素において隔壁として機能している。20

#### 【0124】

絶縁膜 217 として、ここでは、ポジ型の感光性アクリル樹脂膜を用いることにより形成する。また、カバレッジを良好なものとするため、絶縁膜 217 は、当該絶縁膜 217 の上端部または下端部に曲率を有する曲面が形成されるように設ける。例えば、絶縁膜 217 の材料としてポジ型の感光性アクリルを用いた場合、絶縁膜 217 の上端部のみに曲率半径 (0.2 μm ~ 3 μm) を有する曲面を持たせることが好ましい。絶縁膜 217 としては、感光性の光によってエッチャントに不溶解性となるネガ型、或いは光によってエッチャントに溶解性となるポジ型のいずれも使用することができる。他にも、絶縁膜 217 としてエポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン等の有機材料やシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。また、上記実施の形態で示したように、絶縁膜 217 にプラズマ処理を行い、当該絶縁膜 217 を酸化または窒化することによって、絶縁膜 217 の表面を改質して緻密な膜を得ることも可能である。絶縁膜 217 の表面を改質することによって、当該絶縁膜 217 の強度が向上し開口部等の形成時におけるクラックの発生やエッチング時の膜減り等の物理的ダメージを低減することができる。また、絶縁膜 217 の表面が改質されることによって、当該絶縁膜 217 上に設けられる発光層 514 との密着性等の界面特性が向上する。3040

#### 【0125】

また、図 13 に示す半導体装置は、第 1 の電極 513 上に発光層 514 が形成され、当該発光層 514 上に第 2 の電極 515 が形成されている。これら第 1 の電極 513、発光層 514 および第 2 の電極 515 の積層構造により発光素子 516 が設けられている。

#### 【0126】

第 1 の電極 513 および第 2 の電極 515 は、一方を陽極として用い、他方を陰極として用いる。

#### 【0127】

10

20

30

40

50

陽極として用いる場合には、仕事関数の大きい材料を用いることが望ましい。例えば、ITO膜、珪素を含有したインジウム錫酸化物膜、酸化インジウムに2~20wt%の酸化亜鉛(ZnO)を混合したターゲットを用いてスパッタ法により形成した透明導電膜、酸化亜鉛(ZnO)膜、窒化チタン膜、クロム膜、タンゲステン膜、Zn膜、Pt膜などの単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との3層構造等を用いることができる。なお、積層構造とすると、配線としての抵抗も低く、良好なオーミックコンタクトがとれ、さらに陽極として機能させることができる。

#### 【0128】

陰極として用いる場合には、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、またはCa<sub>3</sub>N<sub>2</sub>)を用いることが好ましい。なお、陰極として用いる電極を透光性とする場合には、電極として、膜厚を薄くした金属薄膜と、透明導電膜(ITO、珪素を含有したインジウム錫酸化物、酸化インジウムに2~20wt%の酸化亜鉛(ZnO)を混合したターゲットを用いてスパッタ法により形成した透明導電膜、酸化亜鉛(ZnO)等)との積層を用いるのが良い。

#### 【0129】

ここでは第1の電極513を陽極として透光性を有するITOを用い、フィルム225側から光を取り出す構造とする。なお、第2の電極515に透光性を有する材料を用いることによりフィルム222側から光を取り出す構造としてもいし、第1の電極513および第2の電極515を透光性を有する材料で設けることによって、フィルム225およびフィルム222の両側に光を取り出す構造(両面射出)とすることも可能である。

#### 【0130】

また、発光層514は、低分子系材料、中分子材料(オリゴマー、デンドリマーを含む)、または高分子(ポリマーともいう)材料等による単層または積層構造を、蒸着マスクを用いた蒸着法、インクジェット法、スピンドルコート法等の方法によって形成することができる。

#### 【0131】

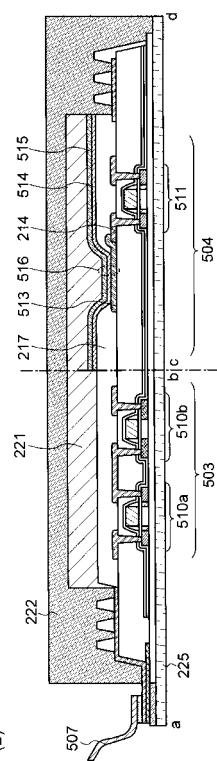

なお、画素部を有する半導体装置としては、上述したように画素部に発光素子を用いた構成に限られず、画素部に液晶を用いた半導体装置も含まれる。画素部に液晶を用いた場合の半導体装置を図14に示す。

#### 【0132】

図14は、液晶を画素部に有する半導体装置の一例を示しており、導電膜214および第1の電極513を覆うように設けられた配向膜521とフィルム222側に設けられた配向膜523との間に液晶522が設けられている。また、第2の電極524がフィルム222に接するように設けられており、第1の電極513と第2の電極524間に設けられた液晶に加える電圧を制御して光の透過率を制御することにより像の表示を行う。また、液晶522中に第1の電極513と第2の電極524との間の距離(セルギャップ)を制御するためにスペーサ525が設けられている。

#### 【0133】

このように、本実施の形態で示す半導体装置の使用形態としては、画素部を発光素子で設けることもできるし、液晶で設けることもできる。

#### 【0134】

次に、上記画素部を有する半導体装置の利用形態について図面を参照して説明する。

#### 【0135】

上記画素部を有する半導体装置の利用形態として、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話機、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDVD(digital versatile disc)等の記録媒体を再生し、その画像を表示しうるディスプレイを備え

10

20

30

30

40

50

た装置)などの電子機器が挙げられる。それらの具体例を以下に示す。

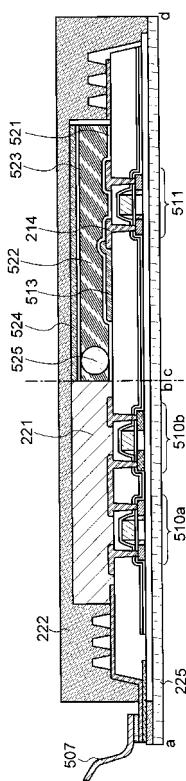

【0136】

図15(A)はディスプレイであり、本体4101、支持台4102、表示部4103等を含む。表示部4103は可撓性を有する基板を用いて形成されており、軽量で薄型のディスプレイを実現できる。また、表示部4103を湾曲させることも可能であり、支持台4102から取り外して湾曲した壁に沿ってディスプレイを取り付けることも可能である。このように、可撓性を有するディスプレイは、フラットな面はもちろん湾曲した部分にも設けることが可能となるため、様々な用途に用いることができる。本実施の形態で示した可撓性を有する半導体装置を表示部4103や回路等に用いることによって、本発明の半導体装置の使用形態の一つである可撓性を有するディスプレイを作製することができる。10

【0137】

図15(B)は巻き取り可能なディスプレイであり、本体4201、表示部4202等を含む。本体4201および表示部4202は可撓性を有する基板を用いて形成されているため、ディスプレイを折り畳んだり、巻き取ったりして持ち運ぶことが可能である。そのため、ディスプレイが大型である場合でも折り畳んだり、巻き取ったりして鞄に入れて持ち運ぶことができる。本実施の形態で示した可撓性を有する半導体装置を表示部4202や回路等に用いることによって、本発明の半導体装置の使用形態の一つである、軽量、薄型の大型のディスプレイを作製することができる。

【0138】

図15(C)は、シート型のコンピュータであり、本体4401、表示部4402、キーボード4403、タッチパッド4404、外部接続ポート4405、電源プラグ4406等を含んでいる。表示部4402は可撓性を有する基板を用いて形成されており、軽量で薄型のコンピュータを実現できる。また、本体4401の部分に収納スペースを設けることによって表示部4402を本体に巻き取って収納することができる。また、キーボード4403も可撓性を有するように設けることによって、表示部4402と同様に本体4401の収納スペースに巻き取って収納することができ、持ち運びが便利になる。また、使用しない場合にも折り畳むことによって場所をとらずに収納することができる。本実施の形態で示した可撓性を有する半導体装置を表示部4402や回路等に用いることによって、本発明の半導体装置の使用形態の一つである、軽量、薄型のコンピュータを作製することができる。30

【0139】

図15(D)は、20~80インチの大型の表示部を有する表示装置であり、本体4300、操作部であるキーボード4301、表示部4302、スピーカー4303等を含む。また、表示部4302は可撓性を有する基板を用いて形成されており、キーボード4301を取り外して本体4300を折り畳んだり巻き取ったりして持ち運ぶことが可能である。また、キーボード4301と表示部4302との接続は無線で行うことができ、例えば、湾曲した壁に沿って本体4300を取り付けながらキーボード4301で無線によって操作することができる。この場合表示部4302を本実施の形態で示した可撓性を有する半導体装置を表示部4302や回路等に用いることによって、本発明の半導体装置の使用形態の一つである、軽量、薄型の大型表示装置を作製することができる。40

【0140】

図15(E)は電子ブックであり、本体4501、表示部4502、操作キー4503等を含む。またモデムが本体4501に内蔵されていても良い。表示部4502は可撓性基板を用いて形成されており、折り曲げたり巻き取ったりすることができる。そのため、電子ブックの持ち運びも場所をとらずに行うことができる。さらに、表示部4502は文字等の静止画像はもちろん動画も表示することができるようになっている。本実施の形態で示した可撓性を有する半導体装置を表示部4502や回路等に用いることによって、本発明の半導体装置の使用形態の一つである、軽量、薄型の電子ブックを作製することができる。

【0141】

10

20

30

40

50

図15(F)はICカードであり、本体4601、表示部4602、接続端子4603等を含む。表示部4602は可撓性基板を用いて軽量、薄型のシート状になっているため、カードの表面に張り付けて形成することができる。また、ICカードを非接触でデータの受信が行える場合に外部から取得した情報を表示部4602に表示することが可能となっている。本実施の形態で示した可撓性を有する半導体装置を表示部4602や回路等に用いることによって、本発明の半導体装置の使用形態の一つである、軽量、薄型のICカードを作製することができる。

#### 【0142】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器や情報表示手段に用いることが可能である。なお、本実施の形態は上記実施の形態と自由に組み合わせて行うことができる。つまり、上記実施の形態で示した材料や形成方法は、本実施の形態でも組み合わせて利用することができるし、本実施の形態で示した材料や形成方法も上記実施の形態でも組み合わせて利用することができる。

10

#### 【図面の簡単な説明】

#### 【0143】

【図1】本発明の半導体装置の作製方法の一例を示す図。

【図2】本発明の半導体装置の作製方法の一例を示す図。

【図3】本発明の半導体装置の作製方法の一例を示す図。

【図4】本発明の半導体装置の作製方法の一例を示す図。

【図5】本発明の半導体装置の作製方法の一例を示す図。

20

【図6】本発明の半導体装置の作製方法の一例を示す図。

【図7】本発明の半導体装置の作製方法の一例を示す図。

【図8】本発明の半導体装置の作製方法の一例を示す図。

【図9】本発明の半導体装置の作製方法の一例を示す図。

【図10】本発明の半導体装置の使用形態の一例を示す図。

【図11】本発明の半導体装置の使用形態の一例を示す図。

【図12】本発明の半導体装置の使用形態の一例を示す図。

【図13】本発明の半導体装置の使用形態の一例を示す図。

【図14】本発明の半導体装置の使用形態の一例を示す図。

【図15】本発明の半導体装置の使用形態の一例を示す図。

30

【図16】本発明の半導体装置の作製方法の一例を示す図。

#### 【符号の説明】

#### 【0144】

101 基板

102 素子群

103 絶縁膜

104 開口部

105 フィルム

106 基板

107 薄膜手段

40

108 薬液

109 フィルム

110 素子形成層

111 クラック

201 基板

202 絶縁膜

203 半導体膜

203a 半導体膜

203b 半導体膜

203c 半導体膜

50

|         |            |    |

|---------|------------|----|

| 2 0 3 d | 半導体膜       |    |

| 2 0 3 e | 半導体膜       |    |

| 2 0 3 f | 半導体膜       |    |

| 2 0 4   | ゲート絶縁膜     |    |

| 2 0 5   | ゲート電極      |    |

| 2 0 6   | N型不純物領域    |    |

| 2 0 7   | P型不純物領域    |    |

| 2 0 8   | 絶縁膜        |    |

| 2 0 9 a | 第1のN型不純物領域 | 10 |

| 2 0 9 b | 第2のN型不純物領域 |    |

| 2 1 0   | 絶縁膜        |    |

| 2 1 1   | 絶縁膜        |    |

| 2 1 2   | 絶縁膜        |    |

| 2 1 3   | 絶縁膜        |    |

| 2 1 4   | 導電膜        |    |

| 2 1 5   | 絶縁膜        |    |

| 2 1 6 a | 導電膜        | 20 |

| 2 1 6 b | 導電膜        |    |

| 2 1 6 c | 導電膜        |    |

| 2 1 6 d | 導電膜        |    |

| 2 1 7   | 絶縁膜        |    |

| 2 1 8   | 導電膜        |    |

| 2 1 9   | 有機化合物層     |    |

| 2 2 0   | 導電膜        |    |

| 2 2 1   | 絶縁膜        |    |

| 2 2 2   | フィルム       |    |

| 2 2 4   | 基板         |    |

| 2 2 5   | フィルム       |    |

| 2 3 0 a | 薄膜トランジスタ   | 30 |

| 2 3 0 b | 薄膜トランジスタ   |    |

| 2 3 0 c | 薄膜トランジスタ   |    |

| 2 3 0 d | 薄膜トランジスタ   |    |

| 2 3 0 e | 薄膜トランジスタ   |    |

| 2 3 0 f | 薄膜トランジスタ   |    |

| 2 3 1 a | 記憶素子部      |    |

| 2 3 1 b | 記憶素子部      |    |

| 2 3 3   | 素子形成層      |    |

| 2 4 1   | ステージ       |    |

| 2 4 3   | ローラー       |    |

| 8 0     | 半導体装置      | 40 |

| 8 1     | 高周波回路      |    |

| 8 2     | 電源回路       |    |

| 8 3     | リセット回路     |    |

| 8 4     | クロック発生回路   |    |

| 8 5     | データ復調回路    |    |

| 8 6     | データ変調回路    |    |

| 8 7     | 制御回路       |    |

| 8 8     | 記憶回路       |    |

| 8 9     | アンテナ       |    |

| 9 1     | コード抽出回路    | 50 |

|         |            |    |

|---------|------------|----|

| 9 2     | コード判定回路    |    |

| 9 3     | C R C 判定回路 |    |

| 9 4     | 出力ユニット回路   |    |

| 3 2 1 0 | 表示部        |    |

| 3 2 0 0 | リーダ / ライタ  |    |

| 3 2 2 0 | 品物         |    |

| 3 2 3 0 | 半導体装置      |    |

| 3 2 5 0 | 半導体装置      |    |

| 3 2 6 0 | 商品         |    |

| 5 0 2   | 走査線駆動回路    | 10 |

| 5 0 3   | 信号線駆動回路    |    |

| 5 0 4   | 画素部        |    |

| 5 1 0 a | 薄膜トランジスタ   |    |

| 5 1 0 b | 薄膜トランジスタ   |    |

| 5 1 1   | 薄膜トランジスタ   |    |

| 5 1 3   | 第 1 の電極    |    |

| 5 1 4   | 発光層        |    |

| 5 1 5   | 第 2 の電極    |    |

| 5 1 6   | 発光素子       |    |

| 5 2 1   | 配向膜        | 20 |

| 5 2 2   | 液晶         |    |

| 5 2 3   | 配向膜        |    |

| 5 2 4   | 第 2 の電極    |    |

| 5 2 5   | スペーサ       |    |

| 4 1 0 1 | 本体         |    |

| 4 1 0 2 | 支持台        |    |

| 4 1 0 3 | 表示部        |    |

| 4 2 0 1 | 本体         |    |

| 4 2 0 2 | 表示部        |    |

| 4 4 0 1 | 本体         | 30 |

| 4 4 0 2 | 表示部        |    |

| 4 4 0 3 | キー ボード     |    |

| 4 4 0 4 | タッチパッド     |    |

| 4 4 0 5 | 外部接続ポート    |    |

| 4 4 0 6 | 電源プラグ      |    |

| 4 3 0 0 | 本体         |    |

| 4 3 0 1 | キー ボード     |    |

| 4 3 0 2 | 表示部        |    |

| 4 3 0 3 | スピーカー      |    |

| 4 5 0 1 | 本体         | 40 |

| 4 5 0 2 | 表示部        |    |

| 4 5 0 3 | 操作キー       |    |

| 4 6 0 1 | 本体         |    |

| 4 6 0 2 | 表示部        |    |

| 4 6 0 3 | 接続端子       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

(A)

(B)

【図14】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/336 (2006.01) H 01 L 29/78 627D

H 01 L 29/786 (2006.01)

(56)参考文献 特開2004-282063(JP,A)

特開2005-252242(JP,A)

特開2002-184959(JP,A)

特開2001-272923(JP,A)

特開2002-353235(JP,A)

国際公開第2002/084739(WO,A1)

特開2005-071063(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 K 19 / 07

G 06 K 19 / 077

H 01 L 21 / 02

H 01 L 21 / 336

H 01 L 21 / 56

H 01 L 27 / 12

H 01 L 29 / 786