(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5039920号

(P5039920)

(45) 発行日 平成24年10月3日(2012.10.3)

(24) 登録日 平成24年7月20日(2012.7.20)

(51) Int.Cl.

H01L 21/20 (2006.01)

F 1

H01L 21/20

請求項の数 6 (全 7 頁)

(21) 出願番号 特願2007-524976 (P2007-524976)

(86) (22) 出願日 平成17年8月4日 (2005.8.4)

(65) 公表番号 特表2008-509562 (P2008-509562A)

(43) 公表日 平成20年3月27日 (2008.3.27)

(86) 國際出願番号 PCT/US2005/027691

(87) 國際公開番号 WO2006/017640

(87) 國際公開日 平成18年2月16日 (2006.2.16)

審査請求日 平成20年6月2日 (2008.6.2)

(31) 優先権主張番号 10/710,826

(32) 優先日 平成16年8月5日 (2004.8.5)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】 改善された熱伝導率をもつ歪みシリコン材料を形成するための方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に Si Ge 層を形成するための方法であって、

第 1 の堆積ステップにおいて、Si 及び Ge の一方の第 1 の層を堆積するステップと、

第 2 の堆積ステップにおいて、Si 及び Ge の他方の第 2 の層を堆積するステップと、

前記第 1 の堆積ステップと前記第 2 の堆積ステップを繰り返して、複数の Si 層及び複数の Ge 層を有する複合 Si Ge 層を形成するステップと、を含み、

前記 Si 層及び前記 Ge 層のそれぞれの厚さが、前記複合 Si Ge 層の Si と Ge の構成比が 1 : 1 になるように選択され、かつ前記 Ge 層の厚さは 10 <sup>10</sup> であり、その結果、前記複合 Si Ge 層が複合 Si<sub>0.5</sub>Ge<sub>0.5</sub> 層として、Si 及び Ge のランダム合金のものより大きい熱伝導率を有する Si 及び Ge のデジタル合金として特徴付けられ、さらに、

Si 層を前記複合 Si Ge 層上に堆積するステップを含む、方法。

## 【請求項 2】

基板上に Si Ge 層を形成するための方法であって、

第 1 の堆積ステップにおいて、Si 及び Ge の一方の第 1 の層を堆積するステップと、

第 2 の堆積ステップにおいて、Si 及び Ge の他方の第 2 の層を堆積するステップと、

前記第 1 の堆積ステップと前記第 2 の堆積ステップを繰り返して、複数の Si 層及び複数の Ge 層を有する複合 Si Ge 層を形成するステップと、を含み、

前記 Si 層及び前記 Ge 層のそれぞれの厚さが、前記複合 Si Ge 層の Si と Ge の構成比が 1 : 1 になるように選択され、かつ前記 Ge 層の厚さは 10 <sup>20</sup> であり、その結果、

10

20

前記複合 SiGe 層が複合  $Si_{0.5}Ge_{0.5}$  層として、 Si 及び Ge のランダム合金のものより大きい熱伝導率を有する Si 及び Ge のデジタル合金として特徴付けられ、

前記第 1 の層及び前記第 2 の層の少なくとも一方が単一の同位体で構成される、方法。

【請求項 3】

Si 層を前記複合 SiGe 層上に堆積するステップをさらに含む、請求項 2 に記載の方法。

【請求項 4】

前記基板が Si 基板の上に重なる SiGe 層を含む、請求項 1 または 2 に記載の方法。

【請求項 5】

前記第 1 の堆積ステップの前に、前記 Si 基板の上に重なる SiGe 層を研磨してその厚さを減少させるステップをさらに含む、請求項 4 に記載の方法。 10

【請求項 6】

前記第 1 の層及び前記第 2 の層の少なくとも一方が単一の同位体で構成される、請求項 1 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子デバイスの製造に関し、より具体的には、 SiGe 合金が改善された熱伝導率を有する、歪み Si 及び SiGe 合金フィルムを形成するためのプロセスに関する。 20

【背景技術】

【0002】

引張り歪みをもつシリコン層は、高性能 CMOS デバイスにおいて用いるのに関心がもたれている。歪み Si 層における改善された電荷キャリアの移動度は、デバイスにおける幾何学的スケーリングの必要なしで、高められた FET 性能（より高いオン状態の電流）を可能にする。歪み Si 層は、典型的には、 Si 層を緩和シリコン・ゲルマニウム（ SiGe ）層上に成長させることにより形成される。デバイスの用途に応じて、 SiGe 層は、バルク Si 基板上に成長させてもよいし、又は、絶縁層の上部に形成してシリコン・ゲルマニウム・オン・インシュレータ（ SGOI ）ウェハを生成してもよい。緩和 SiGe 層上の歪み Si は、 Si / SiGe 二重層構造体として見ることができる。 30

【0003】

基板がどのように製造されたかにかかわらず、 Si / SiGe 二重層構造体におけるデバイス製造にとっての実質的な障害は、 SiGe 合金材料の不良な熱伝導率である。このことは、二重層構造体上に製造されたトランジスタの電気特性を低下させることが明らかになっている。純粋な Si の場合におけるほど熱を迅速に伝送できないため、デバイスのチャネル領域における温度が上昇し、これによって電荷キャリアの移動度が低下する。

【0004】

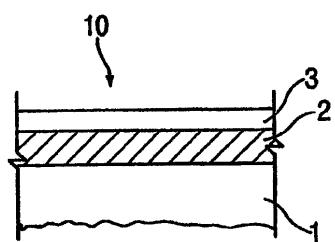

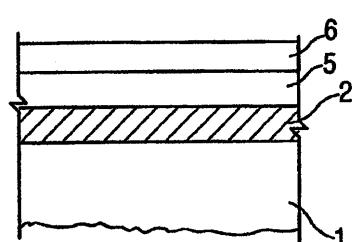

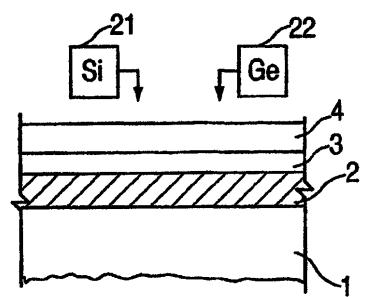

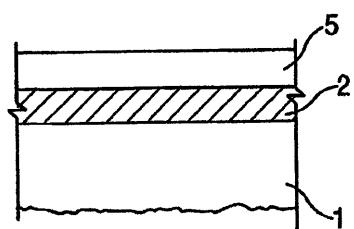

通常、格子内の構成原子の質量変動は、結晶内のフォトンの寿命を減少させ、これは次いで、熱伝導率の減少をもたらす。 SiGe ランダム合金の場合には、 Si 原子と Ge 原子との間、並びに、 Si 及び Ge の種々の同位体における質量変動は、熱伝導率の減少をもたらす。天然に生ずる Si 及び Ge をもつ典型的なランダム SiGe 合金においては、 Si は 3 つの同位体  $^{28}Si$  、  $^{29}Si$  及び  $^{30}Si$  を有し、 Ge は 5 つの同位体  $^{70}Ge$  、  $^{72}Ge$  、  $^{73}Ge$  、  $^{74}Ge$  及び  $^{76}Ge$  を有する。 SiGe 材料の熱伝導率は、 SiGe 形成に同位体標識ガス源を用いる堆積により改善することができ、これは、 Si 及び Ge それぞれの同位体の質量変動を最小にする。特許文献 1 は、シラン（ SiH<sub>4</sub> ）ガス及びゲルマン（ GeH<sub>4</sub> ）ガスを用いることにより SiGe 層を形成することを提案し、ここで  $^{28}Si$  及び  $^{70}Ge$  の同位体濃度は両方共 95 % より大きい。（同様に同位体で標識することができる） Si の層は、この SiGe 層の上に堆積される。この技術は、バルク Si 基板又は SOI 基板上の、同位体の質量変動が減少された緩和 SiGe 合金層上に歪み Si の二重層構造体をもたらす。図 1 及び図 2 は、 SOI 基板上のこの技術 40

の適用例を示す。典型的なS O I基板10は、Si基板1上に絶縁層2及び基板層3を有する(図1)。同位体標識Si及びGeのための原料ガス21、22が堆積プロセスにおいて用いられて、ランダムSiGe合金層4を形成する(図2)。同位体標識は、SiGe層の質量変動を低下させ、これにより、その熱伝導率を改善するように作用する。

#### 【0005】

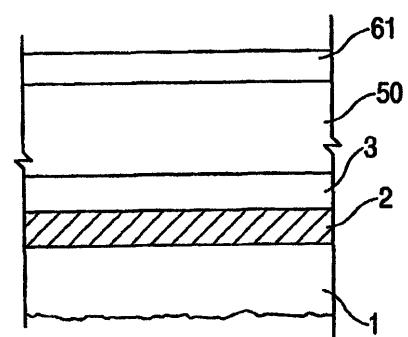

(本出願と同じ譲受人に譲渡された特許文献2に説明されるように、)熱混合プロセスを採用して、基板層3を質量変動が減少したSiGe層4と混合して、緩和SiGe層5を絶縁体2上に生成することができる(図3)。この構造体は、したがって、緩和SiGeオン・インシュレータ(SGOI)基板として見ることができ、図4に示すように、この上に、Si層6を形成して、歪みSi層を与えることができる。

10

#### 【0006】

【特許文献1】米国特許明細書第2004/0004271(Fukuda他)

【特許文献2】Bedell他による米国特許明細書番号第10/055、138号

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

CMOSデバイスにおける歪みSi層の利点を実現するために、SiGe合金層における熱伝導率が改善されたSi/SiGe二重層構造体を提供する必要性がある。複雑さを加えることなく、かつSi及びGeのために同位体標識原料ガスを用いる費用なしで、質量変動が減少された緩和SiGe層を形成することが望ましい。

20

#### 【課題を解決するための手段】

#### 【0008】

本発明は、SiGeのランダム合金のものより大きい熱伝導率を有するSiGe層を基板上に形成するための方法を提供する。この方法においては、第1の堆積ステップにおいて、Si又はGeの第1の層が堆積され、第2の堆積ステップにおいて、他方の要素の第2の層が堆積され、第1の堆積ステップ及び第2の堆積ステップが繰り返されて、複数のSi層と複数のGe層とを有する複合SiGe層が形成される。Si層及びGe層のそれぞれの厚さは、複合SiGe層の望ましい構成比による(例えば、1:1の比率は、典型的には、Si<sub>0.5</sub>Ge<sub>0.5</sub>を形成するように、各々が約厚さのSi層及びGe層により実現される)。Si層及びGe層は歪まされるが、これらは十分に薄いので、歪み緩和転位が形成されることはない。複合SiGe層は、Si及びGeのランダム合金のものより大きい熱伝導率を有するSi及びGeのデジタル合金として特徴付けられる。この方法は、さらに、Si層を複合SiGe層に堆積するステップをさらに含み、複合SiGe層は、緩和SiGe層として特徴付けられ、Si層は歪みSi層である。SiGe層におけるより大きな熱伝導率のためには、第1の層及び第2の層は、各々が、本質的に、単一の同位体で構成されるように堆積することができる。

30

#### 【0009】

本発明の別の態様によれば、半導体デバイスを製造するための方法が提供される。この方法は、SiGeのデジタル合金の層を基板上に形成するステップと、Si層をSiGeのデジタル合金上に形成するステップと、を含む。SiGeのデジタル合金は、Si及びGeのランダム合金のものより大きい熱伝導率を有する。デジタル合金層は、さらに、緩和SiGe層として特徴付けることができ、Si層は歪みSi層である。本発明の特定の実施形態によれば、デジタル合金層は、Si及びGeの複数の交互の副層を含む。これらの副層は、SiGeのデジタル合金の望ましい構成比による厚さで形成される。副層の各々は、本質的に、単一の同位体で構成することができる。

40

#### 【0010】

本発明のさらに別の態様によれば、基板上のSiGeのデジタル合金の層と、SiGeのデジタル合金上のSi層とを含む半導体デバイスが提供され、SiGeのデジタル合金は、Si及びGeのランダム合金のものより大きい熱伝導率を有する。デジタル合金層は、緩和SiGe層として特徴付けることができ、SiGe層上のSi層は歪みSi層とし

50

て特徴付けることができる。デジタル合金層は、Si及びGeの複数の交互の副層を含む。基板は、バルクSi基板であってもよいし、バルクSi基板上に成長されたランダムSiGe合金層であってもよいし、或いはSOI又はSGOI構造体であってもよい。

【発明を実施するための最良の形態】

【0011】

本発明によれば、SiGe合金の層が基板（典型的には、バルクSi、バルクSi上に成長されたSiGe、或いはSOI又はSGOI）上に形成され、SiGe合金層は質量変動が減少されており、したがって、ランダムSiGe合金の層より高い熱伝導率を有する。これは、SiGe層を、ランダム合金ではなく、順序付けられたデジタル合金として形成することにより達成される。

10

【0012】

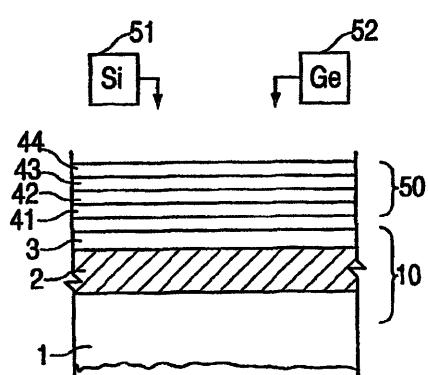

図5は、本発明のプロセスにより形成されたSiGeデジタル合金を示す。基板10（ここでは、バルク基板1上に基板層3及び絶縁体2をもつSGOI構造体として示される）は、Si源51及びGe源52を用いて、Si又はGeのいずれかの層を基板上に堆積することができる処理チャンバ内に置かれる。超高真空CVD（UHV CVD）及び好ましくは650より低い温度における低温エピタキシー（LTE）を含む様々な堆積技術を用いることができる。

【0013】

Siの薄層41が基板上に堆積され、Geの薄層42が層41に堆積される。Si及びGeの交互の層43、44等は、Si/Geの望ましい合計厚さに到達するまで堆積される。Si層及びGe層の相対厚さは、望ましい構成比により調整される。例えば、SiGe層の全体を90%Siにすべき場合には、Siの層41及び層43の各々は、典型的には90厚さにし、Geの層42及び層44の各々は、典型的には10厚さにする。Si層及びGe層の合計数は、複合層50の望ましい厚さに応じて決まり、これはデバイスの用途に応じて、数百からミクロンほどまで異なることができる。例えば、SiGe層を50%Siで500厚さにすべき場合には、典型的には、10厚さの50のSi及びGeの副層（各々25）にする。副層の最適な厚さは、主として、これらの層をプレーナ法により成長させ、欠陥形成を最小にする能力に応じて決まる。Si及びGeの副層は、典型的には、歪まされるため、歪み緩和転位が形成される厚さがある。緩和Siのものに近い（基板表面に平行の）面内格子パラメータをもつ基板においては、Ge副層は10から20を超えるべきではないが、Si副層は数百までになってもよい。緩和Geのものに近い面内格子パラメータをもつ基板においては、Si副層は10から20を超えるべきではないが、Ge副層は数百までになってもよい。

20

【0014】

さらに、基板層3における質量変動の効果を制限することが望ましい（例えば、基板がSGOIである場合には、層3自体がSiGeである）。このことは、層3の厚さが層50のほんの何分の1かになるように層3を薄くすることにより（例えば、研磨することにより）、Si/Ge副層41、42等の堆積前に行うことができる。層50が500厚さであり、Si及びGeの各々が25の副層を含む上述の例においては、層3は50まで薄くすることができる。

30

【0015】

Si及びGeのすべての交互の副層を含む複合層50は、超格子として見ることができ、より具体的には、SiGeの順序付けられた合金又はデジタル合金として見ることができる。各々の副層には1つの要素だけが存在するため、複合層における質量変動は、ランダム合金層におけるより少ないと注目されたい。したがって、Si/Ge複合層50の熱伝導率は、通常通りに堆積されたSiGe層より大きい。

40

【0016】

本実施形態においては、基板の上方層3は、SGOI構造体におけるSiGe層であり、最初に堆積される副層41はSiである。当業者に理解されるように、この構成は、基板と堆積された層との間の好ましい界面という利点を与え、具体的には、シリコンの成長

50

が、成長界面における酸素の量を減少させる傾向をもち、これが、より高品質の結晶層をもたらす。

#### 【0017】

或いは、所望の場合には、最初に堆積される副層はGeであってもよい。上述のように、Si/Ge層50は、さらに、バルクSi上、バルク基板上の既存のSiGe上、又はSOI基板上に形成してもよい。

#### 【0018】

副層42、43、43等の各々は、成長テンプレートとして作用する基板層3の面内格子パラメータにより求められた格子の不一致により歪まされる。例えば、基板層3が完全に緩和された $Si_{0.5}Ge_{0.5}$ 層である場合には、Si副層は約2.0%の引張り歪みをもち、Ge副層は約2.2%の圧縮歪みをもつ。しかし、複合層50は全体として、事実上ゼロの応力を有し、歪みSi層を形成する目的のために、緩和SiGe層として機能する。層50上に堆積されたSiの層61は、したがって、歪みSi層になり(図6を参照されたい)、Si/SiGeの複合物61、50は、SiGeがランダム合金であるSi/SiGe二重層より高い熱伝導率を有する。

#### 【0019】

本実施形態においては、源51、52により送給されたSi及びGe(例えば、それぞれ $SiH_4$ ガス及び $GeH_4$ ガス)は同位体で標識されていない。しかし、同位体標識源を用いて、個々のSi及びGeの副層において非常に低い質量変動を実現することができ、したがって、Si/Ge層50の熱伝導率をさらに改善することができる。

#### 【0020】

本発明は、特定の実施形態について説明されたが、上記の説明を考慮して、幾多の代替的手法、修正、及び変形態様が当業者に明らかであることが明白である。したがって、本発明は、本発明の範囲及び精神並びに特許請求の範囲に入るそうした代替的手法、修正、及び変形態様を包含することを意図する。

#### 【図面の簡単な説明】

#### 【0021】

【図1】典型的なSOI基板の概略図である。

【図2】同位体標識Si源及びGe源を用いるSiGe層形成技術を示す。

【図3】SiGe層とSi層を熱混合することにより形成されたSiGeオン・インシユレータ(SGOI)構造体の概略図である。

【図4】SGOI基板上の歪みSi層を示す。

【図5】本発明による、SOI又はSGOI基板上に質量変動が低いデジタルSiGe合金層を形成するプロセスの概略図である。

【図6】図5のSiGe合金層上に堆積された歪みSi層を示す。

10

20

30

【図1】

【図4】

【図2】

【図5】

【図3】

【図6】

---

フロントページの続き

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 ベデル、ステファン、ダブリュー

アメリカ合衆国 12590 ニューヨーク州 ワピンジャーズ・フォールズ ニコール・ドライ

ブ 32

(72)発明者 チエン、ホワジー

アメリカ合衆国 06810 コネチカット州 ダンベリー アバロン・レイク・ロード 622

(72)発明者 フォーゲル、キース

アメリカ合衆国 12533 ニューヨーク州 ホーブウェル・ジャンクション ドリュー・ドロ

ップ・レーン 7

(72)発明者 ミッチャエル、ライアン・エム

アメリカ合衆国 12515 ニューヨーク州 クリントンデール プリンス・ウッズ・ロード

67

(72)発明者 サダナ、デベンドラ・ケー

アメリカ合衆国 10570 ニューヨーク州 プレザントビル スカイ・トップ・ドライブ 9

0

審査官 太田 一平

(56)参考文献 特開平05-129201(JP, A)

特開平04-335519(JP, A)

特開平03-019211(JP, A)

B. Yang, W. L. Liu, J. L. Liu, K. L. Wang, and G. Chen, Measurements of anisotropic t

hermoelectric properties in superlattices, Applied Physics Letters, 米国, 2002年

11月 4日, vol.81, p.3588-3590

(58)調査した分野(Int.Cl., DB名)

H01L 21/20

H01L 21/205

H01L 21/31

H01L 21/365

H01L 21/469

H01L 21/86