등록특허 10-2046791

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년11월20일

(11) 등록번호 10-2046791

(24) 등록일자 2019년11월14일

- (51) 국제특허분류(Int. Cl.)

*H02N 2/06* (2006.01) *H02M 3/155* (2006.01)

- (21) 출원번호 10-2013-0037000

(22) 출원일자 2013년04월04일

심사청구일자 2018년02월02일

- (65) 공개번호 10-2013-0113387

(43) 공개일자 2013년10월15일

(30) 우선권주장

13/440,110 2012년04월05일 미국(US)

(56) 선행기술조사문헌

JP2006333678 A\*

US20010004181 A1\*

JP2010220466 A

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

제너럴 일렉트릭 캄파니

미합중국 뉴욕 (우편번호 12345) 쉐넥테디 원 리

베 로우드

(72) 발명자

글래저 존 스탠리

미국 뉴욕주 12309 니스카유나 리서치 셔클 1

라마바드란 라마누점

미국 뉴욕주 12309 니스카유나 리서치 셔클 1

(74) 대리인

제일특허법인(유)

전체 청구항 수 : 총 13 항

심사관 : 장성진

## (54) 발명의 명칭 압전 부하 구동 시스템 및 그 제조 방법

## (57) 요 약

드라이버 시스템(driver system)은 직류 전압원(direct voltage source) 및 제 1 양방향 직류/직류 변환기(first bi-directional DC-to-DC converter)를 포함하되, 상기 제 1 양방향 직류/직류 변환기는 상기 직류 전압원에 결합된 일단(a primary side) 및 타단(a secondary side)을 구비하고, 상기 일단 상의 제 1 전압을 상기 (뒷면에 계속)

## 대 표 도

타단 상의 제 2 전압으로 변환하도록 구성된다. 상기 드라이버 시스템은 또한 상기 직류 전압원에 결합된 일단 및 상기 제 1 양방향 직류/직류 변환기 타단에 결합된 타단을 구비하되, 상기 일단 상의 상기 제 1 전압을 상기 타단 상의 제 3 전압으로 변환하도록 구성된 제 2 양방향 직류/직류 변압기를 포함한다. 상기 제 1 및 제 2 양방향 직류/직류 변압기는 상기 제 1 전압을 승압(boost)할 수 있고, 상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수(complement)이다. 상기 제 2 및 제 3 전압 사이의 전압 차이(voltage difference)는 상기 제 1 제어 신호의 증폭(amplification)을 포함하는 출력 전압을 포함한다.

---

## 명세서

### 청구범위

#### 청구항 1

드라이버 시스템(a driver system)으로서,

직류(DC) 전압원(104)과,

제 1 양방향 직류/직류 변환기(a first bi-directional DC-to-DC converter)(106) - 상기 제 1 양방향 직류/직류 변환기는 상기 직류 전압원에 결합된 제 1 일단(a first primary side) 및 제 1 타단(a first secondary side)을 구비하고, 상기 제 1 양방향 직류/직류 변환기의 상기 제 1 일단 상의 제 1 전압을 상기 제 1 양방향 직류/직류 변환기의 상기 제 1 타단 상의 제 2 전압으로 변환시키는 것을 제어하도록 구성된 제 1 제어 신호를 수신하도록 구성된 제어 입력부(control input)를 포함함 - 와,

제 2 양방향 직류/직류 변환기(second bi-directional DC-to-DC converter)(108) - 상기 제 2 양방향 직류/직류 변환기는 상기 직류 전압원에 결합되는 제 2 일단 및 상기 제 1 양방향 직류/직류 변환기의 상기 제 1 타단에 결합되는 제 2 타단을 구비하고, 상기 제 2 양방향 직류/직류 변환기의 상기 제 2 일단 상의 상기 제 1 전압을 상기 제 2 양방향 직류/직류 변환기의 상기 제 2 타단 상의 제 3 전압으로 변환시키는 것을 제어하도록 구성된 제 2 제어 신호를 수신하도록 구성된 제어 입력부를 포함함 - 와,

상기 제 1 양방향 직류/직류 변환기 및 상기 제 2 양방향 직류/직류 변환기에 결합된 제어 시스템(control system)을 포함하되,

상기 제어 시스템은:

교류(AC) 전압원에 의해 생성된 기준 신호에 근거하여 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 생성하고,

상기 제 1 양방향 직류/직류 변환기 및 상기 제 2 양방향 직류/직류 변환기로 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 각각 공급하도록 구성되고,

상기 제 1 양방향 직류/직류 변환기(106) 및 상기 제 2 양방향 직류/직류 변환기(108)는 상기 제 1 전압을 승압(boost)시킬 수 있고,

상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수(complement)이고,

상기 제 2 전압과 상기 제 3 전압 사이의 전압 차이(voltage difference)는 출력 전압(output voltage)을 포함하고,

상기 출력 전압은 상기 제 1 제어 신호의 증폭(amplification)을 포함하고,

상기 제어 시스템은:

함수 생성기(function generator) 및 룩 업 테이블(look-up table) 중 하나를 통해 결정된 복수의 디지털 값으로부터 아날로그 신호를 생성하도록 구성된 디지털-아날로그 변환기와,

상기 아날로그 신호를 오버샘플링하도록 구성된 시그마-델타 변조기- 상기 오버샘플링은 상기 아날로그 신호가 생성될 때 생성된 아티팩트를 더 높은 주파수로 이동시킴 - 와,

원치않는 주파수 성분을 제거하기 위해 상기 시그마-델타 변조기의 출력을 필터링도록 구성된 필터와,

상기 필터링된 출력으로부터 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 생성하도록 구성된 변조기를 더 포함하는

드라이버 시스템.

#### 청구항 2

제 1 항에 있어서,

상기 드라이버 시스템은 제 1 단자(a first terminal) 및 제 2 단자(a second terminal)를 구비하는 무효 부하(reactive load)(102)를 더 포함하되,

상기 제 1 양방향 직류/직류 변환기는 상기 무효 부하의 상기 제 1 단자에 결합되는 제 1 타단 단자, 및 제 2 타단 단자를 포함하고,

상기 제 2 양방향 직류/직류 변환기는 상기 무효 부하의 상기 제 2 단자에 결합되는 제 1 타단 단자, 및 상기 제 1 양방향 직류/직류 변환기의 상기 제 2 타단 단자에 결합되는 제 2 타단 단자를 포함하는

드라이버 시스템.

### 청구항 3

제 2 항에 있어서,

상기 무효 부하(102)는 압전 부하(piezoelectric load)를 포함하는

드라이버 시스템.

### 청구항 4

제 2 항에 있어서,

상기 제 1 양방향 직류/직류 변환기(106)는 상기 직류 전압원에 결합된 제 1 일단 단자 쌍(a first pair of primary-side terminals)을 더 포함하고,

상기 제 2 양방향 직류/직류 변환기(108)는 상기 직류 전압원에 결합된 제 2 일단 단자 쌍을 더 포함하는 드라이버 시스템.

### 청구항 5

제 4 항에 있어서,

상기 제 1 양방향 직류/직류 변환기의 상기 제 2 타단 단자는 상기 제 1 양방향 직류/직류 변환기의 상기 제 1 일단 단자 쌍 중 하나, 및 상기 제 2 양방향 직류/직류 변환기의 상기 제 2 일단 단자 쌍 중 하나에 결합되는 드라이버 시스템.

### 청구항 6

제 2 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 제 1 양방향 직류/직류 변환기 및 상기 제 2 양방향 직류/직류 변환기 각각은,

변압기(transformer) - 상기 변압기는 일단 권선(winding) 및 타단 권선(winding)을 포함함 - 와,

상기 일단 권선에 결합된 제 1 스위치와,

상기 타단 권선에 결합된 제 2 스위치를 포함하는

드라이버 시스템.

### 청구항 7

제 6 항에 있어서,

상기 제 1 양방향 직류/직류 변환기의 상기 타단 권선은 상기 무효 부하의 상기 제 1 단자에 결합되고,

상기 제 2 양방향 직류/직류 변환기의 상기 타단 권선은 상기 무효 부하의 상기 제 2 단자에 결합되고,

상기 제 1 양방향 직류/직류 변환기의 상기 제 2 스위치는 상기 제 2 양방향 직류/직류 변환기의 상기 제 2 스위치에 더 결합되는

드라이버 시스템.

#### 청구항 8

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 출력 전압은 상기 제 1 제어 신호의 실질적인 선형 증폭(a substantially linear amplification)을 포함하는

드라이버 시스템.

#### 청구항 9

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 제 2 전압은 상기 제 1 제어 신호의 비선형 증폭이고,

상기 제 3 전압은 상기 제 1 제어 신호의 비선형 증폭인

드라이버 시스템.

#### 청구항 10

삭제

#### 청구항 11

제 1 항에 있어서,

상기 제어 시스템은 펄스 폭 변조기(pulse-width modulator)를 포함하는

드라이버 시스템.

#### 청구항 12

제 1 항 또는 제 11 항에 있어서,

상기 제어 시스템은 상기 제 2 전압 및 상기 제 3 전압을 기초로 피드백 전압(feedback voltage)을 측정하도록 구성된 피드백 회로(feedback circuit)를 더 포함하고,

상기 제어 시스템은 상기 피드백 전압을 기초로 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 수정하도록 더 구성되어 상기 제 2 전압 및 상기 제 3 전압이 타겟 세트(target set)의 전압값들과 실질적으로 일치하도록 하는

드라이버 시스템.

#### 청구항 13

제 1 항 또는 제 11 항에 있어서,

상기 제어 시스템은 상기 출력 전압이 상기 제 1 제어 신호 및 상기 제 2 제어 신호의 선형 승압 변환(linear boost conversion)의 수용가능 근사치가 되게 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 수정하도록 구성된 전치 왜곡(pre-distortion) 컨트롤러를 더 포함하는

드라이버 시스템.

#### 청구항 14

삭제

#### 청구항 15

압전 드라이버(a piezoelectric driver)(100)를 제조하는 방법으로서,

직류(DC) 전압원(104)을 제 1 전압 변환기의 저전압 측 및 제 2 전압 변환기의 저전압 측에 결합하는 단계 - 상기 제 1 전압 변환기 및 상기 제 2 전압 변환기는 상기 직류 전압원으로부터 전압을 승압시킬 수 있는 양방향 직류/직류 전압 변환기(106, 108)를 포함함 - 와,

상기 제 1 전압 변환기의 고전압 측 상의 제 1 고전압 측 단자를 압전 액추에이터(piezoelectric actuator)의 제 1 측에 결합하는 단계와,

상기 제 2 전압 변환기의 고전압 측 상의 제 1 고전압 측 단자를 상기 압전 액추에이터의 제 2 측에 결합하는 단계와,

상기 제 1 전압 변환기의 제 2 고전압 측 단자를 상기 제 2 전압 변환기의 제 2 고전압 측 단자에 결합하는 단계와,

제어 시스템을 상기 제 1 전압 변환기 및 상기 제 2 전압 변환기에 결합하는 단계와,

제 1 제어 신호를 상기 제 1 전압 변환기로 공급하고 제 2 제어 신호를 상기 제 2 전압 변환기로 공급하도록 상기 제어 시스템을 구성하는 단계를 포함하되,

상기 제 1 제어 신호는 상기 제 1 전압 변환기의 상기 저전압 측 상의 상기 직류 전압원으로부터의 전압을 상기 제 1 전압 변환기의 상기 고전압 측 상의 제 1 출력 전압으로 변환하도록 상기 제 1 전압 변환기를 제어하도록 구성되고,

상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수(complement)이고, 상기 제 2 전압 변환기의 상기 저전압 측 상의 상기 직류 전압원으로부터의 전압을 상기 제 2 전압 변환기의 상기 고전압 측 상의 제 2 출력 전압으로 변환하도록 상기 제 2 전압 변환기를 제어하도록 구성되며,

상기 제 1 출력 전압과 제 2 출력 전압 사이의 전압 차이(voltage difference)는 상기 제 1 제어 신호의 증폭을 포함하는 전압차를 포함하되,

상기 제어 시스템을 구성하는 단계는:

교류(AC) 전압원에 의해 생성된 기준 신호에 근거하여 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 생성하는 단계와,

상기 제 1 전압 변환기 및 상기 제 2 전압 변환기로 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 각각 공급하는 단계를 포함하며,

상기 제 1 제어 신호 및 상기 제 2 제어 신호를 생성하는 단계는:

함수 생성기(function generator) 및 룩 업 테이블(look-up table) 중 하나를 통해 결정된 복수의 디지털 값으로부터 아날로그 신호를 생성하는 단계와,

상기 아날로그 신호를 오버샘플링하는 단계- 상기 오버샘플링은 상기 아날로그 신호가 생성될 때 생성된 아티팩트를 더 높은 주파수로 이동시킴 -와,

원치않는 주파수 성분을 제거하기 위해 상기 오버샘플링하는 단계의 출력을 필터링하는 단계와,

상기 필터링된 출력으로부터 상기 제 1 제어 신호 및 상기 제 2 제어 신호를 생성하는 단계를 포함하는

것인

압전 드라이버 제조 방법.

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

### 발명의 설명

### 기술 분야

[0001] 본 발명의 실시예는 일반적으로 압전 액추에이터(piezoelectric actuators)와 관련되고, 보다 구체적으로, 압전 액추에이터를 위한 드라이버 회로(a driver circuit)와 관련된다.

[0002]

압전 재료(piezoelectric materials)는 전기장 애플리케이션에서 부피(dimension)를 변화시키는 것으로 알려져 있다. 이러한 현상은 압전 재료의 사용이 MEMS(micro-electro-mechanical systems) 장치에서 액추에이터로서 사용되도록 한다. 예를 들어, 그러한 액추에이터는 합성 제트 액추에이터(synthetic jet actuators)에서 사용되어 왔는데 이 합성 제트 액추에이터는 표면상의 유체의 흐름에 영향을 미치도록 유체의 합성 제트를 발생시킨다. 전형적인 합성 제트 액추에이터는 내부 챔버를 정의하는 하우징을 포함한다. 구멍(orifice)은 하우징 벽에 존재한다. 액추에이터는 내부 챔버 내에서 주기적으로 부피를 변화시키기 위해 하우징 안 또는 하우징 근처에 메커니즘을 더 포함하여 일련의 유체 소용돌이가 발생하여 하우징의 구멍으로부터 외부 환경 밖으로 분사되도록 한다. 부피 변화 메커니즘의 예시는 예를 들어, 피스톤 왕복 동작 동안 구멍 안으로 및 안으로부터 유체를 이동시키기 위해 제트 하우징 내 위치한 피스톤이나 하우징 벽으로서 기능하는 플렉서블 다이어프램(flexible diaphragm)을 포함할 수 있다. 플렉서블 다이어프램은 일반적으로 압전 액추에이터 또는 기타 적절한 수단에 의해 작동된다.

[0003]

일반적으로, 압전 액추에이터는 종종 적절한 작동을 위해 수십 볼트 또는 그 이상의 전압을 요구하고, 일부 등급의 액추에이터는 가변 주파수 및 진폭을 가지는 교류(AC) 전압을 요구할 수 있다. 압전 액추에이터가 가령, 휴대용, 소비자, 항공 또는 수송 전기 장치에서와 같이 저전압 전기 회로망과 접속되는 경우, 이러한 액추에이터를 구동하는 것은 어려워질 수 있다. 예를 들어, 전원으로부터 가능한 것보다 더 높은 피크 전압을 나타내는 가변값 또는 교류 전압 파형을 가지는 압전 액추에이터를 구동할 때, 잘 알려진 방법에 따르면 종종 복잡한, 비효율적인, 크기가 큰, 및/또는 비싼 드라이버를 이용하여 이러한 목적을 달성한다. 게다가, 압전 액추에이터가 사용되는 많은 애플리케이션은 최소 소비 전력 사용을 요구하고, 낮은 효율성을 갖는 비효율적인 압전 액추에이터 드라이버는 종종 그러한 최소 소비 전력 요구를 충족하지 못한다.

[0004]

따라서, 저전압원으로부터 작동할 수 있고 가변 주파수 및 진폭을 가진 제어 가능한 고전압 교류 파형을 효율적으로 생성할 수 있는 효율성 높은 드라이버 회로를 제공하기 위한 압전 부하 구동 시스템이 필요하다.

## 발명의 내용

[0005]

본 발명에 관한 일 양태를 따르면, 드라이버 시스템(a driver system)은 직류 전압원(a direct current voltage source) 및 제 1 양방향 직류/직류 변환기(a first bi-directional DC-to-DC converter)를 포함하되, 상기 제 1 양방향 직류/직류 변환기는 상기 직류 전압원에 결합된 일단(a primary side) 및 타단(a secondary side)을 구비하고, 상기 제 1 양방향 직류/직류 변환기의 상기 일단 상의 제 1 전압을 상기 제 1 양방향 직류/직류 변환기의 상기 타단 상의 제 2 전압으로 변환시키는 것을 제어하도록 구성된 제 1 제어 신호를 수신하도록 구성된 제어 입력부(control input)를 포함한다. 또한 상기 드라이버 시스템은 제 2 양방향 직류/직류 변환기(second bi-directional DC-to-DC converter)을 포함하되, 상기 제 2 양방향 직류/직류 변환기는 상기 직류 전압원에 결합되는 일단 및 상기 제 1 양방향 직류/직류 변환기의 상기 타단에 결합되는 타단을 구비하고 상기 제 2 양방향 직류/직류 변환기의 상기 일단 상의 상기 제 1 전압을 상기 제 2 양방향 직류/직류 변환기의 상기 타단의 제 3 전압으로 변환시키는 것을 제어하도록 구성된 제 2 제어 신호를 수신하도록 구성된 제어 입력부를 포함한다. 상기 제 1 및 제 2 양방향 직류/직류 변환기는 상기 제 1 전압을 승압(boost)시킬 수 있고, 상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수(complement)이다. 상기 제 2 및 제 3 전압 사이의 전압 차이(voltage difference)는 출력 전압(output voltage)을 포함하고, 상기 출력 전압은 상기 제 1 제어 신호의 증폭(amplification)을 포함한다.

[0006]

본 발명의 다른 양태에 따르면, 압전 드라이버(a piezoelectric driver)를 제조하는 방법은 직류 전압원을 제 1 전압 변환기의 저전압 측 및 제 2 전압 변환기의 저전압 측에 결합하되, 상기 제 1 및 제 2 전압 변환기는 상기 직류 전압원으로부터 전압을 승압시킬 수 있는 양방향 직류/직류 전압 변환기를 포함하는 단계를 포함한다. 또한, 본 방법은 상기 제 1 전압 변환기의 고전압 측 상의 제 1 고전압 측 단자를 압전 액추에이터(piezoelectric actuator)의 제 1 측에 결합하는 단계, 및 상기 제 2 전압 변환기의 고전압 측 상의 제 1 고전압 측 단자를 상기 압전 액추에이터의 제 2 측에 결합하는 단계, 그리고 상기 제 1 전압 변환기의 제 2 고전압 측 단자를 상기 제 2 전압 변환기의 제 2 고전압 측 단자에 결합하는 단계를 포함한다. 또한, 본 방법은 제어 시스템을 상기 제 1 및 제 2 전압 변환기에 결합하는 단계, 및 상기 제어 시스템이 제 1 제어 신호를 상기 제 1 전압 변환기로 공급하고 제 2 제어 신호를 상기 제 2 전압 변환기로 공급하도록 구성하는 단계를 포함한다. 상기 제 1 제어 신호는 상기 제 1 전압 변환기의 상기 저전압 측 상의 상기 직류 전압원으로부터의 전압을 상기 제 1 전압 변환기의 상기 고전압 측 상의 제 1 출력 전압으로 변환하도록 상기 제 1 전압 변환기를 제어하도록

구성되고, 상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수(complement)이고, 상기 제 2 전압 변환기의 상기 저전압 측 상의 상기 직류 전압원으로부터의 전압을 상기 제 2 전압 변환기의 상기 고전압 측 상의 제 2 출력 전압으로 변환하도록 상기 제 2 전압 변환기를 제어하도록 구성된다. 상기 제 1 및 제 2 출력 전압 사이의 전압 차이(voltage difference)는 상기 제 1 제어 신호의 증폭을 포함하는 전압차를 포함한다.

[0007] 본 발명의 또 다른 양태에 따르면, 압전 드라이버(a piezoelectric driver)는 저전압 측 및 고전압 측을 구비하는 제 1 양방향 직류/직류 전압 변환기 및 저전압 측 및 고전압 측을 구비하는 제 2 양방향 직류/직류 전압 변환기를 포함한다. 상기 제 1 양방향 직류/직류 전압 변환기는 제 1 고전압 측 단자, 제 2 고전압 측 단자를 포함하되, 상기 제 1 양방향 직류/직류 변환기는 상기 제 1 고전압 측 단자의 전압을 승압(boost)시킬 수 있다. 상기 제 2 양방향 직류/직류 전압 변환기는 제 1 고전압 측 단자, 상기 제 1 전압 변환기의 상기 제 2 고전압 측 단자에 결합된 제 2 고전압 측 단자를 포함하고, 상기 제 2 양방향 직류/직류 변환기는 상기 제 1 고전압 측 단자의 전압을 승압시킬 수 있다. 또한, 상기 압전 드라이버는 상기 제 1 및 제 2 양방향 직류/직류 변환기의 상기 저전압 측에 결합된 직류 전압원, 상기 제 1 양방향 직류/직류 전압 변환기의 제 1 고전압 측 단자에 결합되고 상기 제 2 양방향 직류/직류 전압 변환기의 상기 제 1 고전압 측 단자에 연결되는 압전 액추에이터, 및 상기 제 1 및 제 2 전압 변환기에 결합되는 제어 시스템을 포함한다. 상기 제어 시스템은 상기 제 1 양방향 직류/직류 전압 변환기에 제 1 제어 신호를 공급하되, 상기 제 1 양방향 직류/직류 전압 변환기의 상기 저전압 측 상의 전압을 상기 제 1 양방향 직류/직류 전압 변환기의 상기 고전압 측 상의 제 1 출력 전압으로 변환하도록 상기 제 1 제어 신호는 상기 제 1 양방향 직류/직류 전압 변환기를 제어하도록 구성된다. 또한, 상기 제어 시스템은 상기 제 2 양방향 직류/직류 전압 변환기로 제 2 제어 신호를 공급하되, 상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수이고 상기 제 2 양방향 직류/직류 변환기의 상기 저전압 측 상의 전압을 상기 제 2 양방향 직류/직류 전압 변환기의 상기 고전압 측 상의 제 2 출력 전압으로 변환하도록 상기 제 2 양방향 직류/직류 전압 변환기를 제어하도록 구성된다. 상기 제 1 및 제 2 출력 전압 사이의 전압 차이는 상기 제 1 제어 신호의 증폭을 포함하는 전압 차이를 포함한다.

[0008] 이러한 및 기타 이점 및 특징은 첨부된 도면과 연결되어 제공된 본 발명의 바람직한 실시예에 관한 다음의 상세한 설명으로부터 보다 쉽게 이해될 것이다.

### 도면의 간단한 설명

[0009] 도면은 본 발명을 실시하기 위해 제시된 실시예를 개략적으로 설명한다.

도면에서,

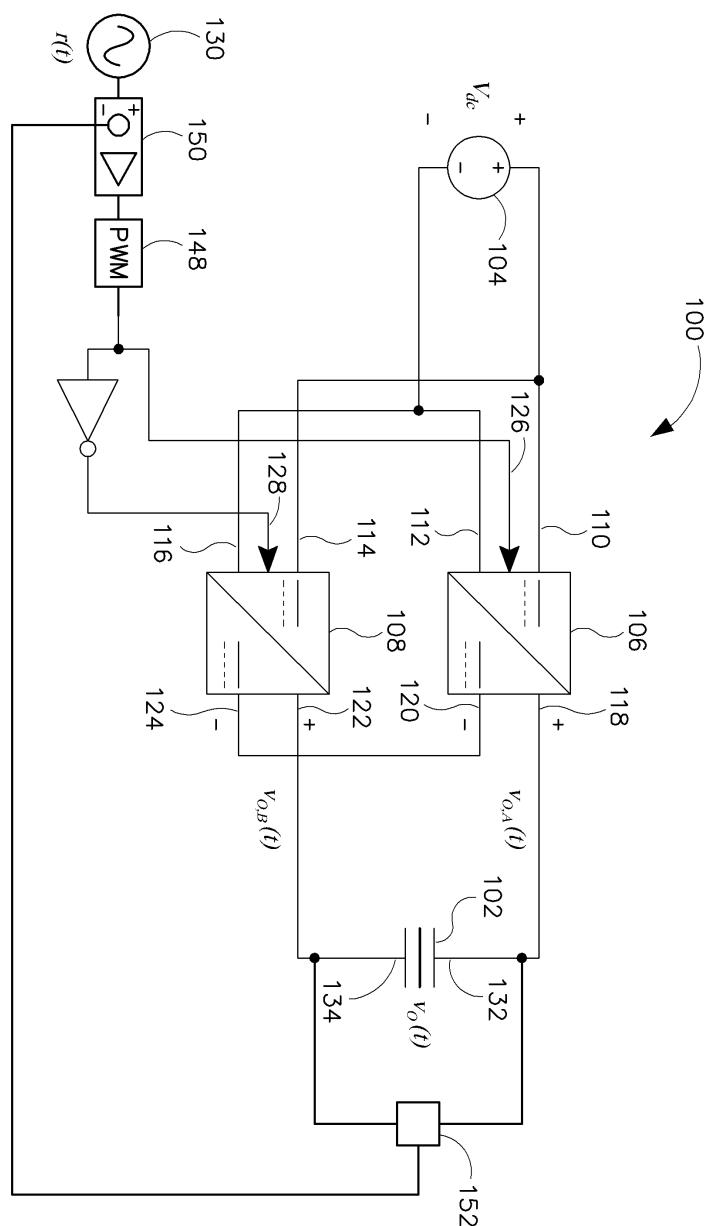

도 1은 본 발명의 일 실시예를 따르는 압전 부하를 위한 압전 드라이버를 개략적으로 나타낸 개략적인 블록 다이어그램이다.

도 2는 본 발명의 일 실시예를 따르는 압전 부하를 위한 압전 드라이버 회로를 개략적으로 나타낸 개략도이다.

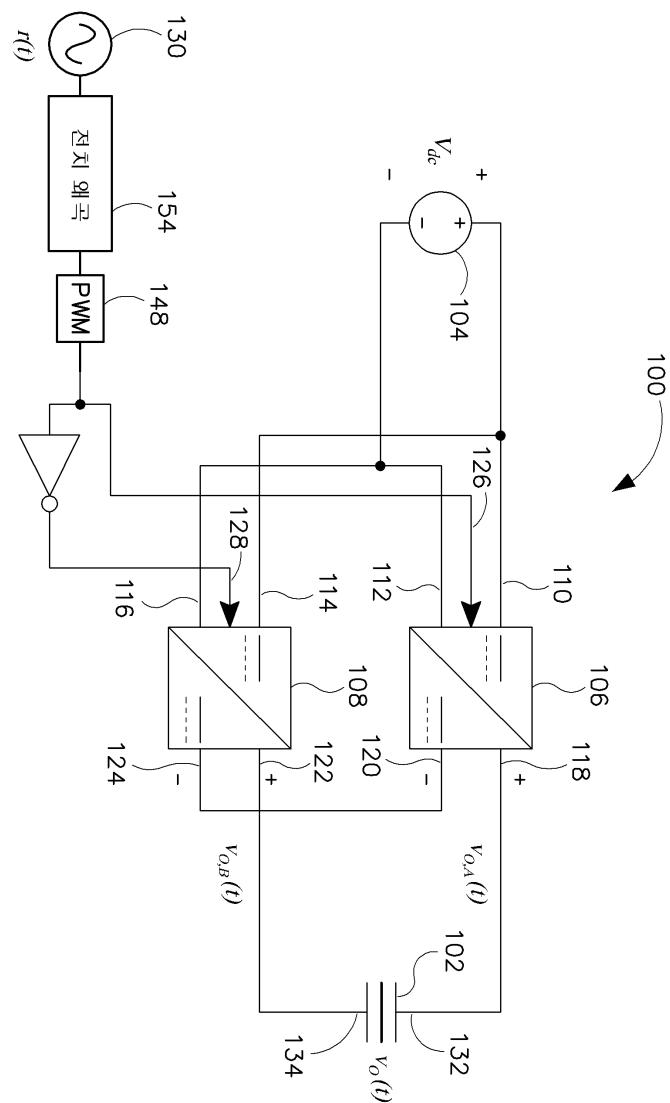

도 3은 본 발명의 다른 실시예를 따르는 압전 드라이버를 개략적으로 나타낸 개략적인 블록 다이어그램이다.

도 4는 본 발명의 다른 실시예를 따르는 압전 드라이버를 개략적으로 나타낸 개략적인 블록 다이어그램이다.

도 5는 본 발명의 일 실시예를 따르는 기준 신호 발생기를 개략적으로 나타낸 개략적인 블록 다이어그램이다.

### 발명을 실시하기 위한 구체적인 내용

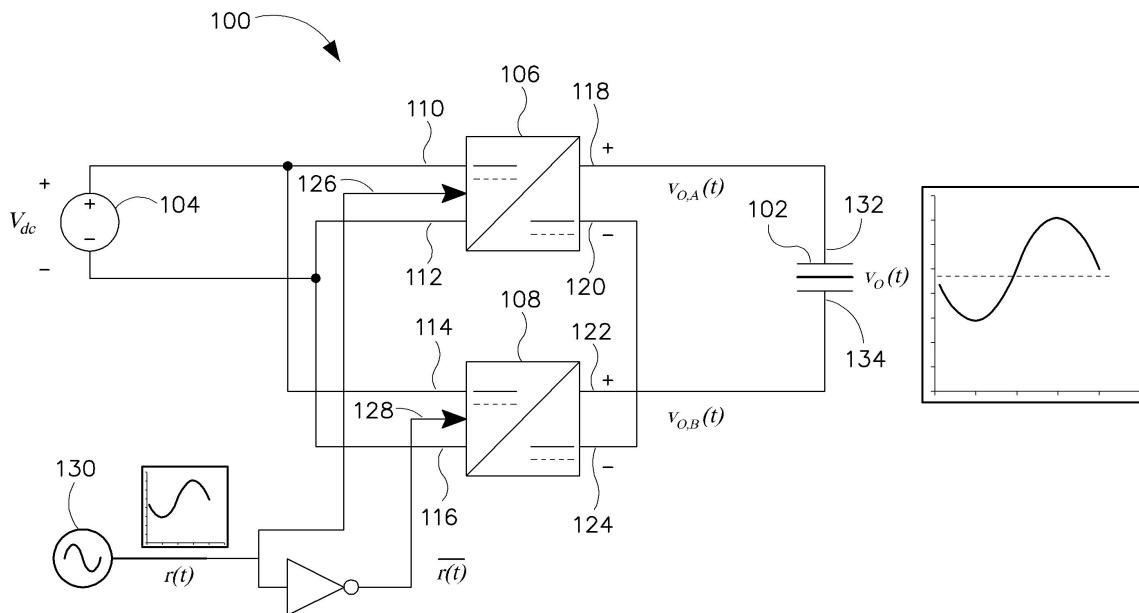

[0010] 도 1을 살펴보면, 개략적인 블록 다이어그램은 압전 부하(a piezoelectric load) 또는 액추에이터(actuator)(102)에 결합한 압전 드라이버(a piezoelectric drive)(100)를 개략적으로 나타낸다. 압전 부하(102)는 용량형(capacitive) 또는 무효 부하(reactive load)이다.

[0011] 압전 드라이버(100)는 전압원(a voltage source)(104)과 제 1 및 제 2 변환기(first and second converters)(106, 108)를 포함한다. 제 1 및 제 2 변환기(106, 108)는 직류/직류 양방향 변환기/증폭기로, 저전압 측 변환기 단자(low-side converter terminals)(110, 112 및 114, 116) 각각의 쌍에 공급된 전압원(104)으로부터의 전압을 취하고, 상기 공급된 전압을 고전압 측 변환기 단자(high-side converter terminals)(118, 120 및 122, 124) 각각의 쌍으로 승압하도록 구성된다. 제 1 및 제 2 변환기(106, 108)는 또한 각 단자(118, 120 및 122, 124)에서 각 단자(110, 112 및 114, 116)로 전압을 강압(buck)한다. 제 1 변환기(106)는 전압원

(104)으로부터의 전압  $v_{dc}$ 를 출력 전압  $v_{OA}$ 로 변환하고, 제 2 변환기(108)는 전압원(104)으로부터의 전압  $v_{dc}$ 를 출력 전압  $v_{OB}$ 로 변환하도록 구성된다. 일 실시예에서, 출력 전압  $v_{OA}$  및  $v_{OB}$ 는 전압  $v_{dc}$ 를 비선형 증폭(non-linear amplifications)한 것이다. 하지만, 전압  $v_{OA}$  및  $v_{OB}$  사이의 차이는 거의 선형 스케일(linear scaled)이거나 전압  $v_{dc}$ 의 승압된 값(boosted version)이다.

[0012] 일 실시예에서, 제 1 및 제 2 컨버터(106, 108)는 상당히 동일한(identical) 단일-스테이지 양방향 스위치-모드 전력 변환기(single-stage bi-directional switch-mode power converters)이다. 본 명세서에서 사용된 것처럼, 단일-스테이지 변환기는 출력 전압 이전에 입력 전압을 중간 전압으로 변환하지 않고 단일-스테이지로 입력 전압을 출력 전압으로 변환하는 변환기이다.

[0013] 제 1 및 제 2 변환기(106, 108)는 교류 전압원(AC voltage source)(130)에 의해 제공되는 제어 입력부(126, 128) 쌍의 제어 신호에 기초하여 전압을 강압 또는 승압하는데, 교류 전압원(130)은 기준 신호(a reference signal)  $r(t)$ 를 생성하며, 이 기준 신호의 증폭된 값이 압전 부하(102)를 구동하도록 의도되며, 기준 신호  $r$

(t)는 제어 입력부(126)로 제공된다. 기준 신호  $r(t)$ 의 보수인 기준 신호  $\overline{r(t)}$ 는 제어 입력부(128)로 공급된다.

[0014] 제 1 변환기(106)의 변환기 단자(converter terminal)(118)는 압전 부하(102)의 제 1 단자(132)에 결합되고, 제 2 변환기(108)의 변환기 단자(122)는 압전 부하(102)의 제 2 단자(134)에 결합된다. 또한, 변환기 단자(120)는 변환기 단자(124)에 결합된다. 이러한 구성에서, 변환기 단자(118-124)는 압전 부하(102)를 차분하여(differentially) 구동한다. 도 1에 개략적으로 나타낸 것과 같이, 컨버터(106, 108)의 각각의 출력 전압  $v_{OA}$  및  $v_{OB}$ 는 단자(132, 134)에 걸쳐진 전압을 보이는 압전 부하(102)로 공급되는데, 이때 단자(132, 134) 사이의 전압  $v_0$ 는  $v_0 = v_{OA} - v_{OB}$ 로 나타난다. 종종,  $v_0 = k \cdot r(t)$ 가 바람직한데, 여기서  $k$ 는 이득 상수(a constant gain)와 동일하다. 이러한 방식으로, 출력 전압  $v_0$ 는 이득 상수를 기준 신호와 곱한 것과 실질적으로 동일하다.

[0015] 많은 주파수에서, 액추에이터(102)와 같은 압전 부하의 임피던스는 상당한 무효 요소(reactive component)를 갖는다. 이와 같이, 교류 구동 상태에서는 전력이 각 교류 사이클(AC cycle)에서 부하 내부로 및 부하로부터 흐를 것이다. 따라서, 제 1 및 제 2 변환기(106, 108)는 양방향 전력 흐름을 수용하기 위해 이상에서 언급된 바와 같이 양방향 변환기이다.

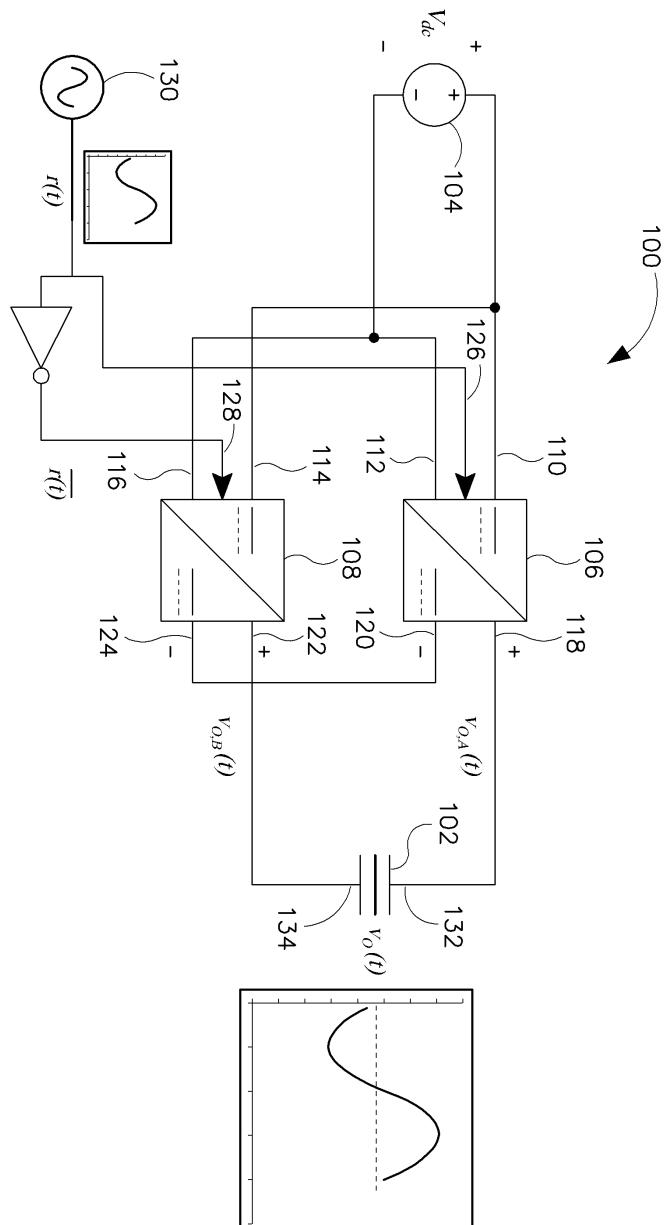

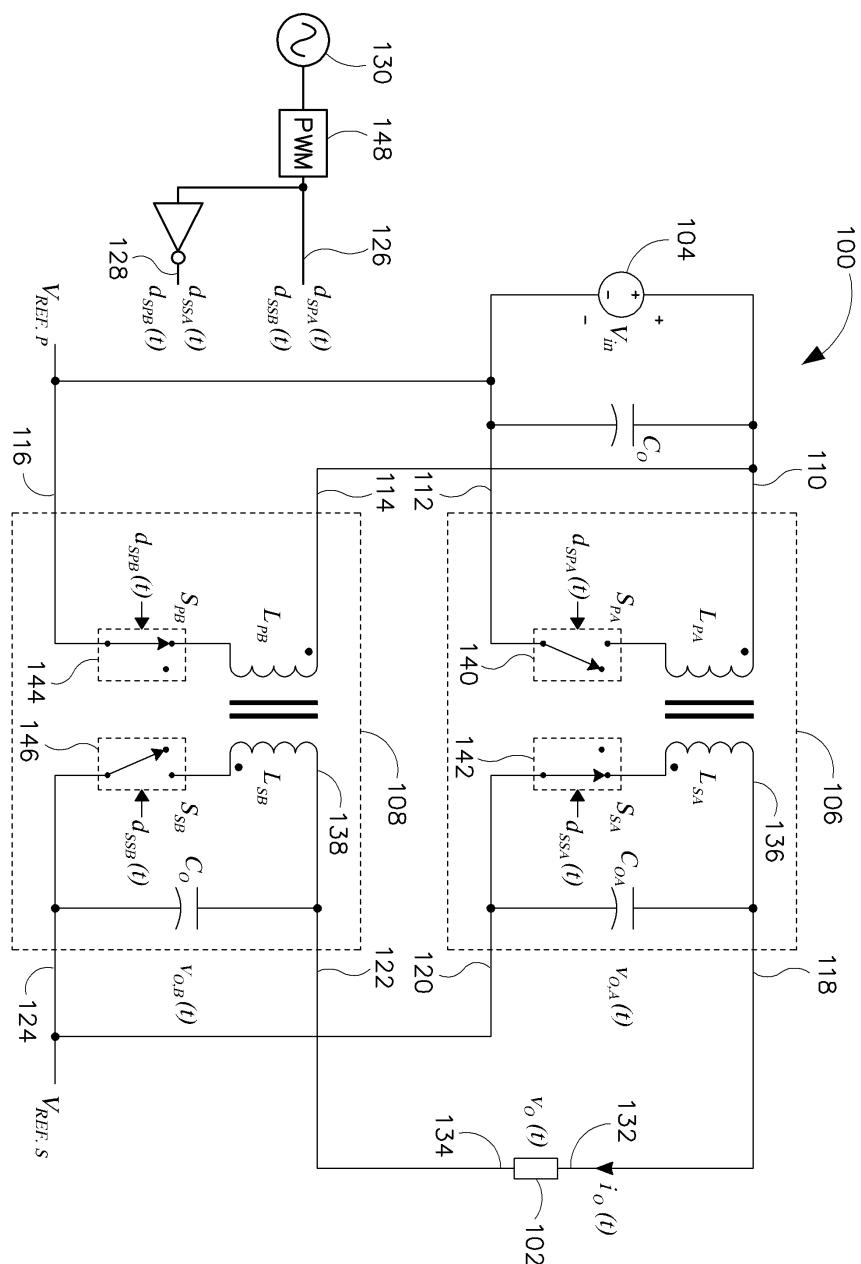

[0016] 제 1 및 제 2 변환기(106, 108)가 전압을 강압 및 승압할 수 있는 임의의 양방향 변환기일 때, 도 2는 본 발명의 실시예에 따라 양방향 플라이백 강압/승압 변환기(bi-directional fly-back buck/boost converter) 실시예를 개략적으로 나타낸다. 그러한 플라이백 변환기는 큰 전압 승압이 필요한 경우 및/또는 분리(isolation)가 필요한 경우에 적합하다. 하지만, 본 발명의 실시예들은 스위칭 손실을 감소시키기 위한 소프트 스위칭(soft-switching) 또는 액티브 클램핑(active clamping)과 같은 변환기 상에서의 변형이 본 명세서에서 설명된 회로들과 함께 또한 사용될 수 있음을 고려한다.

[0017] 보이는 바와 같이, 제 1 및 제 2 변환기(106, 108)는 변압기(transformers)(136, 138) 및 스위치(140, 142 및 144, 146)를 각각 포함한다. 스위치(140-146)는 전원 스위치(power switch)이고, 예를 들어, MOSFETs, IGBTs, SCRs, 및 본 기술 분야에서 알려진 기타 전원 스위치일 수도 있다.

[0018] 일 실시예에서, 펄스폭 변조기(PWM: pulse-width modulator)(148)는 변환기(106, 108)에서의 변환 프로세스(conversion process)를 제어하기 위해 교류 또는 정현파 기준 신호(sinusoidal reference signal)  $r(t)$ 를 제공하도록 제어된다. PMW(148)의 제어 입력부(126)는 스위치(140, 146)에 뚫여 있고 제어 신호  $d_{SPA}(t)$  및  $d_{SSB}(t)$ 를 스위치로 전달하도록 구성된다. 제어 입력부(126)의 역(converse)인 제어 입력부(128)는 스위치(142, 144)에 뚫여 있고 제어 신호  $d_{SPB}(t)$  및  $d_{SSA}(t)$ 를 스위치로 전달하도록 구성된다. 일 실시예에서,  $d_{SPA}(t) = d_{SSB}(t) = k1 \cdot r(t)$ 이고,  $d_{SPB}(t) = d_{SSA}(t) = 1 - k1 \cdot r(t)$ 인데, 여기서  $d_x(t)$ 는 스위치 듀티 사이클(switch duty cycles),  $k1$ 은 상수, 및  $r(t)$ 는 기준 신호이다.

[0019] 노드  $V_{REF,P}$  및  $V_{REF,S}$  쌍은 압전 드라이버(100)의 일단(P) 및 타단(S)에 각각 형성된다. 노드  $V_{REF,P}$  및  $V_{REF,S}$ 는 각각의 접지면(ground plane)에 결합되거나, 예를 들어, 단일 접지면(single ground plane)을 통해 함께 결합될 수도 있다. 단일 접지면을 통해 함께 결합한 노드  $V_{REF,P}$  및  $V_{REF,S}$ 는 압전 드라이버(100)의 설치 비용을 감소시킬

뿐 만 아니라 압전 부하(102)의 구동의 단순화를 돋는다. 공통의 단일 접지면에 결합되는 경우, 변환기 단자(converter terminals)(120 및 124)는 변환기 단자(112 및 116)에 결합된다.

[0020] 제 1 및 제 2 변환기(106, 108)의 제어/출력 함수(control-to output function)가 선형이 아니거나 선형 함수의 허용 근사치가 아닌 경우, 오류 수정(error correction) 또는 오류 감소 방법이 제 1 및 제 2 변환기(106, 108)의 출력을 수정하는데 사용되어 더 선형적인 출력에 근사해지도록 할 수 있다. 도 3은 본 발명의 실시예에 따른 오류 수정 방법에 따라 피드백을 사용하는 예시를 나타내는 블록 다이어그램을 개략적으로 설명한다. 도 3은 도 2의 PWM(148)과 함께 도 1의 압전 드라이버(100)의 요소를 개략적으로 설명한다. 보상기(compensator)(150)는 또한 교류 전압원(130)과 PWM(148) 사이에 결합된 것으로 나타난다. 보상기(150)는 전압 센서(voltage sensor)(152)를 통해 압전 부하(102) 양단에서 측정된 출력 전압  $v_o(t)$ 를 수신한다. 전압 센서(152)로부터 수신된 실제 출력 파형 전압  $v_o(t)$ 은 입력 파형 전압  $r(t)$ 를 수정하는데 사용되는데, 이렇게 수정된 입력 파형 전압에 기초한 제 1 및 제 2 변환기(106, 108)에 대한 PWM 제어가 원하는 출력 전압 파형을 생성하도록 한다. 이러한 방식으로, 입력 파형 전압  $r(t)$ 는 피드백을 이용하여 수정되어 제 1 및 제 2 변환기(106, 108)가 넓은 변환 범위에 걸쳐 선형 변환에 근사한 변환을 하도록 제어한다.

[0021] 도 4는 본 발명의 다른 실시예에 따른 오류 수정 방법으로서 전치 왜곡(pre-distortion)을 사용하는 예시를 나타내는 개략적인 블록 다이어그램을 개략적으로 설명한다. 도 4는 도 2의 PWM(148)과 함께 도 1의 압전 드라이버(100)의 요소를 개략적으로 설명한다. 전치 왜곡 블록(154)은 또한 교류 전압원(130)과 PWM(148) 사이에 결합된 것으로 보여진다. 제 1 및 제 2 변환기(106, 108)에 대한 PWM 제어가 수정된 입력 파형 전압에 기초하여 원하는 출력 전압 파형  $v_o(t)$ 을 생성하도록 하는 것과 같이, 전치 왜곡(154)은 입력 파형 전압  $r(t)$ 를 수정하도록 구성된 컨트롤러 또는 기타 하드웨어 요소를 사용하여 실행될 수 있다. 예를 들어, 파형 범위(waveform range)에 걸쳐 입력 파형 전압  $r(t)$ 에 의해 제어되는 경우, 전치 왜곡 컨트롤러는 제 1 및 제 2 변환기(106, 108)의 알려진 승압 변환 함수 양식(a known boost conversion function behavior)을 기초로 입력 파형 전압  $r(t)$ 를 왜곡하도록 구성된 전치 왜곡 알고리즘과 함께 또는 룩업 테이블(look-up table)과 함께 프로그래밍(programmed)될 수도 있다. 이러한 방식으로, 입력 파형 전압  $r(t)$ 는 미리 결정된 왜곡 수정(pre-determined distortion modification)을 이용하여 수정되어, 제 1 및 제 2 변환기(106, 108)가 넓은 변환 범위에 걸쳐 선형 변환에 가까워지도록 제어한다.

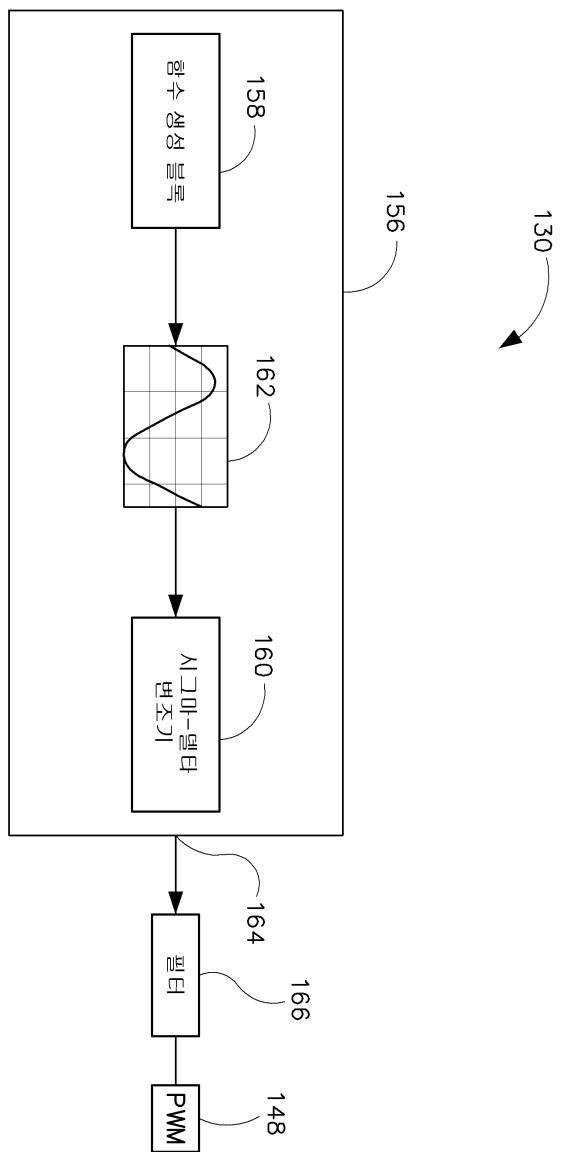

[0022] 도 5는 본 발명의 실시예에 따른 도 1-4에서 개략적으로 설명된 기준 신호  $r(t)$ 를 발생시키는 전압원(130)에 관한 예시를 나타내는 개략적인 블록 다이어그램이다. 이러한 방식으로  $r(t)$ 의 생성은 압전 구동 출력에서의 높은 피델리티(high fidelity)를 얻을 수 있다.

[0023] 기준 신호  $r(t)$ 의 생성은 기준 신호를 합성하기 위해 아날로그 회로(an analog circuit) 또는 디지털 구현(digital implementation)을 사용한다. 간단한 예로, 상기 기준 신호  $r(t)$ 의 생성은 아날로그 회로에서 실시될 수 있다. 예를 들어, 사인파(sine wave) 생성은 빈 브리지(Wein Bridge) 또는 비슷한 오실레이터(oscillator)로 성취될 수도 있다. 하지만, 보다 복잡한 패턴을 생성하기 위해, 또는 변환기에 의해 유도된 왜곡(distortion) 및 비선형 효과(nonlinear effects)를 보상하기 위해, 디지털 구현이 보다 편리하다. FPGA, DSP, 또는 마이크로컨트롤러와 같은 단일 기판 컴퓨터(single board computer)는 이러한 목적을 위해 사용될 수 있다. 디지털 구현에서, 도 4에서 설명된 전치 왜곡(pre-distortion) 또한 포함될 수 있다.

[0024] 도 5는 PWM(148)을 구동할 수 있는 특정 명령 신호(a specified command signal)를 생성하는데 사용되는 컨트롤러(156)를 개략적으로 설명한다. 컨트롤러(156)는 함수 생성(a function generation) 블록(158) 및  $\Sigma$ - $\Delta$ (시그마-델타) 변조기(modulator) 블록(160)을 포함한다. 함수 생성 블록(158)에서, 원하는 파형(desired waveform)은 함수에 따라 또는 룩업 테이블(look-up table)에 따라 프로그래밍될 수 있다. 예를 들어, 함수 생성기(a function generator)는 사용할 디지털 값을 결정하기 위해 알고리즘을 실행할 수도 있다. 그러지 않으면, 룩업 테이블이 미리 계산된 및 저장된 디지털 값을 가질 수도 있다. 디지털 컨트롤러 또는 DSP(도시되지 않음)는 이러한 디지털 값을 취할 수 있고 또한 다양한 방법에 따라 기준 신호  $r(t)$ 를 생성할 수도 있다. 일 실시예에서, 상기 디지털 값은 아날로그 파형을 생성하는 디지털-아날로그 변환기(DAC: Digital to Analog Converter)(162)로 보내질 수 있다. 다른 실시예에서, 상기 디지털 값은 상기 디지털 컨트롤러(156) 내부의 펄스 폭 변조기(도시되지 않음)를 구동할 수 있는데, 펄스 폭 변조기의 출력이 필터들(도시되지 않음)을 통해 후속적으로 여과되어, 원하지 않는 주파수 요소를 제거한다. 또 다른 실시예에서, 상기 디지털 값은 전원 스위치 제어 파형(power switch control waveform)을 직접 생성하는 디지털 PWM(148)을 구동할 수 있다.

[0025]

디지털 파형 생성 방법을 사용할 때의 양자화(quantization)로 인해, 저비용 마이크로컨트롤러(low cost microcontrollers)에서 이용 가능한 비트 수는 일반적으로 제한되고, 이는 파형 구축(waveform construction)에 관한 가시적인 양자(quanta visible) 또는 "단계(steps)"가 있다는 것을 의미한다. 이러한 아티팩트(artifacts)는 컨트롤러(156)의 출력(164)에서 낮은 퍼델리티(low fidelity) 파형 또는 왜곡으로서 나타날 수 있다. 일부 예시에서, 이러한 아티팩트는 예를 들어, 가청 잡음(audible noise) 생성과 같은 원하지 않는 반응을 유발할 수 있다. 기본적인 아날로그 파형은 저 주파수(low frequency)이기 때문에, 이러한 아티팩트를 제거하는 것은 대개 출력(164)에서의 벌키 필터(bulky filter)를 이용하여 고차 조화파(harmonics)를 필터링하는 것을 포함한다. 필터 블록(166)은 상기 컨트롤러(156) 및 상기 PWM(148) 사이의 인터페이스로서 포함된다. 만약 위에서 설명된 양자화 효과(quantization effects)를 해결하기 위해 아무것도 행해지지 않는다면, 상기 양자화 효과가 상기 드라이버 및 변환기의 출력에 영향을 미치지 않도록 하기 위해 중저역 필터링(heavy low pass filtering)이 사용될 수도 있다. 만약 상기 컨트롤러(156)가 더 낮은 정밀도(resolution)를 갖는다면, 상기 필터의 차단 주파수(cutoff frequency)는 상기 기준 주파수  $r(t)$ 가 감쇠되기에 충분하게 낮아질 수도 있다. 이러한 효과를 보상하는 것은 전력 소비에서의 송압을 수반할 수 있다.

[0026]

전치 왜곡이 이용될 때, 기본(fundamental)에 가까운 차단 주파수를 가진 저역 필터(low pass filter)는 제 1 및 제 2 변환기(106, 108)에서  $r(t)$ 에서의 부정확하게 스케일링된 표현(inaccurate scaled representation)을 유발할 수도 있다. 예를 들어, 변환기(106, 108)로부터의 원하는 출력 신호가  $r(t)$ 에 관한 스케일링된 표현일 때, 만약 변환기(106, 108)가 비선형이라면,  $r(t)$ 는 상기 변환기(106, 108)의 비선형 양식을 보상하는 방식으로 PWM(148)로 입력되기 전에 신호  $r'(t)$ 로 전치 왜곡될 수도 있다. 상기 전치 왜곡된 신호  $r'(t)$ 는  $r(t)$ 의 조화파(harmonics)를 수정할 것이다. 만약 저역 필터링이 이러한 조화파를 감소시키거나 서로에 대한 및 기본(fundamental)에 대한 위상을 변화시킨다면, 원하지 않는 왜곡이 추가될 것이고, 변환기(106, 108)의 상기 출력이 더 이상 기준 신호  $r(t)$ 에 관한 정확한 스케일링 표현이 아닐 것이다.

[0027]

필터링 제한(filtering constraints)을 피하고 양자화 관련 영향을 완화하기 위해, 유효 샘플링 정밀도(effective sampling resolution)에서의 증가가 사용된다. 시그마 델타 기술이 양자화 영향을 감소시키고 정밀도를 증가시키기 위해 상기 컨트롤러(156) 내에서 구현된다. 만약 컨트롤러(156)가 충분히 높은 샘플링 레이트(sampling rate)를 갖는다면, 컨트롤러에 관한 계산율(computation rate) 및 상기 높은 샘플링 레이트는 기준 신호  $r(t)$ 의 주파수 요소와 비교하여 트레이드 오프(trade off)될 수 있어 상기 신호를 오버샘플링(oversampling)한다. 이는 또한 루프 테이블에 따라서 구현될 수 있는데, 여기서 상기 기준 신호  $r(t)$ 는 오버샘플링되고 엔트리(entries)는 상기 컨트롤러(156) 내의 루프 테이블로서 프로그래밍된다.

[0028]

이러한 오버샘플링(oversampling)의 이점은 상기 샘플링된 파형 내의 어떤 초래된 부정확성(inaccuracies) 또는 왜곡이 상기 신호가 오버샘플링되거나 초과 표현된 주파수에 종속된다는 것이다. 양자화로부터 발생한 아티팩트는 이제 더 높은 주파수로 이동(shift)된다. 이는 종래의 DAC로 가능한 것보다 더 높은 차단 주파수를 가지고 컨트롤러(156)에서 나옴에 따라 상기 필터링이 상기 아날로그 파형 상에서 구현되도록 하는데, 이것은 상기 시그마 델타 기술(160)이 상기 아티팩트 주파수를 상기 기본적인 기준 요소보다 훨씬 더 높은 값으로 이동시키기 때문이다. 이것은 최소한 두 가지 이점을 갖는다. 첫째, 상기 필터의 크기 및 비용이 감소한다. 둘째, 상기 더 높은 필터 차단 주파수는 전치 왜곡에 의해 수정되거나 생성된 조화파 요소(harmonic components)에 대한 필터 영향이 최소화될 수 있는 수단을 가능하게 하고, 이는 전치 왜곡의 사용을 실용적으로 만든다.

[0029]

상기 PWM(148)로의 분명한 명령(a clean command)을 생성하는 이러한 방법은, 상기 출력 파형  $v_0(t)$ 의 퍼델리티(fidelity)를 유지하는데 중요하다. 실제로, 일부 구현에서, 상기 전체 과정(entire chain)은 상기 필터(166) 및 PWM(148)을 또한 포함하여, 마이크로컨트롤러 블록 또는 디지털 프로세서에서 구현될 수 있다.

[0030]

본 발명의 실시예는 압전 드라이버가 고효율, 저비용, 소형, 및 좋은 파형 퍼델리티를 가지도록 한다. 또한, 일부 실시예에서 도 2에 관한 설명과 같은 플라이백 변환기(fly-back converters)를 사용하는 것은 갈바닉 절연(galvanic isolation), 넓은 전압 범위(a wide voltage range), 및 모든 전력 스위치에 대한 공통 접지(a common reference ground)를 허락한다. 또한, 피드백, 전치 왜곡, 또는 피드-포워드(feed-forward)와 같은 기타 에러 수정 기술을 이용하는 비선형 직류/직류 변환기에 대한 보상은 상기 압전 액추에이터에 걸친 전압이 송압 변환 프로세스를 제어하도록 사용되는 제어 신호의 선형 근사값이 되도록 한다.

[0031]

그러므로, 본 발명의 일 실시예를 따르면, 드라이버 시스템(driver system)은 직류 전압원 및 제 1 양방향 직류/직류 변환기를 포함하되, 상기 제 1 양방향 직류/직류 변환기는 상기 직류 전압원에 결합된 일단 및 타단을 구비하고, 상기 제 1 양방향 직류/직류 변환기 일단의 제 1 전압의 변환을 상기 제 1 양방향 직류/직류 변환기 타

단의 제 2 전압으로 제어하도록 구성된 제 1 제어 신호를 수신하는 제어 입력부를 포함한다. 상기 드라이버 시스템은 또한 제 2 양방향 직류/직류 변환기를 포함하는데, 상기 제 2 양방향 직류/직류 변환기는 상기 직류 전압원에 결합되는 일단 및 상기 제 1 양방향 직류/직류 변환기의 상기 타단에 결합되는 타단을 구비하고, 상기 제 2 양방향 직류/직류 변환기의 상기 일단의 상기 제 1 전압의 변환을 상기 제 2 양방향 직류/직류 변환기의 상기 타단의 제 3 전압으로 제어하도록 구성된 제 2 제어 신호를 수신하도록 구성된 제어 입력부를 포함한다. 상기 제 1 및 제 2 양방향 직류/직류 변환기는 상기 제 1 전압을 승압할 수 있고, 상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수(complement)이다. 상기 제 2 및 제 3 전압 사이의 전압 차이(voltage difference)는 출력 전압을 포함하고, 상기 출력 전압은 상기 제 1 제어 신호의 증폭을 포함한다.

[0032] 본 발명의 다른 실시예를 따르면, 압전 드라이버를 제조하는 방법은 직류 전압원을 제 1 전압 변환기의 저전압 측 및 제 2 전압 변환기의 저전압 측에 결합하는 단계를 포함하되, 상기 제 1 및 제 2 전압 변환기는 상기 직류 전압원으로부터 전압을 승압시킬 수 있는 양방향 직류/직류 전압 변환기를 포함한다. 상기 방법은 또한 상기 제 1 전압 변환기의 고전압 측 상의 제 1 고전압 측 단자를 압전 액추에이터의 제 1 측에 결합하는 단계, 상기 제 2 전압 변환기의 고전압 측 상의 제 1 고전압 측 단자를 상기 압전 액추에이터의 제 2 측에 결합하는 단계, 상기 제 1 전압 변환기의 제 2 고전압 측 단자를 상기 제 2 전압 변환기의 제 2 고전압 측 단자에 결합하는 단계를 포함한다. 상기 방법은 또한 제어 시스템을 상기 제 1 및 제 2 전압 변환기에 결합하는 단계, 상기 제어 시스템이 제 1 제어 신호를 상기 제 1 전압 변환기로 공급하고 제 2 제어 신호를 상기 제 2 전압 변환기로 공급하도록 구성하는 단계를 포함한다. 상기 제 1 제어 신호는 상기 제 1 전압 변환기를 제어하도록 구성되어 상기 제 1 전압 변환기의 상기 저전압 측 상의 상기 직류 전압원으로부터 상기 제 1 전압 변환기의 상기 고전압 측 상의 제 1 출력 전압으로 상기 전압을 변환하고, 상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수(complement)이며 상기 제 2 전압 변환기를 제어하도록 구성되어 상기 제 2 전압 변환기의 상기 저전압 측 상의 상기 직류 전압원으로부터 상기 제 2 전압 변환기의 상기 고전압 측 상의 제 2 출력 전압으로 상기 전압을 변환한다. 상기 제 1 및 제 2 출력 전압 사이의 전압 차이(voltage difference)는 상기 제 1 제어 신호의 증폭을 포함하는 전압 차를 포함한다.

[0033] 본 발명의 또 다른 실시예에 따르면, 압전 드라이버는 저전압 측 및 고전압 측을 구비하는 제 1 양방향 직류/직류 전압 변환기를 포함하고 저전압 측 및 고전압 측을 구비하는 제 2 양방향 직류/직류 전압 변환기를 포함한다. 상기 제 1 양방향 직류/직류 전압 변환기는 제 1 고전압 측 단자, 제 2 고전압 측 단자를 포함하되, 상기 제 1 양방향 직류/직류 변환기는 상기 제 1 고전압 측 단자의 전압으로 전압을 승압시킬 수 있다. 상기 제 2 양방향 직류/직류 전압 변환기는 제 1 고전압 측 단자, 상기 제 1 전압 변환기의 상기 제 2 고전압 측 단자에 결합된 제 2 고전압 측 단자를 포함하되, 상기 제 2 양방향 직류/직류 변환기는 상기 제 1 고전압 측 단자의 전압으로 전압을 승압시킬 수 있다. 상기 압전 드라이버는 또한 상기 제 1 및 제 2 양방향 직류/직류 변환기의 상기 저전압 측에 결합된 직류(DC) 전압원, 상기 제 1 양방향 직류/직류 전압 변환기의 제 1 고전압 측 단자에 결합되고 상기 제 2 양방향 직류/직류 전압 변환기의 상기 제 1 고전압 측 단자에 연결되는 압전 액추에이터, 및 상기 제 1 및 제 2 전압 변환기에 결합되는 제어 시스템을 포함한다. 상기 제어 시스템은 상기 제 1 양방향 직류/직류 전압 변환기에 제 1 제어 신호를 공급하되, 상기 제 1 제어 신호는 상기 제 1 양방향 직류/직류 전압 변환기를 제어하여 상기 제 1 양방향 직류/직류 전압 변환기의 상기 저전압 측 상의 전압을 상기 제 1 양방향 직류/직류 전압 변환기의 상기 고전압 측 상의 제 1 출력 전압으로 변환하도록 구성된다. 상기 제어 시스템은 또한 상기 제 2 양방향 직류/직류 전압 변환기로 제 2 제어 신호를 공급하되, 상기 제 2 제어 신호는 상기 제 1 제어 신호의 보수이고 상기 제 2 양방향 직류/직류 전압 변환기를 제어하여 상기 제 2 양방향 직류/직류 변환기의 상기 저전압 측 상의 전압을 상기 제 2 양방향 직류/직류 전압 변환기의 상기 고전압 측 상의 제 2 출력 전압으로 변환하도록 구성된다. 상기 제 1 및 제 2 출력 전압 사이의 전압 차이는 상기 제 1 제어 신호의 증폭을 포함하는 전압 차이를 포함한다.

[0034] 기술된 설명은 가장 좋은 모드를 포함하여 본 발명을 공개하는 예시를 사용하고, 또한 어떤 디바이스나 시스템을 사용하고 만드는 것 및 어떤 결합된 방법을 수행하는 것을 포함하여 당업자가 본 발명을 실시할 수 있도록 한다. 본 발명의 특허 범주는 특허 청구항에 의해 정의되며, 당업자에게 발생하는 다른 예시들을 포함한다. 만약 당업자가 특허 청구항 문자 그대로의 언어와 다르지 않은 구조적 요소를 갖거나, 특허 청구항 문자 그대로의 언어로부터 실체가 없는 차이를 가진 동일한 구조 요소를 포함한다면, 그러한 다른 예시들을 특허 청구 범위 내에서 포함하고자 한다.

## 부호의 설명

- [0035] 100: 압전 드라이버

102: 압전 부하

104: 전압원

106: 제 1 변환기

108: 제 2 변환기

110, 112, 114, 116: 저전압 측 변환기 단자

118, 120, 122, 124: 고전압 측 변환기 단자

126, 128: 제어 입력부

130: 교류 전압원

132: 제 1 단자

134: 제 2 단자

148: 펄스 폭 변조기(PWM)

140, 142, 144, 146: 스위치

150: 보상기

152: 전압 센서

154: 전치 왜곡

156: 컨트롤러

158: 함수 생성 블록

160: 시그마-델타 변조기

162: 디지털-아날로그 변환기(DAC: Digital to Analog Converter)

164: 출력

166: 필터

도면

도면1

દોર્ય 2

દોર્ય 3

## 도면4

도면5