(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년05월06일

(11) 등록번호 10-0826838

(24) 등록일자 2008년04월25일

(51) Int. Cl.

H01L 21/335 (2006.01) H01L 21/336 (2006.01)

(21) 출원번호 10-2006-7003534

(22) 출원일자 2006년02월21일

심사청구일자 2006년10월09일

번역문제출일자 2006년02월21일

(65) 공개번호 10-2006-0118407

(43) 공개일자 2006년11월23일

(86) 국제출원번호 PCT/US2004/028045

국제출원일자 2004년08월27일

(87) 국제공개번호 WO 2005/036613

국제공개일자 2005년04월21일

(30) 우선권주장

10/652,400 2003년08월29일 미국(US)

(56) 선행기술조사문헌

us 6593625

전체 청구항 수 : 총 32 항

심사관 : 최정윤

(54) 초박형 SOI/SGOI 기판 상의 초고속 SI/SIGE변조 도프트 전계효과 트랜지스터들

### (57) 요약

실리콘 및 실리콘 게르마늄 기반의 반도체 MODFET 소자 디자인 및 제조방법. 상기 MODFET 소자 디자인은 RF, 마이크로파, 서브밀리미터파 및 밀리미터파를 채택하는 다양한 통신 애플리케이션의 초고속, 저잡음 구현 가능하고 이동도 막 구조를 구비한다. 에피택시얼 전계효과 트랜지스터 막 구조는 매우 향상된 RF 성능을 얻을 수 있는 초박형 SOI 또는 SGOI 기판 상의 최적의 변조 도프트 헤테로 구조를 형성하기 위하여 실리콘 및 실리콘 게르마늄 막들을 혼합하고 있는 고이동도 스트레인드 n채널 및 p채널 트랜지스터의 중대한(세로 및 가로) 소자 스케일링 및 막 구조 디자인을 채택한다.

대표도 - 도1a

## 특허청구의 범위

### 청구항 1

30-40% 범위의 Ge 함유량을 갖고, 20nm-30nm 범위의 두께이며,  $1e14 \text{ cm}^{-3}$  -  $5e17 \text{ cm}^{-3}$  범위의 p타입 도핑 농도를 갖는 절연체 상의 SiGe막을 포함하는 SGOI 기판;

상기 SiGe막 상에 0nm-5nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{0.95}\text{Ge}_{0.05}$  씨드막;

상기 씨드막 상에 20nm-30nm 범위의 두께로 성장되고, 10%-40% 범위의 Ge 함유량을 갖는 재성장  $\text{Si}_{1-x}\text{Ge}_x$  완충막;

상기 완충막 상에 5nm-7nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드(tensile strained) Si막;

상기 스트레인드 Si막 상에 3nm-5nm 범위의 두께로 성장되고, 30-40% 범위의 Ge 함유량  $y$ 를 갖는 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막;

상기 스페이서막 상에 2nm-8nm 범위의 두께로 성장되고,  $2e18 \text{ cm}^{-3}$  -  $2e19 \text{ cm}^{-3}$  범위의 n타입 도핑 농도를 가지며, 35-50% 범위의 Ge 함유량을 갖는 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막; 및

상기 공급막 상에 0nm-3nm 범위의 두께로 성장되고,  $5e17 \text{ cm}^{-3}$  -  $5e19 \text{ cm}^{-3}$ 의 n타입 도핑 농도를 갖는 에피택시얼 인장 스트레인드 Si 캐핑막을 포함하는 고전자이동도(high-electron mobility)막 반도체 구조체.

### 청구항 2

제 1 항에 있어서, 상기  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막은 Ge 함유량  $y = x+a$  를 갖되, "a"는 0-20% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 3

제 1 항에 있어서, 상기  $\text{Si}_{1-z}\text{Ge}_z$  공급막은 Ge 함유량  $z = x+b$  를 갖되, "b"는 0-30% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 4

제 1 항에 있어서, 상기  $\text{Si}_{1-z}\text{Ge}_z$  공급막은  $\text{Si}_{1-m-n}\text{Ge}_m\text{C}_n$ 막을 포함하되,  $m=x+c$ 이고, "c"는 0-20% 범위이고, "n"은 0.1-2% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 5

제 1 항에 있어서,

상기 스트레인드 Si 캐핑막 상에 형성되고, 0-1nm 범위의 등가 산화물 두께(equivalent oxide thickness)를 갖는 게이트 유전막;

상기 게이트 유전막 상에 형성된 게이트 도전체;

$5e19 \text{ cm}^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 드레인 영역; 및

$5e19 \text{ cm}^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 소오스 영역을 더 포함하되, 상기 구조체는 고전자 이동도 전계효과 트랜지스터를 이루는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 6

청구항 6은(는) 설정등록료 납부시 포기되었습니다.

제 5 항에 있어서, 상기  $\text{Si}_{1-z}\text{Ge}_z$  공급막은 약 5nm-8nm 범위의 두께이고, 약  $3e12 \text{ cm}^{-2}$ 의 면 도핑 밀도(sheet

doping density)를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 7

청구항 7은(는) 설정등록료 납부시 포기되었습니다.

제 5 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 4nm의 두께이고, 약  $2.4e12\text{cm}^{-2}$ 의 면 도핑 밀도를 갖는 것을 특징으로 하는 고전자 이동도막 반도체 구조체.

### 청구항 8

청구항 8은(는) 설정등록료 납부시 포기되었습니다.

제 6 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 1-1.5% 범위의 C 함유량을 갖는 SiGeC막을 포함하는 것을 특징으로 하는 고전자 이동도막 반도체 구조체.

### 청구항 9

청구항 9은(는) 설정등록료 납부시 포기되었습니다.

제 5 항에 있어서, 상기 게이트 유전막은 실리콘의 산화물, 질화물, 산질화물, 및 Hf, Al, Zr, La, Y, Ta 단일 또는 조합물의 산화물 및 실리케이트를 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고전자 이동도막 반도체 구조체.

### 청구항 10

청구항 10은(는) 설정등록료 납부시 포기되었습니다.

### 청구항 11

청구항 11은(는) 설정등록료 납부시 포기되었습니다.

제 5 항에 있어서, 상기 게이트 도전체는 T-게이트 구조, 사각형(rectangular) 구조 또는 멀티-핑거(multi-finger) 구조 중 하나인 것을 특징으로 하는 고전자 이동도막 반도체 구조체.

### 청구항 12

청구항 12은(는) 설정등록료 납부시 포기되었습니다.

제 5 항에 있어서, 게이트 길이는 30nm-100nm 범위인 것을 특징으로 하는 고전자 이동도막 반도체 구조체.

### 청구항 13

청구항 13은(는) 설정등록료 납부시 포기되었습니다.

제 5 항에 있어서, 상기 게이트 도전체와 상기 드레인 또는 소오스 영역 중 어느 하나와의 거리는 약 20nm-100nm 범위인 것을 특징으로 하는 고전자 이동도막 반도체 구조체.

### 청구항 14

제 5 항에 있어서, 게이트 전극을 둘러싸는 패시베이션막을 더 포함하되, 상기 패시베이션막은 1-4 범위의 유전율을 갖는 것을 특징으로 하는 고전자 이동도막 반도체 구조체.

### 청구항 15

30-40% 범위의 Ge 함유량을 갖고, 20nm-30nm 범위의 두께이며,  $1e14\text{ cm}^{-3}$  -  $5e17\text{cm}^{-3}$  범위의 p타입 도핑 농도를 갖는 절연체 상의 SiGe막을 포함하는 SGOI 기판;

상기 SiGe막 상에 20nm-30nm 범위의 두께로 성장되고, 30-40%의 Ge 함유량 x를 갖는 재성장  $Si_{1-x}Ge_x$  완충막;

상기 완충막 상에 5nm-7nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si막;

상기 스트레인드 Si막 상에 3nm~5nm 범위로 성장되고, 30~40% 범위의 Ge 함유량을 갖는 에피택시얼  $Si_{1-y}Ge_y$  스페이서막;

상기 스페이서막 상에 2nm~8nm 범위의 두께로 성장되고,  $2e18cm^{-3}$ ~ $2e19cm^{-3}$  범위의 n타입 도핑 농도를 가지며, 35~50% 범위의 Ge 함유량을 갖는 에피택시얼  $Si_{1-z}Ge_z$  공급막;

상기 공급막 상에 0nm~3nm 범위의 두께로 성장되고,  $5e17 cm^{-3}$ ~ $5e19cm^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼 인장 스트레인드 Si 캐핑막;

상기 스트레인드 Si 캐핑막 상에 0~1nm 범위의 등가 산화물 두께(equivalent oxide thickness)로 형성된 게이트 유전막;

상기 게이트 유전막 상에 형성된 게이트 도전체;

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 드레인 영역; 및

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 소오스 영역을 포함하는 고전자 이동도 전계효과 트랜지스터(hight-electronmobility field effect transistor).

#### 청구항 16

10nm~50nm 범위의 두께인 절연체 상의  $Si_{1-x}Ge_x$ 막을 포함하는 SGOI 기판,

상기 SiGe막 상에 0nm~5nm 범위의 두께로 성장된 에피택시얼  $Si_{0.95}Ge_{0.05}$  씨드막;

상기 씨드막 상에 2nm~8nm 범위의 두께로 성장되고,  $1e18cm^{-3}$ ~ $5e19cm^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼  $Si_{1-z}Ge_z$  공급막; 및

상기 공급막 상에 3nm~5nm 범위의 두께로 성장된 에피택시얼  $Si_{1-y}Ge_y$  스페이서막;

상기 스페이서막 상에 3nm~10nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si막;

상기 스트레인드 Si막 상에 1nm~2nm 범위의 두께로 성장된 에피택시얼  $Si_{1-y}Ge_y$  스페이서막; 및

상기 스페이서막 상에 0nm~2nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 캐핑막을 포함하는 고전자 이동도막 반도체 구조체.

#### 청구항 17

청구항 17은(는) 설정등록료 납부시 포기되었습니다.

제 16 항에 있어서, 상기 SGOI 기판은 30~50% 범위의 Ge 함유량 x를 갖는  $Si_{1-x}Ge_x$ 막을 구비하는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 18

청구항 18은(는) 설정등록료 납부시 포기되었습니다.

제 16 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 Ge 함유량  $z = x+a$ 을 갖되, "a"는 약 0~30% 범위이고, x는 30~50% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 19

청구항 19은(는) 설정등록료 납부시 포기되었습니다.

제 16 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은  $Si_{1-m-n}Ge_mC_n$ 막을 포함하되,  $m=x+b$ 이고, "b"는 0~30%의 범위이며, "n"은 0.1~2%의 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 20**

청구항 20은(는) 설정등록료 납부시 포기되었습니다.

제 16 항에 있어서, 상기  $Si_{1-y}Ge_y$  스페이서막은 Ge 함유량  $y = x+c$ 를 갖되, "c"의 범위는 0-20%인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 21**

제 16 항에 있어서,

상기 스트레인드 Si 캐핑막 상에 0-1nm 범위의 등가 산화물 두께를 갖도록 형성된 게이트 유전막;

상기 게이트 유전막 상에 형성된 게이트 도전체;

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 드레인 영역; 및

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 소오스 영역을 더 포함하되, 상기 구조는 고전자이동도 전계효과 트랜지스터를 이루는 고전자이동도막 반도체 구조체.

**청구항 22**

청구항 22은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 5nm-8nm 범위의 두께이고, 약  $3e12cm^{-2}$ 의 면 도핑 밀도(sheet doping density)를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 23**

청구항 23은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 4 nm의 두께이고, 약  $2.4e12cm^{-2}$ 의 면 도핑 밀도를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 24**

청구항 24은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 1-1.5%의 C 함유량을 갖는 SiGeC막을 포함하는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 25**

청구항 25은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 상기 게이트 유전막은 실리콘의 산화물, 질화물, 산질화물 및 Hf, Al, Zr, La, Y, Ta 단일 또는 조합물의 산화물 및 실리케이트를 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 26**

청구항 26은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 상기 게이트 도전체는 Pt, Ir, W, Pd, Al, Au, Cu, Ti, Co 단일 또는 조합물을 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 27**

청구항 27은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 상기 게이트 도전체는 T-게이트 구조, 사각형 구조 또는 멀티-핑거(multi-finger) 구조 중

하나인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 28

청구항 28은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 게이트 길이는 30nm-100nm 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 29

청구항 29은(는) 설정등록료 납부시 포기되었습니다.

제 21 항에 있어서, 상기 게이트 도전체와 상기 드레인 또는 소오스 영역중 어느 하나 사이의 거리는 약 20nm-100nm 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 30

제 21 항에 있어서, 게이트 전극을 둘러싸는 패시베이션막을 더 포함하되, 상기 패시베이션막은 1-4 범위의 유전율을 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 31

30-40% 범위의 Ge 함유량을 갖고, 20nm-30nm 범위의 두께인 절연체 상의 SiGe막을 포함하는 SGOI 기판;

상기 SiGe막 상에 2.5nm-8nm 범위의 두께로 성장되고,  $2e18 \text{ cm}^{-3}$  -  $2e19 \text{ cm}^{-3}$  범위의 n타입 도핑 농도를 가지며, 35-50% 범위의 Ge 함유량을 갖는 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막;

상기 공급막 상에 3nm-5nm 범위로 성장되고, 30-40% 범위의 Ge 함유량을 갖는 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막;

상기 스페이서막 상에 5nm-7nm 범위의 두께로 성장되고  $1e16 \text{ cm}^{-3}$  보다 작은 도핑 농도를 갖는 에피택시얼 인장 스트레인드 Si 채널층;

상기 Si 채널층 상에 1nm-2nm 범위의 두께로 성장되고, 30-40% 범위의 Ge 함유량을 갖는 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막;

상기 스페이서막 상에 0nm-2nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 캐핑막;

상기 스트레인드 Si 캐핑막 상에 0-1nm 범위의 등가 산화물 두께로 형성된 게이트 유전막;

상기 게이트 유전막 상에 형성된 게이트 도전체;

$5e19 \text{ cm}^{-3}$  보다 큰 n타입 도핑 농도를 갖는 드레인 영역; 및

$5e19 \text{ cm}^{-3}$  보다 큰 n타입 도핑 농도를 갖는 소오스 영역을 포함하는 고전자이동도 전계효과 트랜지스터.

### 청구항 32

2nm-8nm 범위의 두께이고  $1e18 \text{ cm}^{-3}$  -  $5e19 \text{ cm}^{-3}$  범위의 n타입 도핑 농도를 갖는  $\text{Si}_{1-z}\text{Ge}_z$  공급막을 포함하는 SGOI 기판;

상기 공급막 상에 3nm-5nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막;

상기 스페이서막 상에 3nm-10nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 막;

상기 스트레인드 Si 막 상에 1nm-2nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막; 및

상기 스페이서막 상에 0nm-2nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 캐핑막을 포함하는 고전자이동도막 반도체 구조체.

### 청구항 33

청구항 33은(는) 설정등록료 납부시 포기되었습니다.

제 32 항에 있어서, 상기 SGOI 기판은 30-50% 범위의 Ge 함유량 "x"를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 34

청구항 34은(는) 설정등록료 납부시 포기되었습니다.

#### 청구항 35

청구항 35은(는) 설정등록료 납부시 포기되었습니다.

제 32 항에 있어서, 상기 도핑된 전이  $Si_{1-x}Ge_x$  공급막은  $Si_{1-m-n}Ge_mC_n$ 막을 포함하되,  $m=x+b$ 이고, "b"는 0-30% 범위이며, "n"은 0.1-2% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 36

청구항 36은(는) 설정등록료 납부시 포기되었습니다.

제 32 항에 있어서, 상기  $Si_{1-y}Ge_y$  스페이서막은 Ge 함유량  $y=x+c$ 를 갖되, "c"는 0-20% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 37

제 32 항에 있어서,

상기 스트레인드 Si 캐핑막 상에 1nm보다 작은 두께로 형성된 게이트 유전막;

상기 게이트 유전막 상에 형성된 게이트 도전체;

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 드레인 영역; 및

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 소오스 영역을 더 포함하는 고전자이동도막 반도체 구조체.

#### 청구항 38

청구항 38은(는) 설정등록료 납부시 포기되었습니다.

제 37 항에 있어서, 상기 도핑된 전이  $Si_{1-z}Ge_z$  공급막은 약 5nm-8nm 범위의 두께이고, 약  $3e12cm^{-2}$ 의 면 도핑 밀도를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 39

청구항 39은(는) 설정등록료 납부시 포기되었습니다.

제 37 항에 있어서, 상기 도핑된 전이  $Si_{1-z}Ge_z$  공급막은 약 4 nm의 두께이고, 약  $2.4e12cm^{-2}$ 의 면 도핑 밀도를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 40

청구항 40은(는) 설정등록료 납부시 포기되었습니다.

제 32 항에 있어서, 상기 도핑된 전이  $Si_{1-z}Ge_z$  공급막은 약 1-1.5%의 C 함유량을 갖는 SiGeC막을 포함하는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 41

청구항 41은(는) 설정등록료 납부시 포기되었습니다.

제 37 항에 있어서, 상기 게이트 유전막은 실리콘의 산화물, 질화물, 산질화물 및 Hf, Al, Zr, La, Y, Ta 단일

또는 조합물의 산화물 및 실리케이트를 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 42

청구항 42은(는) 설정등록료 납부시 포기되었습니다.

제 37 항에 있어서, 상기 게이트 도전체는 Pt, Ir, W, Pd, Al, Au, Cu, Ti, Co 단일 또는 조합물을 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 43

청구항 43은(는) 설정등록료 납부시 포기되었습니다.

제 37 항에 있어서, 상기 게이트 도전체는 T-게이트 구조, 사각형 구조 또는 멀티-핑거(multi-finger) 구조중 하나인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 44

청구항 44은(는) 설정등록료 납부시 포기되었습니다.

제 37 항에 있어서, 게이트 길이는 30nm-100nm 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 45

청구항 45은(는) 설정등록료 납부시 포기되었습니다.

제 37 항에 있어서, 상기 게이트 도전체와 상기 드레인 또는 소오스 영역중 어느 하나 사이의 거리는 약 20nm-100nm 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 46

제 37 항에 있어서, 게이트 전극을 둘러싸는 패시베이션막을 더 포함하되, 상기 패시베이션막은 1-4 범위의 유전율을 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 47

10nm-50nm 범위의 두께이고,  $1e17 \text{ cm}^{-3}$  -  $5e19 \text{ cm}^{-3}$  범위의 n타입 도핑 농도를 갖는 절연체 상의 SiGe막을 포함하는 SGOI 기판;

상기 SiGe막 상에 10nm-50nm 범위의 두께로 성장되며, 하부 스페이서막(bottom spacer layer)로써 제공되는  $\text{Si}_{1-x}\text{Ge}_x$  재성장 완충막;

상기 재성장 완충막 상에 3nm-10nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si막;

상기 스트레인드 Si막 상에 3nm-5nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막;

상기 스페이서막 상에 2nm-8nm 범위의 두께로 성장되고,  $1e18 \text{ cm}^{-3}$  -  $5e19 \text{ cm}^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막; 및

상기 공급막 상에 0nm-3nm 범위의 두께로 성장되고,  $5e17 \text{ cm}^{-3}$  -  $5e19 \text{ cm}^{-3}$ 의 n타입 도핑 농도를 갖는 에피택시얼 인장 스트레인드 Si 캐핑막을 포함하는 고전자이동도(high-electronmobility)막 반도체 구조체.

#### 청구항 48

청구항 48은(는) 설정등록료 납부시 포기되었습니다.

제 47 항에 있어서, 상기 SGOI 기판은 30-50% 범위의 Ge 함유량을 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

#### 청구항 49

청구항 49은(는) 설정등록료 납부시 포기되었습니다.

제 47 항에 있어서, 상기  $Si_{1-x}Ge_x$  재성장 완충막은 10-35% 범위의 Ge 함유량을 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 50

청구항 50은(는) 설정등록료 납부시 포기되었습니다.

제 47 항에 있어서, 상기  $Si_{1-y}Ge_y$  스페이서막은 Ge 함유량  $y = x+a$  를 갖되, "a"는 0-20% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 51

청구항 51은(는) 설정등록료 납부시 포기되었습니다.

제 47 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 Ge 함유량  $z = x+b$  를 갖되, "b"는 0-30% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 52

청구항 52은(는) 설정등록료 납부시 포기되었습니다.

제 47 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은  $Si_{1-m-n}Ge_mC_n$ 막을 포함하되,  $m=x+c$ 이고, "c"는 0-20% 범위이고, "n"은 0.1-2% 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 53

제 47 항에 있어서,

상기 스트레인드 Si 캐핑막 상에 형성되되, 0-1nm 범위의 등가 산화물 두께(equivalent oxide thickness)를 갖는 게이트 유전막;

상기 게이트 유전막 상에 형성된 게이트 도전체;

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 드레인 영역; 및

$5e19cm^{-3}$ 보다 큰 n타입 도핑 농도를 갖는 소오스 영역을 더 포함하는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 54

청구항 54은(는) 설정등록료 납부시 포기되었습니다.

제 53 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 5nm-8nm 범위의 두께이고, 약  $3e12cm^{-2}$ 의 면 도핑 밀도(sheet doping density)를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 55

청구항 55은(는) 설정등록료 납부시 포기되었습니다.

제 53 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 4nm의 두께이고, 약  $2.4e12cm^{-2}$ 의 면 도핑 밀도를 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

### 청구항 56

청구항 56은(는) 설정등록료 납부시 포기되었습니다.

제 54 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막은 약 1-1.5% 사이의 C 함유량을 갖는 SiGeC막을 포함하는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 57**

청구항 57은(는) 설정등록료 납부시 포기되었습니다.

제 53 항에 있어서, 상기 게이트 유전막은 실리콘의 산화물, 질화물, 산질화물, Hf, Al, Zr, La, Y, Ta 단일 또는 조합물의 산화물 및 실리케이트를 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 58**

청구항 58은(는) 설정등록료 납부시 포기되었습니다.

제 53 항에 있어서, 상기 게이트 도전체는 Pt, Ir, W, Pd, Al, Au, Cu, Ti, Co 단일 또는 조합물을 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 59**

청구항 59은(는) 설정등록료 납부시 포기되었습니다.

제 53 항에 있어서, 상기 게이트 도전체는 T-게이트 구조, 사각형(rectangular) 구조 또는 멀티-핑거(multi-finger) 구조중 하나인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 60**

청구항 60은(는) 설정등록료 납부시 포기되었습니다.

제 53 항에 있어서, 게이트 길이는 30nm-100nm 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 61**

청구항 61은(는) 설정등록료 납부시 포기되었습니다.

제 53 항에 있어서, 상기 게이트 도전체와 상기 드레인 또는 소오스 영역 중 어느 하나와의 거리는 약 20nm-100nm 범위인 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 62**

제 53 항에 있어서, 게이트 전극을 둘러싸는 패시베이션막을 더 포함하되, 상기 패시베이션막은 1-4 범위의 유전율을 갖는 것을 특징으로 하는 고전자이동도막 반도체 구조체.

**청구항 63**

5nm-25nm 범위의 두께이고,  $1e18 - 5e19\text{cm}^{-3}$  범위의 p타입 도핑 농도를 갖는  $\text{Si}_{1-j}\text{Ge}_j$  공급막을 포함하는 SGOI 기판;

상기 공급막 상에 3nm-7nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-k}\text{Ge}_k$  스페이서막;

상기 스페이서막 상에 5nm-20nm 범위의 두께로 성장된 에피택시얼 압축 스트레인드  $\text{Si}_{1-m}\text{Ge}_m$  채널층; 및

상기 스트레인드  $\text{Si}_{1-m}\text{Ge}_m$  채널층 상에 2nm-10nm 범위의 두께로 성장된 에피택시얼 스트레인드  $\text{Si}_{1-n}\text{Ge}_n$  캐핑막을 포함하는 고정공이동도(high-hole-mobility)막 반도체 구조체.

**청구항 64**

청구항 64은(는) 설정등록료 납부시 포기되었습니다.

제 63 항에 있어서, 상기  $\text{Si}_{1-j}\text{Ge}_j$  공급막은 30-70% 범위의 Ge 함유량  $j$ 를 구비하는 것을 특징으로 하는 고정공이동도막 반도체 구조체.

**청구항 65**

청구항 65은(는) 설정등록료 납부시 포기되었습니다.

제 63 항에 있어서, 상기  $Si_{1-k}Ge_k$  스페이서막은 30-70% 범위의 Ge 함유량 k를 구비하는 것을 특징으로 하는 고정공이동도막 반도체 구조체.

### 청구항 66

청구항 66은(는) 설정등록료 납부시 포기되었습니다.

제 63 항에 있어서, 상기  $Si_{1-m}Ge_m$  채널층은 60-100% 범위의 Ge 함유량 m을 구비하는 것을 특징으로 하는 고정공이동도막 반도체 구조체.

### 청구항 67

청구항 67은(는) 설정등록료 납부시 포기되었습니다.

제 63 항에 있어서, 상기 스트레인드  $Si_{1-n}Ge_n$  캐핑막은 0%-30% 범위의 Ge 함유량 n을 구비하는 것을 특징으로 하는 고정공이동도막 반도체 구조체.

### 청구항 68

제 63 항에 있어서,

상기 게이트 유전막 상에 형성된 게이트 도전체;

$5e19cm^{-3}$  보다 큰 p타입 도핑 농도를 갖는 드레인 영역; 및

$5e19cm^{-3}$  보다 큰 p타입 도핑 농도를 갖는 소오스 영역을 더 포함하는 고정공이동도막 반도체 구조체.

### 청구항 69

청구항 69은(는) 설정등록료 납부시 포기되었습니다.

제 68 항에 있어서, 상기 게이트 유전막은 실리콘의 산화물, 질화물, 산질화물 및 Hf, Al, Zr, La, Y, Ta 단일 또는 조합물의 산화물 및 실리케이트를 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고정공이동도막 반도체 구조체.

### 청구항 70

청구항 70은(는) 설정등록료 납부시 포기되었습니다.

제 68 항에 있어서, 상기 게이트 도전체는 Pt, Ir, W, Pd, Al, Au, Cu, Ti, Co 단일 또는 조합물을 포함하는 그룹으로부터 선택되는 것을 특징으로 하는 고정공이동도막 반도체 구조체.

### 청구항 71

청구항 71은(는) 설정등록료 납부시 포기되었습니다.

제 68 항에 있어서, 상기 게이트 도전체는 T-게이트 구조, 사각형 구조 또는 멀티-핑거(multi-finger) 구조중 하나인 것을 특징으로 하는 고정공이동도막 반도체 구조체.

### 청구항 72

청구항 72은(는) 설정등록료 납부시 포기되었습니다.

### 청구항 73

청구항 73은(는) 설정등록료 납부시 포기되었습니다.

제 68 항에 있어서, 상기 게이트 도전체와 상기 드레인 또는 소오스 영역중 어느 하나 사이의 거리는 약 20nm-100nm 범위인 것을 특징으로 하는 고정공이동도막 반도체 구조체.

**청구항 74**

제 68 항에 있어서, 게이트 전극을 둘러싸는 패시베이션막을 더 포함하되, 상기 패시베이션막은 1-4 범위의 유전율을 갖는 것을 특징으로 하는 고정공이동도막 반도체 구조체.

**청구항 75**

- a) 절연체 상의 이완된  $Si_{1-x}Ge_x$ 막을 갖는 SGOI 기판을 제공하고,

- b) 상기  $Si_{1-x}Ge_x$ 막 상에  $Si_{0.95}Ge_{0.05}$  씨드막을 형성하고,

- c) 상기  $Si_{0.95}Ge_{0.05}$  씨드막 상에 재성장  $Si_{1-x}Ge_x$  완충막을 형성하고,

- d) 상기 재성장  $Si_{1-x}Ge_x$ 막 상에 스트레인드 실리콘 채널층을 형성하고,

- e) 상기 스트레인드 실리콘막 상에  $Si_{1-y}Ge_y$  스페이서막을 형성하고,

- f) 상기  $Si_{1-y}Ge_y$  스페이서막 상에  $Si_{1-z}Ge_z$  공급막을 형성하되, 상기  $Si_{1-z}Ge_z$  공급막을  $1e18 - 5e19 \text{ atoms/cm}^3$  범위의 농도 레벨로 n타입 도핑하고,

- g) 상기  $Si_{1-z}Ge_z$  공급막 상에 실리콘 캐핑막을 형성하는 단계들을 포함하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 76**

청구항 76은(는) 설정등록료 납부시 포기되었습니다.

제 75 항에 있어서, b)-g)의 상기 형성 단계들은 UHVCVD 공정을 수행하는 것을 포함하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 77**

청구항 77은(는) 설정등록료 납부시 포기되었습니다.

제 75 항에 있어서, b)-g)의 상기 형성 단계들은 MBE, RTCVD, LPCVD 공정들 중 하나를 수행하는 것을 포함하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 78**

청구항 78은(는) 설정등록료 납부시 포기되었습니다.

제 75 항에 있어서, b)-g)의 상기 막 형성 단계들은 막들을  $450^\circ\text{C}-600^\circ\text{C}$  온도 범위에서 성장시키는 것을 포함하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 79**

청구항 79은(는) 설정등록료 납부시 포기되었습니다.

제 75 항에 있어서, b)-g)의 상기 막 형성 단계들은 막들을  $1\text{mTorr}-20\text{mTorr}$  압력 범위에서 성장시키는 것을 포함하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 80**

청구항 80은(는) 설정등록료 납부시 포기되었습니다.

제 75 항에 있어서, 절연체 상의 이완된  $Si_{1-x}Ge_x$ 막을 갖는 SGOI 기판을 제공하는 상기 단계 a)는 상기 절연체 상의 이완된  $Si_{1-x}Ge_x$ 막을 이온 주입 또는 인-시투 도핑 중 하나를 이용하여  $1e14 \text{ cm}^{-3} - 5e17 \text{ cm}^{-3}$  의 농도 레벨까지 p타입 도핑 시키는 단계를 더 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 81**

제 75 항에 있어서, 절연체 상의 이완된  $Si_{1-x}Ge_x$ 막을 갖는 SGOI 기판을 제공하는 상기 단계 a)는 상기 SGOI 기판을 형성하는 데에 있어서, 상기 막을 전이시키기 전에 상기 이완된  $Si_{1-x}Ge_x$ 막을  $1e14 \text{ cm}^{-3} - 5e17 \text{ cm}^{-3}$  의 농도 레벨까지 사전도핑하는 단계를 더 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 82**

제 75 항에 있어서,  $Si_{1-z}Ge_z$  공급막을 형성하는 상기 단계 f)는 상기  $Si_{1-z}Ge_z$  공급막을 포스핀 가스를 도편트 전 구체로써 단일 또는 H<sub>2</sub>, He, Ne, Ar, Kr, Xe, N<sub>2</sub>를 포함하는 그룹으로부터 선택된 하나 또는 그 이상의 원소들과 혼합하여 사용하여 인-시투 도핑하는 단계를 더 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 83**

청구항 83은(는) 설정등록료 납부시 포기되었습니다.

제 75 항에 있어서, SiH<sub>4</sub> : GeH<sub>4</sub> 가스 유량 비는 일정하도록 유지하면서 3보다 큰 인자로 SiH<sub>4</sub> 및 GeH<sub>4</sub> 가스 유량을 감소시킴으로써, 상기  $Si_{1-z}Ge_z$  공급막을 더 높은 P 정상 상태 농도 및 과도 혼합을 위하여 감소된 성장 속도에서 성장시키는 것을 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 84**

청구항 84은(는) 설정등록료 납부시 포기되었습니다.

제 82 항에 있어서, 상기 포스핀 가스 도편트 전구체의 유량은 선형 기울기 또는 경사진 프로파일이어서 상기 인-시투 도핑이 상기  $Si_{1-z}Ge_z$  공급막을 형성하는 에피택시얼 성장 공정을 봉괴시킴 없이 수행되는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 85**

청구항 85은(는) 설정등록료 납부시 포기되었습니다.

제 82 항에 있어서, 상기 포스핀 도핑된  $Si_{1-z}Ge_z$ 막은 425°C-550°C의 온도 범위에서 성장되는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 86**

청구항 86은(는) 설정등록료 납부시 포기되었습니다.

제 82 항에 있어서, 상기  $Si_{1-z}Ge_z$  공급막을 425°C-550°C의 온도 범위에서 1-2% 정도의 탄소로 도핑하는 것을 더 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 87**

청구항 87은(는) 설정등록료 납부시 포기되었습니다.

제 75 항에 있어서, n타입  $Si_{1-z}Ge_z$  공급막을 형성하는 상기 단계 f)는 AsH<sub>3</sub> 또는 SbH<sub>3</sub> 중 하나를 전구체로 사용하는 단계를 더 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

**청구항 88**

- a) 절연체 상의 이완된  $Si_{1-x}Ge_x$ 막을 갖는 SGOI 기판을 제공하고,

- b) 상기 이완된  $Si_{1-x}Ge_x$ 막 상에 재성장  $Si_{1-x}Ge_x$  완충막을 형성하고,

- c) 상기 재성장  $Si_{1-x}Ge_x$ 막 상에 스트레인드 실리콘 채널층을 형성하고,

- d) 상기 스트레인드 실리콘막 상에  $Si_{1-y}Ge_y$  스페이서막을 형성하고,

- e) 상기  $Si_{1-y}Ge_y$  스페이서막 상에  $Si_{1-z}Ge_z$  공급막을 형성하되, 상기  $Si_{1-z}Ge_z$  공급막을  $1e18 - 5e19 \text{ atoms/cm}^3$  범위의 농도 레벨로 n타입 도핑하고,

- f) 상기  $Si_{1-z}Ge_z$  공급막 상에 실리콘 캐핑막을 형성하는 단계들을 포함하는 고전자이동도막 구조체를 준비하는 방법.

#### 청구항 89

- a) 절연체 상의 이완된  $Si_{1-x}Ge_x$ 막을 갖는 SGOI 기판을 제공하고,

- b) 상기 SiGe막 상에 에피택시얼  $Si_{0.95}Ge_{0.05}$  씨드막을 형성하고,

- c) 상기 씨드막 상에 에피택시얼  $Si_{1-z}Ge_z$  공급막을 형성하고, 상기 공급막을  $1e18 \text{ cm}^{-3} - 5e19 \text{ cm}^{-3}$  범위의 n타입 도펀트 농도로 도핑 시키고,

- d) 상기 공급막 상에  $Si_{1-y}Ge_y$  스페이서막을  $3\text{nm}-5\text{nm}$  범위의 두께로 형성하고,

- e) 상기 스페이서막 상에 에피택시얼 인장 스트레인드 Si막을 형성하고,

- f) 상기 스트레인드 Si막 상에 에피택시얼  $Si_{1-y}Ge_y$  스페이서막을  $1\text{nm}-2\text{nm}$  범위의 두께로 형성하고,

- g) 상기 공급막 상에 에피택시얼 인장 스트레인드 Si 캐핑막을  $0\text{nm}-2\text{nm}$  범위의 두께로 형성하는 것을 포함하는 고전자이동도막 구조체를 준비하는 방법.

#### 청구항 90

- a) 절연체 상의  $Si_{1-x}Ge_x$  공급막을 갖는 SGOI 기판을 제공하고, 상기  $Si_{1-x}Ge_x$  공급막을  $1e18 - 5e19 \text{ atoms/cm}^3$  범위의 농도 레벨까지 n타입 도핑시키고,

- b) 위의 도핑된  $Si_{1-x}Ge_x$ 막을 덮는 에피택시얼  $Si_{1-y}Ge_y$  스페이서막을 형성하고,

- c) 상기 스페이서막 상에 에피택시얼 인장 스트레인드 Si 채널층을 형성하고,

- d) 상기 스트레인드 Si 채널층 상에 에피택시얼  $Si_{1-y}Ge_y$  스페이서막을 형성하고,

- e) 상기 스페이서막 상에 에피택시얼 스트레인드 Si 캐핑막을 형성하는 것을 포함하는 고전자이동도막 구조체를 준비하는 방법.

#### 청구항 91

제 90 항에 있어서, 이온 주입 또는 인-시투 도핑을 이용하여 절연체 상의 상기  $Si_{1-x}Ge_x$ 막을  $1e18 - 5e19 \text{ atoms/cm}^3$  의 농도 레벨까지 n타입 도핑시키는 단계를 더 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

#### 청구항 92

제 90 항에 있어서, 상기 SGOI 기판을 형성하는 데에 있어서 막 전이 전에 상기  $Si_{1-x}Ge_x$  막을  $1e18 - 5e19 \text{ atoms/cm}^3$  의 농도 레벨까지 사전도핑시키는 단계를 더 구비하는 것을 특징으로 하는 고전자이동도막 구조체를 준비하는 방법.

#### 청구항 93

- a) 절연체 상의  $10\text{nm}-50\text{nm}$  범위의 두께인 이완된 SiGe막을 포함하는 SGOI 기판을 제공하고, 상기 이완된 SiGe막을  $1e14 \text{ cm}^{-3} - 5e17 \text{ cm}^{-3}$  범위의 n타입 도핑 농도로 도핑하고,

- b) 상기 SiGe막 상에 10nm-50nm 범위의 두께로 성장된  $\text{Si}_{1-x}\text{Ge}_x$  재성장 완충막을 형성하고,

- c) 상기 재성장 완충막 상에 에피택시얼 인장 스트레인드 Si막을 3nm-10nm 범위의 두께로 형성하고,

- d) 상기 스트레인드 Si막 상에 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막을 3nm-5nm 범위의 두께로 형성하고,

- e) 상기 스페이서막 상에 2nm-8nm 범위의 두께이고  $1\text{e}18\text{cm}^{-3}$  -  $5\text{e}19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막을 형성하고,

- f) 상기 공급막 상에 0nm-3nm 범위의 두께이고  $5\text{e}17\text{cm}^{-3}$  -  $5\text{e}19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼 인장 스트레인드 Si 캐핑막을 형성하는 것을 포함하는 고전자이동도막 구조체를 준비하는 방법.

#### 청구항 94

- a) 절연체 상의 이완된  $\text{Si}_{1-j}\text{Ge}_j$ 막을 갖는 SGOI 기판을 제공하고-상기 이완된  $\text{Si}_{1-j}\text{Ge}_j$ 막은 상기 SGOI 기판 형성시에 도핑됨,

- b) 상기 도핑된  $\text{Si}_{1-j}\text{Ge}_j$ 막 상에  $\text{Si}_{1-k}\text{Ge}_k$  스페이서막을 형성하고,

- c) 상기  $\text{Si}_{1-k}\text{Ge}_k$  스페이서막 상에 압축 스트레인드  $\text{Si}_{1-m}\text{Ge}_m$  채널층을 형성하고,

- d) 상기 압축 스트레인드  $\text{Si}_{1-m}\text{Ge}_m$  채널층 상에  $\text{Si}_{1-n}\text{Ge}_n$  스페이서막을 형성하는 것을 포함하는 고정공이동도막 구조체를 준비하는 방법.

#### 청구항 95

제 94 항에 있어서, 이온 주입 또는 인-시투 도핑을 이용하여 상기  $\text{Si}_{1-j}\text{Ge}_j$ 막을  $1\text{e}18$  -  $5\text{e}19$  atoms/cm<sup>3</sup> 의 농도 레벨까지 p타입 도핑시키는 단계를 더 구비하는 것을 특징으로 하는 고정공이동도막 구조체를 준비하는 방법.

#### 청구항 96

제 94 항에 있어서, 상기 SGOI 기판을 형성하는 데에 있어서 막 전이 전에 상기 이완된  $\text{Si}_{1-j}\text{Ge}_j$  막을  $1\text{e}18$  -  $5\text{e}19$  atoms/cm<sup>3</sup> 의 농도 레벨까지 붕소로 사전도핑시키는 것을 특징으로 하는 고정공이동도막 구조체를 준비하는 방법.

### 명세서

#### 기술 분야

&lt;1&gt;

본 발명은 일반적으로 실리콘 및 실리콘 게르마늄 기반의 반도체 트랜지스터 소자들에 관한 것이며, 더욱 상세하게는 RF, 마이크로파, 서브밀리미터파 및 밀리미터파를 채택하는 여러 가지 통신 애플리케이션의 초고속, 저잡음 구현 가능한 성장 에피택시얼 전계효과 트랜지스터 구조를 구비하는 소자 디자인에 관한 것이다. 바람직하게는, 상기 에피택시얼 전계효과 트랜지스터 구조는 200GHz를 초과하는  $f_{\text{max}}$ 를 획득하기 위한 초박형 SOI 또는 SGOI 기판 상의 최적의 변조 도프트 헤테로 구조를 형성하기 위한 실리콘 및 실리콘 게르마늄막들을 갖는 고이동도 스트레인드 n채널 트랜지스터에 대한 임계의 소자 스케일링 및 막 구조 디자인을 구비한다.

#### 배경 기술

&lt;2&gt;

변조 도프트 인장 스트레인드(modulation-doped tensile-strained) Si 양자 우물들(quantum wells)에서 전자 이동도가 상당히 크다. 즉, 벌크 실리콘의 3-5배라는 강점 때문에 Si/SiGe n채널 변조 도프트 전계효과 트랜지스터들(MODFETs)이 장기간 개발되어 왔다. 그 후에, SiGe MODFETs은 SiGe 이종접합 바이폴라 트랜지스터들(HBTs)에 비하여 저전력을 소비하고 저잡음 특성을 갖는다는 것이 알려지고 있다. 마찬가지로, RF 벌크 Si CMOS 소자에 비교해볼 때, SiGe MODFETs은 여전히 저잡음 특성을 갖고, 더 높은 최대 진동 주파수( $f_{\text{max}}$ )를 갖는다. 결론적으로, Si/SiGe MODFETs는 고속, 저잡음 및 저전력 통신 애플리케이션을 위한 점점 더 매력적인 장치가 되고 있다. 이때, 저비용 및 CMOS 로직 기술과의 호환성이 요구되며, 때로는 이것이 필수적이다. 최근에는, 0.2  $\mu$

■ 내지  $0.5 \mu\text{m}$  범위의 긴 채널 길이를 갖는 n채널 MODFETs은 향상된 소자 성능을 보여주고 있다.

<3> 전형적으로, Si/SiGe MODFET 소자는 도핑되지 않은, 인장 스트레인드 실리콘(nFET) 또는 압축 스트레인드 SiGe(pFET) 양자 우물(quantum well) 채널들을 채택하므로써, 상기 유도된 스트레인이 캐리어 구속(carrier confinement)을 제공함과 더불어 채널 내에서의 캐리어 이동도를 증가시키는데에 이용된다. 변조 도핑의 상승적 추가는 도편트들로부터 이온화된 불순물 산란을 감소시키고, 매립 채널 내의 표면 거칠기 산란을 더 감소시킴으로써 채널 내의 캐리어 이동도를 더 향상시킨다. 이완된  $\text{Si}_{0.7}\text{Ge}_{0.3}$  완충막 상에 성장된 인장 스트레인드 실리콘 채널 내의 전자 이동도는 상온에서  $2800 \text{cm}^2/\text{V}\cdot\text{s}$ 의 높은 이동도를 기록하였다. 반대로,  $\text{Si}_{0.35}\text{Ge}_{0.65}$  완충막 상에 성장된 순수 Ge 채널 내에서는  $1750 \text{cm}^2/\text{V}\cdot\text{s}$ 의 매우 높은 정공 이동도가 얻어졌다[R. Hammond, 등, DRC, 1999]. 스트레인드 실리콘 nMODFET을 위하여 얻어진 최상의  $f_T$ 는 90 GHz이고[M. Zeuner, 2002], 최상의  $f_{\max}$ 는 190 GHz이다[Koester, 등에 의하여 공개]. 아직까지는, Si/SiGe MODFETs으로는  $f_T$  및  $f_{\max}$ 가 200 GHz까지 이르지 못했다.

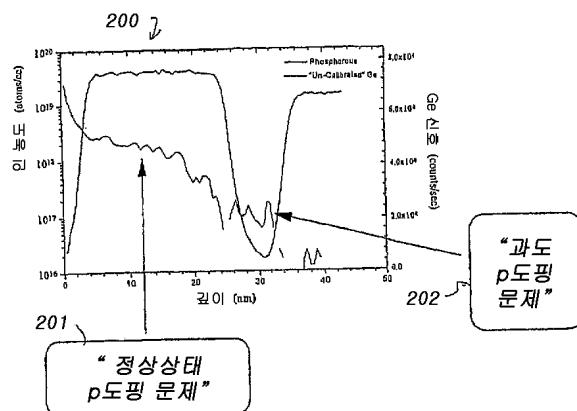

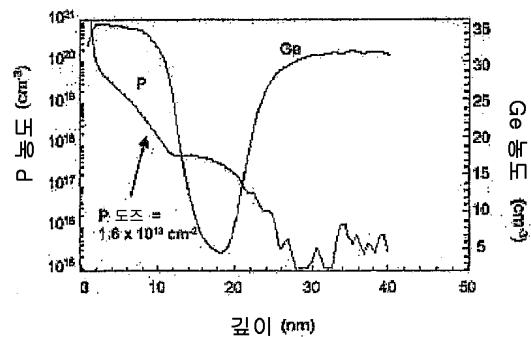

<4> 상기 발명자들에 의하여 수행된 시뮬레이션 연구에 기술된 바와 같이, 더 높은 속도를 얻기 위하여, 상기 MODFET은 세로 치수 및 가로 치수 모두 적절하게 스케일링되어야 한다. 그러나, 다음과 같은 원인에 기인하여 MODFETs의 스케일링은 CMOS 스케일링보다 훨씬 더 어려움이 증명된다. 1) 가로 스케일링은 가로 스케일링을 막는 주요 장애물이 되는 소오스 및 드레인이 가까워지는 것 및 CMOS의 경우와 같이 단채널 효과 및 벌크 편치 쓰루를 유발한다. 그리고, 2) 막 구조의 세로 스케일링은 중대한 것으로 판명된다. 가로 스케일링 단독으로는 성능의 스케일링을 유지하지 못한다. 그러나, 양자 우물( $d_{\text{QW}}$ )의 깊이를 감소시키는 MODFET 구조들의 세로 스케일링은 꽤 도전할만하며, 특히 Annual Review of Materials Science, vol. 30, 2000, pp. 348-355에서 설명된 바와 같이 전형적으로 인으로 도핑된 n+ 공급막의 스케일링 및 갑작스런 도핑에 기인한다. 도 6은 G1(세대) 막 구조의 인(P) 도핑 프로파일의 그래프(200) 및 CVD 성장 시스템에서의 인 도핑과 관련된 정상 상태 P 도핑(201) 문제 및 과도 P 도핑 문제들(202)을 도시한다.

<5> MODFET 소자 구조들의 제조에 있어서 가로 및 세로 스케일링 문제들을 극복하는 MODFET 소자 구조들을 위한 스케일링 기술을 제공하는 것이 매우 바람직할 것이다.

<6> 동일 양수인의, 동시 계류중인 2003년 3월 15일에 출원되고, J. Chu 등에 의한 "마이크로 전자공학을 위한 듀얼 긴장 상태 SiGe 막들(Dual strain state SiGe Layers for Microelectronics)"이라는 제목의 미국 특허 출원 제 10/389,145 호에 더 증명되어 왔다. 상기 미국 특허 출원의 개시 내용은 여기서 그의 내용 전체가 참조문헌으로 병합되었다. 두꺼운 SGOI 기판 상의 MODFET는 벌크 기판 상의 MODFET처럼 작용할 것이다. 동시 계류중인 U.S. 특허 출원 제 10/389,145호는 고성능을 위한 결정적인 막 구조를 규정하지 않고 SGOI 기판 상의 일반적인 MODFET 막 구조를 특히 기술한다.

<7> 초박형 절연체 상의 SiGe(SGOI) 기판 상에 세워진 스케일링된 MODFET 소자 구조를 제공하는 것이 더욱 바람직할 것이며, 여기서 상기 MODFET 소자 구조는 더 나은 잡음 특성, 허용되는 전압 이득 및 좋은 턴-오프 특성들의 초고속 소자 성능(예컨대,  $f_T, f_{\max} > 300\text{GHz}$ )을 보여준다.

### 발명의 상세한 설명

<8> 본 발명은 매우 향상된 RF 성능을 보여주는 얇은 SGOI/SOI 기판 상에 적절히 스케일링되어 구성된 고전자 이동도 n채널 MODFET 소자에 관한 것이다.

<9> 본 발명은 종래 기술의 한계를 제기하고 nMODFET 막 구조 및 전례 없던 정도로의 소오스/드레인 정선의 세로 스케일링 및 상기 소자 구조의 가로 스케일링을 성취함으로써 허용되는 전압 이득 및 좋은 턴-오프 특성들의 초고속 성능 (예컨대,  $f_T, f_{\max} > 300\text{GHz}$ ) 을 보여주는 소자로 귀결되는 MODFET 소자 및 제조방법에 관한 것이다.

<10> 본 발명의 MODFET 소자를 제조하는 방법에서, 상기 MODFET 소자는 초박형 절연체 상의 SiGe(SGOI) 기판 상에 세워져, 바디(body)가 완전히 공핍된다. 억제된 단채널 효과에 기인하여, 출력 컨덕턴스(gd)는 감소될 것이다. 그러므로, DC 전압 이득( $g_m/g_d$ ), 선형성 및  $f_{\max}$ 는 상당히 향상된다. 게다가, 초박형 SiGe 완충막들의 제공은 구동 전류를 감소시키는 SiGe의 낮은 열 전도도에 기인한 셀프-히팅(self-heating) 또한 감소시킨다. 벌크 MODFET와 비교해볼 때, 완전히 공핍된 SGOI MODFET 은 더 나은 잡음 특성 및 더 낮은 소프트 에러율을 보인다. 바람직하

계는, 본 발명의 에피택시얼 전계효과 트랜지스터 구조는  $f_{max} > 300\text{GHz}$ 를 얻기 위하여 초박형 SOI 또는 SGOI 기판 상의 최적의 변조 도프트 헤테로 구조를 형성하기 위한 실리콘 및 실리콘 게르마늄 막들을 갖는 고이동도 스트레이드 n채널 트랜지스터의 임계 소자 스케일링 및 막 구조 디자인을 구비한다.

<11> 인 혼합율이 성장 속도에 의해 조절될 수 있다는 연구 결과에 따라(Annual Review of Materials Science, vol. 30, 2000, pp. 348-355 참고), 갑작스러운 P 도핑의 얇은 SiGe 에피택시얼 막을 얻기 위한 신규한 MODFET 소자 구조 방법을 제공하는 것이 본 발명 목적이다. 이러한 목적에서, 신규한 저온 성장 기술이 초고속 성능을 위해 요구되는 MODFET 막 구조의 적절한 세로 스케일링 또는 디자인에 적응시키고 맞추기 위한 갑작스러운 인 도핑 프로파일들을 얻기 위해 수행된다.

<12> 제조 공정동안 인 혼합을 방지하기 위하여, 동일 양수인의, 동시 계류중인 "UHV-CVD에 의한 Si 상의  $\text{Si}_{1-x-y}\text{Ge}_x\text{C}_y$  및  $\text{Si}_{1-y}\text{C}_y$  혼합막의 에피택시얼 및 다결정 성장(Epitaxial and Polycrystalline Growth of  $\text{Si}_{1-x-y}\text{Ge}_x\text{C}_y$  and  $\text{Si}_{1-y}\text{C}_y$  Alloy Layers on Si by UHV-CVD)"을 제목으로 하는 미국 특허 출원 제 09/838,892호에 기술된 방법과 같이 작은 양의 탄소가 SiGe 공급막의 에피택시얼 성장동안 혼합될 수 있다. 상기 미국 특허 출원의 개시 내용은 여기서 그 내용 전체가 참고문헌으로 병합되었다.

<13> 본 발명은 또한 적절히 스케일링되고 얇은 SGOI/SOI 기판 상에 세워져 매우 높은 RF 성능을 갖는 고정공 이동도 p채널 MODFET에 관한 것이다.

### 실시예

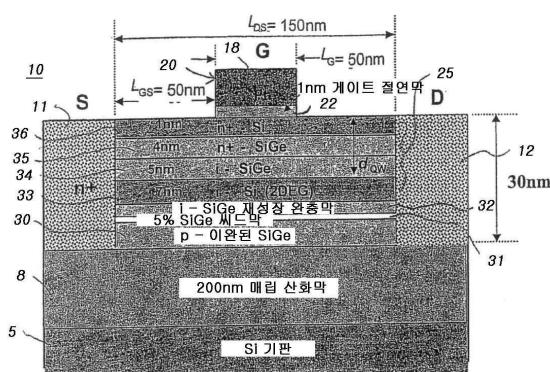

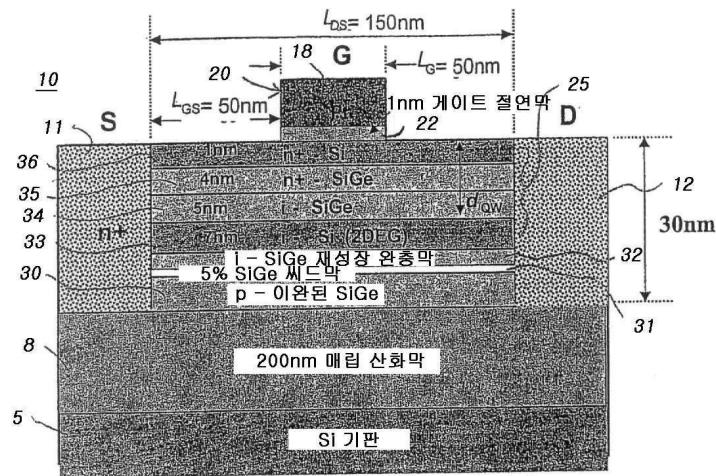

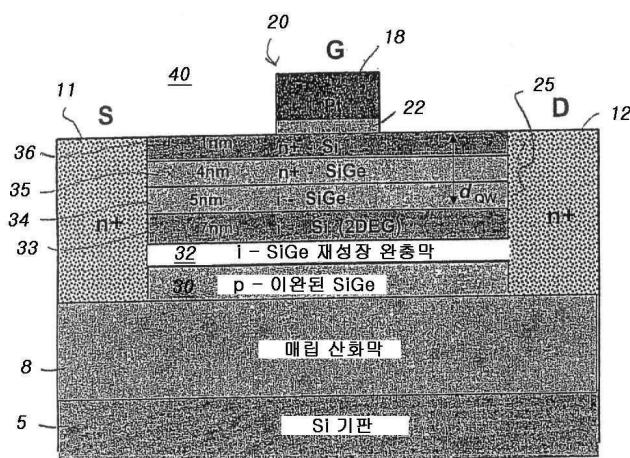

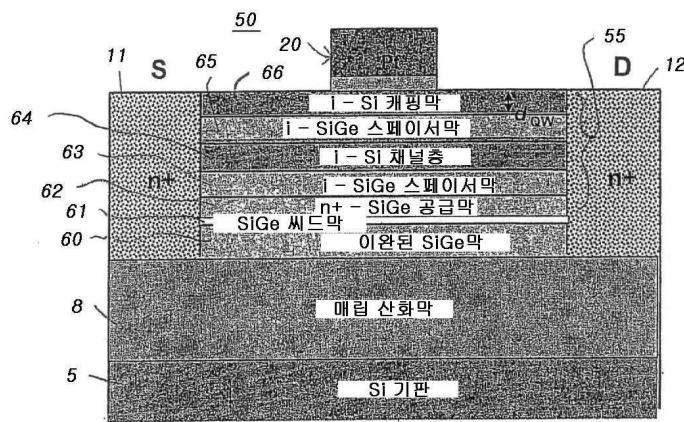

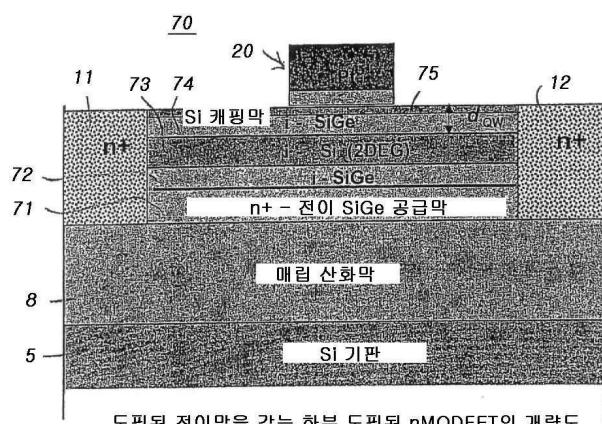

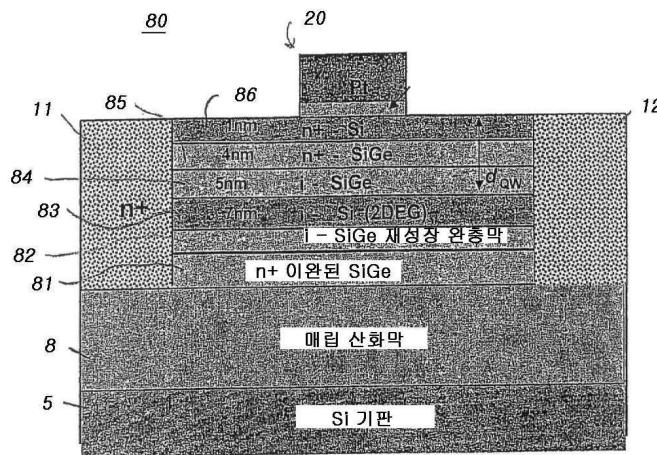

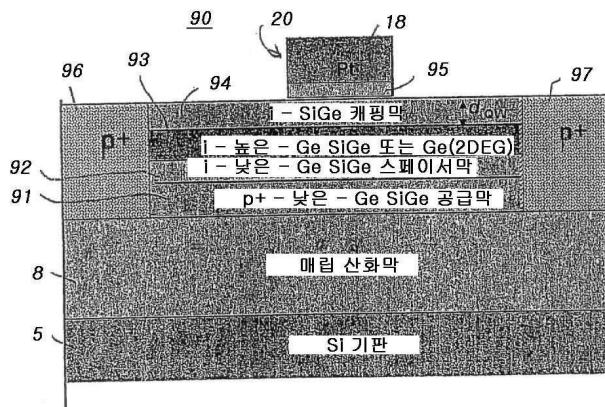

<33> 도 1a-1e는 본 발명에 따라 적절히 스케일링된 얇은 SGOI(SiGe-onInsulator) 기판(세대 G1-G4 소자들) 상의 Si/SiGe n타입 MODFET 구조들을 보여주는 개략적 단면도들이다. 도 1f는 본 발명에 따라 적절히 스케일링된 얇은 SGOI 기판 상의 Si/SiGe p타입 MODFET 구조를 도시한다.

<34> 도 1a는 특히 제1 실시예에 따른 MODFET 소자를 나타낸다. 도 1a에 보여지는 바와 같이, 상부 도핑된 nMODFET 소자(top doped nMODFET device; 10)가 제공되며, 상기 상부 도핑된 nMODFET 소자(10)는 Si 기판층(5), 상기 기판층(5) 상에 형성되며, 200nm의 두께 범위까지 될 수 있으며 실리콘의 산화물, 질화물, 산질화물을 포함할 수 있는 매립 유전막(8), 각각 n+타입으로 도핑된 소오스 및 드레인 영역들(11,12) 사이에 형성된 채널 영역(25), 및 게이트 도전체(18)를 상기 채널(25)로부터 분리시키는 게이트 유전막(22)을 구비하는 게이트 구조체(20)를 포함한다. 상기 도면에서 보여지는 바와 같이, 상기 게이트 유전막은 실리콘의 산화물, 질화물, 산질화물, 및 하프늄(Hf), 알루미늄(Al), 지르코늄(Zr), 란타늄(La), 이트륨(Y) 및 탄탈륨(Ta)의 단일 또는 조합의 산화물 및 실리케이트일 수 있다. 본 발명에 따르면, 드레인, 소오스, 게이트 및 채널 영역들을 구비하는 상기 소자의 크기는 스케일링 되었음을 이해하는 것이 중요하다.

<35> 도 1a에 있어서 소자(10)의 상기 채널 영역(25)의 구성은 다음과 같다. p타입 도펜트를 갖는 이완된 SiGe막(30)이 매립 유전막(8) 상에 제공되며, 상기 이완된 SiGe막(30)은 30-50% 범위의 Ge 함유량을 갖고, 20nm-30nm 범위의 두께이다. 이온 주입 또는 인-시투 도핑 중 하나를 사용하는 상기 p타입 도핑의 농도는  $1\text{e}14\text{cm}^{-3}$  -  $5\text{e}17\text{cm}^{-3}$  범위이다. 상기 이완된 SiGe막은  $1\text{e}4\text{cm}^{-3}$  -  $5\text{e}17\text{cm}^{-3}$ 의 농도 레벨로 사전 도핑(predoped)될 수 있다. 바람직하게는, 상기 이완된 SiGe막 및 상기 채널(25)을 포함하는 다른 막들은 UHVCVD 기술에 따라 성장되나, MBE, RTCVD, LPCVD 공정들과 같은 다른 기술들이 채택될 수 있다. 그 다음, 5 퍼센트(5%) SiGe 씨드막(31)[ $\text{Si}_{0.95}\text{Ge}_{0.05}$ ]이 상기 이완된 SiGe막(30) 상에 에피택시얼 성장되고, 진성  $\text{Si}_{1-x}\text{Ge}_x$  재성장 완충막(32)이 상기 형성된 SiGe 씨드막(31) 상에 형성된다. 에피택시얼 성장된 SiGe 씨드막의 두께는 0nm-5nm의 범위에 이르며, 상기 진성 SiGe 재성장 완충막(32)의 두께는 20nm-30nm의 범위에 이르고, 10%-40% 범위의 Ge 함유량 "x"를 갖는다. 그 다음에, 에피택시얼 인장 스트레이드 Si막(33)이 상기 SiGe 완충막(32) 상에 5nm-7nm 범위의 두께로 성장된다. 그 다음에, 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막(34)이 상기 스트레이드 Si막 상에 3nm-5nm의 범위의 두께로 형성되고, 30-40%의 범위의 Ge 함유량 "y"를 갖는다. 그 다음, 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막(35)이 상기 스페이서막 상에 2nm-8nm 범위의 두께로 성장되고,  $2\text{e}18\text{cm}^{-3}$  -  $5\text{e}19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 가지며 35-50% 범위의 Ge 함유량 "z"를 갖는다. 상기  $\text{Si}_{1-z}\text{Ge}_z$  공급막은 425°C-550°C의 온도 범위에서 성장될 수 있고, 포스핀 가스를 도펜트 전구체로서 단일로 사용하거나, H<sub>2</sub>, He, Ne, Ar, Kr, Xe, N<sub>2</sub>를 포함하는, 그러나 이에 한정하지는 않는, 그룹에서 하나 또는 그 이상의 원소와 혼합하여 인-시투 도핑될 수 있다. 바람직하게는, 상기 포스핀 가

스 도편트 전구체의 유량은 선형 기울기 또는 경사진 프로파일이어서 상기 인-시투 도핑이 에피택시얼 성장 공정을 봉괴시킴 없이 수행된다. 더욱이  $\text{AsH}_3$  또는  $\text{SbH}_3$  같은 전구체가 사용될 수 있음은 물론이다. 여기에 언급되는 바와 같이, 제조 공정 동안 상기 P 확산을 방지하기 위해서, 예컨대, 약 0.1-2%, 바람직하게는 약 1-1.5%의 C 함유량을 갖는 SiGeC막처럼, 상기 SiGe 공급막(34)의 에피택시얼 성장 동안 작은 양의 탄소가 혼합될 수 있다. 마지막으로, 에피택시얼 인장 스트레인드 Si 캐핑막(36)이 상기 공급막(35) 상에 0nm-3nm 사이의 두께로 성장되고,  $5\text{e}17\text{cm}^{-3}$  -  $5\text{e}19\text{cm}^{-3}$ 의 범위의 n타입 도핑 농도를 갖도록 성장된다.

<36> 도 1a의 상기 트랜지스터 소자를 형성하기 위하여, 상기 게이트 유전막(22)이 상기 스트레인드 Si 캐핑막 상에 형성되고, 0-1nm 범위의 등가 산화물 두께(equivalent oxide thickness)를 갖는다. 상기 게이트 도전체(18)는 30nm-100nm 범위의 길이로, 상기 게이트 유전막(22) 상에 T-게이트 구조, 직사각형(rectangular) 구조 또는 멀티-핑거(multi-finger) 구조를 갖도록 형성될 수 있으며, Pt, Ir, W, Pd, Al, Au, Cu, Ti 또는 Co의 단일 또는 조합물을 포함할 수 있다. 상기 형성된 드레인 영역(12)은  $5\text{e}19\text{cm}^{-3}$ 보다 큰 n타입 도핑 농도를 갖고; 상기 형성된 소오스 영역(11)은  $5\text{e}19\text{cm}^{-3}$ 보다 큰 n타입 도핑 농도를 갖는다. 상기 게이트 도전체(18)와 드레인 또는 소오스 영역 중 어느 하나와의 거리는 약 20nm - 100nm의 범위이다. 도면에 도시되지는 않았으나, 상기 소자는 상기 게이트 전극(20)을 둘러싸는 패시베이션막을 더 포함할 수 있고, 상기 패시베이션막은 1-4 범위의 유전율을 가질 수 있다. 도 1a에 지시된 바와 같이, 양자 우물(quantum well)의 깊이, 상기 형성된 nMODFET의  $d_{\text{QW}}$ 는 진성 SiGe(34)의 스페이서막, n+타입 도핑된 SiGe(35)의 막 및 n+ 타입 도핑된 Si 캐핑막(36)을 구비하고, 도 1a에 도시된 치수처럼 합쳐서 약 10nm이다.

<37> 다른 실시예에서 도 1a의 상기 씨드막(31)은 생략될 수 있다. 도 1b는 도 1a의 상기 상부 도핑된(topdoped) nMODFET와 동일하지만 상기 씨드막은 구비하지 않는 고전자 이동도(hight-electronmobility) 소자(40)를 도시한다. 도 1c는 하부 도핑된(bottom doped) 고전자 이동도 MODFET 소자(50)로 결부되는 본 발명의 두번째 실시예를 도시한다. 도 1c에서 보여지는 바와 같이, 상기 소자(50)는 Si 기판층(5), 상기 기판(5) 상에 형성되고, 예컨대, 실리콘의 산화물, 질화물, 산질화물을 포함하는 매립 유전막(8), 및 각각 n+타입 도핑된 소오스 및 드레인 영역들(11,12) 사이에 형성된 채널 영역(55), 및 게이트 구조체(20)를 구비한다. 상기 채널 구조(55)는 절연체(8) 상의 10nm 와 50nm 사이 범위의 두께인 이완된 SiGe막(60), 상기 SiGe막(60) 상에 0nm-5nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{0.95}\text{Ge}_{0.05}$  씨드막(61); 상기 씨드막 상에 2nm-8nm 범위의 두께로 성장되고,  $1\text{e}18\text{cm}^{-3}$  -  $5\text{e}19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  공급막(62); 상기 공급막 상에 3nm-5nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막(63); 및, 상기 스페이서막 상에 3nm-10nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 채널층(64); 상기 스트레인드 Si 층 상에 1nm-2nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막(65); 및, 상기 스페이서막 상에 0nm-2nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 캐핑막(66)을 구비한다. 첫번째 실시예에서와 같이, 예컨대, 약 0.1-2%, 바람직하게는 약 1-1.5%의 C 함유량을 갖는 SiGeC막처럼 작은 양의 탄소가 상기 SiGe 공급막(61)의 에피택시얼 성장 동안 혼합될 수 있다. 더욱이, 도 1c의 두번째 실시예에 대해서는, 모든 상기 게이트 도전체 구조들 및 각각의 소오스/드레인 영역들까지의 거리, 상기 소오스/드레인 영역들의 도편트 농도들, 및 상기 게이트 도전체 금속 및 게이트 유전물의 구성은 첫번째 실시예 (도 1a)와 같다. 도 1c에 지시된 바와 같이, 상기 양자 우물(quantum well)의 깊이, 상기 형성된 nMODFET의  $d_{\text{QW}}$ 는 합쳐서 약 2nm의 깊이인 n+타입 도핑된 Si 캐핑막(66)의 막을 구비한다.

<38> 도 1c의 상기 구조체(50)의 다른 실시예에서는, 상기 씨드막이 생략될 수 있다. 그러므로 결과적인 구조체는 도 1c의 상기 하부 도핑된(bottom-doped) nMODFET와 동일하지만, 상기 씨드막은 구비하지 않는 고전자 이동도 소자이다. 이 다른 실시예에서, SGOI 기판은 절연체 상의 30-40% 범위의 Ge 함유량을 갖고, 20nm-30nm 범위의 두께인 이완된 SiGe막; 상기 이완된 SiGe막 상에 2.5nm-8nm 범위의 두께로 성장되고,  $2\text{e}18\text{cm}^{-3}$  -  $2\text{e}19\text{cm}^{-3}$  범위의 n 타입 도핑 농도 "z"를 가지며, 35-50% 범위의 Ge 함유량을 갖는 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막; 상기 공급막 상에 3nm-5nm 범위의 두께로 성장되고, 30-40% 범위의 Ge 함유량 "y"를 갖는 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막; 상기 스페이서막 상에 5nm-7nm 범위의 두께로 성장되고,  $1\text{e}16\text{cm}^{-3}$ 보다 작은 도핑 농도를 갖는 에피택시얼 인장 스트레인드 Si 채널층; 상기 Si 채널층 상에 1nm-2nm 범위의 두께로 성장되고, 30-40% 범위의 Ge 함유량을 갖는 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막; 및, 상기 스페이서막 상에 0nm-2nm 범위의 두께로 성장된 에피택시얼 인장 스트레

인드 Si 캐핑막을 포함한다. 트랜지스터 소자는 도 1(c)에 대하여 보여지고 설명된 바와 같이 드레인 소오스 및 게이트 도전체 영역들로 완성된다.

&lt;39&gt;

도 1d는 하부 도핑되고 도핑된 전이막을 구비하는 고전자 이동도 nMODFET 소자(70)로 결부되는 본 발명의 세번째 실시예를 도시한다. 도 1(d)에서 보여지는 바와 같이, 상기 소자(70)는 2nm-8nm 범위의 두께이고, 이온 주입 또는 인-시투 도핑에 의하여  $1e18\text{cm}^{-3}$  -  $5e19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 갖는  $\text{Si}_{1-z}\text{Ge}_z$  공급막(71); 상기 공급막 상에 3nm-5nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막(72); 스페이서막(72) 상에 3nm-10nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 채널층(73); 상기 스트레인드 Si 층(73) 상에 1nm-2nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막(74); 및, 상기 스페이서막 상에 0nm-2nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si 캐핑막(75)을 포함하는 SGOI 기판을 구비한다. 바람직하게는, 상기 도핑된 전이  $\text{Si}_{1-z}\text{Ge}_z$  공급막(71)은 Ge 함유량  $z = x+a$  을 갖되, "a"는 약 0-30% 범위, "x"는 30-50% 범위이고, 웨이퍼 접합(wafer bonding) 및 스마트-컷(smart-cut) 공정에 의하여 형성될 수 있다. 이와는 달리, 상기  $\text{Si}_{1-z}\text{Ge}_z$  공급막은 SGOI 기판을 형성하는 데에 있어서 막 전이 전에  $1e18$  -  $5e19$  atoms/cm<sup>3</sup> 의 농도 레벨까지 사전 도핑될 수 있다. 상기 도핑된 전이  $\text{Si}_{1-z}\text{Ge}_z$  공급막은  $\text{Si}_{1-m-n}\text{Ge}_m\text{C}_n$  막을 더 포함할 수 있되,  $m=x+b$ 이고, "b"는 0-30% 범위이며, "n"은 0.1-2% 범위이다. 상기  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막들(72,74)은 "c"가 0-20% 범위인 Ge 함유량  $y = x+c$ 를 구비한다. 게다가, 도 1d의 세번째 실시예에 있어서, 모든 상기 게이트 도전체의 구조들 및 각각의 소오스/드레인 영역들까지의 거리들, 상기 소오스/드레인 영역들의 도편트 농도, 상기 게이트 도전체 금속 및 게이트 유전물의 구성 및 두께들은 첫번째 실시예(도 1a)에 도시된 바와 같다. 도 1d에 지시된 바와 같이, 상기 양자 우물(quantum well)의 깊이, 상기 형성된 nMODFET의  $d_{\text{QW}}$ 는 n+ 타입 도핑된 Si 캐핑막(75) 및 약 4nm 보다 작은 깊이를 갖는 스페이서막(74)의 막을 구비한다.

&lt;40&gt;

도 1e는 하부 및 상부 모두 도핑되고 SiGe 재성장 완충막을 구비하는 고전자 이동도 nMODFET 소자(80)로 결부되는 본 발명의 네번째 실시예를 도시한다. 도 1(e)에서 보여지는 바와 같이, 상기 nMODFET 소자(80)는: 절연체(8) 상의 10nm-50nm 범위의 두께이며,  $1e17\text{cm}^{-3}$  -  $5e19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 가지며, 30-50% 범위의 Ge 함유량을 갖는 이완된 SiGe막(81); 상기 SiGe막(81) 상에 10nm-50nm 범위의 두께로 성장되고, 하부 스페이서막으로 제공되며, 10%-35% 범위의 Ge 함유량 "x"를 구비하는  $\text{Si}_{1-x}\text{Ge}_x$  재성장 완충막(82); 상기 재성장 완충막 상에 3nm-10nm 범위의 두께로 성장된 에피택시얼 인장 스트레인드 Si막(83); 상기 스트레인드 Si막(83) 상에 3nm-5nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막(84); 상기 스페이서막(84) 상에 2nm-8nm 범위의 두께로 성장되고,  $1e18\text{cm}^{-3}$  -  $5e19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막(85); 및, 상기 공급막(85) 상에 0nm-3nm 범위의 두께로 성장되고,  $5e17\text{cm}^{-3}$  -  $5e19\text{cm}^{-3}$  범위의 n타입 도핑 농도를 갖는 에피택시얼 인장 스트레인드 Si 캐핑막(86)을 갖는 SGOI 기판을 구비한다. 상기  $\text{Si}_{1-y}\text{Ge}_y$  스페이서막(84)은 "a"가 0-20% 범위인 Ge 함유량  $y = x+a$ 를 갖고, 상기  $\text{Si}_{1-z}\text{Ge}_z$  공급막은 "b"가 0-30% 범위인 Ge 함유량  $z = x+b$ 를 구비한다. 다른 실시예들에 있어서, 상기  $\text{Si}_{1-z}\text{Ge}_z$  공급막은  $\text{Si}_{1-m-n}\text{Ge}_m\text{C}_n$  막을 포함하되,  $m=x+c$ 이고, "c"는 0-20% 범위이며, "n"은 0.1-2% 범위이다. 게다가, 도 1e의 네번째 실시예에 있어서, 모든 상기 게이트 도전체의 구조들 및 각각의 소오스/드레인 영역들까지의 거리들, 상기 소오스/드레인 영역들의 도편트 농도, 및 상기 게이트 도전체 금속 및 게이트 유전물의 구성 및 두께들은 첫번째 실시예(도 1a)에 도시된 바와 같다. 도 1e에 지시된 바와 같이, 상기 양자 우물(quantum well)의 깊이, 형성된 nMODFET의  $d_{\text{QW}}$ 는 합쳐서 약 16nm 이하의 깊이인 n+타입 도핑된 Si 캐핑막(86), 상기 에피택시얼  $\text{Si}_{1-z}\text{Ge}_z$  공급막(85), 및 스페이서막(84)의 막을 구비한다.

&lt;41&gt;

도 1f는 하부 도핑되고 도핑된 전이막을 구비하는 고정공 이동도(high-hole-mobility) MODFET 소자(80)에 결부되는 본 발명의 다섯번째 실시예를 도시한다. 도 1f에서 보여지는 바와 같이, 상기 pMODFET 소자(90)는: 5nm-25nm 범위의 두께이고,  $1e18$  -  $5e19\text{cm}^{-3}$  범위 농도의 이온주입 또는 인-시투 p타입 도핑을 갖고, 공급막으로써 제공되는 이완된 에피택시얼  $\text{Si}_{1-j}\text{Ge}_j$ 를 갖는 SGOI(절연체(8) 상의 SiGe막(91)) 기판을 구비한다. 이와는 달리, 상기 이완된  $\text{Si}_{1-j}\text{Ge}_j$  막은 상기 SGOI 기판을 형성하는 데에 있어서 막 전이 전에  $1e18$  -  $5e19$  atoms/cm<sup>3</sup> 범위의 봉소 도핑 레벨로 p타입 사전도핑(predoped)될 수 있다; 상기 공급막(91)의 상에 3nm-7nm 범위의 두께로 성장된 에피택시얼  $\text{Si}_{1-k}\text{Ge}_k$  스페이서막(92); 상기 스페이서막 상에 5nm-20nm 범위의 두께로 성장된 에피택시얼 압축 스

트레인드  $Si_{1-m}Ge_m$  채널층(93); 및, 상기 스트레인드  $Si_{1-m}Ge_m$  채널층(93) 상에 2nm-10nm 범위의 두께로 성장된 에피택시얼 스트레인드  $Si_{1-n}Ge_n$  캐핑막(94)을 갖는 SGOI(절연체(8) 상의 SiGe막)을 구비한다. 상기 고정공 이동 도막 반도체 구조체(90)에서 상기  $Si_{1-j}Ge_j$  공급막(91)은 30-70% 범위의 Ge 함유량 "j"를 구비한다. 상기  $Si_{1-k}Ge_k$  스페이서막 (92)은 30-70% 범위의 Ge 함유량 "k"를 구비하고, 상기  $Si_{1-m}Ge_m$  채널층(93)은 60-100% 범위의 Ge 함유량 "m"을 구비하며, 상기 스트레인드  $Si_{1-n}Ge_n$  캐핑막(94)은 0%-30% 범위의 Ge 함유량 n을 구비한다.

<42> 도 1f의 pMODFET 트랜지스터 소자를 형성하기 위하여, 게이트 유전막(95)이 상기 스트레인드 SiGe 캐핑막(94) 상에 형성되고, 0-1nm 범위의 등가 산화물 두께를 갖는다. 상기 게이트 도전체(18)는 30nm-100nm 범위의 길이로 상기 게이트 유전막(95) 상에 형성된 T-게이트 구조, 사각형 구조 또는 멀티-핑거(multi-finger) 구조를 가질 수 있으며, Pt, Ir, W, Pd, Al, Au, Cu, Ti, 또는 Co의 단일 또는 조합물을 포함할 수 있다. 형성된 드레인 영역(97)은  $5e19cm^{-3}$  보다 큰 p타입 도핑 농도를 갖고; 상기 형성된 소오스 영역(96)은  $5e19cm^{-3}$  보다 큰 p타입 도핑 농도를 갖는다. 상기 게이트 도전체(18)와 드레인 또는 소오스 영역 중 어느 하나와의 거리는 약 20nm-100nm 범위이다. 비록 도면에 도시되지는 않았으나, 상기 소자는 상기 게이트 전극(20)을 둘러싸고 1-4 범위의 유전율을 갖는 패시베이션막을 더 포함할 수 있다. 도 1f에 지시된 바와 같이, 상기 양자 우물(quantum well)의 깊이, 상기 형성된 pMODFET(90)의  $d_{QW}$ 는 약 2nm-10nm 범위인 상기 SiGe 캐핑막(94)를 구비한다.

<43> 상기 다른 막 구조들 및 디자인을 갖는 도 1a-1e에 도시된 실시예들을 포함하는 완성된 소자들은 400-600°C, 바람직하게는 500-550°C 범위의 성장 온도 조건들 및 1mTorr-20mTorr 범위의 압력 하에서 UHVCVD에 의해 성장되었다.

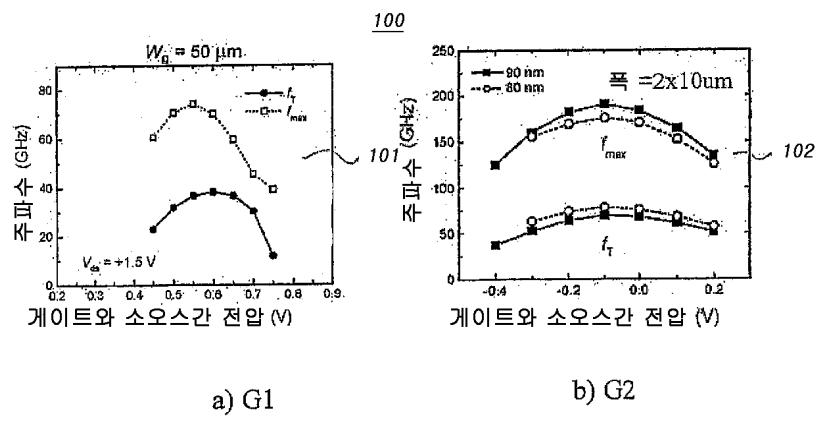

<44> 도 17은 소자 스케일링(예컨대, G1 및 G2 소자들)된 성능(측정된  $f_T$  대  $V_{GS}$ ) 곡선들(100)을 보여준다. 예를 들어, 도 17은  $d_{QW}=15nm$ ,  $L_g=70nm$ 인 G2 소자에 비교되는  $d_{QW}=25nm$ ,  $L_g=250nm$ 인 G1 소자에 대한  $f_T$  곡선을 보여준다. 보여지는 바와 같이, 성능을 더 향상시키기 위해서는, 상기 소자는 도 17에서 보여지는 G2 예에서처럼 가로 및 세로 치수 모두 더 스케일링되어야 한다.

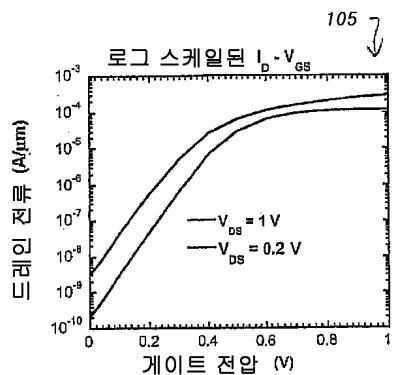

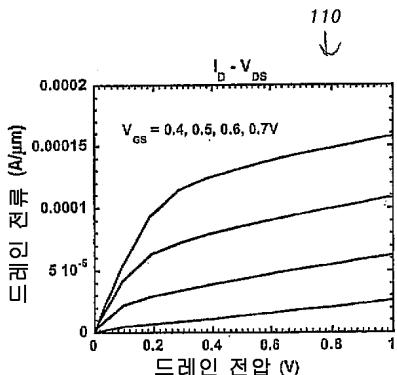

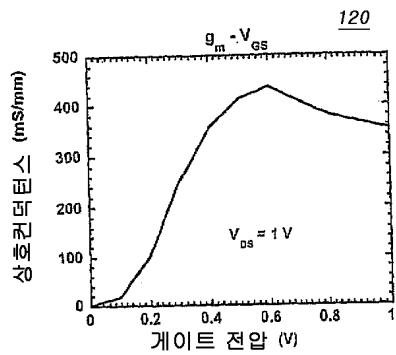

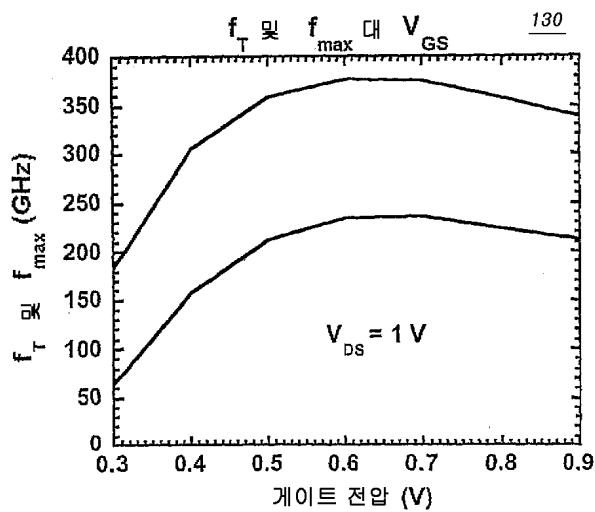

<45> 도 2-5는 도 1a-1f의 적절하게 스케일링된 소자들의 가상의 소자 특성들을 도시한다. 도 2는  $L_{GS}=L_g=L_{GD}=50nm$ 일 때의 도 1의 G4 소자의 가상의  $I_{D-VGS}$  곡선들(105)을 도시한다. 도 3은 도 1의 G4 소자의 가상의  $I_{D-VDS}$  곡선들(110)을 도시하고, 도 4는 도 1에서의 G4 소자의 가상의  $g_{m-VGS}$  곡선들(120)을 도시한다( $L_{GS}=L_g=L_{GD}=50nm$ ). 도 5에서 보여지는 바와 같이,  $f_T=230GHz$ 이고  $f_{max}=370GHz$ 일 때 도 1에서의 상기 소자의 가상의  $f_T$  및  $f_{max}$  대  $V_{GS}$  곡선들(130)이 소자 시뮬레이션에 따라 얻어질 수 있음이 도시되어 있다.

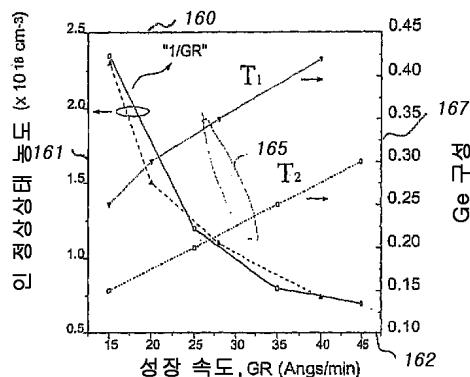

<46> 상술한 바와 같이, 인(P) 도핑은 Ge 함유량 및 UHV CVD 시스템에서의 그것의 관련 성장 속도(associated growth rate)에 의해 조절 가능함이 실험적으로 알려져 왔다. 도 7은 정상 상태의 P 농도(161) 대 UHVCVD(162)에서의 성장 속도를 보여주는 그래프(160)를 도시한다.

<47> 도 7의 정상 상태 P 농도 대 성장 속도 그래프에서 보여지는 바와 같이, 특히, 곡선들(165)로 도시된 P 도핑의 과도 혼합(transient incorporation)은 SiGe막 내의 Ge 함유량(167)에 의해 조절된다. 마찬가지로, 상기 정상 상태 P 농도는 상기 SiGe막의 관련 성장 속도(associated growth rate)에 의해 조절된다. P 프로파일의 돌발성(abruptness)을 얻는 중요 공정은 높은 Ge 함유량을 사용하되, 감소된 성장 속도에서 사용하는 것이나, 이는 높은 Ge는 증가된 또는 높은 성장 속도와 관련이 있는 것으로 잘 알려져 있기 때문에 어렵다.

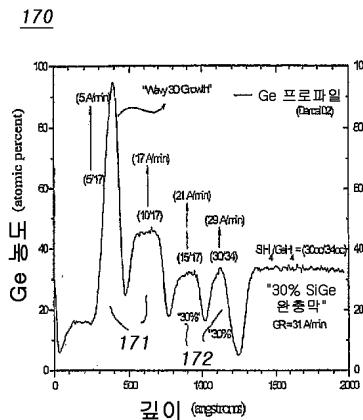

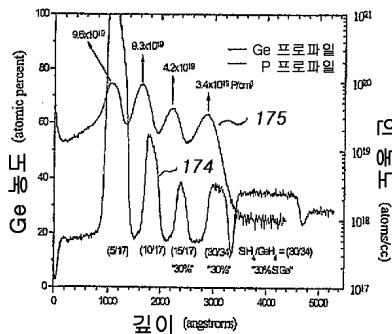

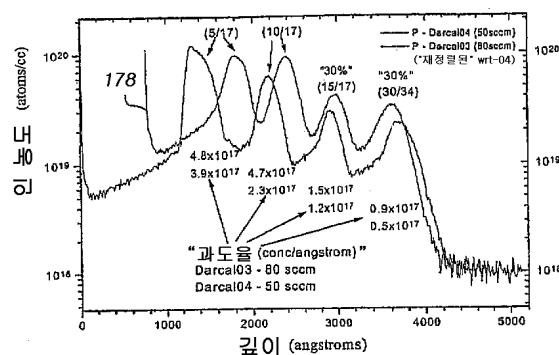

<48> SiGe(30%의 Ge 함유량)의 성장 속도 눈금(170)은 도 8에 도시되는데, 예컨대, 도면에서 보여지는 바와 같이 연속적으로 작아지는 피크(171, 172)를 보여주는 Ge 농도 프로파일이다. PH3를 첨가한 경우 같은 눈금을 사용하는 것은, 즉, 증가된 정상 상태 P 농도(175)는 곡선(174)으로 도시되는 감소된 SiGe 성장 속도의 함수로써 도 9에 도시된다. 유사하게는, 도 10에서 과도 P 혼합 대 감소된 성장 속도들을 도시하는 그래프에서 보여지는 바와 같이, 더 높은 Ge 함유량(177)인 경우에, 상기 과도 P 혼합율 또한 도 10의 프로파일 곡선(178)으로 보여지는 바와 같이 증가한다.

<49> 도 6에서 보여지는 바와 같이 SiH4 대 GeH4(15sccm/17sccm)의 감소된 흐름 조합(flow combination)을 사용함에 따라, G1 도핑 프로파일이 2차이온질량분석(SIMS; secondary ion mass spectroscopy) 프로파일(201, 202)처럼 얻어진다. 대응하는 XTEM(cross-sectional transmission electron micrograph)은 도 13에 도시된다.

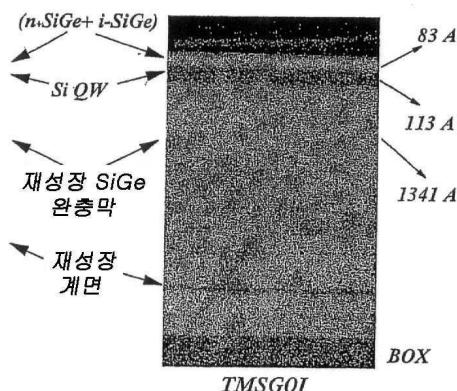

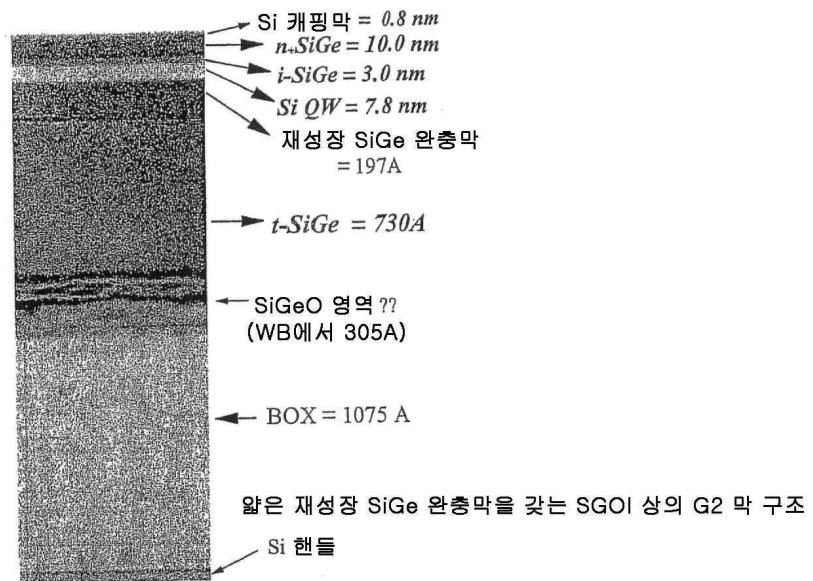

<50> 도 11에서 보여지는 바와 같이 SiH4 대 GeH4(10/17)의 더 낮은 흐름 혼합을 사용함에 따라, G2 도핑 프로파일이

SIMS 프로파일 P 도핑 및 Ge 농도 프로파일처럼 얻어진다. 대응하는 XTEM은 도 14에 도시된다.

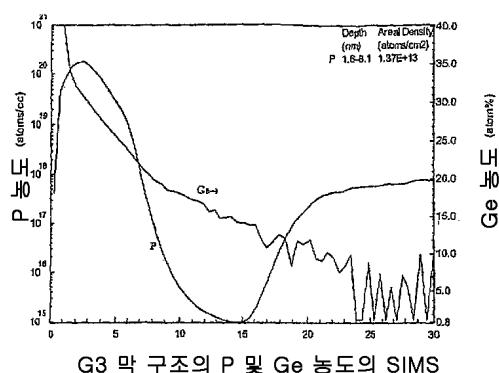

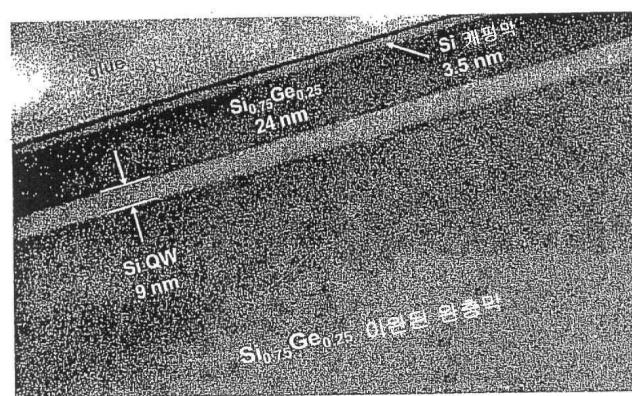

<51> 도 12에서 보여지는 바와 같이 SiH<sub>4</sub> 대 GeH<sub>4</sub> (8/10)의 더욱 더 낮은 흐름 혼합을 사용함에 따라, G3 도핑 프로파일이 SIMS 프로파일 P 도핑 및 Ge 농도 프로파일처럼 얻어진다. 대응하는 XTEM은 도 15에 도시된다. 도 15는 특히 SGOI 기판 상의 50nm의 전이 SiGe막을 갖는 G3 막 구조에 대한 XTEM을 도시하되, 전이 SiGe상의 상기 재성장 SiGe는 재성장 계면에서 탄소 및 산소로 인한 효과들을 최소화하기 위하여 두껍다(예컨대, 약 134.1nm). 그러나, 얇은 SGOI 상의 MODFETs을 만들기 위한 하나의 일은 상기 재성장 SiGe막을 가능한 얇게 만드는 것이다. 성장 공정은 병합되어 동시에 계류중인 미국 특허 출원 10/389,145 호에 기술된 바와 같이 5% SiGe 씨드막을 사용함으로써 개발되어 왔다.

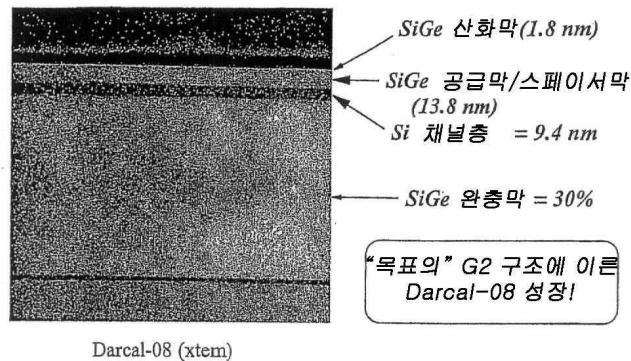

<52> 도 16은 SGOI 기판 상의 73nm 두께의 전이 SiGe막을 갖는 얇은 재성장 SiGe막(예컨대, 약 19.7nm)을 갖는 SGOI 기판 상의 G2 막 구조에 대한 XTEM을 도시한다. 동시에 계류중인 미국 특허 출원 10/389,145 호에 기술된 바와 같은 웨이퍼 접합(wafer bonding) 및 세선화(thinning) 공정에 의해 형성될 수 있는 얇은 SGOI 기판에서 시작하는 것이 유리하다.

<53> 본 발명이 본 발명의 예시적이고 바람직한 실시예들에 관하여 보여지고 기술되는 동안, 형상 및 상세 설명에 있어서 상술한 사항 및 다른 변경들이 첨부한 청구항들의 범위에 의해서만 한정되어야 하는 본 발명의 영감 및 범위로부터 출발함 없이 만들어질 수 있음이 해당 분야의 당업자로부터 이해될 수 있을 것이다.

### 도면의 간단한 설명

<14> 본 발명의 장치 및 발명의 더 많은 특징들, 모양들 및 이점들은 상술한 상세 설명, 첨부된 청구항 및 수반된 도면들에 따라 더 잘 이해될 수 있을 것이다.

<15> 도 1a-1e는 본 발명에 따라 적절히 스케일링된 얇은 SGOI 기판(G1-G4) 상의 본 발명의 Si/SiGe n타입 MODFET 구조를 보여주는 개략적 단면도들이다.

<16> 도 1f는 얇은 SGOI 기판 상의 Si/SiGe p타입 MODFET 구조를 도시한다.

<17> 도 2는 도 1a-1f의 소자들의 시뮬레이션된  $I_d$ - $V_{gs}$  곡선들을 제공하는 그래프를 도시한다( $L_{gs}=L_g=L_{gd}=50\text{nm}$ ).

<18> 도 3은 도 1a-1f의 G4 소자의 시뮬레이션된  $I_d$ - $V_{ds}$  곡선들을 도시한다.

<19> 도 4는 도 1a-1f의 G4 소자의 시뮬레이션된  $g_m$ - $V_{gs}$  곡선들을 도시한다.

<20> 도 5는 도 1a-1f의 G4 소자의 시뮬레이션된  $f_T$  및  $f_{max}$  대  $V_{gs}$  곡선들을 도시한다.

<21> 도 6은 G1(세대) 막 구조의 인(P) 도핑 프로파일 및 G1 막 구조에서 나타나는 정상 상태 및 과도 P 도핑의 SIMS 프로파일을 도시한다.

<22> 도 7은 본 발명에 따라 정상 상태 P 농도 대 성장 UHV CVD 시스템을 나타내는 그래프(160)를 도시한다.

<23> 도 8은 본 발명에 따른 SiGe(30%의 Ge 함유량)의 눈금 성장을 감소(170) 방법을 도시한다.

<24> 도 9는 감소된 성장 속도의 함수로써 정상 상태 P 농도를 나타내는 예시 플롯(plot)을 도시한다.

<25> 도 10은 감소된 성장 속도의 함수로써 과도 P 혼합의 프로파일을 나타내는 그래프이다.

<26> 도 11은 G2 막 구조에서 나타나는 인(P) 도핑 및 Ge 농도의 SIMS 프로파일을 도시한다.

<27> 도 12는 G3 막 구조에서 나타나는 인(P) 도핑 및 Ge 농도의 SIMS 프로파일을 도시한다.

<28> 도 13은 도 6에서 보여진 SIMS 프로파일에 대응하는 벌크 상의 G1 막 구조의 XTEM을 도시한다.

<29> 도 14는 도 11에서 보여진 SIMS 프로파일에 대응하는 벌크 상의 G2 막 구조의 XTEM을 도시한다.

<30> 도 15는 얇은 재성장막을 갖는 SGOI 기판 상의 G3 막 구조의 XTEM을 도시한다.

<31> 도 16은 SGOI 기판 상의 G2 막 구조의 XTEM을 도시한다.

<32> 도 17은  $d_{QW}=25\text{ nm}$ ,  $L_g=250\text{nm}$ 인 G1 소자 및  $d_{QW}=25\text{ nm}$ ,  $L_g=250\text{nm}$ 인 G2 소자의 측정된  $f_T$  대  $V_{gs}$ 를 도시한다.

## 도면

## 도면1a

재성장 완충막을 가진 상부 도핑된 nMODFET의 개략도

## 도면1b

씨드막 없는 상부 도핑된 nMODFET의 개략도

## 도면1c

## 도면1d

## 도면1e

## 도면1f

## 도면2

$L_{gs}=L_g=L_{gd}50\text{nm}$ 인 G4 소자의 시뮬레이션된  $Id-V_{gs}$  곡선들

### 도면3

$L_{gs}=L_g=L_{gd}50\text{nm}$ 인 G4 소자의 시뮬레이션된  $Id-V_{ds}$  곡선들

## 도면4

L<sub>gs</sub>=L<sub>g</sub>=L<sub>gd</sub>50nm인 G4 소자의 시뮬레이션된 g<sub>m</sub>-V<sub>gs</sub> 곡선들

## 도면5

L<sub>gs</sub>=L<sub>g</sub>=L<sub>gd</sub>50nm인 G4 소자의 시뮬레이션된 f<sub>T</sub>, f<sub>max</sub>-V<sub>g</sub> 곡선들

## 도면6

G1 막 구조의 P 도핑 프로파일의 SIMS

## 도면7

정상상태 P 농도 대 성장 속도

## 도면8

Ge의 감소된 성장 속도 눈금 조정

## 도면9

정상상태 P 농도 대 감소된 성장 속도

## 도면10

과도 P 혼합 대 감소된 성장 속도

도면11

G2 막 구조의 P 및 Ge 농도의 SIMS

도면12

도면13

G1 막 구조 TEM

## 도면14

벌크 상의 G2 막 구조

## 도면15

SGOI 상의 G3 막 구조

도면16

도면17

G1 소자 및 G2 소자의 측정된  $f_T$  대  $V_{gs}$