(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3838809号

(P3838809)

(45) 発行日 平成18年10月25日(2006.10.25)

(24) 登録日 平成18年8月11日(2006.8.11)

(51) Int.C1.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>H04L 12/40</b> | <b>(2006.01)</b> | H04L 12/40 | A    |

| <b>G06F 13/38</b> | <b>(2006.01)</b> | G06F 13/38 | 330A |

| <b>G06F 13/42</b> | <b>(2006.01)</b> | G06F 13/38 | 350  |

|                   |                  | G06F 13/42 | 320A |

請求項の数 4 (全 16 頁)

(21) 出願番号 特願平11-88526

(22) 出願日 平成11年3月30日(1999.3.30)

(65) 公開番号 特開2000-286872(P2000-286872A)

(43) 公開日 平成12年10月13日(2000.10.13)

審査請求日 平成16年7月16日(2004.7.16)

(73) 特許権者 501285133

川崎マイクロエレクトロニクス株式会社

千葉県千葉市美浜区中瀬一丁目3番地

(74) 代理人 100080159

弁理士 渡辺 望穂

(74) 代理人 100090217

弁理士 三和 晴子

(72) 発明者 大須賀 文一

東京都千代田区内幸町2丁目2番3号

川崎製鉄株式会社東京本社

内

審査官 矢頭 尚之

最終頁に続く

(54) 【発明の名称】シリアルデータ転送装置

## (57) 【特許請求の範囲】

## 【請求項1】

データを転送するためのシリアルデータラインおよび前記データを保持するクロック信号を転送するためのシリアルクロックラインを介して接続される少なくとも1つのマスタデバイスと、複数のスレーブデバイスと、論理手段とを有し、

通常動作モードにおいて、前記マスタデバイスの1つから前記シリアルデータラインを介して前記スレーブデバイスの1つを指定する固有アドレスが転送され、当該固有アドレスを有するスレーブデバイスが第1の端子より前記シリアルデータラインにアクノリッジ信号を出力し、

ローカルモードにおいて、前記マスタデバイスの1つから前記シリアルデータラインを介して前記複数のスレーブデバイスのうちのあらかじめ設定されている複数のスレーブデバイスに共通の共有アドレスが転送され、当該共有アドレスを有するスレーブデバイスが前記第1の端子と異なる第2の端子よりアクノリッジ信号を前記論理手段に出力し、当該論理手段は前記共有アドレスを有するスレーブデバイスから出力される前記アクノリッジ信号の論理をとって前記シリアルデータラインに出力することを特徴とするシリアルデータ転送装置。

## 【請求項2】

前記論理手段は前記共有アドレスを有する複数のスレーブデバイスの前記第2の端子に入力端子が接続されたORゲートであることを特徴とする請求項1に記載のシリアルデータ転送装置。

**【請求項 3】**

データを転送するためのシリアルデータラインおよび前記データを保持するクロック信号を転送するためのシリアルクロックラインを介して少なくとも1つのマスタデバイスと接続されるスレーブデバイスであって、

前記マスタデバイスと前記シリアルデータラインを介してデータ通信を行う手段と、

前記マスタデバイスから前記シリアルデータラインを介して転送されるアドレス情報と自分自身に固有の固有アドレスとを比較する手段と、

前記マスタデバイスから前記シリアルデータラインを介して転送されるアドレス情報と他のスレーブデバイスとの共通の共有アドレスとを比較する手段と、

前記マスタデバイスから転送されたアドレス情報が前記固有アドレスであると認識したときに第1の端子からアクノリッジ信号を出力する手段と、

前記マスタデバイスから転送されたアドレス情報が前記共有アドレスであると認識したときに前記第1の端子とは異なる第2の端子からアクノリッジ信号を出力する手段とを有することを特徴とするスレーブデバイス。

**【請求項 4】**

さらに、セレクト信号の状態に応じて、前記マスタデバイスから送信される前記データがいずれかに保持される第1および第2のレジスタを有し、

前記第1のレジスタの出力は、当該スレーブデバイスに接続される装置に対して直接接続され、前記第2のレジスタの出力は、I/Oポートを介して、当該スレーブデバイスに接続される装置に双方向に接続されていることを特徴とする請求項3に記載のスレーブデバイス。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、マスタデバイスとスレーブデバイスとの間でシリアルにデータの転送を行うシリアルデータ転送装置に関するものである。

**【0002】****【従来の技術】**

例えば、マイクロコントローラとその周辺デバイスとの間では、8ビット(1バイト)のデータを1つの単位としてデータのやり取りが行われている。シリアルデータ転送装置は、例えばIIC(I<sup>2</sup>C)-bus(Inter-IC Controlバス)(以下、単にIICバスという)に代表されるように、8ビットのデータを単位としてデータのやり取りを行うマスタデバイスと複数のスレーブデバイスとの間でシリアルにデータの転送を行うものである。

**【0003】**

前述のIICバスを適用するシリアルデータ転送装置では、例えばマイクロコントローラ等の制御する側のマスタデバイスと、周辺機器等の制御される側の複数のスレーブデバイスとの間は、データを転送するためのシリアルデータライン(SDA)と、データを保持するクロック信号を転送するためのシリアルクロックライン(SCL)という、ブルアップ抵抗により電源に接続された2つの双方向のシリアルラインで相互に接続されている。

**【0004】**

ここで、シリアルデータラインは、基本的に、シリアルクロックラインがローレベルの期間に変化する。シリアルクロックラインがハイレベルの間に、シリアルデータラインがハイレベルからローレベルに変化すると、データの転送開始を指示するスタート信号(START)であることを意味し、ローレベルからハイレベルに変化すると、データの転送終了を指示するストップ信号(STOP)であることを意味する。

**【0005】**

マスタデバイスは、まず、1ビットのスタート信号をシリアルデータライン上に出力する。続いて、各々のスレーブデバイスにあらかじめ独自に割り当てられている7ビットの固有アドレスと、これに続くスレーブデバイスへのデータライトまたはスレーブデバイスか

10

20

30

40

50

らのデータリードを指示する1ビットのデータ制御信号とからなる8ビットのパラレルデータを、シリアルデータライン上にM S B (Most Significant Bit)側から順次シリアルに出力する。

#### 【0006】

各々のスレーブデバイスでは、マスタデバイスからシリアルデータライン上に出力される8ビットのパラレルデータを、シリアルクロックラインから供給されるクロック信号に同期して順次シリアルに受信し、これを自分自身にあらかじめ割り当てられている固有アドレスと比較する。そして、自分自身の固有アドレスに一致するスレーブデバイスが、シリアルデータライン上に1ビットのアクノリッジ信号（肯定応答信号）を出力する。

#### 【0007】

マスタデバイスは、スレーブデバイスからシリアルデータライン上に出力されたアクノリッジ信号を確認した後、スレーブデバイスへのデータライトの場合、転送すべき8ビットのパラレルデータをシリアルデータライン上に順次シリアルに出力する。アクノリッジ信号を出力したスレーブデバイスは、シリアルデータライン上にマスタデバイスから出力される8ビットのパラレルデータを順次シリアルに受信し、その後、同じく1ビットのアクノリッジ信号を出力する。

#### 【0008】

マスタデバイスからスレーブデバイスに対しては、必要に応じて所定バイト数のデータが転送される。その後、マスタデバイスは、1ビットのストップ信号をシリアルデータライン上に出力し、スレーブデバイスは、このストップ信号を受け取ってデータの送信終了を確認する。以後同じようにして、マスタデバイスは、所望の固有アドレスを出力して、次にデータを転送すべきスレーブデバイスを順次指定してデータを転送することを繰り返し行う。

#### 【0009】

I I Cバスを適用するシリアルデータ転送装置では、データを転送すべき複数のスレーブデバイスを順次アクセスする必要がある。したがって、複数の同じスレーブデバイスに対して、例えばスタート、ストップ、アボート等のスレーブデバイスに接続される複数の同じ装置を制御するための同じ制御信号等を含むデータを転送する場合であっても、複数のスレーブデバイスを同時にアクセスすることができないという問題がある。

#### 【0010】

これを解決するために、従来のシリアルデータ転送装置では、複数のスレーブデバイスに各々接続されている装置に制御信号をマスタデバイスから直接接続して同時に制御したり、あるいは、同時に制御することが無理な場合は、シリアルクロックラインから供給されるクロック信号の周波数を高くして、複数のスレーブデバイスにデータを転送したり、制御する時間差を小さくするなどの手法がとられている。

#### 【0011】

しかし、制御信号をスレーブデバイスに接続されている装置に対してマスタデバイスから直接接続すると、シリアルデータラインやシリアルクロックラインの他にライン数が増大して、シリアルデータ転送のメリットが減少するし、クロック信号の周波数を高くしたとしても、同じデータを各々のスレーブデバイスに繰り返し転送するため、スレーブデバイスの数が多くなるほど長時間が必要になり、無駄が多くなるという問題点がある。

#### 【0012】

##### 【発明が解決しようとする課題】

本発明の目的は、前記従来技術に基づく問題点をかえりみて、マスタデバイスから複数のスレーブデバイスに対して同じデータを同時に転送することができるシリアルデータ転送装置を提供することにある。

#### 【0013】

##### 【課題を解決するための手段】

上記目的を達成するために、本発明は、データを転送するためのシリアルデータラインおよび前記データを保持するクロック信号を転送するためのシリアルクロックラインを介

10

20

30

40

50

して接続される少なくとも 1 つのマスタデバイスと、複数のスレーブデバイスと、論理手段とを有し、

通常動作モードにおいて、前記マスタデバイスの 1 つから前記シリアルデータラインを介して前記スレーブデバイスの 1 つを指定する固有アドレスが転送され、当該固有アドレスを有するスレーブデバイスが第 1 の端子より前記シリアルデータラインにアクノリッジ信号を出力し、

ローカルモードにおいて、前記マスタデバイスの 1 つから前記シリアルデータラインを介して前記複数のスレーブデバイスのうちのあらかじめ設定されている複数のスレーブデバイスに共通の共有アドレスが転送され、当該共有アドレスを有するスレーブデバイスが前記第 1 の端子と異なる第 2 の端子よりアクノリッジ信号を前記論理手段に出力し、当該論理手段は前記共有アドレスを有するスレーブデバイスから出力される前記アクノリッジ信号の論理をとって前記シリアルデータラインに出力することを特徴とするシリアルデータ転送装置を提供するものである。

ここで、前記論理手段は前記共有アドレスを有する複数のスレーブデバイスの前記第 2 の端子に入力端子が接続された OR ゲートであるのが好ましい。

#### 【0014】

また、本発明は、データを転送するためのシリアルデータラインおよび前記データを保持するクロック信号を転送するためのシリアルクロックラインを介して少なくとも 1 つのマスタデバイスと接続されるスレーブデバイスであって、

前記マスタデバイスと前記シリアルデータラインを介してデータ通信を行う手段と、

前記マスタデバイスから前記シリアルデータラインを介して転送されるアドレス情報と自分自身に固有の固有アドレスとを比較する手段と、

前記マスタデバイスから前記シリアルデータラインを介して転送されるアドレス情報と他のスレーブデバイスとの共通の共有アドレスとを比較する手段と、

前記マスタデバイスから転送されたアドレス情報が前記固有アドレスであると認識したときに第 1 の端子からアクノリッジ信号を出力する手段と、

前記マスタデバイスから転送されたアドレス情報が前記共有アドレスであると認識したときに前記第 1 の端子とは異なる第 2 の端子からアクノリッジ信号を出力する手段とを有することを特徴とするスレーブデバイスを提供する。

ここで、さらに、セレクト信号の状態に応じて、前記マスタデバイスから送信される前記データがいずれかに保持される第 1 および第 2 のレジスタを有し、

前記第 1 のレジスタの出力は、当該スレーブデバイスに接続される装置に対して直接接続され、前記第 2 のレジスタの出力は、I/O ポートを介して、当該スレーブデバイスに接続される装置に双方向に接続されているのが好ましい。

#### 【0015】

##### 【発明の実施の形態】

以下に、添付の図面に示す好適実施例に基づいて、本発明のシリアルデータ転送装置を詳細に説明する。

#### 【0016】

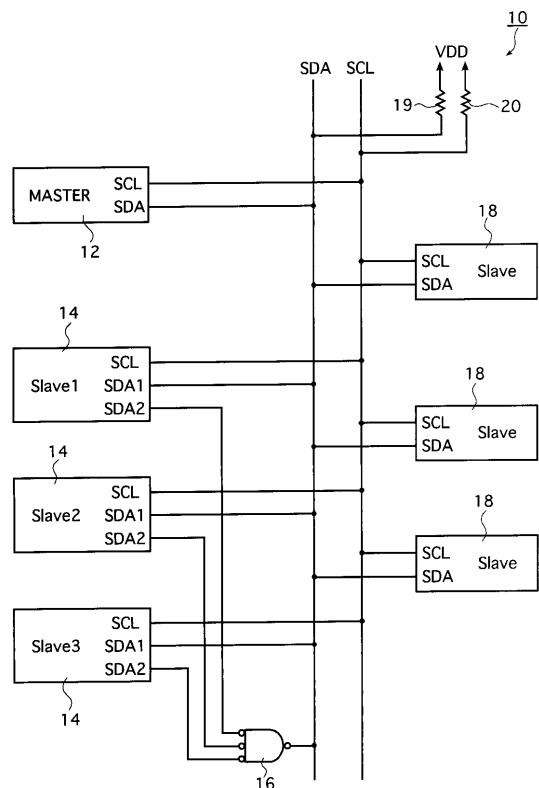

図 1 は、本発明のシリアルデータ転送装置の一実施例のシステム構成図である。同図に示すシリアルデータ転送装置 10 は、マスタデバイス (MASTER) 12 と、本発明を適用するスレーブデバイス (Slave 1 ~ 3) 14 および OR ゲート 16 と、従来構成のスレーブデバイス (Slave) 18 と、プルアップ抵抗 19, 20 と、シリアルデータライン SDA およびシリアルクロックライン SCL を有する。

#### 【0017】

ここで、シリアルデータライン SDA はデータ（制御信号を含む）を転送するためのライン、シリアルクロックライン SCL は、データを保持するクロック信号を供給するためのラインであって、それぞれプルアップ抵抗 19 および 20 を介して電源 VDD に接続されている。マスタデバイス 12 はスレーブデバイス 14 を制御する側のデバイスで、その SCL 端子および SDA 端子は、各々シリアルクロックライン SCL およびシリアルデータ

10

20

30

40

50

ラインに接続されている。

【0018】

続いて、スレーブデバイス14は、マスタデバイス12により制御される側のデバイスであって、そのSCL端子およびSDA1端子は、各々シリアルクロックラインSCLおよびシリアルデータラインSDAに接続され、そのSDA2端子はいずれもORゲート16に入力されている。また、ORゲート16の出力は、オープンドレインまたはオープンコレクタの出力であって、シリアルデータラインSDAに接続されている。

【0019】

同じく、スレーブデバイス18は、マスタデバイス12により制御される側のデバイスで、そのSCL端子およびSDA端子は、各々シリアルクロックラインSCLおよびシリアルデータラインに接続されている。なお、スレーブデバイス14およびORゲート16を除く、マスタデバイス12、スレーブデバイス18、プルアップ抵抗19，20、シリアルデータラインSDAおよびシリアルクロックラインSCLは従来公知の構成のものである。

10

【0020】

本発明のシリアルデータ転送装置10では、シリアルデータラインSDAおよびシリアルクロックラインSCLを介して、マスタデバイス12と複数のスレーブデバイス14，18との間でシリアルにデータの転送が行われる。詳細は後述するが、マスタデバイス12とスレーブデバイス14，18との間で1対1にデータを転送する他、マスタデバイス12から複数のスレーブデバイス14に対して同時にデータを送信することも可能である。

20

【0021】

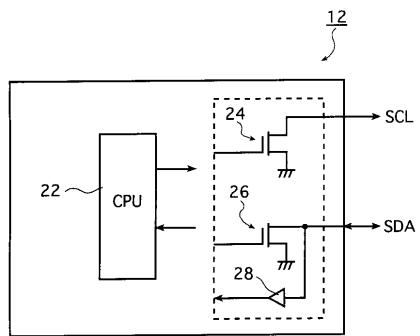

続いて、図2に、マスタデバイスの一実施例の構成概略図を示す。

同図に概念的に示すように、マスタデバイス12は、マイクロコントローラ(CPU)22と、シリアルクロックラインSCLを駆動するオープンドレインタイプのN型MOSトランジスタ(以下、NMOSという)からなる出力バッファ24、および、シリアルデータラインSDAを駆動するオープンドレインタイプのNMOSからなる入出力バッファ26とを有する。

20

【0022】

マスタデバイス12では、マイクロコントローラ22が、あらかじめ設計されているプログラムに応じて全体の動作を制御する。そして、出力バッファ24により、シリアルクロックラインSCL上にクロック信号を出力したり、入出力バッファ26により、シリアルデータラインSDA上に転送すべきデータを出力する、あるいは、シリアルデータラインSDA上に出力されている受信すべきデータを、入力バッファ28を介して取り込む。

30

【0023】

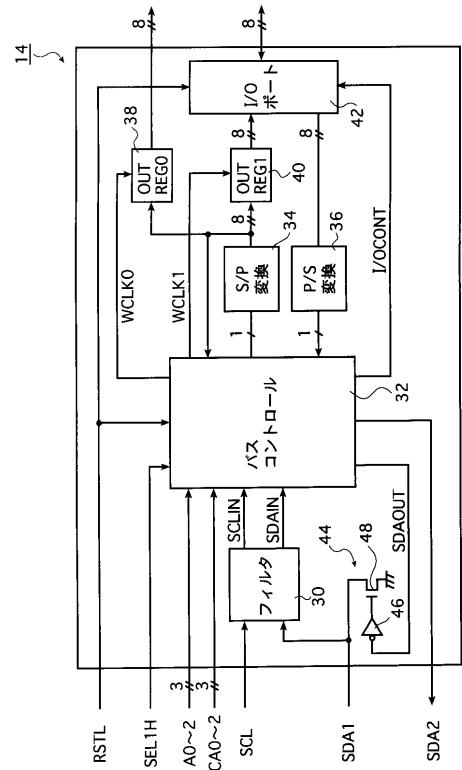

続いて、図3に、スレーブデバイスの一実施例のロック構成図を示す。

スレーブデバイス14は本発明に特有の回路構成を有するもので、同図に示すように、フィルタ30と、バスコントロール回路32と、S/P(シリアル/パラレル)変換回路34と、P/S(パラレル/シリアル)変換回路36と、出力レジスタ38(OUTREG0), 40(OUTREG1)と、I/O(入力/出力)ポート42と、入出力(の出力部)バッファ44とを有する。

40

【0024】

スレーブデバイス14において、まず、フィルタ30には、シリアルクロックライン上に出力されるシリアルクロック信号SCL、および、シリアルデータライン上に出力されるシリアルデータ信号SDA1が入力される。これらの信号SCLおよびSDA1はフィルタ30によってノイズを除去され、それぞれシリアルクロック入力信号SCLINおよびシリアルデータ入力信号SDAINとしてフィルタ30から出力される。

【0025】

フィルタ30から出力されるシリアルクロック入力信号SCLINおよびシリアルデータ入力信号SDAINは、バスコントロール回路32に入力される。この他、バスコントロール回路32には、リセット信号RSTL、セレクト信号SEL1H、固有アドレス信号

50

A 0 ~ 2、共有アドレス信号 C A 0 ~ 2、S / P 変換回路 3 4 から出力されるパラレルデータ、および、P / S 変換回路 3 6 から出力されるシリアルデータが入力される。

#### 【0026】

ここで、リセット信号 R S T L は、このスレーブデバイス 1 4 をリセットして初期化するもので、例えばローレベルの時に、スレーブデバイス 1 4 はリセットされる。セレクト信号 S E L 1 H は、S / P 変換後のパラレルデータ（S / P 変換出力）を出力レジスタ 3 8 または 4 0 のどちらに保持するのかを指定する信号で、S / P 変換後のパラレルデータは、例えばセレクト信号 S E L 1 H がハイレベルの時に出力レジスタ 4 0 に保持される。

#### 【0027】

本発明のシリアルデータ転送装置 1 0 では、マスタデバイス 1 2 からスレーブデバイス 1 4 , 1 8 に対して、所望のスレーブデバイス 1 4 , 1 8 を指定するために、例えば 7 ビットのアドレス情報が送信される。固有アドレス信号 A 0 ~ 2 は、各々のスレーブデバイス 1 4 に独自の固有アドレスを設定するための信号であり、共有アドレス信号 C A 0 ~ 2 は、あらかじめ設定されている複数のスレーブデバイス 1 4 に共通の共有アドレスを設定するための信号である。

#### 【0028】

バスコントロール回路 3 2 は、このスレーブデバイス 1 4 全体の動作を制御する。バスコントロール回路 3 2 からは、フィルタ 3 0 から入力されるシリアルデータ入力信号 S D A I N をシリアルクロック入力信号 S C L I N で順次保持して得られるシリアルデータの他、ライトクロック信号 W C L K 0 , 1 、I / O コントロール信号 I / O C O N T 、シリアルデータ出力 S D A O U T 、および、シリアルデータ出力 S D A 2 が出力される。

#### 【0029】

ここで、ライトクロック信号 W C L K 0 , 1 は、前述のセレクト信号 S E L 1 H の状態に応じて、S / P 変換回路 3 4 から出力される S / P 変換後のパラレルデータを各々出力レジスタ 3 8 および 4 0 に保持するためのクロック信号である。例えば、セレクト信号 S E L 1 H がローレベルの時にはライトクロック信号 W C L K 0 が出力され、セレクト信号 S E L 1 H がハイレベルの時にはライトクロック信号 W C L K 1 が出力される。

#### 【0030】

本発明のシリアルデータ転送装置 1 0 では、前述のアドレス情報に続き、スレーブデバイスへのデータライト、または、スレーブデバイスからのデータリードを指示する 1 ビットのデータ制御信号が送信される。I / O コントロール信号 I / O C O N T は、このデータ制御信号の状態に応じて、スレーブデバイス 1 4 と、このスレーブデバイス 1 4 に接続される装置（以下、接続装置という）との間で、パラレルデータの入出力方向を切り替えるための信号である。

#### 【0031】

データ制御信号がローレベルの時には、マスタデバイス 1 2 からスレーブデバイス 1 4 , 1 8 へのデータライトを意味し、マスタデバイス 1 2 からスレーブデバイス 1 4 , 1 8 を介して接続装置にデータが送信される。一方、データ制御信号がハイレベルの時には、スレーブデバイス 1 4 , 1 8 からマスタデバイス 1 2 へのデータリードを意味し、接続装置側からスレーブデバイス 1 4 , 1 8 を介してマスタデバイス 1 2 にデータが受信される。

#### 【0032】

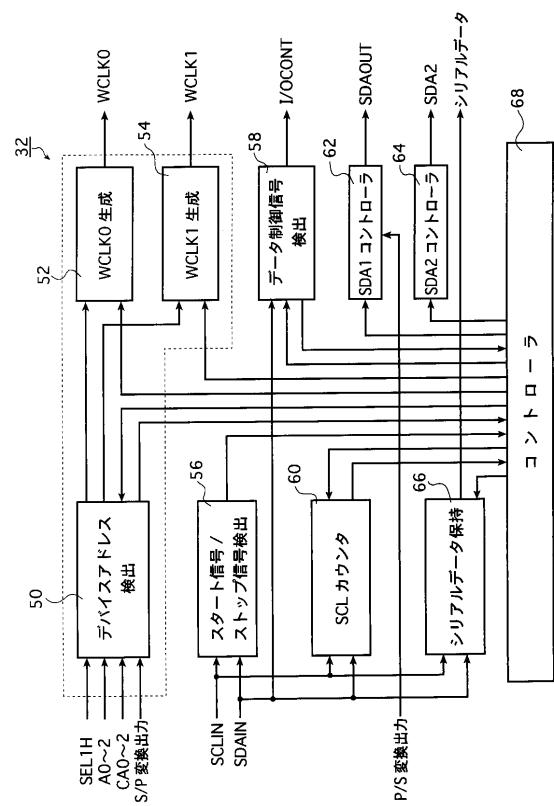

続いて、図 4 に、バスコントロール回路の一実施例のブロック構成図を示す。バスコントロール回路 3 2 は、デバイスアドレス検出回路 5 0 と、W C L K 0 および 1 生成回路 5 2 , 5 4 と、スタート信号 / ストップ信号検出回路 5 6 と、データ制御信号検出回路 5 8 と、S C L カウンタ 6 0 と、S D A 1 および S D A 2 コントローラ 6 2 および 6 4 と、シリアルデータ保持回路 6 6 と、コントローラ 6 8 とを有する。

#### 【0033】

まず、コントローラ 6 8 は、このバスコントロール回路 3 2 全体の動作を制御するものである。コントローラ 6 8 から出力される各種の制御信号は、スタート信号 / ストップ信号検出回路 5 6 を除く、他のデバイスアドレス検出回路 5 0 、W C L K 0 および 1 生成回路

10

20

30

40

50

52, 54、データ制御信号検出回路58、SCLカウンタ60、SDA1およびSDA2コントローラ62および64、ならびに、シリアルデータ保持回路66に供給される。

#### 【0034】

続いて、スタート信号／ストップ信号検出回路56には、シリアルクロック入力信号SCLINおよびシリアルデータ入力信号SDAINが入力される。スタート信号／ストップ信号検出回路56は、データの転送開始を指示するスタート信号(SART)、および、データの転送終了を指示するストップ信号(STOP)を検出する。スタート信号／ストップ信号検出回路56による検出結果はコントローラ68に入力される。

#### 【0035】

本発明のシリアルデータ転送装置10では、基本的に、シリアルデータ入力信号SDAINは、シリアルクロック入力信号SCLINがローレベルの間に変化する。スタート信号／ストップ信号検出回路56は、シリアルクロック入力信号SCLINがハイレベルの間に、シリアルデータ入力信号SDAINのハイレベルからローレベルへの変化を見てスタート信号を検出し、ローレベルからハイレベルへの変化を見てストップ信号を検出する。

#### 【0036】

続いて、デバイスアドレス検出回路50には、セレクト信号SEL1H、固有アドレス信号A0～2、共有アドレス信号CA0～2、および、S/P変換回路34から供給されるパラレルデータ(S/P変換出力)が入力される。デバイスアドレス検出回路50は、S/P変換出力(アドレス情報)と各々のスレーブデバイス14にあらかじめ設定されている固有アドレス信号A0～2および共有アドレス信号CA0～2とを比較する。

#### 【0037】

デバイスアドレス検出回路50の比較結果は、コントローラ68の他、WCLK0, 1生成回路52, 54にも入力される。WCLK0, 1生成回路52, 54は、デバイスアドレス検出回路50からの比較結果を受け取り、データ制御信号によってマスタデバイス12からスレーブデバイス14へのデータライトが指定されている場合、セレクト信号SEL1Hの状態に応じて、各々前述のライトクロック信号WCLK0, 1を生成する。

#### 【0038】

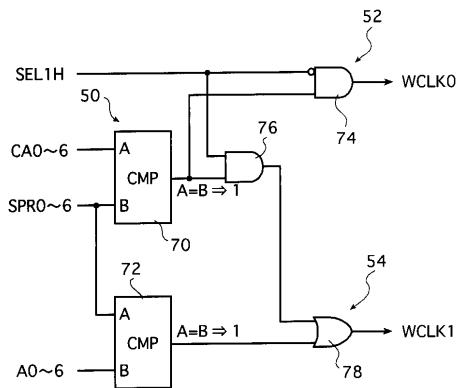

ここで、図5に、デバイスアドレス検出回路およびWCLK生成回路の一実施例の構成回路図を示す。同図は、図4に示すバスコントロール回路32の点線で囲まれている部分に相当するもので、まず、デバイスアドレス検出回路50は、2つのコンパレータ(CMP)70, 72を有する。また、WCLK0生成回路52はANDゲート74を有し、WCLK1生成回路54は、ANDゲート76およびORゲート78を有する。

#### 【0039】

デバイスアドレス検出回路50において、コンパレータ70には、共有アドレス信号CA0～6およびS/P変換出力SPR0～6が入力され、同じく、コンパレータ72には、固有アドレス信号A0～6およびS/P変換出力SPR0～6が入力される。コンパレータ70, 72は各々入力される両方の信号を比較し、その結果、一致が検出されると、コンパレータ70, 72からはハイレベルが出力され、不一致であればローレベルが出力される。

#### 【0040】

なお、固有アドレス信号A0～6、共有アドレス信号CA0～6の内、固有アドレス信号A0～2および共有アドレス信号CA0～2は、図3および図4に示されている信号である。固有アドレス信号A3～6および共有アドレス信号CA3～6は、例えばIICバスの規格との互換性を考慮すれば、「0100」または「0111」の固定値とする必要がある。また、S/P変換出力SPR0～6は、S/P変換後のアドレス情報を表すデータである。

#### 【0041】

コンパレータ70の比較結果は、ANDゲート74, 76の一方の端子に入力され、ANDゲート74, 76の他方の端子にはセレクト信号SEL1Hが入力される。ANDゲート74からはライトクロック信号WCLK0が出力され、ANDゲート76の出力はOR

10

20

30

40

50

ゲート78の一方の端子に入力される。また、コンパレータ72の比較結果はORゲート78の他方の端子に入力され、ORゲート78からはライトクロック信号WCLK1が出力される。

#### 【0042】

すなわち、ライトクロック信号WCLK0は、共有アドレス信号CA0～6とP/S変換出力SPR0～6とが一致し、かつ、セレクト信号SEL1Hがローレベルの時にアクティブ状態であるハイレベルとなる。一方、ライトクロック信号WCLK1は、固有アドレス信号A0～6とS/P変換出力SPR0～6とが一致するか、共有アドレス信号CA0～6とP/S変換出力SPR0～6とが一致し、かつ、セレクト信号SEL1Hがハイレベルの時にハイレベルとなる。

10

#### 【0043】

続いて、データ制御信号検出回路58には、シリアルデータ入力信号SDAINが入力される。データ制御信号検出回路58は、データ制御信号を検出して、マスタデバイス12からスレーブデバイス14, 18へのデータライトであるのか、スレーブデバイス14, 18からマスタデバイス12へのデータリードであるのかを判断して、I/Oコントロール信号I/OCONTを発生する。データのライト/リードの識別結果はコントローラ68にも入力される。

#### 【0044】

SCLカウンタ60には、シリアルクロック入力信号SCLINおよびシリアルデータ入力信号SDAINが入力される。データの送受信は、例えば8ビット(1バイト)を1つの単位として転送される。このため、SCLカウンタ60は、スタート信号を基準として、シリアルクロック入力信号SCLINをカウントすることにより、データの送信および受信のタイミングを調整する。SCLカウンタ60によるカウント結果はコントローラ68に入力される。

20

#### 【0045】

同じく、シリアルデータ保持回路66にも、シリアルクロック入力信号SCLINおよびシリアルデータ入力信号SDAINが入力される。シリアルデータ保持回路66は、シリアルクロック入力信号SCLINに同期して、シリアルデータ入力信号SDAINを順次保持する。シリアルデータ保持回路66に保持されたシリアルデータは、図3に示すように、S/P変換回路34に対して順次出力される。

30

#### 【0046】

SDA1コントローラ62には、P/S変換回路36から供給されるシリアルデータ(P/S変換出力)が入力される。SDA1コントローラ62は、P/S変換回路36からP/S変換出力を受け取り、これをシリアルデータ出力信号SDAOUTとして入出力バッファ44に対して出力する。また、SDA2コントローラ64は、共有アドレスが指定されている場合に、コントローラ68の制御によりアクノリッジ信号を出力する。

#### 【0047】

データライト時には、バスコントロール回路32からシリアルデータが出力され、S/P変換回路34に入力される。S/P変換回路34は、バスコントロール回路32から供給されるシリアルデータを、例えば8ビットのパラレルデータに変換する。S/P変換後のパラレルデータは、出力レジスタ38, 40の他、固有アドレス信号A0～2および共有アドレス信号CA0～2との比較のために、バスコントロール回路32にもフィードバックされる。

40

#### 【0048】

続いて、出力レジスタ38, 40は、各々バスコントロール回路32から入力される前述のライトクロック信号WCLK0, 1により、S/P変換回路34から出力される、例えば8ビットのパラレルデータを保持する。出力レジスタ38に保持されたパラレルデータは、このスレーブデバイス14の接続装置に対して直接出力され、出力レジスタ40から出力されるパラレルデータはI/Oポート42に入力される。

#### 【0049】

50

I/Oポート42と接続装置とは双方向に接続される。このため、出力レジスタ40は、スレーブデバイス14と接続装置との間で相互にデータをやり取りするのに適している。これに対し、出力レジスタ38に保持されるパラレルデータは接続装置に対して直接出力される。したがって、出力レジスタ38は、例えばスタート、ストップ、アポート等の接続装置を制御するための制御信号を保持するのに適しており、これを接続装置に直結して使用することができる。

#### 【0050】

I/Oポート42には、上記パラレルデータの他、リセット信号RSTLや、バスコントロール回路32からのI/Oコントロール信号I/OCONTが入力される。I/Oポート42は、I/Oコントロール信号I/OCONTの状態に応じて、出力レジスタ40から供給されるパラレルデータを接続装置に対して出力するか、あるいは、接続装置から供給されるパラレルデータを、次に述べるP/S変換回路36に対して出力するのかを制御する。

#### 【0051】

前述のように、I/Oポート42と接続装置との間は、8ビットのパラレルバスで双方向に接続される。データリード時に接続装置から供給されるパラレルデータは、I/Oポート42からP/S変換回路36に対して出力される。

P/S変換回路36は、I/Oポート42から供給される8ビットのパラレルデータをシリアルデータに変換する。P/S変換回路36から出力されるシリアルデータは、前出のバスコントロール回路32に入力される。

#### 【0052】

バスコントロール回路32は、P/S変換回路36から供給されるシリアルデータをシリアルデータ出力SDAOUTとして順次出力する。このシリアルデータ出力SDAOUTは、入出力バッファ44のインバータ46を介してNMOS48のゲートに入力される。入出力バッファ44のNMOS48のソースはグランドに接続され、そのドレインは、シリアルデータ信号SDA1としてシリアルデータライン上に出力される。

#### 【0053】

入出力バッファ44からは、シリアルデータ信号SDA1として、バスコントロール回路32から供給されるシリアルデータ出力SDAOUTが順次出力される。なお、アクノリッジ信号は、固有アドレスが指定されて、1つのスレーブデバイス14のみがアクセスされる場合にSDA1端子から出力され、共有アドレスが指定されて、全てのスレーブデバイス14が同時にアクセスされる場合にはSDA2端子から出力される。

#### 【0054】

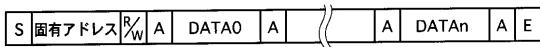

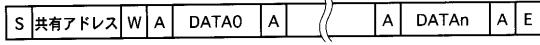

次に、本発明のシリアルデータ転送装置10で使用されるデータ形式について説明する。

#### 【0055】

本発明では、マスタデバイス12は、スタート信号に続くアドレス情報として、固有アドレスまたは共有アドレスのどちらかを選択的に出力可能にプログラムされる。以下の説明では、固有アドレスを使用してスレーブデバイス14または18の中の1つを指定するモードを通常処理モードと呼び、共有アドレスを使用してあらかじめ設定されている複数のスレーブデバイス14を同時に指定するモードをローカルモードと呼ぶことにする。

#### 【0056】

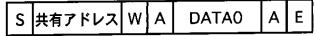

図6は、データ形式の一実施例の概念図である。

通常処理モードの場合には、まず、マスタデバイス12からスタート信号(S)が出力され、続いて、固有アドレス信号およびデータ制御信号(R/W)からなる1バイト目のデータが順次シリアルに出力される。これに対し、固有アドレス信号に一致する固有アドレスが設定されているスレーブデバイス14または18から、アクノリッジ信号(A)が出力される。

#### 【0057】

データ制御信号により、ライト(W)が指定された場合には、マスタデバイス12から、固有アドレス信号に一致する固有アドレスが設定されているスレーブデバイス14または

10

20

30

40

50

18に対してデータ(DATA0~n)が送信される。該当するスレーブデバイス14または18は、マスタデバイス12から送信されてくるデータを順次シリアルに受け取り、例えば8ビット(1バイト)のデータを受信した後、アクノリッジ信号(A)を出力する。

#### 【0058】

一方、リード(R)が指定された場合には、該当するスレーブデバイス14, 18から、マスタデバイス12に対してデータ(DATA0~n)が送信される。マスタデバイスは、スレーブデバイス14または18からの8ビットのデータを順次シリアルに受信する。スレーブデバイス14, 18は、8ビットのデータを送信した後、アクノリッジ信号(A)を出力する。そして、最後に、マスタデバイス12から、ストップ信号(E)が出力される。10

#### 【0059】

これに対して、ローカルモードの時は、まず、セレクト信号SEL1Hがハイレベルの場合、すなわち、出力レジスタ40にデータを書き込む場合、マスタデバイス12からスタート信号(S)が出力され、共有アドレス信号と、マスタデバイス12からスレーブデバイス14, 18へのデータの書き込みを指示するデータ制御信号(W)とからなる1バイト目のデータが出力される。これ以後のデータ形式は、通常処理モードの場合と同じである。

#### 【0060】

また、セレクト信号SEL1Hがローレベルの場合、すなわち、出力レジスタ38にデータを書き込む場合、セレクト信号SEL1Hがハイレベルの場合と同じように、マスタデバイス12からスレーブデバイス14, 18に対して1バイト目のデータが出力され、次いで、1バイトのデータ(DATA0)のみが送信される。その後、スレーブデバイス14, 18からアクノリッジ信号(A)が出力され、マスタデバイス12からストップ信号(E)が出力される。20

#### 【0061】

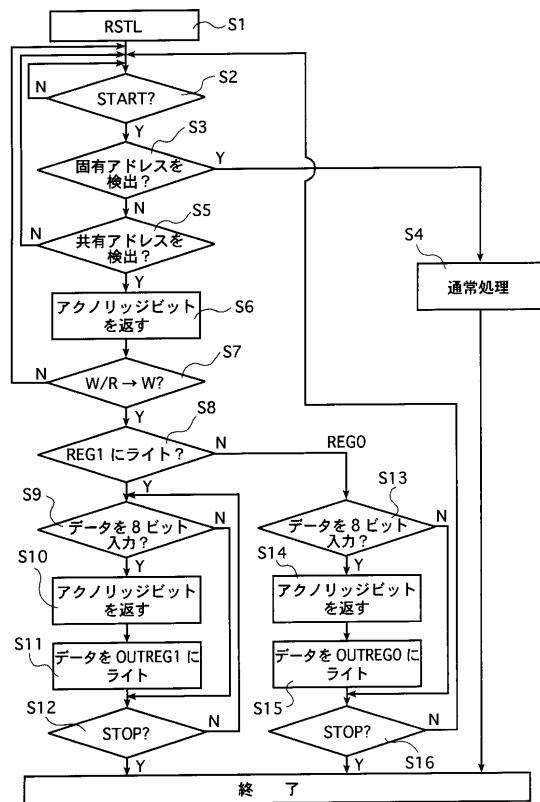

次に、図7に示すフローチャートを参照しながら、本発明のシリアルデータ転送装置の動作について説明する。

#### 【0062】

同図フローチャートのステップS1に示すように、まず、リセット信号RSTLがローレベルとされ、シリアルデータ転送装置10が初期化される。初期化の後、ステップS2へ進み、スレーブデバイス14, 18は、マスタデバイス12からスタート信号(START)が出力されるのを検出する。なお、スレーブデバイス14, 18は、スタート信号が検出されない場合(N)には、スタート信号が検出される(Y)まで繰り返し検出を行う。30

#### 【0063】

スタート信号が検出されると(Y)、全てのスレーブデバイス14, 18は、マスタデバイス12から、アドレス情報およびデータ制御信号からなる1バイト目のデータを受信する。ステップS3に示すように、各々のスレーブデバイス14, 18は、図4に示すSC-Lカウンタ60のタイミング制御により、受信したアドレス情報とあらかじめ設定されている固有アドレスとを比較して、自分自身が指定されているのかどうかを検出する。40

#### 【0064】

その結果、アドレス情報が自分自身の固有アドレスと一致している(Y)スレーブデバイス14または18は、ステップS4に示す通常処理モードに入り、該当するスレーブデバイス14のSDA端子またはスレーブデバイス18のSDA1端子からローレベルのアクノリッジ信号を出力する。以後、図6に示すデータ形式にしたがい、IICバス規格に準拠して、マスタデバイス12とスレーブデバイス14または18との間でデータのやり取りが行われる。

#### 【0065】

一方、マスタデバイス12からのアドレス情報が、自分自身の固有アドレスと一致しない50

場合( N )にはステップ S 5 へ進む。そして、各々のスレーブデバイス 1 4 は、アドレス情報とあらかじめ設定されている共有アドレスとを比較して、アドレス情報が共有アドレスと一致するかどうかを検出する。

この結果、アドレス情報が共有アドレスである場合( Y )には次のステップ S 6 へ進み、共有アドレスでない場合( N )にはステップ S 2 へ戻る。

#### 【 0 0 6 6 】

本実施例では、共有アドレスにより全てのスレーブデバイス 1 4 ( S l a v e 1 ~ 3 ) が指定され、ローカルモードに入る。ステップ S 6 に示すように、全てのスレーブデバイス 1 4 の S D A 2 端子からローレベルのアクノリッジ信号が出力され、図 1 に示す O R ゲート 1 6 に入力され、O R ゲート 1 6 からシリアルデータライン S D A 上にローレベルのアクノリッジ信号が出力される。マスタデバイス 1 2 は、これを受信してローカルモードに入ったことを確認する。10

#### 【 0 0 6 7 】

続いて、ステップ S 7 に進み、全てのスレーブデバイス 1 4 において、図 4 に示す S C L カウンタ 6 0 のタイミング制御により、データ制御信号( R / W )が検出される。ローカルモードの場合には、全てのスレーブデバイス 1 4 が同時にアクセスされるが、マスタデバイス 1 2 は全てのスレーブデバイス 1 4 から同時にデータを受信( リード )することはできないため、データライト( W )ではない場合( N )にはイリガル動作であるとしてステップ S 2 へ戻る。20

#### 【 0 0 6 8 】

一方、データライト( W )である場合( Y )、次のステップ S 8 へ進む。ステップ S 8 では、セレクト信号 S E L 1 H の状態に応じて、2 バイト目のデータを出力レジスタ 3 8 に保持するのか、あるいは、出力レジスタ 4 0 に保持するのかが決定される。そして、2 バイト目のデータを出力レジスタ 3 8 に保持する場合にはステップ S 1 3 へ進み、出力レジスタ 4 0 に保持する場合にはステップ S 9 へ進む。20

#### 【 0 0 6 9 】

ここで、2 バイト目のデータを出力レジスタ 4 0 に保持する場合( Y )、シリアルデータを順次取り込み、ステップ S 9 として、図 4 に示す S C L カウンタ 6 0 の制御により、8 ビット( 1 バイト )のデータを受信したかどうかを検出する。この時、8 ビットのデータ入力がない場合( N )には続くデータは存在せず、送信は終了であるからステップ S 1 2 へ進む。8 ビットのデータ入力がある場合( Y )には次のステップ S 1 0 へ進む。30

#### 【 0 0 7 0 】

ステップ S 1 0 において、全てのスレーブデバイス 1 4 の S D A 2 端子から、ローレベルのアクノリッジ信号が出力され、図 1 に示す O R ゲート 1 6 により、シリアルデータライン S D A 上にローレベルのアクノリッジ信号が出力される。マスタデバイス 1 2 は、シリアルデータライン S D A 上のアクノリッジ信号を検出して、全てのスレーブデバイス 1 4 が2 バイト目のデータを受信したことを確認し、次のデータを送信する。

#### 【 0 0 7 1 】

一方、全てのスレーブデバイス 1 4 では、ステップ S 1 1 に示すように、図 3 に示すバスコントロール回路 3 2 によって発生されるライトクロック W C L K 1 により、P / S 変換回路 3 4 による P / S 変換後のパラレルデータが出力レジスタ 4 0 に保持される。40

#### 【 0 0 7 2 】

そして、ステップ S 1 2 へ進み、全てのスレーブデバイス 1 4 はストップ信号を検出する。スレーブデバイス 1 4 によりストップ信号が検出された場合( Y )、マスタデバイス 1 2 からスレーブデバイス 1 4 へのデータの送信は終了となる。一方、ストップ信号が検出されない場合( N )、マスタデバイス 1 2 からスレーブデバイス 1 4 へ送信されるデータは複数バイトであるから、ステップ S 9 へ戻って次の 8 ビットのデータを繰り返し受信する。

#### 【 0 0 7 3 】

一方、ステップ S 8 において、2 バイト目のデータを出力レジスタ 3 8 に保持する場合( 50 50 )

N)も、出力レジスタ40に保持する場合と同様に動作する。すなわち、ステップS9～S12に対応するステップS13～S16にしたがってデータのやり取りが行われる。本実施例では、送信される制御信号のデータは1バイトであるから、ステップS16で、ストップ信号が検出されない場合(N)にはステップS2へ戻って繰り返し処理を行う。

#### 【0074】

本発明のシリアルデータ転送装置は、基本的に以上のようなものである。

なお、マスタデバイス12は1つ以上何個あってもよいし、スレーブデバイス14は2つ以上の複数個であれば何個であってもよい。また、本発明のシリアルデータ転送装置は、通常処理モードではIICバス規格に準拠しているため、上記実施例にも示すように、本発明を適用するスレーブデバイスと従来構成のスレーブデバイスとを共存させて使用することができる。10

#### 【0075】

上記実施例では、IICバス規格との互換性を考慮して、各信号の極性や転送するデータのビット数、具体的な回路構成等を例示しているが、IICバス規格との互換性が不要であれば、本発明は上記具体例には何ら限定されない。

以上、本発明のシリアルデータ転送装置について詳細に説明したが、本発明は上記実施例に限定されず、本発明の主旨を逸脱しない範囲において、種々の改良や変更をしてよいのはもちろんである。

#### 【0076】

##### 【発明の効果】

以上詳細に説明した様に、本発明のシリアルデータ転送装置は、マスタデバイスからスレーブデバイスに対して、固有アドレスに対応するアドレス情報を送信し、マスタデバイスとアドレス情報に一致する固有アドレスを有するスレーブデバイスとの間で1対1にデータの送受信を行い、これに対して、共有アドレスに対応するアドレス情報を送信し、マスタデバイスからあらかじめ設定されている複数のスレーブデバイスに対して同時にデータを送信するものである。20

したがって、本発明のシリアルデータ転送装置によれば、マスタデバイスとあらかじめ設定されている複数のスレーブデバイスとの間で同じデータを転送したい場合に、これを一度のデータ転送で実現することができる。例えば、従来は7個のスレーブデバイスに同じデータを順次送信していたものが、本発明では1回の送信で済み、6回分の送信時間を削減することができる。また、本発明によれば、接続装置に直接出力されるレジスタを設けることにより、あらかじめ設定されている複数のスレーブデバイスに同時にスタート、ストップ、アボート等の制御信号を送信して、同時に複数の接続装置を制御することができる。例えば、本発明は、あらかじめ指定された複数のRAM(ランダムアクセスメモリ)を同時にクリアするとか、あるいは、VTR(ビデオテープレコーダ)を始めとして、レジスタにあらかじめパラメータを設定しておき、同時にスタートさせるというような制御を要求されるあらゆるシステムに適用可能である。30

##### 【図面の簡単な説明】

【図1】 本発明のシリアルデータ転送装置の一実施例のブロック構成図である。

【図2】 マスタデバイスの一実施例の構成概略図である。40

【図3】 スレーブデバイスの一実施例のブロック構成図である。

【図4】 バスコントロール回路の一実施例のブロック構成図である。

【図5】 デバイスアドレス検出回路およびWCK生成回路の一実施例の構成回路図である。

【図6】 データ形式の一実施例の概念図である。

【図7】 本発明のシリアルデータ転送装置の動作を表す一実施例のフローチャートである。

##### 【符号の説明】

10 シリアルデータ転送装置

12 マスタデバイス

10

20

30

40

50

1 4 , 1 8 スレーブデバイス

1 6 , 7 8 O R ゲート

1 9 , 2 0 プルアップ抵抗

2 2 マイクロコントローラ

2 4 出力バッファ

2 6 , 4 4 入出力バッファ

2 8 入力バッファ

3 0 フィルタ

3 2 バスコントロール回路

3 4 S / P 変換回路

3 6 P / S 変換回路

3 8 , 4 0 出力レジスタ

4 2 I / O ポート

4 6 インバータ

4 8 N型MOSトランジスタ

5 0 デバイスアドレス検出回路

5 2 W C L K 0 生成回路

5 4 W C L K 1 生成回路

5 6 スタート信号 / ストップ信号検出回路

5 8 データ制御信号検出回路

6 0 S C L カウンタ

6 2 S D A 1 コントローラ

6 4 S D A 2 コントローラ

6 6 シリアルデータ保持回路

6 8 コントローラ

7 0 , 7 2 コンパレータ

7 4 , 7 6 A N D ゲート

S D A シリアルデータライン

S C L シリアルクロックライン

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

通常処理モード

ローカルモード

SEL1H=H の時

SEL1H=L の時

---

フロントページの続き

(56)参考文献 特開昭61-73453(JP,A)

特開平10-293746(JP,A)

特開昭61-202266(JP,A)

特開昭62-135038(JP,A)

特開平5-303537(JP,A)

特開平6-53974(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04L 12/40