## (12) NACH DEM VERTRAG ÜBER DIE INTERNATIONALE ZUSAMMENARBEIT AUF DEM GEBIET DES PATENTWESENS (PCT) VERÖFFENTLICHTE INTERNATIONALE ANMELDUNG

(19) Weltorganisation für geistiges Eigentum Internationales Büro

(43) Internationales Veröffentlichungsdatum 19. September 2002 (19.09.2002)

**PCT**

(10) Internationale Veröffentlichungsnummer WO 02/073695 A2

(51) Internationale Patentklassifikation<sup>7</sup>: H01L 27/02

(21) Internationales Aktenzeichen: PCT/DE02/00547

(22) Internationales Anmeldedatum:

15. Februar 2002 (15.02.2002)

(25) Einreichungssprache: Deutsch

(26) Veröffentlichungssprache: Deutsch

Martin-Str. 53, 81669 München (DE).

(30) Angaben zur Priorität:

101 11 462.1 9. März 2001 (09.03.2001) DE

(72) Erfinder; und

(75) Erfinder/Anmelder (nur für US): PETERS, Christian [DE/DE]; Birkhahnweg 4, 85591 Vaterstetten (DE).

(74) Anwalt: EPPING, HERMANN & FISCHER; Ridlerstr. 55, 80339 München (DE).

(81) Bestimmungsstaaten (national): BR, CA, CN, IL, IN, JP, KR, MX, RU, UA, US.

(84) Bestimmungsstaaten (regional): europäisches Patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR).

(71) Anmelder (für alle Bestimmungsstaaten mit Ausnahme von US): INFINEON TECHNOLOGIES AG [DE/DE]; St.- — ohne inte

ohne internationalen Recherchenbericht und erneut zu veröffentlichen nach Erhalt des Berichts

[Fortsetzung auf der nächsten Seite]

**(54) Title:** THYRISTOR CONFIGURATION AND SURGE SUPPRESSOR COMPRISING A THYRISTOR CONFIGURATION OF THIS TYPE

$(\textbf{54) Bezeichnung}: \ \, \textbf{THYRISTORSTRUKTUR UND } \ \, \textbf{ÜBERSPANNUNGSSCHUTZANORDNUNG MIT EINER SOLCHEN } \\ \, \textbf{THYRISTORSTRUKTUR}$

(57) **Abstract:** The invention relates to a thyristor configuration comprising a first connection (1), which is configured as a first region of a first conductivity type. A second region (2) of a second conductivity type adjoins the first region (1). A third region (3) of the first conductivity type, which borders the second region (2), has a common surface with the latter. A second connection (4), configured as a fourth region of the second conductivity type, adjoins the third region. An auxiliary electrode (6, 7) is located on the common surface of the second region (2) and the third region (3), said electrode bordering at least one of the two regions.

(57) Zusammenfassung: Es ist eine Thyristorstruktur mit einem ersten Anschluss (1), der als erstes Gebiet mit einem ersten Leitfähigkeitstyp ausgebildet ist,vorgesehen. Ein zweites Gebiet (2) eines zweiten Leitfähigkeitstyp, grenzt an das erste Gebiet (1). Ein drittens Gebiet (3) vom ersten Leitfähigkeitstyp, das an das zweite Gebiet (2) angrenzt weist mit diesem eine gemeinsame Oberfläche (8) auf. Ein zweiter Anschluss (4), grenzt als viertes Gebiet vom zweiten Leitfähigkeitstyp an das dritte Gebiet an. An der gemeinsamen Oberfläche von dem zweiten Gebiet (2) und dem dritten Gebiet (3) ist zumindest an eines der beiden Gebiete angrenzend eine Hilfs-Elektrode (6, 7) angeordnet.

Zur Erklärung der Zweibuchstaben-Codes und der anderen Abkürzungen wird auf die Erklärungen ("Guidance Notes on Codes and Abbreviations") am Anfang jeder regulären Ausgabe der PCT-Gazette verwiesen.

WO 02/073695 PCT/DE02/00547

1

Beschreibung

(54) Bezeichnung: THYRISTORSTRUKTUR UND ÜBERSPANNUNGSSCHUTZANORDNUNG MIT EINER SOLCHEN THYRISTORSTRUKTUR

Thyristorstruktur und Überspannungsschutzanordnung mit einer solchen Thyristorstruktur

5

Die Erfindung betrifft eine Thyristorstruktur und eine Überspannungsschutzanordnung gemäß der Patentansprüche 1 und 4.

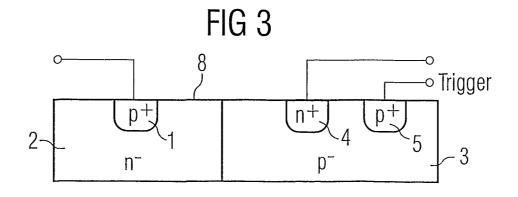

Heutzutage sind bei Verwendung von CMOS-Technologien Thyri-10 storstrukturen üblich, die eine planare Strukur aufweisen. Eine derartige Thyristorstruktur ist prinzipiell in Fig. 3. An der Oberfläche eines solchen Bauelementes sind nebeneinanderliegend ein n-Gebiet 2 und ein p-Gebiet 3 angeordnet, die die auch so genannten Basisgebiete der Thyristorstruktur bilden. Im n-Gebiet 2 ist ein p+-Gebiet 1 ausgebildet, das 15 den Anodenanschluß darstellt. Den Kathodenanschluß stellt ein im p-Gebiet 3 ausgebildetes n+Gebiet 4 dar. Den Steueranschluß wiederum bildet ein im p-Gebiet 3 ausgebildetes p+-Gebiet 5.

20

25

30

35

Bei der Herstellung der zuvor beschriebenen Struktur wird an der Oberfläche 8 ein Nitridschicht aufgetragen. Ladungen in dieser Nitridschicht führen zu einem parasitären Feldeffekt. Der gleiche parasitäre Effekt tritt auf, wenn an der Oberfläche 8 Verunreinigungen in den Gebieten 2 und 3 bei der Herstellung eingebaut werden.

Besonders häufig findet die zuvor beschriebene Thyristorstrukt ihre Anwendung in Überspannungsschutzanordnungen einem so genannten ESD-Schutz. Dieser findet häufig bei MOS-Eingangsstufen von integrierten Schaltungen Anwendung. Am zu schützenden Teil der integrierten Schaltung wird ein Überspannungsdetektor angeordnet, der mit dem Steueranschluß des Thyristors verbunden ist. Eine derartige Anordnung ist in US 4,896,243 beschrieben.

WO 02/073695 PCT/DE02/00547

2

Anode und Kathode des Thyristors sind wiederum mit der Versorgungspannung des zu schützenden Bauelementes verbunden, wenn die Versorgungspannung überwacht werden soll.

5 Tritt nunmehr eine Überspannung auf, so wird der Thyristor über den Steueranschluß eingeschaltet und die Überspannung abgeleitet.

Ist nunmehr der parasitäre Feldeffekttransistor, wie zuvor 10 beschrieben ausgebildet, so wird die überwachte Spannung kurzgeschlossen, was zum Gesamtausfall des zu schützenden Bauelementes führt.

Aus der US 5,907,462 und der US 5,465,189 sind ESD-Strukturen 15 bekannt, die mittels einer Feldeffektstruktur gesteuert werden.

Der Erfindung liegt die Aufgabe zugrunde eine Thyristorstruktur bzw. eine Überspannungsschutzanordnung mit einer derartigen Thyristorstruktur derart weiterzubilden, daß der Einfluß parasitärer Effekte vermieden wird.

20

25

30

35

Diese Aufgabe wird erfindunggemäß mit den in den nebengeordneten Patentansprüchen angegebenen Maßnahmen gelöst.

Durch das Ausbilden zumindest einer Hilfs-Elektrode an der Oberfläche einer der beiden Gebiete des zweiten und dritten Gebietes, ist es möglich, die Oberfläche im Bereich der Hilfs-Elektrode in einen vorbestimmten Ladungszustand zu versetzen.

Eine Überspannungsschutzanordnung mit einer derartigen Thyristorstruktur führt nicht zum Ausfall des zu schützenden Bauteils durch parasitäre Effekte.

Weitere vorteilhafte Ausgestaltungen der Erfindung sind in den untergeordneten Ansprüchen angegeben.

Durch das vorsehen jeweils einer Hilfs-Elektrode auf dem zweiten und dritten Gebiet und dem Verbinden der Hilfs-Elektroden auf dem zweiten Gebiet mit dem ersten Anschluß und der Hilfs-Elektrode am dritten Gebiet mit dem zweiten Anschluß, können auf einfache Weise an der Oberfläche die vorgegebenen Ladungszustände erzeugt werden.

Durch das Ausbilden der Hilfs-Elektrode mit Polysilizium und einem dieses von dem zweiten und dritten Gebiet trennenden Gateoxids, ist die Hilfs-Elektrode in einer üblichen Technologie einfach herstellbar.

Durch das integrieren der Überspannungsschutzanordnung auf einem Halbleiterschip ist der Überspannungsschutz einfach und wirkungsvoll herstellbar.

Nachfolgend wird die Erfindung unter Bezugnahme auf die Zeichnung an Hand von Ausführungsbeispielen erläutert.

20

30

## Es zeigen:

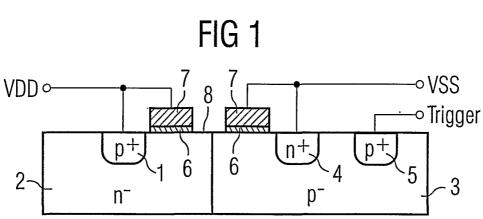

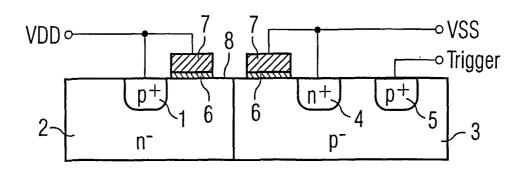

Fig. 1 eine erfindungsgemäße Thyristorstruktur,

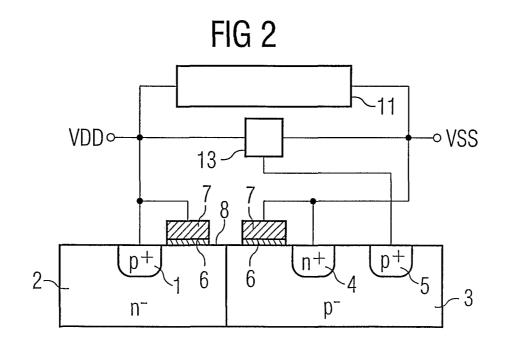

Fig. 2 eine erfindungsgemäße Überspannungsschutzanordnung in prizipieller Darstellung, und

25 Fig. 3 eine übliche Thyristorstrukur.

Fig. 1 zeigt ein erfindungsgemäßes Ausführungsbeispiel einer Thyristorstruktur, die grundsätzlich der entspricht, die unter Bezugnahme auf Fig. 3 bereits in der Beschreibungseinleitung erläutert wurde. Gleiche Teile sind dabei mit gleichen Bezugszeichen versehen.

Zusätzlich ist bei dem dargestellten Ausführaungsbeispiel an der gemeinsamen Oberfläche vom zweiten Gebiet 2 und dritten

35 Gebiet 3, die häufig auch als Basisgebiete des Thyristors bezeichnet sind, voneinander getrennte Hilfs-Elektroden ausgebildet. Diese Hilfs-Elektroden setzen sich aus einem für die

WO 02/073695

PCT/DE02/00547

4

Herstellung von Feldeffektransistoren üblichen Gateoxid 6 und einem Elektrodenkontakt 7 aus Polysilizium zusammen. Der Elektrodenkontakt 7 der Hilfs-Elektrode, die an der Oberfläche des zweiten Gebietes 2 ausgebildet ist, ist elektrisch leitend mit dem ersten Anschluß 1, dem Anodenkontakt verbunden. Die Hilfs-Elektrode, die an dem dritten Gebiet 3 ausgebildet ist, ist mit dem zweiten Anschluß, dem Kathodenkontakt elektrisch leitend verbunden. Auf diese Weise ist sichergestellt, daß sich an der Oberfläche in den Basisgebieten durch parasitäre Effekte kein leitender Kanal ausbilden kann, der einen Kurzschluß zwischen erstem Anschluß 1 und zweitem Anschluß 3 bewirken würde. Eine Aufsteuerung der Thyristorstruktur erfolgt nur durch das Einprägen eines Stroms am Steueranschluß 5.

15

20

25

10

5

Fig. 3 zeigt in prizipieller Darstellung die Thyristorstruktur in einer Überspannungsanordnung. Die zuvor beschriebene Thyristorstruktur ist mit ihrem Anoden- bzw. Kathodenanschluß, d.h. mit dem ersten Anschluß 1 und dem zweiten Anschluß 3, mit der Versorgungspannung VDD und VSS des zu schützenden Bauelements 11 verbunden. Eine Überspannungsdetektoreinrichtung 13 überwacht einen die Versorgungsspannung des zu schützenden Bauelements 11. Beim Auftreten einer Überspannung prägt die Überspannungsdetektoreinrichtung 13 einen Strom über den Steueranschluß 5 in ein Basisgebiet, nämlich dem dritten Gebiet 3, der Thyristorstruktur ein. Diese zündet und schließt die Versorgungsspannung kurz.

Die Anordnung ist besonders für eine Integration geeignet.

30 Dies bedeutet, die Thyristorstruktur wird zusammen mit dem Überspannungsdetektor an der Oberfläche des zu schützenden Bauelements integriert, wobei durch die beiden Hilfs-Elektroden vermieden wird, daß die Thyristorstruktur unter einem Dickoxid angeordnet wird, um parasitäre Effekte zu verständig erhalten.

WO 02/073695 PCT/DE02/00547

Weiterhin ist eine solche Anordnung auf andere Spannungsüberwachungen, wie die Spannung von Signaleingängen anwendbar.

25

## Patentansprüche

- 1. Thyristorstruktur mit

- einem ersten Anschluß (1), der als erstes Gebiet mit einem ersten Leitfähigkeitstyp ausgebildet ist,

- einem zweiten Gebiet (2) eines zweiten Leitfähigkeitstyp, das an das erste Gebiet (1) angrenzt,

- einem dritten Gebiet (3) vom ersten Leitfähigkeitstyp, das 10 an das zweite Gebiet (2) angrenzt und mit diesem eine gemeinsame Oberfläche (8) aufweist, und

- einem zweiten Anschluß (4), das als viertes Gebiet vom zweiten Leitfähigkeitstyp an das dritte Gebiet angrenzt,

- daß an der gemeinsamen Oberfläche von dem zweiten Gebiet

(2) und dem dritten Gebiet (3) zumindest an eines der beiden Gebiete angrenzend eine Hilfs-Elektrode (6, 7) angeordnet ist, dadurch gekennzeichnet, daß an das zweite Gebiet (2) und an das dritte Gebiet (3) angrenzend auf der gemeinsamen Oberfläche (8) von zweitem Gebiet (2) und drittem Gebiet (3) jeweils eine Hilfs-Elektrode (6, 7) angeordnet ist.

- 2. Thyristorstruktur nach Anspruch 1, dadurch gekennzeichnet, daß die Hilfs-Elektrode (6, 7) aus einem leitfähigen Bereich (7) aus Polysilizium und einem den leitfähigen Bereich (7) von der gemeinsamen Oberfläche (8) isolierenden Hilfs-Oxid gebildet ist.

- 3.Überspannungsschutzanordnung mit einer Thyristorstruktur

nach einem der Ansprüche 1 oder 3, bei der ein zu schützendes

Bauelement (5) zwischen dem erste Anschluß (1) und dem zweiten Anschluß (4) elektrisch leitend angeordnet ist und das

zweite oder dritte Gebiet (3) einen Steueranschluß (5) aufweist, an dem ein Überspannungsdetektor angeschlossen ist,

der eine Überspannung an dem zu schützenden Bauelement erfaßt.

5

10

WO 02/073695 PCT/DE02/00547 7

4. Überspannungsschutzanordnung nach Anspruch 3, dadurch gekennzeichnet, daß der Steueranschluß (5) ein Gebiet vom gleichen Leitfähigkeitstyp wie das Gebiet, an dem es angeordnet ist, ist und eine höhere Leitfähigkeit als dieses aufweist.

- 5. Überspannungsschutzanordnug nach Anspruch 3 oder 4, dadurch gekennzeichnet, daß an den ersten Anschluß (1) und den zweiten Anschluß (4) die Versorgungsspannung (VDD, VSS) des zu schützenden Bauelements angeschlossen ist.

- 6. Überspannungsschutzanordnung nach Anspruch 3, 4 oder 5, dadurch gekennzeichnet, daß die Überspannungsschutzanordnung integriert auf einem einzigen Halbleiterchip angeordnet 15 ist.

WO 02/073695 PCT/DE02/00547