# US005283386A

# United States Patent 1191

Patent Number: [11]

5,283,386

Akutsu et al.

Date of Patent:

Feb. 1, 1994

| [24] | APPARATUS AND MUSICAL-TONE CONTROLLING APPARATUS INCLUDING DELAY MEANS AND AUTOMATIC RESET MEANS |                                                                                                                         |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [75] | Inventors:                                                                                       | Takashi Akutsu, Akishima; Teruo<br>Jinbo; Hitoshi Kato, both of Fussa;<br>Naoaki Itoh, Higashimurayama, all<br>of Japan |  |  |  |  |  |

| [73] | Assignee:                                                                                        | Casio Computer Co., Ltd., Tokyo,                                                                                        |  |  |  |  |  |

|       | Computer | Co., | Ltd., | Tokyo, |

|-------|----------|------|-------|--------|

| Japan |          |      |       |        |

[21] Appl. No.: 934,101

Filed: Aug. 21, 1992

| [30]     | Foreign Application Priority Data |      |       |                                         |          |  |  |  |  |

|----------|-----------------------------------|------|-------|-----------------------------------------|----------|--|--|--|--|

| Aug. 30, | 1991                              | [JP] | Japan |                                         | 3-220704 |  |  |  |  |

| Aug. 30, | 1991                              | [JP] | Japan | *************************************** | 3-220705 |  |  |  |  |

| Aug. 30, | 1991                              | [JP] | Japan |                                         | 3-220706 |  |  |  |  |

| A 0      | 1002                              | ITDI | Inna  |                                         | 4 07303  |  |  |  |  |

| [JP] Japan 4-8             | 7282 |

|----------------------------|------|

| <b>G10H 1/057</b> ; G10H 7 | 663; |

|                            |      |

[58] Field of Search ...... 84/602-614, 84/627, 663, 634-638, DIG. 1, DIG. 27; 381/1-28

### [56] References Cited

### U.S. PATENT DOCUMENTS

5,138,925 8/1992 Koguchi et al. ...... 84/609

### FOREIGN PATENT DOCUMENTS

```

2-179692 7/1990 Japan .

7/1990 Japan .

2-179693

2-179694 7/1990 Japan .

2-179695 7/1990 Japan .

2-179696 7/1990 Japan .

7/1990 Japan .

2-179697

2-179698

7/1990 Japan.

4-58291 2/1992 Japan.

```

| 4-58292               | 2/1992 | Japan . |

|-----------------------|--------|---------|

| 4-58293               | 2/1992 | Japan . |

| 4-58294               | 2/1992 | Japan . |

| 4-60595               | 2/1992 | Japan . |

| 4-60596               | 2/1992 | Japan . |

| 4-60696               | 2/1992 | Japan . |

| 4-60697               | 2/1992 | Japan . |

| 4-60698               | 2/1992 | Japan . |

| 4-60722               | 2/1992 | Japan . |

| 4-60723               | 2/1992 | Japan . |

| 4-60724               | 2/1992 | Japan . |

| 4-60725               | 2/1992 | Japan . |

| 4-60744               | 2/1992 | Japan . |

| 4-60746               | 2/1992 | Japan . |

| 4-60749               | 2/1992 | Japan . |

| 4-61097               | 2/1992 | Japan . |

| 4-62595               | 2/1992 | Japan . |

| l-13 <del>6</del> 994 | 5/1992 | Japan . |

| 4-93894               | 8/1992 | Japan . |

|                       |        |         |

Primary Examiner—Stanley J. Witkowski Attorney, Agent, or Firm-Frishauf, Holtz, Goodman & Woodward

### [57] **ABSTRACT**

A musical-tone signal controlling apparatus includes a processor which executes a musical-tone controlling process on an input musical-tone signal supplied to the processor, the processor including a delay unit which executes a delay process on the input musical-tone signal; a first discriminator which determines whether or not the input musical-tone signal to be supplied to the processor has become null; a second discriminator which determines whether or not the output musicaltone signal processed by the processor has become null; and a reset circuit which automatically resets the delay unit when the second discriminator determines that the musical-tone signal processed by the processor has become null after the first discriminator determines that the input musical-tone signal to be supplied to the processor has become null.

17 Claims, 31 Drawing Sheets

FIG.2

FIG.3

FIG.5

FIG.6

| ch1                                                                   |   | ch8 |

|-----------------------------------------------------------------------|---|-----|

| Af: DECIMAL PORTION OF<br>CURRENT ADDRESS                             |   |     |

| Ai : INTEGER PORTION OF<br>CURRENT ADDRESS                            |   |     |

| Pf : DECIMAL PORTION OF PITCH DATA                                    |   |     |

| PI : INTEGER PORTION OF PITCH DATA                                    |   |     |

| OLD AI: INTEGER PORTION OF CURRENT ADDRESS BEFORE CHANGE              |   | ·   |

| AI : LOOP START ADDRESS                                               |   |     |

| Ae: LOOP END ADDRESS                                                  |   |     |

| Xp : PREVIOUS SAMPLE VALUE                                            |   |     |

| Xpi : SAMPLE VALUE OF AI                                              | ] |     |

| D : DIFFERENCE VALUE OF<br>SAMPLE VALUES                              |   |     |

| BK : WITHIN-BLOCK COUNTER                                             |   |     |

| ADR : CURRENT ADDRESS OF QUANTIZED VALUE                              |   |     |

| AX : ACCUMULATED DATA                                                 |   |     |

| Δxt : Δx TIMER VALUE                                                  |   |     |

| Δy: ACCUMULATED ENVELOPE VALUE WITH FLAG FOR ADDER/SUBTRACT OPERATION |   |     |

| OE : TARGET ENVELOPE                                                  | 1 |     |

| E : CURRENT ENVELOPE                                                  | 1 |     |

| O : OUTPUT                                                            |   |     |

FIG.7

B : ACCUMULATING BUFFER

FIG.8

FIG.9

**FIG.10**

**FIG.12**

**FIG.14**

**FIG.15**

**FIG.16**

**FIG.20**

5,283,386

FIG.21

FIG. 22

FIG.26

**FIG.27**

|                                         | 1      | 1           | - 1       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        | <del></del> T | T           | —-т        |                                                                           |                 | —т         | _         |

|-----------------------------------------|--------|-------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-------------|------------|---------------------------------------------------------------------------|-----------------|------------|-----------|

| NSSUB<br>(SUBTRAC-<br>TION)             | 0      | 1           | 0         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0      | -             | 0           | 0          | 0                                                                         | 0               | 0          | 0         |

| ZNSB<br>(B 0)                           | 1      | <b> </b>    | 0         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0      | 0             | 0           | 0          | <del>-</del>                                                              | 0               | -          | 0         |

| ZNSA<br>(A — 0)                         | 0      | l           | 0         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1      | 0             | 0           | 1          | 0                                                                         | 0               | 0          | 0         |

| FAS-B<br>INPUT<br>GATE<br>CLOCK         | 1      | -           | SIG1GT    | SIG1GT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SIGIGT | Z2GT          | Z12GT       | Z11GT      | <b>l</b>                                                                  | DEFGT           | 1          | TM2BGT    |

| FAS-A<br>INPUT<br>GATE<br>CLOCK         | SIGGT  | 1           | DZGT      | SIGGT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1      | TM2AGT        | TM2AGT      |            | TM2AGT                                                                    | TM1GT           | TM1GT      | DZGT      |

| LATCH                                   | SIG1CK | SIGCK       | TM2CK     | DEFCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TM1CK  | TM2CK         | TM2CK       | Z2CK       | DACK<br>Z1CK                                                              | TM1CK<br>DZCK   | TM2CK      | TM2CK     |

| COUNTER<br>LATCH<br>(4MSB)<br>(4LSB)(H) | 0.2    | 0 3         | 0.4       | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90     | 8             | 6 —         | <b>A</b> — | <b>B</b>                                                                  | ၁<br>           | <b>Q</b> — | - E       |

| FUNCTION                                | Σ-1-Σ  | INPUT LATCH | T2 2-1+Dz | <u>\(\lambda\)</u> \(\lambda\) \(\l | T1-2-1 | T2 - T2-Z-2   | T2 T2+2×Z-1 | Z-2 - Z-1  | 16 MORE<br>SIGNIFICANT<br>0 — BITS<br>Z-1 — 3 LESS<br>SIGNIFICANT<br>BITS | T1 4<br>T1+ Δ/4 | T2 T1      | T2 T2+ Dz |

| PROCESS                                 | -      | 8           | က         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22     | 9             | 7           | 80         | <b>o</b>                                                                  | 10              |            | 12        |

# FIG. 29

### MUSICAL-TONE SIGNAL GENERATING APPARATUS AND MUSICAL-TONE CONTROLLING APPARATUS INCLUDING DELAY MEANS AND AUTOMATIC RESET **MEANS**

### BACKGROUND OF THE INVENTION

The present invention relates to a musical-tone signal generating apparatus having a general purpose proces- 10 sor and a processing circuit externally connected therewith, both of which cooperate with each other to perform a process for generating a musical-tone signal and a process for controlling the generated musical-tone

Further, the present invention relates to a musicaltone controlling apparatus which performs on a generated musical-tone signal a musical-tone controlling process including a delay process such as a noise shaping process.

In a conventionally proposed technique, a general purpose processor is employed for generating a musical-tone signal through a software process. A musicaltone signal generating apparatus using the general purpose processor is capable of performing a wider variety 25 of sound-source processes than that employing LSI designed for a special purpose of generating musicaltone signals, and further a reduction in manufacturing costs of the former apparatus can be expected.

The musical-tone signal generating apparatus em- 30 ploying the general purpose processor processes operations of various function keys as keyboard keys and tone-color keys through a general program routine, and generates musical-tone sample data at respective sampling timings through interrupt processes based on 35 timer interrupts caused at predetermined intervals.

The musical-tone signal generating apparatus employing the general purpose processor, however, needs a longer time for executing an arithmetic operation compared with the apparatus employing a special LSI. 40 Accordingly, the musical-tone signal generating apparatus employing only the general purpose processor is not suitable for executing musical-tone control processes which include a rapid arithmetic operation such as an over sampling process, a noise shaping process and 45 tone signal at the present sample timing is held in the

To overcome the above drawbacks, the general purpose processor is provided with an independent processing circuit externally connected therewith for executing the above musical-tone control processes.

In the apparatus including the externally connected processing circuit in addition to the general purpose processor, when the general purpose processor generates musical-tone sample data through an interrupt service executed at predetermined intervals, a time re- 55 quired for performing a sound-source process to generate the musical-tone sample data at respective timings varies depending on how a program is executed. As a result, the musical-tone sample data are not precisely generated at even intervals. Therefore, timings at which 60 in the buffer circuit. respective musical-tone sample data are generated from the general purpose processor are shifted from timings at which the processing circuit executes the musicaltone controlling process on the respective musical-tone sample data. As described above, the apparatus including 65 tus having a general purpose processor and a processing the externally connected processing circuit in addition to the general purpose processor has a drawback that allows the musical-tone controlling process to be exe-

cuted out of synchronism with generation of the musical-tone sample data.

Further, the musical-tone sample data generated by the general purpose processor are temporarily held, for 5 example, in a buffer circuit such as a latch provided in an input portion of a processing circuit, and then are processed by hardware provided in the processing cir-

Now, consider operation of the conventional musical-tone signal generating apparatus having the above mentioned processor and processing circuit, the operation which is executed when the power is applied.

The processor starts running a predetermined program when the power is turned on, and usually initial-15 izes, at the beginning of the program, memories, registers and output latches for outputting the generated musical-tone sample data within the processor, whereby the processor is controlled not to output undesired musical-tone sample data when the power is turned on.

A certain time is needed before the program starts running after the power is applied to the apparatus. Some time (a little time) therefore is required before the above initializing process is executed by means of software.

Meanwhile, since the hardware processing circuit externally connected to the processor starts operation independently of operation of the processor at the time when the power is turned on, contents of the musicaltone sample data held in the input latch provided in the input portion is not kept unchanged for a little time before the above output latch within the processor is reset by means of software.

As described above, the conventional musical-tone signal generating apparatus has drawbacks that the contents of the input latch is processed in the processing circuit, and has the possibility of outputting the resultants through D/A convertor as noise.

Further, when musical-tone controlling processes including a delay process such as the noise shaping process are executed on the generated musical-tone signal, an effect of delay process on the musical-tone signal will be realized as follows: that is, the musicalbuffer circuit such as the latch, and is read out at a later sample timing.

In the musical-tone controlling process including the above delay process, a musical-tone signal at the previ-50 ous sampling timing is delayed by the buffer circuit and is used at the current sampling timing.

It is preferable for the above musical-tone controlling process that when an amplitude of an input musical-tone signal becomes null, the resultant or output signal of the control process becomes null accordingly, but the conventional musical-tone signal generating apparatus has a drawback that even if the amplitude of the input musical-tone signal becomes zero, undesired noise might be output due to signal components previously remaining

### SUMMARY OF THE INVENTION

The first and second themes of the present invention are to provide a musical-tone signal generating apparacircuit externally connected to the general purpose processor, in which apparatus a musical-tone generating process to be executed by the general purpose processor

may be performed precisely in synchronism with various musical-tone controlling processes to be executed by the externally connected processing circuit, whereby a precise and complicated musical-tone control can be effected on a musical-tone signal.

According to the first and second aspects of the present invention, there is provided a musical-tone signal generating apparatus which comprises a general purpose processor and a processing circuit externally connected to the processor, the processor executing sound- 10 source processing program at predetermined intervals or at a sampling timing, successively generating musical-tone sample data, and the processing circuit executing musical-tone controlling processes on the generated musical-tone sample data, such as an over sampling 15 starts generating the musical-tone sample data. process, a noise shaping process and a dither process. The musical-tone signal generating apparatus further comprises synchronizing means which holds the musical-tone sample data that has been generated by the general purpose processor through execution of a 20 sound-source processing program, and inputs the musical-tone sample data to the processing circuit at predetermined intervals that are equivalent to the above predetermined sampling intervals.

The general purpose processor is designed to gener- 25 ate stereophonic musical-tone sample data, the processing circuit is designed to execute the musical-tone controlling process on the stereophonic musical-tone sample data in a time sharing manner and the synchronizing means is designed to hold the stereophonic musical-tone 30 sample data generated by the processor and inputs the musical-tone sample data to the processing circuit at the above predetermined sampling intervals.

When the processor executes the sound-source processing program at predetermined intervals through the 35 interrupt processes, generating the musical-tone sample data, times required for executing the sound-source processes every number of sampling timings to generate the musical-tone sample data are not constant because they change depending on how the program is being 40 executed. Accordingly, the succeeding musical-tone sample data are not output from the processor at completely equivalent intervals.

Meanwhile, the synchronizing means holds the musical-tone sample data output from the processor, and 45 outputs the same to the processing circuit at the predetermined output intervals which are in synchronism with the above predetermined sampling intervals.

As a result, the processing circuit receives the musical-tone sample data at precise intervals independently 50 of the time needed by the processor to execute the sound-source process. The timings at which the processor outputs the musical-tone sample data can be synchronized with the timings at which the processing circuit executes the musical-tone controlling process on 55 the respective musical-tone sample data.

The third theme of the present invention is to provide a musical-tone signal generating apparatus in which noises are suppressed that might be generated when the apparatus is turned on.

According to the third aspect of the present invention, there is provided a musical-tone signal generating apparatus which comprises a general purpose processor and a processing circuit externally connected to the processor, the processor executing a sound-source pro- 65 cessing program, successively generating musical-tone sample data, and the processing circuit executing on the generated musical-tone sample data a musical-tone con-

trolling process such as an over sampling process, a noise shaping process and a dither process. The musicaltone signal generating apparatus further comprises reset means which compulsorily resets the processing circuit when the apparatus is turned on. The reset means is provided, for example in the processing circuit to reset an input latch, which temporarily latches the musicaltone sample data sent from the processor, by means of hardware at the time when the power is turned on.

The processor starts running a predetermined program when the power is turned on, and initializes memories, registers and output latches for outputting the generated musical-tone sample data within the processor after a certain time lapses, and then the processor

Meanwhile, the hardware processing circuit externally connected to the processor starts operation independently of operation of the processor at the time when the power is turned on, and the input latch in the processing circuit is compulsorily reset at the same time when the power is turned on.

Therefore, even if the processing circuit starts operation before the processor outputs the musical-tone sample data, the processing circuit does not output any undesired musical-tone signals, suppressing noise.

The fourth themes of the present invention are to provide a musical-tone signal generating apparatus which executes musical-tone controlling processes such as a noise shaping process, including a delay process to be executed on an input musical-tone signal.

According to the fourth aspect of the present invention, there is provided a musical-tone signal generating apparatus which comprises null input-signal discriminating means for discriminating whether or not an input musical-tone signal to be subjected to a musical-tone controlling process has become null, and reset means for compulsorily resetting contents of a delay section such as a latch for executing a delay process on the musical-tone signal when the null input-signal discriminating means judges that the musical-tone signal has become null.

The null input-signal discriminating means discriminates, for example, that an amplitude envelope of the input musical-tone signal has become null. The null input-signal discriminating means also discriminates that an amplitude of the input musical-tone signal keeps null for more than a predetermined time duration. Further, the null input-signal discriminating means discriminates that a difference between amplitudes of the input musical-tone signal has become null. The null input-signal discriminating means may discriminate that the difference between amplitudes of the input musical-tone signal remains null for more than a predetermined time duration.

In the above musical-tone signal generating apparatus, the reset means compulsorily resets contents of the delay section such as the latch for executing delay process on the musical-tone signal when the null input-signal discriminating means discriminates that the musicaltone signal has been subjected to the noise shaping process and has become null. The musical-tone signal generating apparatus therefore can suppress undesired noise components which might be generated based on a musical-tone signal previously remaining in the delay

According to the fifth aspect of the present invention. there is provided another musical-tone signal generating apparatus which comprises null input-signal dis-

criminating means for discriminating whether or not an input musical-tone signal to be subjected to a musicaltone controlling process has become null, and null output-signal discriminating means for discriminating whether or not a musical-tone signal output from a musical-tone controlling process has become null, and further reset means for compulsorily resetting contents of a delay section such as a latch for executing a delay process on the musical-tone signal, when the null output-signal discriminating means judges that an output 10 musical-tone signal has become null after the null inputsignal discriminating means judges that an input musical-tone signal has become null.

The null output-signal discriminating means discriminates, for example, whether or not an amplitude envelope of an output musical-tone signal has become null. The null output-signal discriminating means also discriminates whether or not an amplitude of the output musical-tone signal keeps null for more than a predetermined time duration. Further, the null output-signal discriminating means discriminates whether or not a difference between amplitudes of the output musicaltone signal has become null. The null output-signal discriminating means may discriminate whether or not 25 the difference between amplitudes of the output musical-tone signal remains null for more than a predetermined time duration.

In the above musical-tone signal generating apparatus, the reset means compulsorily resets contents of the 30 delay section such as the latch for executing a delay process on the musical-tone signal, when the null output-signal discriminating means judges that an output musical-tone signal has become null after the null inputsignal discriminating means judges that an input musi- 35 cal-tone signal has been subjected to the noise shaping process and has become null. The musical-tone signal generating apparatus can suppress noise which might be generated when the contents of the delay section are reset before the output musical-tone signal has com- 40 pletely decreased.

In the apparatus according to the fourth or fifth aspect of the present invention, the null input-signal discriminating means can judge that the input musical-tone signal has become null, by discriminating whether or 45 not the amplitude envelope of the input musical-tone signal has become null or the amplitude of the input musical-tone signal remains to be null for more than a predetermined time duration while the null output-signal discriminating means can judge that the output musical-tone signal has become null by discriminating whether or not the amplitude envelope of the output musical-tone signal has become null or the amplitude of the output musical-tone signal remains to be null for 55 more than a predetermined time duration.

Further, the null input-signal discriminating means can judge that the input musical-tone signal has become null by discriminating whether or not the difference between the amplitudes of the input musical-tone signal 60 various processes executed by the arithmetic circuit; has become null while the null output-signal discriminating means can judge that the output musical-tone signal has become null, by discriminating whether or not the variation in amplitude of the output musicaltone signal has become null. In these cases, even when 65 the amplitude of the input or output musical-tone signal has become null or has become to a low D.C. level, the contents of the delay section can be reset or cleared.

6

## BRIEF DESCRIPTION OF THE DRAWINGS

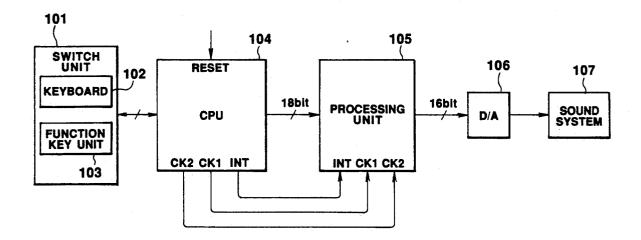

FIG. 1 is a view showing a whole structure of an embodiment of a musical-tone generating apparatus according to the present invention;

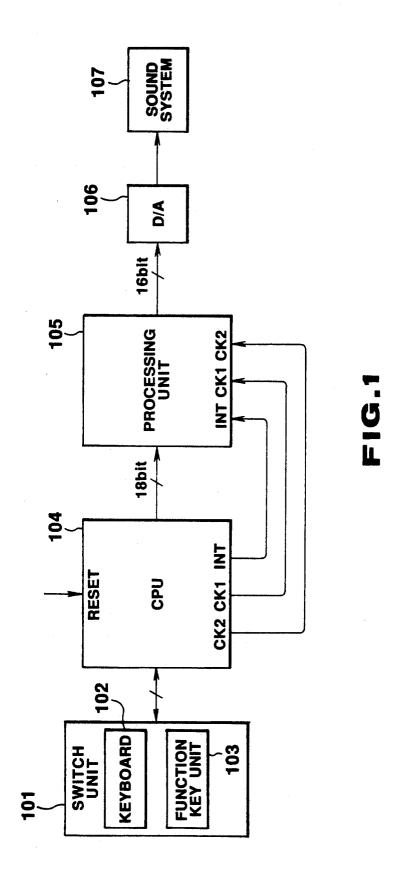

FIG. 2 is a block diagram showing an internal structure of the CPU;

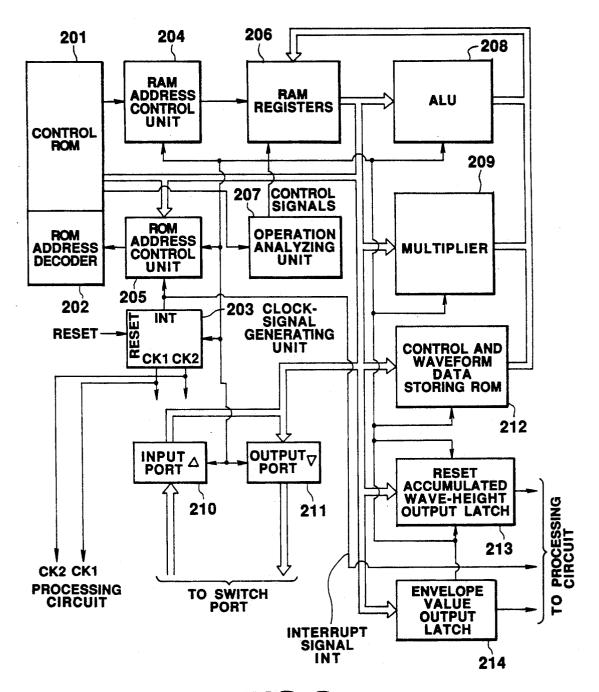

FIG. 3 is a main flow chart showing operation of the CPU;

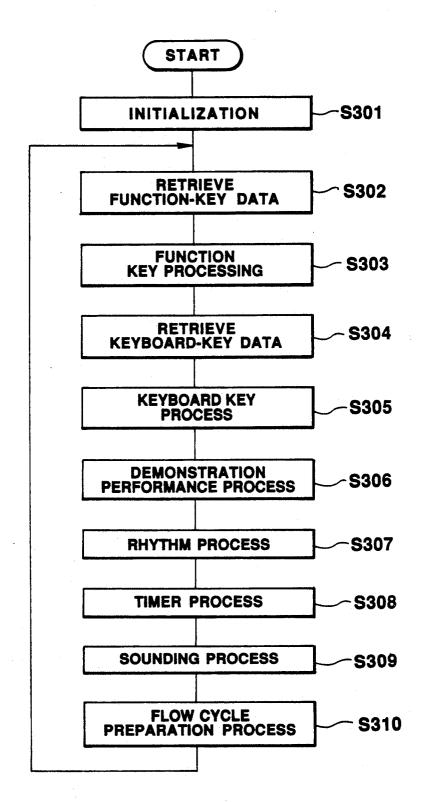

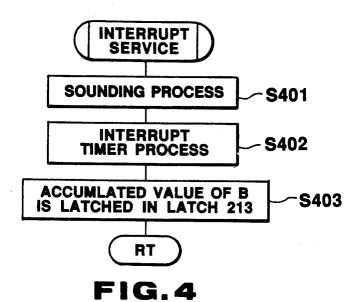

FIG. 4 is an operation flow chart of an interrupt

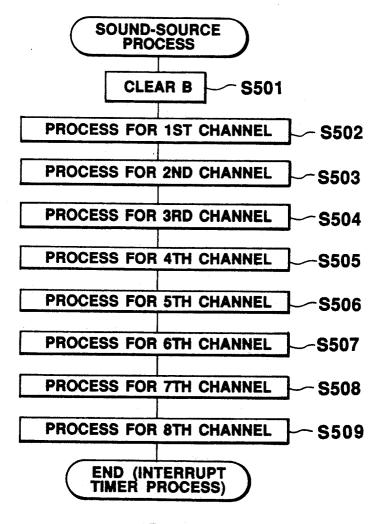

FIG. 5 is an operation flow chart of a sound-source process;

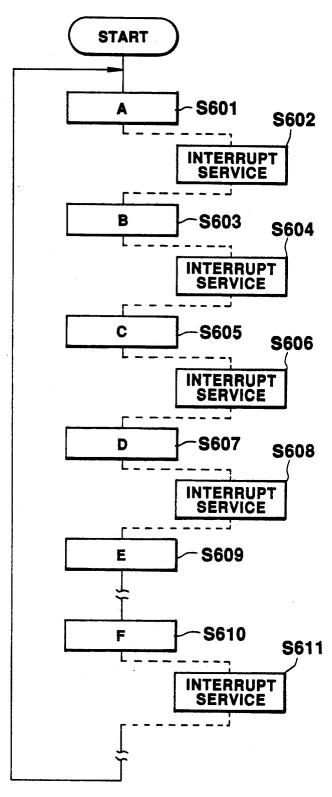

FIG. 6 is a conceptional view showing a relationship between the main flow chart of operation of the CPU and the interrupt process;

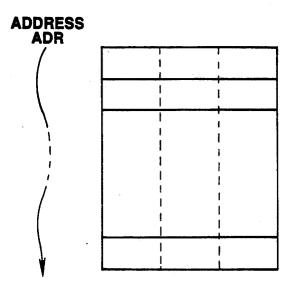

FIG. 7 is a view showing a memory area on the RAM for each sound channel;

FIG. 8 is a view showing buffer area on the RAM; FIG. 9 is a view showing a data format of quantized

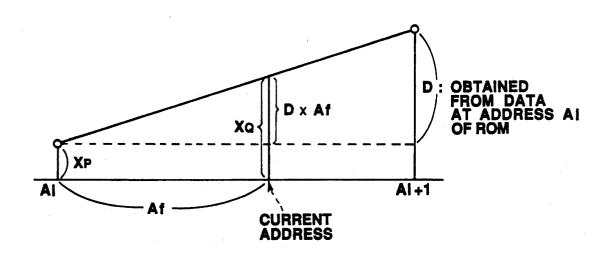

data on a control and waveform data storing ROM; FIG. 10 is a view schematically illustrating a princi-

ple for obtaining an interpolated value Xq using a difference value D and a present address Af on the ADPC system;

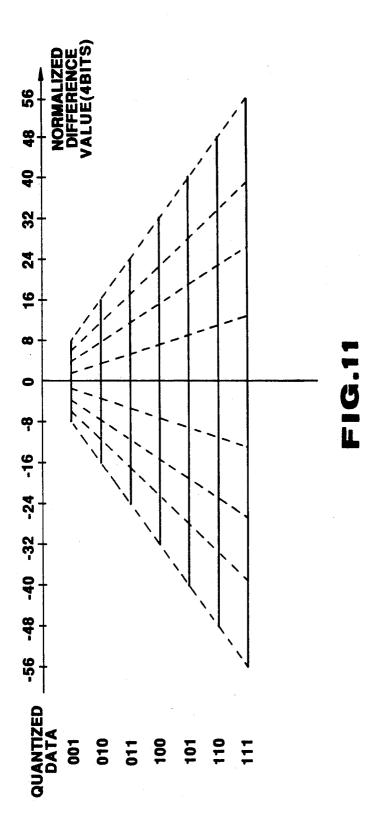

FIG. 11 is a view showing a principle of an adaptive quantization;

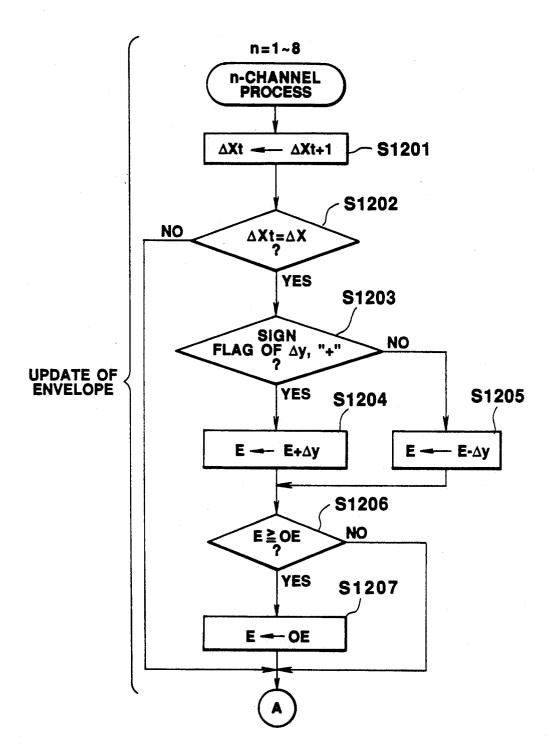

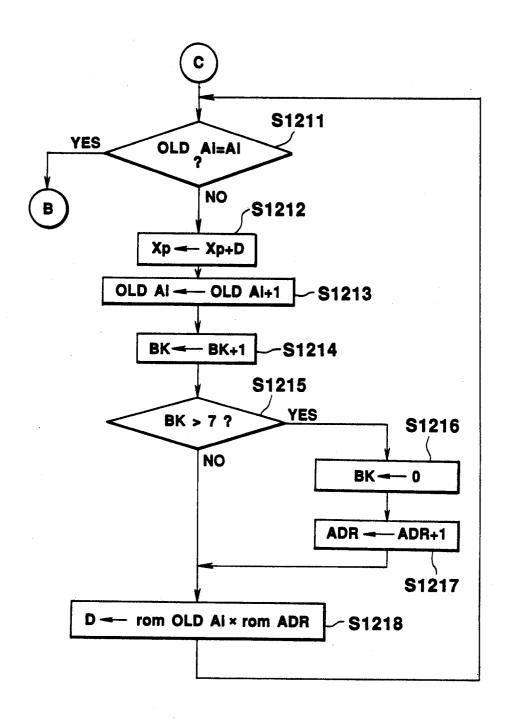

FIG. 12 is an operation flow chart (No. 1) of the sound source process of the ADPC system;

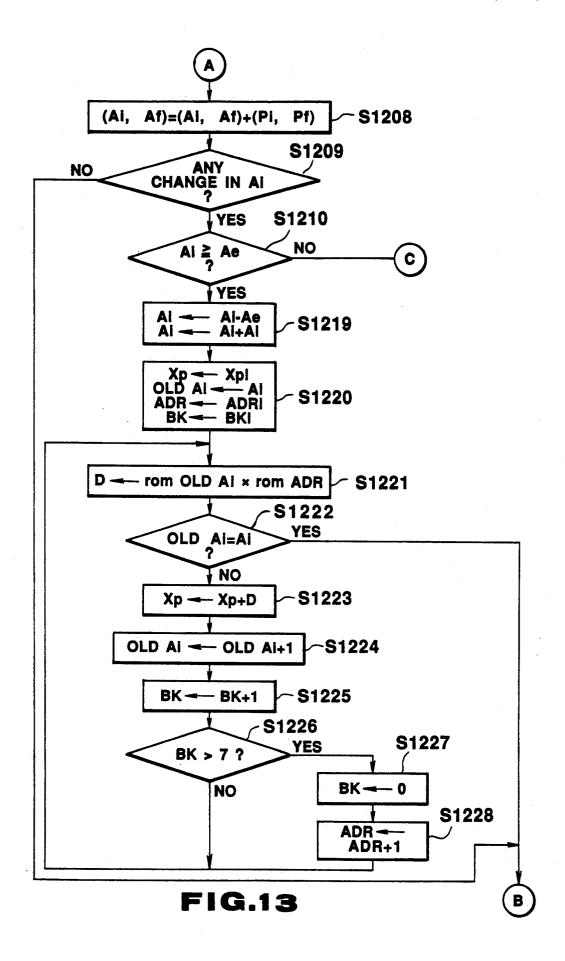

FIG. 13 is an operation flow chart (No. 2) of the sound source process of the ADPC system;

FIG. 14 is an operation flow chart (No. 3) of the sound source process of the ADPC system;

FIG. 15 is an operation flow chart (No. 4) of the sound source process of ADPC system;

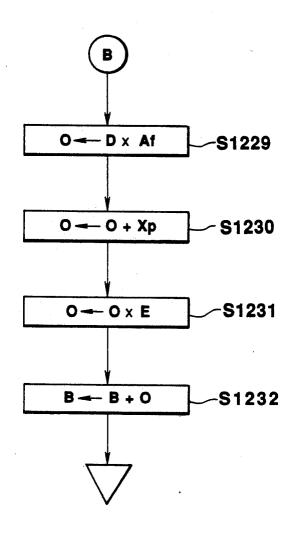

FIG. 16 is a view illustrating envelope features;

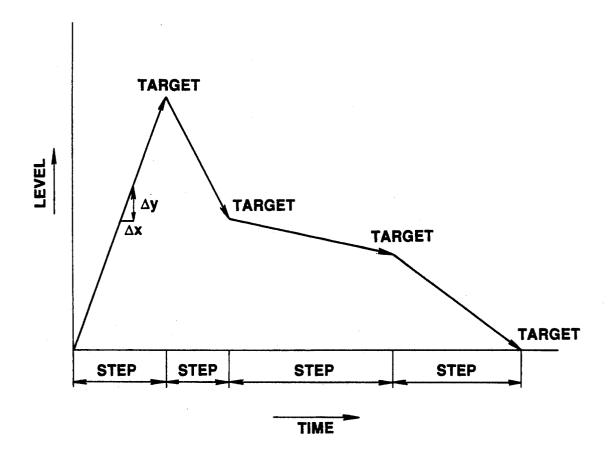

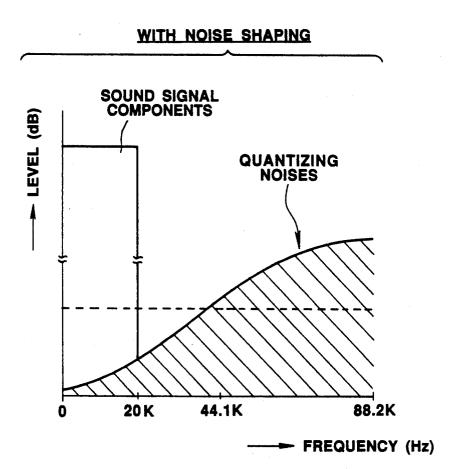

FIG. 17 is a frequency spectrum (No. 1) of a signal output from the D/A convertor;

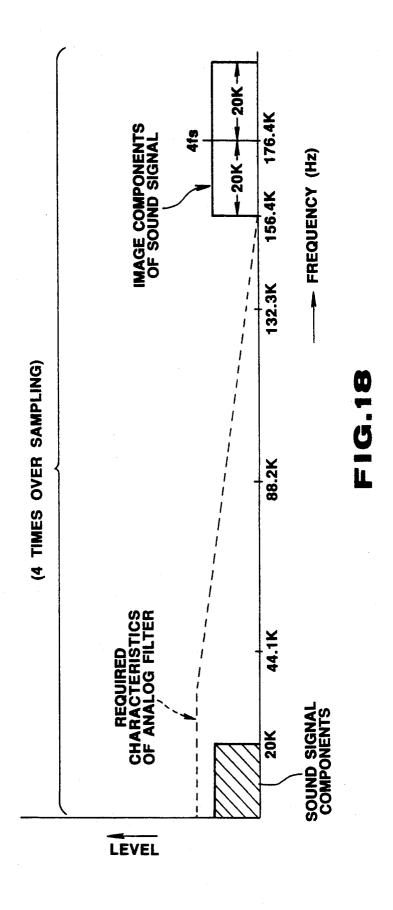

FIG. 18 is a frequency spectrum (No. 2) of a signal output from the D/A convertor;

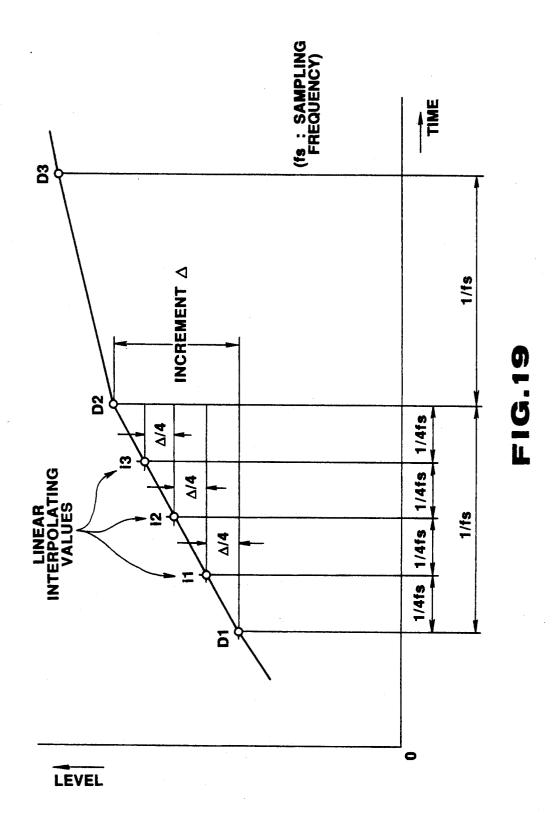

FIG. 19 is a view illustrating a linear interpolation;

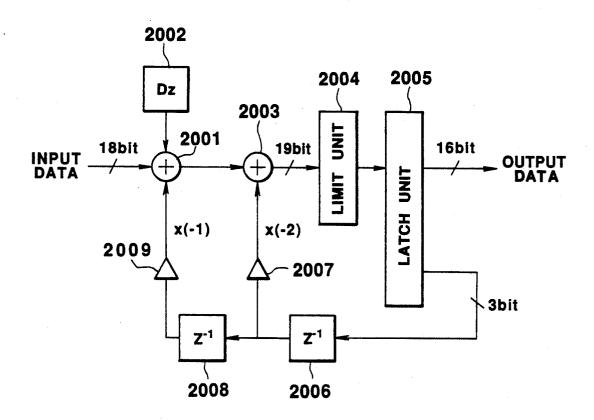

FIG. 20 is a block diagram showing a principle of a noise shaping operation;

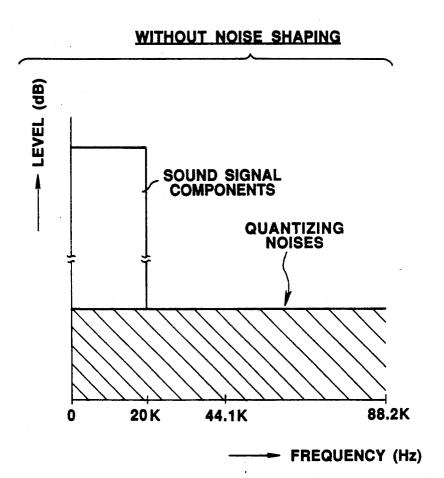

FIG. 21 is a view showing effects (No. 1) of the noise shaping operation;

FIG. 22 is a view showing effects (No. 2) of the noise shaping operation;

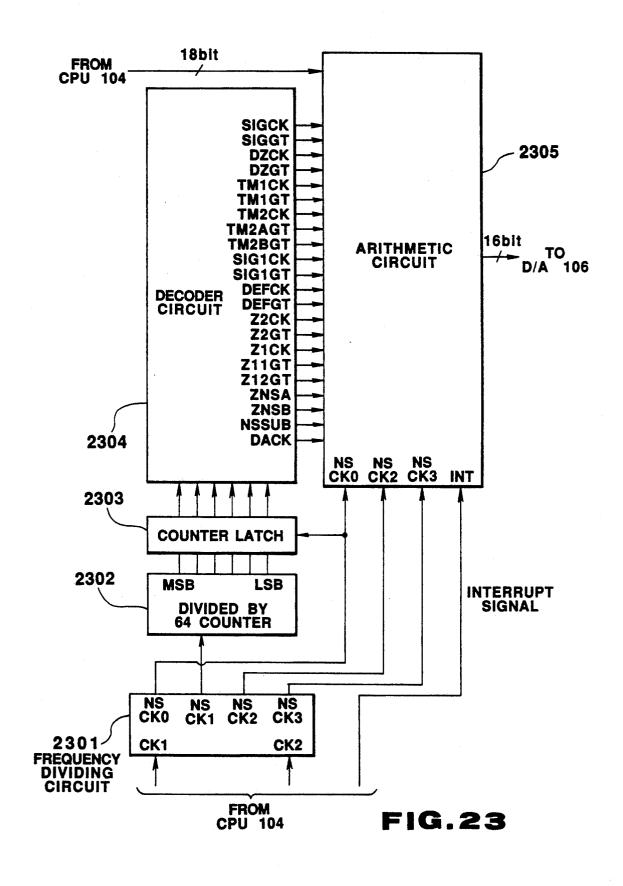

FIG. 23 is a block diagram showing an internal struc-50 ture of a processing circuit;

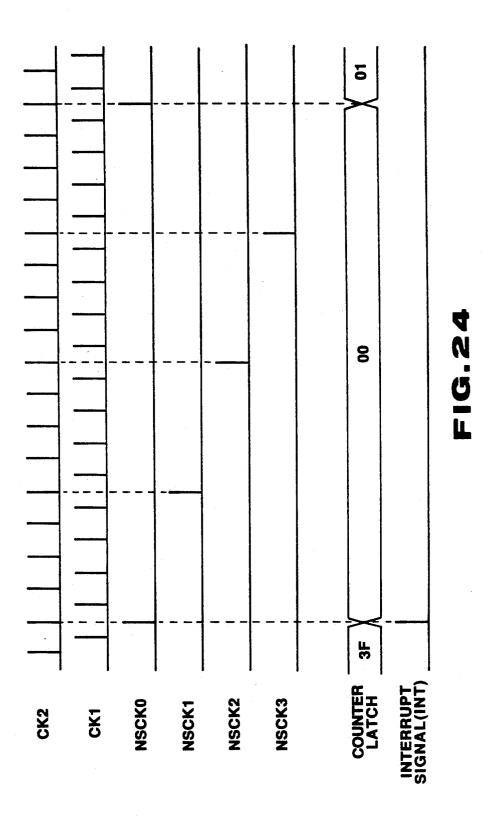

FIG. 24 is a timing chart (No. 1) of clock signals;

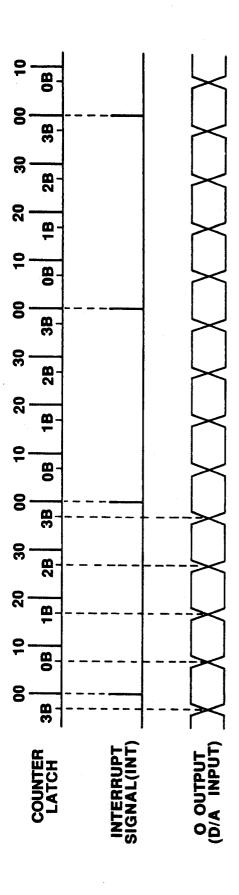

FIG. 25 is a timing chart (No. 2) of clock signals;

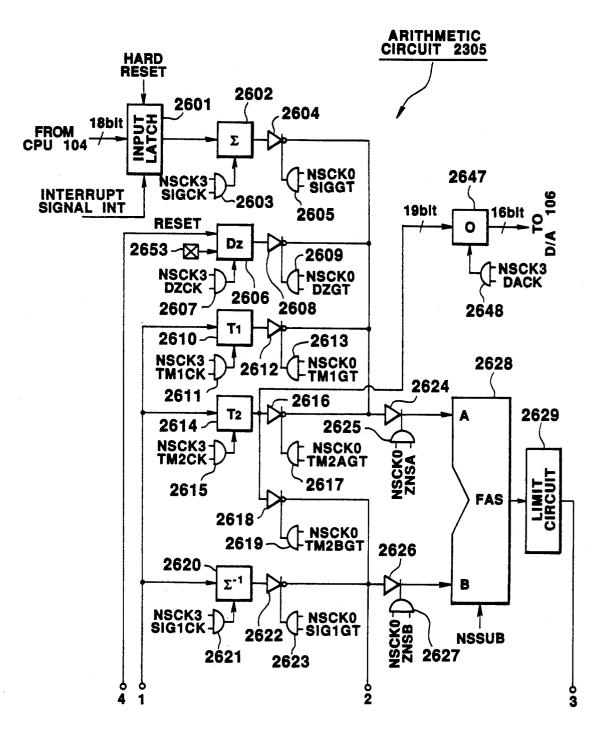

FIG. 26 is a block diagram (No. 1) showing an internal structure of an arithmetic circuit;

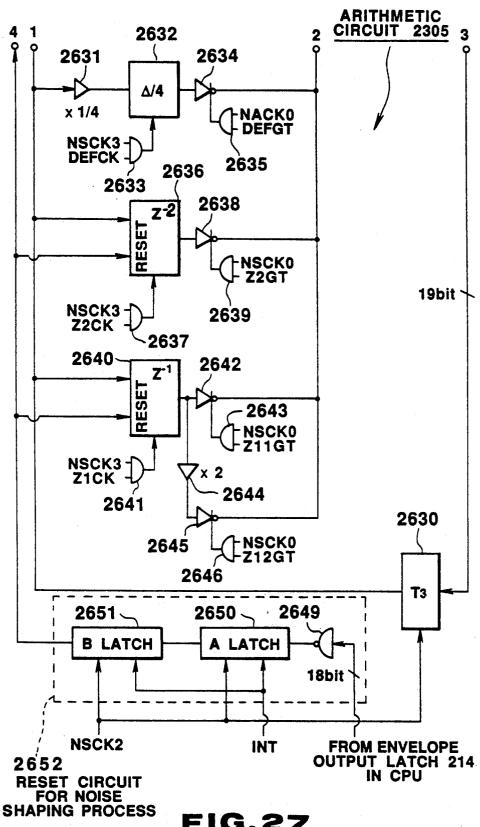

FIG. 27 is a block diagram (No. 2) showing an internal structure of an arithmetic circuit:

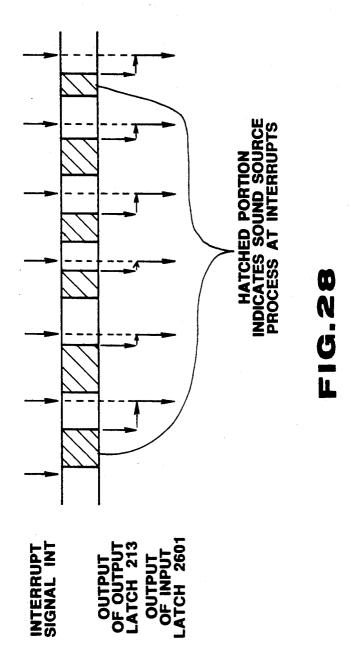

FIG. 28 is a view illustrating a synchronized operation of the CPU and the processing circuit;

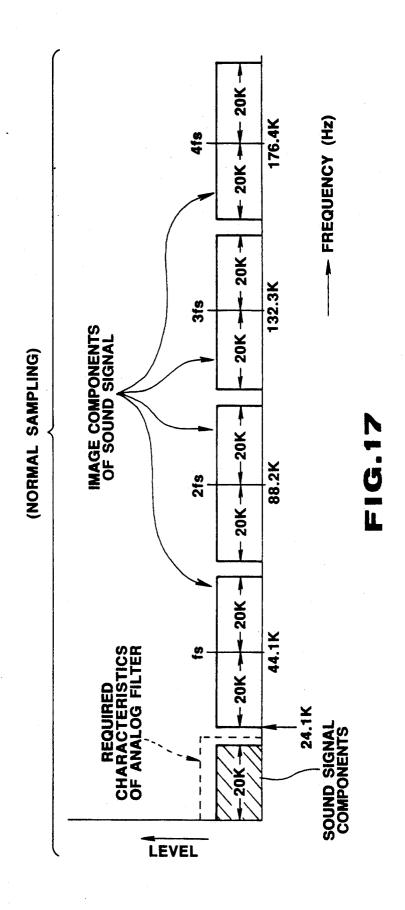

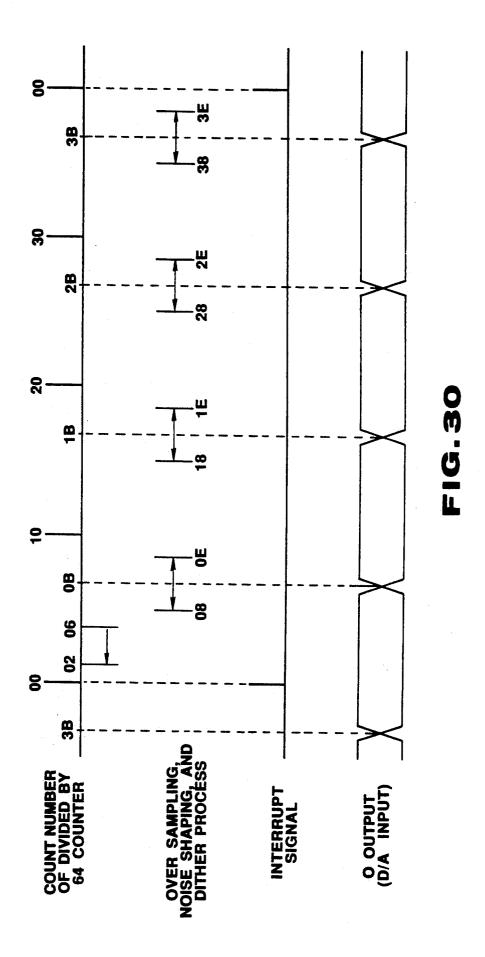

FIG. 29 is a view showing control clocks used in

FIG. 30 is a timing chart of processes executed by the arithmetic circuit;

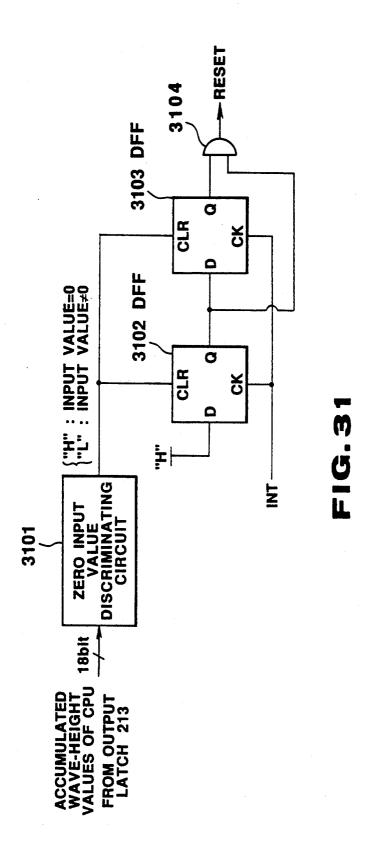

FIG. 31 is a block diagram of a second embodiment of a reset circuit of the noise shaping process;

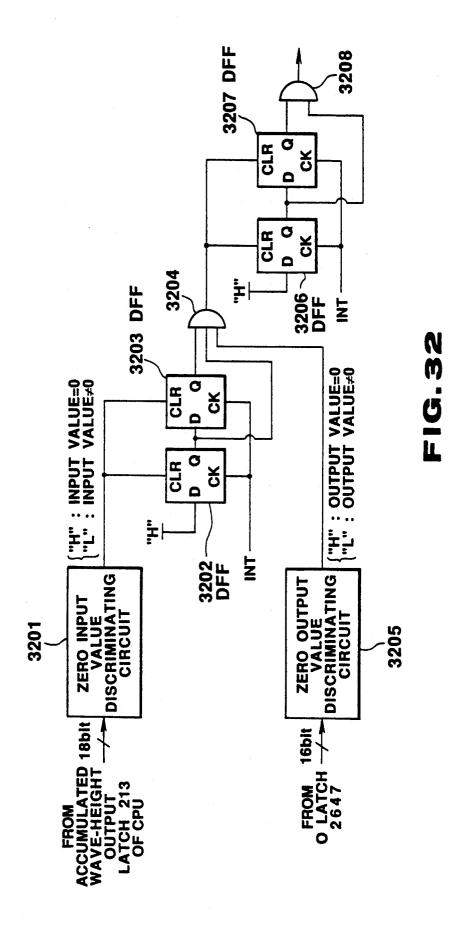

FIG. 32 is a block diagram of a third embodiment of a reset circuit of the noise shaping process;

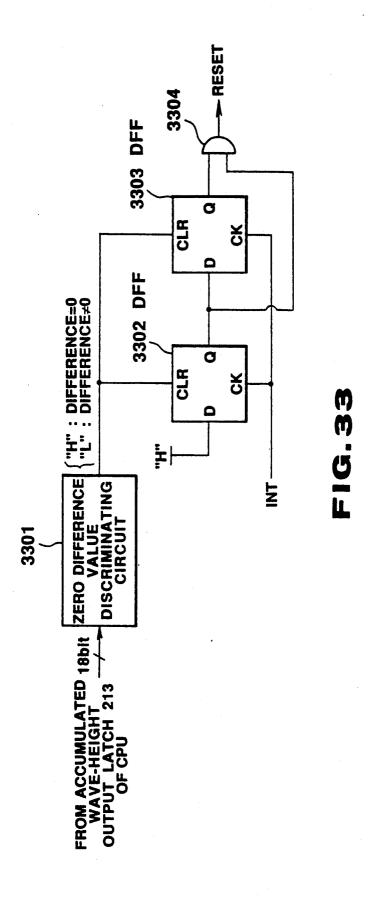

FIG. 33 is a block diagram of a forth embodiment of a reset circuit of the noise shaping process; and

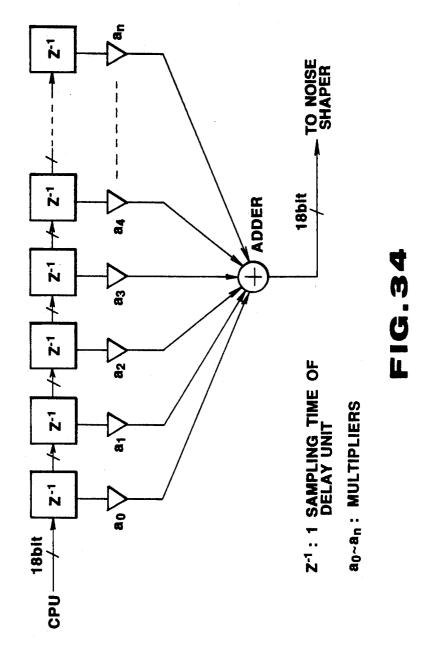

FIG. 34 is a view illustrating function of a digital low pass filtering process in another embodiment of the present invention.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Now, preferred embodiments of a musical-tone signal generating apparatus according to the present invention will be described with reference to the accompanying

### GENERAL STRUCTURE OF THE FIRST EMBODIMENT

FIG. 1 is a view showing a whole structure of the first embodiment of the musical-tone signal generating 15 apparatus of the present invention. As shown in FIG. 1, the embodiment of the musical-tone signal generating apparatus is schematically composed of CPU 104 for generating a musical-tone signal through a software process and a processing circuit for executing the other 20 processes.

A switch unit 101 including a key board 102 and a function key unit 103 is an input operation unit of a musical instrument. Performance data input from the switch unit 101 is processed in CPU 104 and the pro- 25 cessing circuit 105.

A musical-tone signal generated by the processing circuit 105 is supplied to a D/A convertor 106, being converted into an analog signal. The analog signal is smoothed by a low pass filter (not shown) and is audibly 30 output from a sound system 107.

FIG. 2 is a block diagram showing an internal structure of CPU 104.

A control and waveform data storing ROM 212 stores musical-tone control parameters such as target 35 values of envelope values to be described later, musicaltone difference waveform data and quantized data in an adaptive difference pulse code modulation (ADPCM). Successively analyzing contents of a program stored in a control ROM 201, an operation analyzing unit 207 40 accesses the respective data on the control and waveform data storing ROM 212 to perform a sound-source process by means of software.

The control ROM 201 stores a program for controlling a musical tone to be described later, and succes- 45 sively outputs program languages (commands) which are stored at addresses designated through ROM address decoder 202 from ROM address control unit 205. More specifically, language lengths of respective proaddress system is executed in which a part of a program language is input as a less significant part (address within page) of an address to be read out next to ROM address control unit 205. A CPU of a ordinary counter system may be used as CPU 104.

The operation analyzing unit 207 analyzes an operation code of a command output from the control ROM 201, and sends control signals to respective circuits to perform designated operations.

of a relevant register in RAM 206, when an operand of a command sent from the control ROM 201 designates a register. RAM 206 stores various buffers as well as various musical-tone control data for 8 channels, as will be described later.

ALU 208 performs an addition and subtraction and a logical operation, and a multiplier 209 performs a multiplication, based on an instruction of the operation ana8

lyzing unit 207, when a command from the control ROM 201 is an operation command.

A clock-signal generating unit 203 supplies an interrupt signal INT at predetermined intervals to ROM 5 address control unit 205 and an input latch (2601 in FIG. 26) of an arithmetic circuit 2305 within a processing circuit 105 to be described later.

An input port 210 and an output port 211 are connected to the switch unit 101 of FIG. 1.

Various data read out from the control ROM 201 and RAM 206 are supplied via a bus to ROM address control unit 205, ALU 208, the multiplier 209, the control and waveform data storing ROM 212, an accumulated wave-height output latch 213, an envelope value output latch 214, the input port 210 and the output port 211. Output signals of ALU 208, the multiplier 209 and the control and waveform data storing ROM 212 are supplied to RAM 206 via the bus.

An accumulated wave height and an envelope value of one sample data of a musical-tone signal generated through the sound-source process are input via the bus to the accumulated wave-height output latch 213 and the envelope value output latch 214 respectively. When a sound-process complete signal is input to clock inputs of the accumulated wave-height output latch 213 and the envelope value output latch 214 from the operation analyzing unit 207, the accumulated wave heights and the envelope values of one sample data of a musicaltone signal are successively read out from RAM 206 onto the bus, and are successively latched in the accumulated waveform-height output latch 213 and the envelope value output latch 214.

### Operation of CPU 104

General Operation of CPU 104

Now, general operation of CPU 104 of FIG. 1 will be described hereafter referring to the whole structure of the embodiment shown in FIG. 1.

In the present embodiment, CPU 104 repeatedly performs a series of processes at steps S302 through S310 in accordance with a main flow chart of FIG. 3, executing a sound-source process to generate musical-tone data.

CPU 104 executes the actual sound-source process when an interrupt service is entered. More specifically, an interrupt is caused at certain intervals while CPU 104 is executing a program in accordance with the main flow chart of FIG. 3. Then, CPU 104 executes a program of the sound-source process, generating a musicalgram languages are, for example, 28 bits, and a next 50 tone signal of 8 channels. When the sound-source process is finished, musical-tone signals are accumulated for 8 channels, being output as an output musical-tone signal to the accumulated wave-height output latch 213 of FIG. 2. Then, CPU 104 returns from the interrupt 55 service to the processes of the main flow chart. The above interrupt service is periodically executed in accordance with instructions from a hard timer within the clock-signal generating unit 203 of FIG. 2. The period at which the interrupt service is executed is equivalent RAM address control unit 204 designates an address 60 to the sampling period at which musical-tone signals are

> The general operation of CPU 104 has been described above. Now, detailed operation of CPU 104 will be described with reference to FIGS. 3 to 5.

> The main flow chart of FIG. 3 illustrates a flow of processes other than the sound-source process which are executed by CPU 104 while no interrupt is caused by the clock-signal generating unit 203.

When the power is turned on, contents of RAM 206 within CPU 104 shown in FIG. 2 are initialized at step S301. Respective switches in the function key unit 103 of FIG. 1, which is externally connected to CPU 104, are scanned at step S302. States of the respective 5 switches are sent through the input port 210 to a key buffer area of RAM 206. Upon completion of scanning keys, a function key whose state has been changed is detected, and a process of the relevant function is executed at step S303. For example, the number of a musi- 10 cal tone, the number of an envelope are set and number of rhythm is set, if a rhythm performance is to be effected.

Then, the states of depressed keys of the key board 102 are sent to the key buffer area of RAM 206 similarly 15 to the above function key at step S304. When the keys are detected, a key assign process is executed at step

When a demonstration performance key (not shown) of the function key 103 of FIG. 1 is depressed, demon- 20 executed for respective channels of a sounding channel stration performance data (sequencer data) are sequentially read out from the control and waveform data storing ROM 212 of FIG. 2, and the key assign process is executed at step S306. When a rhythm start key (not shown) of the function key unit 103 is depressed, 25 later. rhythm data are sequentially read out from the control and waveform data storing ROM 212, and the key assign process is executed at step S307.

At step S308, a timer process is executed. More specifically, a time value of time data, which has been 30 incremented through an interrupt timer process of step \$402 to be described later, is judged, and the time data is compared with sequencer data for controlling times which are sequentially read out to control a demonstration performance, whereby a time control is effected for 35 the demonstration performance of step \$306 or is compared with rhythm data for controlling time which are read out to control a rhythm performance, whereby a time control is effected for the rhythm performance of step S306.

In a sounding process at step S309, a pitch envelope process is executed to apply an envelope to pitches of a musical tone to be subjected to a sounding process, and to set pitch data to a corresponding sound channel.

A flow cycle preparation process is executed at step 45 S310. During the flow cycle preparation process, a state of a sounding channel of a note number corresponding to a key to be depressed in a keyboard key process is changed while a key is being depressed, or a state of a sounding channel of a note number corresponding to a 50 released key in a keyboard key process is changed while no sound is produced.

Now, an interrupt service of FIG. 4 will be described. When an interrupt is entered by the clock-signal generating unit 203 to a program corresponding to the main 55 flow chart of FIG. 3, execution of the program is halted and a program of the interrupt service of FIG. 4 starts running. The program of the interrupt service controls such that contents of registers which are written during execution of the program of the main flow chart of 60 FIG. 3 are not re-written. A process therefore is not needed which is executed at the beginning and the end of the conventional interrupt service for allowing the registers to retire and comeback, whereby CPU 104 can move rapidly from the operation of the main flow chart 65 of FIG. 3 to the interrupt service and vice versa.

In the interrupt service, the sound-source process starts at step \$401. The details of the sound-source pro10

cess are shown in FIG. 5. Accumulated musical-tone signal data for 8 channels are obtained in a buffer B in RAM 206 of FIG. 2 through the sound-source process.

At step \$402, an interrupt timer process is executed. Since the interrupt service of FIG. 4 is executed every predetermined number of sampling periods, a value of time data (not shown) in RAM 206 of FIG. 2 is incremented accordingly. The time data represents a time lapse. As described above, the time data obtained thus is used in the timer process at step S308 of the main flow chart of FIG. 3 for time controlling.

An accumulated wave height value in the above buffer area is latched in the accumulated wave-height output latch 213 of FIG. 2.

Now, the operation of the sound-source process, which is executed at step S401 of the interrupt service, will be described referring to the flow chart of FIG. 5.

An area of RAM 206 for adding waveform data is cleared at step \$501. The sound-source processes are at steps S502 through S509. Finally, when the soundsource process for the 8th channel is finished, waveform data accumulated for 8 channels is obtained in a buffer area B. The details of the processes will be described

FIG. 6 is a conceptional chart showing a relationship between the processes of the flow chart of FIG. 3 and those of the flow chart of FIG. 4. At step S601, a process A is executed. For example, the process A corresponds to "the function-key process" or "the keyboardkey process" of the main flow chart shown in FIG. 3. Then, the interrupt service is entered, starting the sound-source process at step S602. A musical-tone signal including one-sampling signal for 8 channels is obtained through the sound-source process, and is output to the accumulated wave-height output latch 213. And then CPU 104 returns to a process B of the main flow chart. Similar operation is repeatedly executed at steps S604 to S611, whereby the sound-source process is 40 performed for all the sound channels. The operation is executed while musical tones are being audibly output.

Data Structure in Sound-Source Process

Now, the sound-source process, which is to be executed at step \$401 of FIG. 4, will be described more specifically.

In the present embodiment, CPU 104 executes the sound-source process for 8 sound channels, as described above. Data for 8 channels to be processed in the soundsource process have a data format as illustrated in FIG. 7, and are set respectively in areas which are prepared in RAM 206 of FIG. 2 for 8 sound channels.

In RAM 206, a buffer B as shown in FIG. 8 for temporarily holding accumulated waveforms is prepared.

Various control data used in the sound-source process based on the ADPCM system are stored in respective sound channel areas of FIG. 9. In FIG. 7, a symbol A represents an address designated when an adaptive quantized difference data (which will be described later) is read out during the sound-source process. A symbol Ai stands for an integer portion of a current address that corresponds directly to an address where adaptive quantized difference data of the control an waveform data storing ROM 212 of FIG. 2 is stored. A symbol Af stands for a decimal portion of the current address, which is used for interpolation of an inverse quantized difference value read out from the above ROM 212. Symbols Pi and Pf represent an integer portion and a decimal portion of pitch data respectively.

For example, Pi=1, Pf=0 represent a pitch of an original sound, Pi TM 2, Pf=0 represent a pitch which is higher by one octave and Pi=0, Pf=0 represent a pitch which is lower by one octave. Other various control data will be described in detail when the ADPCM sys- 5 tem is described later.

11

Control data such as pitch data, envelope data, required in the sound-source process are set in corresponding sound-channel areas respectively, when CPU flow chart of FIG. 3. In the sound-source processes which are executed for respective sound-channels of FIG. 5 during the interrupt services of FIG. 4, the various control data set in the sound channel areas are used to generate musical tones. In this manner, data 15 transfer between the program of the main flow-chart process and the program of sound-source process is executed through control data (musical-tone generating data) in the sound-channels area of RAM 206. When one program is running, the sound-channel areas may 20 be accessed independently of how the other program is running and vice versa. The programs therefore may be incorporated as substantially independent modules respectively, and may be written as a simple and effective program structure.

The control and waveform data storing ROM 212 stores adaptive quantized difference data of a data format (not shown) as well as quantized data of a format shown in FIG. 9. As will be described later, the quantized data is used as control data for inverse quantizing 30 adaptive quantized difference data which are read out from the control and waveform data storing ROM 212. Further, the control and waveform data storing ROM 212 stores control data for generating musical tones of respective tone colors. When a player or user of the 35 present apparatus sets tone color, the above control data are transferred from the control and waveform data storing ROM 212 to the sound-channel areas of RAM 206 to be set therein.

Principle of Sound-Source Process depending on 40 ADPCM system

Now, the sound-source process depending on the ADPCM system or a sound-source process (either of processes at steps S502 through S509) for one of the sound-channels of FIG. 5 will be described. The opera- 45 tion analyzing unit 207 of CPU 104 interprets and performs the program for the sound-source process, stored in the control ROM 201, executing the sound-source process. Hereafter, unless otherwise described, all processes are to be executed with this premise.

At first, an operational principle of the ADPCM system will be described in brief.

In FIG. 10, sample data Xp corresponding to an address Ai of the control and waveform data storing ROM 212 of FIG. 2 is obtained from a difference value 55 different from a sample data corresponding to an address (Ai-1) (not shown) preceding the address Ai.

At the address Ai of the control and waveform data storing ROM 212, adaptive quantized difference data is written for obtaining a difference value D from the 60 following sample data. The difference value D can be obtained from the adaptive quantized difference data. A sample data at the following address is obtained from the expression: Xp+D, and the newly obtained data Xp+D is substituted as a new sample data Xp.

If the current address is Af as shown in FIG. 10, the sample data corresponding to the current address Af is obtained from the expression:  $Xp + D \times Af$ .

As described above, in the ADPCM system, adaptive quantized difference data for obtaining a difference value D from a sample data of the following address is read out from the control and waveform data storing ROM 212 of FIG. 2, and the difference value D is calculated, added to the current data. Then, the following sample data is obtained, and in the manner waveform data are sequentially generated.

12

When a waveform signal such as a sound and a musi-104 executes processes in accordance with the main 10 cal tone is quantized, in which a difference value between adjacent data is small, the ADPCM system will be a useful means because the ADPCM system allows data to be quantized with a few number of bits compared with a conventional PCM system.

The ADPCM system employs a fine principle of an adaptive quantization, as will be described later.

Now, we assume that, when difference values of a musical-tone signal are stored in a memory, n bits of quantizating bits are required for quantizing a difference value of a maximum amplitude ±E with a given S/N ratio. If only a data capacity of m bits less than n bits is assigned to one sample data due to a limited capacity of a memory, a difference value per one sample has to be managed to be quantized with m bits of quantizing bits.

For that purpose, a range of the amplitude (from -Eto +E) is divided by  $2^m$ , resulting in a wider range of quantization with poor S/N ratio.

In the ADPCM system, when a difference value of a musical-tone signal is stored in a memory, an absolute amplitude value which can be expressed by m bits with a given S/N ratio defines a range of  $|\pm e|$  smaller than  $|\pm E|$ . A difference value, an absolute value of whose amplitude is larger than  $|\pm e|$ , is divided by a normalizing coefficient larger than 1, being compressed so as to fall into the range. Then, the difference value is quantized by m bits, being stored in the memory. As a result, the bit number per one sample data required for quantization can be reduced with a given S/N ratio. The process described above is called an adaptive quantization.

In order to reproduce the original difference value from difference data adaptive-quantized as described above, the normalizing coefficient by which sample data was normalized is stored together with the sample data. When the adaptive quantized difference data is read out from the memory, a relevant normalizing coefficient is simultaneously read out. The adaptive quantized difference data is multiplied by the normalizing coefficient, whereby the original difference value is obtained. This process is called an inverse-adaptive quantization.

When the normalizing coefficients for respective sample data are stored, a memory capacity is required as much as required when a difference value of an amplitude range ±E is quantized with n bits. Data compression therefore is not realized.

Specific operation of the sound-source process by means of the ADPCM system, which can suppress an increase of memory capacity will be described hereafter. < Specific Operation of Sound-Source Process by means of ADPCM system>.

An amplitude of difference value of a musical-tone signal does not vary abruptly within some time duration corresponding to a continuous 8 samples. So let us assume that difference values for a continuous 8 samples are adaptive-normalized with the same normalizing coefficient to store the difference values in the memory. The normalizing coefficient is also quantized with several bits such that the normalizing coefficient itself varies at not so fine steps.

More specifically, the normalizing coefficient is expressed with 3 bits so that a value of the normalizing coefficient varies at 8 steps. The normalizing coefficient 5 therefore may be quantized every 8 samples with 3 bit data to be stored in the memory, allowing data compression. Hereafter, the above normalizing coefficient will be referred to as quantized data.

The above described principle will be described with 10 has coincided with  $\Delta Xt$ . reference to FIG. 11. In FIG. 11, ±E is ±56.4, ±e is  $\pm$ 8, and a quantization range is 1. Hence, since a range of ±8 is quantized with 16 levels, quantized bit number will be 4 bits and quantized data be 3 bits, when the difference value is adaptive-quantized. When the differ- 15 ence values are adaptive-quantized, the original difference values are divided by a coefficient corresponding to the quantized data, being compressed into a range of  $\pm 8$

In FIG. 11, when the original difference value is 20 within a range of  $\pm 8$ , the original difference value is divided by a coefficient 1 which is designated by quantized data "001", that is, no data compression is effected. When the original difference value is within a range between  $\pm 8$  and  $\pm 16$ , the original difference 25 value is divided by a coefficient 2 which is designated by quantized data "010". Similarly, when the original difference value is within a maximum range between  $\pm 32$  and  $\pm 64$ , the original difference value is divided by a coefficient 8 which is designated by quantized data 30 "111". Difference data which have been data-compressed and quantized with 4 bits are stored in the control and waveform data storing ROM 212 of FIG. 2 and simultaneously quantized data of 3 bits are stored in ROM 212 data by data for respective 8 samples of dif- 35 ference values.

Now, specific operation of the sound-source process by means of the ADPCM system will be described with reference to the flow charts of FIGS. 12 to 15. Respective variables used in processes of the flow charts are 40 secured with the formats shown in FIG. 7 in the corresponding sound channel areas of RAM 206 of CPU 104.

The sound-source process shown in FIGS. 12 to 15 comprises mostly envelope process (steps S1201 through S1207) and waveform process (steps S1208 45 through S1232).

The envelope process will be described before the waveform process based on the principle of ADPCM system of FIGS. 10 and 11.

FIG. 16 is a view showing an envelope generated 50 1 through the envelope process. As will be described later, at step S1231, a musical-tone signal output 0 is multiplied by an envelope value E generated through processes at steps S1201 to S1207 of FIG. 12, applying an envelope to sample data of musical-tone signals.

The envelopes to be applied to respective musicaltone signal data consist of several segments. An example of an envelope consisting of four segments is shown in FIG. 16.  $\Delta X$  stands for a sampling cycle of the envelope while  $\Delta Y$  stands for an increment of the envelope.

At steps S1201 to S1207 of the envelope process, an envelope value E is calculated every number of sampling timings and it is judged whether or not the calculated envelope value E has reached a target envelope value OE of a segment. When the envelope value E has 65 tained at step S1230. reached the target value OE, it is detected in the sounding process at step S309 of the main flow chart of FIG. 3 that the envelope value E has reached the target value

OE. Then, data ( $\Delta X$ ,  $\Delta Y$  and a target envelope value) for the following segment of the envelope are read out from the control and waveform data storing ROM 212 of FIG. 2 and are set to the corresponding sound channel area (see FIG. 7) of RAM of FIG. 2.

More specifically, at step S1201, a timer value  $\Delta Xt$  is incremented every number of interrupt timings to be compared with an arithmetic period  $\Delta X$  of the envelope. Then, it is judged at step S1202 whether or not  $\Delta X$

If not, the envelope process is not effected.

When it is judged at step S1202 that  $\Delta X$  has coincided with  $\Delta Xt$ , a sign bit of the increment  $\Delta Y$  of the envelope is discriminated at step S1203.

When it is judged at step S1203 that the sign bit of the increment  $\Delta Y$  is positive, i.e., the result of the judgement at step S1203 is YES, the envelope is increasing. Then, at step S1204, the increment  $\Delta Y$  is added to the current envelope value E.

On the contrary, when the sign bit of the increment ΔY is negative, and the result of the judgement at step S1203 is NO, the envelope is decreasing. Then, at step S1205, the increment  $\Delta Y$  is subtracted from the current envelope value E.

Thereafter, it is judged at step S1206 whether or not a current envelope value E has reached or exceeded the target envelope value OE. When the current envelope value E has reached or exceeded the target envelope value OE, the current envelope value is replaced with the target envelope value OE.

In the sounding process at step \$309 of the main flow chart shown in FIG. 3, it is recognized that the current envelope value has been replaced with the target envelope value 0E, and then data for the following segment of the envelope are set to RAM 206. When it is recognized in the sounding process that the current envelope value E is 0, it is also recognized the sounding process has been finished.

Now, the waveform process at steps S1208 to S1232 based on the principle of the ADPCM system of FIGS. 10 and 11 will be described.

Let us assume that, among addresses of the control and waveform data storing ROM 212 where adaptive quantized difference data are stored, the address where data to be processed in the present process is stored is designated by (Ai, Af) of FIG. 7.

Pitch data (Pi, Pf) is added to the current address (Ai, Af) at step S1208. The pitch data corresponds to the key number of a depressed key of the key board 102 of FIG.

It is judged at step S1209 whether or not any change in the integer portion Ai of an added address has been found. If the result of the judgement is NO, an interpolated data value 0 corresponding to the decimal portion Af of the address is calculated at step S1229 through an arithmetic process D×Af using the difference value D at the address Ai of FIG. 10. The difference value D has been previously obtained through the sound-source process at a previous interrupt timing (see steps S1218 60 and S1221 to be described later).

Then, sample data Xp corresponding to the integer portion Ai of the address is added to the interpolated data value 0, and thus a new sample data 0 (Xq of FIG. 10) corresponding the current address (Ai, Af) is ob-

The sample data 0 is multiplied by the envelope value E obtained in the previous envelope process at step S1231, and the content of the resultant product 0 is

accumulated at step S1232 on the waveform data buffer B (FIG. 8) in RAM 206 of FIG. 2. Musical-tone signal-outputs generated through the sound-source process for other sound channels are accumulated in the buffer B, and finally musical-tone signal data of one sample is 5 generated as accumulated data of 8 channels.

Then, operation returns to the process of the main flow of FIG. 3, and the interrupt is caused again at the following sampling timing, and wherein the sound-source process of FIGS. 12 to 15 will be executed and 10 pitch data (Pi, Pf) is added to the current address (Ai, Af) at step S1208.

The above operation will be repeatedly performed until a change in the integer portion Ai of the address is found. During the performance of operation, the sample 15 data Xp and the difference value D are not updated, and only the interpolated data 0 is updated in accordance with integer portion Af of the address, whereby a new sample data Xq is obtained every update of the sample data.

If the integer portion Ai of the current address has changed at step S1209 as a result of addition of the pitch data (Pi, Pf) to the current address (Ai, Af), it is judged at step S1210 whether or not the address Ai has reached or exceeded an end address Ae.