(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0076893

(43) 공개일자 2010년07월06일

(51) Int. Cl.

*H03M 13/37* (2006.01) *H03M 13/23* (2006.01)*H03M 13/27* (2006.01)

(21) 출원번호 10-2009-0129663

(22) 출원일자 2009년12월23일

심사청구일자 없음

(30) 우선권주장

200810189684.9 2008년12월26일 중국(CN)

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

차오 챕

중국 100125, 베이징, 차오양 디스트릭트, 시아팡리, No.9, 총디안 파찬 빌딩 12층, 베이징 삼성텔레콤 R&amp;D 센터

최승훈

경기도 수원시 영통구 원천동 주공아파트 원천주공 2단지 213동 1702호

(뒷면에 계속)

(74) 대리인

권혁록, 이정순

전체 청구항 수 : 총 5 항

(54) 터보 코딩 방법 및 터보 코딩 방법을 구현하기 위한 장치

### (57) 요 약

CTC(Convolutional Turbo Coding)를 위한 방법 및 장치 그리고 터보 인코더를 위한 장치가 제공된다. CTC를 위한 방법은 컨스티튜언트 인코더(consituent encoder)를 이용하여 정보 비트 A 그리고 B를 인코딩하고, 패리티 시퀀스  $Y_1$  그리고  $W_1$ 을 출력하는 과정과 상기 정보 비트 A 그리고 B를 CTC 인터리버를 이용하여 정보 비트 C 그리고 D를 얻기 위해 인터리빙하고, 인터리빙한 정보 비트 C 그리고 D를 상기 컨스티튜언트 인코더를 이용하여 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 얻기 위해 인코딩하는 과정과 상기 정보 비트 A 그리고 B, 상기 패리티 시퀀스  $Y_1$  그리고  $W_1$ , 상기 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 각각 인터리빙하는 과정과, 여기서 정보 비트 A 그리고 B를 포함하는 비트 그룹, 시퀀스  $Y_1$  그리고  $W_1$ 을 포함하는 비트 그룹, 시퀀스  $Y_2$  그리고  $W_2$ 를 포함하는 비트 그룹 중 적어도 하나의 비트 그룹에 포함되어 있는 비트는 높은 안정도 및 낮은 안정도를 가지는 성상도 포인트(constellation points)의 비트 중 하나의 비트에 매핑됨, 인코딩된 비트 시퀀스를 얻기 위해 인터리빙 결과를 평쳐링(puncturing)하는 과정을 포함하는 것을 특징으로 한다.

### 대 표 도

(72) 발명자

박성은

서울특별시 동작구 사당1동 446-17 현대빌라트2차

202호

임치우

경기도 수원시 영통구 영통1동 청명마을4단지아파

트 426동 303호

## 특허청구의 범위

### 청구항 1

CTC(Convolutional Turbo Coding)를 위한 방법에 있어서,

(a) 컨스티튜언트 인코더(consituent encoder)를 이용하여 정보 비트 **A** 그리고 **B**를 인코딩하고, 패리티 시퀀스  $Y_1$  그리고  $W_1$ 을 출력하는 과정과 ,

(b) 상기 정보 비트 **A** 그리고 **B**를 CTC 인터리버를 이용하여 정보 비트 **C** 그리고 **D**를 얻기 위해 인터리빙하고, 인터리빙한 정보 비트 **C** 그리고 **D**를 상기 컨스티튜언트 인코더를 이용하여 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 얻기 위해 인코딩하는 과정과 ,

(c) 상기 정보 비트 **A** 그리고 **B**, 상기 패리티 시퀀스  $Y_1$  그리고  $W_1$  , 상기 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 각각 인터리빙하는 과정과, 여기서 정보 비트 **A** 그리고 **B**를 포함하는 비트 그룹, 시퀀스  $Y_1$  그리고  $W_1$ 을 포함하는 비트 그룹, 시퀀스  $Y_2$  그리고  $W_2$ 를 포함하는 비트 그룹 중 적어도 하나의 비트 그룹에 포함되어 있는 비트는 높은 안정도 및 낮은 안정도를 가지는 성상도 포인트(constellation points)의 비트 중 하나의 비트에 매핑된다.

(d) 인코딩된 비트 시퀀스를 얻기 위해 인터리빙 결과를 평처링(puncturing)하는 과정을 포함하는 것을 특징으로 하는 방법.

### 청구항 2

제 1항에 있어서,

상기 c) 과정에서, 상기 비트 그룹의 하나의 시퀀스에서의 비트와 다른 시퀀스에서의 해당 비트는 높은 안정도 및 낮은 안정도를 가지는 성상도 포인트(constellation points)의 비트 중 하나의 비트에 매핑되는 것을 특징으로 하는 방법.

### 청구항 3

CTC(Convolutional Turbo Coding)를 위한 장치에 있어서,

정보 비트 **A** 그리고 **B**를 인코딩하고, 패리티 시퀀스  $Y_1$  그리고  $W_1$ 을 출력하는 컨스티튜언트 인코더(consituent encoder)와,

새로운 정보 비트 **C** 그리고 **D**를 얻기 위해 상기 정보 비트 **A** 그리고 **B**를 인터리빙하고, 인터리빙한 정보 비트 **C** 그리고 **D**를, 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 얻기 위해 인코딩하는 상기 컨스티튜언트 인터리버에 제공하는 CTC 인터리버와,

상기 정보 비트 **A** 그리고 **B**, 상기 패리티 시퀀스  $Y_1$  그리고  $W_1$ , 상기 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 각각 인터리빙하는 인터리버와, 여기서, 정보 비트 **A** 그리고 **B**를 포함하는 비트 그룹, 시퀀스  $Y_1$  그리고  $W_1$ 을 포함하는 비트 그룹, 시퀀스  $Y_2$  그리고  $W_2$ 를 포함하는 비트 그룹 중 적어도 하나의 비트 그룹에 포함되어 있는 비트는 높은 안정도 및 낮은 안정도를 가지는 성상도 포인트(constellation points)의 비트 중 하나의 비트에 매핑된다.

인코딩된 비트 시퀀스를 얻기 위해 상기 인터리버로부터의 출력 시퀀스를 평처링(puncturing)하는 평처링(puncturing)을 포함하는 것을 특징으로 하는 장치.

### 청구항 4

제 3항에 있어서,

상기 인터리버는 상기 비트 그룹의 하나의 시퀀스에서의 비트와 다른 시퀀스에서의 해당 비트를 높은 안정도 및 낮은 안정도를 가지는 성상도 포인트(constellation points)의 비트 중 하나의 비트에 매핑하는 것을 특징으로 하는 장치.

## 청구항 5

터보 인코더를 위한 장치에 있어서,

인터리빙된 정보 서브블록 A와,

인터리빙된 정보 서브블록 B와, 여기서 정보 서브블록 A와 B는 바이패스됨(by-passed).

인터리빙된  $Y_1$  그리고  $Y_2$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스와, 상기 인터리빙된  $Y_1$  그리고  $Y_2$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스는,  $Y_1$  서브블록 인터리버로부터의 제 1 출력 비트,  $Y_2$  서브블록 인터리버로부터의 제 1 출력 비트,  $Y_1$  서브블록 인터리버로부터의 제 2 출력 비트 그리고  $Y_2$  서브블록 인터리버로부터의 제 2 출력 비트를 포함함.

인터리빙된  $W_2$  그리고  $W_1$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스를 포함하는 것을 특징으로 하는 장치.

상기 인터리빙된  $W_2$  그리고  $W_1$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스는  $W_2$  서브블록 인터리버로부터의 제 1 출력 비트,  $W_1$  서브블록 인터리버로부터의 제 1 출력 비트,  $W_2$  서브블록 인터리버로부터의 제 2 출력 비트 그리고  $W_1$  서브블록 인터리버로부터의 제 2 출력 비트를 포함함.

## 명세서

### 발명의 상세한 설명

#### 기술 분야

[0001]

본 발명은 무선 이동 통신 시스템에서 코딩 방법에 관한 것으로, 특히, 본 발명은 콘볼루셔널 터보 코딩 방법 및 상기 방법을 구현하기 위한 장치에 관한 것이다.

#### 배경 기술

[0002]

모바일 와이맥스(WiMAX: Worldwide Interoperability for Microwave Access)는 유선 모드를 대신하는 무선 모드를 이용하여 "last kilometer" 억세스를 구현하는 광대역 접속 기술이다.

[0003]

상기 접속 기술은 이동 장치에 고정된 광대역 네트워크와 포함한다 그리고 편리하고 고속의 광대역 이동 연결을 광대역 무선 접속 기술과 유연한 네트워크 구조를 이용하여 제공한다.

[0004]

상기 와이맥스 기술은 IEEE(Institute of Electrical and Electronics Engineers) 802.16 표준에 그 기초를 둔다. 그리고 상기 IEEE 802.16 표준은 마이크로웨이브 및 밀리미터웨이브 주파수 밴드를 위해 제안되어 있다.

[0005]

이동 와이맥스 표준은 IEEE 802.16d 고정 와이맥스 기술이 제안된 이후에 제안되었다. 상기 이동 와이맥스는 상기 고정 와이맥스 표준의 표준화 과정 동안에 시작된 연구를 집대성함으로써 광대역 억세스의 이동성 제공을 그 목표로 한다.

[0006]

콘볼루셔널 터보 코드(CTC: Convolutional Turbo Code)는 몇가지 콘볼루션 코딩 방식을 이용하는 터보 코드 중의 한 클래스이다. 상기 CTC는 높은 오류 정정 능력으로 인해 IEEE 802.16 과 DVB-RCS(Digital Video Broadcasting - Return Channel via Satellite) 표준에 포함되어 있다.

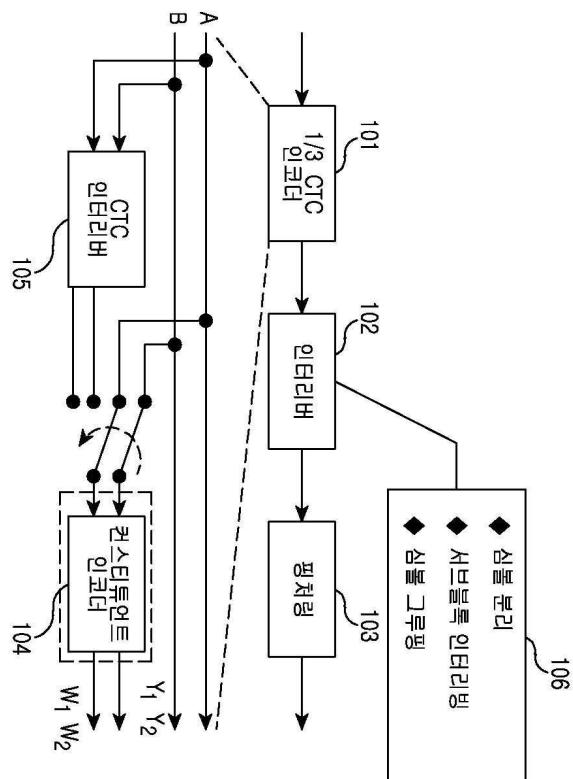

- [0007] 도 1은 연관 기술에 따른 CTC 인코더를 도시한 도면이다.

- [0008] 도 1에 도시된 바와 같이, 상기 CTC 인코더는 1/3 인코더(101), 인터리버(102), 평처링(puncturing)(103)을 포함하여 구성된다.

- [0009] 입력 정보 비트는 상기 1/3 인코더(101)에 입력된다. 여기서, 인코딩된 출력 정보 비트 및 패리티 비트의 수는 정보 비트 수의 3배이다. 인코딩된 데이터는 상기 인터리버(102)에 의해 인터리빙된다. 상기 평처링(103)은 상기 인터리빙한 데이터를 전송률을 기반으로 평처링한다. 상기 전송률에서, 상기 평처링(103)은 전송할 데이터 비트를 선택하고, 인코딩된 비트 시퀀스를 인코딩 프로세스를 마치기 위해서 획득한다.

- [0010] 더욱 자세하게는, 1/3 CTC 인코더(101)에서, 듀오 바이너리 CRSC(Circular Recursive Systematic Convolutional) 코드가 사용된다. 상기 도 1에서 도시된 바와 같이, 1/3 CTC 인코더(101)는 CTC 인터리버(105) 및 컨스티튜언트 인코더(constituent encoder)(104)를 포함할 수 있다.

- [0011] 여기서, 상기 CTC 인터리버(105)에 대한 **A** 및 **B** 입력은 두 번 인코딩된 입력 정보 비트를 나타낸다. 첫 번째로, 듀오 바이너리 CRSC 코딩이 정보 비트 **A** 및 **B**에 대해 수행된다.

- [0012] 즉, 정보 비트  $A_i$  그리고  $B_i$ 의 집합아 동시에 상기 컨스티튜언트 인코더(104)에 인코딩을 위해 입력된다. 그리고 패리티 시퀀스  $Y_1$  그리고  $W_1$ 가 획득된다. 상기 정보비트 **A** 및 **B** 또한, 상기 CTC 인터리버(105)에 의해 인터리빙된다.

- [0013] 이후, 상기 2번째 컨스티튜언트 인코딩 프로세스가 인터리빙된 시퀀스에 대해 수행된다. 즉, 인터리빙된 정보 비트  $A_j$  그리고  $B_j$ 는 동시에 상기 컨스티튜언트 인코더(104)에 페리티 시퀀스  $Y_2$  그리고  $W_2$ 를 얻기 위해 입력된다.

- [0014] 각각의 코드 블록은 상기 컨스티튜언트 인코더(104)에 입력되고,  $k$  정보 비트 또는 정보 비트의  $N$  쌍을 포함한다. 여기서,  $k=2xN$ 이고,  $K$ 는 8의 배수, 그리고  $N$ 은 4의 배수이다. 그리고,  $32 \leq N \leq 4096$ 이다.

- [0015] 블록(106)에 도시된 바와 같이, 상기 인터리버(102)는 심볼 분리 모듈, 서브블록 인터리빙 모듈, 심볼 그루핑 모듈을 포함할 수 있다. 상기 심볼 분리 모듈은 상기 정보 비트 및 6 서브블록에 대해 인코딩된 비트를 할당하기 위해 사용된다. 상기 6 서브블록은 전술한 바와 같이, 차례로,  $A, B, Y_1, Y_2, W_1$  그리고  $W_2$ 이다.

- [0016] 상기 서브 블록 인터리빙 모듈은 이러한 6 서브블록을, 각 서브블록 내에서, 인터리빙하기 위해 사용된다. 인터리빙 순서는 각 서브 블록에 대해 같다. 블록들( $A, B, Y_1, Y_2, W_1$  그리고  $W_2$ )각각에 대해 서브블록 인터리빙이 수행된 후에, 획득된 비트 시퀀스를  $A', B', Y'_1, Y'_2, W'_1$  그리고  $W'_2$ 라고 표시하기로 가정하자 그러면,  $A', B', Y'_1, Y'_2, W'_1, W'_2 = A'_0, A'_1, \dots, A'_{N-1}; B'_0, B'_1, \dots, B'_{N-1}; Y'_{1,0}, Y'_{1,1}, \dots, Y'_{1,N-1}; Y'_{2,0}, Y'_{2,1}, \dots, Y'_{2,N-1}; W'_{1,0}, W'_{1,1}, \dots, W'_{1,N-1}; W'_{2,0}, W'_{2,1}, \dots, W'_{2,N-1}$ 과 같다.

- [0017]

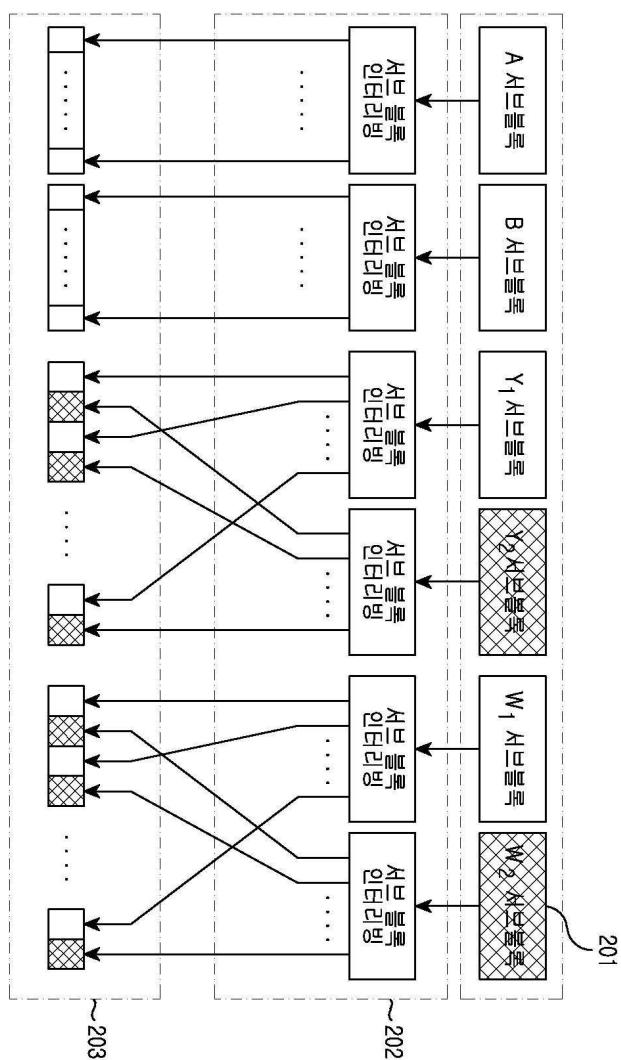

- [0018] 도 2는 연관 기술에 따른 서브 블록 인터리빙 동작을 도시한 도면이다.

- [0019] 상기 도 2를 참조하면, 심볼 분리 모듈은 인코딩된 비트를 서브블록( $A, B, Y_1, Y_2, W_1$  그리고  $W_2$ )으로 분리한다(201 단계), .

- [0020] 인터리빙하는 서브블록은 서브블록( $A, B, Y_1, Y_2, W_1$  그리고  $W_2$ )에 대해 서브블록 연산을 수행한다(202 단계) 그리고 서브블록 그루핑 모듈은 인터리빙된 서브블록을 그룹화한다(203 단계).

- [0021] 여기서, 서브블록  $A$  와  $B$ 는 상기 서브블록 그루핑 모듈의 출력 값이다. 그리고 2개의 서브블록( $Y_1$  그리고  $Y_2$ ) 그리고 2개의 서브블록( $W_1$  그리고  $W_2$ )은 선택적으로 출력되는 출력 값이다. 심볼 그루핑 이후, 출력 시퀀스는  $A'_0, A'_1, \dots, A'_{N-1}; B'_0, B'_1, \dots, B'_{N-1}; Y'_{1,0}, Y'_{1,1}, \dots, Y'_{1,N-1}; Y'_{2,0}, Y'_{2,1}, \dots, Y'_{2,N-1}; W'_{1,0}, W'_{1,1}, \dots, W'_{1,N-1}; W'_{2,0}, W'_{2,1}, \dots, W'_{2,N-1}$ 과 같다.

- [0022] 연관 기술에서의 CTC에서, 고 수준의 변조에서의 비트 안정도는 고려되지 않는다. 여기서, 상기 안정도는 성상

도 상에서 0으로 표시되는 포인트 와 1로 표시되는 포인트 상의 평균 거리를 참조한다. 상기 거리가 길수록, 매핑된 비트의 안정도는 더 커진다.

[0023] 이동 통신 시스템에서, 대역폭의 증가 없이 데이터 전송률을 높이기 위해서는, M-QAM(M-order Quadrature Amplitude Modulation) 기술이 적용될 수 있다. 그러나, 고 수준의 변조는 오류 방지 변조와는 동일하지 않다. M>4 의 경우, M-QAM 심볼에 매핑되는 해당 비트는 서로 다른 BER(Bit Error Rates)을 가진다.

[0024] 성상도 상에서 내부의 포인트(Inner points of the constellation)는 에너지를 덜 가지고 있고 쉽게 페이딩된다. 따라서, 이러한 심볼들을 컨스티튜잉(consituting)하는 것은 덜 안정적이다. 대조적으로, 상기 성상도 상에서 외부의 포인트(points outside the constellation)는 보다 더 안정적이다.

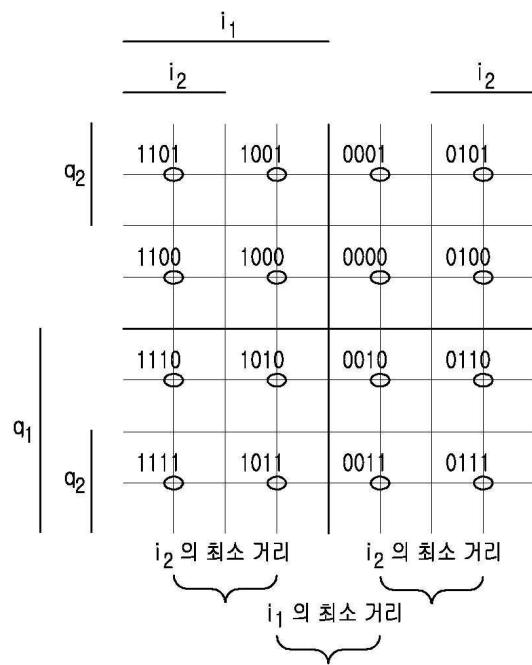

[0025] 도 3은 연관 기술에 따른 고 수준 변조의 비트 매핑 안정도를 도시한 도면이다.

[0026] 상기 도 3을 참조하면, 비트들의 매핑 순서는  $i_1 i_2 q_1 q_2$ 이고, 여기서  $i_1=0$  그리고  $i_1=1$ 에 대해서는 성상도 상에서 오른쪽 절반 플레인 및 왼쪽 절반 플레인에서의 각각의 포인트에 해당한다 그리고  $i_2=0$  그리고  $i_2=1$ 에 대해서는 성상도 상에서 중간 및 양쪽 사이드에 해당한다.

[0027] 이러한 방식으로,  $i_1=1$ ,  $i_1=0$ 에 대한 성상도 포인트 사이의 평균 거리는  $i_2$ 에 해당하는 그것보다 길다. 따라서, 수신단에서의  $i_1$ 는  $i_2$ 보다 더 안정도가 높다.

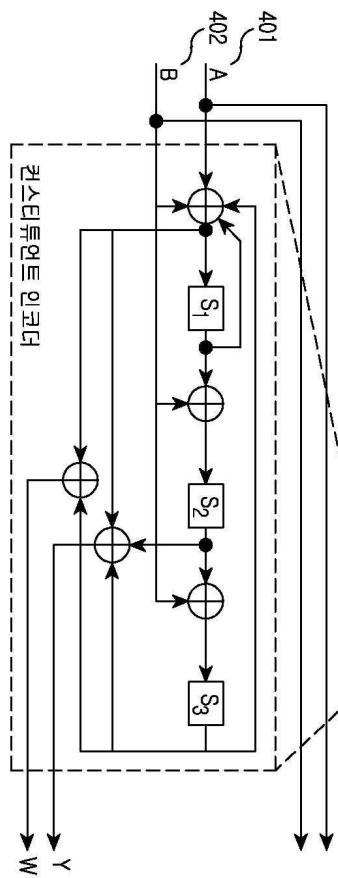

[0028] 도 4는 연관 기술에 따른 듀오 이진 CRSC 코딩을 구현하는 1/3CTC 인코더의 컨스티튜언트 인코더를 도시한 도면이다.

[0029] 상기 도 4를 참조하면, 입력 비트  $A_i$  (401) 및  $B_i$  (402) 는 1/3 CTC 인코더에 대한 입력 집합으로 사용된다 그리고 패리티 비트( $Y_i$  그리고  $W_i$ )는 정보 비트  $A_i$  와  $B_i$  의 병합 정보를 임바디(embody)한다.

[0030] 이러한 형태의 듀오 바이너리 코딩에서, 비트( $A_i$ ,  $B_i$ )는 전체로 고려되고 그룹 유니트처럼 다루어진다. 연관 기술의 CTC 의 설계에서, 만약, 비트  $A_i$  가 높은 신뢰도의 비트에 매핑된 경우, 비트  $B_i$  또한 높은 신뢰도의 비트에 매핑된다.

[0031] 추가적으로, 만약, 비트  $A_i$  가 낮은 신뢰도의 비트에 매핑된 경우, 상기 컨스티튜언트 인코더에 동시에 입력되는 시퀀스 A에서의 정보 비트 및 시퀀스 B에서의 정보 비트는 비트 그룹을 구성한다고 말해질 수 있다.

[0032] 따라서, 그룹 유니트( $A_i, B_i$ )의 관점에서, 서로 다른 그룹 유니트는 비트 안정도에서 동등하지 않다. 어떠한 그룹 유니트는 높은 안정도를 가지는 반면에 어떤 그룹 유니트는 낮은 안정도를 가진다.

[0033] 따라서, 연관 기술에서 비트 매핑에 대해  $A_i$  그리고  $B_i$  를 병합하는 것을 고려하지 않는 것은 문제가 있다. 추가적으로, 연관 기술에서 고 수준의 변조에서의 비트 안정도가 매핑 중에 고려되지 않는 것은 문제가 있다.

[0034]

### 발명의 내용

#### 해결 하고자하는 과제

[0035]

본 발명의 목적은 터보 코딩 방법 및 터보 코딩 방법을 구현하기 위한 장치를 제공함에 있다.

#### 과제 해결수단

[0036]

본 발명의 제 1 견지에 따르면, CTC 방법이 제공된다. 상기 CTC 방법은 컨스티튜언트 인코더(CTC constituent encoder)를 이용하여 정보 비트 A 그리고 B 를 인코딩하고, 패리티 시퀀스  $Y_1$  그리고  $W_1$ 을 출력하는 과정과 상기 정보 비트 A 그리고 B 를 CTC 인터리버를 이용하여 정보 비트 C 그리고 D 를 얻기 위해 인터리빙하고, 인터리빙된 정보 비트 C 그리고 D 를 디코딩하는 과정으로 구성된다.

리빙한 정보 비트 **C** 그리고 **D**를 상기 컨스티튜언트 인코더를 이용하여 패리티 시퀀스  $Y_2$  그리고  $W_2$ ; 를 얻기 위해 인코딩하는 과정과 상기 정보 비트 **A** 그리고 **B**, 상기 패리티 시퀀스  $Y_1$  그리고  $W_1$ , 상기 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 각각 인터리빙하는 과정과, 여기서 정보 비트 **A** 그리고 **B**를 포함하는 비트 그룹, 시퀀스  $Y_1$  그리고  $W_1$ 을 포함하는 비트 그룹, 시퀀스  $Y_2$  그리고  $W_2$ 를 포함하는 비트 그룹 중 적어도 하나의 비트 그룹에 포함되어 있는 비트는 높은 안정도 및 낮은 안정도를 가지는 성상도 포인트(constellation points)의 비트 중 하나의 비트에 매핑됨, 인코딩된 비트 시퀀스를 얻기 위해 인터리빙 결과를 평처링(puncturing)하는 과정을 포함하는 것을 특징으로 한다.

[0037] 본 발명의 제 2 견지에 따르면, CTC를 위한 장치가 제공된다. 상기 CTC를 위한 장치는 정보 비트 **A** 그리고 **B**를 인코딩하고, 패리티 시퀀스  $Y_1$  그리고  $W_1$ 을 출력하는 컨스티튜언트 인코더(consituent encoder)와, 새로운 정보 비트 **C** 그리고 **D**를 얻기 위해 상기 정보 비트 **A** 그리고 **B**를 인터리빙하고, 인터리빙한 정보 비트 **C** 그리고 **D**를, 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 얻기 위해 인코딩하는 상기 컨스티튜언트 인터리버에 제공하는 CTC 인터리버와, 상기 정보 비트 **A** 그리고 **B**, 상기 패리티 시퀀스  $Y_1$  그리고  $W_1$ , 상기 패리티 시퀀스  $Y_2$  그리고  $W_2$ 를 각각 인터리빙하는 인터리버와, 여기서 정보 비트 **A** 그리고 **B**를 포함하는 비트 그룹, 시퀀스  $Y_1$  그리고  $W_1$ 을 포함하는 비트 그룹, 시퀀스  $Y_2$  그리고  $W_2$ 를 포함하는 비트 그룹 중 적어도 하나의 비트 그룹에 포함되어 있는 비트는 높은 안정도 및 낮은 안정도를 가지는 성상도 포인트(constellation points)의 비트 중 하나의 비트에 매핑됨, 인코딩된 비트 시퀀스를 얻기 위해 상기 인터리버로부터의 출력 시퀀스를 평처링(puncturing)하는 평처링 유니트(puncturing unit)를 포함하는 것을 특징으로 한다.

[0038] 본 발명의 제 3 견지에 따르면, 인터리빙된 정보 서브블록 **A**와, 인터리빙된 정보 서브블록 **B**와, 여기서 정보 서브블록 **A** 와 **B**는 바이패스됨(by-passed), 인터리빙된  $Y_1$  그리고  $Y_2$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스와, 상기 인터리빙된  $Y_1$  그리고  $Y_2$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스는  $Y_1$  서브블록 인터리버로부터의 제 1 출력 비트,  $Y_2$  서브블록 인터리버로부터의 제 1 출력 비트,  $Y_1$  서브블록 인터리버로부터의 제 2 출력 비트 그리고  $Y_2$  서브블록 인터리버로부터의 제 2 출력 비트를 포함함, 인터리빙된  $W_2$  그리고  $W_1$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스를 포함하는 것을 특징으로 한다. 상기 인터리빙된  $W_2$  그리고  $W_1$  서브블록 시퀀스의 비트 바이 비트(bit by bit)가 멀티플렉싱된 패리티 시퀀스는  $W_2$  서브블록 인터리버로부터의 제 1 출력 비트,  $W_1$  서브블록 인터리버로부터의 제 1 출력 비트,  $W_2$  서브블록 인터리버로부터의 제 2 출력 비트 그리고  $W_1$  서브블록 인터리버로부터의 제 2 출력 비트를 포함한다.

[0039] 본 발명의 제 4 견지에 따르면,  $A_i$  그리고  $B_i$  가 비트 매핑을 위해 병합된다. 추가적으로, 고 수준의 변조에서 비트 안정도는 매핑과정에서 고려된다 따라서 코딩의 안정도가 개선된다.

## 효과

[0040] 본 발명은 고 수준 변조에서의 비트 안정도가 매핑 중에 고려되기 때문에 효율 또는 성능이 높은 이점이 있다.

## 발명의 실시를 위한 구체적인 내용

[0041] 이하 본 발명의 바람직한 실시 예를 첨부된 도면의 참조와 함께 상세히 설명한다. 그리고, 본 발명을 설명함에 있어서, 관련된 공지기능 혹은 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단된 경우 그 상세한 설명은 생략한다.

[0042] 이하, 본 발명은 터보 코딩 방법 및 터보 코딩 방법을 구현하기 위한 장치에 대해 설명할 것이다.

[0043] 본 발명의 실시 예는 도 1에 도시된 CTC(the Convolutional Turbo Code)의 인터리버(102)와 같은 심볼 그루핑 모듈의 개선을 제공한다. 이하에서, 인터리버에서 서브블록 인터리빙 모듈로부터의 출력은 시퀀스

$(A', B', Y'_1, Y'_2, W'_1)$  그리고  $W'_2$ )라고 가정한다.

[0044] 본 발명의 실시 예의 방식에 따라, 시퀀스  $A'$ 는 첫 번째로 매핑된다. 이후, 시퀀스  $A'$ 에서의 각각의 비트와 함께 동시에 CTC 인코더에 입력되는 시퀀스  $B'$ 에서의 해당 비트가 발견된다.  $A'_{i,j}$ 와 함께 동시에 상기 CTC 인코더에 입력되는 비트는  $B'_{j,i}$ 라고 나타낸다.  $B'_{j,i}$ 는  $A'_{i,j}$ 의 비트에 해당하는 그룹 유니트로서 참조된다. 이후, 시퀀스  $B'$ 는 매핑된다.

[0045] 만약,  $A'_{i,j}$ 가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $B'_{j,i}$ 는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약,  $A'_{i,j}$ 가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $B'_{j,i}$ 는 높은 안정도를 가지는 비트에 매핑된다.

[0046] 추가적으로, 제 2 실시 예의 방식에 따르면, 시퀀스  $Y'_1$ 는 첫 번째로 매핑된다. 이후, 시퀀스  $Y'_1$ 에서의 각각의 비트와 함께 동시에 CTC 인코더로부터 출력되는 시퀀스  $W'_1$ 에서의 해당 비트가 발견된다. 상기 CTC 인코더로부터 출력된 패리티 비트는  $Y'_{1,i}$ 과 함께 같이  $W'_{1,j}$ 로 나타낸다.  $W'_{1,j}$ 는  $Y'_{1,i}$ 의 비트에 해당하는 그룹 유니트로서 참조된다. 이후, 시퀀스  $W'_1$ 이 매핑된다.

[0047] 만약,  $Y'_{1,i}$ 가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{1,j}$ 는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약,  $Y'_{1,i}$ 가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{1,j}$ 는 높은 안정도를 가지는 비트에 매핑된다. 컨스티튜언트 인코더로부터 출력되는 시퀀스  $Y'_1$ 에서의 패리티 비트와 시퀀스  $W'_1$ 에서의 비트는 하나의 비트 그룹을 형성한다.

[0048] 더욱이, 본 발명의 제 3 실시 예의 방식에 따르면, 시퀀스  $Y'_2$ 가 첫 번째로 매핑된다. 이후, 시퀀스  $Y'_2$ 에서의 각각의 비트와 함께 동시에 CTC 인코더로부터 출력되는 시퀀스  $W'_2$ 에서의 해당 비트가 발견된다. 상기 CTC 인코더로부터 출력된 패리티 비트는  $Y'_{2,i}$ 과 함께 같이  $W'_{2,j}$ 로 나타낸다.  $W'_{2,j}$ 는  $Y'_{2,i}$ 의 비트에 해당하는 그룹 유니트로서 참조된다. 이후, 시퀀스  $W'_2$ 이 매핑된다.

[0049] 만약,  $Y'_{2,i}$ 가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{2,j}$ 는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약,  $Y'_{2,i}$ 가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{2,j}$ 는 높은 안정도를 가지는 비트에 매핑된다. 컨스티튜언트 인코더로부터 출력되는 시퀀스  $Y'_2$ 에서의 패리티 비트와 시퀀스  $W'_2$ 에서의 비트는 하나의 비트 그룹을 형성한다.

[0050] 상기 3 개의 실시 예의 방식은 3 개 중 어떠한 2 개를 병합하거나, 또는 상기 3개를 모두 병합함으로써 독립적으로 구현될 수 있다. 모의 실험의 결과에 따라, 가장 작은 성능 계인은 2 번째 또는 3 번째 방식만을 적용함으로써 얻어진다. 만약, 상기 2 번째 또는 3 번째 스킵이 모두 적용되는 경우, 성능 이득 증가는 조금이다.

[0051] 만약, 상기 1 번째 스킵만이 적용된다면, 성능은 상기 2 번째 및 상기 3 번째 스킵을 모두 적용함으로써 얻어진 것에 비해 월등하다. 만약, 상기 1 번째, 2 번째, 그리고 3 번째 스킵이 적용된다면, 가장 좋은 성능이 일반적으로 얻어진다. IEEE 8-2.16e 구현 표준을 기반으로, 본 발명의 실시 예에 따른 서브블록 인터리빙 동작은 하기에서 설명될 도 5를 참조하여 설명될 것이다.

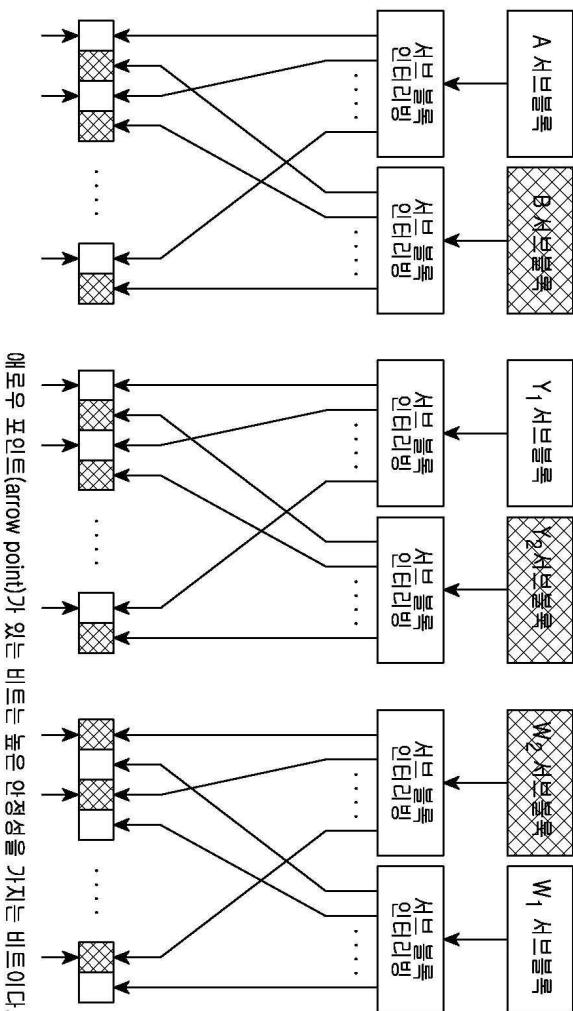

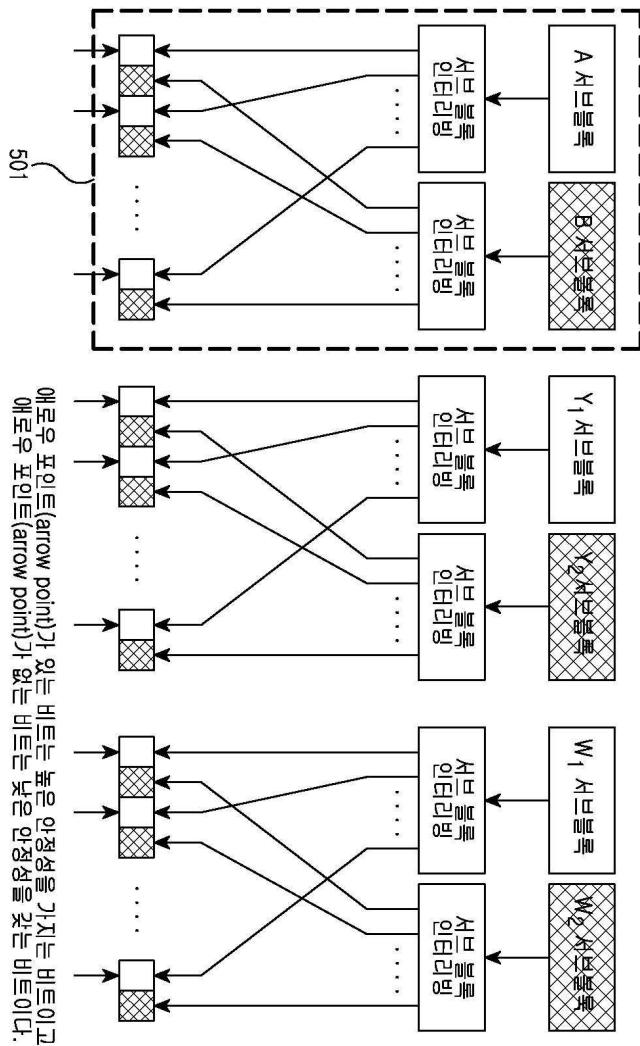

[0052] 도 5는 본 발명의 제 1 실시 예에 따른 리매핑 동작을 도시한 도면이다.

[0053] 상기 도 5에서, 인터리버에서 서브 블록 인터리빙 모듈로부터의 출력들은 시퀀스  $(A', B', Y'_1, Y'_2, W'_1, W'_2)$ 라고 가정한다.

[0054] 여기서,  $A', B', Y'_1, Y'_2, W'_1, W'_2$ 는  $A'_0, A'_1, \dots, A'_{N-1}; B'_0, B'_1, \dots, B'_{N-1}; Y'_{1,0}, Y'_{1,1}, \dots, Y'_{1,N-1}; Y'_{2,0}, Y'_{2,1}, \dots, Y'_{2,N-1}; W'_{1,0}, W'_{1,1}, \dots, W'_{1,N-1}; W'_{2,0}, W'_{2,1}, \dots, W'_{2,N-1}$ 와 같이 정렬된다.

[0055] 상기 도 5를 참조하면, 블록 501에 도시된 바와 같이, 시퀀스  $A'$ 가 첫 번째로 매핑된다.

[0056] IEEE 802.16e 표준을 기반으로,  $A'$ 와 함께 동시에 CTC 인코더에 입력되는 시퀀스  $B'$ 에서의 해당 비트는  $B'_{i,j}$ 이

다. 이후, 시퀀스  $B'$ 가 매핑된다.

[0057] 만약,  $A'_{i_1}$  가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $B'_{i_1}$  는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약,  $A'_{i_1}$  가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $B'_{i_1}$  는 높은 안정도를 가지는 비트에 매핑된다.

[0058] 물론, 상기의 동작은 시퀀스  $Y'_{1,i}$  그리고  $W'_{1,i}$ 로 구성된 비트 그룹에도 수행된다 그리고 시퀀스  $Y'_{2,i}$  그리고  $W'_{2,i}$ 로 구성된 비트 그룹에도 각각 수행된다.

[0059]

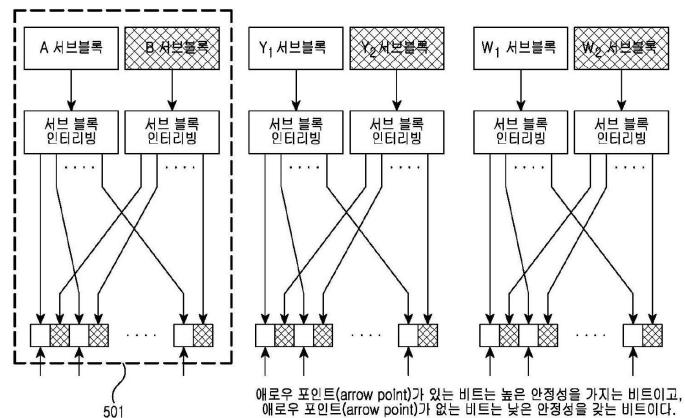

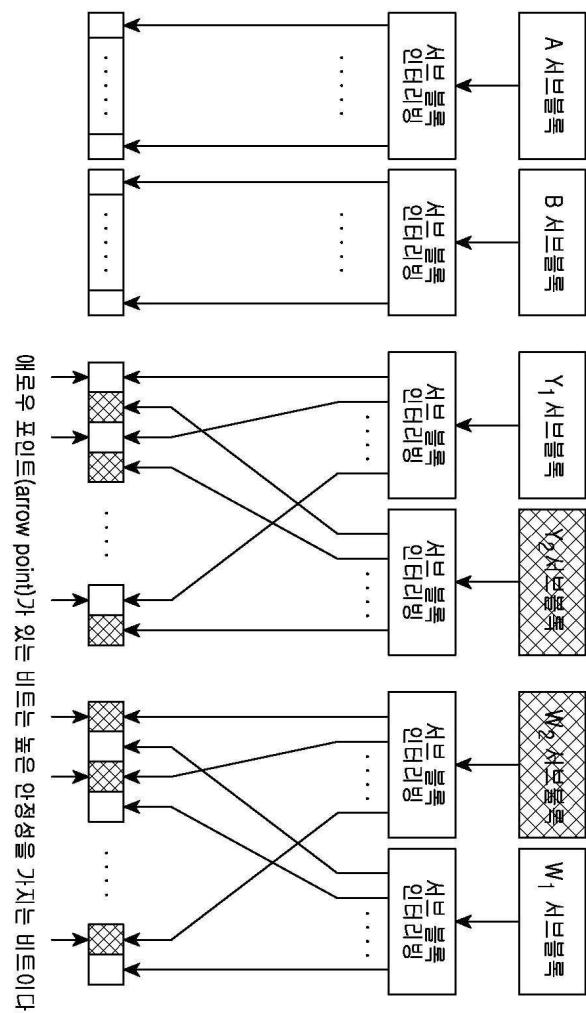

도 6은 본 발명의 제 2 실시 예에 따른 리매핑 동작을 도시한 도면이다.

[0060]

상기 도 6을 참조하면, 시퀀스  $Y'_{1,i}$ 가 첫 번째로 매핑된다. IEEE 802.16e 표준에서,  $Y'_{1,i}$  와 함께 동시에 인코더로부터 출력되는 패리티 비트는  $W'_{1,i}$  이다. 이후,  $W'_{1,i}$ 가 매핑된다.

[0061]

만약,  $Y'_{1,i}$ 가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{1,i}$  는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약,  $Y'_{1,i}$ 가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{1,i}$ 는 높은 안정도를 가지는 비트에 매핑된다. 이후,  $W'_{1,i}$ 가 매핑된다.

[0062]

IEEE 802.16e 표준을 기반으로,  $Y'_{2,i}$ 와 함께 동시에 CTC 인코더로부터 출력되는 패리티 비트는  $W'_{2,i}$ 이다. 이후,  $W'_{2,i}$ 가 매핑된다.

[0063]

만약,  $Y'_{2,i}$ 가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{2,i}$ 는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약,  $Y'_{2,i}$ 가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{2,i}$ 는 높은 안정도를 가지는 비트에 매핑된다.

[0064]

물론, 울터너트 매핑(alternate mapping)의 동작은 시퀀스  $A'$  그리고  $B'$ 로 구성된 비트 그룹에서의 비트에 대해 첫 번째로 수행된다 이후, 시퀀스  $Y'_{1,i}$  그리고  $W'_{1,i}$ 로 구성된 비트 그룹에서의 비트에 대해 수행되거나 시퀀스  $Y'_{2,i}$  그리고  $W'_{2,i}$ 로 구성된 비트 그룹에서의 비트에 대해 각각 수행된다.

[0065]

본 발명의 제 1 및 제 2 실시 예를 병합하는 본 발명의 제 3 실시 예는 하기 도 7을 참조로 하여 설명될 것이다.

[0066]

도 7은 본 발명의 제 3 실시 예에 따른 리매핑 동작을 도시한 도면이다.

[0067]

상기 도 7을 참조하면, 시퀀스  $A'$ 가 첫 번째로 매핑된다.  $A'_{i_1}$  와 함께 동시에 CTC 인코더에 입력되는 시퀀스  $B'$ 에서의 해당 비트는  $B'_{i_1}$ 이다. 이후, 시퀀스  $B'$ 가 매핑된다.

[0068]

만약,  $A'_{i_1}$ 가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $B'_{i_1}$ 는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약,  $A'_{i_1}$ 가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $B'_{i_1}$ 는 높은 안정도를 가지는 비트에 매핑된다. 추가적으로, 도 7에 도시된 바와 같이, 시퀀스  $Y'_{1,i}$ 가 매핑된다.

[0069]

IEEE 802.16e 표준에서,  $Y'_{1,i}$  과 함께 동시에 상기 CTC 인코더로부터 출력된 패리티 비트는  $W'_{1,i}$ 로 나타낸다. 이후, 시퀀스  $W'_{1,i}$ 가 매핑된다.

[0070]

만약,  $Y'_{1,i}$  가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{1,i}$  는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약  $Y'_{1,i}$  가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{1,i}$  는 높은 안정도를 가지는 비트에 매핑된다. 이후, 시퀀스  $Y'_{2,i}$ 가 매핑된다.

[0071]

IEEE 802.16e 표준에서,  $Y'_{2,i}$  과 함께 동시에 상기 CTC 인코더로부터 출력된 패리티 비트는  $W'_{2,i}$ 로 나타낸다.

이후, 시퀀스  $W'_2$  이 매핑된다.

[0074] 만약,  $Y'_{2,i}$  가 높은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{2,i}$  는 낮은 안정도를 가지는 비트에 매핑된다. 또한, 만약  $Y'_{2,i}$  가 낮은 안정도를 가지는 비트에 매핑된다면, 그것의 그룹 유니트 해당 비트  $W'_{2,i}$  는 높은 안정도를 가지는 비트에 매핑된다.

[0075] 상기 도 7에서, 높은 안정도를 가지는 비트는 애로우 포인트(arrows point)에 대한 비트에 의해 지시된다. 만약, 상기 도 7에 도시된 바와 같이 높은 안정도를 가지는 비트가 홀수(odd number)비트이고, 낮은 안정도를 가지는 비트가 짝수(even number) 비트인 경우, 출력 시퀀스는  $A'_0, A'_1, \dots, A'_{N-1}; B'_1, B'_0, \dots, B'_{N-1}, B'_{N-2}; Y'_{1,0}, Y'_{2,0}, Y'_{1,1}, Y'_{2,1}, \dots, Y'_{1,N-1}, Y'_{2,N-1}; W'_{2,0}, W'_{1,0}, W'_{2,1}, W'_{1,1}, \dots, W'_{2,N-1}, W'_{1,N-1}$ . 과 같다.

[0076]

[0077] 한편 본 발명의 상세한 설명에서는 구체적인 실시 예에 관해 설명하였으나, 본 발명의 범위에서 벗어나지 않는 한도 내에서 여러 가지 변형이 가능함은 물론이다. 그러므로 본 발명의 범위는 설명된 실시 예에 국한되어 정해져서는 아니 되며 후술하는 특허청구의 범위뿐만 아니라 이 특허청구의 범위와 균등한 것들에 의해 정해져야 한다.

### 도면의 간단한 설명

[0078] 도 1은 연관 기술에 따른 CTC 인코더를 도시한 도면,

[0079] 도 2는 연관 기술에 따른 서브 블록 인터리방 동작을 도시한 도면,

[0080] 도 3은 연관 기술에 따른 고 수준 변조의 비트 매핑 안정도를 도시한 도면,

[0081] 도 4는 연관 기술에 따른 듀오 이진 CRSC 코딩을 구현하는 1/3CTC 인코더의 컨스티튜언트 인코더를 도시한 도면,

[0082] 도 5는 본 발명의 제 1 실시 예에 따른 리매핑 동작을 도시한 도면,

[0083] 도 6은 본 발명의 제 2 실시 예에 따른 리매핑 동작을 도시한 도면, 및,

[0084] 도 7은 본 발명의 제 3 실시 예에 따른 리매핑 동작을 도시한 도면.

도면

도면1

도면2

도면3

도면4

## 도면5

501

애로우 포인트(arrow point)가 있는 비트는 높은 안정성을 가지는 비트이고,

애로우 포인트(arrow point)가 없는 비트는 낮은 안정성을 갖는 비트이다.

도면6

예로우 포인트(arrow point)가 있는 비트는 높은 안정성을 가지는 비트이다.

## 도면7