(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0138092

(43) 공개일자 2014년12월03일

(51) 국제특허분류(Int. Cl.)

*H01L 21/283* (2006.01) *H01L 21/3065* (2006.01)

(21) 출원번호 10-2014-0063362

(22) 출원일자 2014년05월26일

심사청구일자 없음

(30) 우선권주장

61/827,511 2013년05월24일 미국(US)

(71) 출원인

램 리씨치 코포레이션

미국 94538 캘리포니아주 프레몬트 쿠싱 파크웨이

4650

(72) 벌명자

찬드라쉐카 아난드

미국, 캘리포니아 94086, 썬니베일, 리드 애비뉴

1180, #11

구하 조이딥

미국, 캘리포니아 94506, 덴빌, 하스킨스 웬치 셀 64

(뒷면에 계속)

(74) 대리인

오세일

전체 청구항 수 : 총 62 항

(54) 발명의 명칭 3-차원적인 반도체 피쳐들에서의 보이드-프리한 텅스텐 충진을 위한 방법들 및 장치들

### (57) 요 약

텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법이 본 명세서에 개시된다. 어떤 실시예들에서, 상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 상기 구멍들을 통해 유체적으로 접근 가능한 (accessible) 복수의 내부 영역들을 가지는 복수의 피쳐 (feature) 들로 이어진다. 상기 방법 (뒷면에 계속)

대 표 도 - 도1a

은, 프로세싱 챔버로 3-D 구조물을 가지는 기판을 제공하는 단계; 상기 텅스텐-함유 재료의 제1 층이 부분적으로 상기 3-D 구조물의 상기 복수의 내부 영역들을 충진하도록, 상기 3-D 구조물 내에 상기 텅스텐-함유 재료의 제1 층을 증착하는 단계; 그 후의 수직적으로 에칭하는 단계 및 수평적으로 에칭하는 단계; 상기 텅스텐-함유 재료의 제2 층이 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 내부 영역들의 적어도 일부를 충진하도록, 수직적으로 그리고 수평적으로 에칭한 후에 상기 3-D 구조물 내에 상기 텅스텐-함유 재료의 상기 제2 층을 증착하는 단계를 포함한다. 상기 수직적으로 에칭하는 단계는 상기 복수의 내부 영역들로부터 상기 제1 층의 부분을 실질적으로 제거하지 않고 제1 활성화된 에칭 재료를 사용하여 상기 측벽으로부터 상기 제1 층의 부분을 제거하는 단계를 포함할 수도 있고, 상기 수평적으로 에칭하는 단계는 제2 활성화된 에칭 재료를 사용하여 상기 복수의 내부 영역들로부터 상기 제1 층의 부분을 제거하는 단계를 포함할 수도 있다.

(72) 발명자

후마윤 라쉬나

미국, 캘리포니아 94539, 프레몬트, 노다웨이 에비

뉴 784

시양 후아

미국, 캘리포니아 94588, 플레젤톤, 산 조르지오

코트 4057

## 특허청구의 범위

### 청구항 1

텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법으로서,

상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 상기 구멍들을 통해 유체적으로 접근 가능한 (accessible) 복수의 내부 영역들을 가지는 복수의 피쳐 (feature) 들로 이루어지며,

상기 방법은,

프로세싱 챔버로 3-D 구조물을 가지는 기판을 제공하는 단계;

상기 텅스텐-함유 재료의 제1 층이 부분적으로 상기 3-D 구조물의 상기 복수의 내부 영역들을 충진하도록, 상기 3-D 구조물 내에 상기 텅스텐-함유 재료의 제1 층을 증착하는 단계;

상기 텅스텐-함유 재료의 상기 제1 층을 증착한 후에 수직적으로 에칭하는 단계로서, 상기 수직적으로 에칭하는 단계는 상기 복수의 내부 영역들로부터 상기 제1 층의 부분을 실질적으로 제거하지 않고 제1 활성화된 에칭 재료를 사용하여 상기 측벽으로부터 상기 제1 층의 부분을 제거하는 단계를 포함하는, 상기 수직적으로 에칭하는 단계;

상기 텅스텐-함유 재료의 상기 제1 층을 증착한 후에 수평적으로 에칭하는 단계로서, 상기 수평적으로 에칭하는 단계는 제2 활성화된 에칭 재료를 사용하여 상기 복수의 내부 영역들로부터 상기 제1 층의 부분을 제거하는 단계를 포함하는, 상기 수평적으로 에칭하는 단계; 및

상기 텅스텐-함유 재료의 제2 층이 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 내부 영역들의 적어도 일부를 충진하도록, 수직적으로 그리고 수평적으로 에칭한 후에 상기 3-D 구조물 내에 상기 텅스텐-함유 재료의 상기 제2 층을 증착하는 단계를 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 2

제1 항에 있어서,

상기 텅스텐-함유 재료의 상기 제1 층을 증착하는 단계와 상기 텅스텐-함유 재료의 상기 제2 층을 증착하는 단계 모두는 텅스텐-함유 전구체 (precursor) 및 환원제 (reducing agent) 간의 반응을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 3

제1 항에 있어서,

상기 제1 활성화된 에칭 재료는 이온 종들 (ion species) 을 포함하고,

상기 제2 활성화된 에칭 재료는 중성 종들 (neutral species) 을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 4

제3 항에 있어서,

상기 제2 활성화된 에칭 재료는 상기 3-D 구조물 내에서 상기 제1 활성화된 에칭 재료의 변환 (conversion) 으로부터 발생되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 5

제4 항에 있어서,

상기 제2 활성화된 에칭 재료로의 상기 제1 활성화된 에칭 재료의 변환은, 제1 활성화된 에칭 재료의 이온 종들이 1 이상의 전자들을 수용하여 제2 활성화된 에칭 재료의 중성 종들로 변환시키는 것을 포함하는, 텅스텐-함유

재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 6

제5 항에 있어서,

상기 이온 종들은  $NF_3$ ,  $CF_4$ ,  $CHF_3$ ,  $CH_2F_2$ , 및  $CH_3F$  중 1 이상의 이온화를 통해 상기 프로세싱 챔버 내에서 생성되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 7

제3 항에 있어서,

상기 제1 활성화된 에칭 재료는 상기 프로세싱 챔버 내에서 생성되는 이온 종들을 포함하는 플라즈마이고;

상기 수직적으로 에칭하는 단계는 상기 이온들의 일부분이 상기 3-D 구조물의 바닥을 향하여 지향되도록 (directed), 상기 이온 종들에 전자기장을 인가하는 단계를 포함하고; 그리고

상기 제2 활성화된 에칭 재료는 상기 프로세싱 챔버로부터 멀리 떨어져 생성되어 상기 프로세싱 챔버 내로 도입되는 자유 라디칼 종들 (free radical species) 을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 8

제7 항에 있어서,

상기 이온 종들은 불소를 포함하고; 그리고

상기 자유 라디칼 종들은 불소를 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 9

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 복수의 피쳐들의 적어도 일부는 서로 실질적으로 수직 정렬 (vertical alignment) 되어 적층되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 10

제9 항에 있어서,

상기 구조물은, 16 개 이상의, 서로 수직 정렬되어 수직적으로 적층된 피쳐들을 가지는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 11

제10 항에 있어서,

상기 구조물은, 64 개 이상의, 서로 수직 정렬되어 수직적으로 적층된 피쳐들을 가지는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 12

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 부분적으로 제조된 반도체 기판은 텅스텐 증착에 민감하고 (susceptible) 텅스텐-함유 재료의 상기 제1 층이 증착되는 외부 층을 더 포함하고,

상기 수직적으로 에칭하는 단계는 상기 3-D 구조물의 상기 층벽의 적어도 부분들 내의 상기 외부 층을 제거하여, 상기 텅스텐-함유 재료의 상기 제2 층의 후속하는 증착 동안 실질적으로 어떠한 텅스텐-함유 재료도 이러한 부분들 상에 증착되지 않는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 13**

제12 항에 있어서,

텅스텐 증착에 민감한 상기 외부 층은 금속 나이트라이드 (metal nitride) 를 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 14**

제13 항에 있어서,

상기 금속 나이트라이드는 티타늄 나이트라이드인, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 15**

제1 항 내지 제3항, 제7 항 및 제8 항 중 어느 한 항에 있어서,

상기 수직적으로 에칭하는 단계 이후, 그러나 상기 수평적으로 에칭하는 단계 이전에, 상기 복수의 내부 영역들의 상기 노출된 표면들의 적어도 부분들을 세정하는 단계를 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 16**

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 3-D 구조물을 가지는 상기 기판은, 상기 복수의 구멍들을 통해 상기 복수의 내부 영역들의 유체적 접근 가능성 (fluidic accessibility) 을 부분적으로 억제하는 복수의 폴리실리콘 필라 (polysilicon pillar) 들을 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 17**

제16 항에 있어서,

상기 폴리실리콘 필라들 간의 수평적 캡은 약 1 내지 20 nm 인, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 18**

제1 항 내지 제3항, 제7 항 및 제8 항 중 어느 한 항에 있어서,

상기 프로세싱 챔버로 폴리머 전구체 (polymer precursor) 를 제공하는 단계; 및

상기 수직적으로 에칭하는 단계에서 상기 3-D 구조물의 부분들이 에칭되는 범위를 축소시키는 (attenuate) 상기 3-D 구조물의 부분들 위에 상기 폴리머 전구체의 중합을 통해 보호 층을 형성하는 단계를 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 19**

제18 항에 있어서,

상기 폴리머 전구체는  $\text{CF}_4$ ,  $\text{CHF}_3$ ,  $\text{CH}_2\text{F}_2$ , 및  $\text{CH}_3\text{F}$  에서 선택되고; 그리고

상기 폴리머 전구체를 제공하는 단계는, 약 30 내지 40 sccm 의 유속으로 상기 프로세싱 챔버로 상기 폴리머 전구체를 유동시키는 단계를 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

**청구항 20**

제1 항 내지 제8 항 중 어느 한 항에 있어서,

약 100 내지 700 sccm 의 유속으로 상기 프로세싱 챔버로  $\text{NF}_3$ ,  $\text{CF}_4$ ,  $\text{CHF}_3$ ,  $\text{CH}_2\text{F}_2$ , 및  $\text{CH}_3\text{F}$  중 1 이상을 유동시킴

으로써 상기 프로세싱 챔버로 상기 제1 활성화된 예칭 재료를 제공하여, 그것을 상기 프로세싱 챔버 내에서 이 온화하는 단계를 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

#### 청구항 21

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 수직적으로 예칭하는 단계는, 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하면서, 약 10 내지 120 °C의 온도 및 약 50 내지 90 mTorr의 압력에서 유지되는 상기 프로세싱 챔버로 수행되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

#### 청구항 22

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 수평적으로 예칭하는 단계는, 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하면서, 약 10 내지 120 °C의 온도 및 약 5 mTorr 보다 작은 압력에서 유지되는 상기 프로세싱 챔버로 수행되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

#### 청구항 23

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 제1 활성화된 예칭 재료는 상기 프로세싱 챔버 내에서 생성된 1 이상의 이온 종들을 포함하고; 그리고,

상기 플라즈마는, 약 13 내지 60 MHz의 주파수를 가지는 유도성-커플링된 (inductively-coupled) RF 전력에 의해 생성되고 유지되고, 또한 약 400 kHz 내지 14 MHz의 주파수를 가지는 기판-바이어스된 (substrate-biased) RF 전력에 의해 생성되고 유지되는 유도성-커플링된 플라즈마인, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

#### 청구항 24

제23 항에 있어서,

상기 기판-바이어스된 RF 전력은 상기 기판에 대해 약 100 내지 500 볼트의 전압을 가지는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

#### 청구항 25

제24 항에 있어서,

상기 기판-바이어스된 RF 전력은 약 10% 내지 60%의 뉴티 싸이클 (duty cycle)을 가지고, 약 100 Hz 내지 400 Hz의 레이트 (rate)로 펄싱되는 (pulsed), 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

#### 청구항 26

제23 항에 있어서,

상기 유도성-커플링된 RF 전력은 약 500 내지 600 와트인, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

#### 청구항 27

제26 항에 있어서,

상기 유도성-커플링된 RF 전력은 제1 생성 코일 및 제2 생성 코일을 포함하는 생성 코일들에 의해 생성되고, 상기 제1 생성 코일은 상기 프로세싱 챔버의 외부 영역으로 유도성-커플링된 RF 전력을 공급하고, 상기 제2 생성 코일은 상기 프로세싱 챔버의 내부 영역으로 유도성-커플링된 RF 전력을 공급하고, 상기 유도성-커플링된 RF 전력의 총합은 약 0.1 내지 1.5의 비율로 제1 생성 코일과 제2 생성 코일 간에서 나뉘지는 (split), 텅스텐-함유

재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 28

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 수평적으로 에칭하는 단계 동안 상기 텅스텐-함유 재료의 상기 제1 층의 부분들의 제거에 대응하는 에칭-레이트 (etch-rate) 는 실질적으로 매쓰-수송 제한되는 (mass-transport limited), 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 29

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 텅스텐-함유 재료의 상기 제2 층은 실질적으로 보이드-프리한 (void-free) 방식으로 상기 복수의 내부 영역들 내에 증착되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 30

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 수직적으로 에칭하는 단계, 상기 수평적으로 에칭하는 단계, 및 텅스텐-함유 재료의 상기 제1 층을 증착하는 단계 및 텅스텐-함유 재료의 상기 제2 층을 증착하는 단계는 동일한 프로세싱 챔버에서 수행되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 31

제1 항 내지 제8 항 중 어느 한 항에 있어서,

상기 수직적으로 에칭하는 단계는, 상기 수평적으로 에칭하는 단계, 텅스텐-함유 재료의 상기 제1 층을 증착하는 단계 및 텅스텐-함유 재료의 상기 제2 층을 증착하는 단계와는 달리 상이한 프로세싱 챔버에서 수행되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 32

제1 항 내지 제8 항 중 어느 한 항에 있어서,

텅스텐-함유 재료의 상기 제2 층을 수직적으로 에칭하는 단계로서, 상기 수직적으로 에칭하는 단계는 상기 복수의 내부 영역들로부터 상기 제2 층의 부분들을 실질적으로 제거하지 않고 상기 제1 활성화된 에칭 재료를 사용하여 상기 측벽으로부터 상기 제2 층의 부분들을 제거하는 단계를 포함하는, 상기 수직적으로 에칭하는 단계;

상기 텅스텐-함유 재료의 상기 제2 층을 수평적으로 에칭하는 단계로서, 상기 수평적으로 에칭하는 단계는 상기 제2 활성화된 에칭 재료를 사용하여 상기 복수의 내부 영역들로부터 상기 제2 층의 부분들을 제거하는 단계를 포함하는, 상기 수평적으로 에칭하는 단계; 및

상기 제1 층 및 상기 제2 층에 의해 충진되지 않은 채로 남겨진 상기 내부 영역들의 부분의 적어도 일부를 텅스텐-함유 재료의 제3 층이 충진하도록, 상기 수평적으로 에칭하는 단계 및 상기 수평적으로 에칭하는 단계 이후에 상기 3-D 구조물 내에 텅스텐-함유 재료의 상기 제3 층을 증착하는 단계를 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 33

제1 항 내지 제8 항 중 어느 한 항에 있어서,

약 500 내지 2000 sccm 의 레이트로 상기 수직적으로 에칭하는 단계를 수행하는 동안 상기 프로세싱 챔버로 불활성 희석 가스 (inert diluent gas) 를 유동시키는 단계를 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 34

제33 항에 있어서,

상기 불활성 희석 가스는 He 또는 Ar 또는 양자 모두를 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 35

텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치로서,

상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 복수의 피쳐 (feature) 들로 이어지며, 상기 복수의 피쳐들은 상기 복수의 구멍들을 통해 유체적으로 접근 가능한 복수의 내부들 (interiors) 을 가지며,

상기 장치는,

프로세싱 챔버;

상기 3-D 구조물을 가지는 상기 기판을 홀딩하도록 구성된 상기 프로세싱 챔버 내의 기판 홀더;

텅스텐-함유 전구체 및 환원제를 상기 프로세싱 챔버 내로 도입하도록 구성된 1 이상의 가스 유입구들;

상기 프로세싱 챔버 내에서 유도성-커플링된 플라즈마를 생성하고 유지하도록 구성된 제1 전원 및 제2 전원으로서, 상기 제1 전원은 상기 플라즈마에 유도성-커플링된 RF 전력을 공급하고, 상기 제2 전원은 상기 플라즈마에 기판-바이어스된 RF 전력을 공급하는, 상기 제1 전원 및 상기 제2 전원; 및

기계 관통가능한 코드의 형식인 인스트럭션들 (instructions) 을 가지는 컨트롤러로서, 상기 컨트롤러는 상기 인스트럭션들을 수행하도록 구성되는, 상기 컨트롤러를 포함하고,

상기 인스트럭션들은,

상기 프로세싱 챔버 내로 텅스텐-함유 전구체의 유동 및 환원제의 유동을 도입하도록 상기 1 이상의 가스 유입구들을 동작시키는 인스트럭션들로서, 텅스텐-함유 재료의 층이 상기 텅스텐-함유 전구체 및 상기 환원제 간의 화학적 반응을 통해 상기 3-D 구조물 내에 증착되도록 상기 프로세싱 챔버 내의 압력을 약 1 내지 100 Torr 로 유지하고 상기 프로세싱 챔버 내의 온도를 약 200 내지 450 °C 로 유지하면서, 텅스텐-함유 전구체의 상기 유속은 약 50 내지 500 sccm 이고, 환원제의 상기 유속은 약 0 내지 10000 sccm 인, 상기 1 이상의 가스 유입구들을 동작시키는 인스트럭션들;

약 13 내지 60 MHz 의 주파수로 상기 제1 전원을 동작시켜, 약 500 내지 600 와트의 RF 전력을 생성하는 인스트럭션들; 및

약 400 kHz 내지 14 MHz 의 주파수로, 그리고 상기 기판에 대해 약 100 내지 500 볼트의 전압으로, 약 100 Hz 내지 약 400 Hz 의 펄스 레이트 (pulse rate) 를 가지고, 또한 약 10% 내지 60%의 둑티 싸이클 (duty cycle) 을 가지고, 상기 제2 전원을 동작시키는 인스트럭션들을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

### 청구항 36

제35 항에 있어서,

상기 프로세싱 챔버와 멀리 떨어졌지만 유체적으로 연결된 플라즈마-생성 챔버 내에서 제2 플라즈마를 생성하고 유지하도록 구성된 제3 전원을 더 포함하고,

상기 컨트롤러의 상기 인스트럭션들은, 약 400 kHz 내지 27 MHz 의 주파수로 상기 제3 전원을 동작시켜 약 400 내지 2000 와트의 RF 전력을 생성하는 인스트럭션들을 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

### 청구항 37

부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법으로서,

상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 상기 구멍들을 통해 유체적으로 접근 가능한 (accessible) 복수의 내부 영역들을 가지는 복수의 피쳐 (feature) 들로 이어지며,

상기 방법은,

상기 3-D 구조물을 가지는 기판을 제공하는 단계로서, 상기 3-D 구조물은 적어도 부분적으로 자신의 측벽 및/또

는 자신의 측벽의 구멍들을 덮는 텅스텐-함유 재료의 제1 층을 이미 가지고, 상기 복수의 내부 영역들을 부분적으로 충진하지만, 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 복수의 내부 영역들의 부분을 가진, 상기 기판을 제공하는 단계;

상기 복수의 내부 영역들로부터 상기 제1 층의 부분들을 실질적으로 제거하지 않고 상기 측벽 및/또는 상기 측벽의 구멍들로부터 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하도록 수직적으로 에칭하는 단계; 및

상기 복수의 내부 영역들로부터 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하도록 수평적으로 에칭하는 단계를 포함하는, 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 38

제37 항에 있어서,

상기 수평적으로 에칭하는 단계 및 상기 수직적으로 에칭하는 단계 이후에, 상기 텅스텐-함유 재료의 제2 층을 증착하는 단계를 더 포함하는, 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 39

제37 항에 있어서,

상기 수직적으로 에칭하는 단계는 제1 활성화된 에칭 재료를 이용하고, 상기 수평적으로 에칭하는 단계는 상기 3-D 구조물 내에서의 상기 제1 활성화된 에칭 재료의 변환으로부터 생성되는 제2 활성화된 에칭 재료를 이용하는, 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 40

부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법으로서,

상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 상기 구멍들을 통해 유체적으로 접근 가능한 (accessible) 복수의 내부 영역들을 가지는 복수의 피쳐 (feature) 들로 이어지며,

상기 방법은,

상기 3-D 구조물에서 텅스텐-함유 재료의 제1 층을 증착하는 단계;

이온들의 일부분이 상기 구조물의 베이스를 향하여 지향되도록 (directed), 이온 에칭 종들 (ion etch species) 을 포함하는 플라즈마를 생성하고 상기 이온들에 전자기장을 인가함으로써 상기 제1 층을 증착하는 단계 후에 수직적으로 에칭하는 단계;

상기 3-D 구조물을 가지는 상기 기판을 홀딩하는 상기 프로세싱 챔버로부터 멀리 떨어진 자유 라디칼 종들을 생성하고, 상기 프로세싱 챔버 내로 상기 자유 라디칼 종들을 도입시킴으로써, 상기 수직적으로 에칭하는 단계 후에 수평적으로 에칭하는 단계; 및

상기 수평적으로 에칭하는 단계 후에, 3-차원의 상기 구조물에 상기 텅스텐-함유 재료의 제2 층을 증착하는 단계를 포함하는, 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법.

### 청구항 41

텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치로서,

상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 복수의 피쳐 (feature) 들로 이어지며, 상기 복수의 피쳐들은 상기 복수의 구멍들을 통해 유체적으로 접근 가능한 복수의 내부들 (interiors) 을 가지며,

상기 장치는,

프로세싱 챔버;

상기 3-D 구조물을 가지는 상기 기판을 홀딩하도록 구성된 상기 프로세싱 챔버 내의 기판 홀더;

텅스텐-함유 전구체 및 환원제를 상기 프로세싱 챔버 내로 도입하도록 구성된 1 이상의 가스 유입구들;

상기 프로세싱 챔버 내에 이온화된 플라즈마를 생성하고 유지하도록 구성된 전원; 및

상기 1 이상의 가스 유입구들 및 전원을 동작시키기 위한 기계 팬독가능한 코드의 형식인 인스트럭션들 (instructions) 을 가지는 컨트롤러로서, 상기 컨트롤러는 상기 인스트럭션들을 수행하도록 구성되는, 상기 컨트롤러를 포함하고,

상기 인스트럭션들은,

상기 제1 층이 상기 3-D 구조물의 상기 복수의 내부 영역들을 충진하도록 상기 3-D 구조물 내에서 상기 텅스텐-함유 재료의 제1 층을 증착하는 인스트럭션들;

상기 텅스텐-함유 재료의 상기 제1 층을 증착한 후에 수직적으로 예칭하고 수평적으로 예칭하는 인스트럭션들로서, 상기 수직적으로 예칭하는 것은 상기 복수의 내부 영역들로부터 상기 제1 층의 부분들을 실질적으로 제거하지 않고 제1 활성화된 예칭 재료를 사용하여 상기 측벽으로부터 상기 제1 층의 부분들을 제거하는 것을 포함하고, 상기 수평적으로 예칭하는 것은 제2 활성화된 예칭 재료를 사용하여 상기 복수의 내부 영역들로부터 상기 제1 층의 부분들을 제거하는 것인, 수직적으로 예칭하고 수평적으로 예칭하는 인스트럭션들; 및

텅스텐-함유 재료의 제2 층이 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 내부 영역들의 적어도 일부분을 충진하도록, 수평적으로 예칭하고 수직적으로 예칭한 후에 상기 3-D 구조물 내에서 상기 텅스텐-함유 재료의 상기 제2 층을 증착하는 인스트럭션들을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 42

제41 항에 있어서,

상기 텅스텐-함유 재료의 상기 제1 층을 증착하는 것과 상기 텅스텐-함유 재료의 상기 제2 층을 증착하는 것 모두는 텅스텐-함유 전구체 (precursor) 및 환원제 (reducing agent) 간의 반응을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 43

제41 항에 있어서,

상기 제1 활성화된 예칭 재료는 이온 종들 (ion species) 을 포함하고,

상기 제2 활성화된 예칭 재료는 중성 종들 (neutral species) 을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 44

제43 항에 있어서,

상기 제2 활성화된 예칭 재료는 상기 3-D 구조물 내에서 상기 제1 활성화된 예칭 재료의 변환 (conversion) 으로부터 발생되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 45

제44 항에 있어서,

상기 제2 활성화된 예칭 재료로의 상기 제1 활성화된 예칭 재료의 변환은, 제1 활성화된 예칭 재료의 이온 종들이 1 이상의 전자들을 수용하여 제2 활성화된 예칭 재료의 중성 종들로 변환시키는 것을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 46

제43 항에 있어서,

상기 제1 활성화된 예칭 재료는 상기 프로세싱 챔버 내에서 생성되는 이온 종들을 포함하는 플라즈마이고;

상기 수직적으로 예칭하는 것은 상기 이온들의 일부분이 상기 3-D 구조물의 바닥을 향하여 지향되도록 (directed), 상기 이온 종들에 전자기장을 인가하는 것을 포함하고; 그리고

상기 제2 활성화된 예칭 재료는 상기 프로세싱 챔버로부터 멀리 떨어져 생성되어 상기 프로세싱 챔버 내로 도입

되는 자유 라디칼 종들 (free radical species) 을 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 47

제41 항 내지 제46 항 중 어느 한 항에 있어서,

상기 부분적으로 제조된 반도체 기판은 텅스텐 증착에 민감하고 (susceptible) 텅스텐-함유 재료의 상기 제1 층이 증착되는 외부 층을 더 포함하고,

상기 수직적으로 예칭하는 것은 상기 3-D 구조물의 상기 측벽의 적어도 부분들 내의 상기 외부 층을 제거하여, 상기 텅스텐-함유 재료의 상기 제2 층의 후속하는 증착 동안 실질적으로 어떠한 텅스텐-함유 재료도 이러한 부분들 상에 증착되지 않는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 48

제41 항 내지 제43 항 및 제46 항 중 어느 한 항에 있어서,

상기 컨트롤러는, 상기 수직적으로 예칭하는 것 이후, 그러나 상기 수평적으로 예칭하는 것 이전에, 상기 복수의 내부 영역들의 상기 노출된 표면들의 적어도 부분들을 세정하는 인스트러션들을 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 49

제41 내지 제43 항 및 제46 항 중 어느 한 항에 있어서,

상기 컨트롤러는,

상기 프로세싱 챔버 내로 폴리머 전구체를 유동시키는 인스트러션들; 및

상기 수직적으로 예칭하는 것에서 상기 3-D 구조물의 부분들이 예칭되는 범위를 축소시키는 (attenuate) 상기 3-D 구조물의 부분들 위에 상기 폴리머 전구체의 중합을 통해 보호 층을 형성하는 인스트러션들을 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 50

제49 항에 있어서,

상기 유동은 약 30 내지 40 sccm 의 유속으로 행해지는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 51

제41 항 내지 제46 항 중 어느 한 항에 있어서,

약 100 내지 700 sccm 의 유속으로 상기 프로세싱 챔버로 상기 제1 활성화된 예칭 재료에 대해 전구체를 유동시켜, 그것을 상기 프로세싱 챔버 내에서 이온화하는 인스트러션들을 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 52

제41 항 내지 제46 항 중 어느 한 항에 있어서,

상기 수직적으로 예칭하는 것은, 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하면서, 약 10 내지 120 °C의 온도 및 약 50 내지 90 mTorr 의 압력에서 유지되는 상기 프로세싱 챔버로 수행되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 53

제41 항 내지 제46 항 중 어느 한 항에 있어서,

상기 수평적으로 예칭하는 것은, 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하면서, 약 10 내지 120 °C의 온도 및 약 5 mTorr 보다 작은 압력에서 유지되는 상기 프로세싱 챔버로 수행되는, 텅스텐-함유 재료로 부

분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 54

제41 항에 있어서,

상기 제1 활성화된 에칭 재료는 상기 프로세싱 챔버 내에서 생성된 1 이상의 이온 종들을 포함하고; 그리고,

상기 플라즈마는, 약 13 내지 60 MHz 의 주파수를 가지는 유도성-커플링된 (inductively-coupled) RF 전력에 의해 생성되고 유지되고, 또한 약 400 kHz 내지 14 MHz 의 주파수를 가지는 기판-바이어스된 (substrate-biased) RF 전력에 의해 생성되고 유지되는 유도성-커플링된 플라즈마인, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 55

제54 항에 있어서,

상기 기판-바이어스된 RF 전력은 상기 기판에 대해 약 100 내지 500 볼트의 전압을 가지는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 56

제55 항에 있어서,

상기 기판-바이어스된 RF 전력은 약 10% 내지 60%의 듀티 사이클 (duty cycle) 을 가지고, 약 100 Hz 내지 400 Hz 의 레이트 (rate) 로 펄싱되는 (pulsed), 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 57

제54 항에 있어서,

상기 유도성-커플링된 RF 전력은 약 500 내지 600 와트인, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 58

제57 항에 있어서,

상기 유도성-커플링된 RF 전력은 제1 생성 코일 및 제2 생성 코일을 포함하는 생성 코일들에 의해 생성되고, 상기 제1 생성 코일은 상기 프로세싱 챔버의 외부 영역으로 유도성-커플링된 RF 전력을 공급하고, 상기 제2 생성 코일은 상기 프로세싱 챔버의 내부 영역으로 유도성-커플링된 RF 전력을 공급하고, 상기 유도성-커플링된 RF 전력의 총합은 약 0.1 내지 1.5의 비율로 제1 생성 코일과 제2 생성 코일 간에서 나뉘지는 (split), 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 59

제41 항 내지 제46 항 중 어느 한 항에 있어서,

상기 수평적으로 에칭하는 것 동안 상기 텅스텐-함유 재료의 상기 제1 층의 부분들의 제거에 대응하는 에칭-레이트 (etch-rate) 는 실질적으로 매쓰-수송 제한되는 (mass-transport limited), 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 60

제41 항 내지 제46 항 중 어느 한 항에 있어서,

상기 텅스텐-함유 재료의 상기 제2 층은 실질적으로 보이드-프리한 (void-free) 방식으로 상기 복수의 내부 영역들 내에 증착되는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

#### 청구항 61

제41 항 내지 제46 항 중 어느 한 항에 있어서,

상기 컨트롤러의 상기 인스트럭션들은,

상기 텅스텐-함유 재료의 상기 제2 층을 수직적으로 에칭하고 수평적으로 에칭하는 인스트럭션들로서, 상기 수직적으로 에칭하는 것은 상기 복수의 내부 영역들로부터 상기 제2 층의 부분들을 실질적으로 제거하지 않고 제1 활성화된 에칭 재료를 사용하여 상기 측벽으로부터 상기 제2 층의 부분들을 제거하는 것을 포함하고, 상기 수평적으로 에칭하는 것은 제2 활성화된 에칭 재료를 사용하여 상기 복수의 내부 영역들로부터 상기 제2 층의 부분들을 제거하는 것인, 상기 제2 층을 수직적으로 에칭하고 수평적으로 에칭하는 인스트럭션들; 및

텅스텐-함유 재료의 제3 층이 상기 제1 층 및 상기 제2 층에 의해 충진되지 않은 채로 남겨진 상기 내부 영역들의 부분들의 적어도 일부를 충진하도록, 상기 제2 층을 수평적으로 에칭하고 수직적으로 에칭한 후에 상기 3-D 구조물 내에서 상기 텅스텐-함유 재료의 상기 제3 층을 증착하는 인스트럭션들을 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

## 청구항 62

제41 항 내지 제46 항 중 어느 한 항에 있어서,

상기 컨트롤러의 상기 인스트럭션들은,

약 500 내지 2000 sccm 의 레이트로 상기 수직적으로 에칭하는 것 동안 상기 프로세싱 챔버로 불활성 희석 가스 (inert diluent gas) 를 유동시키는 인스트럭션들을 더 포함하는, 텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 장치.

## 명세서

### 기술 분야

[0001]

본 출원은 2013년 5월 24일에 출원된 미국 가출원 제61/827,511호 "METHODS AND APPARATUSES FOR VOID-FREE TUNGSTEN FILL IN THREE-DIMENSIONAL SEMICONDUCTOR FEATURES"에 대한 우선권을 주장하고, 이 출원은 모든 목적들에 대해 전체적으로 참조로서 본 명세서에 포함된다.

### 배경기술

[0002]

텅스텐 및 텅스텐-함유 재료의 증착은 수많은 반도체 제조 프로세스들 중 필수적인 부분이다. 이러한 증착은 예를 들어 물리적 기상 증착 (PVD) 과 같은 IC 제조 분야에서 알려진 여타의 증착 기술들 뿐만 아니라, 화학적 기상 증착 (CVD) 기술, 플라즈마-향상된 CVD (PECVD) 기술, 원자 층 증착 (ALD) 기술을 통해 달성될 수도 있다. 이하에서 텅스텐-기초 재료 또는 단순히 텅스텐 재료로 지칭되는 텅스텐 및 텅스텐-함유 재료는 수평적 인터커넥트 (horizontal interconnect), 인접한 금속 층들 간의 비아 (via), 제1 금속 층과 실리콘 기판 상의 디바이스 사이의 컨택트에 사용될 수도 있고, 일반적으로 IC 디자인에 이용되는 다양한 고 종횡비 피쳐들 내에 사용될 수도 있다.

[0003]

텅스텐 재료를 증착하는 종래의 프로세스에서, 기판은 증착 챔버 내에서 미리 결정된 프로세스 온도로 가열되고, 텅스텐 재료의 얇은 층이 시드 (seed) 또는 결정핵생성 층 (nucleation layer) 으로 기능하도록 증착된다. 그 후에, 텅스텐 재료의 벌크 층 (bulk layer) 이 결정핵생성 층을 위에 증착된다. 일반적으로, 텅스텐 재료는 수소 ( $H_2$ ) 와 함께 텅스텐 헥사플로라이드 ( $WF_6$ ) 의 감소에 의해 형성된다. 통상적으로, 텅스텐 재료는, 다양한 IC 피쳐들 뿐만 아니라 1 이상의 필드 영역 (field region) 을 종종 포함하는 기판의 완전히 노출된 표면 영역 위에 증착된다. 이러한 피쳐들은 넓게 변화하는 종횡비들을 가질 수도 있고, 어떤 실시예들에서는, 1 이상의 모든 피쳐들이 상대적으로 고 종횡비들을 가질 수도 있다.

### 발명의 내용

#### 과제의 해결 수단

[0004]

텅스텐-함유 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법이 본 명세서에 개시된다. 어떤 실시예들에서, 상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 상기 구멍들을 통해 유체적으로 접근 가능한 (accessible) 복수의 내부 영역들을 가지는 복수의 피쳐 (feature) 들로 이어진다. 상기

방법은, 프로세싱 챔버로 3-D 구조물을 가지는 기판을 제공하는 단계; 상기 텅스텐-함유 재료의 제1 층이 부분적으로 상기 3-D 구조물의 상기 복수의 내부 영역들을 충진하도록, 상기 3-D 구조물 내에 상기 텅스텐-함유 재료의 제1 층을 증착하는 단계; 그 후의 수직적으로 예칭하는 단계 및 수평적으로 예칭하는 단계; 상기 텅스텐-함유 재료의 제2 층이 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 내부 영역들의 적어도 일부를 충진하도록, 수직적으로 그리고 수평적으로 예칭한 후에 상기 3-D 구조물 내에 상기 텅스텐-함유 재료의 상기 제2 층을 증착하는 단계를 포함한다. 상기 수직적으로 예칭하는 단계는 상기 복수의 내부 영역들로부터 상기 제1 층의 부분을 실질적으로 제거하지 않고 제1 활성화된 예칭 재료를 사용하여 상기 측벽으로부터 상기 제1 층의 부분을 제거하는 단계를 포함할 수도 있고, 상기 수평적으로 예칭하는 단계는 제2 활성화된 예칭 재료를 사용하여 상기 복수의 내부 영역들로부터 상기 제1 층의 부분을 제거하는 단계를 포함할 수도 있다.

[0005]

어떤 실시예들에서, 상기 텅스텐-함유 재료의 상기 제1 층을 증착하는 단계와 상기 텅스텐-함유 재료의 상기 제2 층을 증착하는 단계 모두는 텅스텐-함유 전구체 (precursor) 및 환원제 (reducing agent) 간의 반응을 포함한다. 어떤 실시예들에서, 상기 제1 활성화된 예칭 재료는 1 이상의 이온 종들 (ion species) 을 포함하고, 상기 제2 활성화된 예칭 재료는 1 이상의 중성 종들 (neutral species) 을 포함하고, 이러한 특정 실시예들에서, 상기 제2 활성화된 예칭 재료는 상기 3-D 구조물 내에서 상기 제1 활성화된 예칭 재료의 변환 (conversion) 으로 부터 발생될 수도 있다. 어떤 실시예들에서, 상기 제1 활성화된 예칭 재료를 구성하는 상기 이온 종들은  $\text{NF}_3$ ,  $\text{CF}_4$ ,  $\text{CHF}_3$ ,  $\text{CH}_2\text{F}_2$ , 및  $\text{CH}_3\text{F}$  중 1 이상의 이온화를 통해 상기 프로세싱 챔버 내에서 생성된다. 어떤 실시예들에서, 상기 제1 활성화된 예칭 재료는 상기 프로세싱 챔버 내에서 생성되는 1 이상의 이온 종들을 포함하는 플라즈마이다. 어떤 실시예들에서, 상기 수직적으로 예칭하는 단계는 상기 이온들의 일부분이 상기 고 종횡비 피쳐의 베이스를 향하여 지향되도록 (directed), 상기 이온 종들에 전자기장을 인가하는 단계를 포함한다. 어떤 실시예들에서, 상기 제2 활성화된 예칭 재료는 상기 프로세싱 챔버로부터 멀리 떨어져 생성되어 상기 프로세싱 챔버 내로 도입되는 1 이상의 자유 라디칼 종들 (free radical species) 을 포함하는 플라즈마일 수도 있다. 이러한 특정 실시예들에서, 상기 이온 종들 및 상기 자유 라디칼 종들은 모두 불소를 함유할 수도 있다.

[0006]

또한, 텅스텐-함유 재료의 제1 층을 이미 가지는 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 방법이 본 명세서에 개시된다. 상기 3-D 구조물은 측벽을 포함하고, 상기 측벽의 복수의 구멍들은 상기 구멍들을 통해 유체적으로 접근 가능한 (accessible) 복수의 내부 영역들을 가지는 복수의 피쳐 (feature) 들로 이루어진다. 텅스텐-함유 재료의 제1 층은 적어도 부분적으로 측벽 및/또는 자신의 측벽의 구멍들을 덮고, 상기 복수의 내부 영역들을 부분적으로 충진하지만, 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 복수의 내부 영역들의 부분을 가진다. 상기 방법은 3-D 구조물을 가지는 상기 기판을 제공하는 단계와 수직적으로 예칭하는 단계와 수평적으로 예칭하는 단계를 포함할 수도 있다. 상기 수직적으로 예칭하는 단계는 상기 복수의 내부 영역들로부터 상기 제1 층의 부분들을 실질적으로 제거하지 않고 상기 측벽 및/또는 상기 측벽의 구멍들로부터 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거할 수도 있다. 상기 수평적으로 예칭하는 단계는 상기 복수의 내부 영역들로부터 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거할 수도 있다. 이러한 특정 실시예들에서, 상기 방법은 상기 수평적으로 예칭하는 단계 및 상기 수직적으로 예칭하는 단계 이후에, 상기 텅스텐-함유 재료의 제2 층을 증착하는 단계를 더 포함할 수도 있다.

[0007]

또한, 텅스텐-함유 재료로 3-D 구조물을 충진하는 대안적인 방법들이 본 명세서에 개시된다. 어떤 실시예들에서, 상기 방법은, 3-D 구조물을 가지는 기판을 제공하는 단계로서, 상기 3-D 구조물은 측벽, 복수의 피쳐들에 대한 복수의 구멍들, 상기 복수의 피쳐들은 상기 복수의 구멍들을 통해 유체적으로 접근 가능한 복수의 내부들을 가지는, 상기 기판을 제공하는 단계; 제1 층이 상기 복수의 내부들을 부분적으로 (또는 완전히) 충진하도록, 텅스텐-함유 전구체 및 환원제 간의 반응을 통해 상기 구조물 내에서 상기 텅스텐-함유 재료의 제1 층을 증착하는 단계; 텅스텐-함유 재료의 상기 제1 층을 증착하는 단계 이후에 수직적으로 예칭하는 단계; 상기 수직적으로 예칭하는 단계 이후에 수평적으로 예칭하는 단계; 및 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 복수의 내부들의 부분의 적어도 일부분을 제2 층이 충진하도록, 상기 텅스텐-함유 전구체 및 상기 환원제 간의 반응을 통해 상기 수평적으로 예칭하는 단계 후에 상기 구조물 내에서 상기 텅스텐-함유 재료의 제2 층을 증착하는 단계를 포함한다.

[0008]

어떤 실시예들에서, 상기 수직적으로 예칭하는 단계는 제1 활성화 예칭 재료를 제공하는 단계; 및 상기 복수의 피쳐들의 상기 복수의 내부들로부터 상기 제1 층의 부분들을 실질적으로 제거하지 않고 상기 제1 활성화된 예칭 재료를 사용하여 상기 3-D 구조물의 측벽으로부터 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하는 단계를 포함할 수도 있다. 어떤 실시예들에서, 수평적으로 예칭하는 단계는, 제2 활성화된 예칭 재료를 제공하는 단계; 및 상기 제2 활성화된 예칭 재료를 사용하여 상기 복수의 내부들로부터 상기 텅스텐-함유 재료의 상기

제1 층의 부분들을 제거하는 단계를 포함할 수도 있다. 어떤 실시예들에서, 상기 복수의 내부들의 노출된 표면들의 적어도 부분들은 수직적으로 에칭하는 단계에 후속하지만 수평적으로 에칭하는 단계 이전에 수행되는 세정 동작을 통해 세정된다.

[0009] 어떤 실시예들에서, 상기 수평적으로 에칭하는 단계 동안 상기 텅스텐-함유 재료의 상기 제1 층의 부분들의 제거에 대응하는 에칭-레이트 (etch-rate)는 실질적으로 대량-수송 제한된다 (mass-transport limited). 어떤 실시예들에서, 상기 텅스텐-함유 재료의 제2 층은 실질적으로 보이드-프리한 (void-free) 방식으로 상기 복수의 내부들 내에 증착된다.

[0010] 어떤 실시예들에서, 상기 재료의 수직적 에칭은 플라즈마 챔버에서 행해진다. 상기 플라즈마 챔버에서 웨이퍼는 웨이퍼를 홀딩하는 정전 척 (ESC) 상에 위치된다. 고주파 (RF) 전력은, 챔버 내에서 플라즈마의 존재 하에 웨이퍼 상에 셀프-바이어스 (self-bias)를 생성하는 ESC에 인가된다. 플라즈마가 챔버에 생성되는 경우, 피드 가스 (feed gas) (이 가스는 플라즈마 생성을 위해 챔버로 공급됨)의 1 이상의 화학적 종들이 이온화, 해리 등이 되어 반응성 이온들 (예컨대,  $\text{CHF}^+$ ,  $\text{NF}_2^+$ , 등) 및/또는 반응성 중성 종들을 생성한다. 웨이퍼 상의 셀프-바이어스에 기인하여, 플라즈마의 이온들이 웨이퍼 방향으로 가속된다. 웨이퍼 방향으로 충분한 에너지를 가진 이온들의 가속으로 인하여 웨이퍼를 때리는 (striking) 이온들의 에너지는 ESC에 인가되는 RF 전력에 의해 제어될 수 있다. 따라서, 어떤 실시예들에서, 제1 활성화된 에칭 재료는 이온 종들을 포함하는 플라즈마 일 수도 있고, 수직적으로 에칭하는 단계는 상기 프로세싱 챔버 내에 상기 이온 종들을 가지는 플라즈마를 생성하는 단계와, 고 종횡비 피쳐의 바닥을 향해 상기 이온들의 일부분이 지향되도록 상기 이온들에 전자기장을 인가하는 단계를 포함한다. 어떤 실시예들에서, 제2 활성화된 에칭 재료는 자유 라디칼 종들을 포함하는 플라즈마일 수도 있고, 수평적으로 에칭하는 단계는 상기 프로세싱 챔버로부터 멀리 떨어진 자유 라디칼 종들을 생성하는 단계와, 상기 프로세싱 챔버 내로 상기 자유 라디칼 종들을 도입하는 단계를 포함한다. 어떤 실시예들에서, 이온 종들은 불소-함유 종들을 포함하고; 어떤 실시예들에서, 자유 라디칼 종들은 불소-함유 종들을 포함한다. 예를 들어, 어떤 실시예들에서, 이온 종들은 이온화된  $\text{NF}_3$ ,  $\text{CF}_4$ ,  $\text{SF}_6$  또는 그들의 조합들을 포함한다. 어떤 실시예들에서, 자유 라디칼 종들은 불소 라디칼 ( $\text{F}^*$ )을 포함한다. 다른 실시예들에서, 부분적으로 제조된 3-D 구조물들을 충진하는 방법은 습식 에 chant (wet chant)로 에칭하는 단계를 포함할 수도 있다. 채용될 수도 있는 습식 에 chant의 예시들은  $\text{H}_2\text{O}_2$ , HF,  $\text{H}_2\text{SO}_4$ ,  $\text{HNO}_3$  및  $\text{NH}_4\text{OH}$ 의 조합들을 포함한다.

[0011] 어떤 실시예들에서, 3-D 구조물들의 복수의 피쳐들의 적어도 일부분은 서로 실질적으로 수직 정렬 (vertical alignment)되어 적층된다. 예를 들어, 3-D 구조물은 서로 수직 정렬된, 16개 이상, 또는 64개 이상, 또는 128개 이상의 수직적으로 적층된 피쳐들을 가질 수도 있다.

[0012] 어떤 실시예들에서, 상기 기판은 텅스텐 증착에 민감하고 (susceptible) 텅스텐-함유 재료의 상기 제1 층이 증착되는 외부 층을 더 포함할 수도 있다. 어떤 실시예들에서, 상기 수직적으로 에칭하는 단계는 상기 3-D 구조물의 상기 측벽의 적어도 부분들 내의 상기 외부 층을 제거하여, 상기 텅스텐-함유 재료의 상기 제2 층의 후속하는 증착 동안 실질적으로 어떠한 텅스텐-함유 재료도 이러한 부분들 상에 증착되지 않는다. 어떤 실시예들에서, 텅스텐 증착에 민감한 상기 외부 층은 티타늄 나이트라이드와 같은 금속 나이트라이드를 포함한다. 어떤 실시예들에서, 3-D 구조물을 가지는 상기 기판은 복수의 필라들, 예컨대 폴리실리콘 필라들을 더 포함하고, 이것은 상기 복수의 구멍들을 통해 상기 복수의 내부들의 유체적 접근 가능성을 보인다. 어떤 실시예들에서, 상기 필라들 간의 수평적 갭은 약 1 내지 20 nm이다.

[0013] 어떤 실시예들에서, 상기 수직적으로 에칭하는 단계는, 폴리머 전구체 (polymer precursor)를 제공하는 단계; 및 상기 수직적으로 에칭하는 단계 동안 좌우 방향으로 이러한 부분들이 에칭되는 범위를 축소시키는 (attenuate) 부분들 위에 상기 폴리머 전구체의 중합을 통해 보호 층을 형성하는 단계를 더 포함한다. 어떤 실시예들에서, 폴리머 전구체는 불소-함유 화합물이다. 이러한 폴리머 전구체의 예시들은,  $\text{CF}_4$ ,  $\text{CHF}_3$ ,  $\text{CH}_2\text{F}_2$ , 및  $\text{CH}_3\text{F}$ 이다.

[0014] 어떤 실시예들에서, 상기 제1 활성화된 에칭 재료를 제공하는 단계는, 약 300 sccm 내지 700 sccm의 유속으로 상기 프로세싱 챔버 내로  $\text{NF}_3$ 를 유동시키는 단계; 및 약 10 sccm 내지 50 sccm의 유속으로 상기 프로세싱 챔버 내로 상기 폴리머 전구체를 유동시키는 단계를 포함하는 상기 폴리머 전구체를 제공하는 단계를 포함한다. 어떤 실시예들에서, 상기 수직적으로 에칭하는 단계는, 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하면서, 약 10 내지 120 °C의 온도 및/또는 약 5 내지 100 mTorr의 압력에서 유지되는 상기 프로세싱 챔버 내에

서 수행된다. 어떤 실시예들에서, 상기 수평적으로 예칭하는 단계는, 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하면서, 약 0 내지 400 °C의 온도 및 약 0.1 내지 10 Torr의 압력에서 유지되는 상기 프로세싱 챔버 내에서 수행된다. 어떤 실시예들에서, 이러한 동작 동안, 상기 압력은 약 5 Torr 아래, 심지어 약 2 Torr 아래일 수도 있다. 어떤 실시예들에서, 이러한 동작 동안, 상기 온도는 약 250 °C 보다 아래, 심지어 약 150 °C 아래일 수도 있다. 어떤 실시예들에서, 이러한 동작 동안, 상기 온도는 약 50 내지 400 °C, 또는 보다 특별히는, 약 10 내지 400 °C 일 수도 있다.

[0015] 어떤 실시예들에서, 상기 수직적으로 예칭하는 단계에서 사용되는 이온 종들을 포함하는 플라즈마는 유도성-커플링된 RF 전력에 의해 생성되고 유지되는 유도성-커플링된 플라즈마이다. RF 전력은 약 13 내지 60 MHz의 주파수를 가지고 반면 또한 약 400 kHz 내지 14 MHz의 주파수(약 13.56 MHz와 같은 주파수)를 가지는 기판-바이어스된(substrate-biased) RF 전력에 의해 생성되고 유지된다. 어떤 실시예들에서, 기판-바이어스된 RF 전력은 상기 기판에 대해 약 100 내지 1000 볼트의 전압을 가지고, 보다 특별히는 상기 기판에 대해 약 100 내지 500 볼트의 전압을 가진다. 어떤 실시예들에서, 유도성-커플링된 플라즈마를 채용하는 방법들은 약 100 내지 2000 Hz의 펄스 레이트로 상기 기판-바이어스된 RF 전력을 펼성하는 단계를 포함하고, 또는 보다 특별히는 약 100 내지 300 Hz의 펄스 레이트로, 그리고 약 10% 내지 90%의 듀티 싸이클을 가지고, 또는 보다 특별히는 약 10% 내지 60%의 듀티 싸이클을 가지고 상기 기판-바이어스된 RF 전력을 펼성하는 단계를 포함한다. 어떤 실시예들에서, 유도성-커플링된 RF 전력은 약 500 내지 1900 와트, 또는 보다 특별히 약 500 내지 600 와트이다. 어떤 실시예들에서, 유도성-커플링된 RF 전력은 제1 생성 코일 및 제2 생성 코일을 포함하는 생성 코일들에 의해 생성되고, 상기 제1 생성 코일은 상기 프로세싱 챔버의 내부 영역에 유도성-커플링된 RF 전력을 제공하고, 상기 제2 생성 코일은 상기 프로세싱 챔버의 외부 영역에 유도성-커플링된 RF 전력을 제공하고, 상기 유도성-커플링된 RF 전력의 총합은 약 0.1 내지 1.5의 비율로 제1 생성 코일과 제2 생성 코일 간에서 나눠진다(split). 어떤 실시예들에서, 상기 수직적으로 예칭하는 단계에서 사용되는 자유 라디칼 종들을 포함하는 플라즈마는 RF 전력에 의해 생성되고 유지된다.

[0016] 어떤 실시예들에서, 상기 수직적으로 예칭하는 단계, 상기 수평적으로 예칭하는 단계, 및 텅스텐-함유 재료의 제1 층 및 제2 층을 중착하는 동작들은 동일한 프로세싱 챔버 내에서 수행된다. 어떤 실시예들에서, 1 이상의 상기 수직적으로 예칭하는 단계 및 상기 수평적으로 예칭하는 단계가 텅스텐-함유 재료의 상기 제1 층 및 상기 제2 층의 중착과는 달리 상이한 프로세싱 챔버에서 행해질 수도 있다.

[0017] 텅스텐-함유 재료로 3-D 구조물들을 충진하기 위해 본 명세서에 개시된 어떤 방법들은 텅스텐-함유 재료의 제2 층을 중착하는 단계 후에 수직적으로 예칭하는 단계 및 수평적으로 예칭하는 단계, 및 그 후에 상기 텅스텐-함유 재료의 상기 제2 층을 상기 수평적으로 예칭하는 단계 및 상기 수평적으로 예칭하는 단계 이후에 상기 구조물 내에서 텅스텐-함유 재료의 상기 제3 층을 중착하는 단계를 더 포함할 수도 있다. 상기 중착하는 단계는, 상기 제1 층 및 상기 제2 층에 의해 충진되지 않은 채로 남겨진 상기 복수의 내부들의 부분의 적어도 일부를 상기 제3 층이 충진하도록, 상기 텅스텐-함유 전구체 및 상기 환원제 간의 반응을 통해 행해질 수도 있다.

[0018] 또한, 텅스텐 재료로 부분적으로 제조된 반도체 기판의 3-D 구조물을 충진하는 1 이상의 통합 틀들이 본 명세서에 개시된다. 어떤 실시예들에서, 통합 틀은, 1 이상의 프로세싱 챔버들; 상기 3-D 구조물을 가지는 상기 기판을 홀딩하도록 구성된 각 프로세싱 챔버 내의 기판 홀더; 텅스텐-함유 전구체 및 환원제를 상기 1 이상의 프로세싱 챔버들 중 적어도 하나 내로 도입하도록 구성된 1 이상의 가스 유입구들; 상기 1 이상의 프로세싱 챔버 중 적어도 하나 내에서 유도성-커플링된 플라즈마를 생성하고 유지하도록 구성된 제1 전원 및 제2 전원으로서, 상기 제1 전원은 상기 플라즈마에 유도성-커플링된 RF 전력을 공급하고, 상기 제2 전원은 상기 플라즈마에 기판-바이어스된 RF 전력을 공급하는, 상기 제1 전원 및 상기 제2 전원; 상기 1 이사의 프로세싱 챔버들 중 적어도 하나와 멀리 떨어졌지만 유체적으로 연결된 플라즈마-생성 챔버 내에서 제2 플라즈마를 생성하고 유지하도록 구성된 제3 전원; 및 기계 관독 가능한 코드의 형식인 인스트럭션들(instructions)을 가지는 컨트롤러로서, 상기 컨트롤러는 상기 인스트럭션들을 수행하도록 구성되는, 상기 컨트롤러를 포함한다.

[0019] 어떤 실시예들에서, 상기 인스트럭션들은, 텅스텐-함유 재료의 층이 상기 텅스텐-함유 전구체 및 상기 환원제 간의 화학적 반응을 통해 상기 3-D 구조물 내에 중착되도록 상기 1 이상의 프로세싱 챔버들 중 적어도 하나 내로 텅스텐-함유 전구체의 유동 및 환원제의 유동을 도입하기 위해 상기 1 이상의 가스 유입구들을 동작시키는 인스트럭션들을 포함한다.

[0020] 어떤 실시예들에서, 상기 인스트럭션들은, 약 13 내지 60 MHz의 주파수로 상기 제1 전원을 동작시켜, 약 500 내지 1900 와트의 RF 전력을 생성하는 인스트럭션들을 포함한다. 어떤 실시예들에서, 상기 인스트럭션들은, 약

400 kHz 내지 15 MHz 의 주파수 (보다 특별히는 13.56 MHz) 로, 그리고 상기 기판에 대해 약 100 내지 1000 볼트의 전압으로, 약 100 내지 약 2000 Hz 의 펄스 레이트 (pulse rate) 를 가지고, 또한 약 10% 내지 90%의 둑티 싸이클 (duty cycle) 을 가지고, 상기 제2 전원을 동작시키는 인스트럭션들을 포함한다.

[0021] 또한, 측벽, 상기 측벽의 복수의 구멍들, 및 상기 구멍들을 통해 유체적으로 접속 가능한 복수의 내부 영역들을 포함하는 3-D 구조물을 충진하는 방법들이 개시되는데, 상기 방법들은 하기의 동작들을 포함한다. 상기 하기의 동작은, 상기 제1 층이 복수의 구조물 내부들을 부분적으로 충진하여 비충진된 구조물 내부들의 일부분을 남기도록 3-D 구조물 내에서 텅스텐-함유 재료의 제1 층을 증착시키는 동작; 상기 복수의 구조물 내부들로부터 상기 제1 층의 부분들을 실질적으로 제거하지 않고 제1 활성화된 에칭 재료를 사용하여 상기 제1 층의 부분들이 상기 측벽으로부터 제거되도록 상기 텅스텐-함유 재료의 상기 제1 층을 증착하는 동작 후에 수직적으로 에칭하는 동작; 제2 활성화된 에칭 재료를 사용하여 상기 텅스텐-함유 재료의 상기 제1 층의 부분들이 상기 복수의 구조물 내부들로부터 제거되도록 상기 텅스텐-함유 재료의 제1 층을 증착시키는 동작 이후에 수평적으로 에칭하는 동작; 및 상기 제1 층에 의해 충진되지 않은 채로 남아있는 상기 구조물 내부들의 적어도 일부분을 상기 제2 층이 충진하도록 수평적으로 에칭하는 동작 및 수직적으로 에칭하는 동작 이후에 3-D 구조물 내에서 상기 텅스텐-함유 재료의 제2 층을 증착하는 동작이다.

[0022] 또한, 측벽, 상기 측벽의 복수의 구멍들, 및 상기 구멍들을 통해 유체적으로 접속 가능한 복수의 내부 영역들을 포함하는 3-D 구조물을 충진하는 방법들이 본 명세서에 개시된다. 상기 방법들은, 상기 3-D 구조물을 가지는 상기 기판을 제공하는 단계로서, 상기 3-D 구조물은 3-D 구조물의 측벽 및/또는 구조물 구멍들을 덮는 텅스텐-함유 재료의 제1 층을 이미 가지고, 상기 3-D 구조물의 상기 복수의 내부 영역들을 부분적으로 충진하지만, 상기 제1 층에 의해 충진되지 않은 채로 남겨진 상기 복수의 내부 영역들의 일부분을 가진, 상기 기판을 제공하는 단계; 상기 복수의 구조물 내부들로부터 상기 제1 층의 부분들을 실질적으로 제거하지 않고 상기 측벽 및/또는 상기 구조물 구멍들로부터 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 균일하게 제거하도록 수직적으로 에칭하는 단계; 및 상기 복수의 내부 영역들로부터 상기 텅스텐-함유 재료의 상기 제1 층의 부분들을 제거하도록 수평적으로 에칭하는 단계를 포함한다. 이러한 특정 실시예들에서, 상기 제1 활성화된 에칭 재료는 1 이상의 대전된 (charged) 종들을 포함하고, 상기 제2 활성화된 에칭 재료는 1 이상의 중성 종들을 포함한다. 이러한 특정한 방법들은 상기 수직적으로 에칭하는 단계 및 상기 수평적으로 에칭하는 단계 이후에 상기 텅스텐-함유 재료의 제2 층을 증착하는 단계를 더 포함할 수도 있다.

[0023] 또한, 측벽, 상기 측벽의 복수의 구멍들, 및 상기 구멍들을 통해 유체적으로 접속 가능한 복수의 내부 영역들을 포함하는 3-D 구조물을 충진하는 방법들이 본 명세서에 개시된다. 상기 방법들은, 상기 3-D 구조물 내에서 텅스텐-함유 재료의 제1 층을 증착하는 단계; 이온 에칭 종들을 포함하는 플라즈마를 생성하고 상기 이온들의 일부분이 상기 구조물의 바닥을 향하여 지향되도록 상기 이온들에 전자기장을 인가함으로써 수직적으로 에칭하는 단계 이후에 수직적으로 에칭하는 단계; 상기 3-D 구조물을 가지는 상기 기판을 홀딩하는 상기 프로세스 챔버로부터 멀리 떨어진 자유 라디칼 종들을 생성하고 상기 프로세스 챔버로 상기 자유 라디칼 종들을 도입함으로써 상기 수직적으로 에칭하는 단계 이후에 수평적으로 에칭하는 단계; 및 상기 수평적으로 에칭하는 단계 이후에 3-차원적인 구조물에 상기 텅스텐-함유 재료의 제2 층을 증착하는 단계를 포함한다.

### 도면의 간단한 설명

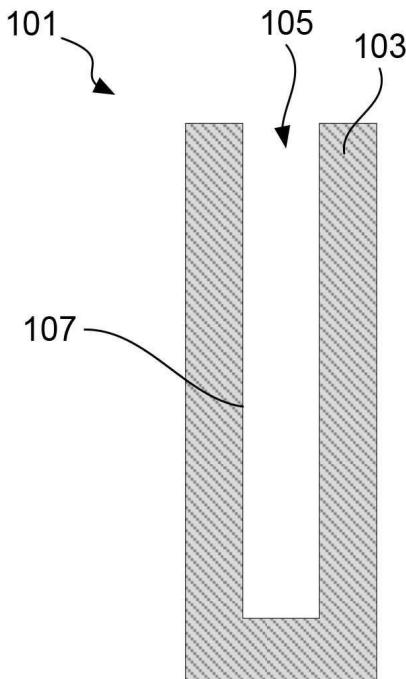

[0024] 도 1a는 텅스텐 재료로 충진되도록 디자인될 수도 있는 기판 내의 수직적 피쳐의 단면도를 나타낸다.

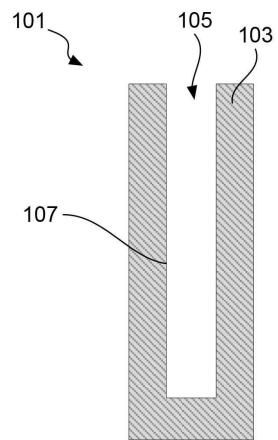

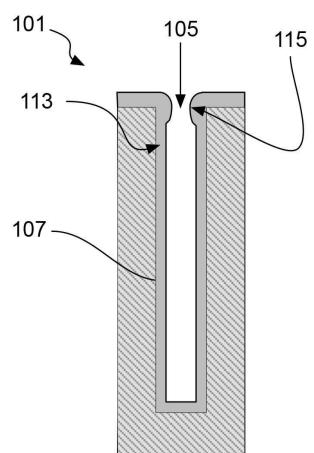

도 1b는 바닥, 측벽들, 및 피쳐의 구멍들을 라이닝하는 (lining) 언더-층의 존재에 기인하여, 도 1a와 유사한 피쳐이지만 요각의 프로파일을 가지는 예시를 나타낸다.

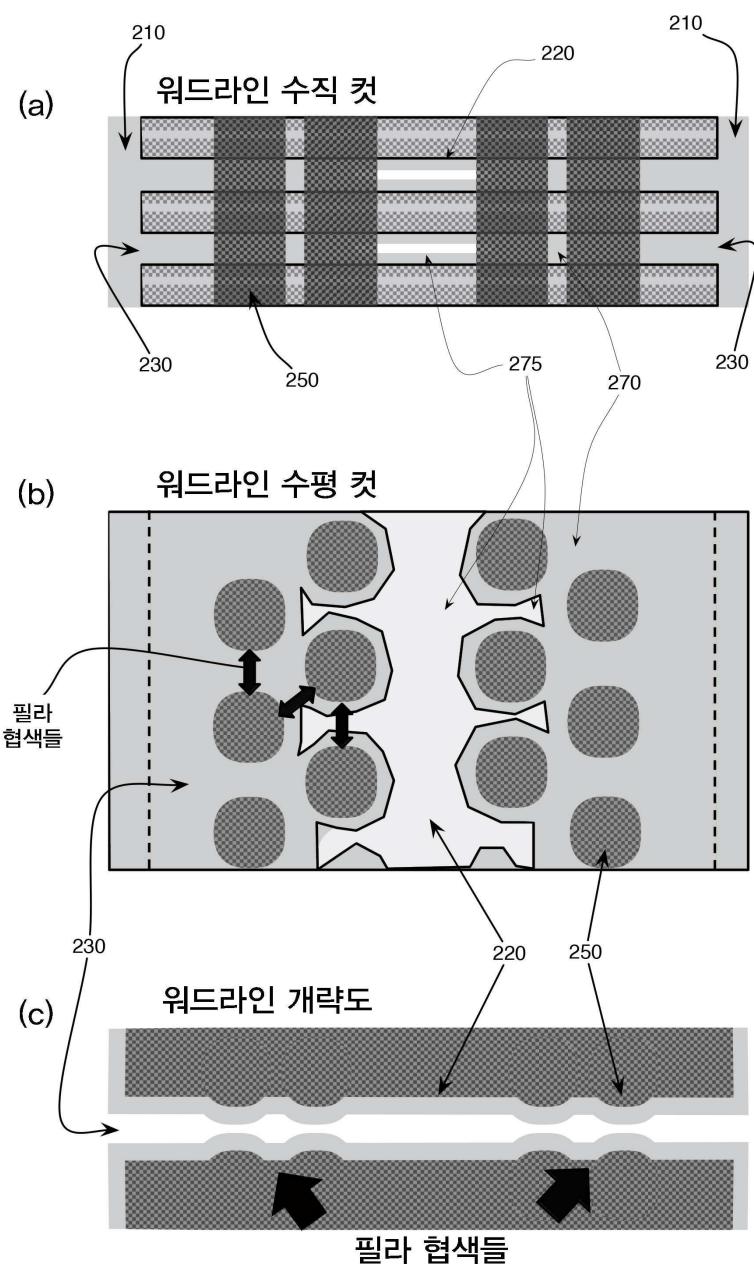

도 1c는 러프하게 그것의 측벽의 중앙에서 협색을 보이는 수평적 피쳐의 위에서 내려다본 평면도를 도시한다. 어떤 실시예들에서, 이러한 수평적 피쳐들은 수직적으로 접속된 메모리 구조에서 "워드라인" (wordline) 으로 지칭되는 것일 수도 있다.

도 2a는 VNAND 스택들 (좌측, 우측), 중앙 수직적 구조물, 및 중앙 수직적 구조물의 대향 측벽들 상의 구멍들을 가진 복수의 적층된 수평적 피쳐들을 가지는 (반도체 기판 상에 형성되는) 3D 수직적 메모리 NAND (VNAND) 구조물의 측단면도를 도시한다.

도 2b는 도 2a의 점선의 수평선에 의해 나타내어진 수평적 섹션을 통해 취해진 단면을 가진 도 2a의 측면도에 도시된 동일한 VNAND 구조물의 위에서 내려다본 단면도를 나타낸다.

도 3의 (a) 는 도 2a에 도시된 것과 유사한 VNAND 구조물의 수직 단면 (컷) 을 보이지만, 도 3의 (a) 에서는 단일 쌍의 워드라인들 및 부가적으로 개략적으로 워드라인 내에 보이드들의 형성으로 이어지는 텅스텐 충진 프로세스를 도시하는 것에 초점을 맞추었다.

도 3의 (b) 는 도 2a에 도시된 것과 유사한 VNAND 구조물의 수평 단면 (컷) 을 보이지만, 도 3의 (a) 에서와 같은 보이드들의 존재를 또한 개략적으로 도시한다.

도 3의 (c) 는 위로부터 단면적으로 보여지는 단일 워드라인을 나타내고, 어떻게 일반적으로 도면에 도시된 필라들의 존재에 기인하여 텅스텐 재료의 컨포멀 (conformal) 증착이 보여지는 워드라인의 내부를 핀치-오프하는 것을 시작하는지를 도시한다.

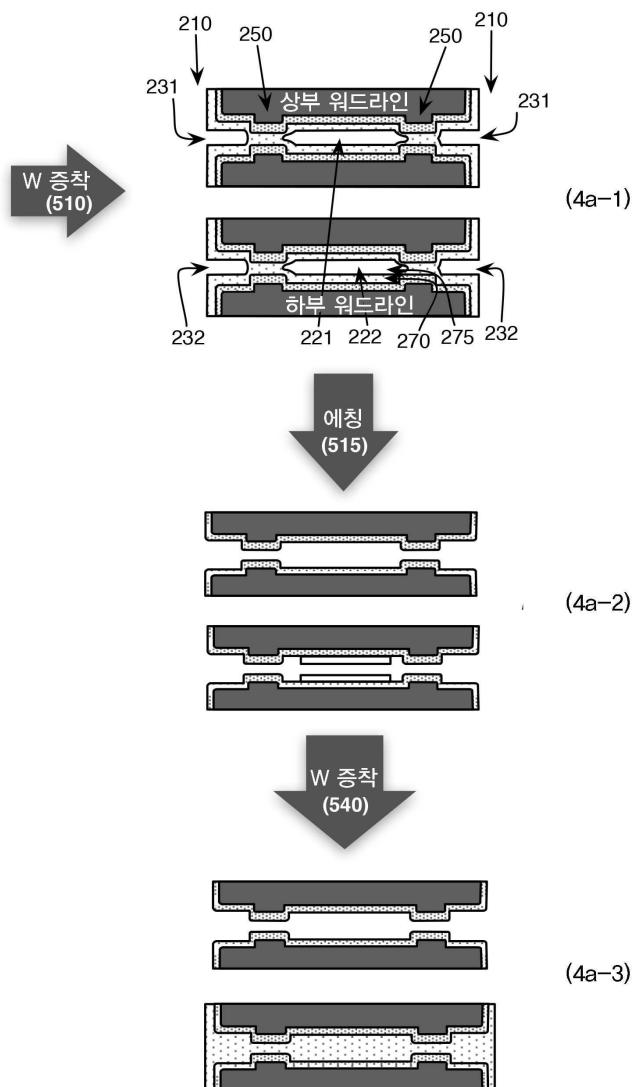

도 4a-1 내지 도 4a-3은 일련의 텅스텐 증착 및 에칭 단계들 동안 다양한 스테이지들에서의 수직적 구조물 및 그들의 연관된 텅스텐 증착물의 패턴들 내에 상이한 수직적 깊이들에서의 2 개의 워드라인들을 개략적으로 도시한다.

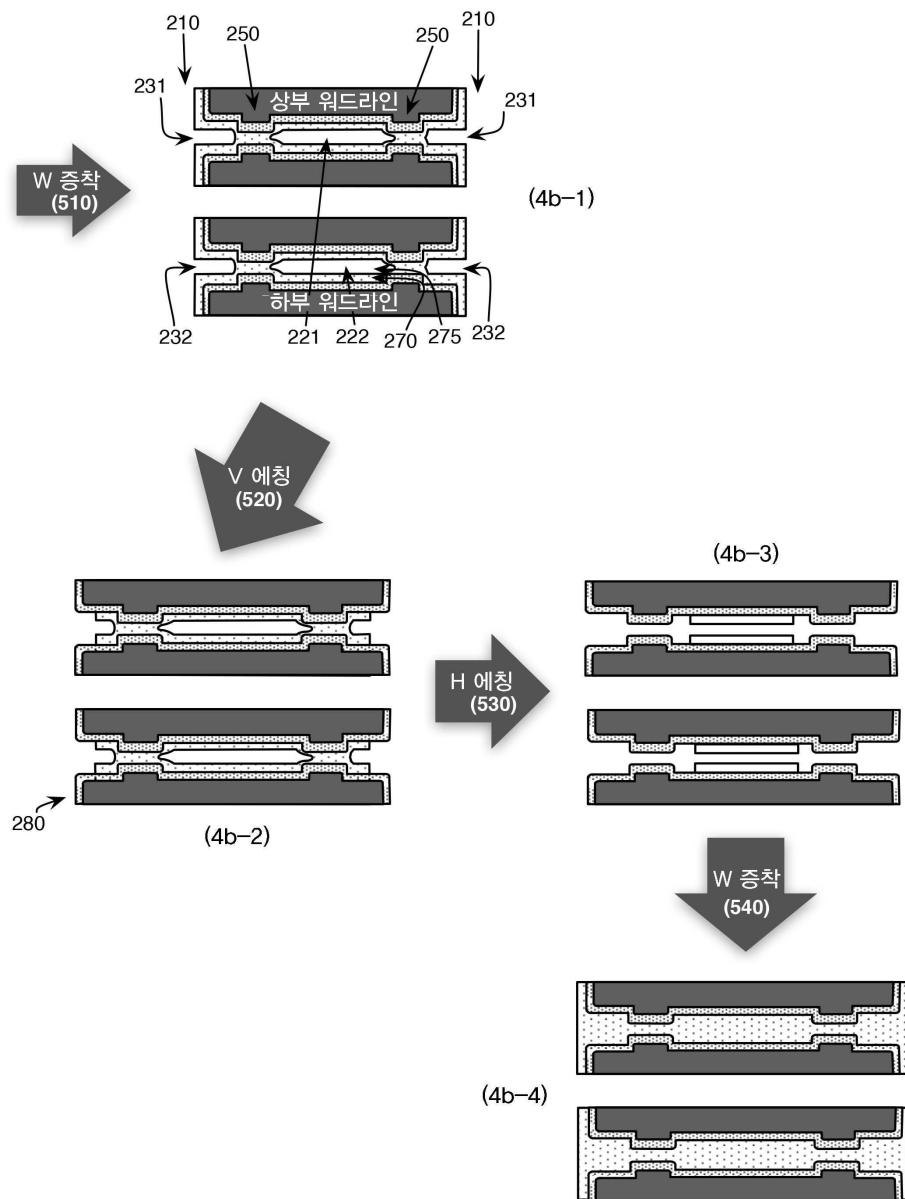

도 4b-1 내지 도 4b-4는 수평적 에칭과 수직적 에칭을 수반하는 일련의 텅스텐 증착 및 에칭 단계들 동안 다양한 스테이지들에서의 수직적 구조물 및 그들의 연관된 텅스텐 증착물의 패턴들 내에 상이한 수직적 깊이들에서의 2 개의 워드라인들을 개략적으로 도시한다.

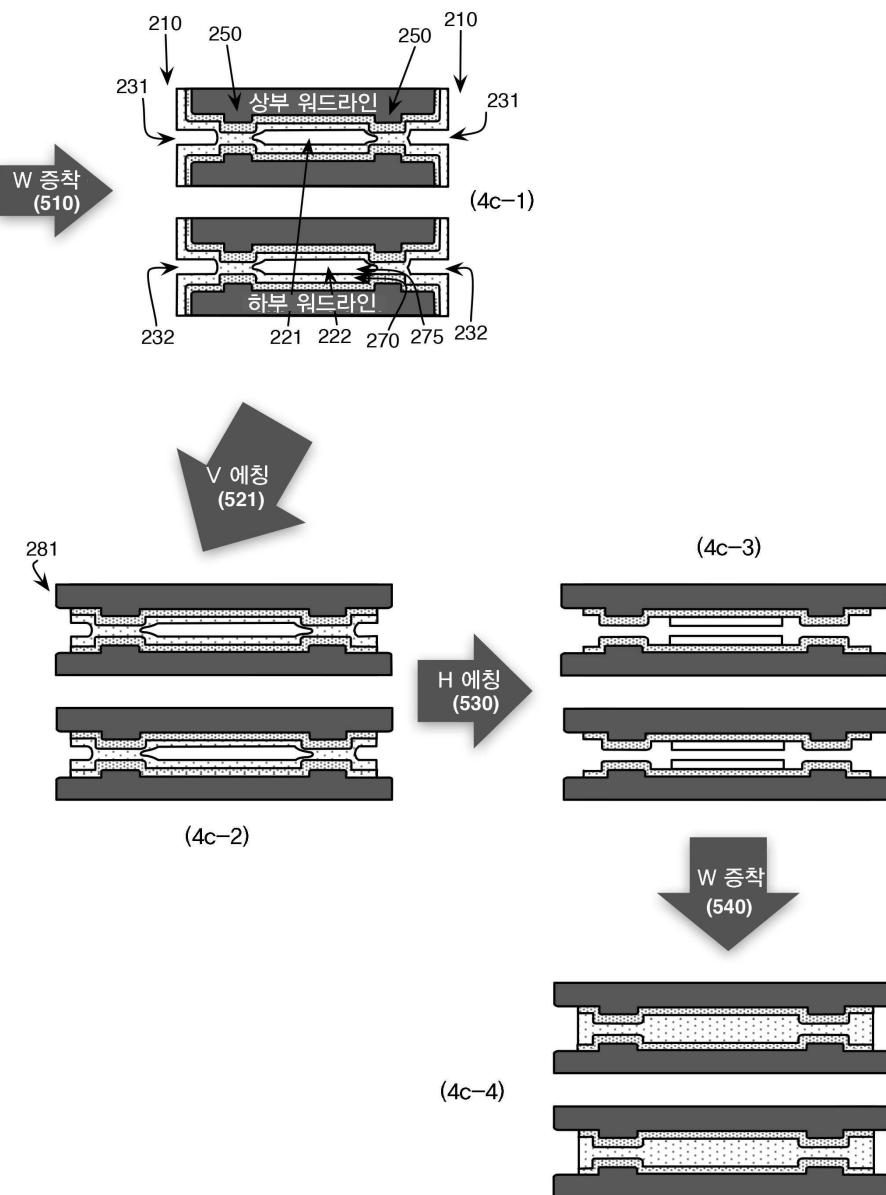

도 4c-1 내지 도 4c-4는 도 4b-1 내지 도 4b-4 에 도시된 것과 유사한 수평적 에칭과 수직적 에칭을 수반하는 일련의 텅스텐 증착 및 에칭 단계들 동안 다양한 스테이지들에서의 수직적 구조물 및 그들의 연관된 텅스텐 증착물의 패턴들 내에 상이한 수직적 깊이들에서의 2 개의 워드라인들을 개략적으로 도시하지만, 활성화된 에천트 재료는 수직적 구조물의 측벽 상에서의 텅스텐 증착을 방지하기 위해 티타늄 나이트라이드의 얇은 층을 제거하도록 사용된다.

도 4d는 수평적 퍼쳐들을 가지는 3-D 수직적 구조물들의 실질적으로 균일하고/보이드 프리한 텅스텐 충진을 달성하기 위해 본 명세서에 개시되는 특정 기술들 및 동작들을 채용함으로써 얻어지는 결과를 도시한 전자 현미경 사진 (electron micrograph) 을 표시한다.

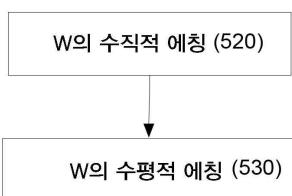

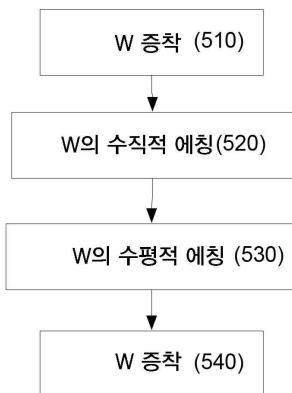

도 5a는 특정 실시예들과 일치하는 수평적 텅스텐 에칭에 이어지는 수직적 텅스텐 에칭 동작을 도시한 플로우챠트를 나타낸다.

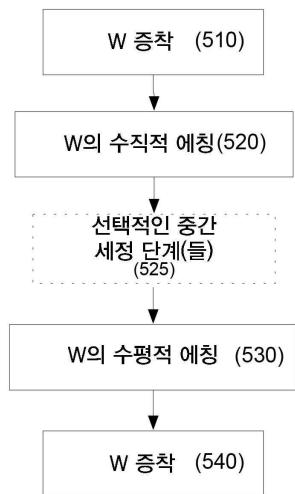

도 5b는 도 5a에서 보여지는 일련의 수평적 및 수직적 텅스텐 에칭 동작들을 채용하는 텅스텐 증착 방법론을 도시한 플로우챠트를 나타낸다.

도 5c는 도 5a 및 도 5b에 보여지는 수직적 에칭 및 수평적 에칭 동작들 간의 개재하는 세정 동작을 채용한 텅스텐 증착 방법론을 도시한 플로우챠트를 나타낸다.

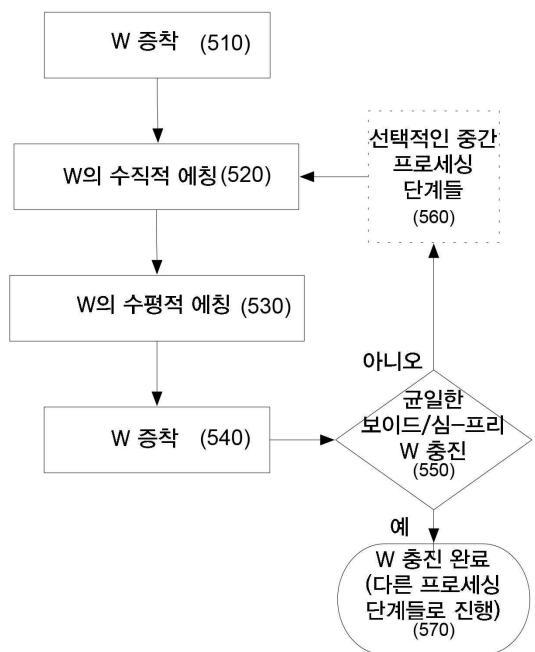

도 5d는 일련의 다중 텅스텐 증착 및 에칭 동작들을 채용한 텅스텐 증착 방법론을 도시한 플로우챠트를 나타낸다.

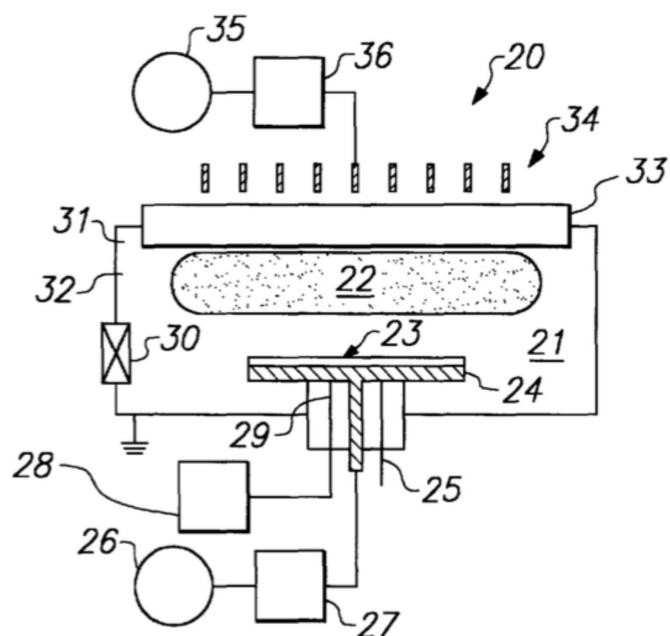

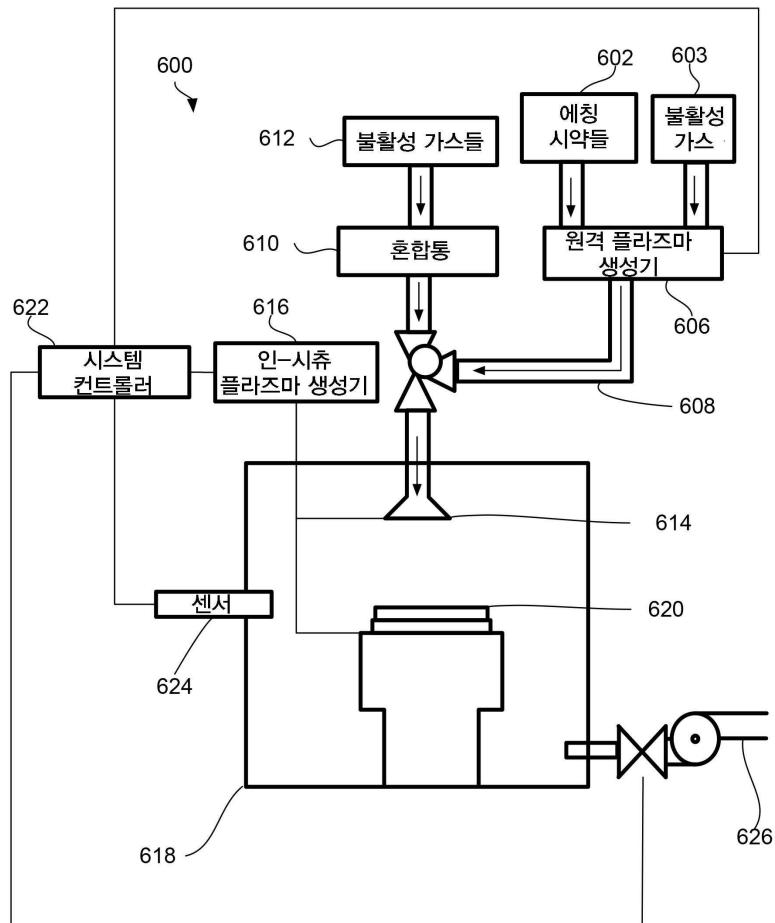

도 6은 본 명세서에 개시된 특정 실시예들에 따른, 특정 텅스텐 증착 및/또는 에칭 동작들을 수행하도록 채용될 수도 있는 프로세싱 챔버 및 관련된 하드웨어를 개략적으로 도시한다.

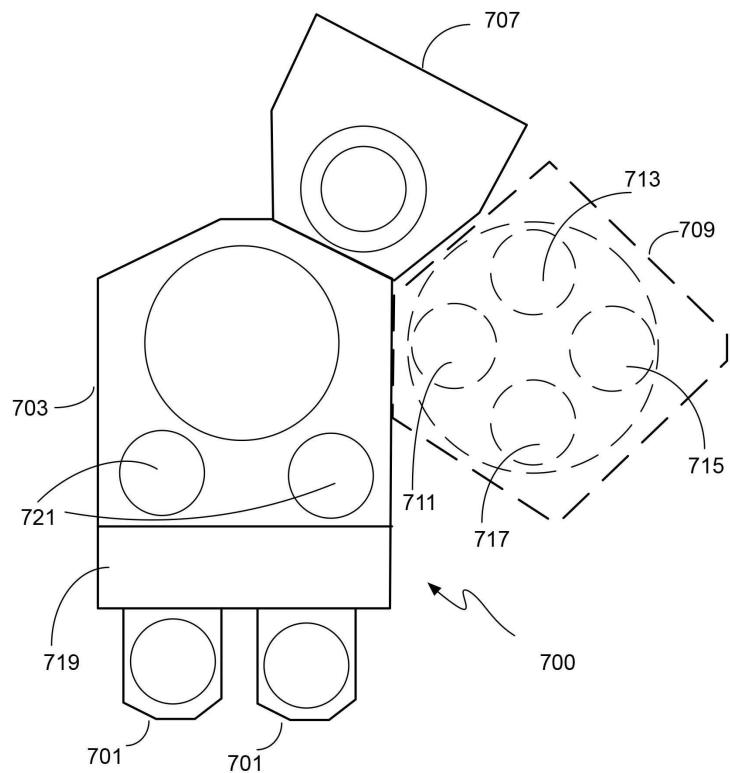

도 7은 본 명세서에 개시된 특정 실시예들에 따른 텅스텐 증착 프로세스들을 수행하기에 적합한 CVD 프로세싱 시스템을 개략적으로 도시한다.

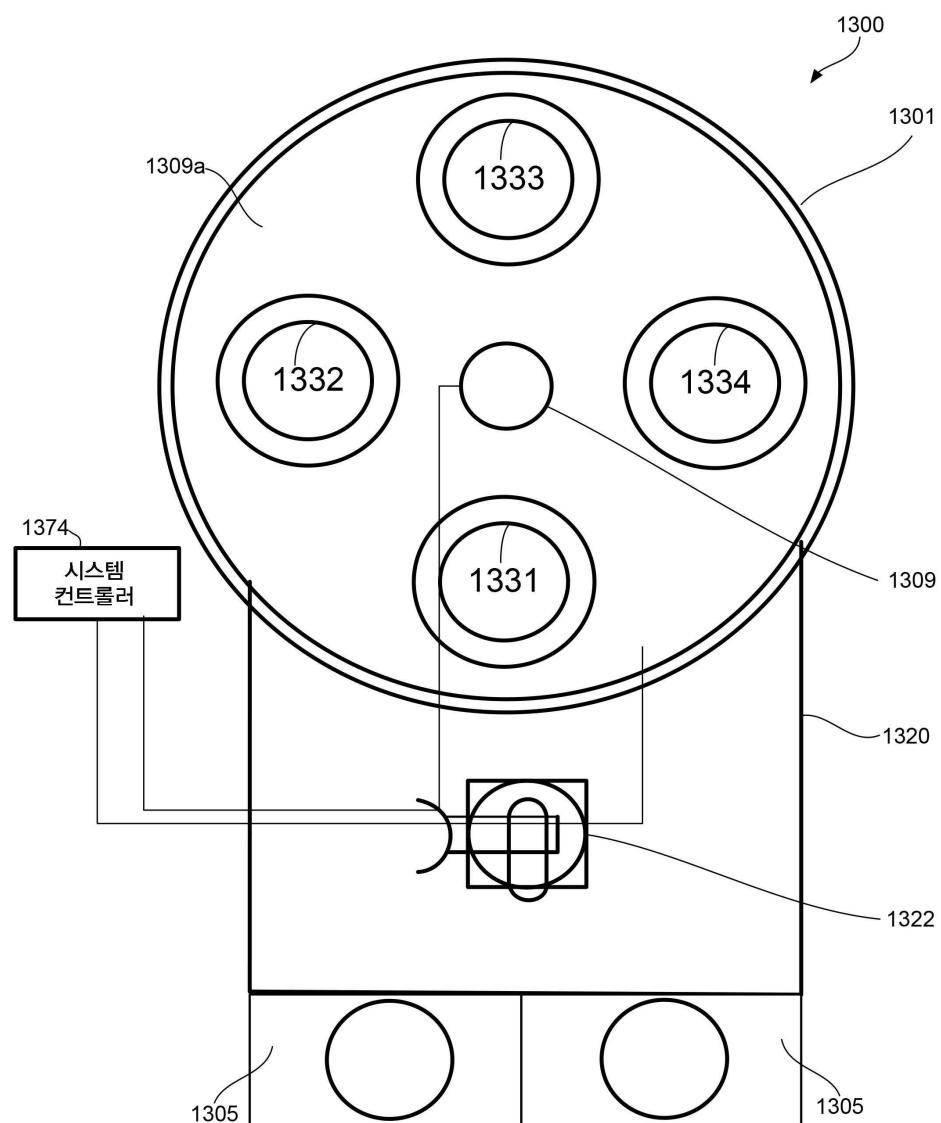

도 8은 본 명세서에 개시된 특정 텅스텐 증착 및/또는 에칭 동작들을 수행하는데 사용될 수도 있는 다중-스테이션 기판 프로세싱 장치를 개략적으로 나타낸다.

도 9는 본 명세서에 개시된 특정 수직적 에칭 동작들에 채용되는 인 시츄 플라즈마를 생성하기 위해 사용될 수도 있는 유도성 커플링된 플라즈마 반응기의 실시예를 개략적으로 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0025] 이하의 설명에서, 다양한 구체적 상세들이 본 발명의 완전한 이해를 제공하기 위해 제시된다. 그러나, 본 발명은 이러한 구체적 상세들 중 일부 또는 전부 없이도 실시될 수도 있다. 일부 예시들에서, 잘 알려진 프로세스 동작들은, 불필요하게 개시된 발명 컨셉들을 모호하게 하지 않기 위해 상세하게 기술되지 않았다. 게다가, 구체적인 상세한 실시예들의 맥락에서 본 발명이 기술될 것이지만, 이러한 구체적인 상세한 실시예들은 개시된 발

명 컨셉들의 범위를 제한하고자 의도되지 않았다는 점이 이해된다.

[0026] IC 디자인 및 제조에서의 텅스텐 재료의 빈번한 채용에도 불구하고, 그것의 사용과 관련된 어려움들이 그럼에도 존재한다. 예를 들어, 작은 피쳐들 또는 고 종횡비를 가지는 피쳐들 내로 텅스텐 재료를 증착하는 것은 증착된 텅스텐 내에 보이드 (void)의 형성을 야기할 수도 있다. 보이드는 간단하게는 주위의 영역들이 채워진 후에 남겨진 구조물 (structure) 또는 피쳐 (feature) 내의 영역이다. 종종, 보이드 형성은 피쳐의 입구 근처에서 증착된 재료의 불균형적인 축적에 의해 야기되고, 그 결과 입구는 막히게 되고, 내부 볼륨 (volume) 내에 추가적인 증착을 방지하여 피쳐의 내부 볼륨을 핀치 오프 시킨다 (pinch off). 일단 막히고 핀치 오프되면, 반응성 증착 전구체 (precursor) 종들은 내부 볼륨 내로의 어떠한 진입 경로도 가지지 않아, 이러한 영역들 내의 더 이상의 증착이 발생되는 것을 방지한다. 다른 경우에는, 핀치-오프가 없다고 하더라도, (보톰-업 충진 (bottom-up fill)을 보이는 것보다는) 텅스텐 재료가 측벽으로부터 바깥으로 증착되기 쉽다는 사실에 기인하여 심 (seam) 이 증착된 텅스텐 재료에 보여질 수도 있다. 따라서, 이러한 심은 통상적으로 피쳐의 중심 축의 상당한 부분을 따라 길어지고, 피쳐의 바닥을 향해 연장된다. 때때로, 충진 프로세스 및 이어지는 화학적-기계적 평탄화가 심을 개방한 후에 심이 필드 영역에 가깝게 연장되는 경우와 같이 심의 존재는 보이드 형성으로 이끌 수도 있다. 아무튼, 심 및 보이드는 높은 저항, 기판 오염, 재료의 손실을 야기할 수도 있고, 그렇지 않으면 반대로 집적 회로의 전기적 특성에 영향을 미칠 수도 있다. 이에 따라, 개선된 방법, 장치 및 시스템이 기판 구조물 및 피쳐의 보이드-프리 (void-free) 및 심-프리 (seam-free) 텅스텐 충진을 달성하기 위해 반도체 제조 기술에 필요된다.

[0027] 이에 따라, 본 명세서에 기술되는 것은, 보이드 및 경계선의 형성을 최소화하거나 제거하면서 반도체 기판 구조물 및 피쳐의 균일한 텅스텐 충진을 달성하기 위한 방법, 장치 및 시스템이다. 이러한 균일한 텅스텐 충진의 어플리케이션들은 로직 및 메모리 컨택트 충진 (logic and memory contact fill), DRAM 매립된 워드라인 충진 (DRAM buried wordline fill), 수직으로 집적된 메모리 게이트/워드라인 충진 (vertically integrated memory gate/wordline fill), 및 TSV (3D integration) 을 포함한다. 본 명세서에 기술되는 방법, 장치 및 시스템은, 이하에서 기술될 것과 같이, 수직 NAND (VNAND) 구조물 내의 수평적 워드라인 (wordline) 과 같은 수평적 피쳐뿐만 아니라 예를 들어 비아와 같은 수직적 피쳐를 충진하는데 이용될 수도 있다. 충진될 구조물 및 피쳐를 가지는 기판은 200, 300 또는 450 mm 반도체 웨이퍼, 혹은 약 200 내지 300 mm 직경을 가지는 웨이퍼, 혹은 약 300 내지 450 mm 직경을 가지는 웨이퍼, 혹은 약 450 mm 초과의 직경을 가지는 웨이퍼, 혹은 여타의 적절하게 사이징된 (sized) 웨이퍼일 수도 있다. 게다가, 방법, 장치, 및 시스템은 패널, 디스플레이 기판 등을 포함하는 다른 종류의 기판 상에 텅스텐으로 피쳐를 충진하는데 사용될 수도 있다.

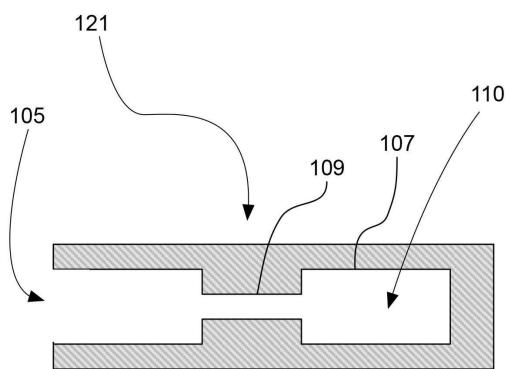

[0028] 위에 지적된 바와 같이, 텅스텐 재료로 반도체 기판 구조물 및 피쳐를 증진하는 것과 관련된 상당한 문제점은 텅스텐 충진 프로세스 동안의 심 및 보이드의 형성이다. 특히, 1 이상의 협소한 (narrow) 및/또는 요각의 (re-entrant) 구멍들 (openings) 을 가지는 것, 또는 협색들 (constrictions), 또는 단순히 상대적으로 고 종횡비를 가지는 것과 같이 특성화될 수 있는 피쳐들을 가지는 구조물들이 문제가 될 수도 있다. 도 1a는 텅스텐 재료로 충진되도록 디자인될 수도 있는 기판 (103) 의 수직적 피쳐 (101) 의 단면을 나타낸다. 이러한 수직적 피쳐는 피쳐 구멍 (105) 및 측벽 (107) 을 가진다. 수직적 피쳐 (101) 는 적어도 약 2:1 의 종횡비를 가질 수도 있고, 또는 적어도 약 4:1 의 종횡비를 가질 수도 있고, 또는 적어도 약 6:1 의 종횡비를 가질 수도 있고, 또는 적어도 약 10:1 의 종횡비를 가질 수도 있고, 또는 적어도 약 20:1 의 종횡비를 가질 수도 있고, 또는 심지어 그 이상의 종횡비를 가질 수도 있다. 피쳐 구멍 (105) 은 약 10 나노미터 내지 500 나노미터, 예를 들어 약 25 나노미터 내지 300 나노미터의 직경을 가질 수도 있다.

[0029] 유사하게, 도 1b는 피쳐 (101) 의 바닥, 측벽들, 및 구멍을 라이닝하는 (lining) 언더-층 (113) 의 존재에 기인한, 유사하지만 요각의 프로파일 (re-entrant profile) 을 가지는 피쳐 (101) 의 예시를 도시한다. 요각의 프로파일은, 피쳐 구멍 및 피쳐의 바닥 또는 단혀진 단부 사이의 어딘가에 단면상의 내로우잉 (narrowing) 을 보임으로써 그에 따라 프로파일 내에서 "보틀넥" (bottleneck) 을 보이는 것이다. 어떤 케이스에서는, 요각의 프로파일은 피쳐 구멍으로부터 한쪽으로 서서히 좁아질 수도 있으며, 또는 피쳐 구멍 그 자체 바로 거기에서의 오버행 (overhang) 을 포함할 수도 있다. 도 1b는 후자의 예시를 도시하는데, 재차 설명하자면, 여기서 내로우잉은 피쳐의 바닥 위 혹은 피쳐 측벽 (107) 의 더 아래 보다 피쳐 구멍 근처에서 더 두꺼운 언더-층 (113) 의 존재에 기인한 것이고, 이에 따라 오버행 (115) 을 형성한다. 언더-층 (113) 은 예를 들어, 발산 배리어 층 (diffusion barrier layer), 접착 층 (adhesion layer), 또는 앞서 언급한 것의 임의의 조합, 또는 여타의 잠재적으로 유용하거나 유리한 재료의 층일 수도 있다.

[0030] 어떤 실시예들에서, 피쳐의 측벽에서의 1 이상의 협색들이 균일한 텅스텐 충진을 달성하는데 어려움을 만든다.

도 1c는 내부 영역 (110) 에의 접근을 보이는 그것의 측벽 (107) 의 중앙에서 러프하게 협색 (109) 을 보이는 예시적인 수평적 피쳐 (121) 를 위에서 내려다본 평면도를 도시한다. 어떤 실시예들에서, 이러한 수평적 피쳐는 이하에서 더 자세히 기술될 3-D 수직적 NAND (VNAND) 구조물들 중 하나와 같은 수직적으로 집적된 메모리 구조물에서 "워드라인" (wordline) 으로서 지칭되는 것일 수도 있다. 도 1d는 수직적 구조물 (122) 로의 구멍 (105) 을 가짐으로써 수직적 구조물 (122) 의 일부분을 형성하는 동일한 수평적 피쳐 (121) 의 측면도를 도시한다. 어떤 실시예들에서, 그리고 어떤 증착 케미스트리들 (chemistries) 및 프로세스들에 대해, 이러한 구조물들에서 균일한 텅스텐 충진을 달성하는 것이 도전적일 수 있는데, 그 이유는 증착 전구체의 각각의 층들의 충분한 양이 수직적으로 아래로 구조물 (122) 의 베이스까지 이동해야만 하고, 그 이후 수평적으로 수평적 피쳐 (121) 를 통과해 이동해야만 하고, 특히 협색 (109) 의 영역을 통과해 이동해야만 한다. 다시 한번, 도 1c가 수평적 피쳐 (121) 및 수축 (109) 을 나타내는 위에서 내려다본 평면도를 나타내고, 반면 도 1d는 동일한 것을 나타내는 측면도를 나타낸다는 점에 주목하라. 따라서, 이 실시예에서, 수축 (109) 이 피쳐 (121) 의 측벽 (107) 으로부터 수평적으로 그리고 수직적으로 안쪽으로 연장되는 것이 이러한 도면들로부터 명확하다. 그러나, 다른 실시예들에서는, 피쳐 내의 협색들이 단지 2개의 단면적 차원 (cross-sectional dimension) 중 하나에 존재할 수도 있고, 1개 또는 2개의 차원들 중 어떤 것인 임의의 종류의 협색이 균일한 텅스텐 충진을 보다 도전적으로 만들 수도 있다.

[0031] 어떤 실시예들에서, 반도체 기판 상에 충진될 구조물은 수직적 구조물의 측벽에 구멍들을 갖는 복수의 수평적 피쳐를 가지는 수직적 구조물일 수도 있고, 이 구멍들은 피쳐 구멍들을 통해 메인 수직적 구조물로부터 유체적으로 (fluidically) 접근가능한 (accessible) (수평적 피쳐들의) 복수의 내부 볼륨으로 이어진다.

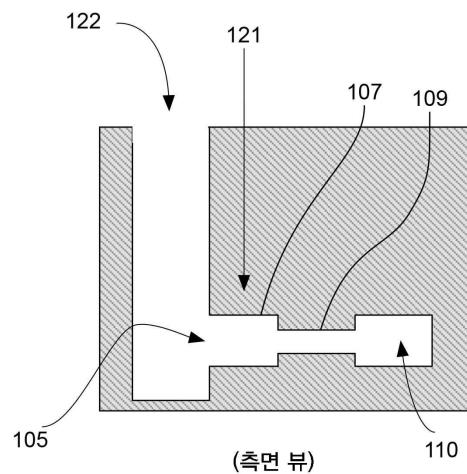

[0032] 예를 들어, 도 2a는 VNAND 스택들 (좌측 205, 우측 206), 중앙 수직적 구조물 (210), 및 중앙 수직적 구조물 (210) 의 대향 측벽들 (240) 상의 구멍들 (230) 을 가진 복수의 적층된 수평적 피쳐들 (220) 을 가지는 (반도체 기판 (201) 상에 형성되는) 3D 수직적 메모리 NAND (VNAND) 구조물 (200) 의 측면도를 나타낸다. 도 2a는 보여지는 VNAND 구조물의 2개의 "스택들" 을 도시하는데, 이것은 같이 "트렌치-같은" (trench-like) 중앙 수직적 구조물 (201) 을 형성하지만, 그러나 특정 실시예들에서는, 도 2a에 명쾌하게 도시된 것과 같이, 차례로 배열되고 서로 공간적으로 (spatially) 평행하게 달리는 (running) 2 이상의 "스택들", 중앙 수직적 구조물 (210) 을 형성하는 인접한 한 쌍의 "스택들" 각각 사이의 갭이 존재할 수도 있다는 점에 주목하라. 이 실시예에서, 수평적 피쳐들 (220) 은 실제적으로 구멍들 (230) 을 통해 수직적 구조물 (210) 로부터 유체적으로 접근가능한 3D 메모리 "워드라인들"이다. 비록 도면에는 명확히 도시되지는 않았으나, 도 2a에 도시된 VNAND 스택들 (205, 206) 양자 모두 (즉, 왼쪽 VNAND 스택 (205) 및 오른쪽 VNAND 스택 (206)) 에 제공되는 수평적 피쳐들 (220) 은 또한 (도시되지는 않았으나 가장 왼쪽 그리고 가장 오른쪽으로의) 부가적인 VNAND 스택들에 의해 형성되는 유사한 수직적 구조물들을 통해 (각각 가장 왼쪽 그리고 가장 오른쪽의) VNAND 스택들의 다른 측면들로부터 접근가능하다. 달리 말하면, 각각의 VNAND 스택 (205, 206) 은 중앙 수직적 구조물 (210) 을 통해 VNAND 스택의 양 측면들로부터 유체적으로 접근가능한 워드라인의 스택을 포함한다. 도 2a에 개략적으로 도시된 특정 예시에서, 각각의 VNAND 스택은 6 쌍의 적층된 워드라인들을 포함하지만, 다른 실시예들에서는, 3-D VNAND 메모리 레이아웃 (layout) 은 구멍들 (230) 을 가진 16, 또는 32, 또는 64, 또는 128 개의 적층된 수평적 워드라인 피쳐들 (220) 에 대응하는 8 쌍, 또는 16 쌍, 또는 32 쌍, 또는 64 쌍의 수직적으로 적층된 워드라인들을 포함할 수도 있다. VNAND 스택에서의 워드라인은 통상적으로 실리콘 옥사이드와 실리콘 나이트라이드 층들의 교변하는 층을 증착함으로써 형성되고, 이후 나이트라이드 층을 제거하는 프로세스를 사용하여 그들 사이에 갭들을 가지는 옥사이드 층들의 스택을 남긴다는 점에 주목하라. 이러한 갭들은 워드라인들이다. 원칙적으로 수직적 피쳐들의 보이드-프리 충진들을 (실질적으로) 성공적으로 달성하는 것이 이용가능한 기술 뿐만 아니라 임의의 수의 워드라인들을 사용가능하게 형성하는 기술이 있기만 하면, 임의의 수의 워드라인들이 이러한 VNAND 구조물로 수직적으로 적층될 수도 있다. 따라서, 예를 들어 VNAND 스택은 2 내지 256 개의 수평적 워드라인 피쳐들, 또는 8 내지 128 개의 수평적 워드라인 피쳐들, 또는 16 내지 64 개의 수평적 워드라인 피쳐들 등등 (나열된 끝 점들을 포함하도록 이해되는 리스트된 범위들)을 포함할 수도 있다.

[0033] 도 2b는 도 2a에 나타내어진 (즉, 점선의 수평선에 의해 나타내어진) 수평적 섹션 (260) 을 통해 취해진 단면을 가진 도 2a의 측면도에 도시된 동일한 VNAND 구조물 (200) 의 위에서 내려다본 단면도를 나타낸다. 도 2b의 단면은 반도체 기판 (201) 의 베이스로부터 VNAND 스택 (200) 의 상단부로 수직으로 달리는 도 2a에 도시된 복수의 열의 필라 (pillar) 들 (250) 을 도시한다. 어떤 실시예들에서, 이러한 필라들 (250) 은 폴리실리콘 재료로 형성되고, 구조적으로 그리고 기능적으로 VNAND 구조물 (200) 에 중요하다. 어떤 실시예들에서, 이러한 폴리실리콘 필라들은 워드라인들에 의해 형성되는 적층된 메모리 셀들에 대해 게이트 전극들 (gate electrode) 로서 기능할 수도 있다. 도 2b의 상측도는 필라들 (250) 이 구멍들 (230) 내에 워드라인들 (220) 에 대해 협색들을

형성하는 것, 즉 구멍들 (230) 을 통한 수직적 구조물 (210) 로부터의 워드라인들 (220) 의 유체적 접근가능성 (accessibility) (도 2b에서 화살표로 표시됨) 이 필라들 (250) 에 의해 억제되는 것을 도시한다. 어떤 실시예들에서, 인접하는 폴리실리콘 필라들 간의 수평적 갭의 사이즈는 약 1 내지 20 nm 이다. 유체적 접근가능성의 이러한 감소는 텅스텐 재료로 워드라인들 (220) 을 균일하게 충진하는 것에 대한 어려움을 증가시킨다.

[0034] 워드라인들 (200) 의 구조물 및 필라들 (250) 의 존재로 인해서 텅스텐 재료로 그들을 균일하게 충진하는 것에 대한 도전이 도 3a, 도 3b 및 도 3c에 더 도시된다. 도 3a는 도 2a에 도시된 것과 동일한 VNAND 구조물 (200) 을 수직으로 관통하여 자른 (vertical cut through) 것을 보여주지만, 여기서는 단일 쌍의 워드라인들 (220) 및 부가적으로 개략적으로 워드라인 (220) 내에 보이드들 (270) 의 형성으로 이어지는 텅스텐 충진 프로세스를 도시하는 것에 초점을 맞추었다. 도 3b는 또한 보이드들 (270) 을 개략적으로 도시하지만, 필라들 (250) 을 수직으로 관통하여 자른 것을 통해 도시된 이 도면에서, 도 2b에 보여지는 수평 컷 (horizontal cut) 과 유사하다. 도 3b는, 협색-형성 필라들 (250) 주변의 텅스텐 재료의 축적, 구멍들 (230) 의 펀치-오프로 이어지는 축적에 의해, 어떠한 부가적인 텅스텐 재료가 보이드들 (270) 의 영역에 증착될 수 없다는 것을 도시한다. 구멍들 (220) 의 펀치-오프를 야기하고 워드라인들 (230) 로의 추가적인 전구체 이주를 방지하는 필라들 (250) 주위로의 텅스텐의 축적된 증착 이전에, 보이드-프리 텅스텐 충진이, 수직적 구조물 (210) 을 통과해, 구멍들 (220) 을 통과해, 협색된 필라들 (250) 을 지나, 그리고 워드라인들 (220) 의 가장 먼 도달지로의, 아래로의 증착 전 구체의 충분한 양들의 이주에 의존한다는 점이 도 3a 및 도 3b로부터 명확하다. 유사하게, 도 3c는 위로부터 단면적으로 보여지는 단일 워드라인 (230) 을 나타내고, 필라들 (250) 의 상당한 폭이 부분적인 블록 (block), 및/또는 폭이 좁음 (narrow), 및/또는 협착으로 작용한다는 사실에 기인하여 어떻게 일반적으로 텅스텐 재료의 컨포멀 (conformal) 증착이 워드라인 (220) 의 내부를 펀치-오프하는 것을 시작하는지, 그렇지 않으면 무엇이 워드라인 (220) 을 통한 열린 경로 (open path) 인지를 도시한다. (도 3c의 예시는 도 3b에 도시된 필라 협착들의 구조물의 3-D 피쳐들의 2-D 렌더링 (rendering) 으로서 이해될 수 있다는 점에 유의해야만 하고, 그에 따라 단면도에서보다 평면도에서 보여지는 협착들을 도시한다.

[0035] 이에 따라, 반도체 피쳐들의 협착된 (constricted) 영역들로 텅스텐 함유 재료를 균일하게 증착하는 것은 대단한 도전을 제기할 수 있다. 위에서 구체적으로 기술된 예시들이 3-D VNAND 메모리 구조물들의 메모리 워드라인들을 균일하게 충진하는 것에 대한 문제점에 관계되는 것이긴 하지만, 본 명세서에서 기술되는 방법들은 텅스텐 함유 재료의 소스로부터 균일한 텅스텐 증착이 요구되는 피쳐의 영역으로 상대적으로 협착된 경로가 존재하는 임의의 유형의 피쳐에 적용될 수 있다. 보이드 형성을 피하고 수평적 피쳐들의 균일한 텅스텐 충진을 달성하기 위한 종류의 기술들은 텅스텐 에칭 작업과 텅스텐 증착 작업의 조합을 포함한다. 일반적 아이디어는 펀치-오프 발생 전에 텅스텐을 증착하는 것, 폐쇄 영역 (closed-off region) 을 다시 열기 위해 (reopen) 펀치 점 (pinch point) 을 에칭-백 (etch-back) 하는 것, 및 그 후 이전에 폐쇄된 영역으로 한번 더 텅스텐을 재증착시키는 것이다. 이러한 기술이 채용될 수도 있는 어떤 상황에서는, 특정 수평적 피쳐들 내라 하더라도 한쌍의 증착 작업들 간의 사이에 있는 에칭 작업이 충분히 균일한 텅스텐 충진을 달성하는데 충분할 수도 있다. 그러나, 더 도전적인 상황들에서는, 구조물의 종횡비의 크기, 충진될 수평적 피쳐 내의 협색의 정도 등에 따라 부가적인 증착-에칭 싸이클이 적합한 충진에 필요할 수도 있다.

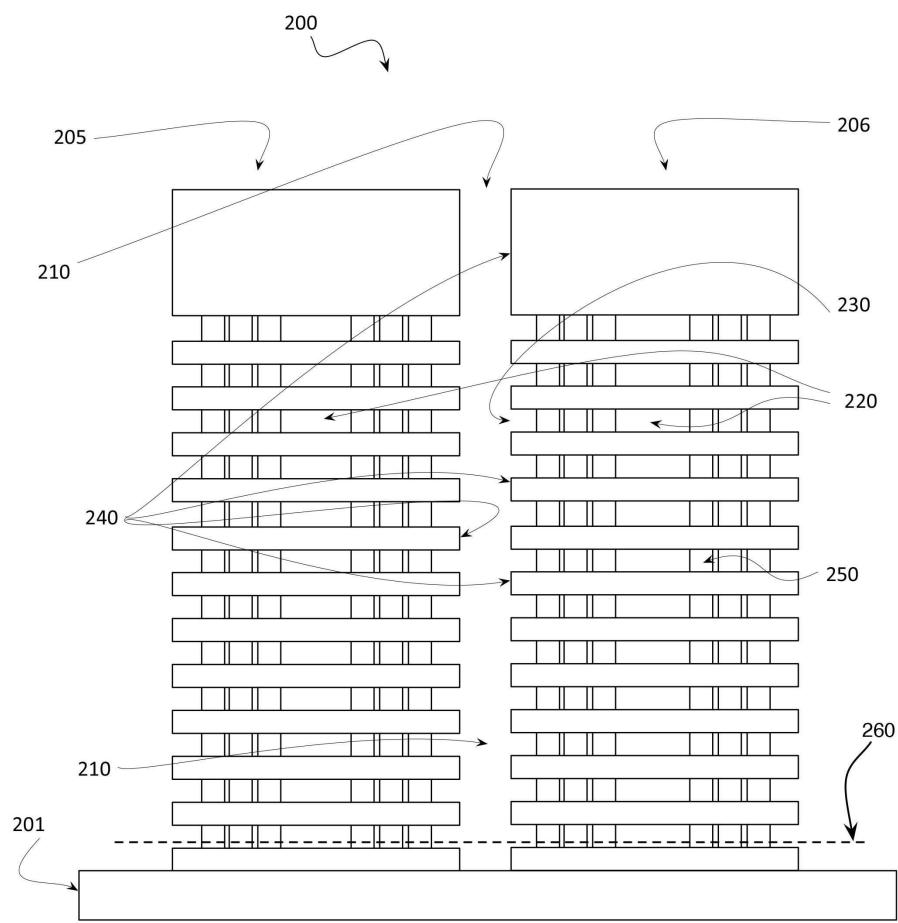

[0036] 도 4a-1 내지 도 4a-3은 종종 개선된 텅스텐 충진으로 이끄는 앞서 언급한 증착-에칭-증착 절차의 예시를 개략적으로 도시한다. 그러나, 이러한 도면들은 또한 고 종횡비 구조물 내의 상이한 수직 깊이들에서 위치되는 수평적 피쳐 - 예를 들어 도 2a 및 도 2b에 도시된 VNAND 구조물과 같은 - 들의 균일한 충진에 의해 제공되는 부가적인 문제점을 도입한다. 도 4a-1 내지 도 4a-3 은 이러한 구성이 간단한 증착-에칭-증착 기술에 의해 적절히 처리되지 않을 수도 있다는 점을 설명한다.

[0037] 특히, 도 4a-1 내지 도 4a-3 의 각각은 2개의 워드라인들, 즉 상부 워드라인 (221) 및 하부 워드라인 (222) 을 도시하는데, 이 워드라인들 각각은 중앙 수직적 구조물들 (210) 의 동일한 인접 쌍으로 상이한 수직 깊이들에서, 구체적으로는 각각 구멍들 (231 및 232) 의 2개의 대칭적인 쌍들을 통해 개방된다. 이 도면들의 각각에 대해, 이 도면들에서 볼 수 있는 협색들 (250) 은 수평적 차원으로 실제로 돌출된다는 점에 주목하라. 도 3c에서와 같이, 이러한 도면들은 워드라인들 (221 및 222) 을 가진 구조물의 3-D 피쳐들의 2-D 렌더링으로 이해될 수 있다. 이러한 도면들은 단면적 뷔를 도시하지만, 단면적 뷔로 보여지는 협색들 (250) 이 위로부터 취해진 평면도에 단지 실제적으로 보여질 수 있는 협색들을 실제로 나타낸다. 임의의 경우에서, 이러한 도면들은 도 2b, 도 3b 및 도 3c에 도시된 것과 같은 수평적 차원으로 돌출되는 협색하는 폴리실리콘 필라들을 가지는 3-D VNAND 구조물들에 유사한 것으로서 생각될 수 있다.

[0038] 예시된 증착-에칭-증착 프로세스는 제1 증착 동작 (510) 및 도 4a-1에 도시된 텅스텐 증착 (270) 의 패턴으로

이어진다. 상부 워드라인 (221) 및 하부 워드라인 (222) 양자 모두에서, 핀치-오프가 발생되어 보이드 (275)를 형성하는 이러한 워드라인들의 내부 (핀치-오프된) 영역 내에 어떠한 추가적인 증착이 방지된다. 다음으로 텅스텐 에칭 동작 (515) 이 수행되고, 텅스텐 증착 (270), 후-에칭 (post-etch) 의 남아있는 패턴, 후-에칭이 도 4a-2에 도시된다. 도면에 도시된 바와 같이, 일부 텅스텐 (270) 은 다음의 증착 동작에서 시드 층 (seed layer) 로 기능할 수도 있는 하부 워드라인 (222) 상에 남겨진다. 그러나, 통상적 텅스텐 에칭 프로세스가 우선적으로 고 종횡비 구조물의 최상부를 향하여 텅스텐을 에칭해버릴 것이라는 사실, 즉 "에칭 로딩" (etch loading) 으로 종종 지칭되는 현상에 기인하여, 상부 워드라인 (221) 은 완전히 에칭되어 버린 그것의 텅스텐을 가진 후속의 텅스텐 증착 동작 (540) 에서의 텅스텐 재성장을 위한 어떠한 시드 층도 남기지 않는다. 그 결과가 도 4a-3에 도시된다. 여기서, 하부 워드라인 (222) 은 보이드-프리 텅스텐 충진을 달성하였지만, 상부 워드라인 (221) 은 완전히 충진되지 않았고, 그 이유는 에칭 (515) 이 완전히 텅스텐 시드 층을 제거했기 때문이다. 또한, 단지 2 개의 워드라인들이 도 4a-1 내지 도 4a-3 에 분명하게 도시되었지만, 이러한 개략적인 도면들의 아이디어는 2 개의 분명하게 도시된 워드라인들이 수많은 개재된 워드라인들 (또는 여타의 수평적 피쳐들) 에 의해 수직적으로 분리될 수도 있다는 것이다. 예를 들어, 어떤 실시예들에서, 3-D VNAND 스택들은 2 이상, 8 이상, 16 이상, 32 이상, 64 이상, 128 이상, 256 이상의 수직적으로 적층된 워드라인들을 채용할 수도 있고, 이에 따라 이 도면들에 분명하게 도시된 2개의 워드라인들은 수십개 또는 심지어 백개 또는 그렇게 개재된 워드라인들에 의해 서로로부터 수직적으로 떨어지는 워드라인들을 나타낼 수도 있다. 임의의 경우에서, 수직적 스택 내의 모든 워드라인들이 보이드-프리 방식으로 텅스텐으로 균일하게 충진되는 것이 통상적으로 요구되고, 이러한 목표는 앞서 언급한 "에칭 로딩" 현상에 의해 빈번히 방해받게 될 수도 있다. 간단히 말하면, 전형적인 텅스텐 에칭 동작에서, "에칭 로딩"은 상부 워드라인 및 하부 워드라인 양자 모두에 동시에 래터럴/수평적 (lateral/vertical) 에칭의 정확한 정도를 달성하는 것은 불가능하지는 않지만 이것을 대단히 어렵게 만든다. 상부 워드라인은 수평적으로 너무 많이 에칭되기 쉬운 반면, 하부 워드라인은 너무 적게 에칭되기 쉽다. 그리고, 문제점은 일반적으로 수직적으로 적층된 수평적 피쳐들의 수가 증가할수록 증가된다.

[0039]

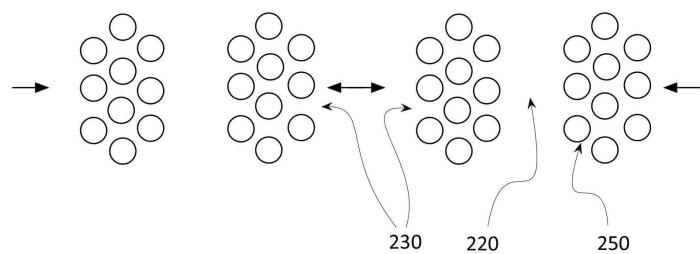

이에 따라, 요구되는 것은 "에칭 로딩"을 감소시키고 (또는 제거하고) 대신에 고 종횡비 구조물의 가장 높은 피쳐들로부터 가장 낮은 피쳐들로 내리면서 텅스텐을 균일하게 (또는 적어도 충분히 균일하게) 에칭하는 텅스텐 에칭 방법론 (methodology) 이다. 이것을 달성하기 위한 한가지 접근법은 수직적 텅스텐 에칭 (520) 에 이어서 특정 실시예들에서 수행될 수도 있는 수평적 에칭 (530) 동작을 도시한 도 5a의 플로우챠트에 의해 보여진다. (도 2a, 도 3a, 도 3b 및 도 4a-1 내지 도 4a-3 에서 보여지는 바와 같이) 상이한 깊이들의 수평적 피쳐들을 가지는 고 종횡비 구조물들을 다시 한번 참조하면, 실시예들은 (i) 반도체 구조물의 최상부로부터 워드라인들의 구멍들을 노출하는 그것의 베이스까지 아래로 최상부로부터 바닥까지 상대적으로 균일하게 텅스텐을 에칭하는 수직적 에칭 동작 (520), 및 (ii) 후속적으로 노출된 워드라인 내로 에칭하여 임의의 핀치-오프 점들의 에칭 어웨이 (etching away) 를 통해 그들을 여는 수평적 에칭 동작 (530) 을 포함할 수도 있다. 따라서, 도 5b의 플로우챠트에 도시된 것과 같은 앞서 언급한 2-단계 에칭을 채용하는 텅스텐 증착 방법론은 텅스텐 증착의 동작 (510) 으로 시작하고, 수직적 에칭 동작 (520) 으로 진행되어, 수평적 에칭 동작 (530) 으로 이어지고, 제2 텅스텐 증착 동작 (540) 으로 이어진다. 어떤 실시예들에서는, 1 이상의 중간 프로세싱 동작들이 수직적 에칭 동작 (520) 및 수평적 에칭 동작 (530) 사이에 개재될 수도 있다. 예를 들어, 도 5c는 수직적 에칭 동작 (520) 및 수평적 에칭 동작 (530) 사이에 개재되는 세정 동작 (525) 을 가지는 방법 실시예를 보인다.

[0040]

이제 도 5d를 참조하면, 대안적인 실시예들에서, 다중의 에칭-증착 싸이클들이 적합할 수도 있다. 도면에 도시된 바와 같이, 어떤 다중-싸이클 프로세스들은 텅스텐 충진이 균일한 정도 및 보이드 프리가 평가되는 결정점 (550) 을 포함할 수도 있고, 만약 충진이 충분히 균일하고 보이드 프리하다면 프로세싱이 앞으로부터 여타의 프로세싱 동작들 (570) 로 이동하고, 반면 만약 충진이 불충분하다면 프로세싱은, 특정 중간 프로세싱 동작들 (560) 을 선택적으로 수행한 후에, 에칭-증착 (예를 들어, 수직적 에칭 (520), 수평적 에칭 (530) 및 증착 (540)) 의 다른 라운드 (round) 로 돌아간다. 어떤 다른 실시예들에서, 다중-싸이클 프로세스는 앞서 언급된 평가를 행하지 않을 수도 있고, 대신에 간단하게 보통의 방법대로 미리 정해진 횟수로 앞서 언급된 에칭-증착 싸이클을 반복할 수도 있다. 따라서, 본 실시예에 따르면, 1-25의 증착-에칭 싸이클들이 수행될 수도 있고, 예를 들어, 1-15, 또는 5-20 증착-에칭 싸이클들이 수행될 수도 있다. 어떤 실시예들에서, 일 범위의 증착-에칭 싸이클이 수행될 수도 있고, 이 범위는 앞서 언급된 값들의 임의의 쌍에 의해 정의된 범위의 엔드포인트 (endpoint) 를 가질 수 있다 (예를 들어 1-25로부터 선택된 임의의 쌍의 값들).

[0041]

도 5a 내지 도 5d의 수평적 에칭 동작 (530) 은 텅스텐 증착/에칭 장치의 조작자 (사람 또는 제어 로직) 에 의한 수직적 에칭과는 관계없는 초기의 개별 에칭보다는 수직적 에칭 (520) 의 화학적 및 물리적 결과 (그리고 수직적 에칭의 선택된 프로세스 조건들의 결과) 일 수도 있다는 점에 주목해야 한다. 예를 들어, 어떤 실시예

들에서, 수직적 예칭 동작 (520) 은, 전하 (electrical charge) 때문에 고 종횡비의 수직적 피쳐의 베이스를 향하여 (전기장을 통해) 방향이 있게 (directionally) 집중될 수도 있는 (그럼으로써 수직적 예칭을 달성하는) 이온화된 에천트 (etchant) 재료를 이용할 수도 있다. 그러나, 일단 수직적 에천트 재료의 이온들이 피쳐의 베이스에 충돌하면, 그들은 전자들을 수용하여 중성 (neutral) 에천트 종들을 생성할 수도 있고, 이 중성 에천트 종들은 그 후 외부로 그리고 좌우로 수평적 피쳐들 내로 방출될 수도 있다. 이러한 물리적/화학적 프로세스는, 어떤 실시예들에서는, 도 5a 내지 도 5d에서 나타내어지는 수평적 예칭 (530) 을 구성할 수도 있다. 보다 일반적으로는, 수직적 이온화된 에천트 종들의 물리적/화학적 전환 (conversion)에 의한, 수평적 피쳐의 밖으로의, 텅스텐 재료의 상당한 예칭과 커플링된 (coupled) 수평적 피쳐들 내로의 어떤 상당한 좌우방향의 방출 또는 에천트 종들의 대량 이동은 수평적 예칭 (530) 을 구성할 수도 있다. 그러나, 또한 여타의 실시예들에서, 수평적 예칭 (530) 은 물리학, 화학, 및 수직적 예칭의 프로세스 조건들 - 예를 들어 텅스텐 증착/예칭 장치의 조작자 (인간이거나 제어 로직)에 의해 초기화되는 독립적 프로세스에 의해 - 과는 관계없이 1 이상의 동작들의 시퀀스 (sequence)에 의해 달성될 수도 있다는 점에 주목해야 한다.

[0042] 또한, 도 5a 내지 도 5d에 도시된 플로우챠트들은 수직적 예칭 (520) 및 수평적 예칭 (530) 이 염격하게 차례차례로 발생한다는 점을 의미한다고 이해되어서는 안된다는 점을 주목해야 한다 - 예를 들어, 수직적 예칭 (520) 은 수평적 예칭 (530) 이 시작되기 전에 완료될 수 있다. 예칭 종들의 특정한 문자가 좌우방향의 에천트 종들로의 전환 (예를 들어, 수직적 구조물의 베이스에서 1 이상의 전자들을 받아들임으로써 중성으로 전환되는 것)이 발생하기 이전에 수직적으로 (예를 들어서, 이온으로서) 예칭할 것이고, 이에 따라 개별 에천트 문자가 수평적으로 예칭하기 이전에 수직적으로 예칭한다고 할 수도 있다는 점이 종종 사설일 것이다. 그러나, 에천트 문자들의 총체 (ensemble) 가 보여지는 경우 - 에천트 전환이 발생하고 있는 예칭 기술들에서 - 수직적 및 수평적 예칭은 명백하게 특정 범위로 동시에 발생하고 있을 것이다. 물론, 수직적 예칭이 그들을 아직 개방하지 않았거나/않고 그들에 대해 하방으로 예칭하지 않은 이유로 수평적 피쳐들이 접근 가능하지 않는 한, 그런 면에서, 개별 피쳐들에 대해, 수직적 예칭은 수평적 예칭 전에 발생하다라고 할 수도 있다. 이에 따라, 이러한 관점들에서, 도 5a 내지 도 5d는, 수직적 예칭이 구조물의 수평적 피쳐들에 대해 수직적 3-D 구조물 아래로 예칭하여, 그 후 수평적 예칭이 수평적 피쳐들 내를 예칭할 수 있다는 점을 개념적으로 도시한 것이라 해석되어야 한다. 이것은 또한 도 4a-1 내지 도 4c-4의 다이어그램에 의해 개념적으로 도시된다 (그러나, 특정 실시예에서는, 도 5c의 선택적인 세정 단계 (525) 가 2 개의 예칭 단계 (520 및 530) 사이의 분할로서 기능할 수도 있다는 점에 유의해야 한다).

[0043] 도 5a-도 5d에 관해 기술된 바와 같은 수평적 그리고 수직적 예칭 접근법을 이용한 텅스텐 증착 절차에 의한 수평적 피쳐들의 충진에 관련된 장점들은 도 4b 및 도 4c에 도시된다. 달리 지적하지 않는 한, 도 4a-1에 명확하게 표시된 참조 번호들 (도 4b-1 및 도 4c-1에 반복됨) 은 여타의 도 4 시리즈 도면들에 나타낸 대응하는 피쳐들에 적용한다는 점에 유의하라.

[0044] 도 4b-1 내지 도 4b-4에 도시된 워드라인 충진 시퀀스는 조합된 수직적/수평적 예칭을 이용한다. 도 4b에 나타내어지는 바와 같이, 텅스텐 충진 절차는 (또한 도 5b의 플로우챠트에 나타내어지는 바와 같은) 텅스텐 증착 동작 (510) 으로 시작하는데, 텅스텐 충진 동작 (510) 은 도 4a-1에 개략적으로 도시된 충진 패턴과 기본적으로 동일한 것인 도 4b의 충진 패턴을 생성한다. 따라서, 이 첫 증착은, 협색들 (250) (예를 들어, 폴리실리콘 필라들) 부근에서의 텅스텐 재료의 컨포멀 증착으로 인해, 도 4b-1 (및 도 4a-1) 에 도시된 상부 워드라인 (221) 및 하부 워드라인 (222) 양자 모두에 러프하게 동등한 핀치-오프 (roughly equivalent pinch-off) 를 야기한다.

[0045] 첫 증착 동작 (510) 후에, 도 5b의 플로우챠트 및 도 4b-2에서 지향된 (directed) 화살표에 나타내어지는 바와 같이, (이하에서 보다 자세히 기술될 것과 같이) 수직적 예칭 동작 (520) 이 수행되는데, 도 4b-2에 도시된 바와 같이, 수평적 워드라인들 (221 및 222) 의 내부 영역들로부터 텅스텐을 제거하지 않으면서 (또는 눈에 띄게 제거하지 않으면서), 이것은 중앙 수직 구조물 (210) 의 측벽들로부터 텅스텐을 제거한다. 이것은 "워드라인 컷" (wordline cut) 이라 지칭될 수도 있다. 그 후에, 도 4b-2에서 도시된 바와 같이, 워드라인들 (221 및 222) 의 내부는 협색들 (250) 에서 제거되지 않은 핀치-오프로 인해 접근 불가능한 상태로 남아있다. 그러나, 도 4b-2에 도시된 바와 같이, 상부 워드라인 (221) 및 하부 워드라인 (222) 이 러프하게 똑같이 예칭된다는 점, 즉 "예칭-로딩" 효과가 없다는 점이 명확한 장점이다. 이것은 수직적 예칭의 지향적인 특성 (directional character) 로부터의 결과, 구체적으로 수직적 예칭이 아래 방향으로 반도체 구조물의 베이스를 향해 지향되고, 그래서 수직적 예칭이, 수평적 피쳐들로부터 텅스텐을 눈에 띄게 좌우방향으로 제거하지 않으면서, 실질적으로 고르게 (evenly) 그리고 균일하게 수직적으로 (uniformly vertically) 중앙 수직 구조물로부터 텅스텐을 제거한다

는 사실로부터의 결과로서 예견될 수 있다.

[0046] 중앙 수직 구조물 (210)의 측벽들에서 실질적으로 텅스텐이 제거됨과 함께, 도 5b에서 나타내어지는 것과 같이 그리고 도 4b-3에서 지향되는 화살표에 의해 수평적 에칭 동작 (530)이 수행된다. 주로 지향적인 특성을 가지는 것보다, 어떤 실시예에서는, 수평적 에칭 (530)이 대체적으로 (generally) 등방성으로 (isotropically) 작용하여, 활성화된 에센트 재료를 수평적 피쳐들 내에서 좌우 방향으로 에칭하고, 핀치-오프 점들을 제거하고, 그에 따라 워드라인들 (221 및 222)의 내부 영역들을 개방하게 할 수도 있다. 도 4b-3은 수평적 에칭 (530) 후의 보유하고 있는 텅스텐 증착의 패턴을 도시하고, 도 4a-2에 도시된 에칭-로딩 효과와 달리, 도 4b-3에서는, 상부 워드라인 (221) 및 하부 워드라인 (222)이 그들의 내부 영역들 내에서 텅스텐 증착의 대략적으로 동일한 양들을 유지한다. 텅스텐 시트 층이 양 워드라인드에 남아있기 때문에, 효과적인 텅스텐 재성장이 이어지는 증착 동안 발생할 수도 있다. 따라서, 도 5b 및 도 4b-4로 지향된 화살표가 나타내는 것과 같이, 텅스텐 충진 동작을 완성하도록 이어지는 텅스텐 증착 동작 (540)은 도 4b-4에서 도시된 것과 같이 균일하고 보이드-프리한 텅스텐 충진을 야기하는데, 이는 도 4a-3에 도시된 상부 워드라인 (221) 상에 보여지는 텅스텐 재성장의 결핍과는 대비되는 것이다.

[0047] 또한, 어떤 실시예들에서, 수평적 에칭 동작 (530)에서 사용되는 활성화된 에칭 재료는 방출-제한된 에칭 레짐 (regime)으로 동작될 수도 있고, 이론적으로 고려할 때 (as such), 수평적 에칭 동안 고 종횡비 피쳐의 최상부 및 바닥을 비교할 때 제공되는 다소 작은 정도의 에칭 로딩이 존재할 수도 있다. (다르게 말하면, 반도체 구조물의 일부 영역들에서, 방출의 속도 (rate)가 에칭 케미스트리 (etching chemistry)의 속도와 엇비슷하지 않을 수 있다.) 그럼에도 불구하고, 이러한 작은 정도의 에칭 로딩은 도 4a-3에 의해 예시되는 문제점 (텅스텐 시드 층의 완전한 제거 및 보다 상측 워드라인들에서의 재성장 없음)을 야기하지 않는데, 그 이유는 방대한 다수의 에칭 로딩이 지향적인 수직적 에칭 동작 (520)에 의해 피해졌기 때문이다.

[0048] 마지막으로, 도 4c-1 내지 도 4c-4는 도 4b-1 내지 도 4b-4에 도시된 수직적 및 수평적 에칭 방법론의 조금 다른 실시예를 개략적으로 도시한다. 도 4 시리즈의 다이어그램의 각각에서, 반도체 구조물의 벽들은 티타늄 나이트라이드 (TiN)의 얇은 층으로 코팅된다. 이러한 티타늄 나이트라이드 층 (280)은 증착될 텅스텐 필름의 성장의 핵을 이루도록 (nucleate) 기능할 수도 있다. 텅스텐 증착이 대단히 더 느리거나, 베어 실리콘 (bare silicon) 또는 실리콘 옥사이드의 층으로 코팅된 실리콘 상에 실존하지 않기 때문에 (이러한 종류의 프로세싱에서 사용되는 동작 조건들의 통상적인 범위 하에서 적어도 대단히 더 느린 것), TiN 층 (280) 또는 적합한 대체물 (substitute) 없이, 텅스텐 성장이 일반적으로 발생하지 않는다. 게다가, TiN 층의 존재는 유용하고 심지어 필수적이라고 할 수도 있는데, 어떤 실시예들에서는, TiN 층 (280)의 선택적인 제거가 또한 유용할 수도 있다. 따라서, 도 4c-1에 개략적으로 도시된 것은, TiN 층 (280)을 예칭해버릴 수 있는 활성화된 에칭 재료를 이용하여 노출된 베어 실리콘 (281)을 남기는 수직적 에칭 동작 (521)의 결과이다. 수직적 에칭 (521) 이후, 수평적 에칭 (530)이 평소처럼 진행되고, 이어서 텅스텐 증착 (540)의 제2 동작이 행해진다. 도 4b-4로서 중앙 수직적 구조물 (210)의 측벽들 상으로 연장되는 텅스텐 성장보다는, 도 4c-4에서 도시된 결과는 워드라인들 (221 및 222) 내에 국한된 (localized) 텅스텐 재료의 보이드-프리한 균일한 증착이다 (그 이유는 그것이 TiN 층 (280)이 남아있는 유일한 영역이기 때문이다). 물론, 이것은 전기적으로 서로서로 절연된, 수직적으로 적층된 워드라인들을 남기는데, 이는 만약 이러한 적층된 워드라인들이 3-D NAND 메모리 디바이스에서 메모리 셀들로서 사용되는 경우에는 궁극적인 목표이다.

[0049] 도 4d는 수평적 피쳐들을 가지는 3-D 수직적 구조물들의 실질적으로 균일하고/보이드 프리한 텅스텐 충진을 달성하기 위해 본 명세서에 개시되는 특정 기술들 및 동작들을 채용함으로써 얻어지는 결과를 도시한 전자 현미경 사진 (electron micrograph)을 표시한다.

## [0050] 텅스텐 증착

[0051] 위에서 기술된 바와 같이, 텅스텐-함유 재료로 반도체 구조물들 및 피쳐들을 균이하게 충진하기 위한 본 명세서에 개시된 방법론들은 1 이상의 텅스텐 증착의 동작들을 채용한다. 어떤 실시예들에서, 텅스텐 증착은 실질적으로 컨포멀로 기술될 수도 있고, 텅스텐-함유 전구체 및 환원제 간의 반응을 통해 달성될 수도 있다. 특정한 이러한 실시예들에서, 텅스텐은 처음에 베어 실리콘 기판 (또는 실리콘 기판의 산화된 표면)을 덮는 언더층 (underlayer)의 맨 위에 증착된다.

[0052]

언더층은 확산 방지 층 (diffusion barrier layer)으로서 기능할 수도 있고, 또는 컨포말 텅스텐 증착을 위한 핵형성 층 (nucleation layer)으로서 기능할 수도 있고, 또는 양자 모두로서 기능할 수도 있다. 컨포말 텅스텐 증착이 일반적으로 반도체 제조와 관련된 열역학적인 레짐 (thermodynamic regime) 들에서 베어 실리콘 또는 산화된 실리콘 상에 발생하지 않기 때문에, 위에서 언급한 바와 같이 어떤 종류의 언더층은 일반적으로 필요하다. 본 명세서에서 지칭되는 "언더층"은 또한 본 발명에서 텅스텐 증착에 민감하고 (susceptible) 텅스텐이 증착될, 부분적으로 제조된 반도체 기판의 "외부 층" (outer layer)으로 지칭된다는 점에 유의하라. 물론, 텅스텐 증착 이전의 반도체 기판의 "외부 층"인 것은 텅스텐 증착 그 자체에 "언더층"으로서 기능하기 때문에, 전문 용어 (terminology)는 일관된다. 따라서, 어떤 실시예들에서는, 부분적으로 제조된 반도체 기판이 텅스텐 증착에 민감하고 텅스텐-함유 재료의 층이 증착될 수도 있는 외부 층을 가지는 구조물을 포함할 수도 있다. 임의의 경우에서, 기판의 외부 층으로 지칭되는 것이든 텅스텐 증착에 대한 언더층으로서 지칭되는 것이든 간에 이 층은 1 이상의 종류의 금속 나이트라이드를 포함할 수도 있고, 어떤 실시예들에서, 이 층은 티타늄 나이트라이드 (TiN) 및/또는 텅스텐 나이트라이드 (WN) 및/또는 여타의 것들을 포함할 수도 있다. 층은 10Å 내지 500Å (옹스트롬) 두께일 수도 있고, 또는 보다 구체적인 실시예들에서는, 25Å 내지 200Å 두께일 수도 있다. 또한, 어떤 실시예들에서는, 구조물의 측벽들로부터 텅스텐을 제거하는 수직적 예칭 동작이 텅스텐 증착에 민감하고 텅스텐이 증착된 앞서 언급한 외부 층에 눈에 띄게 영향을 미칠 수도 있고, 다른 실시예에서는, 수직적 예칭 동작이 구조물의 측벽들의 적어도 일부분들 상에서 이러한 층의 일부분들을 제거할 수도 있다. 이러한 뒤의 실시예들에서, 텅스텐-함유 재료의 후속된 층들의 임의의 증착 동안 측벽들의 이러한 일부분들 상에 실질적으로 어떠한 텅스텐도 증착되지 않는다. 다시 한번, 이것은 도 4c-1 내지 도 4c-4에 도시된다.

[0053]

언더 층이 핵형성 층으로 기능하는 경우, 언더 층은 통상적으로 그 상의 대규모 (bulk) 텅스텐-함유 재료의 후속된 증착을 가능하게 하는 얇은 컨포밀 층이다. 특정 실시예들에서, 핵형성 층은 펄스된 (pulsed) 핵형성 층 (PNL) 기술을 사용하여 증착된다. PNL 기술에서, 환원제 및 텅스텐-함유 전구체의 펄스들은 연속적으로 반응 챔버로부터 (퍼지 가스 (purge gas)의 주입된 펄스 (injected pulse)를 통해) 주입되고, 퍼지된다 (purged). 프로세스는 원하는 두께가 얻어질 때까지 순환하는 방식으로 (in a cyclical fashion) 반복된다. PNL은, 원자 층 증착 (ALD)을 포함하는, 반도체 기판 상에서의 반응을 위해 반응물을 연속적으로 첨가하는 임의의 순환하는 프로세스를 넓게 (broadly) 포함한다. 텅스텐 핵형성 층들을 증착하기 위한 PNL 기술들은 2008년 2월 13일에 출원된 미국 특허출원 번호 제12/030,645호, 2007년 12월 5일에 출원된 미국 특허출원 번호 제11/951,236호, 및 2009년 3월 19일에 출원된 미국 특허출원 번호 제12/407,541호에 기술되고, 이들 각각은 모든 목적들을 위해 전체적으로 참조로서 본 명세서에 포함된다. PNL 탑입의 프로세스들에 관한 추가적인 논의는 미국 특허출원 번호 제11/265,531호 뿐만 아니라 미국 특허번호 제6,635,965호, 제6,844,258호, 제7,005,372호, 및 제7,141,494호에서 찾을 수 있고, 이들 각각은 또한 모든 목적들을 위해 전체적으로 참조로서 본 명세서에 포함된다. 본 명세서에 기술된 방법들은 텅스텐 핵형성 층 증착의 특정한 방법에 제한되는 것은 아니지만, PNL, ALD, CVD, PVD 및 여타의 다른 방법을 포함하는 임의의 방법에 의해 형성된 텅스텐 핵형성 층들 상에 대규모 텅스텐 필름을 증착하는 것을 포함한다. 게다가, 특정 실시예들에서, 대규모 텅스텐은 핵형성 층의 사용 없이 직접 증착될 수도 있다.

[0054]

증착 스테이션 (deposition station)은 텅스텐을 증착하기 위해 사용될 수도 있지만, 또한 특정한 이전의 동작들 (예를 들어, 확산 방지 층의 증착, 핵형성 층의 증착) 및/또는 후속되는 동작들 (예를 들어, 증착된 텅스텐의 예칭, 다른 텅스텐 증착, 마지막의 피쳐 충진)을 수행하는데 사용될 수도 있다. 특정 실시예들에서, 증착 스테이션은 도 5의 텅스텐 증착 동작 (510 및 540)을 수행하도록 구체적으로 지정될 수도 있다. 장치는 또한 이러한 증착 동작들을 수행하는 부가적인 증착 스테이션들을 포함할 수도 있다. 예를 들어, 처음의 텅스텐 증착 (예를 들어, 도 5의 동작 (510))은 제1 증착 스테이션에서 수행될 수도 있다. 그렇다면 반도체 기판은 수직적 예칭 또는 수평적 예칭 (예를 들어, 도 5의 동작들 (520 및/또는 530))에 대한 것과 같은 예칭을 위한 다른 스테이션으로 이동될 수도 있다. 이하에서 더 기술될 특정 실시예들에서, 예칭 스테이션은 다른 챔버에 위치되어, 그들의 각각의 동작들에 대한 상이한 재료들 및 조건들을 사용하는 증착 환경 및 예칭 환경 간의 교차-오염 (cross-contamination)을 방지한다. 이후 프로세스가 다른 증착 동작 (예를 들어, 도 5의 동작 (540))을 사용한다면, 기판은 제1 증착 스테이션으로 돌아가거나, 다른 증착 스테이션으로 이동될 수도 있다. 다중 증착 스테이션들은 또한 수많은 기판들 상의 병렬의 증착 동작들을 수행하는데 이용될 수 있다. 추가적인 상세들 및 장치 실시예들은 도 6, 도 7 및 도 8의 문맥으로 이하에서 설명된다.

[0055]

어떤 실시예들에서, 텅스텐 증착은, 텅스텐-함유 전구체가 텅스텐을 증착하기 위해 수소에 의해 환원되는 화학적 기상 증착 (CVD) 프로세스를 포함한다. 텅스텐 헥사플로라이드 ( $WF_6$ )가 종종 사용되지만, 프로세스는, 제

한되는 것은 아니지만 텉스텐 혼화물로라이드 ( $WC_{16}$ ), 유기 금속 전구체들 (organo-metallic precursors), 및 MDNOW (methylcyclopentadienyl-dicarbonylnitrosyl-tungsten) 및 EDNOW (ethylcyclopentadienyl-dicarbonylnitrosyl-tungsten) 과 같은 불소가 없는 전구체를 포함하는 여타의 텉스텐 전구체들을 가지고 수행될 수 있다. 게다가, 수소가 일반적으로 대량 텉스텐 층의 CVD 증착에서 환원제로서 사용되지만, 본 발명의 범위로부터 벗어나지 않으면서 실레인 (silane) 을 포함하는 여타의 환원제들이 추가적으로 사용될 수 있거나, 수소 대신에 사용될 수도 있다. 다른 실시예에서, 텉스텐 혼화물로보닐 ( $W(CO)_6$ ) 은 환원제를 가지고 또는 환원제 없이 사용될 수도 있다. 위에서 기술된 PNL 프로세스들과 달리, CVD 기술에서,  $WF_6$  및  $H_2$  또는 여타의 반응물들은 반응 챔버로 동시에 도입된다. 이것은 기판 표면 상에 텉스텐 필름을 연속적으로 형성하는 혼합 반응물 가스 (mix reactant gas) 들의 연속적인 화학적 반응을 야기한다. 화학적 기상 증착 (CVD) 를 사용하여 텉스텐 필름들을 증착하는 방법들은 2008년 8월 29일에 출원된 미국 특허출원 번호 제12/202,126호에 기술되고, 이는 증착 프로세스를 기술하는 목적들을 위해 전체적으로 참조로서 본 명세서에 포함된다. 다양한 실시예들에 따르면, 본 명세서에서 기술되는 방법들은 피쳐를 부분적으로 충진하는 특정 방법들에 한정되는 것은 아니지만, 임의의 적합한 기술을 포함할 수도 있다. 부분적으로 제조된 반도체 기판들 상에 텉스텐을 증착하는 방법과 관련되는 보다 상세한 사항들은 모든 목적들을 위해 본 명세서에 참조로서 전체적으로 포함되는 미국 특허번호 제 8,124,531호에서 발견될 수 있다.

[0056]

어떤 증착 프로세스가 사용되든, 증착 동작은 증착된 층이 특정 두께에 이를 때까지 진행될 수도 있다. 어떤 실시예들에서, 선택된 두께는 고 종횡비 구조물의 수평적 피쳐들 이내에서 임의의 협색된 (constricted) 영역들의 폭에 의존할 수도 있다. 예를 들어, 일단 편치-오프가 이러한 수평적 피쳐 내에 발생하면, 이 피쳐 내에서의 더이상의 텉스텐 증착이 방지된다. 따라서, 일단 피쳐 내의 증착된 층의 평균 두께가 수평적 피쳐 내의 협색의 가장 좁은 점의 평균 반경과 대략적으로 동일한 값에 이른다면, 그것이 텉스텐 증착을 멈추고 위에서 기술된 텉스텐 에칭 시퀀스를 시작하기 위한 적절한 점 (point) 일 수도 있다.

[0057]

수직적 에칭

[0058]

위에서 기술된 바와 같이, 본 명세서에서 기술된 균일한 텉스텐 증착을 달성하기 위한 기술들은 텉스텐의 처음 층을 증착한 후에 수직적 에칭을 채용할 수도 있다. 다시 한번, 위에서 기술된 바와 같이, 수직적 에칭은 "에칭 로딩" 현상을 최소화하거나 제거하면서 인접한 3-D VNAND 스택들에 의해 형성된 중앙 수직적 구조물 아래로 "워드라인 컷"을 달성하기 위해 수행된다. 또한 위에서 기술된 바와 같이, 이 수직적 에칭은 (적어도 상대적으로 말하면) 지향적 에칭 (directional etch) 으로 특징될 수도 있고, 이론적으로 고려할 때 (as such), 그것은 중앙 수직적 구조물로 통하는 수평적 피쳐들로부터 좌우 방향으로 텉스텐을 눈에 띄게 에칭하지 않는다. (그러나, 수직적 에칭 재료가 에칭될 수직적 피쳐의 베이스/바닥에서 수평적 에칭 재료로 변하는 실시예들에서, 단지 좌우 방향으로 에칭되지 않는 것의 특징은 래터럴 에천트 (lateral etchant) 로의 변환 전의 에천트에 적용된다는 점에 이해되어야만 한다.) 따라서, 어떤 실시예들에서, 수직적 에칭 동작은 활성화된 에칭 재료를 제공하는 것, 및 수평적 피쳐들의 내부로부터 텉스텐의 초기 증착된 층의 일부분들을 실질적으로 제거하지 않으면서 활성화된 에칭 재료를 사용하여 수직적 구조물의 측벽들로부터 초기-증착된 텉스텐-함유 재료의 층의 일부분들을 제거하는 것을 포함한다.

[0059]

활성화된 에칭 재료는 (프로세싱 챔버에서) 인 시츄 (in situ) 생성된 1 이상의 이온 종들을 포함하는 이온화된 플라즈마일 수도 있다. 따라서, 수직적 에칭 - 지향적인 워드라인 컷 - 은, 전자기장을 플라즈마 내의 이온들에 인가하여 수직적으로 에칭될 고 종횡비 피쳐/3-D 구조물의 바닥 또는 베이스를 향하여 이온들을 지향시킴으로써 수행될 수도 있다. 이온화된 플라즈마 종들에 대한 화학적 전구체들 (예를 들어, 프로세싱 챔버 내에서의 이온화를 통해서 이온 종들을 생성할 플라즈마 시약들 (reagents)) 은 불소-함유 화합물들의 다양한 형태를 포함할 수도 있다. 일례는  $NF_3$ 이다. 다른 예들은  $CF_4$ ,  $CHF_3$ ,  $CH_2F_2$ ,  $CH_3F$ , 또는  $SF_6$  (비록  $SF_6$ 는 과도하게 공격적인 (aggressive) 점이 발견될 수도 있다 하더라도) 를 포함한다. 불소 미함유 플라즈마 시약들의 일례는  $Cl_2$ 를 포함할 수도 있다. 이온화된 플라즈마 종들을 형성하는데 사용되는 플라즈마 시약들은, 프로세싱 챔버와 유체적으로 연결된 1 이상의 공급 라인들을 통해 에칭이 발생하는 프로세싱 챔버로 통상적으로 제공된다. 프로세싱 챔버로의 플라즈마 시약들의 유속 (flow rate) 은 약 100 내지 1000 sccm 일 수도 있고, 보다 바람직하게는 약 100 내지 700 sccm 일 수도 있고, 또한 더 보다 바람직하게는 약 300 내지 700 sccm 일 수도 있고, 또한 더 보

다 바람직하게는 약 400 내지 600 sccm 일 수도 있고, 또는 어떤 실시예들에서는, 약 100 내지 500 sccm 일 수도 있다.

[0060] 앞서 언급한 플라즈마 시료들 뿐만 아니라, 수직 예칭 동작은 약 500 내지 2000 sccm, 또는 보다 특별히는 약 1000 내지 1500 sccm 의 유속으로 수직적 예칭 동작 동안 프로세싱 챔버로 유동될 수도 있는 희석 가스 (diluent gas) 의 사용을 통해 향상될 수도 있다. 어떤 실시예들에서, 희석 가스는 헬륨 또는 아르곤 (또는 양자 모두) 또는 어떤 다른 불활성 가스 (또는 불활성 가스들의 조합) 일 수도 있다. 희석 가스는 예칭될 구조물의 바깥으로 나오는 (및/또는 예칭될 구조물에서 떠나는) 에천트 부산물 (통상적으로는 WF<sub>6</sub>) 의 확산 속도를 증가시킴으로써 수직적 예칭 동작 동안 예칭 속도를 향상시키도록 작용할 수도 있다. 예를 들어, 웨이퍼 기판의 상부 표면 위로의 Ar, He 또는 여타의 다른 불활성 희석 가스의 높은 유속은 예칭될 수직적 피쳐의 내부 대 외부의 (inside versus outside) 예칭 부산물의 농도 구배 (concentration gradient) 를 증가시킬 수도 있으며, 그에 따라 부산물 제거에 대한 확산 장벽을 감소시킨다.

[0061] 어떤 실시예들에서, 폴리머릭 희생 보호 재료 (polymeric sacrificial protection material) 에 대한 폴리머릭 전구체들 (polymeric precursors) 은 또한 희생 보호 재료를 형성하기 위해 프로세싱 챔버에 제공될 수도 있다. 어떤 환경들에서는, 희생 보호 층이, 3-D NAND 트렌치 (trench) 의 중앙 수직적 구조물의 상부 부분들이 예칭되는 범위를 약화시킬 수도 있으며, 그에 따라 최상부에서의 과도한 예칭 (overetching) 이 방지된다. 어느 정도, 희생 보호 층이 수직적 예칭의 지향성 (directionality) 를 향상시킨다. 희생 보호 층에 대한 화학적 폴리머릭 전구체는 다양한 형태의 불소-함유 화합물들을 포함한다. 구체적인 예시들은 CF<sub>4</sub>, CHF<sub>3</sub>, CH<sub>2</sub>F<sub>2</sub> 및 CH<sub>3</sub>F를 포함한다. 폴리머릭 전구체 종들은 또한 통상적으로 프로세싱 챔버와 유체적으로 연결된 1 이상의 공급 라인들을 통해 예칭이 발생하는 프로세싱 챔버에 제공된다. 프로세싱 챔버로의 폴리머릭 전구체의 유속은 약 10 내지 100 sccm, 또는 보다 바람직하게 약 20 내지 60 sccm, 또는 보다 바람직하게 약 30 내지 40 sccm 일 수도 있다.

[0062] 수직적 예칭은 챔버 동작 조건들의 범위를 넘어 수행될 수도 있다. 어떤 실시예들에서, 수직적 예칭 동안의 프로세싱 챔버 내의 온도는 약 10 내지 140 °C, 또는 보다 특별히 약 20 내지 120 °C, 또는 보다 특별히 약 30 내지 100 °C, 또는 보다 특별히 약 40 내지 80 °C 또는 어떤 실시예에서는 약 60 °C 로 유지될 수도 있다. 어떤 실시예들에서, 수직적 예칭 동안의 프로세싱 챔버 내의 압력은 약 20 내지 120 mTorr, 또는 보다 바람직하게 약 30 내지 100 mTorr, 또는 보다 바람직하게 약 50 내지 90 mTorr 또는 약 40 내지 80 mTorr 로 유지될 수도 있다. 텅스텐 예칭 동작들을 위한 인 시츄 생성된 플라즈마 (in site generated plasma) 를 채용하는 것은 이하에서 보다 구체적으로 기술된다.

[0063] 어떤 실시예들에서, 유도성 커플링된 플라즈마 반응기 (inductively coupled plasma reactor) 는 수직적 예칭에 사용되는 인 시츄 플라즈마를 생성하기 위해 사용된다. 유도성 커플링된 플라즈마들 및 관련된 유도성 커플링된 플라즈마 반응기들은 본 명세서에 모든 목적들을 위해 전체적으로 참조로서 포함되는 미국 특허번호 제 6,184,158호에 기술된다. 유도성 커플링된 플라즈마 반응기의 예시들은 또한 도 9에 대하여 이하에서 기술된다.

[0064] 어떤 실시예들에서, 수직적 예칭 동작에 사용되는 이온 종들을 포함하는 플라즈마는 유도성 커플링된 RF 전력에 의해 생성되고 유지된다. RF 전력은 약 400 kHz 내지 14 MHz 의 (약 13.56 MHz 와 같은) 주파수를 가지는 기판-바이어스된 (substrate-biased) RF 전력에 의해 생성되고 유지됨에도 불구하고, 약 13 MHz 내지 60MHz 의 주파수를 가질 수도 있다. 어떤 실시예들에서, 기판-바이어스된 RF 전력은 기판에 대해 약 100 내지 1000 볼트, 또는 보다 특별히 기판에 대해 약 100 내지 700 볼트, 또는 보다 특별히 기판에 대해 약 100 내지 500 볼트의 전압을 가진다. 어떤 실시예들에서, 유도성-커플링된 플라즈마를 채용하는 방법들은 약 100 내지 2000 Hz 의 펄스 레이트 (pulse rate) 로, 또는 보다 특별히 약 100 내지 300 Hz 의 펄스 레이트로, 또는 약 400 내지 900 Hz 의 펄스 레이트로, 그리고 약 10% 내지 90% 의 듀티 사이클 (duty cycle), 또는 보다 특별히 약 10% 내지 60% 의 듀티 사이클을 가지고 기판-바이어스된 RF 전력을 펄싱하는 것을 더 포함할 수도 있다. 이러한 방식으로 바이어스 전압을 펄싱하는 것은, 어떤 실시예들에서는, 수직적 예칭 레이트를 향상시킨다고 발견되었다.

[0065] 어떤 실시예들에서는, 유도성-커플링된 RF 전력은 약 500 내지 1900 와트, 또는 보다 특별히 약 500 내지 600 와트 또는 약 1300 내지 1900 와트이다. 어떤 실시예들에서, 유도성-커플링된 RF 전력은 제1 생성 코일 및 제2 생성 코일을 포함하는 생성 코일 (generating coil) 에 의해 생성되고, 제1 생성 코일은 프로세싱 챔버의 내부 영역에 유도성-커플링된 RF 전력을 공급하고, 제2 생성 코일은 프로세싱 챔버의 외부 영역에 유도성-커플링된 RF 전력을 공급하며, 유도성-커플링된 RF 전력의 총합은 약 0.1 내지 1.5의 비율로 제1 생성 코일과 제2 생성

코일 간에서 나눠진다 (split). 어떤 실시예들에서, 수평적 에칭 동작에 사용되는 자유 라디칼 종들 (free radical species) 을 포함하는 플라즈마는 RF 전력에 의해 생성되고, 유지된다.

[0066] 어떤 실시예들에서, 수평적 피쳐들 내에서 눈에 띄게 좌우 방향으로 에칭하지 않고 주로 중앙 수직적 구조물의 측벽들로부터 텅스텐을 제거하기 위해 워드라인 컷을 행하는 습식 에칭 기술 (wet etch technique) 을 사용하는 것은 실현 가능하다는 점에 주목하라.

#### [0067] 수평적 에칭

[0068] 위에서 기술된 바와 같이, 본 명세서에 개시된 균일한 텅스텐 증착을 달성하기 위한 기술들은 수직적 에칭 뿐만 아니라 수직적 에칭도 채용할 수도 있다. 다시 한번, 위에서 기술된 바와 같이, 수평적 에칭은 좌우 방향으로 에칭하는데 사용될 수도 있고, 3-D VNAND 스택들의 수평적 워드라인들 내의 이전에 증착된 텅스텐 재료에 의해 형성된 편치-오프 점들을 개방할 수도 있다. 어떤 실시예들에서, 수평적 에칭 동작은 활성화된 에칭 재료를 제공하는 것, 및 활성화된 에칭 재료를 사용하여 워드라인들의 내부 이내로부터 텅스텐-함유 재료의 초기-증착된 층의 일부분들을 제거하는 것을 포함한다. 어떤 실시예들에서, 활성화된 에칭 재료는 (아래에서 기술될 바와 같이) 프로세싱 챔버로부터 멀리 생성될 수도 있고, 수평적 에칭 동작을 수행하도록 프로세싱 챔버로 유동될 수도 있다. 다른 실시예들에서, 위에서 지적된 바와 같이, 수평적 에칭 동작에 사용되는 활성화된 에칭 재료는 수직적 에칭 동작에 사용되는 활성화된 에칭 재료의 변환으로부터 생성될 수도 있고, 변환은 에칭될 수직적 피쳐/구조물 내에서 행해진다. 예를 들어, 만약 수직적 에칭 재료가 (수직적 피쳐의 베이스로 전기장을 통해 지향되는) 이온 종들을 포함한다면, 이온 종들은, 수직적 구조물의 베이스에서의 기판과의 충돌 후에 주위의 재료로부터 전자들을 받아들임으로써 중성 수평적/래터럴 에칭 재료로 변환시킬 수도 있다.

[0069] 수평적 에칭에 사용되는 활성화된 에칭 재료는 자유 라디칼-베이스의 플라즈마일 수도 있다. 특정의 이러한 실시예들에서, 자유 라디칼-베이스의 플라즈마는 수평적 에칭을 수행하는 프로세싱 챔버에 도입되기 전에 프로세싱 챔버로부터 멀리 생성될 수도 있다. 플라즈마를 형성하는 자유 라디칼 종들은 다양한 불소 라디칼 종들을 포함할 수도 있고, 상응하게 이러한 자유 라디칼-베이스의 플라즈마에 대한 화학적 전구체들 (즉, 플라즈마 시료들) 은 다양한 종류의 불소-함유 화합물들을 포함할 수도 있다. 예시들은  $NF_3$ 를 포함한다. 다른 예시들은  $CF_4$ ,  $CHF_3$ ,  $CH_2F_2$ , 및  $CH_3F$ , 또는 어떤 실시예들에서는 어쩌면 가능하게  $SF_6$ 를 포함한다. 또한, 비-불소 함유 플라즈마 시료들은 염소-함유 화합물들과 같은 다른 에천트들을 포함할 수도 있다.

[0070] 멀리 생성된 플라즈마를 채용하는 실시예들에서, 플라즈마를 포함하는 여기 가스 (excited gas) 는 프로세싱 챔버와 유체적으로 연결된 1 이상의 가스 도관들 또는 공급 라인들을 통해 수평적 에칭이 발생할 프로세싱 챔버로 공급될 수도 있다. 텅스텐 에칭 동작들을 위해 멀리 생성되는 플라즈마를 채용하는 장치들은 이하에서 보다 구체적으로 기술된다.

[0071] 수평적 에칭은 챔버 동작 조건들의 범위를 넘어 수행될 수도 있다. 어떤 실시예들에서, 수평적 에칭 동안의 프로세싱 챔버 내의 온도는 약 50 내지 400 °C, 또는 보다 특별히 약 50 내지 250 °C 로 유지될 수도 있다. 어떤 실시예들에서, 약 150 °C 보다 낮은 온도가 사용될 수도 있다. 어떤 실시예들에서, 수직적 에칭 에칭 동안의 프로세싱 챔버 내의 압력은 약 10 Torr 보다 작게, 예를 들어 약 5 Torr 보다 작게, 또는 심지어 2 Torr 보다 작게 유지될 수도 있다. 어떤 실시예들에서, 수평적 에칭에서 사용되는 활성화된 에칭 재료가 수직적 에칭에 사용되는 활성화된 에칭 재료의 변환을 통해 생성되는 경우에서와 같이, 수평적 에칭 동안의 프로세스 조건들은 수직적 에칭 동안 채용되는 프로세스 조건들과 동일하다.

[0072] 수평적 에칭을 위한 다양한 기술들이, 모든 목적들을 위해 본 명세서에 참조로서 포함되는, 2013년 3월 27일에 출원된 미국 출원번호 제13/851,885호에 기술된다. 예를 들어, 에칭 컨포말러티 모듈레이션 (etch conformality modulation) 은 그 안에서 기술되고 수평적 에칭 동안 피쳐 프로파일을 튜닝하기 (tune) 위해 채용될 수도 있다. 온도, 압력 및 유속은, 예를 들어 불소 라디칼 베이스의 에칭의 프로파일을 튜닝하기 위해 제어될 수도 있다. 보다 높은 온도들에서, 들어오는 (incoming) 불소 원자들은 쉽게 반응하여 피쳐 입구에서 에칭하고, 그 결과 보다 많은 비-컨포멀 에칭이 야기되고; 보다 낮은 온도에서, 들어오는 불소 원자들은 확산되고 피쳐 내에서 추가적으로 에칭될 수 있고, 그 결과 보다 컨포멀한 에칭이 야기된다. 보다 높은 에천트 유속은 보다 많은 불소 원자 생성을 야기하고, 보다 많은 불소 원자들이 확산되고 피쳐 내에서 추가적으로 에칭되게 하

여, 결과적으로 보다 컨포멀한 에칭에 이른다. 보다 낮은 에천트 유속은 보다 적은 불소 원자 생성을 야기하고, 이것은 피쳐 입구에서 반응하고 에칭하는 경향이 있어, 보다 비 컨포멀한 에칭에 이른다. 보다 높은 압력은 불소 라디칼들의 보다 많은 재결합 (recombination) 을 야기하여 분자 불소를 형성하게 할 것이다. 분자 불소는 불소 라디칼들보다 더 낮은 흡착 계수 (sticking coefficient) 를 가지고, 그래서 보다 쉽게 텅스텐 에칭 전에 피쳐 내로 확산되고, 보다 컨포멀한 에칭에 이른다.

[0073] 장치들

[0074] 본 명세서에 제공된 텅스텐 증착 및 에칭 방법들은 다양한 판매자들로부터 입수 가능한 다양한 증착 장치 및/또는 에칭 장치로 수행될 수도 있다. 적합할 수도 있는 장치들의 예시들은 노벨러스 Concept-1 ALTUS<sup>TM</sup>, Concept-2 ALTUS<sup>TM</sup>, Concept-2 ALTUS-S<sup>TM</sup>, Concept-3 ALTUS<sup>TM</sup>, 및 ALTUS Max<sup>TM</sup> 증착 시스템들, 또는 임의의 다양한 여타의 상업적으로 입수 가능한 화학적 기상 증착 (CVD) 툴들을 포함한다. 사용될 수도 있는 장치의 예시는, 어떤 실시예들에서는, 다양한 수직적 에칭 동작 및/또는 수평적 에칭 동작을 수행하기 위한, 램 리씨치 사의 키요 에칭 툴 (Kiyo etch tool) 이다. 다른 예시들은 어플라이드 머터리얼스 사의 Mesa 및 C3 제품들 등을 포함한다. 도쿄 일렉트로닉 사의 RLSA 등이 어떤 실시예들에서는 래터럴 에칭에 사용될 수도 있다. 히타치 또한 어떤 실시예에서는 수평적 에칭 및/또는 수직적 에칭에 사용될 수도 있는 다양한 툴들을 제조한다. 일반적으로, 수직적 에칭 및 가능하다면 수평적 에칭 동작들에 사용되는 툴은 이온 플라즈마를 생성할 수 있고, 바람직하게는 기판의 평면에 실질적으로 수직인 지향성 (directionality) 을 가지고, 기판 방향으로 플라즈마의 이온들을 지향시킬 수 있을 것이다.

[0075] 도 6은 특정 실시예들에 따른, 부분적으로 가공된 반도체 기판을 처리하기 위한 장치 (600) 의 개략적인 묘사를 도시한다. 장치 (600) 는 페데스탈 (pedestal, 620) 을 가진 챔버 (618), 샤크 헤드 (614), 인-시츄 플라즈마 생성기 (616) 및 원격 플라즈마 생성기 (606) 를 포함한다. 장치 (600) 는 또한 입력을 받고/받거나 다양한 디바이스들에 제어 신호들을 공급하기 위한 시스템 컨트롤러 (622) 를 포함한다.

[0076] 위에서 기술된 바와 같이, 반도체 피쳐들의 균일한 텅스텐 충진을 달성하기 위해 (또는 적어도 실질적으로 균일한 및/또는 비교적으로 또는 상대적으로 균일한 텅스텐 충진을 달성하기 위해) 본 명세서에 개시된 어떤 방법들은 1 이상의 자유 라디칼 종들을 포함하는 플라즈마일 수도 있는 활성화된 에칭 재료를 사용하여 텅스텐을 에칭하는 동작을 포함한다. 어떤 실시예들에서, 프로세싱 챔버로부터 멀리 떨어지지만 프로세싱 챔버와 유체적으로 연결된 플라즈마 생성기는, 이후에 유체 연결을 통해 프로세싱 챔버로 공급되는 자유 라디칼 종들 및 플라즈마를 생성하는데 사용될 수도 있다. 도 6에 개략적으로 도시된 실시예는, 예를 들어 연결 라인 (608) 을 통해 프로세싱 챔버 (618) 와 유체적으로 연통되는 원격 플라즈마 생성기 (606) 를 가지는 이러한 한가지 실시예이다. 시스템 컨트롤러 (622) 는, 도면에 도시된 바와 같이, 원격 플라즈마 생성기 (606) 로부터 프로세싱 챔버 (618) 로의 활성화된 에칭 재료의 공급을 제어하는 것 뿐만 아니라, 원격 플라즈마 생성기 (606) 의 동작을 제어할 수도 있다.

[0077] 임의의 적절한 원격 플라즈마 생성기가, 그것을 챔버 (618) 내로 도입하기 전에, 텅스텐 애천트를 활성화시키는 데 사용될 수도 있다. 예를 들어, 앤드오버, 매사추세츠 (Andover, Massachusetts) 에 위치한 MKS 인스트루먼츠 사로부터 모두 입수 가능한, ASTRON<sup>®</sup> i Type AX7670, ASTRON<sup>®</sup> e Type AX7680, ASTRON<sup>®</sup> ex Type AX7685, ASTRON<sup>®</sup> hf-s Type AX7645 와 같은 원격 플라즈마 생성 유닛들이 사용될 수도 있다. 일반적으로, 원격 플라즈마 생성 유닛은 통상적으로 공급된 에천트 시약을 사용하여 (또한 어느 정도 약하게 이온화될 수도 있는) 자유-라디칼 베이스의 플라즈마를 생성하는 자체-내장된 디바이스이다. 원격 플라즈마 생성기는 플라즈마 내의 전자들에 에너지를 공급하는 고전력 RF 생성기이다. 이 에너지는 그렇다면 중성 에천트 시약으로 전달되어 대략 20,000K 의 온도로 이어져서 이러한 분자들의 열적 해리 (thermal dissociation) 를 야기하게 된다. 원격 플라즈마 생성기 유닛은 그것의 높은 RF 에너지 및 특수한 채널 기하구조 (special channel geometry) 때문에 들어오는 에천트 시약의 60% 이상을 해리시킬 수 있어, 에천트가 이 에너지의 대부분을 흡수하게 한다. 어떤 실시예들에서, 초음파 소스가 에천트 시약의 분자들을 여기시키는데 (excite) 사용될 수도 있다. 어떤 실시예들에서, 실시예에 따라, 약 400 kHz 내지 60 MHz, 또는 약 400kHz 내지 27 MHz, 또는 약 27 내지 60 MHz, 또는 구체적으로 13.56 MHz 혹은 27 MHz 혹은 60 MHz 의 RF에서 원격 플라즈마 생성기를 동작시킴으로; 그리고 약 400

내지 2000 와트의 RF 전력을 생성함으로써, 적절한 플라즈마들이 생성될 수도 있다.

[0078] 특정 실시예들에서, 도 6에 도시된 것과 같이, 에천트가 원격 플라즈마 생성기 (606)로부터 연결 라인 (608)을 통해 챔버 (618)로 유동되는데, 여기서 혼합물은 샤큐 헤드 (614)를 통해 나누어 퍼뜨려진다 (distributed). (원격 플라즈마 생성기에서 생성되는) 활성화된 에칭 재료에 대한 전구체들을 담당하는 화학적 종들은 - 즉, 에천트 시약들 - 저장 탱크일 수도 있는 소스 (602)를 통해 생성기로 공급될 수도 있다. 또한, 특정 실시예들에서, 아르곤, 헬륨 및 여타의 것들과 같은 불활성 가스들은 또한 저장 탱크일 수도 있는 소스 (603)로부터 원격 플라즈마 생성기 (606)에 또한 공급된다.

[0079] 어떤 실시예들에서, 위에서 기술된 바와 같이, 본 명세서에 개시된 텅스텐 증착 및 에칭 동작들은, 원격 플라즈마 생성기 (606) 내의 플라즈마 생성과 같은 원격 활성화 (remote activation) 대신에 또는 이와 더불어, 프로세싱 챔버 (618) 그 자체 내에서 활성화되는 (즉, 인 시츄 (in situ)) 활성화된 에천트 재료를 채용할 수도 있다. 이러한 특정 실시예들에서, 이러한 인 시츄 생성된 플라즈마는 1 이상의 이온화된 에천트 종들을 포함할 수도 있다. 이러한 특정 실시예들에서, 이러한 이온들은 에칭될 텅스텐 재료를 향하여 인가된 전자기장에 의해 지향될 수도 있다.

[0080] 다양한 불소 함유 화합물들과 같은 다양한 적절한 전구체 에천트 시약들이 위에서 기술되었다. 인 시츄 플라즈마 활성화를 채용하는 실시예들에서, 이러한 전구체 종들은 - 원격 플라즈마 생성기 (606)를 완전히 우회하는 방식으로 - 예컨대, 도 6의 연결 라인 (608)의 그것과 유사한 연결 라인을 통해 에천트를 직접 전달하지만, 그것이 원격 플라즈마 생성기 (606)에 실제로 연결되지 않음으로써, 프로세싱 챔버에 직접 제공될 수도 있다. 어떤 실시예들에서, 원격 플라즈마 생성기는 심지어 존재하지 않을 수도 있다. 대안적으로, 인 시츄 플라즈마 생성을 위한 에천트 시약의 프로세싱 챔버로의 전달은, 에천트 시약이 그것을 통해 유동되게 하고 이후 에천트 시약이 활성화될 챔버 (618) 내로 유동되게 하는 동안 원격 플라즈마 생성기 (606)를 끔으로써, 달성될 수도 있다. 물론, 다시 한번, 이러한 인 시츄 플라즈마 활성화/생성은, 원격 플라즈마 활성화 대신에, 또는 그와 함께 행할 수 있다.

[0081] 일단 전구체 에천트 시약들이 프로세싱 챔버 (618) 내로 도입되면, 인 시츄 플라즈마 활성화는 샤큐 헤드 (614) 및 페데스탈 (620)에 부착된 내부 플라즈마 생성기 (616)를 통해 달성될 수도 있다. 특정한 실시예에서, 내부 플라즈마 생성기 (616)는 약 1 내지 100 MHz의 주파수들로 약 0 W 내지 10,000 W의 전력을 공급할 수 있는 고주파수 (HF) RF 생성기이다. 보다 구체적인 실시예에서, 고주파수 RF 생성기는 약 13.56 MHz에서 약 0 내지 5,000 W의 전력을 전달할 수도 있다.

[0082] 위에서 기술된 바와 같이, 이러한 인 시츄 플라즈마는, 어떤 실시예들에서, 수직적 구조물들의 측벽들에서 구멍들을 가진 수평적 구조물들의 내부로부터 텅스텐-함유 재료를 실질적으로 제거하지 않으면서, 다양한 고 종횡비 수직적 구조물의 측벽들로부터 증착된 텅스텐-함유 재료를 제거하는데 사용될 수도 있다. 어떤 실시예들에서, 인 시츄 생성된 플라즈마는 1 이상의 이온 종들을 포함할 수도 있다. 이러한 특정 실시예들에서, 수직적 측벽들 대 (versus) 수평적 괴쳐 내부들의 우선적 에칭 (preferential etch)은, 이온들의 일부분이 대체적으로 아래 방향, 에칭될 수직적 괴쳐의 바닥을 향하여 지향되도록, 전자기장을 이온들에 인가함으로써 달성될 수도 있다 (다시 한번, 위에서 보다 자세히 기술된 바와 같음).

[0083] 챔버 (618)는, 증착 및 에칭의 정도, 농도, 압력, 온도 및 기타의 것들과 같은 다양한 프로세스 파라미터들을 센싱하는 센서 (624)를 포함할 수도 있다. 센서 (624)는 시스템 컨트롤러 (622)에 대한 프로세스 동안의 챔버 조건들에 대한 정보를 제공할 수도 있다. 센서 (624)의 예시들은 매쓰 플로우 컨트롤러 (mass flow controller), 압력 센서, 써모커플 (thermocouple), 및 여타의 것들을 포함한다. 센서 (624)는 또한 챔버 내에서 가스의 존재를 모니터링하고 측정값들을 제어하기 위해 적외선 디텍터 또는 광 디텍터를 포함한다. 센서들은, 원격 플라즈마 생성기 (606)로부터의 그리고 원격 플라즈마 생성기 (606)로의 플라즈마 종들 및 그들의 전구체들의 유속 뿐만 아니라, 프로세싱 챔버로의 환원제들 및 텅스텐-함유 전구체들의 유속을 결정하는데 이용될 수도 있는 정보를 제공할 수도 있다.

[0084] 증착 및 선택적인 제거 동작들은 챔버 (618)로부터 배기되는 다양한 휘발성 종들을 생성한다. 게다가, 프로세싱은 챔버 (618)의 특정한 미리 정해진 압력 레벨들로 행해진다. 이러한 기능들의 양자 모두는 전공 펌프일 수도 있는 전공 배출구 (626)를 사용하여 달성된다. 어떤 실시예들에서, 도 6에 개략적으로 도시된 바와 같이, 임의의 필요한 또는 유익한 프로세스 가스들이 혼합통 (610)을 통과한 후에 프로세스 가스 소스 (612)로부터 챔버 (618)로 공급될 수도 있다.

- [0085] 특정 실시예들에서, 시스템 컨트롤러 (622) 는 텅스텐 증착 및 에칭 동작들 동안 프로세스 조건들 및 파라미터들을 제어하기 위해 채용된다. 시스템 컨트롤러 (622) 는 통상적으로 1 이상의 메모리 디바이스들 및 1 이상의 프로세서들을 포함한다. 프로세서는 CPU 또는 컴퓨터, 아날로그 및/또는 디지털 입력/출력 연결들, 스텝퍼 모터 (stepper motor) 컨트롤러 보드 등을 포함할 수도 있다. 통상적으로 시스템 컨트롤러 (622) 와 연관된 유저 인터페이스 (user interface) 가 존재할 것이다. 유저 인터페이스는 표시 화면, 장치 및/또는 프로세스 조건들의 그래픽적인 소프트웨어 표시들, 및 포인팅 디바이스들 (pointing devices), 키보드들, 터치 스크린들, 마이크로폰들 등과 같은 유저 입력 디바이스들을 포함할 수도 있다.

- [0086] 특정 실시예들에서, 시스템 컨트롤러 (622) 는 기판 온도, 챔버 압력, 에천트 시료 (활성화된 에천트 전구체) 유속, 전력 출력 및 원격 플라즈마 생성기 (606) 의 동작 주파수 (또는 주파수 범위), 인 시츄 플라즈마 생성기 (616) 의 전력 출력 및 동작 주파수 (또는 주파수 범위), 및 여타의 프로세스 파라미터들을 제어한다. 시스템 컨트롤러 (622) 는 앞서 언급한 제어를 제공하기 위해 시스템 제어 소프트웨어 및 인스트럭션들 (instructions) 을 실행시킨다. 컨트롤러와 연관된 메모리 디바이스들 상에 저장된 여타의 컴퓨터 프로그램들이 어떤 실시예들에서 채용될 수도 있다.

- [0087] 프로세스 시퀀스에서 프로세스들을 제어하기 위한 컴퓨터 프로그램 코드는 임의의 종래의 컴퓨터 판독가능한 프로그래밍 언어: 예를 들어, 어셈블리 언어, C, C++, 파스칼, 포트란 또는 여타의 것들로 작성될 수 있다. 컴파일된 (compiled) 오브젝트 코드 (object code) 또는 스크립트 (script) 는 프로그램에서 식별된 테스크들을 수행하기 위해 프로세서에 의해 실행된다. 시스템 소프트웨어는 다양한 상이한 방법들로 디자인되거나 구성될 수도 있다. 예를 들어, 다양한 챔버 컴포넌트 서브루틴 (subroutine) 들 또는 제어 오브젝트들이 기술된 프로세스들을 수행하는데 필요한 챔버 컴포넌트들의 동작을 제어하기 위해 작성될 수도 있다. 이 목적을 위한 프로그램들 또는 프로그램들의 섹션들 (sections) 의 예시들은 기판 온도 제어 코드, 챔버 압력 제어 코드, 에천트 시약 (활성화된 에천트 전구체) 유속 제어 코드, 프로세스 가스 제어 코드, 원격 플라즈마 생성기 제어 코드 (가능하게는 전력 출력 및 동작 주파수 제어 코드를 포함함), 인 시츄 플라즈마 생성기 제어 코드 (가능하게는 전력 출력 및 작동 주파수 제어 코드를 포함함), 및 여타의 프로세스 파라미터들을 위한 제어 코드를 포함한다.

- [0088] 기판 온도, 챔버 압력, 에천트 시약 (활성화된 에천트 저구체) 유속, 원격 플라즈마 생성기의 전력 출력 및 작동 주파수 (또는 주파수 범위), 인 시츄 플라즈마 생성기의 전력 출력 및 작동 주파수 (또는 주파수 범위), 및 여타의 프로세스 파라미터들을 제어하기 위한 파라미터들은 레시피 (recipe) 의 형태로 유저에 의해 제공될 수도 있고, 유저 인터페이스를 이용하여 입력될 수도 있다.

- [0089] 프로세스를 모니터링하기 위한 신호들은 시스템 컨트롤러 (622) 의 아날로그 및/또는 디지털 입력 연결들에 의해 제공될 수도 있다. 프로세스들을 제어하기 위한 신호들은 장치 (600) 의 아날로그 및 디지털 출력 연결들 상에 출력된다.

- [0090] 도 7은 본 명세서에 개시된 다양한 실시예들과 따른, 텅스텐 증착 프로세스들을 수행하기에 적합한 CVD 프로세싱 시스템의 블록 다이어그램을 개략적으로 도시한다. 시스템 (700) 은 이송 모듈 (703) 을 포함한다. 이송 모듈 (703) 은 그들이 다양한 반응 모듈들 사이에서 이동됨으로서 처리될 기판의 오염의 위험을 최소화하도록 깨끗하고 기밀된 (pressurized) 환경을 제공한다. 이송 모듈 (703) 에 장착된 것은 본 명세서에 개시된 다양한 텅스텐 증진에 따른 PNL 및 CVD 프로세스들을 수행할 수 있는 다중-스테이션 반응기 (709) 이다. 챔버 (709) 는 이러한 동작들을 순서대로 수행할 수도 있는 복수의 스테이션들 (711, 713, 715, 717) 을 포함할 수도 있다. 예를 들어, 챔버 (709) 는, 스테이션 (711) 이 PNL 증착을 수행하고, 스테이션 (713) 이 1 이상의 처리 동작들 (treatment operations) 을 수행하고, 스테이션들 (715 및 717) 이 CVD를 수행하도록 구성될 수 있다.

- [0091] 또한, 이송 모듈 (703) 에 장착된 것은 플라즈마 또는 화학적 (비-플라즈마) 전-세정 (pre-cleans), 수평적 에칭 및/또는 수직적 에칭을 수행하는 것이 가능한 1 이상의 단일 또는 다중-스테이션 모듈들 (707) 일 수도 있다. 모듈은 또한 다양한 여타의 처리들 예를 들어 후 라이너 텅스텐 나이트라이드 처리들 (post liner tungsten nitride treatments) 을 위해 사용될 수도 있다. 시스템 (700) 은 또한 웨이퍼들이 프로세싱 전 및 후에 저장되는 1 이상의 (이 경우에는 2개의) 웨이퍼 소스 모듈 (701) 을 포함한다. 대기압의 이송 챔버 (719) 내의 대기압의 로봇 (미도시) 은 먼저 소스 모듈들 (701) 로부터 로드록 (loadlock, 721) 들로 웨이퍼들을 제거 한다. 이송 모듈 (703) 내의 웨이퍼 이송 디바이스 (일반적으로 로봇 아암 유닛) 는 로드록들 (721) 로부터 이송 모듈 (703) 에 장착된 모듈들로 그리고 이송 모듈 (703) 에 장착된 모듈들 가운데에 웨이퍼들을 이동시킨다.

- [0092] 도 8은 특정텅스텐 증착 및/또는 에칭 동작들을 수행하는데 이용될 수도 있는 다중-스테이션 장치 (1300) 를 개략적으로 도시한다. 장치 (1300) 는 다수의 스테이션들을 내장하는 프로세싱 챔버 (1301) 를 포함한다. 이러한

한 특정 실시예에서, 프로세싱 챔버 (1301) 는 4개의 스테이션들 (1331, 1332, 1333 및 1334) 를 내장하는데, 그러나 다른 실시예들에서는, 2개 또는 3개 또는 4개 보다 많은 스테이션들이 적절한 프로세싱 챔버 내에 내장될 수도 있다. 이러한 실시예에서, 4 개의 스테이션들 속에서 웨이퍼를 훌딩하고 회전시키도록 기능하는, 도면에서의 4 개의 스테이션들 (1331, 1332, 1333 및 1334) 과 일치하는 4 개의 웨이퍼 캐리어 링들 (wafer carrier rings) 이 존재한다. 인덱싱 툴 (indexing tool, 1309) 은 스테이션들 (1331, 1332, 1333, 및 1334) 사이에서 회전함으로써, 각각의 웨이퍼를 캐리어 링을 통해 어느 하나의 스테이션에서 다음의 스테이션으로 이송한다.

[0093] 프로세싱 챔버 (1301) 를 가진 다중-스테이션 장치 (1300) 내의 모든 스테이션들은 시스템 컨트롤러 (1374) 에 의해 제어되는 동일한 압력 환경에 노출될 수도 있다. 센서들 (미도시) 은 또한 챔버 압력 측정값 (reading) 을 제공하는 압력 센서를 포함할 수도 있다. 그러나, 각 스테이션은 개별 온도 조건들 또는 여타의 조건들을 가질 수도 있다.

[0094] 여전히 도 8을 참조하면, 증착 프로세스에서, 통상적으로 프로세스될 웨이퍼는 카세트 (cassette) 로부터 로드-록 (1305) 을 통해 스테이션 (1331) 으로 로딩된다. 외부 로봇 (1307) 은 카세트로부터 로드-록 (1305) 으로 웨이퍼를 이송하도록 사용될 수도 있다. 도시된 실시예에서, 2개의 개별 로드-록 (1305) 이 존재한다. 이것들은 통상적으로 프로세싱 챔버 (1301) 로부터의 제거를 위해 로드-록 (1305) 으로부터 스테이션 (1331) 으로, 그리고 스테이션 (1334) 으로부터 다시 로드-록 (1305) 으로 웨이퍼를 이동시키도록 웨이퍼 이송 디바이스들을 갖추고 있다.

[0095] 시스템 컨트롤러 (1374) 는 인덱싱 툴 (1309), 스테이션들, 및 프로세싱 챔버 (1301) 의 조건들, 예컨대 챔버의 압력을 제어할 수 있다. 예를 들어, 컨트롤러 (1374) 는 스테이션들 (1331, 1332, 1333 및 1334) 사이에서 웨이퍼를 이동시킬 수도 있다.

[0096] 어떤 실시예들에서, 프로세싱 챔버 내의 특정 스테이션들은 본 명세서에 개시된 균일한 텅스텐 충진 동작들의 특정 증착 동작 및 특정 에칭 동작을 수행하도록 사용될 수도 있다. 예를 들어, 텅스텐 증착은 참조번호 1331 과 같은 하나의 스테이션에서 행해질 수도 있고, 수직적 에칭은 참조번호 1332와 같은 다른 스테이션에서 행해질 수도 있고, 수평적 에칭은 참조번호 1333과 같은 제3의 스테이션에서 행해질 수도 있고, 마지막으로 추가적인 텅스텐 증착 동작은 참조번호 1334와 같은 또다른 제4의 스테이션에서 행해질 수도 있다. 다른 실시예들에서, 1 이상의 앞서 언급한 동작들은 단일 스테이션에서 행해질 수도 있다. 뿐만 아니라, 복수의 스테이션들은 상이한 반도체 기판들 상에서 병렬적으로 동일한 동작들을 수행하는데 사용될 수도 있다. 예를 들어, 만약 4개의 동작들 및 8개의 스테이션들이 존재한다면, 쌍으로 반도체 기판들을 처리하는 것이 실행가능하고/거나 적합할 수도 있다.

[0097] 다른 예시에서, 만약 제1 스테이션 (1331) 이 텅스텐 증착에 사용된다면, 그렇다면 환원성 가스 (reducing gas) 들 및 텅스텐-함유 가스들은, 기판 표면에서 국부적인 분위기 (localized atmosphere) 를 만드는 개별 가스 공급 시스템을 사용하여, 대안적으로 제1 스테이션 (1331) 에서 반도체 기판의 표면에 도입되도록 할 수도 있다.

[0098] 어떤 실시예들에서, 유도성 커플링된 플라즈마 반응기는 위에서 기술된 것과 같은 수직적 에칭에 사용되는 인시츄 플라즈마를 생성하는데 사용될 수도 있다. 이러한 반응기의 일 실시예는 도 9에 개략적으로 도시된다. 간단하게 말해서, 유도성 커플링된 플라즈마 반응기 (20) 는 플라즈마 (22) 가 인접한 기판 (23) 에서 생성되는 프로세스 챔버 (21) 를 포함한다. 기판은 웨이퍼 냉각 기판 지지체 (24) 상에 지지되고, 기판의 온도 제어는 기판과 기판 지지체 사이의 공간에 도관 (25) 을 통해 헬륨 가스를 공급함으로써 달성된다. 기판 지지체는 가열될 수도 있는 아노다이징된 (anodized) 알루미늄 전극, 또는 그 안에 매립된 전극을 가지는 세라믹 재료, RF 매칭 (matching) 을 제공하기 위해 RF 소스 (26) 및 관련된 전기회로 (27) 에 의해 전력공급되는 전극 등을 포함할 수 있다. 그것의 프로세싱 동안의 기판의 온도는 온도 프로브 (29) 에 부착된 온도 모니터링 장치 (28) 에 의해 모니터링된다.

[0099] 진공을 챔버 (21) 에 공급하기 위해, 펌프는 배출구 포트 (30) 에 연결되고, 압력 제어 밸브가 원하는 진공 압력을 유지하도록 사용될 수 있다. 프로세스 가스들은, 유전체 윈도우 (33) 의 밀면 주변으로 연장되는 가스 분배 링들에 플라즈마 시약 가스들을 공급하는 공급 라인 또는 도관들 (31, 32) 에 의해 챔버로 공급될 수 있고, 또는 프로세스 가스들은 유전체 샤퍼헤드 윈도우를 통해 공급될 수 있다. 윈도우와 인접하여 챔버 외부에 위치되는 외부 ICP 코일 (34) 에는, 임피던스 매칭 등을 위해 RF 소스 (35) 및 관련 전기회로 (36) 에 의해 RF 전력이 공급된다. 명백한 바와 같이, 외부 유도 코일은 실질적으로 평면이고, 일반적으로 평면적 나선 (planar spiral) 또는 일련의 동심 링들로 형성되는 단일 도전성 엘리먼트를 포함한다. 평면적 구성은, 코일 직경을 증

가시키는 더 긴 도전성 엘리먼트를 채용함으로써, 코일이 쉽게 확장되게 하고 (scaled-up), 이에 따라 더 큰 기판들을 수용하거나 복수의 코일 배열들이 넓은 영역에 걸쳐 균일한 플라즈마를 생성하도록 사용될 수 있다. 기판이 챔버 내에서 처리될 때, RF 소스 (35)는 코일 (34)에 유도성-커플링된 RF 전력을 공급하고, RF 소스 (26)는 하부 전극에 기판-바이어스된 RF 전력을 공급한다.

[0100] 어떤 실시예들에서, 유도성-커플링된 RF 전력은 약 13 내지 60 MHz 의 주파수로 RF 소스 (35)에 의해 생성될 수도 있고, 한편 기판-바이어스된 RF 전력은 약 400 kHz 내지 13.5 MHz 의 주파수로 RF 소스 (36)에 의해 생성될 수도 있다. 어떤 실시예들에서, 기판-바이어스된 RF 전력은 기판에 대하여 약 100 내지 1000 볼트의 전압을 가질 수도 있다. 어떤 실시예들에서, 기판-바이어스된 RF 전력은 약 10% 내지 90%의 드티 싸이클을 가지고, 약 100 Hz 내지 2000 Hz 의 펄스 레이트로 RF 소스 (26)에 의해 펄싱될 수도 있다. 어떤 실시예들에서, RF 소스 (35)는 약 500 내지 1900 와트의 유도성-커플링된 RF 전력을 생성할 수도 있다.

[0101] 위에서 언급한 바와 같이, 복수의 동심의 생성 코일들은 더 넓은 영역에 걸쳐 플라즈마를 생성하는데 이용될 수도 있다. 따라서, 어떤 실시예들에서, 유도성-커플링된 RF 전력은 제1 생성 코일 및 제2 생성 코일의 쌍에 의해 생성될 수도 있다. 이러한 특정 실시예들에서, 제1 생성 코일은 프로세싱 챔버의 내부 영역에 유도성-커플링된 RF 전력을 공급할 수도 있고, 제2 생성 코일은 프로세싱 챔버의 외부 영역에 유도성-커플링된 RF 전력을 공급할 수도 있다. 어떤 구성들에서, 유도성-커플링된 RF 전력의 총합은 약 0.1 내지 1.5의 비율로 제1 생성 코일과 제2 생성 코일 간에서 나눠질 수도 있다 (split).

[0102] 기판의 표면 상의 큰 DC 쉬스 전압 (sheath voltage) 이 전극으로 RF 전력을 공급함으로써 제공될 수 있다. RF 바이어스는 통상적으로, 수직적 예칭을 대상으로 한 기판 상의 고 종횡비 구조물의 베이스를 향하여 아래 방향으로 플라즈마 이온들을 지향시키도록 기판에 인가된다. 어떤 실시예들에서, RF 주파수는 기판 주변의 정상 상태 쉬스 전압 (steady state sheath voltage) 을 지속하는데 필요한 값 - 종종 몇백 kHz - 위의 어떤 것이도록 선택될 수 있다.

[0103] 어떤 실시예들에서, (1 이상의 물리적 또는 논리적 컨트롤러들을 포함할 수도 있는) 시스템 컨트롤러는 예칭 챔버, 중착 챔버, 및/또는 1 이상의 예칭 모듈들 및/또는 1 이상의 중착 모듈들을 포함하는 다중-모듈 터의 동작들의 일부 또는 전부를 제어한다. 시스템 컨트롤러는 1 이상의 메모리 디바이스들 및 1 이상의 프로세서들을 포함할 수도 있다. 프로세서는 중앙 처리 유닛 (CPU) 또는 컴퓨터, 아날로그 및/또는 디지털 입력/출력 연결들, 스텝퍼 모터 (stepper motor) 컨트롤러 보드, 및 여타의 이와 같은 컴포넌트들을 포함할 수도 있다. 적합한 제어 동작들을 시행하기 위한 인스트럭션들이 프로세서 상에서 실행된다. 이러한 인스트럭션들은 컨트롤러와 연관된 메모리 디바이스들에 저장될 수도 있고, 또는 그들은 네트워크 상에서 제공될 수도 있다. 특정 실시예들에서, 시스템 컨트롤러는 시스템 제어 소프트웨어를 실행한다.

[0104] 시스템 제어 소프트웨어는, 1 이상의 다음과 같은 챔버 동작 조건들의 적용의 타이밍 (timing) 및/또는 크기를 제어하기 위한 인스트럭션들을 포함할 수도 있다: 챔버 동작 조건들은 가스들의 혼합률 및/또는 조성, 챔버 압력, 챔버 온도, 웨이퍼 온도, 웨이퍼에 인가된 바이어스, 코일들 또는 다른 플라즈마 생성 컴포넌트들에 인가된 주파수 및 전력, 웨이퍼 위치, 웨이퍼 이동 속도, 및 터에 의해 수행되는 특정 프로세스의 여타의 파라미터들이다. 시스템 제어 소프트웨어는 임의의 적절한 방식으로 구성될 수도 있다. 예를 들어, 다양한 프로세스 터 컴포넌트 서브루틴 (subroutine) 또는 제어 오브젝트들이, 다양한 프로세스 터 프로세스들을 수행하는데 충분한 프로세스 터 컴포넌트들의 동작을 제어하도록 쓰여질 수도 있다 (written). 시스템 제어 소프트웨어는 이의의 적절한 컴퓨터 판독가능한 프로그래밍 언어로 코딩될 수도 있다.

[0105] 어떤 실시예들에서, 시스템 제어 소프트웨어는 위에서 기술된 다양한 파라미터들을 제어하기 위한 입력/출력 제어 (IOC) 시퀀싱 인스트럭션들을 포함한다. 예를 들어, 각각의 페이즈 (phase)의 반도체 가공 프로세스는, 시스템 컨트롤러에 의한 실행을 위한 1 이상의 인스트럭션들을 포함할 수도 있다. 예칭 페이즈를 위한 프로세스 조건들을 설정하기 위한 인스트럭션들은 예를 들어 대응하는 예칭 레시피 페이즈에 포함될 수도 있다. 어떤 실시예들에서, 레시피 페이즈는, 프로세스 페이즈를 위한 모든 인스트럭션들이 그 프로세스 페이즈와 함께 수행되도록, 연속적으로 배열될 수도 있다. 중착 페이즈를 위한 프로세스 조건들을 설정하기 위한 인스트럭션들은 대응하는 중착 레시피 페이즈에 포함될 수도 있다.

[0106] 다른 컴퓨터 소프트웨어 및/또는 프로그램들이 어떤 실시예들에 채용될 수도 있다. 이 목적을 위한 프로그램들 또는 프로그램들의 섹션들의 예시들은 기판 포지셔닝 (positioning) 프로그램, 프로세스 가스 조성 제어 프로그램, 압력 제어 프로그램, 히터 제어 프로그램, 및 RF 전원 공급 제어 프로그램을 포함한다.

- [0107] 어떤 케이스들에서, 컨트롤러들은 가스 농도, 웨이퍼 이동, 및/또는 코일 및/또는 정전 척 (electrostatic chuck)에 공급되는 전력을 제어한다. 어떤 케이스들에서, 컨트롤러는 가스 농도, 웨이퍼 이동, 및/또는 원격 플라즈마 생성기에 공급되는 전력을 제어한다.

- [0108] 컨트롤러는, 예를 들어 적절한 농도 (들)로 필요한 시료 (들)을 제공하는 1 이상의 유입 가스 스트림들 (inlet gas streams)을 만들도록 관련 밸브들을 개방 그리고 폐쇄함으로써 가스 농도를 제어할 수도 있다. 웨이퍼 이동은, 예를 들어 원하는대로 이동하도록 웨이퍼 포지셔닝 시스템을 지휘함으로써 제어될 수도 있다. 코일들 및/또는 척 및/또는 원격 플라즈마 생성기에 공급되는 전력은 특정 RF 전력 레벨들을 제공하도록 제어될 수도 있다. 컨트롤러들은 센서 출력 (예컨대, 전력, 포텐셜 (potential), 압력 등이 특정 문턱값 (threshold)에 이른 경우), 동작의 타이밍 (예컨대, 프로세스의 특정 시간들에서 밸브들을 개방하는 것)에 기초한 또는 유저로부터 받은 인스트럭션들에 기초한 이것들 또는 다른 측면 (aspect)을 제어할 수도 있다.