(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 603 20 301 T2 2009.06.25**

(12)

## Übersetzung der europäischen Patentschrift

(97) **EP 1 570 487 B1**

(51) Int Cl.<sup>8</sup>: **G11C 11/16 (2006.01)**

(21) Deutsches Aktenzeichen: **603 20 301.9**

(86) PCT-Aktenzeichen: **PCT/EP03/14011**

(96) Europäisches Aktenzeichen: **03 789 209.8**

(87) PCT-Veröffentlichungs-Nr.: **WO 2004/055821**

(86) PCT-Anmeldetag: **10.12.2003**

(87) Veröffentlichungstag

der PCT-Anmeldung: **01.07.2004**

(97) Erstveröffentlichung durch das EPA: **07.09.2005**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **09.04.2008**

(47) Veröffentlichungstag im Patentblatt: **25.06.2009**

(30) Unionspriorität:

**318709 13.12.2002 US**

(84) Benannte Vertragsstaaten:

**DE, FR, GB**

(73) Patentinhaber:

**IBM International Business Machines Corporation, Hopewell Junction, N.Y., US; Qimonda AG, 81739 München, DE**

(72) Erfinder:

**GOGL, Dietmar, Essex Junction, VT 05452, US; SCHEUERLEIN, Roy Edwin, Cupertino, CA 95104, US; REOHR, William Robert, Ridgefield, CT 06877, US**

(74) Vertreter:

**Müller - Hoffmann & Partner Patentanwälte, 81667 München**

(54) Bezeichnung: **ARCHITEKTUR FÜR HOCHGESCHWINDIGKEITSPEICHER**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

### Hinweis zu Rechten der Regierung

**[0001]** Die Erfindung wurde mit Unterstützung der Regierung unter der Vertragsnummer MDA972-99-C-0009 gemacht, wobei der Vertrag von der Defense Advanced Research Projects Agency (DARPA) des Verteidigungsministeriums der USA vergeben wurde. Die Regierung hält Rechte an dieser Erfindung.

### Gebiet der Erfindung

**[0002]** Die Erfindung betrifft allgemein Speierschaltungen und insbesondere Verfahren zum Auslesen und Schreiben magnetischer Speicher mit wahlfreiem Zugriff (MRAM).

### Hintergrund der Erfindung

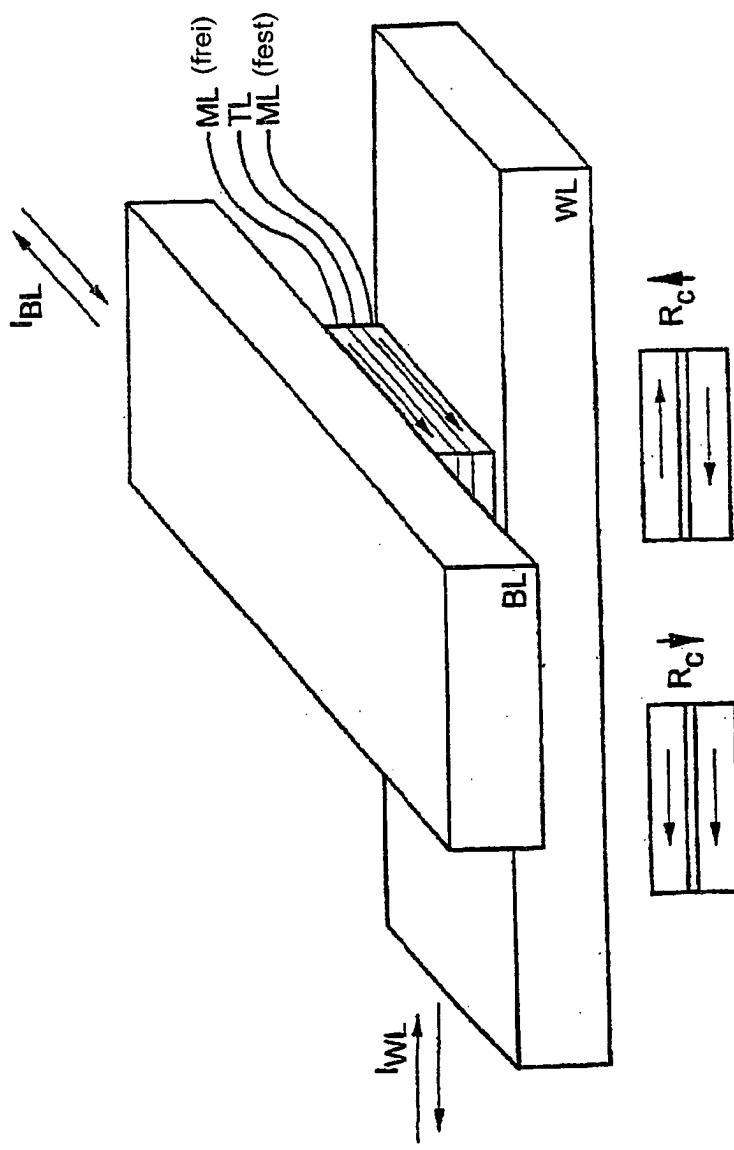

**[0003]** [Fig. 1](#) zeigt ein gewöhnliches Bauelement **100** mit magnetischem Tunnelübergang (MTJ). Der MTJ **100** besteht üblicherweise aus einem Stapel zweier ferromagnetischer Schichten (ML), die von einer Tunnelbarriere (TL) an einem Kreuzungspunkt zweier Leiter getrennt sind, wobei einer der Leiter eine Wortleitung (WL) darstellen kann und der andere Leiter einer Bitleitung (BL) entsprechen kann. Eine der beiden magnetischen Schichten wird oft als freie magnetische Schicht bezeichnet. Die magnetische Ausrichtung in der freien magnetischen Schicht kann durch Überlagerung von magnetischen Feldern geändert werden, wobei die magnetischen Felder durch Programmierströme  $I_{WL}$  und  $I_{BL}$  erzeugt werden können, welche in den Leitern WL und BL fließen. Die andere der beiden magnetischen Schichten ML wird oft als feste magnetische Schicht bezeichnet. Die Programmierströme  $I_{WL}$  und  $I_{BL}$  können die magnetische Ausrichtung der festen magnetischen Schicht nicht ändern. Der logische Zustand (z. B. ein „0“-Bit oder ein „1“-Bit) wird allgemein in dem MTJ **100** durch Ändern der Ausrichtung der freien magnetischen Schicht relativ zur festen magnetischen Schicht gespeichert. Falls beide magnetischen Schichten dieselbe Ausrichtung aufweisen, nimmt der MTJ **100** typischerweise einen hiermit verknüpften niedrigen Widerstand  $R_C$  ein, der zwischen den Leitern WL und BL gemessen wird. Ebenso ist der Widerstand  $R_C$  des MTJ **100** allgemein hoch, falls die magnetischen Schichten in entgegen gesetzten Richtungen zueinander ausgerichtet sind.

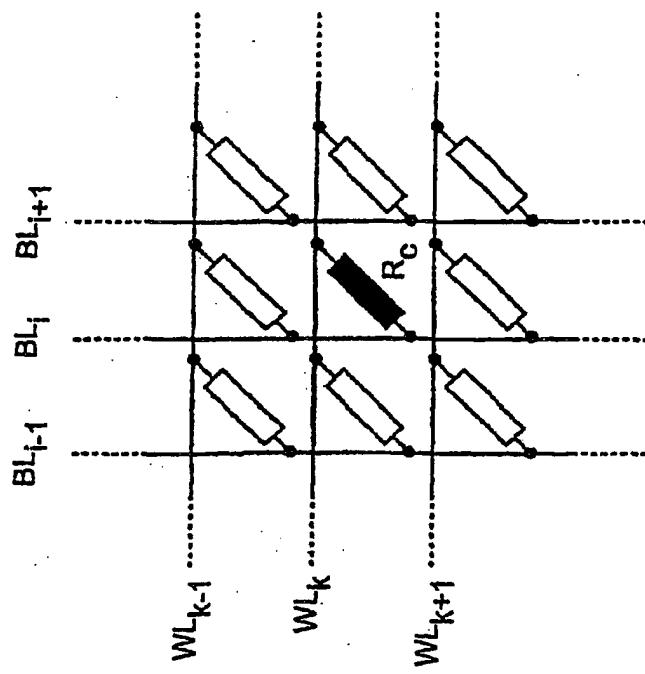

**[0004]** Ein gewöhnlicher MRAM umfasst allgemein eine Mehrzahl von MTJ-Bauelementen, die in einer Arrayanordnung miteinander verbunden sind. Zwei Beispiele herkömmlicher MRAM-Arrays sind in den [Fig. 2A](#) und [Fig. 2B](#) gezeigt. Die [Fig. 2A](#) zeigt ein Kreuzpunktarray, wobei jede Speicherzelle ein einzelnes MTJ-Bauelement aufweist, das am Schnitt-

punkt einer Wortleitung (z. B.  $WL_{k-1}$ ,  $WL_k$ ,  $WL_{k+1}$ ) und einer zugehörigen Bitleitung (z. B.  $BL_{i-1}$ ,  $BL_i$ ,  $BL_{i+1}$ ) verbunden ist. Die MTJ-Bauelemente sind in der Abbildung stellvertretend als Widerstände (z. B.  $R_C$ ) gezeigt. [Fig. 2B](#) zeigt eine alternative Speicherarchitektur unter Verwendung einer Mehrzahl von Speicherzellen, wobei jede Zelle einen Auswahltransistor aufweist, der in Serie mit einem MTJ-Bauelement geschaltet ist (d. h. eine 1T1MTJ-Speicherzelle). Der Auswahltransistor wird zum Ansteuern des zugehörigen MTJ-Bauelements während eines Lesevorgangs verwendet. MRAM-Schaltungen werden zudem detailliert in z. B. dem Artikel von W. Reohr et al. „*Memories of Tomorrow*“, IEEE Circuits and Devices Mag., S. 17–27, Vol. 18, Nr. 5, Sept. 2002 diskutiert.

**[0005]** Um die Programmierströme anzulegen, welche zum Schreiben des logischen Zustands der ausgewählten Speicherzelle erforderlich sind und zum Auslesen von Daten aus den Bitleitungen im Speicherarray, wird gewöhnlich eine Spaltenauswahlschaltung (nicht gezeigt) benötigt. Die Spaltenauswahlschaltung verbindet allgemein eine ausgewählte Bitleitung mit einer Programmierschaltung, welche den Zellenprogrammierstrom während eines Schreibvorgangs der Speicherzelle bereitstellt. Die Spaltenauswahlschaltung verbindet ebenso die ausgewählte Bitleitung mit einem Leseverstärker (nicht gezeigt) während eines Lesevorgangs der ausgewählten Speicherzelle, um den programmierten logischen Zustand der Zelle abzutasten.

**[0006]** Ein gewöhnliches MRAM-Array verwendet eine einzelne Stromquelle, um einen der beiden Programmierströme zum selektiven Schreiben der Speicherzellen in dem MRAM-Array bereitzustellen (z. B.  $I_{BL}$  oder  $I_{WL}$  in [Fig. 1](#)). Allgemein wird in einem magnetischen Speicherarray ein Wortleitungsstrom zur Unterstützung der Auswahl einer oder mehrerer Speicherzellen in dem Array benötigt. Ein oder mehrere Bitleitungsströme für eine oder mehrere zugehörige Speicherzellen einer oder mehrerer Bitleitungen werden zum Schreiben der Speicherzellen in einen logischen Null- oder einen logischen Eins-Zustand benötigt. Wie oben ausgeführt ist, stellen die durch das Speicherarray geführten Wortleitungen und Bitleitungen die Programmier- und Ausleseströme zum Schreiben und Lesen für ausgewählte Speicherzellen in dem Array bereit. Jedoch weist jede dieser Wort- und Bitleitungen eine verteilte Kapazität auf, die als Funktion der Länge der Wort- oder Bitleitung ansteigt. Da die Abstände zwischen der Programmierstromquelle und der Auslesestromquelle zur ausgewählten Speicherzelle beträchtlich sein können, insbesondere in größeren Speicherarrays, kann die entsprechende Lastkapazität, die mit den Wort- oder Bitleitungen in dem ausgewählten Signalpfad verknüpft ist, vergleichsweise groß werden. Zusätzlich tragen Schaltkreise zum Umschalten, die mit dem Lese- und Schreibpfad verknüpft sind, typi-

scherweise erheblich zur Gesamtlastkapazität bei. Diese Lastkapazität kann die Geschwindigkeit des Speicherbauelements negativ beeinflussen.

**[0007]** Somit liegt ein Bedürfnis nach einer verbesserten MRAM-Architektur vor, die sich obigen Problemen, welche in einem herkömmlichen MRAM-Array auftreten, widmet.

#### Zusammenfassung der Erfindung

**[0008]** Die Erfindung ist in den Ansprüchen 1 und 8 definiert.

**[0009]** Die Erfindung betrifft Verfahren zum Verbessern der Geschwindigkeit des Zugriffs auf Speicherzellen in einer magnetischen Speicherschaltung während eines Lese- und/oder Schreibvorgangs. Die Erfindung oder wenigstens ein Aspekt derselben gibt hierfür eine Lösung an durch Reduzieren der Lastkapazität der Bitleitungen und/oder Wortleitungen, welche mit den Speicherzellen verbunden sind, wobei die Lastkapazität primär auf das Vorliegen großer Schaltkreise zum Umschalten (z. B. Schalter, Multiplexer (MUXs), usw.) zurückzuführen ist, und diese Schaltkreise mit den Bitleitungen und Wortleitungen verbunden sind, um einen Auslesestrom und/oder Programmierstrom selektiv durch die entsprechenden Bitleitungen und Wortleitungen zu führen.

**[0010]** Da während des Auslesevorgangs ein erheblich kleinerer Strom zum Abtasten des logischen Zustands einer oder mehrerer Speicherzellen durch Unterteilen der Schalter in eine Mehrzahl getrennter Leseschalter und Schreibschalter zum Auslesen und Schreiben verwendet wird, können die Leseschalter erheblich kleiner als die entsprechenden Schreibschalter gestaltet werden. Die kleineren Schalter weisen hiermit einhergehend eine erheblich reduzierte Kapazität auf, wodurch die Geschwindigkeit des Auslesevorgangs verbessert wird. Zudem kann die Geschwindigkeit des Schreibvorgangs erheblich verbessert werden, indem eine Programmierstromquelle unterteilt wird, welche den Programmierstrom zum Schreiben des logischen Zustands der Speicherzellen für jeden Messwerteingang entlang einer Bitleitungsabmessung einer Mehrzahl von Stromquellen zuführt, wobei jede Stromquelle mit einer Gruppe einer oder mehrerer zugehöriger Schreib-Bit-Schalter verbunden ist. Deshalb können die Lastkapazitäten von den Schreib-Bit-Schaltern unter der Mehrzahl entsprechender Stromquellen aufgeteilt werden. Auf diese Weise erfährt keine einzelne Stromquelle die gesamte Lastkapazität, wodurch die Kapazität am Ausgang jeder Stromquelle reduziert und damit die Geschwindigkeit des Schreibvorgangs erhöht wird.

**[0011]** Gemäß einem Aspekt der Erfindung weist eine magnetische Speicherschaltung eine Mehrzahl von Speicherzellen auf sowie eine Mehrzahl von Bit-

leitungen, die mit den Speicherzellen zur selektiven Auswahl einer oder mehrerer der Speicherzellen verbunden sind. Die Speicherschaltung weist zudem wenigstens eine Bitleitungsprogrammierschaltung auf, die als Stromquelle zum Erzeugen eines Programmierstroms zum Schreiben eines logischen Zustands von wenigstens einer Speicherzelle und/oder als Stromsenke zum Zurücknehmen des Programmierstroms konfigurierbar ist, sowie eine erste Gruppe von Schaltern. Die erste Gruppe von Schaltern ist wenigstens während eines Lesevorgangs der Speicherzellen ausgeschaltet und wenigstens ein Teil der ersten Gruppe von Schaltern ist während eines Schreibvorgangs der Speicherzellen selektiv eingeschaltet. Jeder Schalter der ersten Gruppe von Schaltern eignet sich dazu, die wenigstens eine Bitleitungsprogrammierschaltung mit einer zugehörigen Bitleitung als Antwort auf ein erstes Steuersignal zu verbinden. Die Speicherschaltung weist zudem wenigstens einen Leseverstärker als auch eine zweite Gruppe von Schaltern auf. Die zweite Gruppe von Schaltern ist wenigstens während eines Schreibvorgangs der Speicherzellen ausgeschaltet und wenigstens ein Teil der zweiten Gruppe von Schaltern ist während eines Lesevorgangs der Speicherzellen selektiv eingeschaltet. Jeder Schalter der zweiten Gruppe von Schaltern eignet sich dazu, den wenigstens einen Leseverstärker mit einer entsprechenden Bitleitung als Antwort auf ein zweites Steuersignal zu verbinden.

**[0012]** Diese und weitere Aufgaben, Merkmale und Vorteile der Erfindung werden aus der nachfolgenden detaillierten Beschreibung beispielhafter Ausführungsformen ersichtlich, welche in Zusammenhang mit den begleitenden Abbildungen zu lesen sind.

#### Kurzbeschreibung der Abbildungen

**[0013]** [Fig. 1](#) zeigt eine grafische Darstellung eines herkömmlichen Bauelements mit magnetischem Tunnelübergang.

**[0014]** [Fig. 2A](#) zeigt eine schematische Abbildung wenigstens eines Teils eines herkömmlichen Kreuzpunkt-Speicherarrays.

**[0015]** [Fig. 2B](#) zeigt eine schematische Abbildung wenigstens eines Teils eines herkömmlichen 1T1MTJ-Speicherzellenarrays.

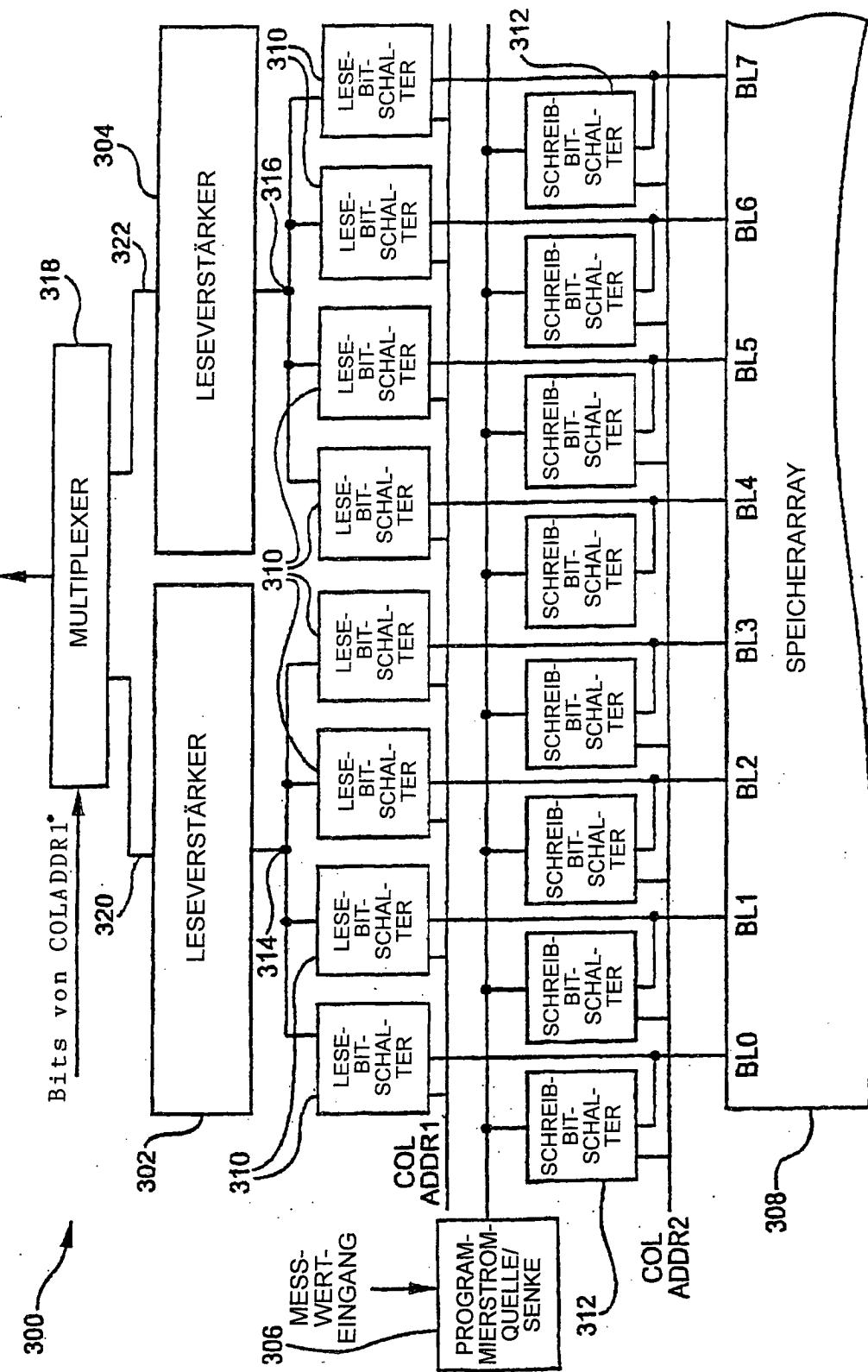

**[0016]** [Fig. 3](#) zeigt ein Blockdiagramm einer beispielhaften magnetischen Speicherschaltung zum Lesen und/oder Schreiben von Speicherzellen gemäß einem Aspekt der Erfindung.

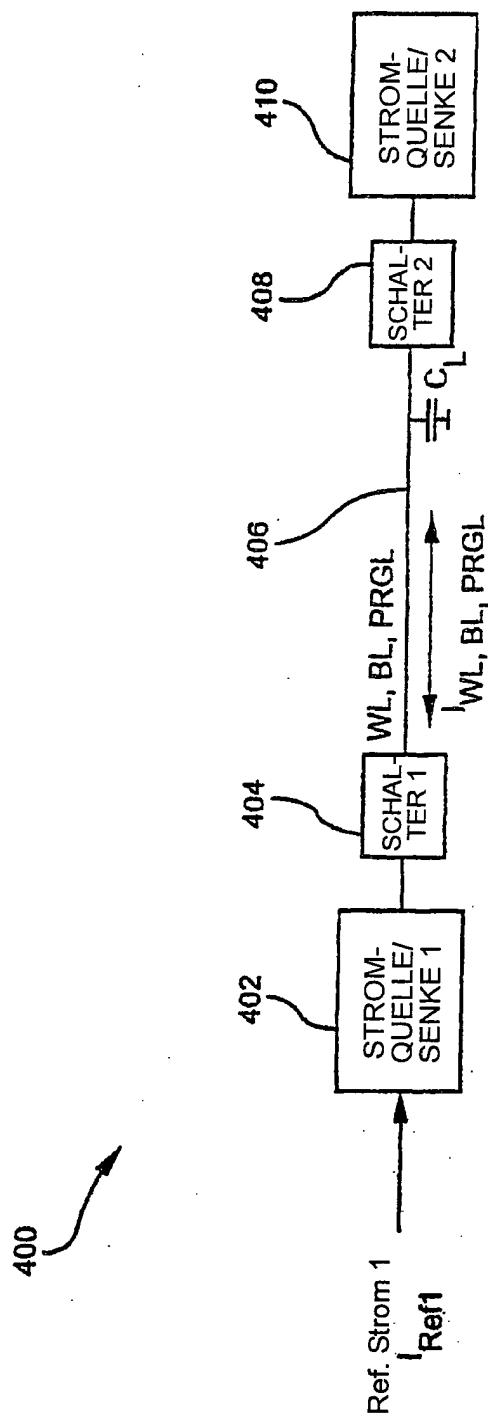

**[0017]** [Fig. 4](#) zeigt ein Blockdiagramm eines beispielhaften Programmierstrompfads.

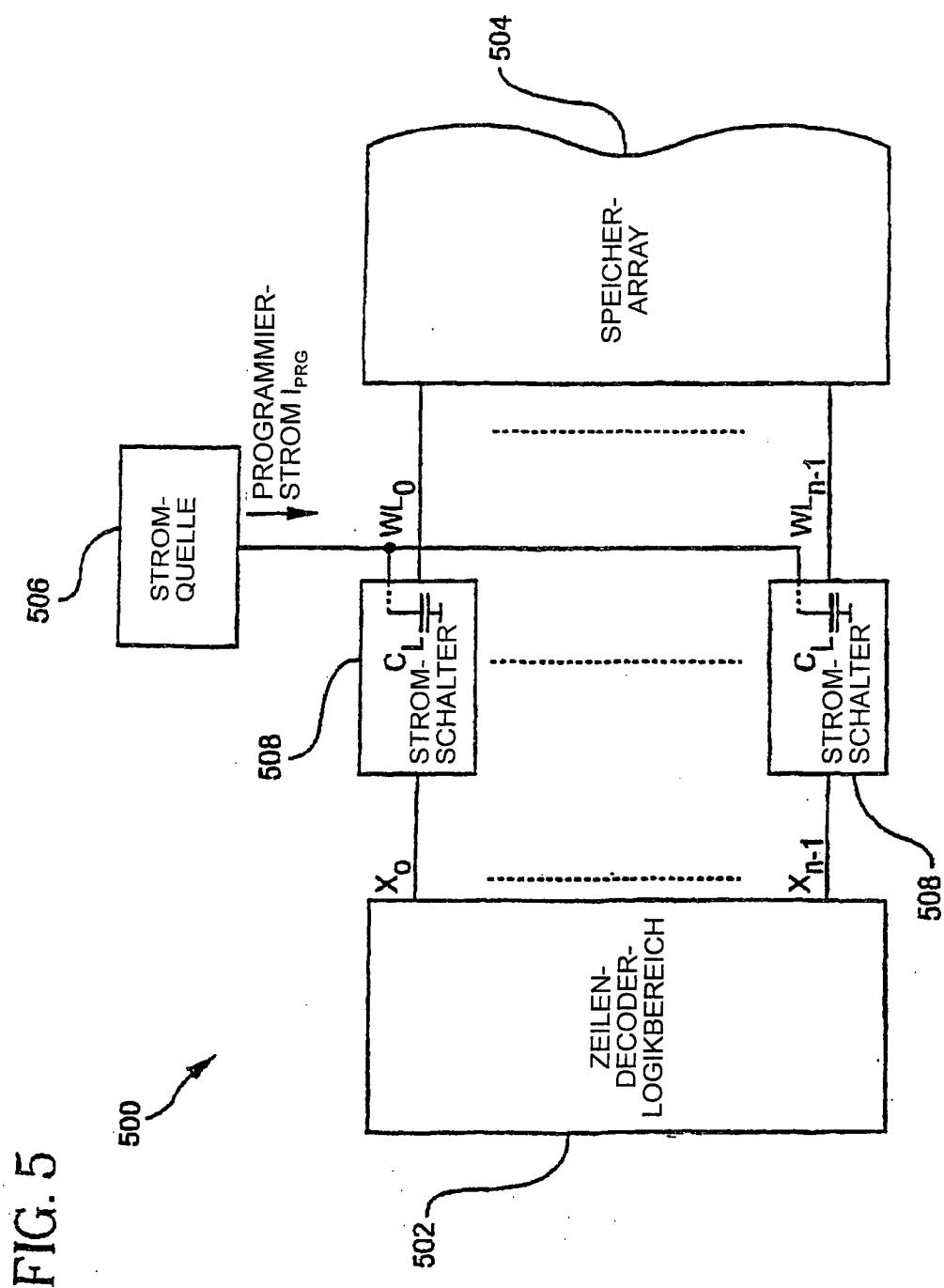

**[0018]** [Fig. 5](#) zeigt ein Blockdiagramm einer Pro-

grammierschaltung zum Steuern des Anlegens eines Programmierstroms an ausgewählte Speicherzellen eines magnetischen Speicherarrays.

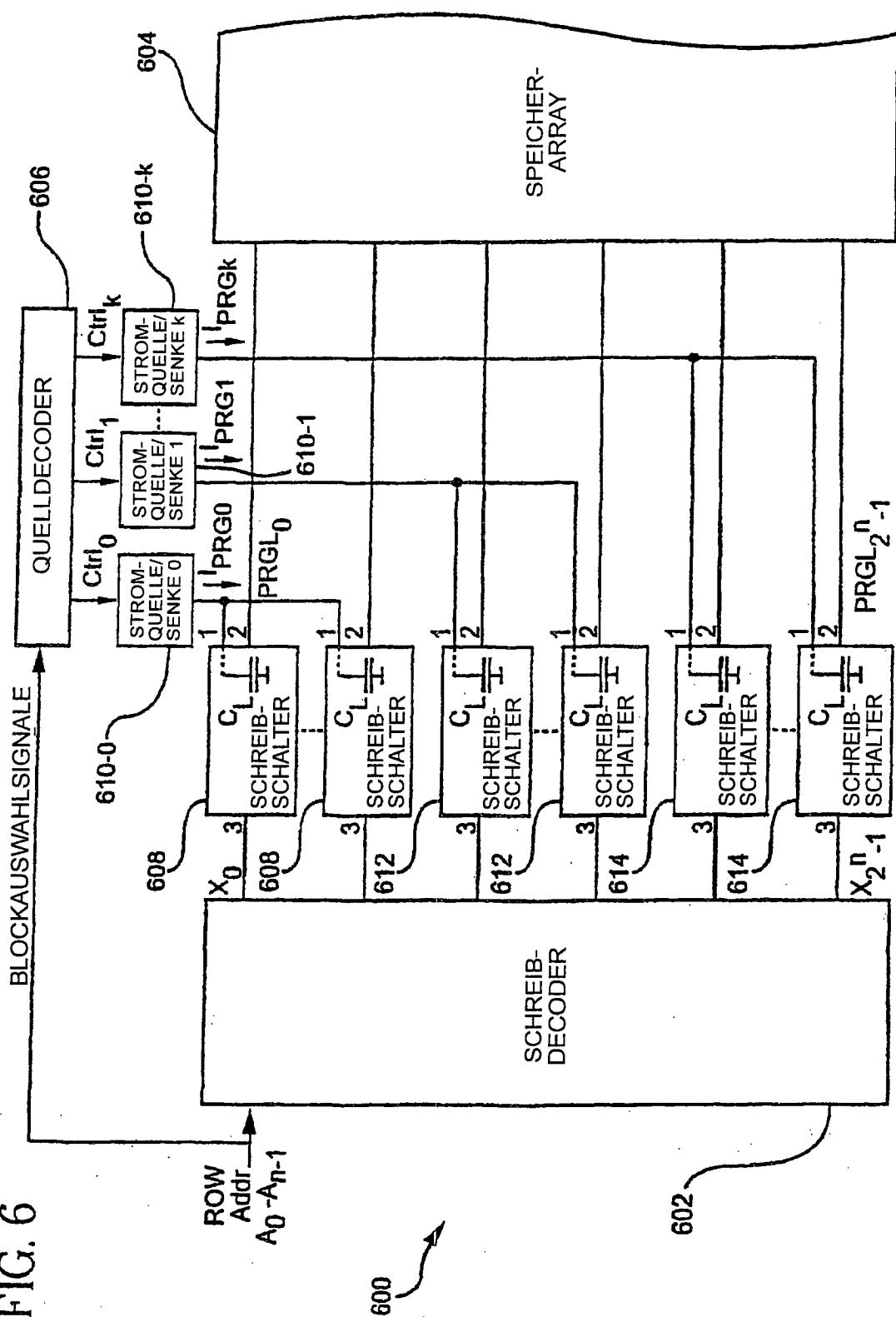

[0019] [Fig. 6](#) zeigt ein Blockdiagramm einer beispielhaften verbesserten Programmierschaltung gemäß einem Aspekt der Erfindung.

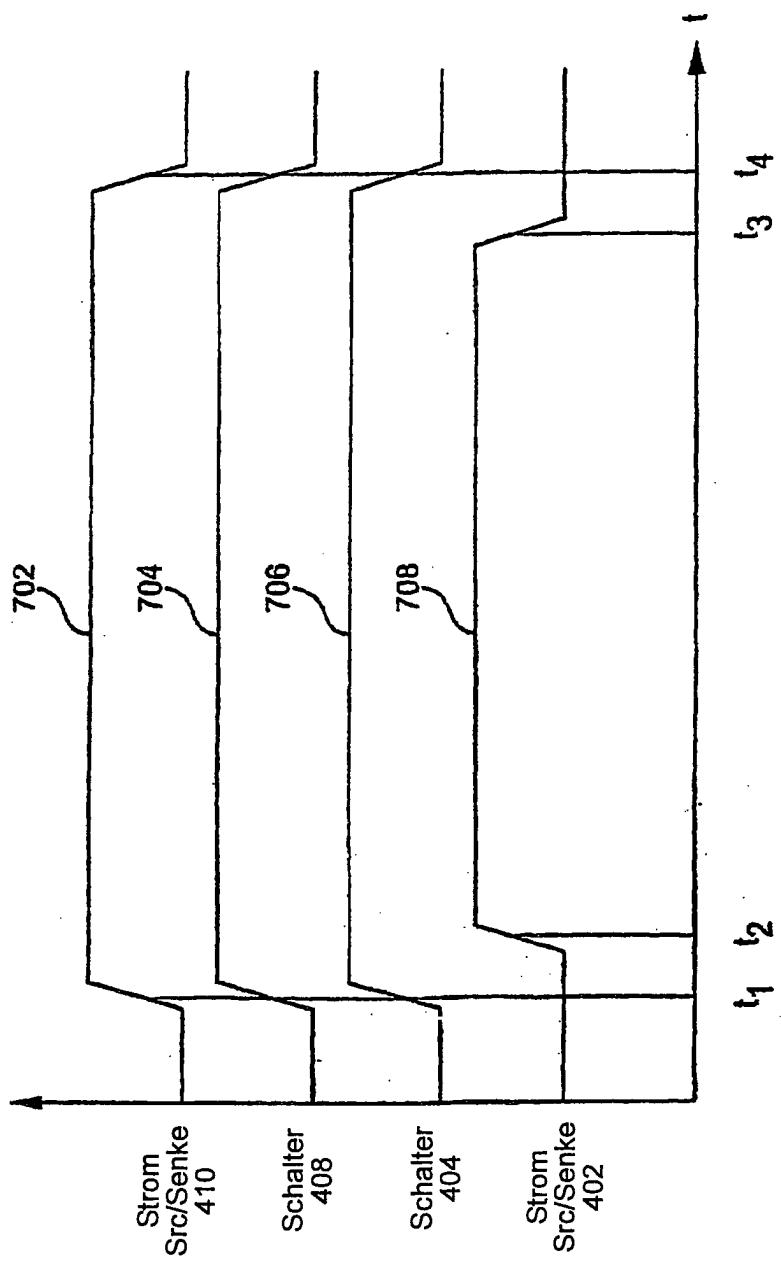

[0020] [Fig. 7](#) zeigt ein Zeitablaufdiagramm mit dem Zeitverlauf von Signalen zum Verbessern eines Schreibvorgangs einer magnetischen Speicherschaltung gemäß einem Aspekt der Erfindung.

Detaillierte Beschreibung bevorzugter Ausführungsformen

[0021] Die Erfindung wird hierin im Kontext eines beispielhaften magnetischen Speicherbauelements mit wahlfreiem Zugriff(MRAM)-Bauelement beschrieben. Es gilt jedoch zu berücksichtigen, dass diese Erfindung nicht auf diese oder eine weitere bestimmte magnetische Speicherschaltung oder Architektur beschränkt ist. Vielmehr ist die Erfindung allgemein auf Verfahren zum Reduzieren einer Lastkapazität im Lese- oder Schreibsignalpfad in einer magnetischen Speicherschaltung übertragbar. Obwohl darüber hinaus Ausführungsformen der Erfindung mit Bezug auf magnetische Tunnelübergangsbauelemente(MTJ)-Bauelemente beschrieben wurden, gilt zu berücksichtigen, dass die Erfindung keineswegs auf derartige Bauelemente beschränkt ist und dass weitere geeignete Bauelemente wie z. B. andere magneto-resistive Speicherelemente ebenso verwendet werden können, mit oder ohne Abänderungen der erfindungsgemäßen magnetischen Speicherarchitektur.

[0022] Wie einem Fachmann geläufig, werden „Wortleitungen“ allgemein als in einer Zeilen- oder horizontalen Richtung orientiert definiert, während „Bitleitungen“ allgemein als in einer Spalten- oder einer vertikalen Richtung orientiert definiert werden. Es ist jedoch zu berücksichtigen, dass die Verfahren der hierin beschriebenen Erfindung keineswegs auf diese oder eine bestimmte Ausrichtung von Wortleitungen und/oder Bitleitungen beschränkt sind.

[0023] [Fig. 3](#) zeigt eine beispielhafte magnetische Speicherschaltung **300**, auf die die Verfahren der Erfindung übertragen werden können. Die beispielhafte magnetische Speicherschaltung **300** weist ein Speicherarray **308** einschließlich einer Mehrzahl von Speicherzellen (nicht gezeigt) auf, die auf herkömmliche Weise konfiguriert sein können (z. B. als 1T1MTJ-Speicherarray), als auch eine Mehrzahl von Bitleitungen BL0, BL1, BL2, BL3, BL4, BL5, BL6, BL7, usw., die operativ mit den Speicherzellen verknüpft sind, um die Speicherzellen im Speicherzellenarray **308** selektiv anzusteuern. Die Anzahl verwendeter Bitleitungen wird wenigstens teilweise von

der Anzahl und der Anordnung von Speicherzellen im Speicherarray **308** abhängen. Diese Erfindung ist jedoch nicht auf die hierin verwendete Anzahl von Bitleitungen beschränkt.

[0024] Zum Aufbau einer magnetischen Speicherarchitektur hoher Geschwindigkeit ist es wünschenswert, die mit einem gegebenen Lese-(d. h. Abtast-)Signalpfad verknüpfte kapazitive Last soweit wie möglich zu reduzieren. Eine Möglichkeit dies zu erzielen liegt darin, wenigstens einen Teil des Lesesignalpfads vom Schreibsignalpfad zu trennen, wie weiter unten detailliert erläutert wird.

[0025] Der Schreibsignalpfad weist typischerweise eine hohe Lastkapazität auf, die mit diesem verknüpft ist und wenigstens teilweise auf das Vorhandensein der Schreib-Bit-Schalter **312**, welche mit dem Schreibsignalpfad verknüpft sind, zurückzuführen ist. Die Schreib-Bit-Schalter **312** sind auf geeignete Weise auszulegen, um einen großen Programmierstrom handhaben zu können (z. B. ungefähr 2 bis 6 Milliampere (mA)), der zum Schreiben der logischen Zustände in die jeweiligen Speicherzellen notwendig sein kann. Die Schreib-Bit-Schalter **312** können jeweils einen Transistor aufweisen, z. B. einen n-Typ Feldefekttransistor (NFET), der als Spannung-gesteuerter Schalter wirkt. Diese Erfindung berücksichtigt ebenso, dass weitere Schaltkreise (z. B. MUX) zur Umsetzung der Schreib-Bit-Schalter **312** verwendet werden können, was einem Fachmann verständlich erscheint.

[0026] Ein erster Anschluss (z. B. Drainanschluss des NFET) jeder der Schreib-Bit-Schalter **312** ist vorzugsweise mit einer Programmierstromquelle/senke **306** verbunden. Die Stromquelle/senke **306** umfasst vorzugsweise einen Ausgang zum Erzeugen des Programmierstroms, der zum Schreiben einer oder mehrerer ausgewählter Speicherzellen verwendet wird, als auch einen Messwerteingang (Messwerteingang), der die Richtung des Programmierstroms steuert. Die Stromquelle/senke **306** ist vorzugsweise entweder als Stromquelle zum Bereitstellen eines bestimmten Stroms konfigurierbar oder als Stromsenke zum Zurücknehmen des Programmierstroms. Wie vorhergehend erläutert wurde, ist es die Richtung des Programmierstroms, die den logischen Zustand, der in eine Speicherzelle geschrieben wird, ultimativ festlegt. Ein zweiter Anschluss (z. B. ein Sourceanschluss des NFET) jeder der Schreib-Bit-Schalter **312** ist vorzugsweise mit einer zugehörigen Bitleitung (z. B. BL0, BL1, BL2, usw.), welche mit dem Speicherarray **308** verknüpft ist, verbunden. Somit liegt in der ersten beispielhaften magnetischen Speicherschaltung **300** vorzugsweise ein zugehöriger Schreib-Bit-Schalter **312** für jede Bitleitung im Speicherarray **308** bereit.

[0027] Die Schreib-Bit-Schalter **312** in der beispiel-

haften magnetischen Speicherschaltung **300** können einen oder mehrere Steuereingänge zum selektiven Verbinden des Ausgangs der Programmierstromquelle/senke **306** mit einer vorgegebenen Bitleitung als Antwort auf ein oder mehrere bereitgestellte Steuersignale enthalten. Das Steuersignal kann beispielsweise eine teilweise oder vollständig decodierte Adresse (COL ADDR2) sein, wenn es einer Mehrzahl von Schreib-Bit-Schaltern **312** bereitgestellt wird, und kann zudem über einen Schaltkreis (nicht gezeigt) decodiert werden, wie z. B. einen in den Schreib-Bit-Schaltern **312** enthaltenen Decoder zum selektiven Aktivieren eines vorgegebenen Schreib-Bit-Schalters. Die COL ADDR2-Adresse umfasst vorzugsweise ein Schreibsignal oder weitere Signal(e), so dass wenigstens ein Teil der Schreib-Bit-Schalter **312** lediglich während eines Schreibvorgangs aktiv (d. h. eingeschaltet) ist. Wenn eine solche Decoderschaltung nicht in den Schreib-Bit-Schaltern **312** eingebaut ist, kann ein getrennter Decoder (nicht gezeigt), der extern zu den Schreib-Bit-Schaltern liegt, in der beispielhaften magnetischen Speicherschaltung **300** enthalten sein. Weitere Decodieranordnungen werden ebenso von der Erfindung berücksichtigt.

**[0028]** Gemäß einem Aspekt der Erfindung umfasst die beispielhafte magnetische Speicherschaltung **300** einen oder mehrere Leseverstärker **302, 304**, die in enger Nachbarschaft zu den zugehörigen auszulesenden Speicherzellen sind. Die auszulesenden Speicherzellen stellen wenigstens einen Teil der Speicherzellen im Speicherarray **308** dar. Die Leseverstärker **302, 304** sind vorzugsweise selektiv mit den Speicherzellen über eine Mehrzahl von Lese-Bit-Schaltern **310** verbunden. Die Lese-Bit-Schalter **310** in der beispielhaften magnetischen Speicherschaltung **300** sind von den Schreib-Bit-Schaltern **312** getrennt und wirken vorzugsweise auf dieselbe Weise wie die vorhergehend erläuterten Schreib-Bit-Schalter **312**. Da jedoch ein erheblich geringerer Strom zum Abtasten des logischen Zustands der Speicherzellen während eines Lesevorgangs verwendet wird (z. B. ungefähr 50 Mikroampere ( $\mu$ A)) kann jeder der Lese-Bit-Schalter **310** einen beträchtlich kleineren Transistor (z. B. NFET) aufweisen im Vergleich zu den in den Schreib-Bit-Schaltern **312** verwendeten Transistoren. Vorzugsweise sind die Transistoren in den Lese-Bit-Schaltern derart Art dimensioniert, dass diese wenigstens ungefähr viermal kleiner als die Transistoren in den Schreib-Bit-Schaltern sind. Die beispielhafte magnetische Speicherschaltung **300** erniedrigt somit in erheblichem Maß die Lastkapazität, die wenigstens teilweise auf die Drain- und/oder Sourcediffusionen, welche mit den Transistoren in den Lese-Bit-Schaltern, die im Leseignalpfad verbunden sind, zurückzuführen ist.

**[0029]** Wie die Schreib-Bit-Schalter **312** kann jeder der Lese-Bit-Schalter **310** einen ersten Anschluss

aufweisen, der mit einem der Leseverstärker **302, 304** an einem entsprechenden Eingangsknoten **314, 316** des Leseverstärkers verbunden ist, sowie einen zweiten Anschluss, der mit einer entsprechenden Bitleitung (BL0, BL1, usw.) in dem Speicherarray **308** verbunden ist. Die Lese-Bit-Schalter **310** können einen oder mehrere Steuereingänge zum selektiven Verbinden eines zugehörigen Leseverstärkers mit einer mit diesem Leseverstärker verknüpften zugehörigen Bitleitung als Antwort auf ein oder mehrere vorhandene Steuersignale umfassen. Das Steuersignal kann beispielsweise eine vollständig oder teilweise decodierte Adresse (COL ADDR1) aufweisen, die bei Bereitstellung für eine Mehrzahl von Lese-Bit-Schaltern **310** zudem von einem Schaltkreis (nicht gezeigt) decodiert sein kann, um einen vorgegebenen Schalter selektiv zu aktivieren, wobei der Schaltkreis in den Lese-Bit-Schaltern **310** enthalten sein kann. Diese COL ADDR1-Adresse umfasst vorzugsweise ein Lesesignal oder weitere Signal(e), so dass die Lese-Bit-Schalter **310** lediglich während eines Lesevorgangs aktiv (d. h. eingeschaltet) sind.

**[0030]** Wie vorhergehend in Verbindung mit dem Schreib-Bit-Schalter **312** erläutert wurde, kann im Falle, dass die Lese-Bit-Schalter **310** keine Decoderschaltung umfassen, ein Decoder (nicht gezeigt) außerhalb der Lese-Bit-Schalter **310** in der Speicherarchitektur **300** zum Decodieren der Adresse COL ADDR1 enthalten sein. Derselbe Decoder kann zur Erzeugung der Steuersignale zur Auswahl eines oder mehrerer der Schreib-Bit-Schalter **312** und Lese-Bit-Schalter **310** konfigurierbar sein.

**[0031]** Die beispielhafte magnetische Speicherschaltung **300** kann zudem einen Multiplexer **318** enthalten, um Daten von einem der Mehrzahl von Leseverstärkern **302, 304** auszuwählen. Der Multiplexer **318** weist vorzugsweise eine Mehrzahl von Dateneingängen **320, 322** auf, wenigstens einen Steuereingang und wenigstens einen Messwertausgang (Messwertausgang). Für  $2^n$ -Eingänge enthält der Multiplexer vorzugsweise  $n$ -Steuereingänge zum Empfangen eines  $n$ -Bit Steuersignals (Adresse), wobei  $n$  eine ganze Zahl größer als Null ist. Jeder der Dateneingänge **320, 322** ist mit einem Ausgang eines zugehörigen Leseverstärkers **302, 304** verbunden. Der Multiplexer **318** leitet Daten von einem der Mehrzahl von Eingängen als Antwort auf ein Steuersignal oder Steuersignale, die wenigstens einem der Steuereingänge zugeführt werden, weiter. Die Steuersignale können beispielsweise wenigstens einen Bereich der COL ADDR1-Adresse umfassen, der zur Auswahl eines oder mehrerer der Lese-Bit-Schalter **310** verwendet wird, wie vorhergehend beschrieben wurde.

**[0032]** Da die Leseverstärker **302, 304** vorzugsweise bei den zu lesenden Speicherzellen lokalisiert sind (d. h. in engerer Nachbarschaft), kann die Länge des

gesamten Lesepfads und die kumulative Anzahl von Schaltungen, die im Lesepfad verbunden sind und mit einer bestimmten Speicherzelle verknüpft sind, reduziert werden, wodurch die Lastkapazität weiter abnimmt. Die Abnahme in der Lastkapazität verbessert in vorteilhafter Weise die Geschwindigkeit des Lesevorgangs in der beispielhaften magnetischen Speicherschaltung 300. Darüber hinaus stellt die beispielhafte magnetische Speicherschaltung 300 eine symmetrischere Bitleitungsverdrahtungsanordnung bereit. Dies ist insbesondere dann von Vorteil, falls differenzielle Leseverstärker zum Einsatz kommen, da sonst ein Rauschen auf den Bitleitungen asymmetrisch auf die Bitleitungen koppeln könnte. Einige Vorteile einer symmetrischen Bitleitungsverdrahtung werden beispielsweise in US 6,269,040 von Reohr et al. diskutiert.

**[0033]** Wie vorhergehend erläutert, liegt ein wichtiger Aspekt der Erfindung in der Trennung des Lese-Signalpfads vom Schreibsignalpfad, welcher allgemein eine erheblich höhere zugehörige Lastkapazität aufweist. Das normalerweise übliche Verbinden der Leseverstärker über denselben Schalter wie die Programmierstromquelle erzeugt eine große kapazitive Last im Lesepfad und am Leseverstärkereingang, was den mit dem Lesevorgang verknüpften Abtastprozess verlangsamt. Stattdessen sind mehrere Leseverstärker 302, 304 mit den Bitleitungen über getrennte Lese-Bit-Schalter 310 verbunden, die derart dimensioniert sind, dass sie erheblich kleiner als die Schreib-Bit-Schalter 312 sind, welche mit der Programmierstromquelle/senke 306 verbunden sind, so dass, wie oben erläutert, jeder Lese-Bit-Schalter 310 lediglich einen Lesestrom (Abtaststrom) in der Größenordnung von ungefähr 50  $\mu$ A zu verarbeiten hat. Somit ist jeder Lesepfad eines vorgegebenen Leseverstärkers 302, 304 lediglich mit der Kapazität eines kleineren Lese-Bit-Schalters 310 und der von der ausgewählten Bitleitung beigetragenen Kapazität belastet.

**[0034]** Ein zusätzlicher Vorteil der beispielhaften Speicherschaltung 300 der Erfindung liegt darin, dass die Decodierung der Schreib-Bit-Schalter 312, welche mit der Programmierstromquelle/senke 306 verbunden sind, und der Lese-Bit-Schalter 310, welche mit den Leseverstärkern 302, 304 verbunden sind, unabhängig gesteuert werden kann. Folglich kann die Anzahl von Bitleitungen, die mit der Programmierstromquelle/senke 306 verbunden sind, verschieden sein von der Anzahl von Bitleitungen, die mit einem bestimmten Leseverstärker verbunden sind. Dies ermöglicht in vorteilhafter Weise eine Reduzierung der Anzahl von Stromquellen verglichen mit der Anzahl von Leseverstärkern. Zu Kalibrierungszwecken ist eine geringere Anzahl von Stromquellen wünschenswert, während eine größere Anzahl von Leseverstärkern in vorteilhafter Weise eine lokale Verstärkung ermöglicht, wodurch Signalrau-

schen abgeschwächt wird und Lesepfadverzögerungen minimiert werden.

**[0035]** Um die Nähe zu den Bitleitungen zu gewähren, können die Leseverstärker in der beispielhaften Speicherschaltung 300 unmittelbar auf einem Abschnitt einer bestimmten Anzahl von Bitleitungen platziert werden. Der hierin verwendete Ausdruck „Abschnitt“ bezieht sich auf eine Mehrzahl von Speicherzellen, die in einer bestimmten Richtung (z. B. einer Spalte) ausgerichtet sind. Das Anordnen der Leseverstärker auf diese Weise sichert im Wesentlichen gleiche Lesepfadlängen und kapazitive Lasten. Der Schreib-Bit-Schalter und/oder Leseverstärker kann an oder in der Nähe einer Grenze des Speicherarrays 308 platziert werden, abhängig von den Beschränkungen des Programmierstroms, welche vom Leitungswiderstand beeinflusst werden können, oder von der Lesezugriffsduer, welche von Rauschen, kapazitiven Lasten, usw. abhängen kann.

**[0036]** Um eine ausreichende Programmierausbeute mit Hilfe einer größeren Anzahl magnetischer Speicherzellen eines Speicherarrays zu erzielen, werden die zum Schreiben der logischen Zustände von Speicherzellen verwendeten Programmierströme vorzugsweise im Wesentlichen innerhalb eines gewünschten Strombereichs gehalten. Das Steuern des Programmierstroms innerhalb eines wohl definierten Strombereichs stellt sicher, dass lediglich ausgewählte Speicherzellen programmiert werden und dass alle weiteren nicht-ausgewählten Speicherzellen in dem Array im Wesentlichen ungestört bleiben. Auf diese Weise werden lediglich ausgewählte Speicherzellen im Array beschrieben und nicht-ausgewählte Speicherzellen behalten ihre logischen Zustände.

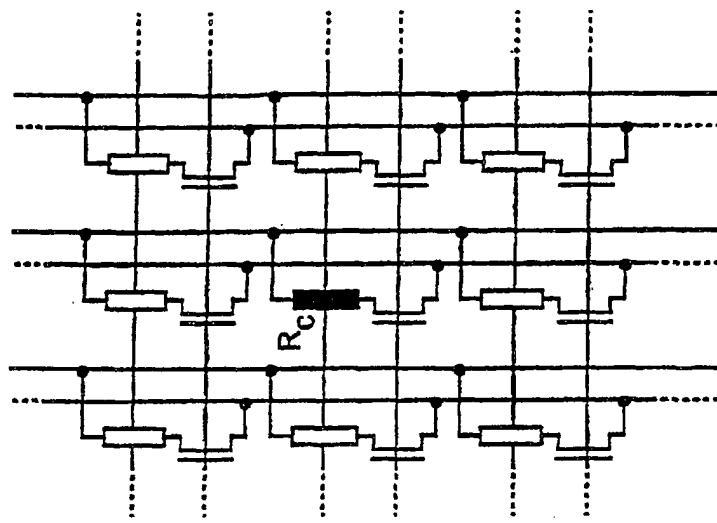

**[0037]** [Fig. 4](#) zeigt einen beispielhaften Programmierstrompfad 400 in einem MRAM-Bauelement. Wie der Abbildung entnommen werden kann, umfasst der beispielhafte Stromprogrammierpfad 400 eine erste Stromquelle/senke 402, die über einen ersten Schalter 404 mit einem ersten Ende eines Leiters 406 verbunden ist, der beispielsweise eine Wortleitung (WL), eine Bitleitung (BL) oder eine Programmierleitung (PRGL) im Speicherarray darstellen kann. Es gilt zu berücksichtigen, dass sich eine Programmierleitung auf einen beliebigen Leiter bezieht, der zum Schreiben des logischen Zustands einer magnetischen Speicherzelle verwendet wird, und somit kann eine Programmierleitung entweder eine Wortleitung oder eine Bitleitung sein. Ein zweites Ende des Leiters 406 kann mit einer zweiten Stromquelle/senke 410 über einen zweiten Schalter 408 verbunden sein. Die Stromquellen/senken 402, 410 sind vorzugsweise selektiv konfigurierbar, um entweder Strom für eine weitere Stromsenke bereitzustellen oder Strom von der weiteren Stromquelle zurückzunehmen.

**[0038]** Die Stromquelle/senke **402**, die mit einem ersten Ende des Leiters **406** verbunden ist, und die Stromquelle/senke **410**, die mit dem zweiten Ende des Leiters **406** verbunden ist, steuern vorzugsweise die Richtung und die Größe des Programmierstroms  $I_{WL}$ ,  $I_{BL}$ ,  $I_{PRGL}$ , der in der Wortleitung, Bitleitung oder Programmierleitung fließt. Diese bidirektionale Stromanordnung ist notwendig, um einen logischen „0“- oder einen logischen „1“-Zustand in eine ausgewählte Speicherzelle zu schreiben. Unidirektionale Konfigurationen, bei denen ein Ende des Leiters **406** auf einer vorgegebenen Spannung fixiert ist, die Masse sein kann, werden von der Erfindung ebenso berücksichtigt. Es gilt zu beachten, dass eine Stromquelle/senke von mehreren Schaltern gemeinsam verwendet werden kann.

**[0039]** [Fig. 5](#) zeigt eine Programmierschaltung **500** mit einem Zeilendecoder **502**, einer Mehrzahl von Stromschaltern **508**, die mit dem Zeilendecoder **502** verbunden sind, und einer Stromquelle **506**, die einen Programmierstrom  $I_{PRG}$  erzeugt. Der Zeilendecoder **502** kann zur Steuerung der Zufuhr des Programmierstroms  $I_{PRG}$  entlang einer der  $n$ -Wortleitungen  $WL_0$  bis  $WL_{n-1}$ , die mit einem Speicherarray **504** verknüpft sind, verwendet werden, wobei  $n$  eine ganze Zahl größer Eins ist. Wie vorhergehend dargelegt, sind die Wortleitungen allgemein so definiert, dass sie in einer Zeilen- oder horizontalen Richtung ausgerichtet sind, während Bitleitungen allgemein so definiert sind, dass sie entlang einer Spalten- oder vertikalen Richtung ausgerichtet sind.

**[0040]** Jeder Ausgang  $X_0$  bis  $X_{n-1}$  des Zeilendecoders **502** steuert einen zugehörigen unabhängigen Stromschalter **508** an. Ein erster Anschluss (Anschluss 1) jedes Stromschalters **508** ist mit einem Ausgang der Stromquelle **506** verbunden, ein zweiter Anschluss (Anschluss 2) jedes Stromschalters **508** ist mit einer zugehörigen Wortleitung ( $WL_0$  bis  $WL_{n-1}$ ) im Speicherarray **504** verbunden, und ein dritter Anschluss (Anschluss 3) jedes Stromschalters **508** ist mit einem zugehörigen Ausgang  $X_0$  bis  $X_{n-1}$  des Zeilendecoders **502** verbunden. Die Stromschalter **508** verbinden die Stromquelle **506** selektiv mit einer ausgewählten Wortleitung ( $WL_0$  bis  $WL_{n-1}$ ) des Speicherarrays **504** als Antwort auf ein Steuersignal, das vom Zeilendecoder **502** erzeugt wird. Der Zeilendecoder **502** stellt sicher, dass lediglich ein Stromschalter **508** zur selben Zeit eingeschaltet ist.

**[0041]** Ein Nachteil der Programmierschaltung **500** ist es, dass die Anstiegs- und Abfallszeiten des Programmierstrompulses sehr langsam sind, was hauptsächlich auf eine große kapazitive Last zurückzuführen ist, die am Ausgang der Stromquelle **506** vorliegt. Diese große Lastkapazität ist, wenigstens teilweise, auf eine Summe der Lastkapazitäten  $C_L$  zurückzuführen, welche von jedem der Stromschalter **508** beigetragen werden, die mit dem Ausgang der Stromquelle

**506** verbunden sind. Wie vorhergehend erläutert wurde, ist die Größe der Schalter **508** auf geeignete Weise festzulegen, um einen Programmierstrom von einigen Milliampere zu verarbeiten, und somit weisen diese Schalter **508** hiermit verknüpfte große Lastkapazitäten  $C_L$  auf. Diese Lastkapazitäten, die als große konzentrierte Kapazität am Ausgang der Programmierstromquelle **506** erscheinen, müssen von der Stromquelle geladen werden und ebenso von einer Stromsenke entladen werden, wodurch die Anstiegs- und Abfallszeiten des Stromprogrammierpulses erheblich ansteigen, so dass der Leistungsverbrauch ebenso zunimmt.

**[0042]** [Fig. 6](#) zeigt eine beispielhafte Programmierschaltung **600**, die eine verbesserte Anstiegs- und Abfallsdauerreaktion auf den Programmierstrompuls gemäß einem Aspekt der Erfindung zeigt. Die beispielhafte Programmierschaltung **600** umfasst ein Speicherarray **604**, das eine Mehrzahl von Speicherzellen (nicht gezeigt) enthalten kann, und einen Schreibdecoder **602** einschließlich  $n$ -Eingängen zum Empfangen einer  $n$ -Bit Zeilenadresse ( $A_0$  bis  $A_{n-1}$ ), und  $2^n$ -Ausgänge  $X_0$  bis  $X_{2^n-1}$ , wobei  $n$  eine ganze Zahl größer Eins ist. Der Schreibdecoder **602** erzeugt ein Steuersignal an einem der Ausgänge  $X_0$  bis  $X_{2^n-1}$  als Antwort auf die eingegebene Adresse  $A_0$  bis  $A_{n-1}$ . Decoder, die zur Verwendung mit der Erfindung geeignet sind, sind einem Fachmann bekannt. Die beispielhafte Programmierschaltung **600** umfasst eine Mehrzahl von Schreibschaltungen **608**, **612**, **614**, die in einer Bit- oder Wortrichtung angeordnet sind, oder eine Kombination von beiden, wobei jede Untergruppe wenigstens einen Schalter umfasst. Weitere Ausrichtungen werden ebenso von der Erfindung berücksichtigt (z. B. eine diagonale Ausrichtung). Jeder der Schreibschalter **608**, **612**, **614** weist vorzugsweise einen ersten Anschluss (Anschluss 1) auf, der mit einer Programmierstromquelle/senke verbunden ist, einen zweiten Anschluss (Anschluss 2), der mit einer zugehörigen Programmierleitung ( $PRGL_0$  bis  $PRGL_{2^n-1}$ ) im Speicherarray **604** verbunden ist, und wenigstens einen Steuereingang (Anschluss 3), der mit einem zugehörigen Ausgang des Schreibdecoders **602** verbunden ist, so dass die gesamte Anzahl von Schreibschaltern **608**, **612**, **614** vorzugsweise der Anzahl der Ausgänge des Decoders **602** entspricht.

**[0043]** Um gemäß einem Aspekt der Erfindung die kapazitive Last am Ausgang der in [Fig. 5](#) gezeigten Stromquelle **506** zu reduzieren und damit die Anstiegs- und Abfallszeiten des Programmierstrompulses zu erniedrigen, sind die Schreibschalter **608**, **612**, **614** entlang derselben Richtung (d. h. eines Abschnitts) vorzugsweise in zwei oder mehrere Untergruppen (d. h. Blöcke) unterteilt, wobei jede Untergruppe wenigstens einen Schreibschalter umfasst. Beispielsweise kann eine erste Untergruppe definiert werden, dass sie Schreibschalter **608** enthält, eine zweite Untergruppe kann Schreibschalter

**612** enthalten, und eine dritte Untergruppe kann Schreibschalter **614** enthalten.

**[0044]** In der beispielhaften Programmierschaltung **600** ist die Programmierstromquelle (**506** in [Fig. 5](#)), welche herkömmlich mit den Schreibschaltern in derselben Richtung verknüpft ist, in eine Mehrzahl von Stromquellen/senken **610-0** bis **610-k** unterteilt, wobei  $k$  eine ganze Zahl größer Null ist. Die Stromquellen/senken **610-0** bis **610-k** sind vorzugsweise im Wesentlichen auf einander abgestimmt und können auf dieselbe Weise wie die Programmierstromquelle **306** in [Fig. 3](#) ausgeführt sein. Darüber hinaus kann wenigstens ein Bereich der Stromquellen/senken **610-0** bis **610-k** in enger Nachbarschaft zu den zugehörigen Speicherzellen sein, wodurch die Länge des Programmierstrompfads reduziert wird und somit die hiermit verknüpfte Lastkapazität weiter abnimmt.

**[0045]** Jede Stromquelle/senke **610-0**, **610-1**, **610-k** ist vorzugsweise mit einer zugehörigen Untergruppe von Schreibschaltern **608**, **612**, **614** verbunden. In vorteilhafter Weise ist die Anzahl der Schreibschalter in jeder Gruppe dieselbe, wodurch Beiträge der Lastkapazität  $C_L$  der Schreibschalter unter den Stromquellen/senken gleichmäßig verteilt wird. Die beispielhafte Programmierschaltung **600** ist derart konfiguriert, um auf vorteilhafte Weise sicherzustellen, dass keine bestimmte Stromquelle/senke eine große Lastkapazität an ihrem Ausgang erfährt, da die gesamte Anzahl von Stromschaltern, die mit einer bestimmten Stromquelle/senke verbunden sind, über mehrere Stromquellen/senken verteilt werden kann, wie oben erläutert wurde. Somit steuert jede der Stromquellen/senken **610-0** bis **610-k** eine geringere Anzahl von Schreibschaltern an, wodurch eine kleinere Lastkapazität getrieben wird, als dies unter gewöhnlichen Umständen erforderlich wäre, falls lediglich eine einzelne Stromquelle/senke zum Einsatz kommt.

**[0046]** Da nicht alle Stromquellen/senken kontinuierlich aktiviert sein müssen, kann jede der Stromquellen/senken **610-0**, **610-1**, **610-k** in der beispielhaften Programmierschaltung **600** wenigstens einen Steuereingang zum selektiven Einschalten einer gewünschten Stromquelle/senke als Antwort auf ein bereitgestelltes Steuersignal  $Ctrl_0$ ,  $Ctrl_1$ ,  $Ctrl_k$  umfassen. Die Steuersignale  $Ctrl_0$ ,  $Ctrl_1$ ,  $Ctrl_k$  können von einem Quellddecoder **606** erzeugt werden, der in der beispielhaften Programmierschaltung **600** enthalten sein kann. Weitere Schaltungen zur selektiven Aktivierung einer bestimmten Stromquelle/senke können der Erfindung ebenso zugrunde gelegt werden. Der Quellddecoder **606** umfasst vorzugsweise wenigstens einen Eingang zum Empfangen wenigstens eines Teils der Zeilenadresse  $A_0$  bis  $A_{n-1}$  oder weiterer Blockauswahlsignale, sowie eine Mehrzahl von Ausgängen, die mit den Steuereingängen der Stromquellen/senken **610-0** bis **610-k** verbunden sind.

**[0047]** Die Programmierstrompfade, welche die Stromquellen/senken **610-0** bis **610-k**, die Schreibschalter **608**, **612**, **614** und die Programmierleitungen  $PRGL_0$  bis  $PRGL_{2^{n-1}}$ , in der beispielhaften Programmierschaltung **600** umfassen, können derart konfiguriert sein, dass sie mit dem Programmierstrompfad **400** übereinstimmen, der vorhergehend mit Bezug auf die [Fig. 4](#) beschrieben wurde. Somit wird, obwohl dies nicht dargestellt ist, jede der Programmierleitungen  $PRGL_0$  bis  $PRGL_{2^{n-1}}$ , vorzugsweise von einer zugehörigen Stromquelle/senke abgeschlossen, welche auf einfache Weise einen Kurzschluss zu einem bestimmten Potenzial (z. B. Masse) aufweisen kann. In einer bidirektionalen Stromanordnung können die Stromquellen/senken **610-0** bis **610-k** entweder selektiv als Stromquelle oder Stromsenke konfiguriert werden. In einer unidirektionalen Stromanordnung können die Stromquellen/senken **610-0**, **610-1**, **610-k** als Stromquellen konfiguriert werden, welche der zugehörigen Gruppe von Schreibschaltern bidirektionale Ströme  $I_{PRG0}$ ,  $I_{PRG1}$ ,  $I_{PRGk}$  bereitstellen, was einem Fachmann ersichtlich ist.

**[0048]** Während eines Schreibvorgangs aktiviert der Sourcedecoder **606** vorzugsweise lediglich die mit einem ausgewählten Schreibschalter verknüpfte Stromquelle/senke, (d. h. der ausgewählte Schreibschalter wird von dem Schreibdecoder **602** aktiviert (eingeschaltet)). Da die Programmierschaltung **600** nicht auf die Anzahl der Untergruppen von Schaltern beschränkt ist, und da die Größe einer bestimmten Untergruppe im Wesentlichen eine beliebige Anzahl von Schreibschaltern enthalten kann, lassen sich die Anstiegs- und Abfallszeiten des Programmierstrompulses auf gewünschte Weise steuern, indem die Anzahl der Schreibschalter in einer bestimmten Untergruppe und/oder die Anzahl von Untergruppen in der Programmierschaltung **600** variiert werden. Die mit einer bestimmten Untergruppe oder Untergruppen verknüpfte Anzahl von Schaltern kann gemäß einem weiteren Aspekt der Erfindung sowohl manuell als auch automatisch (z. B. über einen Controller oder eine weitere Steuerschaltung (nicht gezeigt)) oder auch über eine Kombination aus beiden variiert werden.

**[0049]** Um einen Schreibvorgang mit hoher Präzision zu erzielen, welcher so definiert werden kann, dass lediglich ausgewählte Speicherzellen im Speicherarray erfolgreich beschrieben werden, wird der Programmierstrom vorzugsweise präzise gesteuert, während der Programmierstrompuls an die ausgewählte Programmierleitung angelegt ist. Da die Programmierpulse vergleichsweise kurz sein können (z. B. kürzer als zehn Nanosekunden (ns)), hat die kapazitive Last  $C_L$  auf dem Programmierstrompfad (siehe [Fig. 4](#)) eine noch größere Auswirkung im Schreibbetrieb, nicht nur hinsichtlich der Geschwindigkeit, sondern auch hinsichtlich weiterer Faktoren (z. B. Ausbeute, Zuverlässigkeit, usw.).

**[0050]** In [Fig. 4](#) stellt die Kapazität  $C_L$  den konzentrierten Widerstand aller Kapazitäten im Programmierstrompfad von der Stromquelle zur Stromsenke dar, einschließlich der Kapazitäten der beiden Schalter **404**, **408** und des Leiters **406**. Schwankungen im Pegel der Programmierstrompulse wie z. B. Stromerhöhungen können den logischen Zustand der nicht-ausgewählten Speicherzellen im Speicherarray auf unerwünschte Weise stören, wodurch die Ausbeute und Zuverlässigkeit abnimmt. Derartige Schwankungen im Pegel des Programmierstrompulses können insbesondere dann auftreten, falls die Kapazität  $C_L$  auf Spannungen aufgeladen wird, die der positiven Versorgungsspannung entsprechen oder nahe bei dieser sind, z. B. bei VDD, und die Kapazität plötzlich entladen wird, z. B. durch die Aktivierung der großen Stromschalter **404**, **408**.

**[0051]** Um die Programmierstromerhöhungen (Programmierstromspikes) zu reduzieren, werden die Schalter **404**, **408** unter Verwendung der beispielhaften Steuersignale, die im beispielhaften Zeitablaufdiagramm von [Fig. 7](#) gezeigt sind, vorzugsweise eingeschaltet und/oder ausgeschaltet. In [Fig. 7](#) werden die beispielhaften Steuersignale **702**, **704**, **706** und **708** vorzugsweise zur Aktivierung und/oder Deaktivierung der Stromquelle/senke **410**, des zweiten Schalters **408**, des ersten Schalters **404** und der Stromquelle/senke **402** verwendet, wie in [Fig. 4](#) gezeigt ist. Es gilt zu berücksichtigen, dass weitere Steuersignale gemäß den hierin beschriebenen Verfahren der Erfindung verwendet werden können. Es wird angenommen, dass der Programmierstrom (z. B.  $I_{PRGL}$ ) von der Stromquelle/senke **402**, die als gesteuerte Stromquelle konfiguriert werden kann, durch den Leiter **406** und in die Stromquelle/senke **410** fließt, wobei Letztere als Stromsenke konfiguriert werden kann (z. B. als Kurzschluss nach Masse).

**[0052]** Beispielweise sind lediglich in einem ersten Schritt die Stromquelle/senke **410**, der zweite Schalter **408** und der erste Schalter **404** zur Zeit  $t_1$  aktiviert. Nachfolgend wird die Stromquelle/senke **402** zur Zeit  $t_2$  aktiviert, wobei  $t_2$  größer ist als  $t_1$ . Die Stromquelle/senke **402** lädt im Wesentlichen den Programmierstrompfad, der erste und zweite Schalter **404**, **408** und den Leiter **406** umfasst, und stellt einen exponentiell ansteigenden Programmierstrom bereit, bis ein Ruhestrom nach  $t_2$  erreicht ist. Die Größe der vom Programmierstrompfad zur Aufladung bis zum Ruhezustand benötigten Zeit wird von Eigenschaften abhängen, die mit dem Programmierstrompfad zusammenhängen, wie z. B. jedoch nicht hierauf beschränkt, einer verteilten Kapazität, Widerstand, usw. Zur Zeit  $t_3$ , wobei  $t_3$  größer als  $t_2$  ist, wird die Stromquelle/senke **402** deaktiviert. In dem Programmierstrompfad gespeicherte Ladung wird exponentiell über die Stromquelle/senke **410** entladen, welche verbunden bleibt. Nachdem der Programmierstrompfad im Wesentlichen entladen wurde, können der

erste Schalter **404**, der zweite Schalter **408** und die Stromquelle/senke **410** zur Zeit  $t_4$  deaktiviert werden, wobei  $t_4$  größer ist als  $t_3$ . Auf diese Weise können Stromerhöhungen, die mit dem Schalten der ersten und zweiten Schalter **404**, **408** verknüpft sind, im Wesentlichen vermieden werden.

**[0053]** Wenigstens ein Teil der magnetischen Speicherschaltung und/oder verbesserten Programmierschaltung der Erfindung kann in einer Halbleitervorrichtung umgesetzt werden, die eine oder mehrere derartige magnetische Speicher und/oder Programmierschaltungen enthält. Die hierin beschriebenen Verfahren der Erfindung können entweder einzeln oder in Kombination verwendet werden, um Verbesserungen gegenüber herkömmlichen magnetischen Speicherarchitekturen zu erzielen. Beispielsweise kann die in [Fig. 6](#) gezeigte beispielhafte Programmierschaltung anstatt der Schreibschaltung in [Fig. 3](#) verwendet werden, einschließlich der Bitleitungsprogrammierstromquelle/senke **306** und den Schreib-Bit-Schaltern **312**, um die mit dem Schreibpfad verknüpfte Lastkapazität zu reduzieren. Um eine Verwirrung hinsichtlich einer Mehrzahl von Stromquellen zu vermeiden, wird im Stand der Technik eine Stromquelle für jeden Messwerteingang in der Bitleitungsrichtung benötigt. Im Gegensatz hierzu benötigt die Erfindung in einer Ausführungsform eine Mehrzahl von Stromquellen/senken für jeden Messwerteingang in der Bitleitungsrichtung.

**[0054]** Obwohl beispielhafte Ausführungsformen der Erfindung mit Bezug auf die begleitenden Abbildungen erläutert werden, gilt zu berücksichtigen, dass die Erfindung keineswegs auf diese bestimmten Ausführungsformen beschränkt ist und dass verschiedene Abänderungen und Modifikationen von einem Fachmann vorgenommen werden können, ohne vom Schutzbereich der beigefügten Patentansprüche abzuweichen.

## Patentansprüche

1. Programmierschaltung zur Verwendung in einem magnetischen Speicherzellenarray (**604**) mit einer Mehrzahl von Speicherzellen und einer Mehrzahl von Programmierleitungen, die mit den Speicherzellen zur selektiven Auswahl einer oder mehrerer der Speicherzellen verbunden sind, wobei die Programmierschaltung aufweist:

- eine Mehrzahl erster Schalter (**608**, **612**, **614**), wobei jeder der ersten Schalter mit einer zugehörigen Programmierleitung verbunden ist;

- gekennzeichnet durch

- eine Mehrzahl von Stromquellen/senken (**610**), die jeweils mit einer Untergruppe eines oder mehrerer erster Schalter übereinstimmender Dimensionierung verbunden sind und wenigstens als eines der Elemente Stromquelle zum Erzeugen eines Programmierstroms zum Schreiben eines logischen Zustands

in eine oder mehrere Speicherzellen, und Stromsenke zum Zurücknehmen des Programmierstroms konfigurierbar sind, und einen ersten Decoder (602) mit wenigstens einem Steuereingang zum Empfangen eines ersten Steuersignals und einer Mehrzahl von Ausgängen, von denen jeder mit einem zugehörigen ersten Schalter (608, 612, 614) verbunden ist, wobei der erste Decoder (602) als Antwort auf das erste Steuersignal zur Auswahl eines der ersten Schalter (608, 612, 614) konfigurierbar ist; wobei eine Gesamtlastkapazität, die mit der Mehrzahl der ersten Schalter (608, 612, 614) verknüpft ist, unter der Mehrzahl von Stromquellen/senken (610) verteilt ist, wodurch eine Lastkapazität wenigstens einer der Stromquellen/senken (610) reduziert wird.

2. Programmierschaltung nach Anspruch 1, zusätzlich umfassend einen zweiten Decoder (606) mit wenigstens einem Steuereingang zum Empfangen eines zweiten Steuersignals, und einer Mehrzahl von Ausgängen, wobei jeder der Ausgänge mit einer zugehörigen Stromquelle/senke (610) verbunden ist, und der zweite Decoder (606) als Antwort auf das zweite Steuersignal bezüglich wenigstens einer der Funktionen selektives Einschalten und Ausschalten einer oder mehrerer der Stromquellen/senken (610) konfigurierbar ist.

3. Programmierschaltung nach Anspruch 1, wobei das zweite Steuersignal wenigstens einen Teil des ersten Steuersignals umfasst.

4. Programmierschaltung nach Anspruch 1, wobei alle der Stromquellen/senken (610) im Wesentlichen aufeinander abgestimmt sind.

5. Programmierschaltung nach Anspruch 1, wobei die Mehrzahl erster Schalter (608, 612, 614) im Wesentlichen gleichmäßig unter der Mehrzahl von Stromquellen/senken (610) aufgeteilt sind.

6. Programmierschaltung nach Anspruch 1, zusätzlich umfassend: wenigstens einen Leseverstärker (302, 304); und eine Mehrzahl zweiter Schalter (310), wobei jeder der zweiten Schalter einen ersten Anschluss aufweist, der mit einem Eingang des wenigstens einen Leseverstärkers (302, 304) verbunden ist, einen zweiten Anschluss, der mit einer zugehörigen Programmierleitung (BL0-BL7) verbunden ist, und wenigstens einen Steuereingang zum Empfangen eines zweiten Steuersignals (COL ADDR 1), wobei jeder der zweiten Schalter als Antwort auf das zweite Steuersignal die zugehörige Programmierleitung mit dem Eingang des wenigstens einen Leseverstärkers verbindet.

7. Programmierschaltung nach Anspruch 6, wobei: das zweite Steuersignal (COL ADDR 1) eine Adresse

aufweist; und wenigstens einer der zweiten Schalter (310) eine mit dem Steuereingang verbundene Decodierschaltung aufweist, die zum Decodieren der Adresse und zum selektiven Verbinden der zugehörigen Programmierleitung mit dem Eingang des wenigstens einen Leseverstärkers konfigurierbar ist.

8. Magnetische Speicherschaltung (300), umfassend: eine Mehrzahl von Speicherzellen; eine Mehrzahl von Bitleitungen (BLi), die mit den Speicherzellen zur selektiven Auswahl einer oder mehrerer der Speicherzellen verbunden sind; und eine Programmierschaltung nach Patentanspruch 1, wobei der Decoder wenigstens eine Bitleitungsprogrammierschaltung (306) aufweist, die wenigstens als eines der Elemente Stromquelle zum Erzeugen eines Programmierstroms zum Schreiben eines logischen Zustandes wenigstens einer Speicherzelle und Stromsenke zum Rücknehmen des Programmierstroms konfigurierbar ist; die Mehrzahl von Schaltern eine erste Gruppe von Schaltern (312) aufweist, die wenigstens während eines Lesevorgangs der Speicherzellen ausgeschaltet ist und wenigstens ein Teil der ersten Gruppe von Schaltern während eines Schreibvorgangs der Speicherzellen selektiv eingeschaltet ist, wobei jeder Schalter der ersten Gruppe von Schaltern (312) sich dazu eignet, die wenigstens eine Bitleitungsprogrammierschaltung (306) als Antwort auf ein erstes Steuersignal mit einer zugehörigen Bitleitung zu verbinden, und wobei eine zweite Gruppe von Schaltern (310) wenigstens während eines Schreibvorgangs der Speicherzellen ausgeschaltet ist und wenigstens ein Teil der zweiten Gruppe von Schaltern (310) während eines Lesevorgangs der Speicherzellen selektiv eingeschaltet ist, wobei jeder Schalter der zweiten Gruppe von Schaltern (310) sich dazu eignet, den wenigstens einen Leseverstärker (302, 304) als Antwort auf ein zweites Steuersignal mit einer zugehörigen Bitleitung zu verbinden.

9. Schaltung nach Anspruch 8, wobei jede der ersten und zweiten Gruppe von Schaltern (310, 312) Feldeffekttransistoren (FET) aufweist.

10. Schaltung nach Anspruch 9, wobei der FET in jeder zweiten Gruppe von Schaltern (310) derart dimensioniert ist, dass dieser wenigstens viermal kleiner ist als der FET in jeder der ersten Gruppe von Schaltern (312).

11. Schaltung nach Anspruch 1, zusätzlich umfassend: eine Mehrzahl von Wortleitungen (WL), die mit den Speicherzellen zur selektiven Auswahl einer oder mehrerer der Speicherzellen verbunden sind, wobei: jeder der ersten Schalter (312) einen mit einer zuge-

hörigen Bitleitung verbundenen ersten Anschluss aufweist, einen mit der wenigstens einen Programmierstromquelle/senke verbundenen zweiten Anschluss, und wenigstens einen Steuereingang zum Empfangen eines ersten Steuersignals, wobei jeder der ersten Schalter die zugehörige Bitleitung als Antwort auf das erste Steuersignal mit der wenigstens einen Programmierstromquelle/senke verbindet, und jeder der zweiten Schalter (310) einen ersten Anschluss aufweist, der mit einem Eingang des wenigstens einen Leseverstärkers (302, 304) verbunden ist, einen zweiten Anschluss, der mit einer zugehörigen Bitleitung verbunden ist, und wenigstens einen Steuereingang zum Empfangen eines zweiten Steuersignals, wobei jeder der zweiten Schalter (310) die zugehörige Bitleitung als Antwort auf das zweite Steuersignal mit dem Eingang des wenigstens einen Leseverstärkers (302, 304) verbindet.

12. Schaltung nach Anspruch 11, wobei das erste Steuersignal eine Adresse umfasst; und jeder Schalter von wenigstens einem Teil der Mehrzahl erster Schalter (312) eine Decodierschaltung aufweist, die mit dem Steuereingang verbunden ist, wobei die Decodierschaltung zum Decodieren der Adresse und zum selektiven Verbinden der zugehörigen Bitleitung mit dem Ausgang der wenigstens einen Programmierstromquelle/senke konfigurierbar ist.

13. Schaltung nach Anspruch 11, wobei das zweite Steuersignal eine Adresse aufweist; und jeder Schalter von wenigstens einem Teil der Mehrzahl zweiter Schalter (310) eine Decodierschaltung aufweist, die mit dem Steuereingang verbunden ist, wobei die Decodierschaltung zum Decodieren der Adresse und zum selektiven Verbinden der zugehörigen Bitleitung mit dem Ausgang des wenigstens einen Leseverstärkers konfigurierbar ist.

14. Schaltung nach Anspruch 11, wobei: die Mehrzahl erster Schalter (312) als Mehrzahl von Untergruppen übereinstimmender Dimensionierung angeordnet ist und jede Untergruppe wenigstens einen Schalter umfasst; und die wenigstens eine Programmierstromquelle/senke eine Mehrzahl von Stromsenken/quellen umfasst und jede der Stromquellen/senken mit einer zugehörigen Untergruppe verbunden ist und einem entsprechenden Messwerteingang zugeordnet ist.

15. Schaltung nach Anspruch 14, zusätzlich umfassend einen Decoder mit wenigstens einem Steuereingang zum Empfangen eines dritten Steuersignals, sowie eine Mehrzahl von Ausgängen, wobei jeder der Ausgänge mit einem Steuereingang einer zugehörigen Stromquelle verbunden ist und der Decoder als Antwort auf das Steuersignal zur Auswahl einer der Stromquellen konfigurierbar ist.

16. Schaltung nach Anspruch 14, wobei wenigstens ein Teil der Mehrzahl von Stromquellen/senken in enger Nachbarschaft zu den zugehörigen Speicherzellen angeordnet ist.

17. Schaltung nach Anspruch 11, wobei jede Speicherzelle von wenigstens einem Teil der Mehrzahl von Speicherzellen ein magnetisches Tunnelübergangselement (MTJ) umfasst.

18. Schaltung nach Anspruch 11, zusätzlich umfassend: wenigstens einen zweiten Leseverstärker; und einen Multiplexer (318) einschließlich wenigstens eines Steuereingangs zum Empfangen eines dritten Steuersignals, eines Ausgangs und einer Mehrzahl von Dateneingängen, wobei jeder der Dateneingänge mit einem Ausgang eines zugehörigen Leseverstärkers verbunden ist, und wobei der Multiplexer als Antwort auf das dritte Steuersignal zur Auswahl einer der Leseverstärker konfigurierbar ist.

Es folgen 7 Blatt Zeichnungen

FIG. 1 STAND DER TECHNIK

FIG. 2a STAND DER TECHNIK

FIG. 2b STAND DER TECHNIK

FIG. 3

FIG. 4

FIG. 6

FIG. 7