(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 974 326**

(51) Int. Cl.:

**H04L 1/00** (2006.01)

**H04H 20/16** (2008.01)

**H04H 20/18** (2008.01)

**H04L 1/08** (2006.01)

**H04L 5/00** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

- (86) Fecha de presentación y número de la solicitud internacional: **24.01.2018 PCT/CN2018/073951**

(87) Fecha y número de publicación internacional: **02.08.2018 WO18137641**

(96) Fecha de presentación y número de la solicitud europea: **24.01.2018 E 18745334 (5)**

(97) Fecha y número de publicación de la concesión europea: **21.02.2024 EP 3574595**

---

(54) Título: **Codificación y decodificación de canales de difusión**

(30) Prioridad:

**26.01.2017 WO PCT/CN2017/072721**

(45) Fecha de publicación y mención en BOPI de la traducción de la patente:

**26.06.2024**

(73) Titular/es:

**QUALCOMM INCORPORATED (100.0%)

5775 Morehouse Drive

San Diego, CA 92121-1714, US**

(72) Inventor/es:

**WEI, CHAO;

XU, CHANGLONG;

HOU, JILEI y

LI, JIAN**

(74) Agente/Representante:

**ISERN JARA, Jorge**

**ES 2 974 326 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Codificación y decodificación de canales de difusión

5 Antecedentes de la invención

Lo siguiente se refiere, en general, a la comunicación inalámbrica y más específicamente a la codificación y decodificación de canales de difusión.

10 Los sistemas de comunicación inalámbricas se implementan ampliamente para proporcionar varios tipos de contenidos de comunicación tales como voz, video, paquetes de datos, mensajería, difusión y así sucesivamente. Estos sistemas pueden ser sistemas de acceso múltiple capaces de admitir la comunicación con múltiples usuarios al compartir los recursos disponibles del sistema (por ejemplo, tiempo, frecuencia y potencia). Ejemplos de tales sistemas de acceso múltiple incluyen sistemas de acceso múltiple por división de código (CDMA), sistemas de

15 acceso múltiple por división de tiempo (TDMA), sistemas de acceso múltiple por división de frecuencia (FDMA) y sistemas de acceso múltiple por división de frecuencia ortogonal (OFDMA), (por ejemplo, un sistema de evolución a largo plazo (LTE) o un sistema de nueva radio (NR)).

20 Un sistema de comunicación inalámbrica de acceso múltiple puede incluir un número de estaciones base o nodos de red de acceso, cada uno de las cuales admite simultáneamente la comunicación de múltiples dispositivos de comunicación, conocidos de cualquier otra manera como equipo de usuario (UE). Las tecnologías inalámbricas de acceso múltiple se han adoptado en varios estándares de telecomunicaciones para proporcionar un protocolo común que permita a distintos dispositivos inalámbricos comunicarse a nivel municipal, nacional, regional e incluso mundial. Un ejemplo de estándar de telecomunicaciones es LTE. La LTE se diseña para mejorar la eficiencia espectral, reducir costos, mejorar los servicios, hacer uso de nuevo espectro e integrarse mejor con otros estándares abiertos. La LTE puede usar OFDMA en el enlace descendente (DL), acceso múltiple por división de frecuencia de portadora única (SC-FDMA) en el enlace ascendente (UL) y tecnología de antenas de múltiple entrada múltiple salida (MIMO).

25 30 Antes de intercambiar datos en el sistema de comunicación inalámbrica, un UE puede participar en un procedimiento de adquisición de células (por ejemplo, para determinar información relevante sobre la estación base o el nodo de la red de acceso, tal como la temporización de los símbolos, el formato del canal de control, el ancho de banda del sistema, etc.). El procedimiento de adquisición de células puede incluir la transmisión de un bloque de señal de sincronización (SS), que puede referirse a una combinación de señales de sincronización y un bloque de información maestra (MIB). Algunos procedimientos de adquisición de células pueden usar códigos de aleatorización para la transmisión del MIB para mitigar la interferencia y transmitir implícitamente información de temporización. Un UE puede decodificar a ciegas el MIB aleatorizado para determinar la información de adquisición de la célula. Pero la decodificación ciega puede ser inviable en ciertos escenarios (por ejemplo, puede introducir una latencia intolerable, consumir energía, etc.). Es posible que se deseen técnicas mejoradas para la codificación y decodificación de canales de difusión.

35 40 45 El borrador 3GPP R1-1700837 de Qualcomm Incorporated, reunión Ad-Hoc 3GPP TSG-RAN WGI NR, Spokane, Washington, Estados Unidos, del 16 al 20 de enero de 2017, se refiere a la "codificación de canal PBCH". Propone que un diseño adecuado debería permitir a un UE combinar, de manera factible, un NR-PBCH y un índice de bloque de SS que se transmite en diferentes bloques de SS. Considera que la clave para ello es el uso de códigos de canal que tengan propiedades cíclicas.

50 55 El borrador 3GPP R1-1612034 de Qualcomm Incorporated, reunión #87 de 3GPP TSG RAN WGI, Reno, Nevada, Estados Unidos, del 14 al 18 de noviembre de 2016, se refiere al "Transmisión del índice de símbolos durante la sincronización multihaz". De acuerdo con este borrador, no es necesario introducir una nueva señal dedicada para transmitir un índice de bloque de SS. Propone que un diseño adecuado debería permitir a un UE combinar, de manera factible, un NR-PBCH que se transmite en diferentes bloques de SS. Propone además que se indique un índice de bloque de SS en NR-PBCH a través de un número de versión de redundancia, y que las versiones de redundancia se creen mediante desplazamientos circulares.

60 65 El borrador 3GPP R1-1700788 de Qualcomm Incorporated, reunión Ad-Hoc 3GPP TSG-RAN WGI NR, Spokane, Washington, Estados Unidos, del 16 al 20 de enero de 2017, se refiere a las "Consideraciones de diseño del PBCH". Entre otras cosas, propone que en un bloque de SS que contenga el PBCH, se multiplexen en el tiempo señales de sincronización y dos símbolos del PBCH idénticos.

60 Sumario

La invención se define por las reivindicaciones independientes. Las realizaciones preferidas de la invención se definen por las reivindicaciones dependientes. Aunque se divultan varias realizaciones y/o ejemplos a lo largo de esta descripción, el objeto para el que se busca protección se limita a tales ejemplos y/o realizaciones que se abarcan por el ámbito de las reivindicaciones adjuntas. Las realizaciones y/o ejemplos descritos en la presente memoria que no entran en el ámbito de las reivindicaciones adjuntas deben considerarse útiles para comprender la

invención. Las técnicas descritas se refieren a procedimientos, sistemas, dispositivos o aparatos que admiten la codificación y decodificación de canales de difusión. Generalmente, las técnicas descritas proporcionan la codificación conjunta de una carga útil que comprende un conjunto de bits de información del canal físico de difusión (PBCH) con un conjunto de bits de información representativos de un índice de bloque de señal de sincronización (SS). Los conjuntos de información codificados conjuntamente pueden transmitirse en un vector de salida. Un dispositivo de decodificación puede recibir la transmisión y, en algunos casos, usar combinación suave para facilitar la decodificación de la carga útil del PBCH o el índice de bloque de SS, o ambos.

5 Breve descripción de las figuras

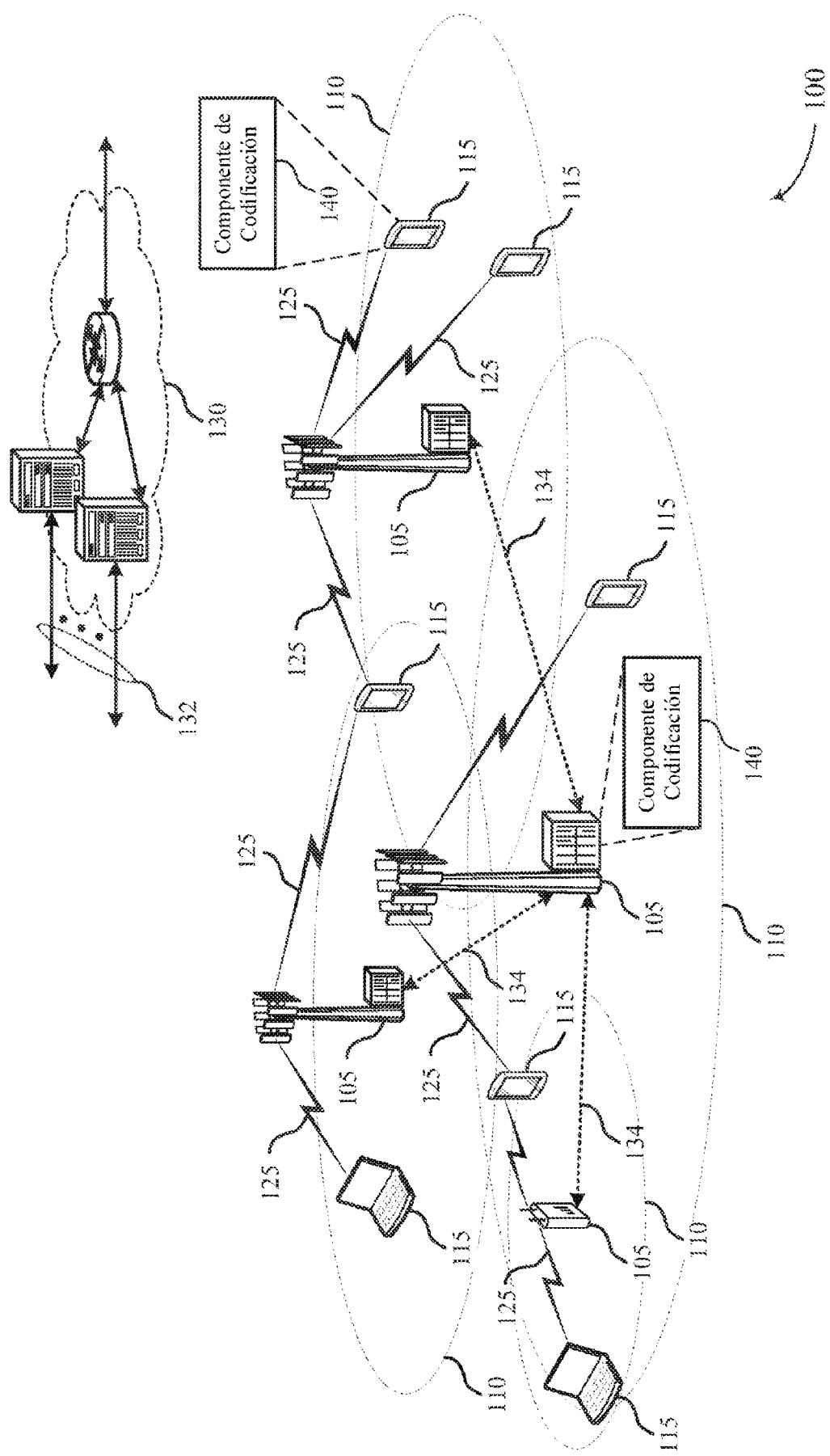

10 La Figura 1 ilustra un ejemplo de un sistema para comunicación inalámbrica que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

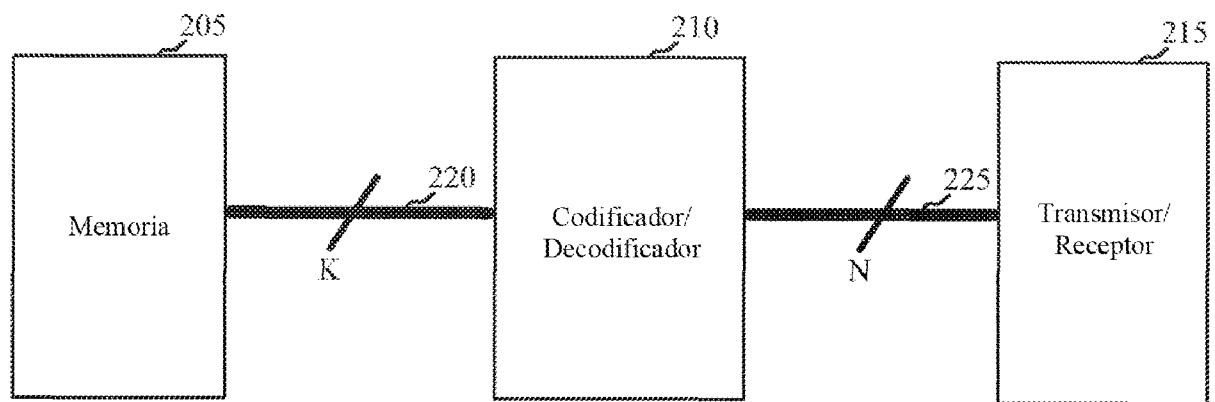

15 La Figura 2 ilustra un ejemplo de un dispositivo que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

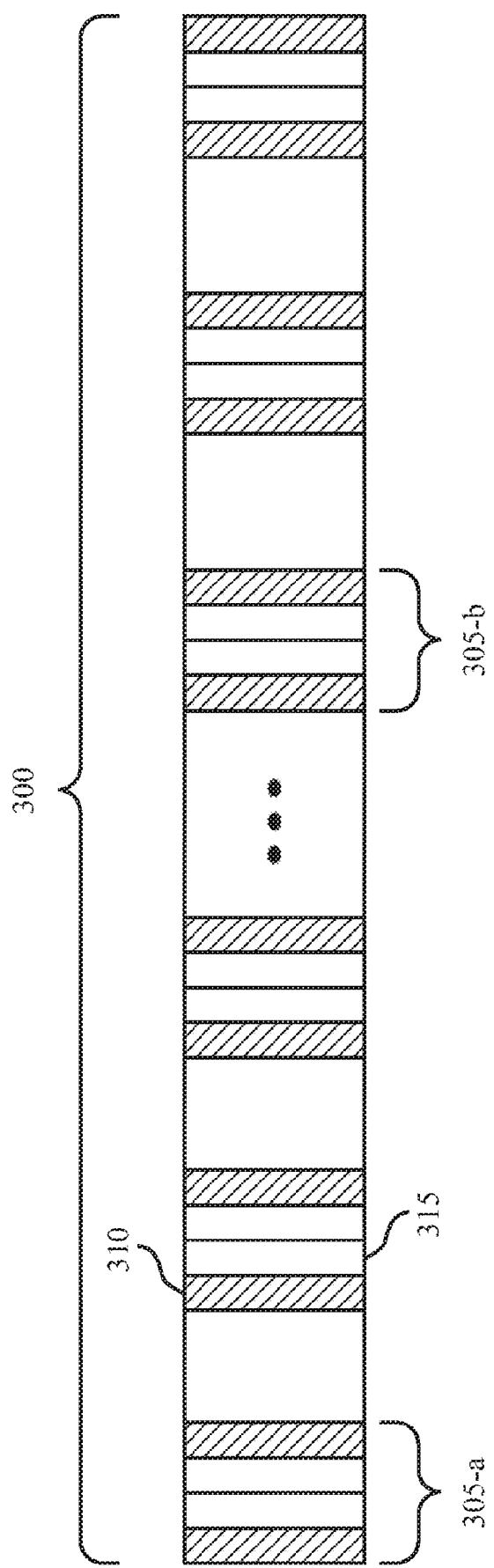

20 La Figura 3 ilustra un ejemplo de una ráfaga PBCH que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

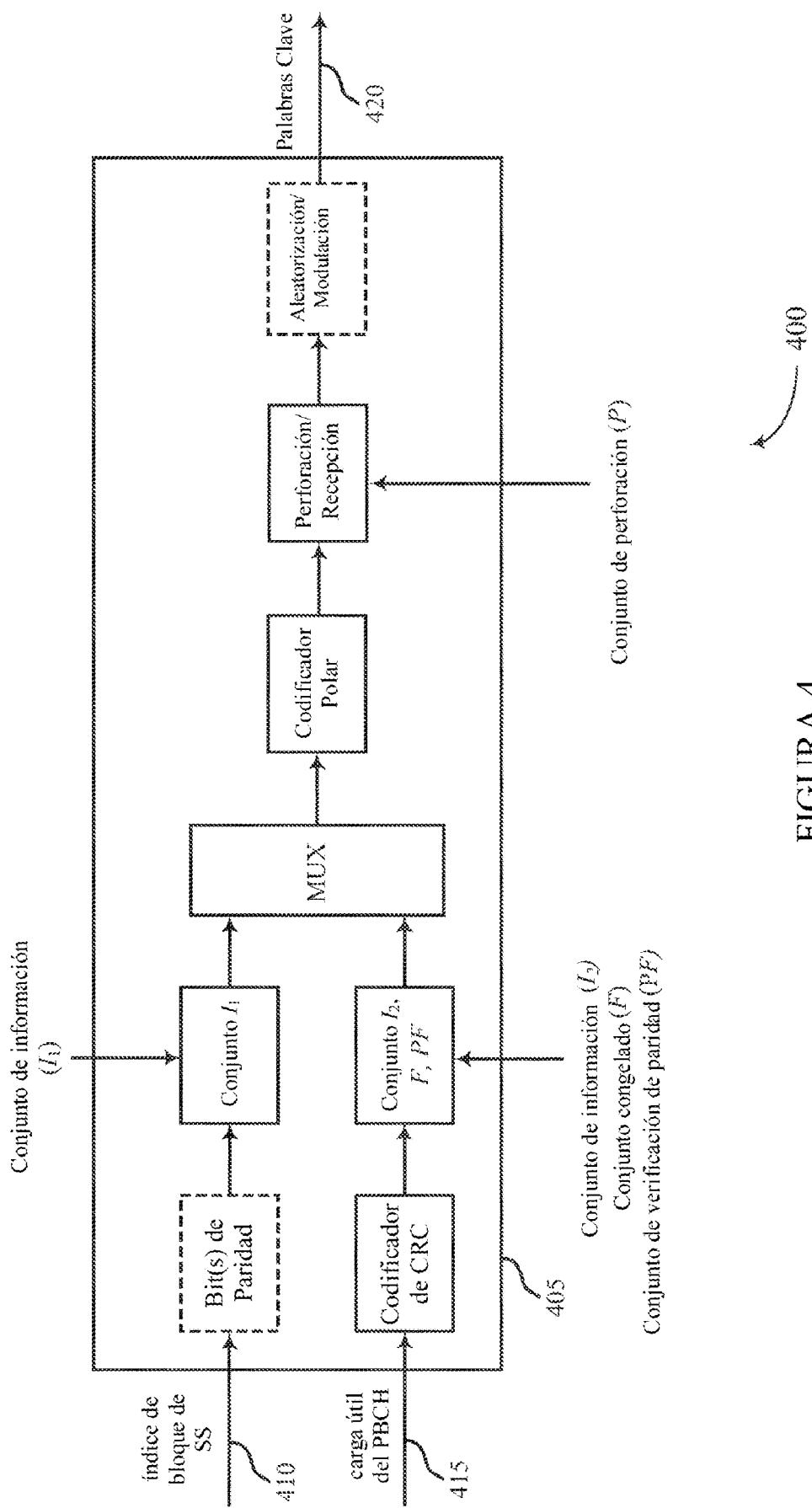

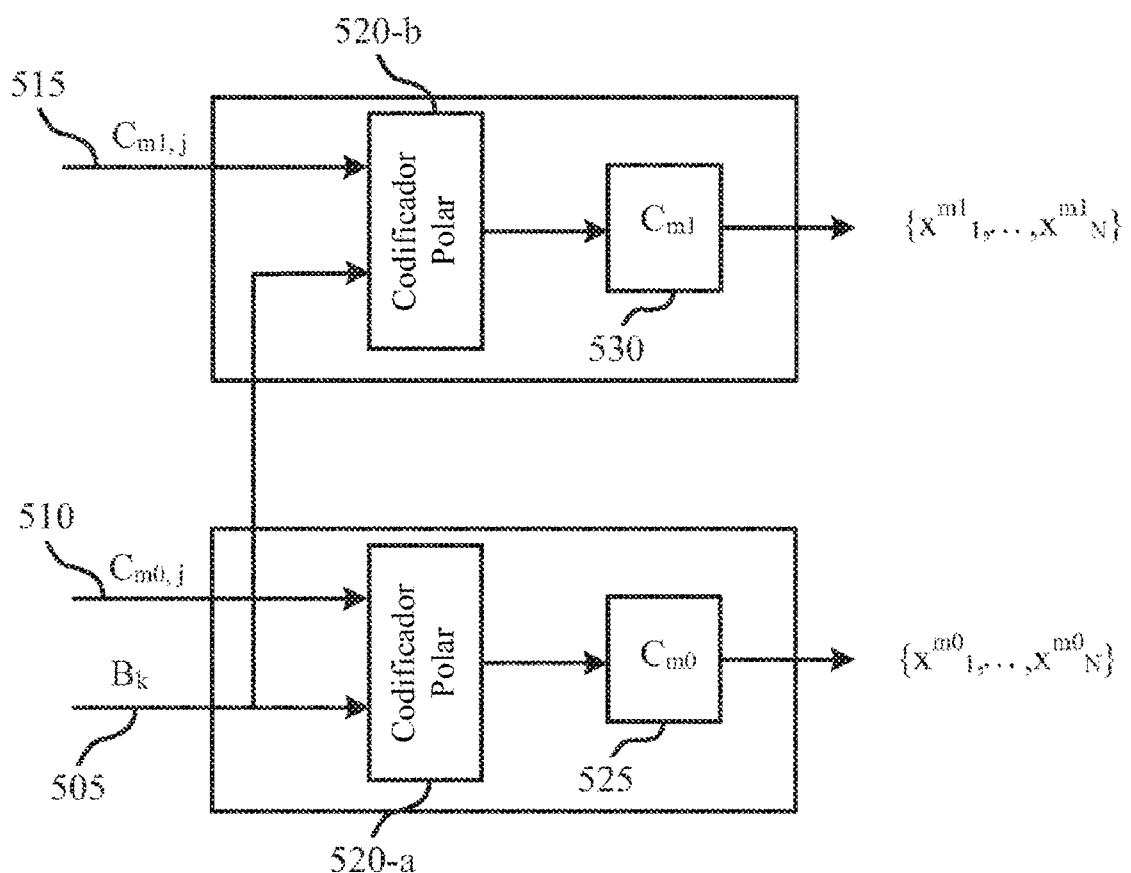

25 Las Figuras 4 y 5 ilustran ejemplos de esquemas de codificación que admiten la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

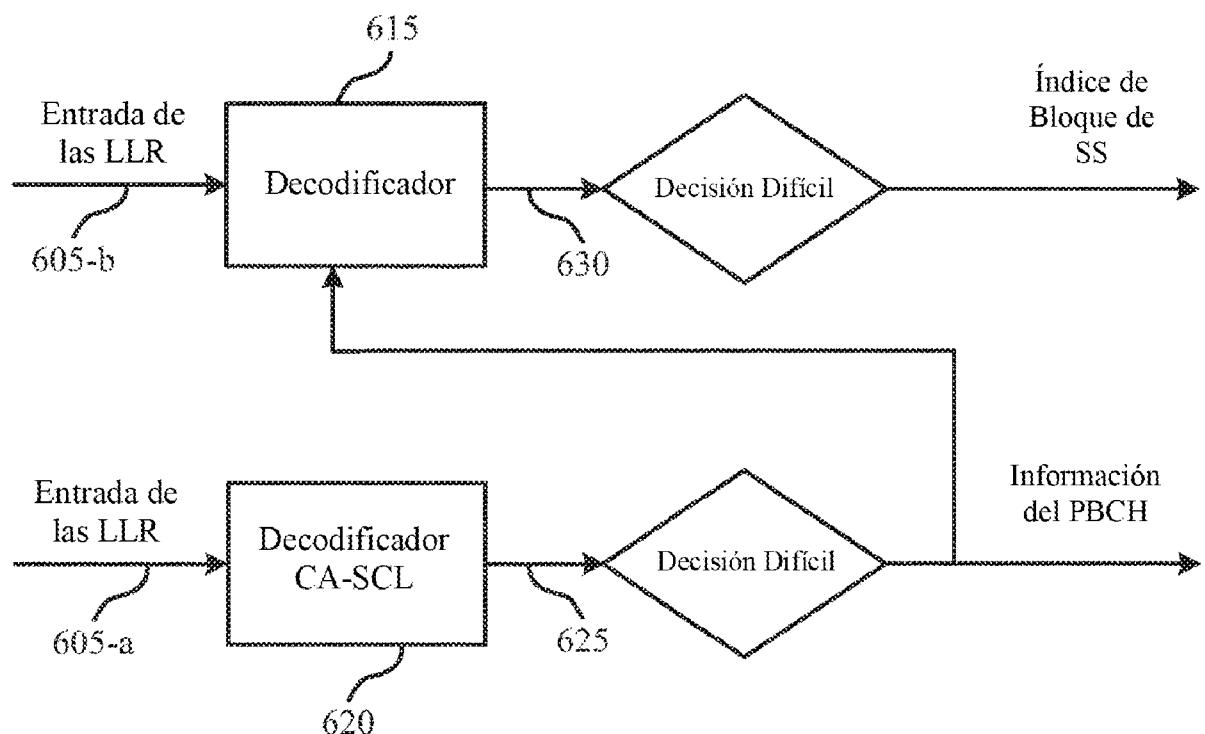

30 La Figura 6 ilustra un ejemplo de un esquema de decodificación que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

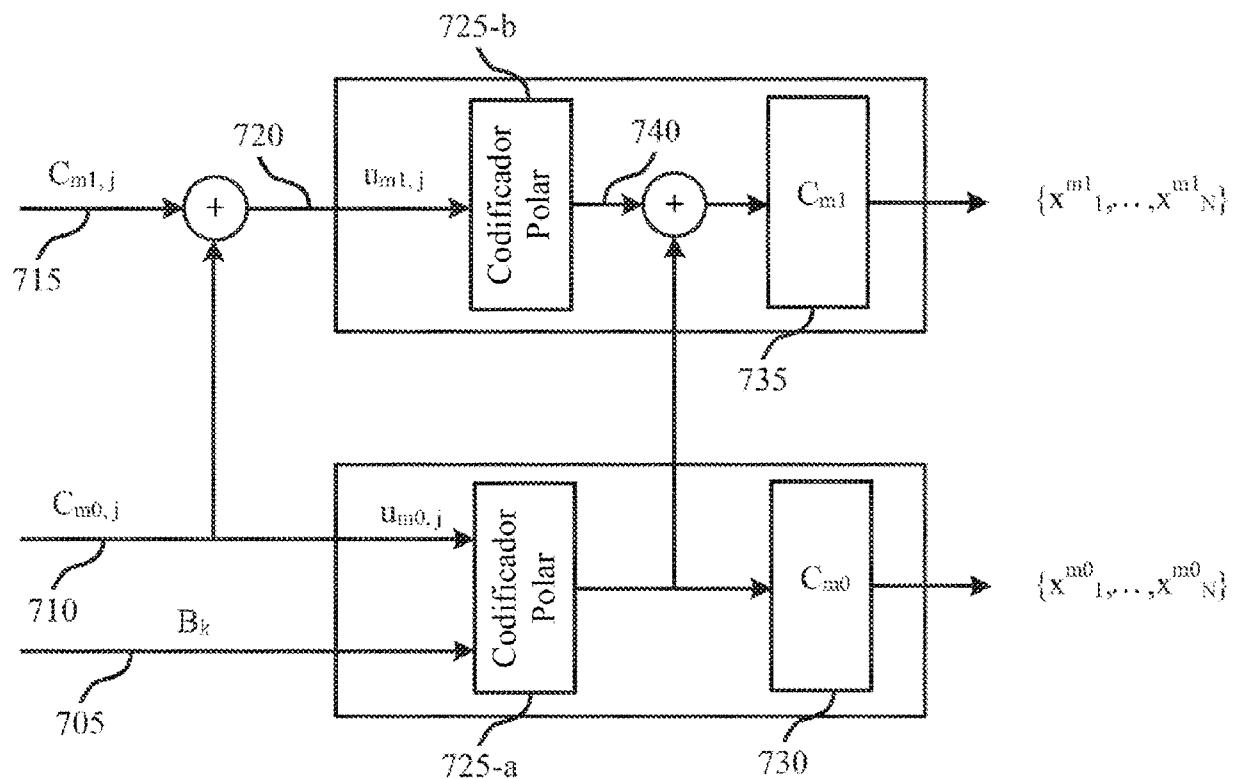

35 La Figura 7 ilustra un ejemplo de un esquema de codificación que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

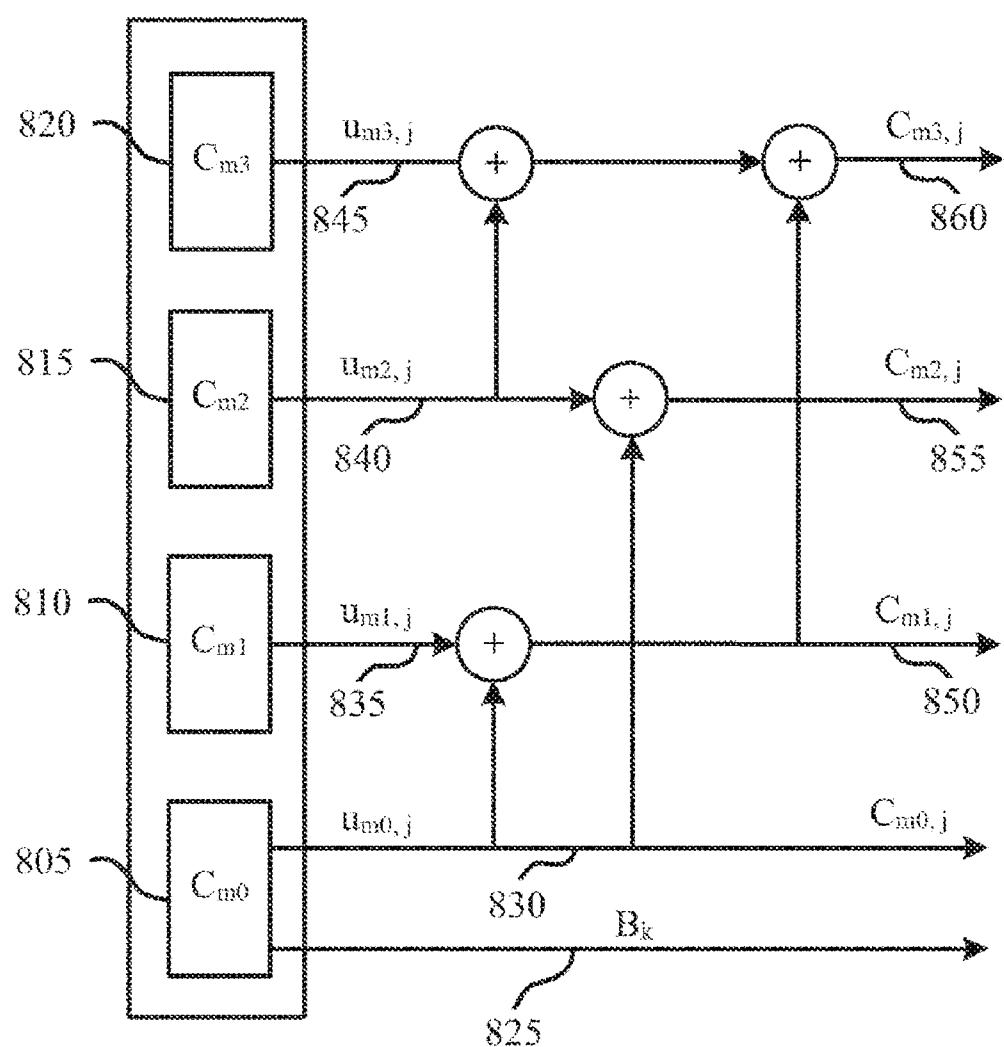

40 La Figura 8 ilustra un ejemplo de un esquema de decodificación que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

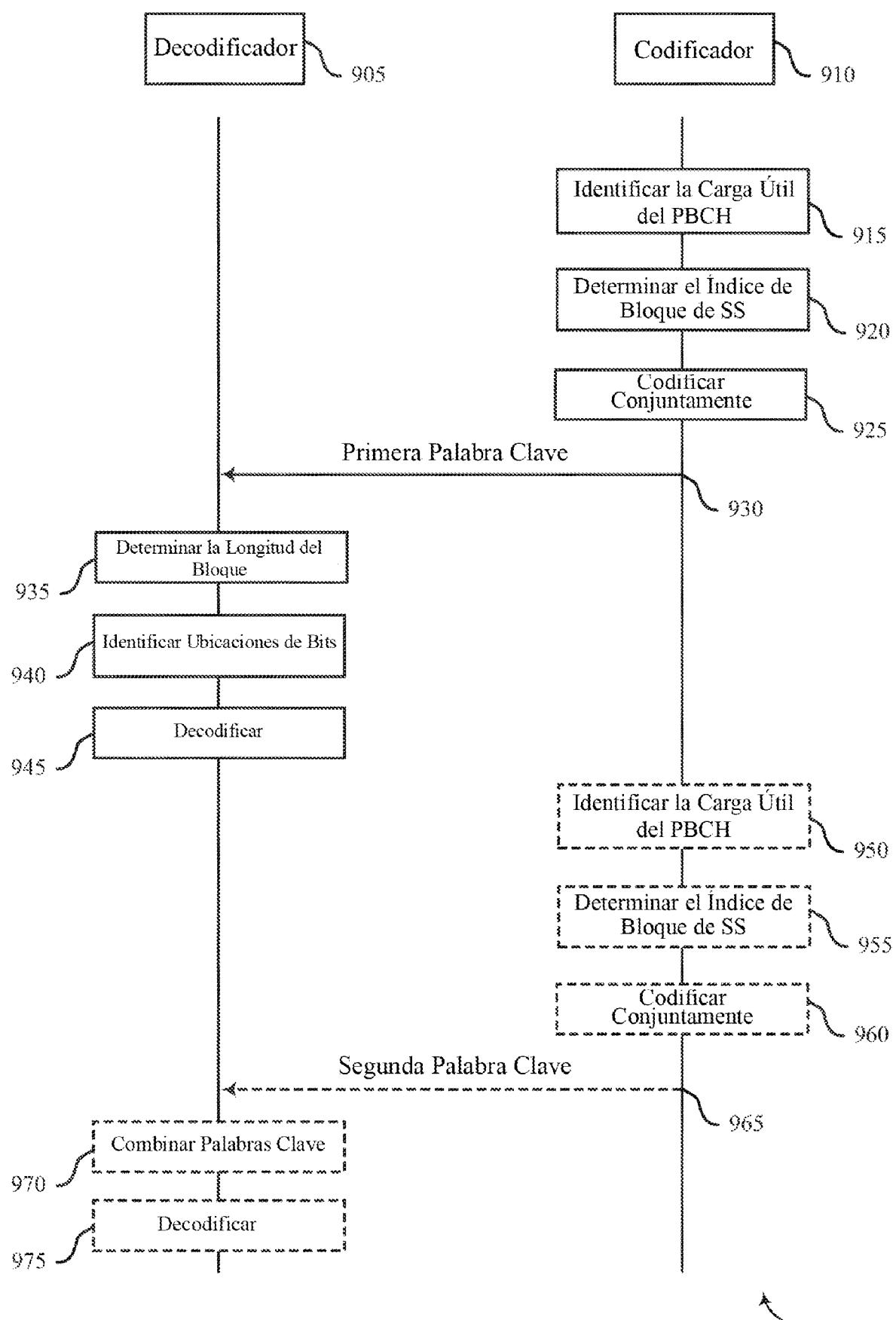

45 La Figura 9 ilustra un ejemplo de un flujo de procedimiento que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

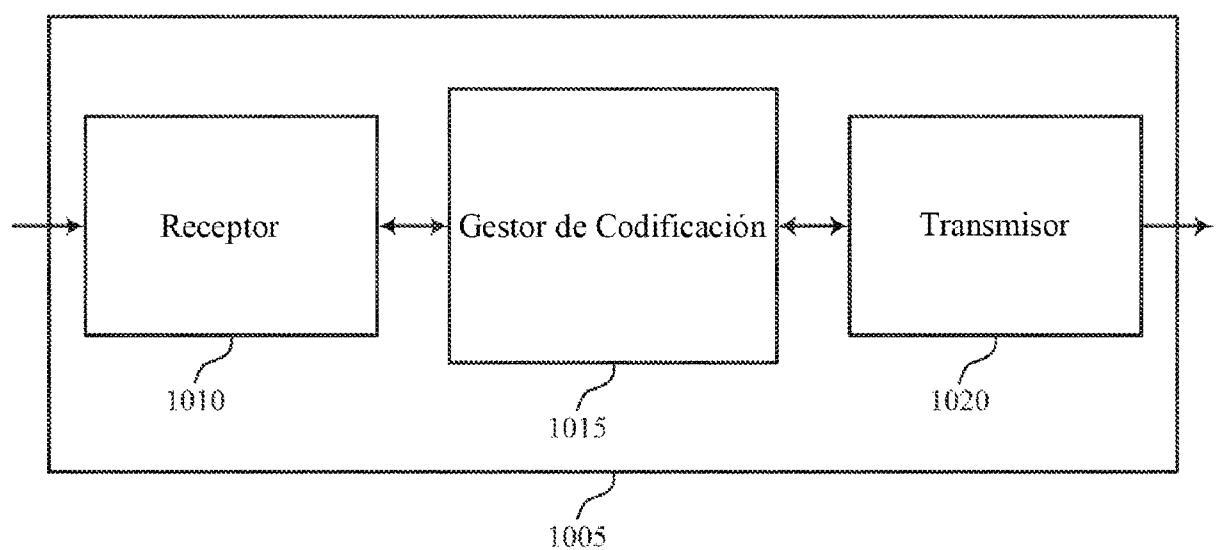

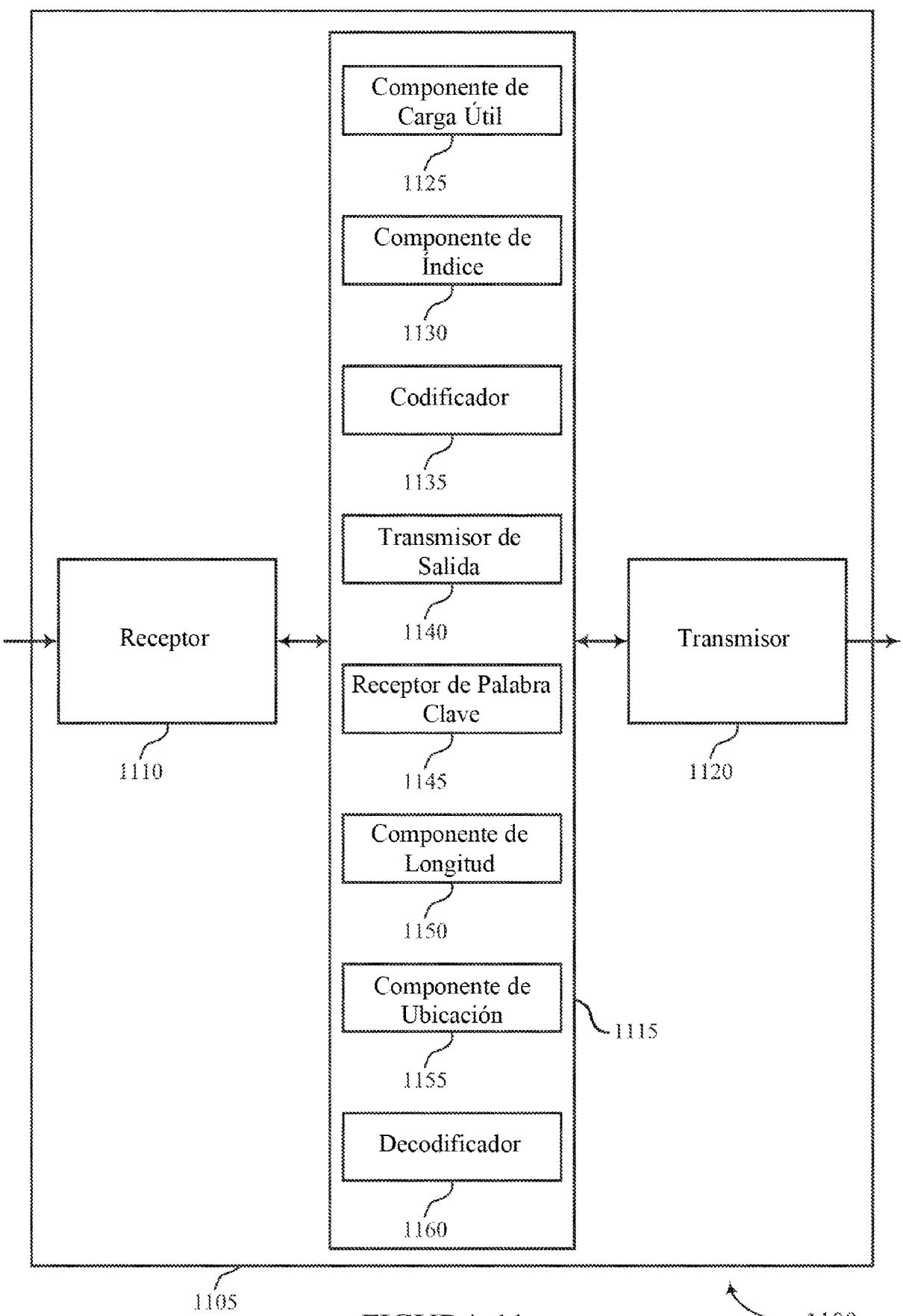

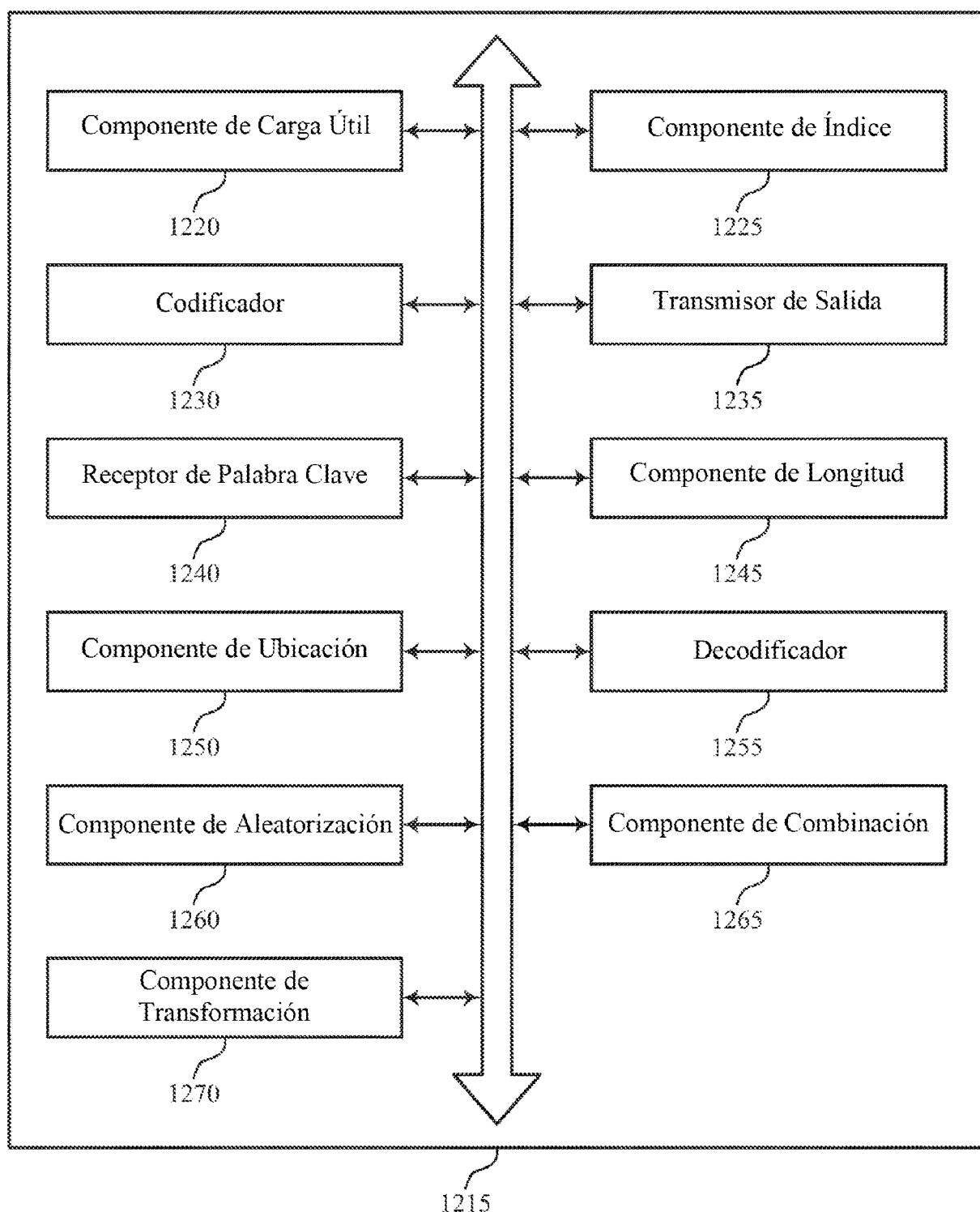

50 Las Figuras de la 10 a la 12 muestran diagramas de bloques de un dispositivo que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

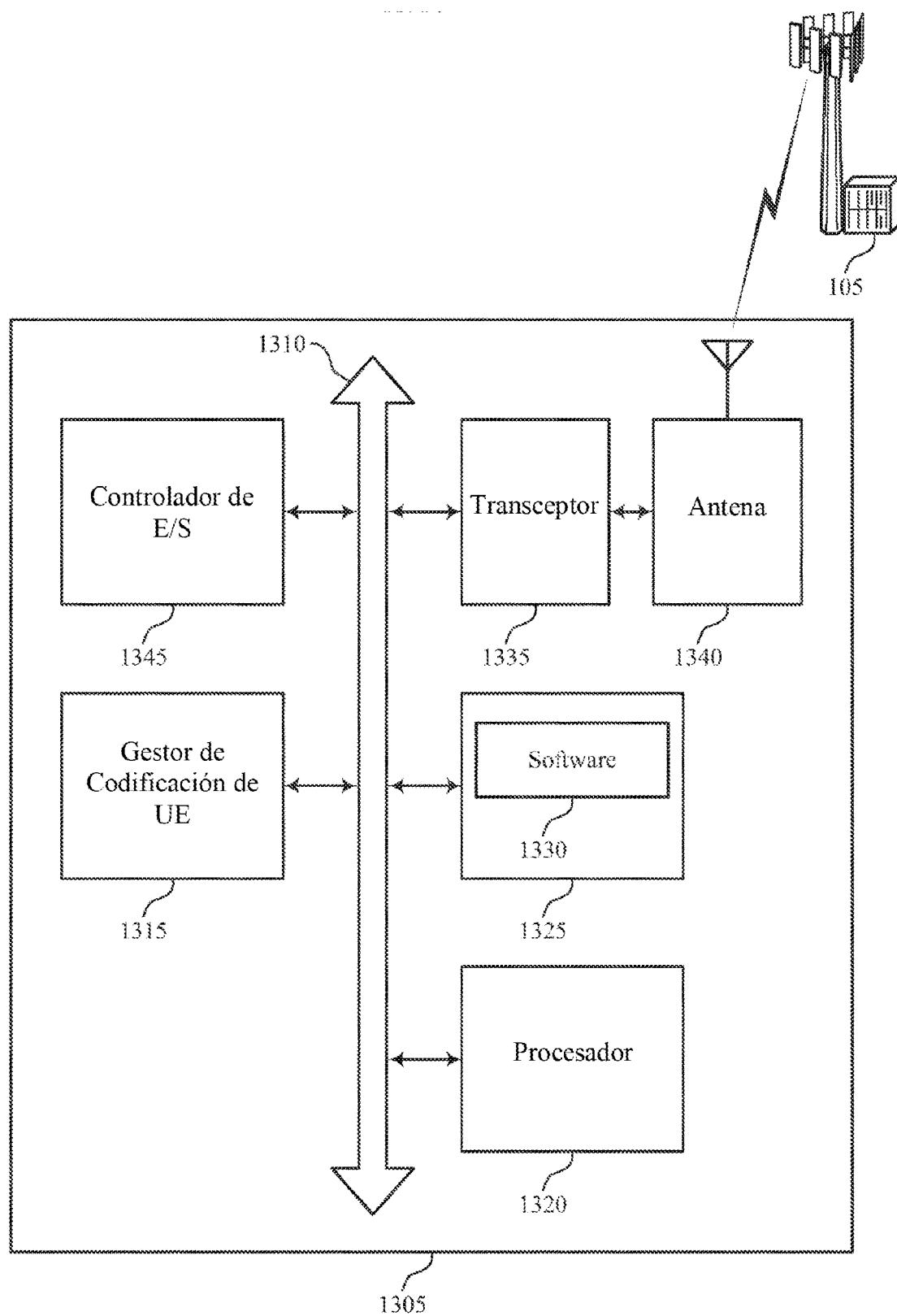

55 La Figura 13 ilustra un diagrama de bloques de un sistema, que incluye un dispositivo (por ejemplo, un UE), que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación;

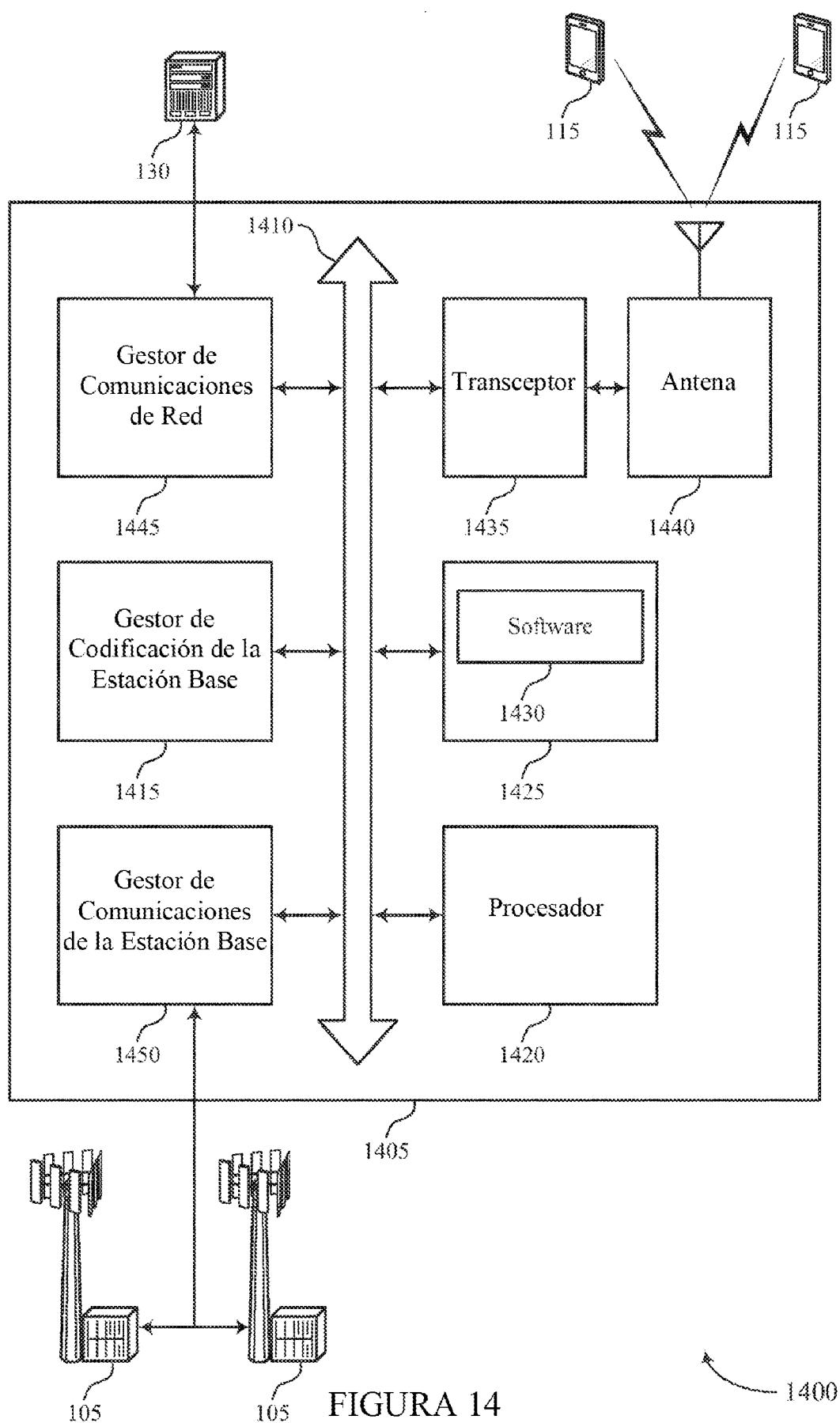

60 La Figura 14 ilustra un diagrama de bloques de un sistema, que incluye un dispositivo (por ejemplo, una estación base), que admite la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación; y

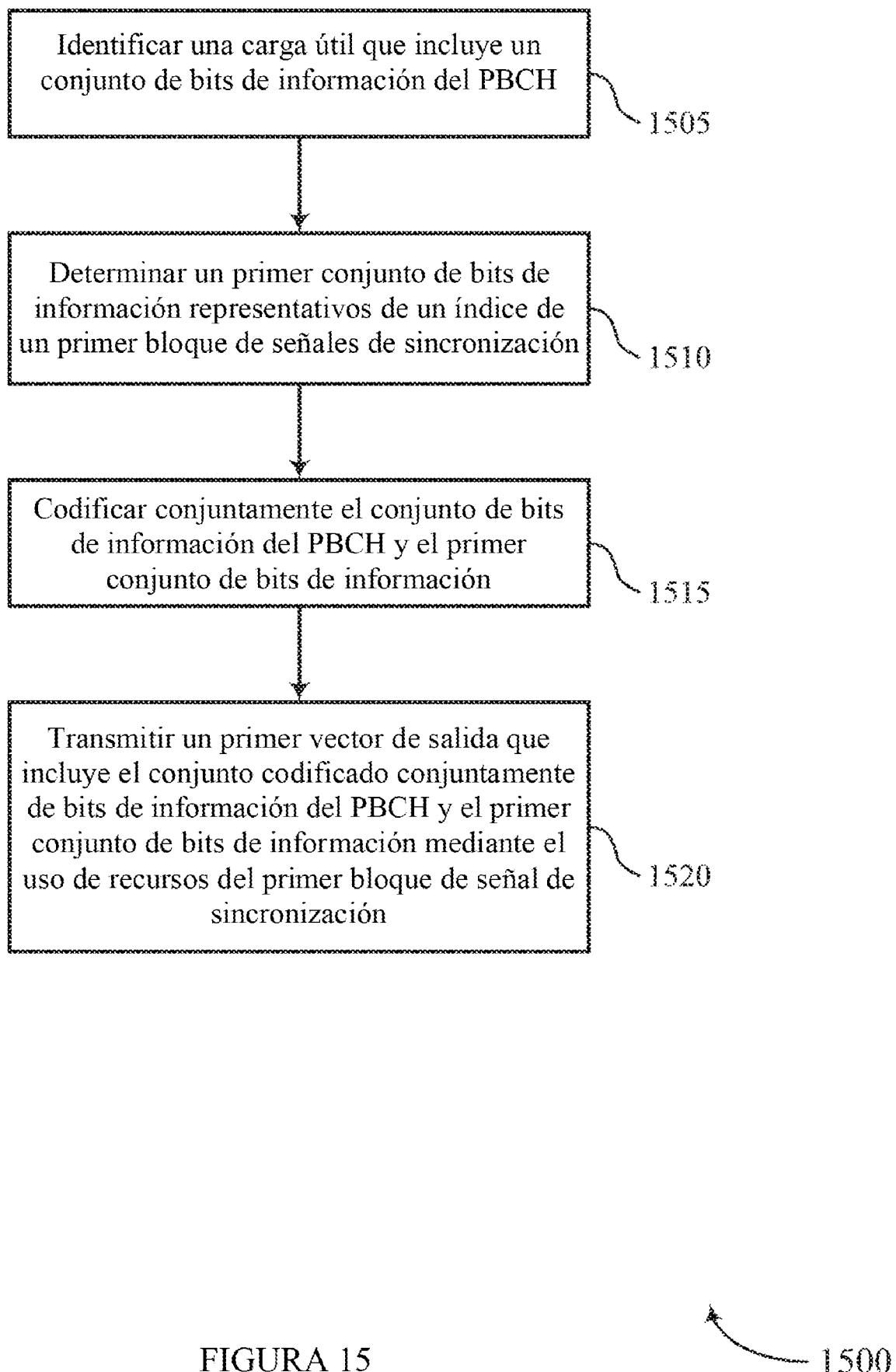

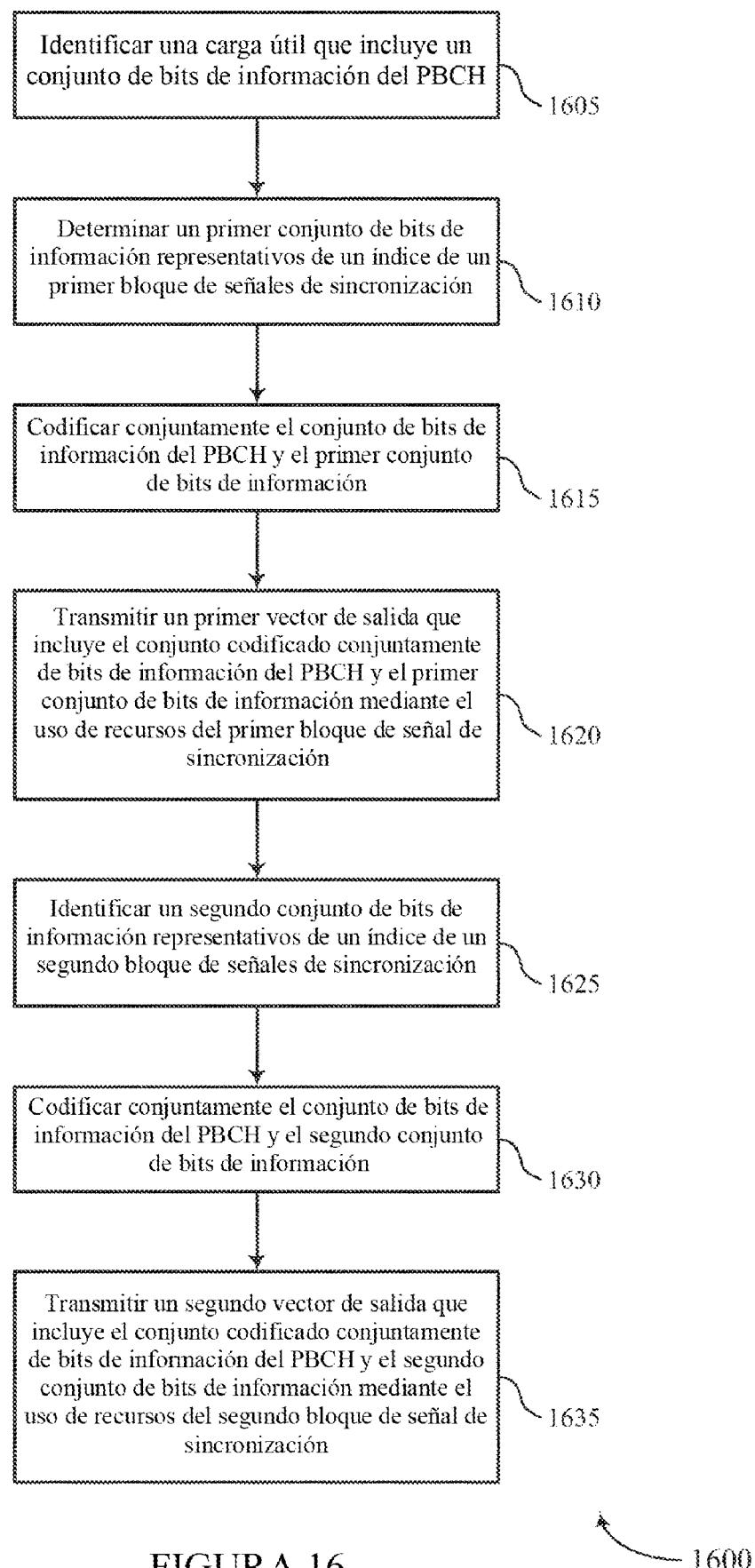

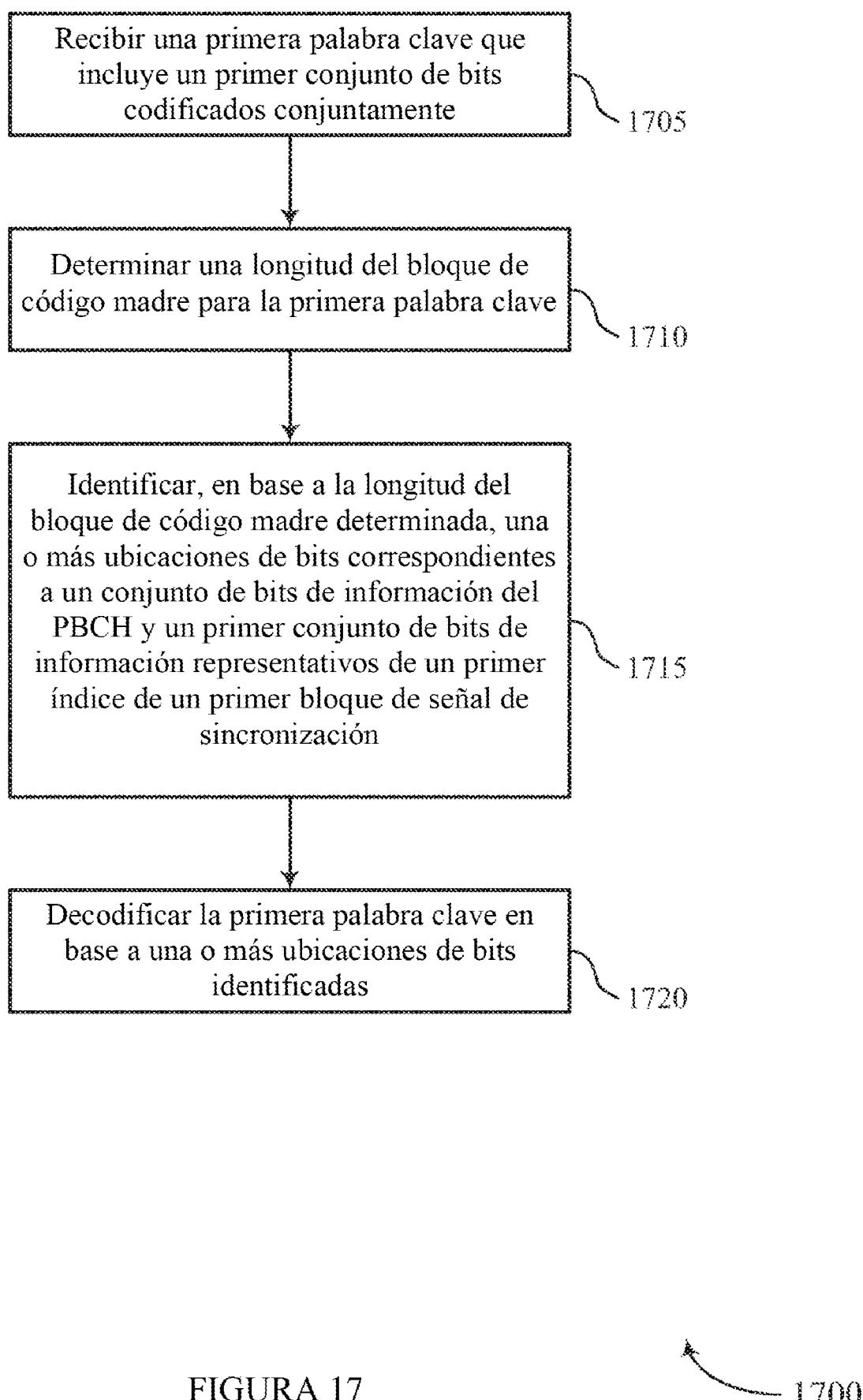

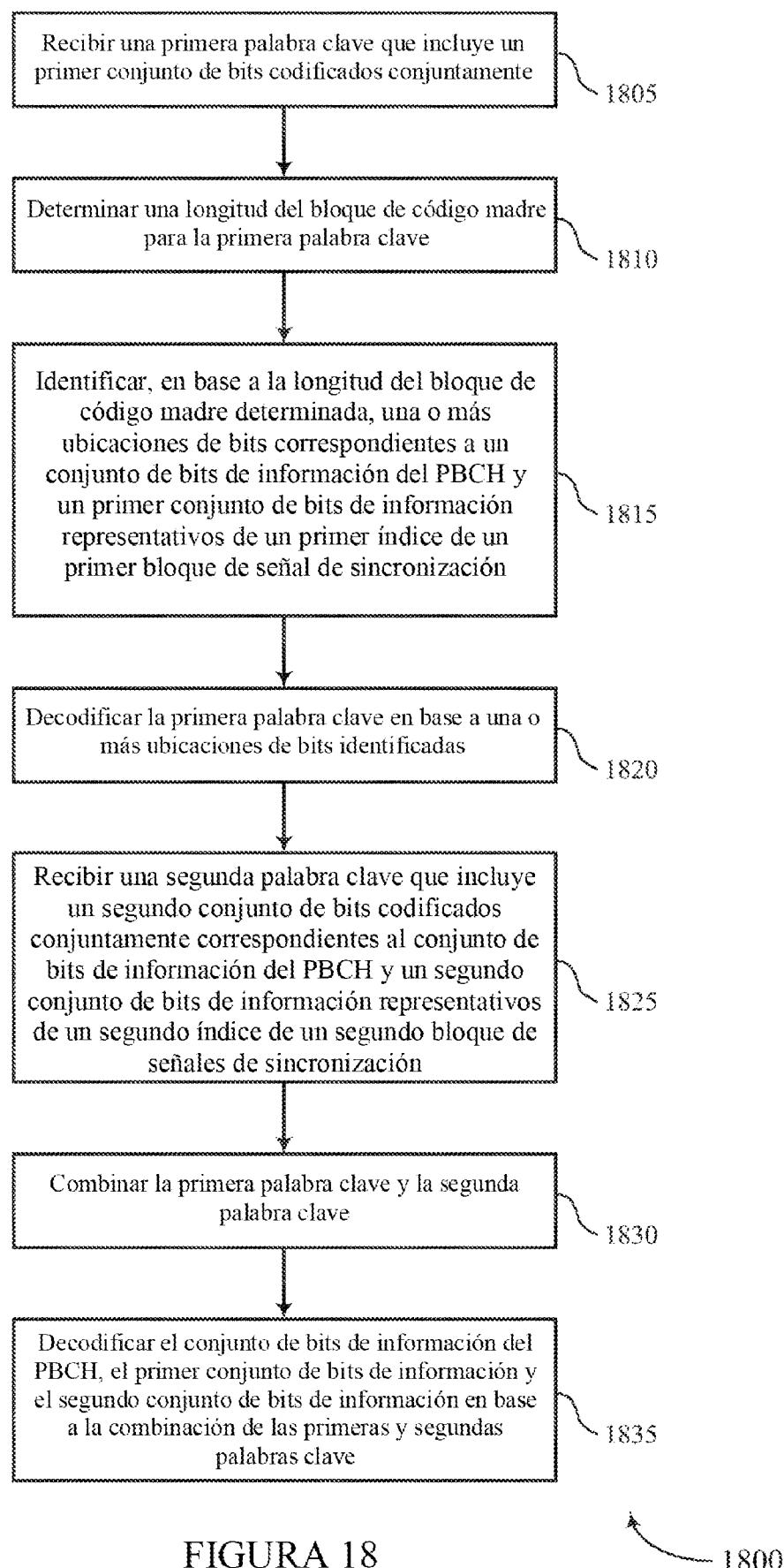

65 Las Figuras de la 15 a la 18 ilustran procedimientos para la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación.

50 Descripción detallada

60 Las cargas útiles del canal físico de difusión (PBCH), que incluyen la información crítica del sistema que se transmite en un bloque de información maestra (MIB), pueden codificarse conjuntamente con índices de señales de sincronización. Las ráfagas de tales transmisiones del PBCH codificadas conjuntamente pueden decodificarse sin los efectos nocivos de la decodificación ciega y sin pérdida significativa de protección contra errores o aumentos significativos de la latencia. La codificación polar puede emplearse para codificar conjuntamente la información que incluye la carga útil del PBCH y los índices de la señal de sincronización.

65 A modo de ejemplo, un dispositivo inalámbrico puede completar primero un procedimiento de adquisición de células para intercambiar datos sobre una red de comunicaciones inalámbricas. Este procedimiento puede permitir al dispositivo inalámbrico determinar información relevante sobre la célula. El dispositivo inalámbrico puede realizar múltiples procedimientos de adquisición de células en serie o en paralelo (por ejemplo, para determinar la mejor célula disponible). Ejemplos de información relevante para una célula dada incluyen desplazamientos de temporización y frecuencia, ancho de banda, formatos de canal de control, etc.

70 En algunos casos, es posible que un dispositivo inalámbrico no pueda recibir datos o transmitir datos con éxito al anfitrión de célula (por ejemplo, que puede ser una estación base, un nodo de red de acceso, o alguna otra entidad

- coordinadora) sin participar primero en el procedimiento de adquisición de células. El procedimiento de adquisición de células puede incluir el intercambio de una o más señales de sincronización, así como también un MIB. Debido a que el MIB contiene información crítica para comunicarse con la célula, el anfitrión de la célula puede difundir el MIB (por ejemplo, sobre un canal físico de difusión (PBCH)). Aunque en la presente divulgación se hace referencia principalmente a su aplicación a un procedimiento de adquisición inicial, el MIB también puede contener información relevante para los dispositivos inalámbricos que ya han adquirido la red (por ejemplo, actualizaciones sobre el formato del canal de control).

- Una función del MIB puede ser transmitir información de temporización para la célula. En algunos sistemas convencionales, esta información de temporización puede transmitirse a través de alguna combinación de información explícita dentro del MIB (por ejemplo, los ocho bits más significativos de un número de trama del sistema (SFN)), y la información implícita usada para transmitir el MIB (por ejemplo, un código de aleatorización usado para indicar los bits restantes del SFN). Como ejemplo, para reducir la sobrecarga en estos sistemas convencionales, puede generarse un MIB periódicamente y transmitirse varias veces (por ejemplo, mediante el uso de uno de los múltiples códigos de aleatorización). Un dispositivo inalámbrico puede ser capaz de determinar información de temporización relevante a partir de la decodificación a ciegas del MIB mediante el uso de cualquiera de los posibles códigos de aleatorización para esa célula. Cuando el número de códigos de aleatorización es relativamente bajo (por ejemplo, del orden de 4 códigos de aleatorización), la decodificación ciega puede ser eficiente. Sin embargo, a medida que aumenta el número de códigos de aleatorización potenciales (por ejemplo, debido a que el MIB se transmite con más frecuencia), la decodificación ciega puede resultar inviable. En consecuencia, los aspectos de la presente divulgación pueden proporcionar técnicas alternativas para transmitir esta información de manera más eficiente.

- Los aspectos de la divulgación introducidos anteriormente se describen a continuación en el contexto de un sistema de comunicaciones inalámbricas. A continuación, se describen codificadores, decodificadores, estructuras de recursos físicos y esquemas ilustrativos para la codificación y decodificación de canales de difusión. Los aspectos de la divulgación se ilustran y se describen adicionalmente con referencia a diagramas de aparatos, diagramas de sistemas y diagramas de flujo que se relacionan con la codificación y decodificación de canales de difusión.

- La Figura 1 ilustra un ejemplo de un sistema de comunicaciones inalámbricas 100 de acuerdo con varios aspectos de la presente divulgación. El sistema de comunicaciones inalámbricas 100 incluye las estaciones base 105, los UE 115 y una red central 130. En algunos ejemplos, el sistema de comunicaciones inalámbricas 100 puede ser una red LTE, LTE-Avanzada, de nueva radio(NR) o 5G.

- En redes de NR o 5G, las estaciones base 105 pueden incluir nodos de acceso (AN), unidades centrales (CU) y/o unidades distribuidas (DU). Un AN puede ser un ejemplo de una estación base de nueva radio (NR BS), un Nodo B de nueva radio (NRNB), un nodo de red (NN), o similares. Una CU puede ser un ejemplo de un nodo central (CN), un controlador de nodo de acceso (ANC), o similares. Cada una de las DU puede ser un ejemplo de un nodo de borde (EN), una unidad de borde (EU), una cabeza de radio (RH), una cabeza de radio inteligente (SRH), un punto de transmisión y recepción (TRP), o similares.

- Los UE 115, las estaciones base 105 y otros dispositivos del sistema de comunicaciones inalámbricas 100 pueden tener codificadores de baja latencia que emiten bits de palabras clave para su transmisión antes de cargar todos los bits de entrada. Un LTE 115, una estación base 105, o ambas, pueden incluir un componente de codificación 140 (por ejemplo, un codificador, decodificador, etc.) como se describe a continuación en más detalle. En algunos casos, el sistema de comunicaciones inalámbricas 100 puede admitir comunicaciones de banda ancha mejoradas, comunicaciones ultrafiables (es decir, de misión crítica), comunicaciones de baja latencia y comunicaciones con dispositivos de bajo costo y baja complejidad. El sistema de comunicaciones inalámbricas 100 también puede admitir codificación polar para un PBCH.

- Las estaciones base 105 pueden comunicarse de forma inalámbrica con los UE 115 a través de una o más antenas de estación base. Cada estación base 105 puede proporcionar cobertura de comunicación para un área de cobertura geográfica respectiva 110. Los enlaces de comunicación 125 que se muestran en el sistema de comunicaciones inalámbricas 100 pueden incluir transmisiones de enlace ascendente (UL) desde un UE 115 a una estación base 105, o transmisiones de enlace descendente (DL), desde una estación base 105 a un LTE 115. La información de control y los datos pueden multiplexarse en un canal de enlace ascendente o de enlace descendente de acuerdo con varias técnicas. La información de control y los datos pueden multiplexarse en un canal de enlace descendente, por ejemplo, mediante el uso de técnicas de multiplexación por división de tiempo (TDM), técnicas de multiplexación por división de frecuencia (FDM) o técnicas híbridas TDM-FDM. En algunos ejemplos, la información de control que se transmite durante un intervalo de tiempo de transmisión (TTI) de un canal de enlace descendente puede distribuirse entre diferentes regiones de control de forma en cascada (por ejemplo, entre una región de control común y una o más regiones de control específicas de LTE).

- Los UE 115 pueden estar dispersos por todo el sistema de comunicaciones inalámbricas 100, y cada UE 115 puede ser fijo o móvil. Un UE 115 también puede denominarse como una estación móvil, una estación de abonado, una unidad móvil, una unidad de abonado, una unidad inalámbrica, una unidad remota, un dispositivo móvil, un

- dispositivo inalámbrico, un dispositivo de comunicaciones inalámbricas, un dispositivo remoto, una estación de abonado móvil, un terminal de acceso, un terminal móvil, un terminal inalámbrico, un terminal remoto, un teléfono, un agente de usuario, un cliente móvil, un cliente o alguna otra terminología adecuada. Un UE 115 también puede ser un teléfono celular, un asistente digital personal (PDA), un módem inalámbrico, un dispositivo de comunicación inalámbrica, un dispositivo de mano, una tableta, un ordenador portátil, un teléfono inalámbrico, un dispositivo electrónico personal, un dispositivo de mano, un ordenador personal, una estación de bucle local inalámbrico (WLL), un dispositivo de Internet de las cosas (IoT), un dispositivo de Internet de todo (IoE), un dispositivo de comunicación tipo máquina (MTC), un aparato, un automóvil o similares.

- 5           10          En algunos casos, un UE 115 también puede ser capaz de comunicarse directamente con otros UE 115 (por ejemplo, mediante el uso de un protocolo de igual a igual (P2P) o de dispositivo a dispositivo (D2D)). Uno o más de un grupo de UE 115 que utilizan comunicaciones D2D pueden estar dentro del área de cobertura 110 de una célula. Otros UE 115 en tal grupo pueden estar fuera del área de cobertura 110 de una célula, o de cualquier otra manera incapaz de recibir transmisiones desde una estación base 105. En algunos casos, los grupos de UE 115 que se comunican a través de comunicaciones D2D pueden utilizar un sistema de uno a muchos (1:M) en el que cada UE 115 transmite a todos los demás UE 115 del grupo. En algunos casos, una estación base 105 facilita la programación de recursos para comunicaciones D2D. En otros casos, las comunicaciones D2D se llevan a cabo de manera independiente (por ejemplo, sin una estación base 105).

- 15         20          Algunos UE 115, tales como los dispositivos MTC o IoT, pueden ser dispositivos de bajo costo o baja complejidad, y pueden proporcionar comunicación automatizada entre máquinas, es decir, comunicación de máquina a máquina (M2M). M2M o MTC pueden referirse a tecnologías de comunicación de datos que permiten que los dispositivos se comuniquen entre sí o una estación base sin intervención humana. Por ejemplo, M2M o MTC pueden referirse a comunicaciones desde dispositivos que integran sensores o medidores para medir o capturar información y transmitir esa información a un servidor central o programa de aplicación que puede hacer uso de la información o presentar la información a humanos que interactúan con el programa o aplicación. Algunos UE 115 se pueden diseñar para recoger información o permitir el comportamiento automatizado de las máquinas. Ejemplos de aplicaciones para dispositivos MTC incluyen medición inteligente, monitoreo de inventario, monitoreo de nivel de agua, monitoreo de equipos, monitoreo de atención médica, monitoreo de vida silvestre, monitoreo de eventos meteorológicos y geológicos, gestión y seguimiento de flotas, detección de seguridad remota, control de acceso físico, y carga comercial basada en transacciones.

- 25         30          Las estaciones base 105 pueden comunicarse con la red central 130 y entre sí. Por ejemplo, las estaciones base 105 pueden interactuar con la red central 130 a través de enlaces de retorno 132 (por ejemplo, S1, etc.). Las estaciones base 105 pueden comunicarse entre sí a través de enlaces de retorno 134 (por ejemplo, X2, etc.) ya sea directa o indirectamente (por ejemplo, a través de la red central 130). Las estaciones base 105 pueden realizar la configuración y programación de radio para la comunicación con UE 115, o pueden funcionar bajo el control de un controlador de estación base (no mostrado). En varios ejemplos, las estaciones base 105 pueden ser macro células, células pequeñas, puntos calientes o similares. Las estaciones base 105 también pueden denominarse como eNodoB (eNB) 105.

- 35         40          Una estación base 105 puede conectarse mediante una interfaz S1 a la red central 130. La red central puede ser un núcleo de paquetes evolucionado (EPC), que puede incluir al menos una entidad de gestión de la movilidad (MME), al menos una puerta de enlace de servicio (S-GW) y al menos una puerta de enlace de paquetes (P-GW). La MME puede ser el nodo de control que procesa la señalización entre el UE 115 y el EPC. Todos los paquetes de protocolo de Internet (IP) del usuario pueden transferirse a través de la S-GW, que a su vez puede conectarse a la P-GW. La P-GW puede proporcionar la asignación de direcciones IP, así como también otras funciones. La P-GW puede conectarse a los servicios IP de los operadores de red. Los servicios IP de los operadores pueden incluir la internet, la intranet, un subsistema multimedia IP (IMS) y un servicio de transmisión en continuo con conmutación de paquetes (PSS).

- 45         50          La red central 130 puede proporcionar autenticación de usuario, autorización de acceso, seguimiento, conectividad IP y otras funciones de acceso, enrutamiento o movilidad. Al menos algunos de los dispositivos de red, tales como una estación base 105, pueden incluir subcomponentes tales como una entidad de red de acceso, que puede ser un ejemplo de un controlador de nodo de acceso (ANC). Cada entidad de red de acceso puede comunicarse con un número de UE 115 a través de un número de otras entidades de transmisión de red de acceso, cada una de las cuales puede ser un ejemplo de una cabeza de radio inteligente, o un TRP. En algunas configuraciones, varias funciones de cada entidad de red de acceso o estación base 105 pueden distribuirse a través de varios dispositivos de red (por ejemplo, cabezas de radio y controladores de red de acceso) o consolidarse en un único dispositivo de red (por ejemplo, una estación base 105).

- 55         60          El sistema de comunicaciones inalámbricas 100 puede operar en una región de frecuencia de ultra alta frecuencia (UHF) mediante el uso de bandas de frecuencia desde 700 MHz a 2.600 MHz (2,6 GHz), aunque en algunos casos las redes de red de área local inalámbrica (WLAN) pueden usar frecuencias de hasta 4 GHz. Esta región también puede conocerse como la banda de decímetros, ya que las longitudes de onda oscilan entre aproximadamente un decímetro a un medidor de longitud. En algunos casos, el sistema de comunicaciones inalámbricas 100 también

puede utilizar porciones de frecuencia extremadamente alta (EHF) del espectro (por ejemplo, desde 30 GHz a 300 GHz). Esta región también puede conocerse como banda milimétrica, ya que las longitudes de onda oscilan entre aproximadamente un milímetro y un centímetro de longitud.

- 5 Una estación base 105 puede usar múltiples antenas o matrices de antenas para llevar a cabo operaciones de conformación de haces para comunicaciones direccionales con un UE 115. La conformación de haces puede usarse junto con bandas de UHF o de EHF; adicional o alternativamente, el sistema 100 puede emplear la conformación de haces con otras bandas de frecuencia. La conformación de haces, que también puede denominarse como filtrado espacial o transmisión direccional, es una técnica de procesamiento de señales que puede usarse en un transmisor (por ejemplo, una estación base 105) para dar forma y/o dirigir un haz general de antena en la dirección de un receptor de destino (por ejemplo, un UE 115). Esto puede lograrse al combinar los elementos en una matriz de antenas de tal manera que las señales transmitidas en ángulos particulares experimenten interferencia constructiva mientras que otras experimenten interferencia destructiva.

- 10

- 15 Los sistemas inalámbricos de múltiple entrada múltiple salida (MIMO) usan un esquema de transmisión entre un transmisor (por ejemplo, una estación base 105) y un receptor (por ejemplo, un UE 115), donde tanto el transmisor como el receptor se equipan con múltiples antenas. Algunas porciones del sistema de comunicaciones inalámbricas 100 pueden usar la conformación de haces. Por ejemplo, la estación base 105 puede tener una matriz de antenas con un número de filas y columnas de puertos de antena que la estación base 105 puede usar para la conformación de haces en su comunicación con el UE 115. Las señales pueden transmitirse múltiples veces en diferentes direcciones (por ejemplo, cada transmisión puede ser formadora de haz de manera diferente). Un receptor mmW (por ejemplo, un UE 115) puede probar múltiples haces (por ejemplo, submatrices de antena) mientras recibe las señales de sincronización.

- 20

- 25 En algunos casos, las antenas de una estación base 105 o UE 115 pueden ubicarse dentro de una o más matrices de antenas, que pueden admitir la conformación de haces o la operación MIMO. Pueden colocarse una o más antenas de estación base o matrices de antenas en un conjunto de antena, tal como una torre de antena. En algunos casos, las antenas o matrices de antenas asociadas con una estación base 105 pueden ubicarse en diversas ubicaciones geográficas. Una estación base 105 puede usar múltiples antenas o matrices de antenas para llevar a cabo operaciones de conformación de haces para comunicaciones direccionales con un LTE 115.

- 30

- 35 En algunos casos, el sistema de comunicaciones inalámbricas 100 puede ser una red basada en paquetes que opera de acuerdo con una pila de protocolos por capas. En el plano del usuario, las comunicaciones en la portadora o en la capa del Protocolo de convergencia de datos en paquetes (PDCP) pueden basarse en IP. Una capa de Control de enlace de radio (RLC) en algunos casos puede realizar la segmentación y el reensamblaje de paquetes para comunicarse sobre canales lógicos. Una capa de Control de acceso al medio (MAC) puede realizar el manejo de prioridad y la multiplexación de canales lógicos en canales de transporte. La capa de MAC también puede usar la solicitud de repetición automática híbrida (HARQ) para proporcionar la retransmisión en la capa de MAC para mejorar la eficiencia del enlace. En el plano de control, la capa de protocolo de control de recursos de radio (RRC) puede proporcionar el establecimiento, configuración y mantenimiento de una conexión de RRC entre un UE 115 y un dispositivo de red (por ejemplo, una estación base 105) o red central 130 que admite portadoras de radio para los datos del plano de usuario. En la Capa física (PHY), los canales de transporte se pueden mapear a los Canales físicos.

- 40

- 45 El sistema de comunicaciones inalámbricas 100 puede admitir la operación en múltiples células o portadoras, una característica que puede denominarse agregación de portadora (CA) u operación de múltiples portadoras. Una portadora también puede denominarse como portadora de componentes (CC), una capa, un canal, etc. Los términos "portadora", "portadora de componente", "célula" y "canal" pueden usarse indistintamente en la presente memoria. Un LTE 115 puede configurarse con múltiples CC de enlace descendente y una o más CC de enlace ascendente para la agregación de portadoras. La agregación de portadoras puede usarse tanto con portadoras de componentes de dúplex por división de frecuencia (FDD) como de dúplex por división de tiempo (TDD).

- 50

- 55 En algunos casos, el sistema de comunicaciones inalámbricas 100 puede utilizar portadoras de componentes mejoradas (eCC). Una eCC puede caracterizarse por una o más características que incluyen: un ancho de banda más amplio, una duración de símbolo más corta, TTI más corto y una configuración modificada del canal de control. En algunos casos, una eCC puede asociarse con una configuración de agregación de portadoras o una configuración de conectividad dual (por ejemplo, cuando múltiples células de servicio tienen un enlace de retorno subóptimo o no ideal). Una eCC también puede configurarse para su uso en espectro sin licencia o espectro compartido (donde más de un operador está autorizado a usar el espectro). Una eCC caracterizada por un ancho de banda amplio puede incluir uno o más segmentos que pueden utilizarse por los UE 115 que no son capaces de monitorear todo el ancho de banda o prefieren usar un ancho de banda limitado (por ejemplo, para conservar potencia).

- 60

- 65 En algunos casos, el sistema inalámbrico 100 puede utilizar bandas del espectro de radiofrecuencia tanto con licencia como sin licencia. Por ejemplo, el sistema inalámbrico 100 puede emplear tecnología de acceso de radio LTE de acceso asistido por licencia (LTE-LAA) o LTE sin licencia (LTE U) o tecnología de NR en una banda sin

licencia tal como la banda Industrial, Científica y Médica (ISM) de 5 GHz. Cuando operan en bandas de espectro de radiofrecuencia sin licencia, los dispositivos inalámbricos tales como las estaciones base 105 y los UE 115 pueden emplear procedimientos de escuchar antes de hablar (LBT) para garantizar que un canal esté libre antes de transmitir datos. En algunos casos, las operaciones en bandas sin licencia pueden ser en base a una configuración

5 de agregación de portadoras junto con portadoras de componentes que operan en una banda con licencia. Las operaciones en el espectro sin licencia pueden incluir transmisiones de enlace descendente, transmisiones de enlace ascendente, o ambas. El dúplex en el espectro sin licencia puede ser en base a FDD, TDD o una combinación de ambos.

10 Un UE 115 que intenta acceder a una red inalámbrica puede realizar una búsqueda de célula inicial mediante la detección de una señal de sincronización primaria (PSS) desde una estación base 105. La PSS puede permitir la sincronización de la temporización de ranura (o símbolo) y puede indicar un valor de identidad de la capa PHY (por ejemplo, puede indicar una identidad de célula dentro de un grupo). El UE 115 puede recibir entonces una señal de sincronización secundaria (SSS). La SSS puede permitir la sincronización de tramas de radio (por ejemplo, temporización de trama) y proporcionar un valor de identidad de célula, que puede combinarse con la identidad de célula dentro del grupo para identificar la célula. La SSS también puede permitir la detección de un modo dúplex y una longitud de prefijo cíclico. Algunos sistemas, tales como los sistemas TDD, pueden transmitir una SSS, pero no una PSS.

15 20 25 Un UE 115 que intenta acceder a una red inalámbrica puede realizar una búsqueda de célula inicial mediante la detección de una señal de sincronización primaria (PSS) desde una estación base 105. La PSS puede permitir la sincronización de la temporización de ranura (o símbolo) y puede indicar un valor de identidad de la capa PHY (por ejemplo, puede indicar una identidad de célula dentro de un grupo). El UE 115 puede recibir entonces una señal de sincronización secundaria (SSS). La SSS puede permitir la sincronización de tramas de radio (por ejemplo, temporización de trama) y proporcionar un valor de identidad de célula, que puede combinarse con la identidad de célula dentro del grupo para identificar la célula. La SSS también puede permitir la detección de un modo dúplex y una longitud de prefijo cíclico. Algunos sistemas, tales como los sistemas TDD, pueden transmitir una SSS, pero no una PSS.

20 25 Después de recibir la PSS y/o la SSS, el LTE 115 puede recibir un bloque de información maestra (MIB), que puede transmitirse en un PBCH. El MIB puede contener información sobre el ancho de banda del sistema, un SFN (por ejemplo, los 8 bits más significativos del SFN de 10 bits), una configuración de canal indicador de HARQ físico (PHICH), un número de antenas de transmisión en la estación base 105, o cualquier otra información de adquisición pertinente. La información de adquisición contenida en el MIB puede denominarse alternativamente en la presente memoria como carga útil del PBCH.

30 35 40 45 En algunos casos, el PBCH puede diseñarse para admitir una decodificación de baja latencia y una recepción fiable para los usuarios del borde de la célula. Como ejemplo, cada MIB en un sistema LTE se genera con una periodicidad de 40 ms (por ejemplo, la capa PHY recibe un nuevo MIB para codificar cada 40 ms). Cada nuevo MIB generado incluye un SFN actualizado. Otros componentes de la carga útil del PBCH pueden actualizarse adicionalmente (por ejemplo, la configuración del PHICH, el ancho de banda del enlace descendente, etc.). El MIB puede codificarse a una velocidad muy baja y repetirse cuatro veces (por ejemplo, una vez por trama de 10 ms) durante el período de 40 ms (por ejemplo, mediante el uso de una velocidad de código de 1/48 durante un TTI de 40 ms). Tal diseño puede proporcionar una fuerte protección contra errores. Cada una de las cuatro transmisiones repetidas puede ser autodecodificable (por ejemplo, de manera que cuando la relación señal a interferencia y ruido (SINR) es relativamente alta, el UE 115 puede decodificar el MIB correctamente sin recibir necesariamente las cuatro transmisiones repetidas). Adicionalmente, las transmisiones pueden combinarse suavemente (por ejemplo, de manera que cuando la SINR es relativamente baja, el UE 115 puede combinar suavemente cada transmisión con las ya recibidas hasta que se logre la decodificación exitosa del MIB). Es decir, debido a que cada MIB puede transmitirse cuatro veces (una vez por trama de 10 ms) antes de que se genere otro MIB, las cuatro transmisiones del mismo MIB contienen la misma información (por ejemplo, la misma carga útil del PBCH) y, por lo tanto, pueden combinarse suavemente.

50 55 60 La temporización del TTI de 40 ms para cada MIB en el PBCH puede no indicarse explícitamente al LTE 115 (por ejemplo, en cambio, puede determinarse implícitamente a partir de secuencias de aleatorización, que se reinician cada 40 ms). En consecuencia, el LTE 115 puede decodificar a ciegas el PBCH (por ejemplo, el UE 115 puede procesar el PBCH a ciegas mediante el uso de todas las formas posibles en las que la estación base 105 podría haber manipulado la información) para determinar la información de temporización deseada. Es decir, el UE 115 puede determinar inicialmente la temporización dentro del TTI de 40 ms al realizar cuatro decodificaciones separadas del PBCH mediante el uso de cada una de las cuatro posibles secuencias de aleatorización y verificar la verificación de redundancia cíclica (CRC) para cada decodificación.

65 70 75 En algunos casos, las cuatro posibles secuencias de aleatorización pueden basarse en una identidad de célula, que a su vez puede determinarse a partir de la recepción de la PSS y SSS. Debido a que las cuatro secuencias de aleatorización pueden ocurrir en un orden conocido y repetitivo, pueden usarse para transmitir implícitamente información de temporización dentro del TTI de 40 ms (por ejemplo, una primera secuencia de aleatorización puede asociarse con una primera trama de 10 ms del TTI de 40 ms, una segunda secuencia de aleatorización puede asociarse con una segunda trama de 10 ms del TTI de 40 ms, etc.). En consecuencia, la periodicidad de 40 ms del PBCH puede permitir que el UE 115 recopile los dos bits restantes del SFN (por ejemplo, los dos bits menos significativos).

80 85 90 Como se describió anteriormente, también puede aplicarse una combinación suave de la carga útil del PBCH en múltiples tramas de radio para mejorar el rendimiento de decodificación. Como ejemplo, el UE 115 puede intentar inicialmente decodificar la carga útil del PBCH a partir de una única trama de radio (por ejemplo, a partir de un primer bloque de señal de sincronización (SS)). Si la decodificación falla para los cuatro códigos de aleatorización posibles, la carga útil del PBCH del primer bloque de SS puede combinarse suavemente con la carga útil del PBCH

que se recibe en el siguiente bloque de SS, etc. En algunos casos, un bloque de SS como se describe en la presente memoria puede referirse a una combinación de señales de sincronización (por ejemplo, PSS y SSS) y el MIB dentro de un intervalo de tiempo dado.

5 Sin embargo, en algunos casos, la decodificación ciega del PBCH puede no ser factible. Como ejemplo, una estación base 105 en un sistema de NR puede transmitir señales NR-PBCH en ráfagas que comprenden más de cuatro bloques de SS (por ejemplo, un MIB determinado puede transmitirse más de cuatro veces, de manera que serían necesarios más de cuatro códigos de aleatorización para distinguir las transmisiones). En consecuencia, un UE 115 que detecte el NR-PBCH en cualquiera de los múltiples bloques de SS puede emplear técnicas alternativas 10 para determinar el índice de bloque de SS y el límite de temporización de la subtrama. Es decir, mientras que el número de bloques de SS en una única ráfaga PBCH en un sistema LTE puede restringirse a 4, el número de bloques de SS en una ráfaga NR-PBCH puede ser superior a 4 (por ejemplo, 8, 12, 16, etc.).

15 Mientras que los cuatro posibles códigos de aleatorización en el sistema LTE pueden transmitir implícitamente información de temporización del sistema, el uso de códigos de aleatorización en un sistema de NR para transportar información de temporización similar puede ser costoso (por ejemplo, en términos de complejidad y/o latencia) debido al aumento en el número de hipótesis sobre el índice de bloque de SS para la decodificación NR-PBCH. Es decir, mientras que un LTE 115 puede ser capaz de decodificar a ciegas un PBCH mediante el uso de cualquiera de las cuatro secuencias de aleatorización posibles en un sistema LTE, la complejidad, la latencia, el consumo de 20 energía, etc., de tal decodificación ciega puede aumentar sustancialmente para el uso de, por ejemplo, 16 códigos de aleatorización en un sistema de NR. Por lo tanto, la información de temporización transmitida implícitamente mediante el uso de códigos de aleatorización en un sistema LTE puede transmitirse explícitamente de manera más eficiente en un sistema de NR.

25 Adicional o alternativamente, en un sistema de NR, la estación base 105 puede aplicar barrido de haz a través de una ráfaga PBCH, de manera que un UE 115 puede no ser capaz de recibir bloques de SS sucesivos. Por tanto, un diseño que permita al LTE 115 combinar cargas útiles del PBCH de múltiples bloques de SS no continuos puede permitir un mejor rendimiento de decodificación. En la presente memoria se describen técnicas que admiten tal diseño.

30 La Figura 2 ilustra un ejemplo de un dispositivo 200 para la codificación y decodificación de canales de difusión de acuerdo con uno o más aspectos de la presente divulgación. El dispositivo 200 puede ser cualquier dispositivo dentro del sistema de comunicaciones inalámbricas 100 que realice una operación de codificación o decodificación. El dispositivo 200 puede ser, por ejemplo, un LTE 115 o una estación base 105 como se describe en la Figura 1. Además, el codificador/decodificador 210 puede ser un ejemplo del componente de codificación 140 como se describe con referencia a la Figura 1.

Como se muestra, el dispositivo 200 puede incluir una memoria 205, un codificador/decodificador 210 y un transmisor/receptor 215. El bus 220 puede conectar la memoria 205 al codificador/decodificador 210 y el bus 225 40 puede conectar el codificador/decodificador 210 al transmisor/receptor 215. En algunos casos, el dispositivo 200 puede tener datos almacenados en la memoria 205 para transmitirlos a otro dispositivo, tal como el UE 115 o la estación base 105. Para iniciar el procedimiento de transmisión, el dispositivo 200 puede recuperar (por ejemplo, desde la memoria 205) los datos para su transmisión. Los datos pueden incluir un número de bits de información 45 que se proporcionan desde la memoria 205 al codificador/decodificador 210 a través del bus 220. El número de bits de información puede representarse como un valor 'K' como se muestra. El codificador/decodificador 210 puede codificar el número de bits de información y emitir una palabra clave que tiene una longitud N que puede ser diferente o igual que K. Los bits que no se asignan como bits de información (es decir, N - K bits) pueden ser bits de paridad o bits congelados. Los bits de paridad pueden usarse en técnicas de codificación polar de verificación de 50 paridad (PC) y los bits congelados pueden ser bits de un valor dado (0, 1, etc.) conocido tanto por el codificador como por el decodificador (es decir, el codificador codifica bits de información en un transmisor y el decodificador decodifica la palabra clave recibida en un receptor). Además, desde la perspectiva del dispositivo receptor, el dispositivo 200 puede recibir datos codificados (por ejemplo, una palabra clave) a través del transmisor/receptor 215, y decodificar los datos codificados mediante el uso del codificador/decodificador 210 para obtener los datos transmitidos.

55 En algunos ejemplos, el procedimiento para codificar transmisiones de datos por el codificador/decodificador 210 puede implicar generar un código polar de longitud N y dimensión 'K' (correspondiente al número de bits de información). Un código polar es un ejemplo de un código lineal de corrección de errores de bloque y es la primera técnica de codificación que logra demostrar la capacidad del canal y puede usarse para aumentar la probabilidad de éxito de la transmisión. Durante la codificación, un codificador puede incluir múltiples instancias de canal (por ejemplo, ramas de codificación) que se cargan cada una con un bit a codificar. Los bits a codificar pueden incluir bits de información y bits sin información. Las métricas de fiabilidad pueden calcularse en base a las ubicaciones de bits del codificador/decodificador 210. Por ejemplo, puede calcularse la probabilidad de que una ubicación de bit dada se decodifique con éxito. Esta probabilidad puede denominarse como fiabilidad y puede asociarse con la ubicación del bit dada. En algunos casos, las ubicaciones de los bits pueden ordenarse en base a las métricas de fiabilidad determinadas (por ejemplo, en orden de fiabilidad decreciente o creciente) y a todas o una porción de las

ubicaciones de bits se les asigna un tipo de bit dado (por ejemplo, bit de paridad, bit de información, bit congelado, etc.). Para una dimensión dada K, las K ubicaciones de bits más fiables se asignan como bits de información y los bits restantes pueden ser bits congelados o bits de paridad.

5 El codificador/decodificador 210 puede usar un número de técnicas de codificación para codificar los datos para su transmisión tales como la codificación lineal de bloques, la codificación polar, la codificación polar de PC, codificación Reed-Muller (RM), codificación RM polar y similares, que pueden introducir redundancia en la salida codificada. Esta redundancia puede aumentar la probabilidad general de que el número de bits de información se decodifique con éxito tras la recepción.

10 La Figura 3 ilustra un ejemplo de una ráfaga PBCH 300 para la codificación y decodificación de canales de difusión, de acuerdo con aspectos de la presente divulgación. La ráfaga PBCH 300 incluye múltiples bloques de SS 305, cada uno de los cuales comprende el(los) bloque(s) del PBCH 310 y el(los) bloque(s) de PSS/SSS 315. La ráfaga PBCH 300 puede abarcar 40 ms o alguna otra duración adecuada (por ejemplo, 80 ms) y puede contener más de 4 (por ejemplo, 6, 8, 12) bloques de SS 305. Aunque se muestra que tiene dos bloques de PSS/SSS 315 entre dos bloques del PBCH 310, puede emplearse cualquier configuración adecuada de acuerdo con la presente divulgación (por ejemplo, puede haber un solo bloque del PBCH 310, el(los) bloque(s) del PBCH 310 puede(n) ubicarse alternativamente entre los bloques de PSS/SSS 315, alguna de sus combinaciones, etc.). En consecuencia, la Figura 3 se incluye sólo con propósitos ilustrativos y no limita su ámbito.

15 20 En aspectos de la presente divulgación, la carga útil del PBCH y el índice de bloque de SS pueden codificarse conjuntamente. En este ejemplo, la misma carga útil del PBCH (por ejemplo, que puede contener bits de CRC) puede repetirse en múltiples (por ejemplo, todos) bloques de SS 305 dentro de la ráfaga PBCH 300. Pueden transmitirse diferentes índices del bloque de SS (por ejemplo, que puede incluir opcionalmente bits de verificación de paridad) en bloques de SS separados 305 (por ejemplo, el bloque de SS 305-a y el bloque de SS 305-b pueden tener diferentes índices de bloque de SS). La verificación de paridad opcional para el índice de bloque de SS puede facilitar la detección de errores del índice de bloque de SS decodificado. Debido a que la carga útil del PBCH puede ser la misma en diferentes bloques de SS 305, un decodificador receptor (no se muestra) puede ser capaz de combinar suavemente la carga útil del PBCH de múltiples bloques de SS 305 dentro de la ráfaga PBCH 300. Sin embargo, debido a que cada bloque de SS 305 puede asociarse con un índice de bloque de SS separado, la combinación suave directa de las relaciones de probabilidad logarítmica (LLR) recibidas puede no ser aplicable a todo el bloque de SS 305. Debido a que el índice de bloque de SS puede transmitir información importante de temporización (por ejemplo, información de temporización dentro de la duración de la ráfaga PBCH 300), pueden tomarse medidas adicionales para aumentar la probabilidad de transmisión con éxito del índice de bloque de SS. En 25 30 35 un ejemplo descrito con referencia a la Figura 4, la carga útil del PBCH (con los bits de CRC) y el índice de bloque de SS pueden asignarse a diferentes ubicaciones de canal de bits (por ejemplo, mediante el uso de un codificador polar) de manera que el índice de bloque de SS pueda transmitirse a través de los canales de bits más fiables.

40 Como se describió anteriormente, la ráfaga PBCH 300 puede emplearse en un sistema de comunicación que emplea barrido de haz de manera que un dispositivo de decodificación puede no recibir todos los bloques de SS 305 en la ráfaga PBCH 300. Adicional o alternativamente, la atenuación de señales de alta frecuencia puede inhibir al dispositivo decodificador de recibir una transmisión (por ejemplo, incluso si la transmisión se dirige hacia el dispositivo decodificador). Como ejemplo, un decodificador puede recibir los bloques de SS 305-a y 305-b sin recibir ninguno de los bloques de SS 305 intermedios. En consecuencia, el decodificador puede necesitar ser capaz de decodificar la información relevante del bloque de SS 305 sin depender de la recepción de cada bloque de SS 305 en la ráfaga PBCH 300.

45 50 La Figura 4 ilustra un ejemplo de un esquema de codificación 400 para la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación. El esquema de codificación 400 puede realizarse mediante un codificador 405, que puede ser un ejemplo del codificador/decodificador 210 descrito con referencia a la Figura 2. Los aspectos del esquema de codificación 400 se describen con referencia a un esquema de codificación polar en aras de la simplicidad. Sin embargo, otros esquemas de codificación en los que diferentes ubicaciones de bits se asocian con diferentes grados de fiabilidad pueden adicional o alternativamente ser usados sin desviarse del ámbito de la presente divulgación.

55 Como se ilustra, el codificador 405 puede recibir un primer conjunto de bits de información representativos de un índice de bloque de SS 410 y un segundo conjunto de bits de información que comprende una carga útil del PBCH 415. Los dos conjuntos de bits de información pueden procesarse por separado durante al menos una porción de sus respectivas rutas a través del codificador 405. Con referencia primero al índice de bloque de SS 410, los bits pueden ser opcionalmente adjuntos con uno o más bits de paridad. En algunos casos, puede usarse un único bit de paridad para indicar si la representación binaria del índice de bloque de SS 410 tiene un número par o impar de bits '1'. Puede usarse una verificación de paridad opcional para el índice de bloque de SS en el decodificador para mejorar la detección de errores. En la siguiente descripción, el índice de bloque de SS 410 puede referirse a los bits de información o puede referirse a los bits de información y el(los) bit(s) de paridad, en función de si se realiza el procedimiento opcional de incluir bits de paridad. Subsecuentemente, e independientemente de si se ha añadido el(los) bit(s) de paridad, el índice de bloque de SS 410 puede asignarse a un conjunto de ubicaciones de bits  $I_1$ .

Como ejemplo, en el caso de que el índice de bloque de SS 410 se represente por J bits (por ejemplo, J bits de información, J1 bit de información y 1 bit de paridad, etc.), l<sub>1</sub> pueden ser los índices binarios ordenados descendentes [N-J, N-(J-1), ..., N-2, N-1] donde N es la longitud de una palabra clave madre (por ejemplo, que puede ser una potencia de dos). En este ejemplo, l<sub>1</sub> contiene, por lo tanto, los J canales de bits más fiables. l<sub>1</sub> y el índice de bloque de SS 410 puede servir entonces como entradas a un multiplexor.

Los bits de información que comprenden la carga útil del PBCH 415 pueden codificarse inicialmente con CRC. Subsecuentemente, la carga útil del PBCH 415 (por ejemplo, que en este punto puede referirse a los bits de información y los bits de CRC) puede asignarse a un conjunto de ubicaciones de bits l<sub>2</sub>. l<sub>1</sub> y l<sub>2</sub> pueden ser diferentes.

l<sub>2</sub> puede determinarse a partir de los K canales de bits más fiables después de eliminar el conjunto de ubicaciones de bits l<sub>1</sub> y cualquier bit perforado P. Es decir, debido a la tasa de codificación relativamente baja, puede emplearse la perforación de bloques para reducir la cantidad de datos a transmitir. Como ejemplo, si la longitud de la palabra clave (por ejemplo, vector) a transmitir es M bits, P puede incluir las N-M ubicaciones de bits menos fiables en los índices binarios ordenados ascendentes [0, 1, ..., P-2, P-1]. En algunos casos, también pueden identificarse uno o más de otros conjuntos de bits (por ejemplo, bits congelados de verificación de paridad (PF) o bits congelados (F)). Los bits congelados pueden ser bits con un valor conocido tanto por el codificador como por el decodificador, y los bits congelados de verificación de paridad pueden facilitar aún más la detección de errores en el decodificador. l<sub>2</sub>, F, y PF junto con la carga útil del PBCH 415 pueden alimentarse entonces al multiplexor.

La secuencia de bits de salida del multiplexor puede introducirse en un codificador polar (por ejemplo, un codificador Arikan), que puede codificar la secuencia de bits en base a l<sub>1</sub>, l<sub>2</sub>, F, y PF. Tras la codificación, la secuencia de bits puede ser perforada de acuerdo con P (por ejemplo, para generar la longitud deseada M palabra clave 420 para la transmisión). En algunos casos, puede producirse una perforación en el codificador polar. La palabra clave perforada 420 puede aleatorizarse subsecuentemente mediante una secuencia de aleatorización específica de la célula inicializada al comienzo de cada ráfaga PBCH. Por lo tanto, aún puede usarse la aleatorización, por ejemplo, para mitigar la interferencia entre células. En este ejemplo, dado que puede usarse la misma secuencia de aleatorización para todos los bloques de SS en una ráfaga PBCH, es posible que no aumente significativamente la complejidad de decodificación, pero puede ayudar a aleatorizar la interferencia entre células y mejorar la decodificabilidad. Pueden usarse técnicas alternativas para mitigar la interferencia entre células además o en lugar de la aleatorización dentro del ámbito de la presente divulgación.

La Figura 5 ilustra un ejemplo de un esquema de codificación 500 para la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación. El esquema de codificación 500 puede realizarse mediante un codificador, que puede ser un ejemplo del codificador/decodificador 210 descrito con referencia a la Figura 2. El esquema de codificación 500 puede admitir la decodificación en base a un único bloque de SS (por ejemplo, decodificación sin combinación suave de múltiples bloques de SS). En consecuencia, el esquema de codificación 500 puede emplearse en un sistema en el que cada bloque de SS recibido es autodecodificable (por ejemplo, como se describió anteriormente con referencia a la Figura 1).

El esquema de codificación 500 puede incluir B<sub>k</sub> 505 (por ejemplo, el vector de bits de información de longitud K que representa la carga útil del PBCH con los bits de CRC adjuntos). El esquema de codificación 500 puede incluir adicionalmente c<sub>m0,j</sub> 510 y c<sub>m1,j</sub> 515 (por ejemplo, los vectores de bits de información de longitud J que representan el índice de bloque de SS para los bloques de SS correspondientes). Cada uno de estos componentes puede alimentarse a un codificador (por ejemplo, un codificador polar 520-a, 520-b) para generar las palabras clave 525 y 530 para el primer y segundo bloque de SS, respectivamente. Como se ilustra, cada una de las palabras clave 525 y 530 es una palabra clave de longitud N bits. Sin embargo, como se describió anteriormente, la perforación puede realizarse en la palabra clave de N bits para generar una palabra clave de Mbits (M<N). Las palabras clave 525 y 530 pueden representar palabras clave contiguas (por ejemplo, palabras clave que se transmiten secuencialmente en el tiempo) o pueden representar palabras clave no contiguas (por ejemplo, en el caso de barrido de haz por el transmisor). Aunque el esquema de codificación 500 ilustra dos palabras clave que se usan para transmitir la misma carga útil del PBCH (por ejemplo, que puede denominarse alternativamente B<sub>k</sub> 505), pueden transmitirse más de dos palabras clave (por ejemplo, tres, cuatro, etc. palabras clave) de acuerdo con la presente divulgación.

La Figura 6 ilustra un ejemplo de un esquema de decodificación 600 para la codificación y decodificación de canales de difusión de acuerdo con aspectos de la presente divulgación. El esquema de decodificación 600 puede realizarse mediante un decodificador, que puede ser un ejemplo del codificador/decodificador 210 como se describió con referencia a la Figura 2. El esquema de decodificación 600 puede admitir la decodificación en base a un único bloque de SS (por ejemplo, decodificación sin combinación suave de múltiples bloques de SS). En consecuencia, el esquema de decodificación 600 puede emplearse en un sistema en el que cada bloque de SS recibido es autodecodificable (por ejemplo, como se describió anteriormente con referencia a las Figuras 1 y 5). Como ejemplo, el esquema de decodificación 600 puede usarse para decodificar la palabra clave transmitida 525 y/o la palabra clave 530 de la Figura 5.

En el decodificador, pueden calcularse una o más LLR para la palabra clave de M bits (por ejemplo, para estimar varias condiciones del canal). Las LLR 605-a pueden servir como entrada para el decodificador 620 de lista de cancelación sucesiva asistido por CRC (CA-SCL). En algunos casos, el decodificador 620 puede establecer las LLR

de cualquier bit perforado en cero. El decodificador de CA-SCL 620 puede intentar decodificar los K bits de la carga útil del PBCH (por ejemplo, que incluye los bits de CRC). Si la CRC pasa, la carga útil del PBCH decodificada 625 puede usarse como bits congelados para decodificar el J índice de bloque de SS de bits mediante el uso del decodificador 615. El decodificador 615 puede recibir las LLR 605-b como entrada (por ejemplo, que puede ser lo mismo que las LLR 605-a). El decodificador 615 puede ser un decodificador de lista de cancelación sucesiva (SCL), un decodificador de máxima verosimilitud (ML) o algún otro decodificador adecuado. La carga útil del PBCH decodificada 625 y el índice de bloque de SS decodificado 630 pueden usarse entonces para determinar la información de adquisición de célula relevante. Aunque se representan por separado, el decodificador CA-SCL 620 y el decodificador 615 pueden compartir componentes.

La Figura 7 ilustra otro ejemplo de un esquema de codificación 700 para la codificación y decodificación de canales de difusión, de acuerdo con aspectos de la presente divulgación. El esquema de codificación 700 puede realizarse mediante un codificador, que puede ser un ejemplo del codificador/decodificador 210 descrito con referencia a la Figura 2. El esquema de codificación 700 puede admitir la decodificación en base a la combinación de múltiples bloques de SS (por ejemplo, mediante el uso de combinación suave). Aunque el esquema de codificación 700 ilustra dos palabras clave que se usan para transmitir la misma carga útil del PBCH (por ejemplo,  $B_k$  705), pueden transmitirse más de dos palabras clave (por ejemplo, tres, cuatro, etc. palabras clave) de acuerdo con la presente divulgación. Debido a que cada bloque de SS (es decir, cada palabra clave respectiva 730 y 735) contiene la misma carga útil del PBCH (es decir,  $B_k$  705) con diferentes índices de bloque, pueden combinarse múltiples bloques de SS recibidos en el decodificador para mejorar el rendimiento del sistema.

El esquema de codificación 700 es similar al esquema de codificación 500 de la Figura 5 excepto que el esquema de codificación 700 incluye codificación adicional para convertir  $c_{m0,j}$  710 y  $c_{m1,j}$  715 (por ejemplo, los vectores de bits de información de longitud J que representan los índices de bloque de SS para los bloques de SS correspondientes) a  $u_{m0,j}$  710 y  $u_{m1,j}$  720 mediante el uso de una operación exclusiva o (XOR). En el ejemplo que se representa en la Figura 7,  $c_{m0,j}$  710 y  $u_{m0,j}$  710 pueden ser los mismos vectores. Sin embargo, mientras que  $c_{m1,j}$  715 representa el índice de bloque de SS absoluto,  $u_{m1,j}$  720 representa el índice de bloque diferencial (por ejemplo, la cantidad en la que el índice de bloque de SS para la palabra clave 735 difiere del índice de bloque de SS para la palabra clave 730 o alguna otra referencia adecuada). También se contemplan otros ejemplos. En el presente ejemplo,  $B_k$  705 y  $u_{m0,j}$  710 se alimentan al codificador polar 725-a para generar la primera palabra clave 730. Sólo el índice diferencial  $u_{m1,j}$  720 se alimenta al codificador polar 725-b (por ejemplo, que puede ser igual o diferente del codificador polar 725-a). La salida 740 del codificador polar 725-b puede someterse a XOR con la primera palabra clave 730 para la generación de la segunda palabra clave 735. Alternativamente,  $B_k$  705 y los índices diferenciales  $u_{m0,j}$  710 y  $u_{m1,j}$  720 pueden codificarse para generar una palabra clave más larga (por ejemplo, de longitud 2N), y porciones de la palabra clave más larga (por ejemplo, la parte inferior y superior de la palabra clave) puede representar la palabra clave de cada bloque de SS correspondiente.

La Figura 8 ilustra un ejemplo de un esquema de decodificación 800 para la codificación y decodificación de canales de difusión, de acuerdo con aspectos de la presente divulgación. El esquema de decodificación 800 puede realizarse mediante un decodificador, que puede ser un ejemplo del codificador/decodificador 210 como se describió con referencia a la Figura 2. El esquema de decodificación 800 puede admitir la decodificación en base a la combinación de múltiples bloques de SS (por ejemplo, mediante el uso de combinación suave). Es decir, debido a que cada bloque de SS puede contener la misma carga útil del PBCH con diferentes índices de bloque, múltiples bloques de SS recibidos (por ejemplo, que pueden ser palabra clave cortas de longitud X) pueden combinarse y decodificarse como una palabra clave más larga (por ejemplo, una palabra clave de longitud 2X, 4X, etc.). En algunos ejemplos, una palabra clave madre de longitud  $2^{m+X}$  puede obtenerse al combinar recursivamente varias palabras clave más cortas de longitud  $2^m$ . La decodificación de la palabra clave madre puede no emitir el índice de bloque de SS absoluto, pero puede proporcionar información relacionada con el índice diferencial que puede transformarse en el índice de bloque de SS absoluto como se describe a continuación.

En el ejemplo que se representa en la Figura 8, las palabras clave 805, 810, 815 y 820 son transmisiones asociadas con sus respectivos bloques de SS dentro de una ráfaga PBCH dada (por ejemplo, ráfaga PBCH 300 como se describe con referencia a la Figura 3). Aunque se ilustran cuatro palabras clave, puede emplearse cualquier número adecuado de palabras clave mediante el uso de las técnicas descritas en la presente memoria. Adicionalmente, las palabras clave pueden ser contiguas (por ejemplo, pueden transmitirse secuencialmente) o no contiguas. El esquema de decodificación 800 puede incorporar aspectos del esquema de decodificación 600 descrito con referencia a la Figura 6. Como ejemplo, el esquema de decodificación 800 puede incluir un decodificador CA-SCL para decodificar la carga útil del PBCH (por ejemplo,  $B_k$  825). En el presente ejemplo, el rendimiento del decodificador CA-SCL puede aumentarse al combinar la carga útil del PBCH de las múltiples palabras clave 805, 810, 815 y/o 820 (por ejemplo, decodificar como palabras clave progresivamente más largas hasta que se pase la CRC). Es decir, puede lograrse una ganancia de combinación suave para decodificar los bits de información de carga útil del PBCH al combinar múltiples bloques de SS recibidos (por ejemplo, palabras clave 805, 810, 815 y/o 820). Despues de la combinación, la palabra clave más larga puede contener un número significativo de bits congelados, que pueden usarse para simplificar la decodificación de manera que el aumento de la complejidad en el lado del decodificador puede no ser sustancial.

Una vez que se pasa la CRC, la carga útil del PBCH (por ejemplo,  $B_k$  825) pueden servir como bits congelados mientras el decodificador intenta determinar la información del índice de bloque de SS. Como se describió anteriormente con referencia a la Figura 7, en algunos casos (por ejemplo, para una palabra clave más larga) el índice de bloque de SS se codifica como un índice diferencial (por ejemplo, en lugar de un índice absoluto). En consecuencia, el decodificador puede decodificar índices de bloques diferenciales 830, 835, 840 y 845 a partir de las palabras clave 805, 810, 815 y 820, respectivamente (por ejemplo, o alguna combinación de estas palabras clave). Estos índices de bloque diferenciales pueden convertirse subsecuentemente en índices de bloque absolutos 830, 850, 855 y 860, respectivamente (por ejemplo, mediante el uso de una transformada de Hadamard o alguna otra técnica adecuada). En el presente ejemplo, el índice de bloque diferencial 830 y el índice de bloque absoluto 830 10 pueden representarse mediante el mismo vector. Un esquema de ejemplo para determinar un índice de bloque absoluto respectivo (por ejemplo,  $c_{m2,j}$ ) de uno o más índices de bloques diferenciales (por ejemplo,  $u_{m0,j}$  y  $u_{m2,j}$ ) se ilustra en las ecuaciones de ejemplo siguientes (por ejemplo, donde  $\Theta$  representa una operación XOR que se realizará en las respectivas secuencias de bits):

$$\begin{aligned} 15 \quad c_{m0,j} &= u_{m0,j} \\ c_{m1,j} &= u_{m0,j} \Theta u_{m1,j} \\ c_{m2,j} &= u_{m0,j} \Theta u_{m2,j} \\ 20 \quad c_{m3,j} &= u_{m0,j} \Theta u_{m1,j} \Theta u_{m2,j} \Theta u_{m3,j}, \text{ etc.} \end{aligned}$$

etc.

25 Debido a que los bloques de SS combinados en estos ejemplos pueden no ser continuos, el decodificador puede determinar adaptativamente los bloques de SS para combinar (por ejemplo, en base a la calidad de las LLR recibidas como se describió anteriormente). Además, en el caso de que el decodificador sea capaz de determinar la diferencia entre cualquier índice de bloque de SS (por ejemplo, en base al tiempo de recepción de los bloques de SS), la diferencia puede usarse como una verificación de paridad adicional para verificar el índice de bloque de SS 30 decodificado (por ejemplo, ya sea el índice diferencial o el índice absoluto). Como ejemplo, si la diferencia entre los índices de las palabras clave 805 y 810 es de dos (es decir, hubo un bloque de SS transmitido entre ellos que el decodificador no detectó, ignoró debido a una LLR baja, etc.), se puede saber que los dos últimos bits del índice de bloque diferencial 835 son '10'. Si el índice de bloque diferencial decodificado difiere (es decir, no es '10'), se puede detectar un error. Si la diferencia entre los índices de las palabras clave 805 y 810 es cuatro, los últimos tres bits del índice de bloque diferencial 835 son '100,' etc.

40 Adicional o alternativamente, alguna porción de los bits de índice de bloque diferencial puede usarse como bits congelados (por ejemplo, ya que pueden derivarse en base al conocimiento de la diferencia relativa de bloques de SS). Como ejemplo, el último bit del índice de bloque diferencial puede derivarse en base a si la diferencia entre los dos índices de bloque de SS asociados es par (o impar). En algunos casos, un decodificador puede cambiar (por ejemplo, dinámicamente, semiestáticamente, etc.) entre esquemas de decodificación de bloque único y múltiple.

45 La Figura 9 ilustra un ejemplo de un flujo de procedimiento 900 para la codificación y decodificación de canales de difusión. El flujo de procedimiento 900 puede incluir un decodificador 905 y un codificador 910, cada uno de los cuales puede ser un ejemplo del codificador/decodificador 210 descrito con referencia a la Figura 2. En algunos casos, el decodificador 905 puede ubicarse o asociarse de cualquier otra manera con un UE 115 como se describe con referencia a la Figura 1. De manera similar, el decodificador 910 puede ubicarse o asociarse de cualquier otra manera con una estación base 105 como se describe con referencia a la Figura 1. En algunos ejemplos, un UE 115 puede incluir un codificador y un decodificador para facilitar la comunicación D2D, por ejemplo.

50 En 915, el codificador 910 puede identificar una carga útil que comprende un conjunto de bits de información del PBCH (por ejemplo, una carga útil del PBCH). Como se describió anteriormente con referencia a la Figura 1, la carga útil del PBCH puede contener una variedad de información relevante para el procedimiento de adquisición de células. Como ejemplo, el conjunto de bits de información del PBCH puede comprender un SFN de 10 bits.

55 En 920, el codificador 910 puede determinar un primer conjunto de bits de información representativos de un índice de un primer bloque de SS. Como ejemplo, el primer conjunto de bits de información puede comprender 4 bits que representan el bloque de SS.

60 En 925, el codificador 910 puede codificar conjuntamente la carga útil del PBCH y el primer conjunto de bits de información representativos del primer bloque de SS. En algunas realizaciones de ejemplo, la carga útil del PBCH codificada conjuntamente y el índice de bloque de SS codificados conjuntamente pueden ser aleatorizados en base, al menos en parte, a una secuencia de aleatorización específica de la célula. De acuerdo con la invención reivindicada, la codificación conjunta comprende asignar bits de la carga útil del PBCH y bits del índice de bloque de SS a ubicaciones de bits respectivas de un codificador 910 en base, al menos en parte, a una métrica de fiabilidad 65

asociada con las ubicaciones de bits del codificador 910 (por ejemplo, cada ubicación de bits del codificador 910 puede tener una métrica de fiabilidad asociada). En algunas realizaciones, la asignación de los bits puede comprender identificar un primer conjunto de ubicaciones de bits fiables del codificador 910 en base, al menos en parte, a las métricas de fiabilidad y asignar el primer conjunto de bits de información (es decir, el índice de bloque de SS) a las respectivas ubicaciones de bits del primer conjunto de ubicaciones de bits fiables. En algunos casos, la asignación de los bits puede comprender adicional o alternativamente identificar un segundo conjunto de ubicaciones de bits fiables (por ejemplo, que son disjuntas del primer conjunto de ubicaciones de bits fiables) del codificador 910 en base, al menos en parte, a la métrica de fiabilidad y la asignación de la carga útil del PBCH a las ubicaciones de bits respectivas del segundo conjunto de ubicaciones de bits fiables. En aspectos, el segundo conjunto de ubicaciones de bits fiables puede tener una fiabilidad menor que el primer conjunto de ubicaciones de bits fiables.

En algunas realizaciones, la codificación conjunta puede comprender identificar un conjunto de ubicaciones de perforación en el codificador 910 y asignar la carga útil del PBCH y el índice de bloque de SS a ubicaciones de bits del codificador 910 diferentes de las ubicaciones de bits del conjunto de ubicaciones de perforación. En algunos casos, el conjunto de ubicaciones de perforación comprende un conjunto continuo de ubicaciones de bits. En algunas realizaciones de ejemplo, el conjunto de bits de información del PBCH (por ejemplo, la carga útil del PBCH) comprende un conjunto de bits de CRC. En algunos casos, el primer conjunto de bits de información (por ejemplo, el índice de bloque de SS) comprende además un conjunto de bits de verificación de paridad. En algunos casos, la carga útil del PBCH y el índice de bloque de SS se codifican conjuntamente mediante el uso de al menos una operación de codificación polar o una operación de codificación polar de PC.

En 930, el codificador 910 puede transmitir la información codificada conjuntamente como un primer vector de salida (por ejemplo, una primera palabra clave). En algunos casos, la primera palabra clave puede comprender la información de aleatorización conjuntamente codificada.

En 935, el decodificador 905 puede determinar una longitud de bloque de código madre para la primera palabra clave.

En 940, el decodificador 905 puede identificar, en base, al menos en parte, a la longitud del bloque de código madre determinada, una o más ubicaciones de bits correspondientes a la carga útil del PBCH y un índice de bloque de SS. La identificación de una o más ubicaciones de bits se basa, al menos en parte, en una métrica de fiabilidad asociada con la primera palabra clave.

En 945, el decodificador 905 puede decodificar la primera palabra clave en base a las ubicaciones de bits identificadas. En algunos ejemplos, la decodificación puede comprender decodificar la carga útil del PBCH en base a la una o más ubicaciones de bits identificadas y decodificar el índice de bloque de SS en base, al menos en parte, a la carga útil del PBCH decodificada. En algunos casos, decodificar el índice de bloque de SS puede comprender designar la carga útil del PBCH decodificada como bits congelados. En algunos casos, la carga útil del PBCH comprende bits de CRC y la decodificación de la carga útil del PBCH comprende realizar una CRC.

En algunos casos, como se describió anteriormente, pueden combinarse múltiples palabras clave (por ejemplo, combinado suave) para mejorar el rendimiento del decodificador 905. En consecuencia, en 950, 955, 960 y 965 el codificador 910 puede repetir 915, 920, 925 y 930, respectivamente. En aspectos de la presente divulgación, los dos conjuntos de procesos de codificación solo pueden diferir en el índice de bloque de SS determinado en 920 y 955 de manera que las cargas útiles del PBCH de la primera y segunda palabras clave sean idénticas (por ejemplo, el codificador 910 sólo puede realizar 915 sin realizar necesariamente 950).

En 955, el codificador 910 puede identificar un segundo conjunto de bits de información representativos de un índice de un segundo bloque de SS (por ejemplo, un segundo índice de bloque de SS). En algunos casos, el segundo índice de bloque de SS es diferente del primer índice de bloque de SS.

En 960, el codificador 910 puede codificar conjuntamente la carga útil del PBCH y el segundo índice de bloque de SS. En algunos casos, la información codificada conjuntamente puede aleatorizarse mediante el uso de la misma secuencia de aleatorización específica de la célula que la primera palabra clave.

En 965, el codificador 910 puede transmitir un segundo vector de salida (por ejemplo, una segunda palabra clave) que comprende la información codificada conjuntamente. En algunos casos, el primer vector de salida en 930 y el segundo vector de salida en 965 pueden transmitirse mediante el uso del primer y segundo parámetros de formación de haz, respectivamente (por ejemplo, de manera que el primer y segundo parámetros de formación de haz son diferentes).

En 970, el decodificador 905 puede combinar la primera y segunda palabras clave para construir una palabra clave larga (por ejemplo, puede combinar suavemente las dos palabras clave como se describió anteriormente). En algunos ejemplos, combinar la primera y la segunda palabra clave comprende concatenar la primera palabra clave como una primera parte de la palabra clave larga y la segunda palabra clave como una segunda parte de la palabra

- clave larga. En 975, el decodificador puede decodificar la carga útil del PBCH, el primer índice de bits de SS y el segundo índice de bits de SS en base a la palabra clave combinada. En algunos casos, decodificar la palabra clave combinada puede comprender determinar una segunda longitud de bloque de código madre (por ejemplo, para la primera y segunda palabras clave combinadas) y decodificar las palabras clave combinadas en base, al menos en parte, a la segunda longitud de bloque de código madre determinada y las ubicaciones de bits identificadas. En algunos casos, el decodificador 905 puede aplicar una transformación de Hadamard al primer y segundo conjunto de bits de información decodificados para decodificar el primer índice de bloque de SS o el segundo índice de bloque de SS.

- 10 Aunque solo se ilustran dos palabras clave, debe entenderse a la luz de la presente divulgación que puede combinarse cualquier número adecuado de palabras clave para mejorar el rendimiento del decodificador 905 sin aumentar significativamente la complejidad.

- 15 La Figura 10 muestra un diagrama de bloques 1000 de un dispositivo inalámbrico 1005 que admite la codificación y decodificación de canales de difusión de acuerdo con varios aspectos de la presente divulgación. El dispositivo inalámbrico 1005 puede ser un ejemplo de aspectos de un LTE 115 o una estación base 105 como se describe con referencia a la Figura 1. El dispositivo inalámbrico 1005 puede incluir el receptor 1010, el gestor de codificación 1015 y el transmisor 1020. El dispositivo inalámbrico 1005 también puede incluir un procesador. Cada uno de estos componentes pueden estar en comunicación entre sí (por ejemplo, a través de uno o más buses).

- 20 El receptor 1010 puede recibir información tal como paquetes, datos de usuario o información de control asociada con varios canales de información (por ejemplo, canales de control, canales de datos e información relacionada con la codificación y decodificación de canales de difusión, etc.). La información puede pasarse a otros componentes del dispositivo. El receptor 1010 puede ser un ejemplo de aspectos del transceptor 1335 descritos con referencia a la Figura 13.

- 25 El gestor de codificación 1015 puede identificar una carga útil que incluye un conjunto de bits de información del PBCH, determinar un primer conjunto de bits de información representativos de un índice de un primer bloque de señal de sincronización y codificar conjuntamente el conjunto de bits de información del PBCH y el primer conjunto de bits de información.

- 30 Adicional o alternativamente, el gestor de codificación 1015 puede, en combinación con el receptor 1010, recibir una primera palabra clave que incluye un primer conjunto de bits codificados conjuntamente, determinar una longitud de bloque de código madre para la primera palabra clave, identificar, en base a la longitud de bloque de código madre determinada, una o más ubicaciones de bits correspondientes a un conjunto de bits de información del PBCH y un primer conjunto de bits de información representativos de un primer índice de un primer bloque de señal de sincronización, y decodificar la primera palabra clave en base a la una o más ubicaciones de bits identificadas. El gestor de codificación 1015 puede ser un ejemplo de aspectos del gestor de codificación 1315 descrito con referencia a la Figura 13.