(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-505798

(P2006-505798A)

(43) 公表日 平成18年2月16日(2006.2.16)

| (51) Int.C1.         | F 1        | テーマコード (参考)       |

|----------------------|------------|-------------------|

| GO1R 31/28 (2006.01) | GO1R 31/28 | Z E C G 2 G 1 3 2 |

| GO6F 11/22 (2006.01) | GO6F 11/22 | 3 6 0 P 5 B 0 4 8 |

| GO6F 21/22 (2006.01) | GO6F 9/06  | 6 6 0 L 5 B 0 7 6 |

審査請求 未請求 予備審査請求 未請求 (全 18 頁)

|                                        |                                                                                                                |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 特願2004-557093 (P2004-557093) | (71) 出願人 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国テキサス州 78729, オ<br>ースティン, ウエスト・パーマー・レーン<br>7700 |

| (86) (22) 出願日 平成15年4月14日 (2003.4.14)   |                                                                                                                |

| (85) 翻訳文提出日 平成16年11月29日 (2004.11.29)   |                                                                                                                |

| (86) 國際出願番号 PCT/US2003/011399          |                                                                                                                |

| (87) 國際公開番号 WO2004/051294              |                                                                                                                |

| (87) 國際公開日 平成16年6月17日 (2004.6.17)      |                                                                                                                |

| (31) 優先権主張番号 10/135,877                | (74) 代理人 100116322                                                                                             |

| (32) 優先日 平成14年4月30日 (2002.4.30)        | 弁理士 桑垣 衛                                                                                                       |

| (33) 優先権主張国 米国(US)                     | (72) 発明者 トカシク、トーマス<br>アメリカ合衆国 85044 アリゾナ州<br>フェニックス エス. サーティエイス<br>プレイス 13406                                  |

最終頁に続く

(54) 【発明の名称】機密保護走査試験のための方法および装置

## (57) 【要約】

電子的ハッキングから感知可能情報を保護するためのプロセッサ、走査コントローラおよび方法。プロセッサ内に存在する感知可能データのセキュリティを維持するために、走査コントローラは、プロセッサの走査観察可能部分からデータが除去されるまで、走査チェーンへのアクセスを拒否し、次に試験モードから抜け出す前に走査チェーンを再びクリアし、通常動作を再開する。試験モードへおよび/またはから遷移する場合に、プロセッサの走査観察可能部分内に記憶しているデータを除去または他の方法で修正すると、許可を受けていない人が、走査チェーンから機密保護データを簡単にシフトするのが防止され、感知可能状態情報を設定しようとする際に、通常動作の前に走査チェーン内にデータが予め負荷されるのが防止される。

**【特許請求の範囲】****【請求項 1】**

構成信号を受信して試験のために走査チェーン（180）を準備するステップと、前記構成信号に応じて、データ・プロセッサの走査観察可能部分の情報を修正するステップと、

前記修正ステップの後で、前記走査観察可能部分の走査試験をできるようにするステップと、を含む方法。

**【請求項 2】**

前記修正ステップが、前記構成信号に応じて、前記走査観察可能部分をリセットすることを含み、

前記走査試験をできるようにするステップが、イネーブル走査信号を生成して前記走査観察可能部分内で走査ロジックを動作できること、を含む請求項1に記載の方法。

**【請求項 3】**

前記走査試験をできるようにするステップの前に、前記走査観察可能な部分に情報が走査されるのを防止するステップと、

前記走査試験をできるようにするステップの前に、前記走査観察可能部分から情報が走査されるのを防止するステップと、をさらに含む請求項1に記載の方法。

**【請求項 4】**

構成インジケータを受信して、通常動作のために走査チェーン（180）を準備するステップと、

前記構成インジケータに応じて、データ・プロセッサ（100）の走査観察可能部分の情報を修正するステップと、

前記修正ステップの後で前記データ・プロセッサの通常動作を可能にするステップとを含む方法。

**【請求項 5】**

前記修正ステップが、前記走査観察可能部分をリセットすること、を含む請求項4に記載の方法。

**【請求項 6】**

前記走査試験をできるようにするステップの後で、前記走査観察可能部分内に情報が走査されるのを防止するステップと、

前記走査試験をできるようにするステップの後で、前記走査観察可能な部分から情報が走査されるのを防止するステップとをさらに含む、請求項4に記載の方法。

**【請求項 7】**

走査試験の前に、走査リセット信号を供給するためのロジックを備え、前記走査リセット信号がデータ・プロセッサの走査観察可能な部分の情報を修正する走査コントローラ（120）。

**【請求項 8】**

通常モード中に機密保護情報を処理するための機能部分であって、試験モード中に観察することができる機能部分と、

前記機能部分を試験する前に、前記機能部分の情報を修正することにより、前記機密保護情報へのアクセスを防止するための試験制御部分とを備えるプロセッサ。

**【請求項 9】**

前記試験制御部分が、走査試験の前に走査リセット信号を供給するためのロジックを備え、前記走査リセット信号が前記プロセッサの前記機能部分の情報を修正する、請求項8に記載のプロセッサ。

**【請求項 10】**

前記試験制御部分が、走査試験の後で走査リセット信号を供給するためのロジックをさらに備える、請求項8に記載のプロセッサ。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、概して、プロセッサ走査試験に関し、特に走査試験機密保護デバイスに関する。

**【背景技術】****【0002】**

走査チェーンの最も基本的な形態の場合、走査チェーンは、1つの素子の出力が次の素子の入力に直列にリンクし、この素子の出力が次の素子の入力にリンクし、以後同様に前の素子の出力が次の素子の入力にリンクするように一緒にリンクしている一連の素子である。場合によっては、回路設計者は、そうでない場合にはアクセスすることができないプロセッサの内部素子に試験の目的でアクセスするために、走査チェーンを使用する。走査チェーンを使用することにより、試験エンジニアは、1つの入力ポートを通してデータをプロセッサ内に順次シフトすることができる。プロセッサは、データを処理して、次に、1つの出力ポートを通して、処理結果が順次読み出される。このようにして、最大量の内部回路を、複雑になるのを最小限度に留めながら試験することができる。

**【0003】**

しかし、試験はこのように簡単になっても、データにアクセスする問題が起こる。この問題は、特に、ソフトウェア、電気通信、エンターテインメントおよび他の産業の暗号化および機密保護要件の観点から見て考慮に入れなければならない。例えば、電気通信産業は、携帯電話、ポケットベル（p a g e r）等で情報を処理するために使用する半導体チップの中のものに機密保護コードを記憶させる必要がある。これらの機密保護コードは、機密保護状態を指定する目的でハードウェアの識別および認証を行うための、または他のいくつかの目的のための専用のデータ処理方法の一部として使用することができる。しかし、これらのコードを取り扱うための回路が、走査チェーンを介してアクセスすることができる場合には、競合相手が、チップ内に記憶している機密保護コードにアクセスするため、または機密保護状態に侵入するために走査チェーンを利用できるかもしれない。

**【0004】**

チップ内に記憶している機密保護情報にアクセスすべく走査チェーンを利用する、またはチップをだまして機密保護状態にあるように思い込ませて走査チェーンを利用する、という問題を解決するために、メーカーは、一般的に、機密保護情報を処理するために使用した回路を走査チェーンから除去しておく。走査チェーンからこの回路を除去することにより、許可を受けていないユーザが機密保護コードにアクセスするのがますます困難になる。しかし、この解決方法を使用した場合には、チップのかなりの部分を完全には試験できないという問題が残る。

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

上記説明から明らかなように、現在入手できる試験方法は、これらの試験方法を使用した場合、設計者は、データの機密保護を犠牲にして試験のためのアクセスをするか、またはデータ・プロセッサのかなりの部分に試験のためのアクセスをしないでデータの機密保護を守るか、のどちらかを選択しなければならないという点で理想的な方法であるとは言えない。現在必要なのは、機密保護情報を処理するプロセッサの一部に試験のためにアクセスすることはできるが、すべての機密保護情報の秘密をプロセッサ内に機密保持する何らかの方法である。

**【課題を解決するための手段】****【0006】**

添付の図面を参照しながら、下記の説明および特許請求の範囲を読めば、本発明の種々の利点、機能および特徴、および構造の関連素子の方法、動作および機能、並びに製造部材および製造の経済性の組合せを理解することができるだろう。上記図面、説明および特

許請求の範囲は、すべて本明細書の一部を形成している。

【発明を実施するための最良の形態】

【0007】

下記の図面の詳細な説明においては、「アサート (assert) する」および「否定する」(または「アサートを解除する」)という用語は、信号、状態ビットまたは類似の装置を、それぞれ論理的真または論理的偽の状態にする行為に言及する際に使用する。論理的真の状態が論理レベル1である場合には、論理的偽の状態は論理レベル0である。論理的真の状態が論理レベル0である場合には、論理的偽の状態は論理レベル1である。

【0008】

それ故、本明細書で説明する各信号は、正または負のロジックとして設計することができる。この場合、負のロジックは、信号名の上のバーにより、または信号名の後のアステリスク (\*) で表すことができる。負の論理信号の場合には、信号はアクティブ・ロー・レベルにあり、論理的真の状態は論理レベル0に対応する。正の論理信号の場合には、信号はアクティブ・ハイ・レベルにあり、論理的真の状態は論理レベル1に対応する。

【0009】

図1～図7は、プロセッサ試験モードにより感知可能情報へのアクセスを防止することにより、電子ハッキングに対する保護レベルを実現するために、情報プロセッサ内で走査コントローラをどのように使用できるかを示す。機密保護が維持されるこの方法を使用すれば、感知可能情報の機密保護を犠牲にしないで、構成要素試験の範囲を広げることができる。試験範囲が広くなると、製品の試験のコストが安くなり、市場へもっと短時間で出荷できるようになる。

【0010】

感知可能データのセキュリティを維持するために、本明細書において説明する一実施形態は、走査チェーンにアクセスできるようにする前に、プロセッサの走査を観察することができる部分から読出感知可能セキュリティ・データを除去して試験モードから外し、通常動作を再開する前に書き込み感知可能セキュリティ・データを除外する。これらの時点で走査チェーンの感知可能部分を除去すれば、許可を受けていない人が機密保護データを簡単に走査したり、感知可能状態情報を設定するために通常動作の前に走査チェーン上に要素を予め負荷することが防止される。

【0011】

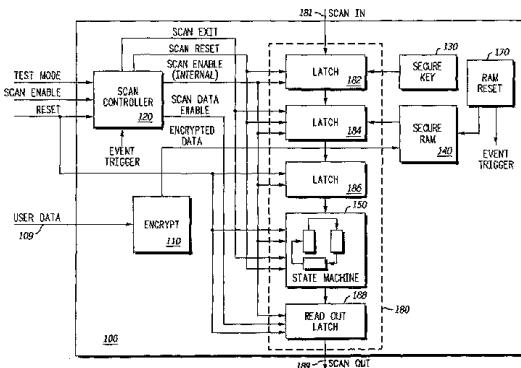

図1について説明すると、この図は、本明細書に記載する教示による走査コントローラを使用するプロセッサである。参照番号100はプロセッサ全体を示す。プロセッサ100は、一連のラッチ182～188および走査チェーン180上に位置する状態機械150、機密保護キー130および機密保護ランダム・アクセス・メモリ(RAM)140のような感知可能情報の種々のソース、および走査チェーン180へのアクセスを制御し、リセットおよび/またはモード構成信号を供給する走査コントローラ120を含む。プロセッサ100は、またユーザのデータを暗号化するための暗号化ブロック110、および機密保護RAM140から情報をクリアするためのRAMリセット170を含む。走査チェーン180上にはいくつかの要素しか示していないが、例えば、暗号化ブロック110のような走査試験を必要とする任意の要素も走査チェーン180上に設置することができることに留意されたい。

【0012】

アクセスから保護しなければならない情報は、配線識別キー(hardwired identification key)および専用ハードウェア/ファームウェアが実施したアルゴリズム、または製造後に記憶した感知可能情報のような、製造中にプロセッサ100内に記憶した情報を含むことができる。例えば、機密保護キー130は、特定の移動体通信デバイスを識別するために使用するハードウェア識別キーであってもよいし、状態機械150は、プロセッサのモードが機密保護動作モードであるかどうかを判断するために、プロセッサ100が使用する一連の論理要素であってもよい。これらそれぞれの場合において、プロセッサ100内に組み込まれた情報は、偽造を防止するために、または

10

20

30

40

50

競合者によるリバース・エンジニアリングをさらに困難にするために、機密保護状態に維持しなければならない。

#### 【0013】

機密保護キー130は製造中に実施することができるが、機密保護RAM140は、製造プロセスが終了した後でプロセッサ100内で機密保護情報を記憶するための1つの方法である。例えば、プロセッサ100が無線インターネット装置で使用するグラフィックス・プロセッサであると仮定しよう。特定のサービス・プロバイダが専用のグラフィックス圧縮アルゴリズムを有している場合には、プロバイダは、暗号化したアルゴリズムをユーザ・データ入力109を通して、プロセッサ100内にロードすることができる。プロセッサ100は、次に、暗号化ロック110によりこのアルゴリズムを解読し、解読したデータを記憶するために機密保護RAM140に転送する。当業者であれば、図1に示す方法の他に、または代わりに、プロセッサ100に情報を記憶するための適当な方法を本明細書の教示から逸脱することなしに使用することができる理解することができるだろう。

#### 【0014】

ラッチ182、184、186および188は、通常モードおよび試験モードの両方のモードで機能することができる。通常モードの場合には、ラッチ182および184および状態機械150は、プロセッサ100の他の部分が使用できるように感知可能情報を保持する。例えば、ラッチ182は、機密保護キー130にアクセスするために使用する多数のラッチのうちの1つであってもよく、機密保護キー130をプロセッサ100の認証部分（図示せず）に配信することができる。もう1つの例について説明すると、暗号化したソフトウェア・サブルーチンを、ラッチ184を通して機密保護RAM140から中央処理装置に送ることができる。ラッチ182または184が、正式な許可なしでアクセスしてはならない情報を含んでいる場合には、ラッチは読み出感知可能情報を含んでいると言われる。

#### 【0015】

状態機械150は、プロセッサ100を非機密保護モードにするデータを保持することができる。状態機械150内の状態データを、走査モードから抜け出す直前に変更することができる場合には、プロセッサにモードが非機密保護モードであると思い込ませ、それにより機密保護動作が危険にさらされる恐れがある。走査モード動作の後で記憶から保護する必要があるデータを書き感知可能データと呼ぶことができる。他のラッチ（図示せず）は、読み出または書き感知可能情報を含むことができる他の状態機械（図示せず）の出力を記憶するために使用することができる。これらの各例の場合、走査チェーンへのアクセスが保護されていない場合には、データのセキュリティが危険にさらされる恐れがある。

#### 【0016】

試験モードの場合には、ラッチ182、184、186および状態機械150に関連するラッチは、走査チェーン180を介して、プロセッサ100の外部から観察することができる。走査チェーン180へのアクセスは、スキャンイン・ポート181およびスキャンアウト・ポート189を通して行われる。データは、スキャンイン・ポート181を介して、ラッチ182、すなわち走査チェーン180上の第1の走査観察可能なラッチにクロック制御の下で送られる。データが、ラッチ182内にクロック制御の下で送られる度に、ラッチ182のところの出力データは、ラッチ184の入力に送られる。ラッチ182の出力データがラッチ184の入力に送られる度に、出力データ・ラッチ184がラッチ186の入力に送られ、データがチェーンを通してスキャンアウト・ポート189に送られるまで、同じ動作が反復して行われる。例えば、図の走査チェーン180において、論理1が第1のクロック・サイクル中にラッチ182内にクロック制御の下で送られたと仮定しよう。第2のクロック・サイクル中、ラッチ182内に記憶された論理1は、ラッチ184に配信される。第3のクロック・サイクル中、同じ論理1がラッチ186に送られる。このプロセスは、最後に、論理1が読み出されラッチ188に転送され、第4のクロック・サイクル中に、スキャンアウト・ポート189での読み出しが使用できるよう

になるまで継続して行われる。当業者であれば、この簡単な例は単に例示としてのものに過ぎないこと、特定のラッチにシフトしたデータを走査チェーン 180 の残りの部分を通して送る前に、種々の方法で操作することができることを理解することができるだろう。

#### 【0017】

図の実施形態の場合には、読み出しラッチ 188 は、ラッチ 182、184 および状態機械 150 とは対照的に、通常モード中、感知可能データを保持しない。代わりに、読み出しラッチ 188 は、走査コントローラ 120 の制御の下で、ある所定の条件の場合を除いて、走査チェーンからのデータの読み出しを阻止する。図示していないが、読み出しラッチ 188 に類似の方法で制御されているラッチを、任意のデータが走査されるのを阻止するためには、走査チェーン 180 への入力のところで使用できることを理解することができるだろう。また、以下に説明する種々の実施形態のような他の実施形態の場合には、読み出しラッチ 188 を使用しないことも理解することができるだろう。

10

#### 【0018】

走査コントローラ 120 は、走査チェーン 180 へのアクセスを制御し、それによりラッチ 182、184 および状態機械 150 に記憶することができるすべての感知可能情報へのアクセスを制御する。少なくとも 1 つの実施形態の場合には、走査コントローラ 120 は、入力として TEST MODE 信号、SCAN ENABLE 信号、RESET 信号、および EVENT TRIGGER 信号を受信する。これらの入力信号を使用して、走査コントローラ 120 は、SCAN ENABLE (INTERNAL) 信号および SCAN DATA ENABLE 信号を生成し、これらの信号は走査試験を行うことができるよう、ラッチ 182～188 および状態機械 150 を構成するために使用される。例えば、アサートした SCAN ENABLE (INTERNAL) は、各走査ラッチを走査モードにするが、アサートした走査データ・イネーブルは、データをスキャンアウト・ポート 189 に走査できるようにする。走査コントローラ 120 は、また必要に応じて走査チェーン 180 上の素子をリセットするために使用される SCAN EXIT および SCAN RESET 信号を生成する。

20

#### 【0019】

図の実施形態の場合には、走査コントローラ 120 は、走査チェーン 180 に関連する大部分のリセット・シーケンスを制御し、各ラッチ 182～188 および状態機械 150 が、確実に必要に応じて正しくリセットされるようにする。図の実施形態の場合には、感知可能情報を記憶するのに使用しないラッチ 186 および 188 は、感知可能情報を保護するためにリセットする必要がないことに留意されたい。しかし、「ハード」リセット中または他の時点でラッチ 186 および 188 をリセットすることが望ましい場合もあるので、走査コントローラ 120 への RESET 入力が、ラッチ 186、188 をリセットするために供給される。他の実施形態の場合には、RESET 信号を SCAN RESET 信号の他に、例えば、状態機械 150 のような機密保護走査チェーン素子に供給することができる。多くの状況の下で、走査チェーン上の各素子をリセットするのが望ましい場合があるが、非感知性要素は、本明細書の教示から逸脱することなしに、走査コントローラ 120 の出力によりリセットしない状態に保持することができる。

30

#### 【0020】

一実施形態の場合には、RAM リセット 170 は、あるイベントに応じて機密保護 RAM 140 から情報をクリアするために使用される。RAM リセット 170 は、別のリセット状態機械（図示せず）により、走査コントローラ 120 により直接、または他の方法により制御することができる。RAM リセット 170 は、また、機密保護 RAM 140 内に記憶しているデータのクリアに成功したことを示す EVENT TRIGGER 信号を供給することができる。この出力信号は、走査コントローラ 120 に対する EVENT TRIGGER 入力として使用することができる。機密保護 RAM 140 をリセットするに必要な時間がはっきりしない場合には、EVENT TRIGGER 信号を使用すると特に有利である。図の実施形態では RAM リセット 170 が使用されているが、すべての実施形態にとって必要なものではないことを理解することができるだろう。少なくとも一

40

50

実施形態の場合には、SCAN DATA ENABLE信号、SCAN ENABLE(INTERNAL)信号、およびEVENT TRIGGER信号または他の類似の信号の生成が、少なくとも部分的には、走査チェーン180の素子内に含まれているデータが、リセットまたは他の方法により機密保護されているかどうかを示す信号(図1に図示せず)により制御される。このような信号の一実施形態としてはUNSECURE\*信号があるが、これについては後で図5のところで説明する。

#### 【0021】

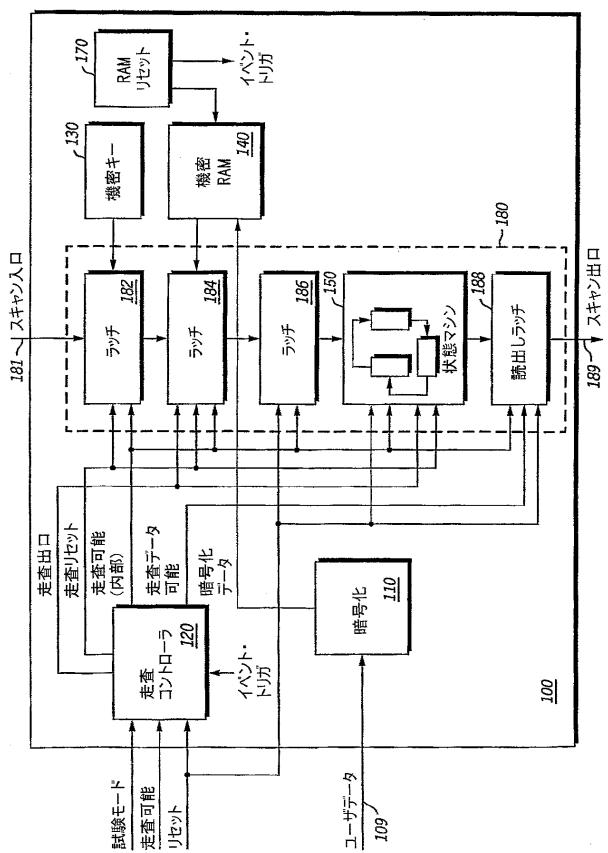

図2を参照しながら、本発明のある実施形態によるプロセッサ100(図1)のようなプロセッサを走査試験するための方法について説明する。この方法はステップ210からスタートする。この場合、プロセッサ100は、通常モード、すなわち非試験モードで動作している。通常モードの場合には、走査チェーン180上の素子は、通常の処理タスクを実行するために使用される。走査チェーン180の素子が通常モードである場合には、これらの素子には、スキャンイン・ポート181またはスキャンアウト・ポート189を介してアクセスすることができない。何故なら、ラッチ182～188および状態機械150は、その走査チェーン・ポートを介して情報を送受信するように構成されていないからである。通常モードの場合、ラッチ182、184および状態機械150は、感知可能データまたは状態情報を含むことができる。そのため、走査チェーン180上の素子が、通常動作中に走査チェーン・アクセスのために動作できるようにする場合には、走査チェーンの素子内に含まれている任意の情報をスキャンアウト・ポート189から読み出すことができ、情報のセキュリティが危険にさらされる恐れがある。

10

20

30

40

#### 【0022】

この方法はステップ220に進む。このステップにおいては、リセットによる試験のために、または所望の入力または入力の組合せに応じて、走査チェーン・ラッチ182、184および状態機械150内の感知可能データを他の方法で修正するために走査チェーンの準備が行われる。例えば、一実施形態の場合には、アサートされたTEST MODE信号およびアサートされたSCAN ENABLE信号を受信すると、走査コントローラ120は、ラッチ182、184および状態機械150のリセット・ピンに直接供給することができるアサートされたSCAN RESET信号を生成する。別の方針としては、適当なハードウェア、ソフトウェアまたはファームウェア・コントローラは、機密保護データがラッチから決して検索されないように、ランダムにまたは他の方法でラッチ182、184および状態機械150内のデータを修正することができる。

#### 【0023】

ステップ230において、走査コントローラは、任意の感知可能データがクリアされたか、または他の方法で修正されたかをチェックする。ステップ230において、走査コントローラ120の入力のところにアサートされたEVENT TRIGGER信号が存在しているかどうかをチェックすることができ、EVENT TRIGGER信号がアサートされない場合には、SCAN ENABLE(INTERNAL)信号もアサートされない。例えば、走査チェーン180にアクセスできるようになる前に、機密保護RAM140をリセットしたい場合には、走査コントローラ120は、機密保護RAM140のリセットがすでに完了したことを示すRAMリセット170からの信号を受信するために待機することができる。他の実施形態の場合には、EVENT TRIGGER信号は必要ない。何故なら、走査チェーン素子内のデータの修正のためのタイミングが決定性であり、ステップ230が、ラッチ182～184をリセットすることをできるようにするには十分な、多数のクロック・サイクルを単に待機するだけで行われるからである。

#### 【0024】

ステップ230において感知可能データが修正されると、走査コントローラ120は、ステップ240において走査チェーン180へのアクセスを許可する。ステップ240中に、当業者にとって周知の通常の走査試験手順を、走査チェーン180の走査観察可能素子の中の任意の素子内にすでに記憶されていた感知可能情報のセキュリティを犠牲にしないで使用することができる。データをスキャンイン・ポート181内まで走査するこ

50

でき、プロセッサ 100 の種々の内部の部分の機能を試験するために、スキャンアウト・ポート 189 から読出しができる。

#### 【0025】

走査試験が終了すると、図 2 の方法はステップ 240 からステップ 250 に進む。ステップ 250 において、走査試験モードから抜け出し、通常モードに再度入るための準備が行われる。一実施形態の場合には、ステップ 250 中は、走査チェーン 180 へのアクセスが阻止され、ラッチ 182、184 および状態機械 150 内の任意のデータが修正またはリセットされる。走査チェーン 180 は、TEST MODE 信号のアサートを解除することにより、通常モードに入ることを走査コントローラ 120 (図 1) に通知することにより阻止することができる。TEST MODE 信号のアサートを解除するとそれに応じて、ラッチ 182、184 および状態機械 150 (図 1)、および感知可能情報の読み出しありは書き込みを含むことができる走査チェーン 180 の任意の他の素子をリセットするために SCAN RESET 信号をアサートすることができる。さらに、走査チェーンの観察可能部分上の素子を、データが走査により読み出されるのを防止するために再構成することができる。通常動作の目的で走査チェーンを準備するために使用した信号については、図 7 のところでさらに詳細に説明する。

#### 【0026】

非試験状態に抜け出る前にプロセッサ 100 の走査観察可能な部分から情報をクリアすることにより、何者かが走査試験中に「シード」情報を走査するのを防止し、次に、シード情報に対してどんな動作が行われたのかを判断するために、プロセッサ 100 の出力を監視するのが防止される。また、この時点で情報をクリアすれば、何者かが、事実はそうでなくとも、例えば、プロセッサに機密保護モードで動作していると「信じ込ませる」ことができる特定の状態に、例えば、状態機械 150 のような状態機械を設定するのが防止される。少なくとも 1 つの実施形態の場合には、ステップ 250 中に生成した SCAN EXIT 信号を、すでに説明したように、データの修正 / リセットの代わりにまたはこれに加えて、現在の状態が正確でないのかもしないことを示すために、種々の状態機械への入力として使用することができる。状態機械は、次に、状態ビットが走査出口でクリアされてなくとも、それ自身の上の既知の状態に遷移することができる。

#### 【0027】

ステップ 260 において、走査コントローラ 120 は、ステップ 230 のところで説明したのと同じかまたは類似の技術により、プロセッサ 100 の任意の必要な走査観察可能な部分からデータがクリアされていることを確認するためにチェックを行う。例えば、一実施形態の場合には、走査コントローラ 120 は、データが走査チェーン 180 内にまたはからシフトするのを許可し、または防止するために使用することができる SCAN DATA ENABLE 信号がアサートされる前に、リセットが終了したことを示すために、EVENT TRIGGER 信号のアサートを待機することができる。図 5 のところでさらに詳細に説明する他の実施形態の場合には、UNSECURE \* 信号のアサートの解除を、EVENT TRIGGER 信号がアサートされた場合に記述することができる。

#### 【0028】

図 5 のところで説明する UNSECURE \* 信号は、通常動作のための走査チェーン 180 上の種々の素子の構成を禁止または許可するために、走査チェーン 180 上の 1 つまたはそれ以上の素子を制御するために使用される。例えば、UNSECURE \* は、データが出力されるのを防止するために、図 1 の SCAN DATA ENABLE 信号のような制御信号の代わりに使用することができる。別の方法としては、UNSECURE \* を、例えば、SCAN DATA ENABLE または SCAN ENABLE (INTERNAL) のような 1 つまたはそれ以上の信号を生成するために使用する論理回路への 1 つの入力として使用することができる。少なくとも 1 つの実施形態の場合には、UNSECURE \* 信号 (図 5) は、SCAN RESET および SCAN EXIT 信号 (図 3 ~ 図 4) 両方の機能を結合する。データおよび / または状態情報がクリアされると、走査コントローラ 120 または他の適当なハードウェア、ソフトウェアまたはファームウェ

10

20

30

40

50

ア素子は、プロセッサ 100 を通常モードに戻すことができる。

【0029】

図 2 の方法の種々のステップは、本発明の教示から逸脱することなしに、同時にまたは異なる順序で実施することができる理解することができるだろう。例えば、ステップ 230 の場合のように、感知可能データが、走査観察可能素子からクリアされたかどうかを確認するためのチェックは、ステップ 230 の後でも実行することができるし、通常モード 210 でも実行することができる。別の方針としては、感知可能データがクリアされたかどうかのチェックは、継続的に行うこともできる。また、種々の設計、マーケティング、コスト、セキュリティまたは他の要因により、図 2 の方法のある部分を、他の部分を除いて実施することもできる。例えば、ステップ 220 の場合のように、試験モードに入る時に、いくつかのラッチ内のデータだけをクリアすることもできるし、ステップ 250 および 260 を、通常モードへ抜け出す前に、機密保護状態機械から状態情報をクリアするためだけに使用することができる。

【0030】

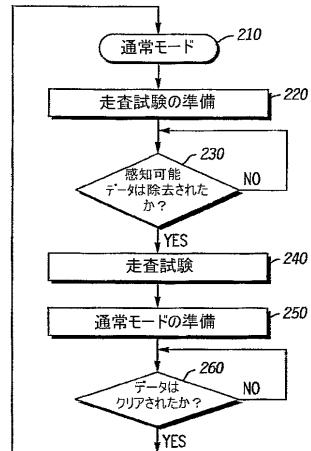

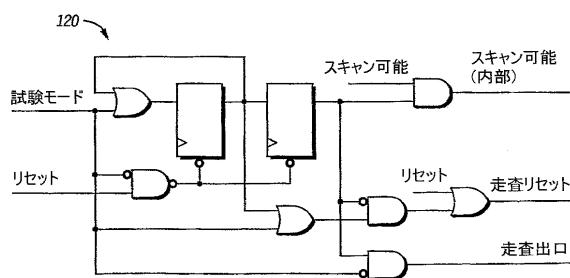

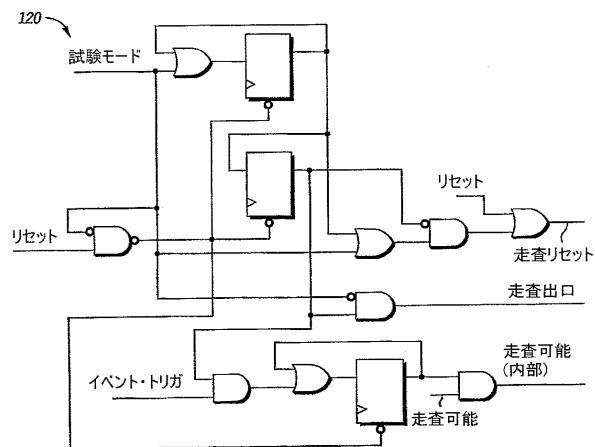

図 3 を参照しながら、走査コントローラ 120 の一部の特定の実施形態について説明する。この図の実施形態の場合には、走査コントローラ 120 の一部は、3 つの入力、すなわち、TEST MODE、RESET および SCAN ENABLE を有する。これら 3 つの入力は、3 つの出力、すなわち、SCAN ENABLE (INTERNAL)、SCAN RESET および SCAN EXIT を生成するために組合わせて使用される。TEST MODE は、もっと簡単に試験できるように回路を機能的に修正するために使用する信号である。この信号は走査試験がスタートする前にアサートされる。SCAN

ENABLE は、データを走査チェーン内にシフトするために使用する信号であり、RESET は、内部データをクリアし、既知の状態に設定し、および / または他の方法で修正すべきであることを示す信号である。SCAN ENABLE (INTERNAL) は、走査チェーンを通してデータをシフトするために、SCAN ENABLE の代わりに、内部回路が使用する SCAN ENABLE をゲート制御したものである。SCAN RESET は、アサートされた場合、走査チェーンの走査観察可能素子から感知可能データをクリアするために使用することができる。SCAN EXIT は、アサートされた場合、TEST MODE 信号が示すように、試験モードのアサートがすでに解除されていて、既知の状態に強制的に状態遷移するために、状態機械への入力として使用することができる信号である。

【0031】

走査コントローラ 120 の一部は、感知可能回路内に情報がクリアされるまで、データを決して走査チェーン内にシフトすることができないようにする。例えば、制御中の回路が試験モードであることを示す TEST MODE 信号がアサートされるまで、データは走査チェーン内にシフトすることはできない。さらに、走査コントローラ 120 の一部は、TEST MODE 信号がアサートされてから 2 つのクロック・サイクルまで、情報が走査チェーン内にシフトするのを遅延する。これにより、確実に、走査コントローラ 120 は、TEST MODE 信号がアサートされた場合に自動的に生成される SCAN RESET パルスを生成するための時間を有する。試験モードから抜け出した場合には、TEST MODE 信号のアサートの解除が示すように、SCAN EXIT 信号がアサートされる。信号のタイミングについては、図 6 および図 7 のところでさらに詳細に説明する。

【0032】

図 4 について説明すると、この図は走査コントローラ 120 の一部のもう 1 つの実施形態である。図の実施形態のロジックは、SCAN ENABLE (INTERNAL) のアサートが、この場合、EVENT TRIGGER 信号のアサートの際に記述される点を除けば、図 3 のところで説明したロジックと本質的に同じものである。図 3 の走査コントローラは、必要な場合には、図 4 の走査コントローラが供給する機能を含むように修正することができることを理解することができるだろう。EVENT TRIGGER 信号

10

20

30

40

50

は、図1のところで説明したように、制御下の回路内の情報が必ず修正、リセット、クリア等されているようにするために、また走査チェーンのすべての素子または特定の素子がクリアされ、設定され、または他の方法で試験モードに入る準備ができているようにするための追加制御として使用される。EVENT TRIGGER信号を受信した場合だけ、出力信号、SCAN ENABLE(INTERNAL)が生成される。SCAN ENABLE(INTERNAL)信号は、データが走査チェーン内にまたはからシフトするのを防止する目的で、入力または出力ゲート、フリップフロップ等の制御を含んでいて、図3のところで説明したように使用することができる。

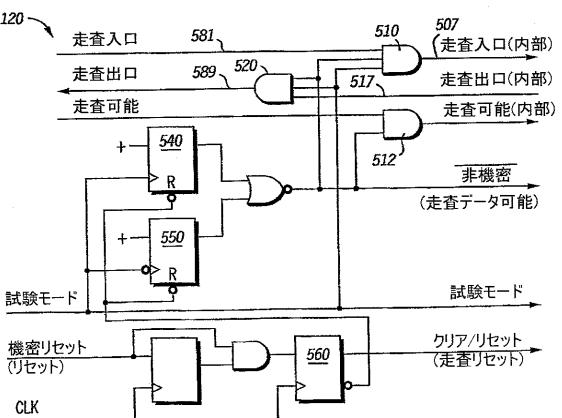

### 【0033】

図5を参照しながら、非同期フリップフロップを使用する走査コントローラ120の一部からなるある実施形態について考察する。図5の実施形態は、図3および図4の実施形態と本質的に同じ効果を達成するために動作するが、若干異なるロジック構成を使用する。さらに、図5は、修正した走査コントローラまたは図1の他の回路の一部とすることができるゲート510および520を含むロジックも示す。

### 【0034】

図5について説明すると、TEST MODE信号は、TEST MODE信号の立上がり縁部が、フリップフロップ540の出力を高レベルにし、TEST MODE信号の立下がり縁部がフリップフロップ550の出力を高レベルにするように、フリップフロップ540のクロック入力およびフリップフロップ550の倒置クロック入力に送られる。

### 【0035】

それ故、TEST MODEの任意の遷移は、フロップへのRESET入力のアサートが解除されると仮定した場合、UNSECURE\*をアサートさせる。UNSECURE\*がアサートされると、SCAN ENABLE INTERNALのアサートが解除され、走査チェーンの動作を防止する。非同期状態にあるフリップフロップ540および550のリセット入力は、フリップフロップ560の倒置出力に接続され、そのためフリップフロップ540および550は、SECURE RESET信号に応じてリセットされる。SECURE RESETは、ユーザの動作に応じて、または他の方法で、システム・リセットの一部として生成することができる。少なくとも1つの実施形態の場合には、SECURE RESETは、図1のRESET信号の特別な例である。フリップフロップ540および550の信号入力は、高い基準電圧に接続しているので、SECURE RESET信号が少なくとも2つのクロック・サイクルの間アサートされると、アクティブ・ローの論理信号、UNSECURE\*のアサートが解除され（すなわち、論理ハイ値になり）、感知可能データが機密保護されていることを示す。

### 【0036】

図の実施形態の場合には、SECURE RESET信号がアサートされる前に、TEST MODEがアサートされると、アサートされたSECURE RESET信号を受信した後で、UNSECURE\*信号のアサートが解除され、感知可能データが機密保護されていることを示し、SECURE RESET信号のアサートが解除された後でも、UNSECURE\*はアサートされないままになる。しかし、TEST MODE信号が、SECURE RESET信号のアサートが解除された後で状態を変えると、UNSECURE\*信号がアサートされ、走査チェーン内のデータは機密保護されないことを示す。UNSECURE\*信号の機能の理解を容易にするために、以下の節においてその例について考察する。

### 【0037】

下記の例について考察する場合、SCAN IN(INTERNAL)507、SCAN OUT(INTERNAL)517、およびSCAN ENABLE(INTERNAL)は、SCAN IN181、SCAN OUT189およびSCAN ENABLE(図1)をゲート制御したものであり、これらすべては走査チェーン180の外部アクセスを制限するために使用することができることに留意されたい。SCAN IN(INTERNAL)およびSCAN OUT(INTERNAL)は、図1にははっきりと示

10

20

30

40

50

してないが、実施した場合、図1のSCAN INおよびSCAN OUT信号をゲート制御することに留意されたい。例えば、走査チェーン180(図1)のモードが、現在走査試験モードになっていて、TEST MODE信号はアサートされ、UNSECURE\*信号はアサート解除されていると仮定しよう。走査試験モードから抜け出すために、TEST MODE信号のアサートが解除される。フリップフロップ550は、TEST MODE信号の立上がり縁部によりトリガされ、それによりUNSECURE\*がアサートされる。アサートされたUNSECURE\*信号は、走査試験モードから抜け出していることを示し、また走査チェーン180(図1)内のデータをクリアする必要があることを示す。図の実施形態の場合には、UNSECURE\*は、データSCAN IN581が、ANDゲート510を通過し、走査チェーン180(図1)内に走査することができるSCAN IN(INTERNAL)データ507になるのを阻止するための、またデータSCAN OUT(INTERNAL)517が走査チェーン180(図1)から読み出されるのを阻止するための論理ゲート510への入力として使用される。さらに、UNSECURE\*は、SCAN ENABLE(INTERNAL)が、データが機密保護されていない場合、SCAN ENABLEに応じてアサートされるのを阻止するための論理ゲート512への入力として使用される。これらのことの任意のものを、データがデバイス100から走査されるのを防止するために使用することができる。

10

20

30

40

#### 【0038】

論理ゲート510、512および520への入力として使用されるほかに、UNSECURE\*信号は、例えば、SECURE RESET信号をアサートするために、または他の方法で走査チェーン内のデータをクリアする目的で、中央プロセッサに通知するために使用することができる。UNSECURE\*信号は、また、種々のファームウェアまたはソフトウェアが走査チェーンの状態を判断するために参照することができる機密保護/非機密保護レジスタ(図示せず)を設定するためにも使用することができる。別のこととしては、UNSECURE\*信号を、図1の1つまたはそれ以上のラッチまたは状態機械の構成を制御するための直接入力として使用することができる。

#### 【0039】

最後に、図5の実施形態は、走査チェーンの走査観察可能素子内に記憶されているデータを修正する目的で、アサートされたCLEAR/RESET信号を生成するために、SECURE RESET信号を使用する。CLEAR/RESETは、図1のSCAN RESETに類似しているものでもよいことに留意されたい。SECURE RESET信号は、走査コントローラ120を使用するプロセッサ内の他の回路により自動的に生成することができるか、またはシステムを、オペレータがリセットを物理的にスタートした後でだけ、SECURE RESET信号を生成するように構成することができる。

30

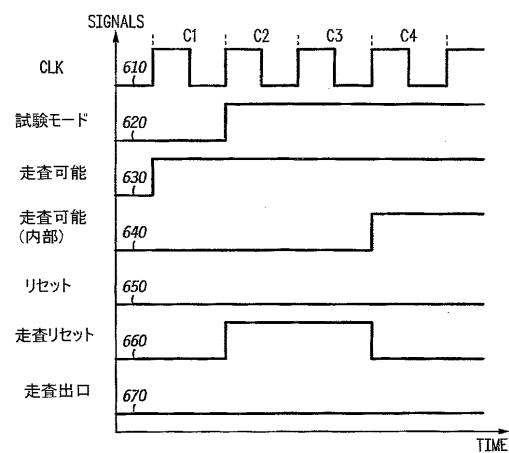

#### 【0040】

図3および図6を参照しながら、走査コントローラの一実施形態で使用する信号間のタイミングの関係について説明する。図6は、試験モードに入った場合のタイミングの関係である。以下の説明のすべてのタイミングは、クロック610を基準にしていて、特にクロック・サイクルC1の第1の立上がり縁部を基準にしている。クロック・サイクルC1がスタートする前に、すべての信号のアサートが解除され、動作モードが通常モード、すなわち、非試験モードであることを示す。クロック・サイクルC1の前の半分の間に、ユーザはSCAN ENABLE630をアサートすることにより走査ができるようにしようとする。走査コントローラ120を使用しているプロセッサは、依然として通常モードで動作しているので、SCAN ENABLE630をアサートしても、SCAN ENABLE(INTERNAL)640は高レベルにならない。

40

#### 【0041】

しかし、第2のクロック・サイクルC2の第1の立上がり縁部のところで、TEST MODE620がアサートされる。SCAN RESET660は、TEST MODE620がアサートされると高レベルになる。SCAN RESET660は、走査チェー

50

ン上の走査観察可能素子の修正、リセットまたはクリアをトリガするパルスである(図1参照)。クロック・サイクルC4の第1の立上がり縁部のところで、TEST MODE 620の後の2つの立ち上がりクロック縁部がアサートされ、SCAN ENABLE 630およびTEST MODE 620の両方が高レベルになっているので、SCAN ENABLE(INTERNAL)640が高レベルになる。2つのクロック・サイクル中、SCAN ENABLE(INTERNAL)640のアサートを遅らせることにより、走査チェーンへのアクセスが許可される前にリセットを行うことができる。それにより、試験モードになった場合、感知可能情報を保護する。RESET 650およびSCAN EXIT 670は、試験モード中にはアサートされないことに留意されたい。サイクルC4のところでSCAN ENABLE(INTERNAL)がアサートされてから後しばらく経過した後で、サイクルC1のところでアサートされているTEST MODE 620に応じて、内部プロセッサの構成要素の試験を容易にするために、走査チェーン内に10およびからデータをシフトすることができるが、この時点ですべての機密保護情報はクリアされる。

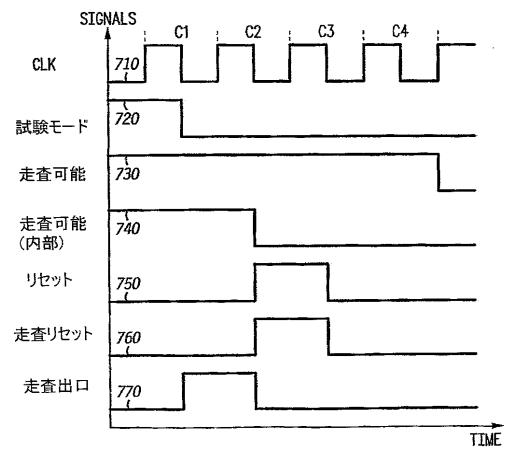

#### 【0042】

図3および図7を参照しながら、走査コントローラの一実施形態の信号間のタイミングの関係、特に試験モードから抜け出した場合のタイミングの関係についてさらに詳細に説明する。図7の信号のタイミングの関係について、クロック・サイクルC1の第1の立上がり縁部を参照しながら説明する。クロック・サイクルC1のスタートのところで、TEST MODE 720、SCAN ENABLE 730およびSCAN ENABLE(INTERNAL)740がアサートされ、一方、すべての他の信号が取り消される。このことは、感知可能データの漏洩を心配しないで、走査チェーン内におよびからデータを自由にシフトすることができる試験モードに対応する。クロック・サイクルC1の立下がり縁部のところで、TEST MODE 720が取り消され、試験サイクルの終了および通常モードへの移行が通知される。TEST MODE 720が取り消されるのと同時に、最後にRESET 750がアサートされて以来試験モードに入っていて、そのモードから抜け出したことを通知するためにSCAN EXIT 770がアサートされる。SCAN EXIT 770は、既知の状態に強制的に状態遷移するための状態機械への入力として使用することができ、ラッチの動作状態を制御するためのラッチへの入力として使用することができ、走査チェーン内のデータを通常動作で使用することができる前にリセットする必要があることを表示するためにプロセッサに結合することができ、または走査試験モードから抜け出したことを表示するために種々の他の類似の方法で使用することができる。30

#### 【0043】

第2のクロック・サイクルC2の立下がり縁部のところで、RESET 750がアサートされ、それによりSCAN RESET 760がアサートされる。SCAN RESET 760は、少なくとも1つの実施形態の場合には、走査チェーンを形成しているデータ・ラッチおよび状態機械へのリセット入力として使用される。このように使用された場合には、SCAN RESET 760は、走査試験モードから抜け出した場合に、走査チェーンから感知可能データをクリアする。SCAN ENABLE(INTERNAL)740は、SCAN EXIT 770が取り消されるのと同時に低レベルになり、それにより、走査試験モードから抜け出した後で、走査チェーンからデータが走査されるのを防止する。最後に、SCAN ENABLE 730のアサートが解除され、そのため追加のデータを走査チェーン内に走査することができない。現在タイミングを考察している走査コントローラ120の実施形態の場合には、SCAN RESET 760は、TEST MODE 720が取り消された場合、自動的にはアサートされないことに留意されたい。その代わりに、RESET 750を、ユーザの動作または他の方法に応じてアサートしなければならないし、それにより、通常モードに入る前に走査チェーンをクリアするためにSCAN RESET 760がアサートされる。他の実施形態は、試験モードから抜け出した場合に、RESET 750に類似のリセット・パルスを自動的に生成することができる40

10

20

30

40

50

。

## 【0044】

要するに、上記説明をよく読めば、走査チェーンへのアクセスの許可の前および後で、プロセッサの走査観察可能部分内に記憶している情報を修正することにより、本明細書の教示により組立てた走査コントローラを使用するプロセッサは、試験性能を犠牲にしないでデータのセキュリティを強化することができることは明らかである。データのセキュリティが強化されると、自称模倣者がデータにアクセスするのを制限することにより感知可能データを簡単に利用できないようにすることができる。同時に、試験性能の向上により、製造コストを安くし、市場への製品の導入をスピードアップすることができる。

## 【0045】

図面の上記詳細な説明において、本明細書の一部を構成していて、本発明を実行することができる例示としての特定の実施形態を示す添付の図面を参照した。これらの実施形態については、当業者が本発明を実行できるようにするために十分詳細に説明してあるが、他の実施形態も使用できること、また本発明の精神および範囲から逸脱することなしに、論理的、機械的、化学的、および電気的変更を行うことができるこ理解されたい。

## 【0046】

当業者が本発明を実行できるようにするために必要ではない詳細な説明を避けるために、当業者であれば周知のいくつかの情報を省略することができる。さらに、当業者であれば、本発明の教示を含む多くの他の変形した実施形態を容易に組立てることができるだろう。それ故、本発明の説明は、本明細書に記載した特定の形状に限定されるものではなく、それどころかこののような代替物、変形したものおよび等価物を、当然本発明の精神および範囲内に含まれるものとしてカバーする。それ故、上記の詳細な説明は、本発明を制限するものではなく、本発明の開示の範囲は添付の特許請求の範囲によってだけ定義される。

## 【図面の簡単な説明】

## 【0047】

【図1】本発明のある実施形態による走査コントローラを使用するプロセッサのブロック図。

【図2】本発明のある実施形態によるプロセッサの走査観察可能部分にアクセスできるようになる前に、感知可能データをクリアすることを含む走査試験方法を示すフローチャート。

【図3】本発明の種々の実施形態による走査チェーンへのアクセスを制御するための走査コントローラを示す論理図。

【図4】本発明の種々の実施形態による走査チェーンへのアクセスを制御するための走査コントローラを示す論理図。

【図5】本発明の種々の実施形態による走査チェーンへのアクセスを制御するための走査コントローラを示す論理図。

【図6】試験モードへ入る行動に関連する、図3に示す論理図のタイミングを示す例示としてのタイミング図。

【図7】試験モードから抜け出す行動に関連する、図3の論理図のタイミングを示す例示としてのタイミング図。

10

20

30

40

【 図 1 】

【 図 2 】

〔 3 〕

【 図 4 】

【 四 5 】

【図6】

【図7】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                       |                                                                                                                                                                             | Int'l Application No<br>PCT/US 03/11399                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 G01R31/3185 G06F1/00                                                                                                                                                                                 |                                                                                                                                                                             |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                 |                                                                                                                                                                             |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G01R G06F                                                                                                                |                                                                                                                                                                             |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                     |                                                                                                                                                                             |                                                                                |

| Electronic data base consulted during the International search (name of data base and, where practical, search terms used)<br>EPO-Internal, IBM-TDB, INSPEC                                                                                       |                                                                                                                                                                             |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                            |                                                                                                                                                                             |                                                                                |

| Category *                                                                                                                                                                                                                                        | Citation of document, with indication, where appropriate, of the relevant passages                                                                                          | Relevant to claim No.                                                          |

| A                                                                                                                                                                                                                                                 | US 5 898 776 A (CHAN ANDREW K ET AL)<br>27 April 1999 (1999-04-27)<br>abstract; figures 3,5<br>column 5, line 35 -column 7, line 51<br>column 1, line 12 -column 2, line 41 | 1-10                                                                           |

| A                                                                                                                                                                                                                                                 | US 5 530 749 A (ZAJAC MYRON W ET AL)<br>25 June 1996 (1996-06-25)<br>abstract; figure 3<br>column 2, line 11 ~ line 38                                                      | 1-10                                                                           |

| <input type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                               |                                                                                                                                                                             | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents :                                                                                                                                                                                                         |                                                                                                                                                                             |                                                                                |

| *A* document defining the general state of the art which is not considered to be of particular relevance                                                                                                                                          |                                                                                                                                                                             |                                                                                |

| *E* earlier document but published on or after the International filing date                                                                                                                                                                      |                                                                                                                                                                             |                                                                                |

| *L* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)                                                                          |                                                                                                                                                                             |                                                                                |

| *O* document referring to an oral disclosure, use, exhibition or other means                                                                                                                                                                      |                                                                                                                                                                             |                                                                                |

| *P* document published prior to the International filing date but later than the priority date claimed                                                                                                                                            |                                                                                                                                                                             |                                                                                |

| *T* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                               |                                                                                                                                                                             |                                                                                |

| *X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                      |                                                                                                                                                                             |                                                                                |

| *Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art. |                                                                                                                                                                             |                                                                                |

| *Z* document member of the same patent family                                                                                                                                                                                                     |                                                                                                                                                                             |                                                                                |

| Date of the actual completion of the International search<br><br>25 August 2003                                                                                                                                                                   |                                                                                                                                                                             | Date of mailing of the International search report<br><br>01/09/2003           |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax (+31-70) 340-3016                                                             |                                                                                                                                                                             | Authorized officer<br><br>Böhm-Pélissier, A                                    |

| INTERNATIONAL SEARCH REPORT            |                  |                         |         | Interr           | Application No |

|----------------------------------------|------------------|-------------------------|---------|------------------|----------------|

|                                        |                  |                         |         | PCT/US 03/11399  |                |

| Patent document cited in search report | Publication date | Patent family member(s) |         | Publication date |                |

| US 5898776                             | A 27-04-1999     | NONE                    |         |                  |                |

| US 5530749                             | A 25-06-1996     | US                      | 5530753 | A                | 25-06-1996     |

## フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NI,NO,NZ,OM,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 スピッタル、ジョン イー. ジュニア

アメリカ合衆国 85355 アリゾナ州 ウォデル エヌ. ワンハンドレッドセブンティセブン

ス アベニュー 7601

(72)発明者 ラツ、ジョナサン

カナダ国 N2M 5E7 オンタリオ州 キッチナー ベルモント アベニュー 565 ナン

バー24

(72)発明者 ケース、ローレンス

アメリカ合衆国 85268 アリゾナ州 ファウンテン ヒルズ ノース スカイリッジ レー

ン 16433

(72)発明者 ハーディ、ダグラス

アメリカ合衆国 85259 アリゾナ州 スコットsdale イー. ローレル レーン 1070

5

(72)発明者 レッドマン、マーク

アメリカ合衆国 85296 アリゾナ州 ギルバート イー. アベニダ シエラ マドレ 73

4

(72)発明者 シュミット、グレゴリー

アメリカ合衆国 85226 アリゾナ州 チャンドラー ダブリュ. シカゴ ストリート 53

50

(72)発明者 トゥーゲンバーグ、スティーブン

アメリカ合衆国 85258 アリゾナ州 スコットsdale エヌ. セブンティセブンス ストリ

ート 10210

(72)発明者 フィッツシモンズ、マイケル ディ.

アメリカ合衆国 78731 テキサス州 オースティン エヌ. キャピタル オブ テキサス

ハイウェイ 7700 ナンバー723

(72)発明者 カーダー、ダレル エル.

アメリカ合衆国 78620 テキサス州 ドリッピング スプリングス ロッキー クリーク

301

F ターム(参考) 2G132 AA03 AB01 AC14 AK14 AK15 AK23 AL11

5B048 AA11 CC18 FF01

5B076 FA00 FA05 FC08 FD02 FD03