(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5017773号

(P5017773)

(45) 発行日 平成24年9月5日(2012.9.5)

(24) 登録日 平成24年6月22日(2012.6.22)

(51) Int.Cl.

F 1

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

GO9G 3/30 J

GO9G 3/20 611H

GO9G 3/20 624B

GO9G 3/20 641D

GO9G 3/20 642A

請求項の数 11 (全 22 頁) 最終頁に続く

(21) 出願番号

特願2004-270786 (P2004-270786)

(22) 出願日

平成16年9月17日 (2004.9.17)

(65) 公開番号

特開2006-84899 (P2006-84899A)

(43) 公開日

平成18年3月30日 (2006.3.30)

審査請求日

平成19年8月20日 (2007.8.20)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100118290

弁理士 吉井 正明

(74) 代理人 100094363

弁理士 山本 幸久

(74) 代理人 100120640

弁理士 森 幸一

(72) 発明者 山下 淳一

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】 画素回路及び表示装置とこれらの駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

制御パルスを供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含み、

サンプリングトランジスタは、1水平期間をサンプリング期間として、該サンプリング期間に走査線から供給される制御パルスに応じ導通して信号線から供給された映像信号をサンプリングし、

容量部は、サンプリングされた映像信号に応じた入力電位を保持し、

ドライブトランジスタは、容量部に保持された入力電位に応じて所定の発光期間に出力電流を供給し、

発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する画素回路であって、

アクティブ期間が1水平期間よりも短く設定された、補正期間を規定するための補正用制御パルスと、補正期間内において発光素子を発光から非発光に切り換えるためのドライブ用制御パルスとが入力されることによって、1水平期間より短い補正期間内にリセット期間と検出期間とが設けられ、出力電流に対するドライブトランジスタのキャリア移動度及び閾電圧の影響を両方同時に補正する動作を、サンプリング期間に先行して設定されたリセット期間及び検出期間からなる1水平期間よりも短い補正期間に行なう補正手段を備えており、

10

20

補正手段は、ドライブトランジスタ及び容量部に接続されており、リセット期間で、補正手段は容量部に通電して容量部が保持していた電位をリセットし、検出期間で、通電を遮断しドライブトランジスタに過渡電流が流れている間に、ドライブトランジスタのソースとゲート間に現れる電位差を補正手段が検出し、補正手段が検出した電位差に応じた電位を容量部が保持し、容量部が保持した電位は、ドライブトランジスタの出力電流に対する閾電圧の影響を減殺する分とキャリア移動度の影響を減殺する分の両方を含み、補正手段は、リセットが解除された後にドライブトランジスタがカットオフに到達するまでの時間幅よりも短い時間幅に検出期間が設定されることで、出力電流に対するキャリア移動度及び閾電圧の影響を両方同時に補正可能である

10 画素回路。

**【請求項 2】**

第1のクロックに同期するアクティブ期間が1水平期間であるパルスと、時間幅を制限するための制限用パルスとの論理積をとることにより補正用制御パルスが設定され、

第1のクロックと同一周期である第2のクロックに同期して、発光素子の発光と非発光を制御するドライブ用制御パルスが設定され、

検出期間は、補正用制御パルスのアクティブ期間とドライブ用制御パルスの非発光期間のオーバーラップ部分で規定され、

オーバーラップ部分は、第1のクロックと第2のクロックの位相の調整により設定される

請求項1に記載の画素回路。

**【請求項 3】**

検出期間は、第1のクロック及び第2のクロックの半周期未満の分解能で調整可能である

請求項2に記載の画素回路。

**【請求項 4】**

補正手段は、リセット期間の時間幅が制限されており、通電によりリセット期間中ドライブトランジスタを通じて発光素子に流れる貫通電流を抑制し、以て、貫通電流に起因する発光素子の異常発光を抑制する

請求項1乃至請求項3の何れか1項に記載の画素回路。

**【請求項 5】**

ドライブトランジスタはPチャネル型のトランジスタから成り、

容量部に保持された電位のうち、キャリア移動度の影響を減殺する分による発光素子の発光を防ぐため、黒表示時における映像信号の電位レベルを、ドライブトランジスタの一端に印加される所定の電源電位よりも高く設定した

請求項1乃至請求項4の何れか1項に記載の画素回路。

**【請求項 6】**

画素アレイ部とスキャナ部と信号部とを含み、

画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、

信号部は、信号線に映像信号を供給し、

スキャナ部は、走査線に制御パルスを供給して順次行ごとに画素を走査し、

各画素は、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含み、

サンプリングトランジスタは、1水平期間をサンプリング期間として、該サンプリング期間に走査線から供給されるサンプリング用制御パルスに応じ導通して信号線から供給された映像信号をサンプリングし、

容量部は、サンプリングされた映像信号に応じた入力電位を保持し、

ドライブトランジスタは、容量部に保持された入力電位に応じて所定の発光期間に出力

10

20

30

40

50

電流を供給し、

発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する表示装置であって、

各画素は、アクティブ期間が1水平期間よりも短く設定された、補正期間を規定するための補正用制御パルスと、補正期間内において発光素子を発光から非発光に切り換えるためのドライブ用制御パルスとが入力されることによって、1水平期間より短い補正期間内にリセット期間と検出期間とが設けられ、出力電流に対するドライブトランジスタのキャリア移動度及び閾電圧の影響を両方同時に補正する動作を、サンプリング期間に先行して設定されたリセット期間及び検出期間からなる1水平期間よりも短い補正期間に行なう補正手段を備えており、

10

補正手段は、ドライブトランジスタ及び容量部に接続されており、

リセット期間で、補正手段は容量部に通電して容量部が保持していた電位をリセットし

検出期間で、通電を遮断しドライブトランジスタに過渡電流が流れている間に、ドライブトランジスタのソースとゲート間に現れる電位差を補正手段が検出し、

補正手段が検出した電位差に応じた電位を容量部が保持し、

容量部が保持した電位は、ドライブトランジスタの出力電流に対する閾電圧の影響を減殺する分とキャリア移動度の影響を減殺する分の両方を含み、

スキャナ部は、少なくともライトスキャナとドライブスキャナと補正用スキャナとを含み、

20

ライトスキャナは、サンプリング期間にサンプリング用制御パルスを走査線に供給し、補正用スキャナは、補正期間を規定する補正用制御パルスを走査線に供給し、

ドライブスキャナは、補正期間内でリセット期間と検出期間を区切るとともに、発光期間とこれ以外の非発光期間を区切るためのドライブ用制御パルスを走査線に供給し、

補正手段は、リセットが解除された後にドライブトランジスタがカットオフに到達するまでの時間幅よりも短い時間幅に検出期間が設定されることで、出力電流に対するキャリア移動度及び閾電圧の影響を両方同時に補正可能である

表示装置。

#### 【請求項 7】

補正用スキャナは第1のクロックに同期して動作し、第1のクロックに同期するアクティブ期間が1水平期間であるパルスと、時間幅を制限するための制限用パルスとの論理積をとることにより1水平期間ごと補正用制御パルスを順次各行の走査線に供給し、

ドライブスキャナは、第2のクロックに同期して動作し、1水平期間ごとドライブ用制御パルスを順次各行の走査線に供給し、

第2のクロックは、第1のクロックに対して周期が同じで位相が異なっており、以て、補正用制御パルス及びドライブ用制御パルスによって規定される検出期間を1水平期間よりも短い時間幅に設定することで、出力電流に対するキャリア移動度及び閾電圧の影響を両方同時に補正可能にした

請求項 6 に記載の表示装置。

#### 【請求項 8】

スキャナ部は、第1のクロックと第2のクロックの位相差を調整可能であり、位相差の調整により検出期間の時間幅を設定することで、出力電流に対するキャリア移動度及び閾電圧の影響を両方同時に補正可能である

請求項 7 に記載の表示装置。

#### 【請求項 9】

検出期間は、補正用制御パルスのアクティブ期間とドライブ用制御パルスの非発光期間のオーバーラップ部分で規定され、

オーバーラップ部分は、第1のクロックと第2のクロックの位相の調整により設定される

請求項 8 に記載の表示装置。

40

50

**【請求項 10】**

補正用スキャナは補正用制御パルスの時間幅を制限する手段を備えており、これによりリセット期間の時間幅を短縮化して通電によりリセット期間中ドライブトランジスタを通じて発光素子に流れる貫通電流を抑制し、以て、貫通電流に起因する発光素子の異常発光を抑制する

請求項 6 乃至 請求項 9 の何れか 1 項に記載の表示装置。

**【請求項 11】**

ドライブトランジスタは P チャネル型のトランジスタから成り、容量部に保持された電位のうち、キャリア移動度の影響を減殺する分による発光素子の発光を防ぐため、信号部は、黒表示時における映像信号の電位レベルを、ドライブトランジスタの一端に印加される所定の電源電位よりも高く設定した

請求項 6 乃至 請求項 10 の何れか 1 項に記載の表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、画素毎に配した発光素子を電流駆動する画素回路に関する。又この画素回路がマトリクス状（行列状）に配列された表示装置であって、特に各画素回路内に設けた絶縁ゲート型電界効果トランジスタによって、有機 E L などの発光素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の表示装置に関する。

**【背景技術】****【0002】**

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機 E L 素子を画素に用いた有機 E L ディスプレイなどにおいても同様であるが、液晶画素と異なり有機 E L 素子は自発光素子である。その為、有機 E L ディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。又、各発光素子の輝度レベル（階調）はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。

**【0003】**

有機 E L ディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式がある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子（一般には薄膜トランジスタ、 TFT）によって制御するものであり、以下の特許文献に記載がある。

【特許文献 1】特開 2003 - 255856

【特許文献 2】特開 2003 - 271095

【特許文献 3】特開 2004 - 133240

【特許文献 4】特開 2004 - 029791

【特許文献 5】特開 2004 - 093682

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

従来の画素回路は、制御パルスを供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含む。サンプリングトランジスタは、走査線から供給される制御パルスに応じ導通して信号線から供給された映像信号をサンプリングする。容量部は、サンプリングされた映像信号に応じた入力電位を保持する。ドライブトランジスタは、容量部に保持された入力電位に応じて所定の発光期間に出力電流を供給する。尚一般に

10

20

30

40

50

、出力電流はドライブトランジスタのチャネル領域のキャリア移動度及び閾電圧に対して依存性を有する。発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する。

【0005】

ドライブトランジスタは、容量部に保持された入力電位をゲートに受けてソース／ドレイン間に出力電流を流し、発光素子に通電する。一般に発光素子の発光輝度は通電量に比例している。更にドライブトランジスタの出力電流供給量はゲート電圧すなわち容量部に書き込まれた入力電位によって制御される。従来の画素回路は、ドライブトランジスタのゲートに印加される入力電圧を入力映像信号に応じて変化させることで、発光素子に供給する電流量を制御している。

10

【0006】

ここでドライブトランジスタの動作特性は以下の式で表わされる。

$$I_{ds} = (1/2) \mu (W/L) C_o x (V_{gs} - V_{th})^2 \dots \text{式1}$$

このトランジスタ特性式1において、 $I_{ds}$ はソース／ドレイン間に流れるドレン電流を表わしており、画素回路では発光素子に供給される出力電流である。 $V_{gs}$ はソースを基準としてゲートに印加されるゲート印加電圧を表わしており、画素回路では上述した入力電位である。 $V_{th}$ はトランジスタの閾電圧である。又 $\mu$ はトランジスタのチャネルを構成する半導体薄膜の移動度を表わしている。その他 $W$ はチャネル幅を表わし、 $L$ はチャネル長を表わし、 $C_o x$ はゲート容量を表わしている。このトランジスタ特性式1から明らかな様に、薄膜トランジスタは飽和領域で動作する時、ゲート電圧 $V_{gs}$ が閾電圧 $V_{th}$ を超えて大きくなると、オン状態となってドレン電流 $I_{ds}$ が流れる。原理的に見ると上記のトランジスタ特性式1が示す様に、ゲート電圧 $V_{gs}$ が一定であれば常に同じ量のドレン電流 $I_{ds}$ が発光素子に供給される。従って、画面を構成する各画素に全て同一のレベルの入力信号を供給すれば、全画素が同一輝度で発光し、画面の一様性（ユニフォーミティ）が得られるはずである。

20

【0007】

しかしながら実際には、ポリシリコンなどの半導体薄膜で構成された薄膜トランジスタ（TFT）は、個々のデバイス特性にばらつきがある。特に、閾電圧 $V_{th}$ は一定ではなく、各画素毎にばらつきがある。前述のトランジスタ特性式1から明らかな様に、各ドライブトランジスタの閾電圧 $V_{th}$ がばらつくと、ゲート印加電圧 $V_{gs}$ が一定であっても、ドレン電流 $I_{ds}$ にばらつきが生じ、画素毎に輝度がばらついてしまう為、画面のユニフォーミティを損なう。従来からドライブトランジスタの閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路が開発されており、例えば前記の特許文献3に開示がある。

30

【0008】

閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路は、ある程度画面のユニフォーミティを改善することが可能である。しかしながら、ポリシリコン薄膜トランジスタの特性は、閾電圧ばかりでなく移動度 $\mu$ も素子毎にばらつきがある。前述のトランジスタ特性式1から明らかな様に、移動度 $\mu$ がばらつくと、ゲート印加電圧 $V_{gs}$ が一定であってもドレン電流 $I_{ds}$ にばらつきが出てしまう。この結果発光輝度が画素毎に変化する為、画面のユニフォーミティを損なうという課題がある。

40

【課題を解決するための手段】

【0009】

上述した従来の技術の課題に鑑み、本発明は閾電圧と移動度の影響を両方同時に補正し、以ってドライブトランジスタが供給するドレン電流（出力電流）のばらつきを補償可能な画素回路及び表示装置及びこれらの駆動方法を提供することを目的とする。係る目的を達成する為に以下の手段を講じた。即ち本発明は、制御パルスを供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御パルスに応じ導通し

50

て信号線から供給された映像信号をサンプリングし、前記容量部は、サンプリングされた映像信号に応じた入力電位を保持し、前記ドライブトランジスタは、該容量部に保持された入力電位に応じて所定の発光期間に出力電流を供給し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画素回路において、該出力電流に対する該ドライブトランジスタのキャリア移動度及び閾電圧の影響を両方同時に補正するための補正手段を備えており、前記補正手段は該ドライブトランジスタ及び容量部に接続しており、該サンプリング期間に先行して設定された補正期間に動作し、該補正期間はリセット期間と検出期間に分かれており、前記リセット期間で、該補正手段は該容量部に通電して該容量部が保持していた電位をリセットし、前記検出期間で、該補正手段は該通電を遮断し該ドライブトランジスタに過渡電流が流れている間に、該ドライブトランジスタのソースとゲート間に現れる電位差を検出し、前記容量部は該検出した電位差に応じた電位を保持し、該保持した電位は該ドライブトランジスタの出力電流に対する閾電圧の影響を減殺する分とキャリア移動度の影響を減殺する分の両方を含むことを特徴とする。

## 【0010】

好ましくは前記補正手段は、該検出期間を該サンプリング期間よりも短い時間幅に設定することで、該出力電流に対するキャリア移動度及び閾電圧の影響を両方同時に補正可能にする。又前記補正手段は、該リセット期間の時間幅が制限されており、該通電によりリセット期間中該ドライブトランジスタを通じて該発光素子に流れる貫通電流を抑制し、以って該貫通電流に起因する該発光素子の異常発光を抑制する。又該容量部に保持された電位のうち、該キャリア移動度の影響を減殺する分による発光素子の発光を防ぐため、黒表示時における映像信号の電位レベルを所定の電源電位よりも高く設定する。

## 【0011】

本発明は又、画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は、該信号線に映像信号を供給し、前記スキャナ部は、該走査線に制御パルスを供給して順次行ごとに画素を走査し、各画素は、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給されるサンプリング用制御パルスに応じ導通して信号線から供給された映像信号をサンプリングし、前記容量部は、サンプリングされた映像信号に応じた入力電位を保持し、前記ドライブトランジスタは、該容量部に保持された入力電位に応じて所定の発光期間に出力電流を供給し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する表示装置において、各画素は、該出力電流に対する該ドライブトランジスタのキャリア移動度及び閾電圧の影響を両方同時に補正するための補正手段を備えており、前記補正手段は該ドライブトランジスタ及び容量部に接続しており、該サンプリング期間に先行して設定された補正期間に動作し、該補正期間はリセット期間と検出期間に分かれており、前記リセット期間で、該補正手段は該容量部に通電して該容量部が保持していた電位をリセットし、前記検出期間で、該補正手段は該通電を遮断し該ドライブトランジスタに過渡電流が流れている間に、該ドライブトランジスタのソースとゲート間に現れる電位差を検出し、前記容量部は該検出した電位差に応じた電位を保持し、該保持した電位は該ドライブトランジスタの出力電流に対する閾電圧の影響を減殺する分とキャリア移動度の影響を減殺する分の両方を含み、前記スキャナ部は、少なくともライトスキャナとドライブスキャナと補正用スキャナとを含み、前記ライトスキャナは、該サンプリング期間に該サンプリング用制御パルスを走査線に供給し、前記補正用スキャナは、該補正期間を規定する補正用制御パルスを走査線に供給し、前記ドライブスキャナは、該補正期間内にリセット期間と検出期間を区切るとともに、発光期間とこれ以外の非発光期間を区切るためのドライブ用制御パルスを走査線に供給することを特徴とする。

## 【0012】

好ましくは、前記補正用スキャナは第1のクロックに同期して動作し、1水平期間ごと

10

20

30

40

50

該補正用制御パルスを順次各行の走査線に供給し、前記ドライブスキャナは、第2のクロックに同期して動作し、1水平期間ごと該ドライブ用制御パルスを順次各行の走査線に供給し、前記第2のクロックは、第1のクロックに対して周期が同じで位相が異なっており、以って該補正用制御パルス及び該ドライブ用制御パルスによって規定される該検出期間を該1水平期間よりも短い時間幅に設定することで、該出力電流に対するキャリア移動度及び閾電圧の影響を両方同時に補正可能にする。又前記スキャナ部は、該第1のクロックと第2のクロックの位相差を可変調整可能であり、該検出期間の時間幅を最適に設定し、以って該出力電流に対するキャリア移動度及び閾電圧の影響を両方同時に補正可能にする。又前記補正用スキャナは該補正用制御パルスの時間幅を制限する手段を備えており、これにより該リセット期間の時間幅を短縮化して該通電によりリセット期間中該ドライブトランジスタを通じて該発光素子に流れる貫通電流を抑制し、以って該貫通電流に起因する該発光素子の異常発光を抑制する。また、該容量部に保持された電位のうち、該キャリア移動度の影響を減殺する分による発光素子の発光を防ぐため、前記信号部は、黒表示時ににおける映像信号の電位レベルを所定の電源電位よりも高く設定する。

#### 【0013】

更に本発明は、制御パルスを供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含み、前記サンプリングトランジスタは所定のサンプリング期間に走査線から供給される制御パルスに応じ導通して信号線から供給された映像信号をサンプリングし、前記容量部はサンプリングされた映像信号に応じた入力電位を保持し、前記ドライブトランジスタは該容量部に保持された入力電位に応じて所定の発光期間に出力電流を供給し、前記発光素子は該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画素回路の駆動方法において、該出力電流に対する該ドライブトランジスタのキャリア移動度及び閾電圧の影響を両方同時に補正するための補正手順と保持手順とを含んでおり、前記補正手順は該サンプリング期間に先行して設定された補正期間に行なわれ、該補正期間はリセット期間と検出期間に分かれており、前記リセット期間で、該補正手順は該容量部に通電して該容量部が保持していた電位をリセットし、前記検出期間で、該補正手順は該通電を遮断し該ドライブトランジスタに過渡電流が流れている間に、該ドライブトランジスタのソースとゲート間に現れる電位差を検出し、前記保持手順は該検出した電位差に応じた電位を該容量部に保持し、以って該保持した電位は該ドライブトランジスタの出力電流に対する閾電圧の影響を減殺する分とキャリア移動度の影響を減殺する分の両方を含むことを特徴とする。

#### 【0014】

加えて本発明は、画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は該信号線に映像信号を供給し、前記スキャナ部は該走査線に制御パルスを供給して順次行ごとに画素を走査し、各画素は少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含み、前記サンプリングトランジスタは所定のサンプリング期間に走査線から供給されるサンプリング用制御パルスに応じ導通して信号線から供給された映像信号をサンプリングし、前記容量部はサンプリングされた映像信号に応じた入力電位を保持し、前記ドライブトランジスタは該容量部に保持された入力電位に応じて所定の発光期間に出力電流を供給し、前記発光素子は該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する表示装置の駆動方法において、該出力電流に対する該ドライブトランジスタのキャリア移動度及び閾電圧の影響を両方同時に個々の画素で補正するための補正手順と保持手順とを含んでおり、前記補正手順は該サンプリング期間に先行して設定された補正期間に行なわれ、該補正期間はリセット期間と検出期間に分かれており、前記リセット期間で該補正手順は該容量部に通電して該容量部が保持していた電位をリセットし、前記検出期間で該補正手順は該通電を遮断し該ドライブトランジスタに過渡電流が流れている間に、該ドライブトランジスタのソースとゲート間に現れる電位差を検出し、前記保持手順は該検出した電位差に

10

20

30

40

50

応じた電位を該容量部に保持し、以って該保持した電位は該ドライブトランジスタの出力電流に対する閾電圧の影響を減殺する分とキャリア移動度の影響を減殺する分の両方を含み、更にライト走査手順とドライブス走査手順と補正走査手順とを含み、前記ライト走査手順は該サンプリング期間に該サンプリング用制御パルスを走査線に供給し、前記補正走査手順は該補正期間を規定する補正用制御パルスを走査線に供給し、前記ドライブ走査手順は該補正期間内でリセット期間と検出期間を区切るとともに発光期間とこれ以外の非発光期間を区切るためのドライブ用制御パルスを走査線に供給することを特徴とする。

【発明の効果】

【0015】

本発明によれば、画素回路は出力電流のキャリア移動度及び閾電圧に対する依存性を両方同時に補正している。すなわち、所定の検出期間で、ドライブトランジスタに検出用の過渡電流が流れている間に、ドライブトランジスタのソースとゲート間に現われる電位差を検出し、これを容量部にフィードバックしている。検出期間を従来に比べ短く設定している為、過渡電流が流れている状態で、ソース／ゲート間の電位差を検出できる。この結果、検出した電位差は、ドライブトランジスタの出力電流に対する閾電圧の影響を減殺する分に加え、キャリア移動度の影響を減殺する分を含む。従来の様に、検出期間を長めに設定して過渡電流が消滅した状態でソース／ゲート間の電位差を検出すると、これには閾電圧の影響を減殺する分しか含まれない。電流が流れている状態で電位差を検出することで、キャリア移動度に関する情報も獲得することができる。この様に各画素毎閾電圧及び移動度の影響を排除できるので、画素アレイ全体から見ると画素毎の出力電流のばらつきを抑えることができる。特に、グレーから白表示時では出力電流の移動度に対する依存性が高い。本発明では、移動度による出力電流のばらつきを抑制することができるので、グレーから白表示時における画面のユニフォーミティを大幅に改善することができる。本発明は、基本的に従来の画素回路構成を維持しつつ、適切なタイミング制御を行なうことと、閾電圧及び移動度のばらつきを両方補正することができる。従って、画素回路の素子数を増加させることなく、出力電流のばらつきを抑制することが可能である。

【0016】

又本発明では、ドライブトランジスタに流れる過渡電流を安定して検出する為、検出期間に先立つリセット期間で容量部をリセットしている。このリセット動作により、ドライブトランジスタに瞬間的ではあるが貫通電流が流れ、発光素子が異常発光する。グレーから白表示では目立たないが、黒表示ではこの異常発光が影響し、いわゆる「黒浮き」となって画面のコントラストを損なう。本発明では、このリセット期間の時間幅を極力少なくすることにより貫通電流を抑制し、以って「黒浮き」を防いでいる。

【発明を実施するための最良の形態】

【0017】

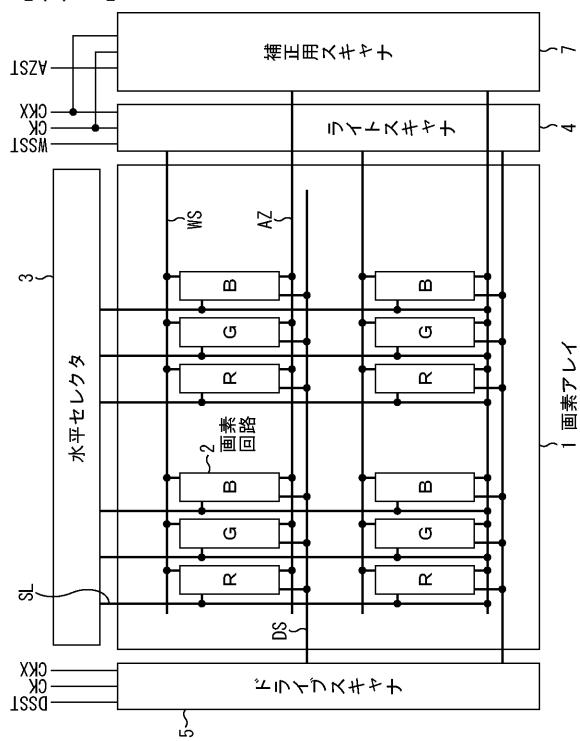

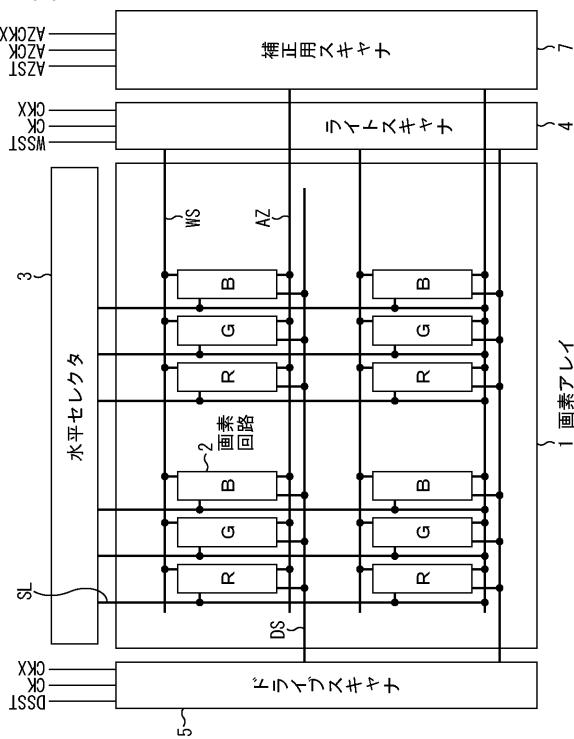

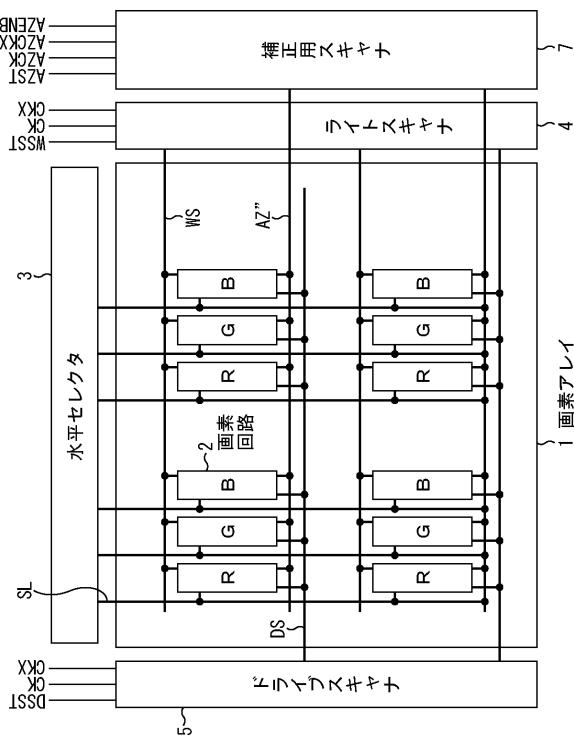

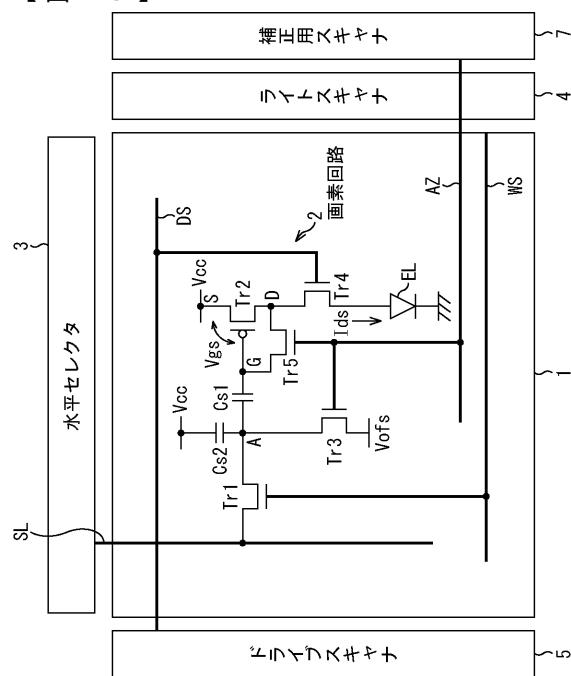

以下図面を参照して本発明の実施の形態を詳細に説明する。まず最初に本発明の概念を明らかにする為、図1を参照してアクティブマトリクス表示装置の基本的な構成を説明する。図示する様に、アクティブマトリクス表示装置は主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、補正用スキャナ7などを含んでいる。画素アレイ1は行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素R, G, Bとで構成されている。カラー表示を可能とする為、RGBの三原色画素を用意しているが、本発明はこれに限られるものではない。各画素R, G, Bは夫々画素回路2で構成されている。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。尚、走査線WSと平行に別の走査線DS及びAZも配線されている。走査線DSはドライブスキャナ5によって走査される。走査線AZは補正用スキャナ7によって走査される。ライトスキャナ4、ドライブスキャナ5及び補正用スキャナ7はスキャナ部を構成しており、1水平期間毎画素の行を順次走査する。各画素回路2は走査線WSによって選択された時信号線SLから映像信号をサンプリングする。更に走査線DSによって選択された時

10

20

30

40

50

、サンプリングされた映像信号に応じて画素回路 2 内に含まれている発光素子を駆動する。加えて画素回路 2 は走査線 A Z によって走査された時、あらかじめ決められた補正動作を行なう。

【 0 0 1 8 】

ライトスキャナ 4 は基本的にはシフトレジスタで構成されており、外部から供給された互いに反対極性のクロック信号 C K , C K X に応じて動作し、同じく外部から供給されたサンプリング用のスタートパルス W S S T を 1 水平期間毎に順次転送し、以って各行の画素の走査線 W S に順次サンプリング用の制御パルスを出力する。同様にドライブスキャナ 5 もシフトレジスタで構成されており、クロック信号 C K , C K X に応じてドライブ用のスタートパルス D S S T を 1 水平期間毎順次転送し、以って画素の各行の走査線 D S に、ドライブ用の制御パルスを出力する。同様に補正用スキャナ 7 もシフトレジスタで構成されており、外部から供給された補正用のスタートパルス A Z S T をクロック信号 C K , C K X に同期して順次転送し、画素の各行に補正用の制御パルスを出力する。図示する様に、スキャナ部を構成するライトスキャナ 4 、ドライブスキャナ 5 及び補正用スキャナ 7 には共通のクロック信号 C K , C K X が供給されており、スタートパルスのみ各スキャナの機能に応じて W S S T , D S S T , A Z S T と波形が異なっている。

10

【 0 0 1 9 】

上述した画素アレイ 1 は通常ガラスなどの絶縁基板上に形成されており、フラットパネルとなっている。各画素回路 2 はアモルファスシリコン薄膜トランジスタ ( T F T ) 又は低温ポリシリコン T F T で形成されている。アモルファスシリコン T F T の場合、スキャナ部はパネルとは別の T A B などで構成され、フレキシブルケーブルにてフラットパネルに接続される。低温ポリシリコン T F T の場合、スキャナ部も同じ低温ポリシリコン T F T で形成できるので、フラットパネル上に画素アレイ部とスキャナ部を一体的に形成できる。いずれの場合であっても、上述した様に各スキャナ 4 , 5 , 7 に供給するクロックパルス C K , C K X は共通として、入力クロック数を削減するのが一般的である。

20

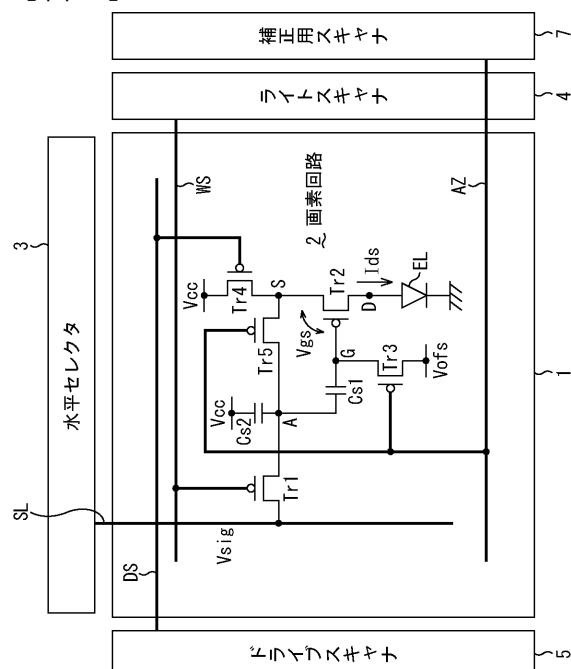

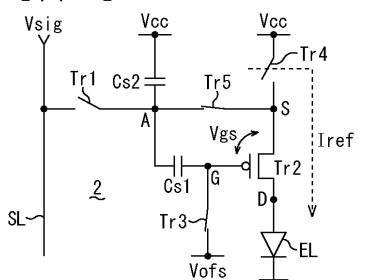

【 0 0 2 0 】

図 2 は、図 1 に示した画素アレイに含まれる画素回路の基本的な構成を示す回路図である。図示する様に、画素回路 2 は 5 個の薄膜トランジスタ T r 1 ~ T r 5 と 2 個の容量素子 C s 1 , C s 2 と 1 個の発光素子 E L とで構成されている。トランジスタ T r 1 ~ T r 5 は全て P チャネル型のポリシリコン T F T である。但し本発明はこれに限られるものではなく、N チャネル型のポリシリコン T F T を混在させてもよい。あるいは、N チャネル型のアモルファスシリコン T F T で画素回路を構成してもよい。2 個の容量素子 C s 1 と C s 2 は両者合わせて画素回路 2 の容量部を構成している。発光素子 E L は例えアノード及びカソードを備えた 2 端子型の有機 E L 素子からなる。但し本発明はこれに限られるものではなく、発光素子は一般的に電流駆動で発光する全てのデバイスを含む。

30

【 0 0 2 1 】

画素回路 2 の中心となるドライブトランジスタ T r 2 はゲート ( G ) が G 点に接続され、ソース ( S ) が S 点に接続され、ドレイン ( D ) が D 点に接続されている。発光素子 E L はアノードが D 点に接続され、カソードが接地されている。スイッチングトランジスタ T r 4 は電源電位 V c c と S 点との間に接続されており、発光素子 E L のオン / オフを制御する。トランジスタ T r 4 のゲートは走査線 D S に接続されている。

40

【 0 0 2 2 】

一方サンプリングトランジスタ T r 1 は信号線 S L と A 点との間に接続されている。サンプリングトランジスタ T r 1 のゲートは走査線 W S に接続している。A 点と S 点との間に検出トランジスタ T r 5 が接続されている。そのゲートは走査線 A Z に接続している。又スイッチングトランジスタ T r 3 は G 点と所定のオフセット電位 V o f s との間に接続されている。そのゲートは走査線 A Z に接続されている。尚、検出トランジスタ T r 5 とスイッチングトランジスタ T r 3 は V t h キャンセル用の補正手段を構成している。一方の容量素子 C s 1 は A 点と G 点との間に接続され、他方の容量素子 C s 2 は電源電位 V c c と A 点との間に接続されている。

50

## 【0023】

ドライブトランジスタTr2はソース/ゲート間に印加されるゲート電圧Vgsに応じてソース/ドレイン間にドレイン電流Idsを流し、これで発光素子ELを駆動する。本明細書ではゲート電圧Vgsを入力電位とし、ドレイン電流Idsを出力電流と定義している。信号線SLから供給される映像信号Vsigに応じてゲート電圧Vgsを設定し、これによりドレイン電流Idsを流すことで、映像信号の階調に従って発光素子ELの発光輝度を制御できる。

## 【0024】

ドライブトランジスタTr2の閾電圧Vthは画素毎に変動する。これをキャンセルする為あらかじめドライブトランジスタTr2の閾電圧Vthを検出し、容量素子Cs1に保持しておく。この後サンプリングトランジスタTr1をオンして容量素子Cs2に信号電位Vsigを書き込む。この様にして設定されたゲート電圧Vgsにより、ドライブトランジスタTr2を駆動する。

10

## 【0025】

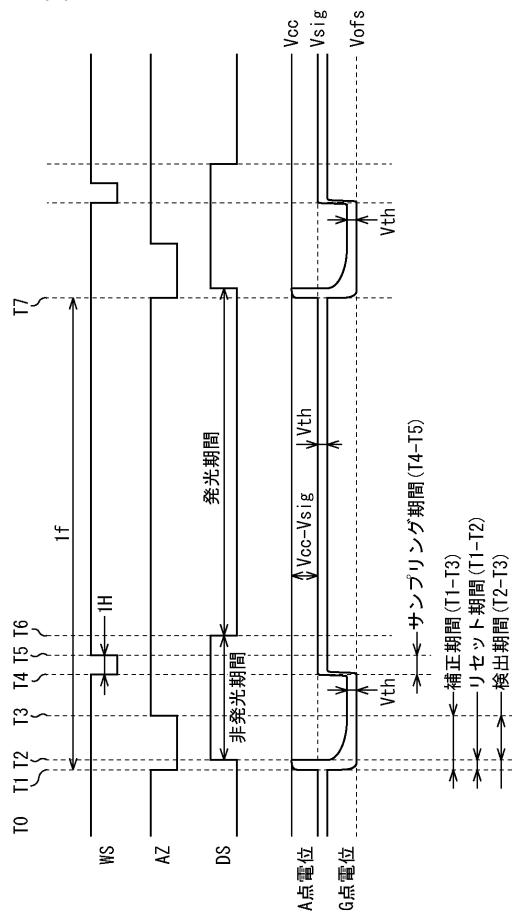

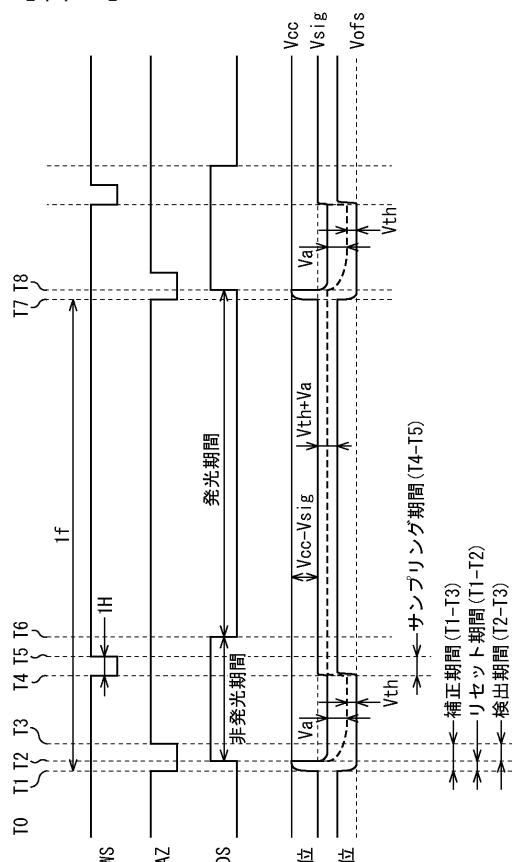

図3は、図2に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って各走査線WS, AZ及びDSに印加される制御パルスの波形を表わしてある。表記を簡略化する為、制御パルスも対応する走査線の符号と同じ符号で表わす。トランジスタは全てPチャネル型なので、走査線がハイレベルの時オフし、ローレベルの時オンする。そこで表記を簡略化する為、制御パルスがハイレベルからローレベルに立ち下がる場合を「オン」と表わし、ローレベルからハイレベルに立ち上がる場合を「オフ」と呼ぶ。各制御パルスWS, AZ, DSの波形とともに、A点及びG点の電位変化も表わしてある。

20

## 【0026】

図示のタイミングチャートではタイミングT1～T7までを1フィールド(1f)としてある。1フィールドの間に画素アレイの各行が1回順次走査される。タイミングチャートは、1行分の画素に印加される各制御パルスWS, AZ, DSの波形を表わしてある。

## 【0027】

当該フィールドが始まる前のタイミングT0で、制御パルスWS及びAZはオフであるのに対し、制御パルスDSがオンしている。従ってサンプリングトランジスタTr1、検出トランジスタTr5及びスイッチングトランジスタTr3がオフ状態であるのに対し、スイッチングトランジスタTr4のみがオン状態にある。この状態で、A点電位は信号電位Vsigにあり、G点電位はVsigからVthだけ下がった電位にある。この時S点はトランジスタTr4がオンしているのでVccとなっている。従ってトランジスタTr2のソースとゲートとの間にはVthを超える十分な電圧が印加されており、出力電流Idsが発光素子ELに供給されている。従ってタイミングT0では発光素子ELは発光状態にある。

30

## 【0028】

この後当該フィールドに入りタイミングT1で制御パルスAZがオンし、トランジスタTr5及びTr3が導通する。この結果A点とS点が直接つながるので、A点電位は電源電位Vccに急激に立ち上がる。一方トランジスタTr3がオンする為、G点電位は所定のオフセット電位Vofsまで急激に立ち下がる。

40

## 【0029】

この直後タイミングT2で制御パルスDSがオフになり、スイッチングトランジスタTr4が非導通状態となる。これによりS点が電源電位Vccから切り離され、非発光状態に変わる。タイミングT1からタイミングT2までの期間T1-T2で、A点電位がVccとなりG点電位がVofsとなって各容量素子Cs1, Cs2の電位がリセットされる。このリセット動作は、次に続く検出動作を安定化する為の準備であって、本明細書では期間T1-T2をリセット期間と呼ぶ。

## 【0030】

タイミングT2で制御パルスDSがオフするとS点がVccから切り離されるので、電

50

源からの給電が遮断される一方容量素子  $C_{s1}$  の放電が始まり過渡電流がトランジスタ  $T_{r5}$  を通して流れ、A点電位が  $V_{ccc}$  から低下していく。G点電位に対してA点電位が  $V_{th}$  まで低下した時、過渡電流が流れなくなる。この結果A点とG点の電位差が  $V_{th}$  となり、これが容量素子  $C_{s1}$  に保持される。

#### 【0031】

タイミング  $T_3$  で制御パルス  $A_Z$  がオフし、トランジスタ  $T_{r5}$  及び  $T_{r3}$  がオフして、容量素子  $C_{s1}$  のG点側が  $V_{off}$  から切り離されるとともに、A点側がS点から切り離される。タイミング  $T_2 \sim T_3$  までの期間で  $V_{th}$  を検出し且つ  $C_{s1}$  に保持するので、本明細書では期間  $T_2 - T_3$  を特に検出期間と呼ぶ。この検出期間  $T_2 - T_3$  はドライブトランジスタに流れる過渡電流が0になる様十分な時間幅を取ってある。

10

#### 【0032】

以上説明した様に、リセット期間  $T_1 - T_2$  におけるリセット動作と検出期間  $T_2 - T_3$  における検出動作とで閾電圧  $V_{th}$  の補正動作が行なわれる。そこでリセット期間と検出期間を合わせた期間  $T_1 - T_3$  を本明細書では補正期間と呼ぶ。図3のタイミングチャートから明らかな様に、補正期間  $T_1 - T_3$  は制御パルス  $A_Z$  によって規定される。一方、補正期間  $T_1 - T_3$  内でリセット期間  $T_1 - T_2$  と検出期間  $T_2 - T_3$  を区分するのが制御パルス  $D_S$  である。制御パルス  $D_S$  は基本的にスイッチングトランジスタ  $T_{r4}$  のオン／オフを制御するパルスであり、従って非発光期間と発光期間を規定している。

#### 【0033】

補正期間  $T_1 - T_3$  が経過した後、タイミング  $T_4$  で制御パルス  $W_S$  がオンし、サンプリングトランジスタ  $T_{r1}$  が導通する。この結果、信号線  $S_L$  から供給された映像信号  $V_{sig}$  が容量素子  $C_{s2}$  にサンプリングされる。これによりA点電位は  $V_{th}$  から信号電位  $V_{sig}$  に上昇する。この上昇に連動してG点電位も差分  $V_{th}$  を維持したまま上昇する。タイミングチャートから明らかな様に、サンプリング後でもA点電位とG点電位の電位差は  $V_{th}$  に維持されている。この後1水平期間が経過するタイミング  $T_5$  で制御パルス  $W_S$  はオフし、サンプリングトランジスタ  $T_{r1}$  が非導通状態となる。 $V_{sig}$  をサンプリングして  $C_{s2}$  に保持するサンプリング動作は期間  $T_4 - T_5$  で行なわれる為、これをサンプリング期間と呼ぶ。サンプリング期間  $T_4 - T_5$  は1水平期間1Hに等しい。

20

#### 【0034】

この後タイミング  $T_6$  で制御信号  $D_S$  が再びオンし、スイッチングトランジスタ  $T_{r4}$  が導通する。この結果ドライブトランジスタ  $T_{r2}$  はS点電位とG点電位との差  $V_{gs}$  に応じてドレン電流  $I_{ds}$  を発光素子  $E_L$  に供給する。発光素子  $E_L$  はこれにより  $V_{gs}$  に応じた輝度で発光する。

30

#### 【0035】

この後タイミング  $T_7$  に至り当該フィールドが終了するとともに、次のフィールドに移行する。次のフィールドでは最初にリセット期間に入る。

#### 【0036】

図3のタイミングチャートに基づいて、サンプリング期間  $T_4 - T_5$  及びその後の発光期間における入力電位  $V_{gs}$  を求める。入力電位  $V_{gs}$  はS点を基準にしたG点の電位である。サンプリング期間  $T_4 - T_5$  の後の発光期間ではトランジスタ  $T_{r4}$  がオンしている為、S点電位は電源に接続され  $V_{ccc}$  となっている。一方A点電位は前述した様に  $V_{ccc}$  よりも  $V_{sig}$  だけ低い。更にG点電位はA点電位から  $V_{th}$  だけ低い。従ってS点電位を基準にしたG点電位を表わす  $V_{gs}$  は  $V_{ccc} - (V_{sig} - V_{th})$  となる。前述のトランジスタ特性式1の  $V_{gs}$  にここで求めた  $V_{ccc} - (V_{sig} - V_{th})$  を代入すると、以下の特性式2が得られる。

$$I_{ds} = (1/2) \mu (W/L) C_o \times (V_{ccc} - V_{sig})^2 \dots \text{式2}$$

上記特性式2では特性式1に含まれていた  $V_{th}$  の項がキャンセルされ、 $V_{ccc} - V_{sig}$  で置き換えられている。従って図2に示した画素回路2は、ドライブトランジスタ  $T_{r2}$  の  $V_{th}$  に依存することなく、 $V_{sig}$  の値に応じた出力電流  $I_{ds}$  を発光素子  $E_L$  に供給することができる。従ってドライブトランジスタ  $T_{r2}$  の  $V_{th}$  が画素毎にばらつ

40

50

いていても、画素アレイとしてはそのばらつきを取り除いた出力電流を各画素の発光素子 E L に供給することができる。

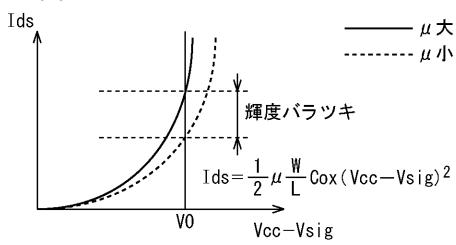

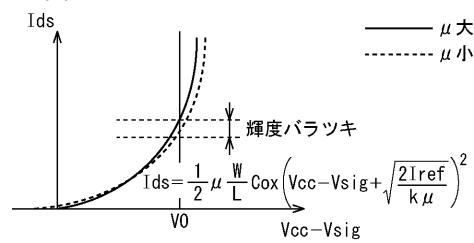

【0037】

図4は、特性式2をグラフ化したものであり、縦軸に出力電流  $I_{d,s}$ を取り、横軸に入力電位  $V_{c,c} - V_{s,i,g}$  を取ってある。合わせてグラフの傍に特性式2を再掲してある。特性式2から明らかな様に、ドライブトランジスタの  $V_{t,h}$  の項は消えている。しかしながら移動度  $\mu$  が残されている。この移動度  $\mu$  は  $V_{t,h}$  と同じくデバイス依存性があり、各画素毎にばらついている。従って、 $V_{t,h}$  をキャンセルしたのみでは出力電流  $I_{d,s}$  のばらつきは完全に抑えることはできない。グラフでは  $\mu$  の大きいトランジスタ特性を実線で表わし、 $\mu$  の小さなトランジスタ特性を点線で表わしている。グラフから明らかな様に、特性式の係数  $\mu$  が大きくなる程、特性カーブは急峻になっている。従って入力電位  $V_{c,c} - V_{s,i,g} = V_0$  で一定であっても、移動度  $\mu$  のばらつきが画素間で生じる為、出力電流  $I_{d,s}$  は  $\mu$  に依存して変動し、画素間で輝度のばらつきが生じてしまう。特に  $V_{c,c} - V_{s,i,g}$  がグレーから白表示の階調にある時移動度  $\mu$  に依存する輝度ばらつきが顕著となり、表示ムラが生じて解決すべき課題である。

10

【0038】

図5は、本発明に係る画素回路の動作説明に供するタイミングチャートである。画素回路の構成自体は図2に示した通りであるが、その制御シーケンスを改良して  $V_{t,h}$  に加え  $\mu$  のばらつきもキャンセル可能な様にしている。図3のタイミングチャートと同様に、図5のタイミングチャートも制御パルス  $W_S$ ,  $A_Z$ ,  $D_S$  の波形変化と A 点電位及び G 点電位の変化を表わしている。理解を容易にする為本発明に係る画素回路の A 点電位を実線で表わすとともに、これと比較する為図3で説明した画素回路の A 点電位の変化を点線で表わしてある。

20

【0039】

まず最初に点線で示した先の画素回路の A 点電位の変化を再度説明する。初めにリセット期間  $T_1 - T_2$  で G 点には  $V_{o,f,s}$  が書き込まれる。又 A 点電位はソース電位と等しくなり  $V_{c,c}$  に達する。ここで所定の接地電位  $V_{o,f,s}$  は全てのドライブトランジスタがオンする電圧設定 ( $V_{g,s} > V_{t,h}$ , すなわち  $V_{c,c} - V_{o,f,s} > V_{t,h}$ ) とする。尚リセット期間  $T_1 - T_2$  では制御パルス  $D_S$  と  $A_Z$  が同時にオンしている。

30

【0040】

次に検出期間  $T_2 - T_3$  に進むと、制御パルス  $D_S$  がオフすることでドライブトランジスタ  $T_{r,2}$  への電源供給が遮断され、A 点電位は点線で示す様にドライブトランジスタ  $T_{r,2}$  がカットオフするまで放電される。カットオフ後の A 点電位は  $V_{o,f,s} + V_{t,h}$  となり、 $V_{t,h}$  の検出並びに保持が行なわれる。その後制御パルス  $A_Z$  がオフし(図3参照)制御パルス  $W_S$  がオンすることで信号電圧  $V_{s,i,g}$  が書き込まれ、G 点電位は  $V_{s,i,g} - V_{t,h}$  となる。この後発光期間には制御パルス  $D_S$  がオンして、S 点電位は  $V_{c,c}$  となる。依ってドライブトランジスタ  $T_{r,2}$  に流れる出力電流  $I_{d,s}$  は前述した特性式2の様になり、 $V_{t,h}$  の項がキャンセルされ  $V_{t,h}$  ばらつきによるユニフォーミティの悪化を防ぐことができた。しかしながら、 $\mu$  のばらつきによるユニフォーミティの悪化は防げない。

40

【0041】

そこで本発明では図5のタイミングチャートに示す様に、制御パルス  $A_Z$  によって規定される補正期間  $T_1 - T_3$  を大幅に短くすることで、 $V_{t,h}$  補正と同時に移動度  $\mu$  の補正を行なう様にしている。図5のタイミングチャートから明らかな様に、補正期間  $T_1 - T_3$  を短縮することで、検出期間  $T_2 - T_3$  も短くなる。この為ドライブトランジスタ  $T_{r,2}$  はカットオフには到達せず、検出期間  $T_2 - T_3$  の終了時点における A 点電位は、実線で示す様に  $V_{o,f,s} + V_{t,h} + V_a$  となり、前述したカットオフレベルよりも有限の電圧  $V_a$  分だけ高くなる。その後は図3のタイミングチャートと同様にサンプリング期間  $T_4 - T_5$  を経て発光期間に至り発光素子への発光動作が行なわれる。

40

【0042】

図5のタイミングチャートに基づいて、サンプリング期間  $T_4 - T_5$  及びその後の発光

50

期間における入力電位  $V_{g s}$  を求める。入力電位  $V_{g s}$  は S 点を基準にした G 点の電位である。サンプリング期間  $T_4 - T_5$  の後の発光期間ではトランジスタ  $T_{r4}$  がオンしている為、S 点電位は電源に接続され  $V_{cc}$  となっている。一方 A 点電位は前述した様に  $V_{cc}$  よりも  $V_{sig}$  だけ低い。更に G 点電位は A 点電位から  $V_{th} + V_a$  だけ低い。従って S 点電位を基準にした G 点電位を表わす  $V_{g s}$  は  $V_{cc} - (V_{sig} - (V_{th} + V_a))$  となる。前述のトランジスタ特性式 1 の  $V_{g s}$  にここで求めた  $V_{cc} - (V_{sig} - (V_{th} + V_a))$  を代入すると、以下の特性式 3 が得られる。

$$I_{ds} = (1/2) \mu (W/L) C_o x (V_{cc} - V_{sig} + V_a)^2 \dots \text{式 3}$$

前述した特性式 2 とこの特性式 3 を比較すれば明らかな様に、 $V_{th}$  は同じ様にキャンセルされているが電圧分  $V_a$  が加わっている。結果的に、特性式 3 は特性式 2 に比較し  $V_a$  分が新たに加えられた形となっている。なお、特性式 3 では移動度補正を行う事で  $V_a$  項により輝度が明るい側にオフセットする。従来発光期間は特性式 2 に示す出力電流状態であり、黒表示の条件は  $I_{ds}$  がゼロとなる  $V_{sig} = V_{cc}$  であった。しかしながら、本発明では移動度補正を行う為に  $V_{th}$  補正期間を短くしており、発光期間の出力電流は特性式 3 に示すようになる。これにより、従来の黒条件  $V_{sig} = V_{cc}$  では  $V_a$  項分のみ発光してしまう。そこで、本発明においても黒表示を完全に無発光とする為に、黒表示での信号電圧設定を  $V_{sig} > V_{cc}$  とする必要がある。

#### 【0043】

特性式 3 に追加された項  $V_a$  は、ちょうど特性式 3 の係数部にある移動度  $\mu$  の寄与を減殺する方向に作用するので、本発明は  $V_{th}$  に加え  $\mu$  のばらつきも抑制することが可能である。この点につき図 6 を参照して説明する。図 6 は検出期間における画素回路 2 の動作状態を示す回路図である。前述した様に検出期間ではサンプリングトランジスタ  $T_{r1}$  及びスイッチングトランジスタ  $T_{r4}$  がオフしている一方、検出トランジスタ  $T_{r5}$  及びスイッチングトランジスタ  $T_{r3}$  がオンしている。トランジスタ  $T_{r4}$  がオフしている為ドライブトランジスタ  $T_{r2}$  は電源から切り離されている一方、検出トランジスタ  $T_{r5}$  がオンしている為ドライブトランジスタ  $T_{r2}$  のゲート G とソース S とが容量素子  $C_s1$  を介して接続されている。この時ドライブトランジスタ  $T_{r2}$  に流れる過渡電流を  $I_{ref}$  とする。変化する S 点の電位を  $V_s$ 、ドライブトランジスタの係数を  $k = W/L \cdot C_o x$  とすると、検出期間に流れる過渡電流  $I_{ref}$  は以下の特性式 4 の様に表わされる。

$$I_{ref} = (1/2) k \mu (V_s - V_{ofs} - V_{th})^2 \dots \text{式 4}$$

尚、S 点電位が  $V_s$  であり、G 点電位が  $V_{ofs}$  となっている為、式 4 中  $V_s - V_{ofs}$  は  $V_{gs}$  を表わしている。

#### 【0044】

ここで図 6 の A 点は S 点と同電位である為、図 5 に示した検出期間  $T_2 - T_3$  における A 点電位は  $V_s$  で表わされる。従って図 5 のタイミングチャートから明らかな様に、 $V_a$  は A 点電位  $V_s$  から  $V_{ofs}$  を引き更に  $V_{th}$  を引いたものである。依って  $V_a = V_s - V_{ofs} - V_{th}$  となる。これは式 4 中の  $V_s - V_{ofs} - V_{th}$  と同じなので、この項をそっくり  $V_a$  で置き換えることができる。従って  $V_a$  は以下の式 5 によって表わされる。

$$V_a = V_s - V_{ofs} - V_{th} = (2 I_{ref} / k \mu)^{1/2} \dots \text{式 4}$$

#### 【0045】

ここで  $V_a$  を含んだ特性式 3 に戻り、この  $V_a$  に式 5 を代入すると最終的に以下の特性式 6 が得られる。

$$I_{ds} = (1/2) \mu (W/L) C_o x (V_{cc} - V_{sig} + (2 I_{ref} / k \mu)^{1/2})^2 \dots \text{式 6}$$

#### 【0046】

図 7 は特性式 6 で表わされるドライブトランジスタの電流 / 電圧特性を示すグラフである。合わせてグラフの傍に特性式 6 を再掲してある。グラフは図 4 と対応させており、縦軸に出力電流  $I_{ds}$  を取り横軸に入力電位  $V_{cc} - V_{sig}$  を取っている。実線の特性カーブは移動度  $\mu$  がばらつきの範囲で最大を取る場合であり、点線の特性カーブは移動度が

ばらつきの範囲内で最小を取る場合である。特性式 6 で表わされる特性カーブは、電圧項に含まれる  $V_a$  分だけ、横軸の負方向にシフトする。ここで  $V_a$  は移動度  $\mu$  を分母に含む為、移動度  $\mu$  が高いと  $V_a$  は小さく、移動度が低いと  $V_a$  は大きくなり、特性カーブのシフト量が異なる。このシフト量はちょうど移動度  $\mu$  の影響をキャンセルする方向に働く。図 7 のグラフに示す様に、移動度  $\mu$  の異なる I / V 特性カーブはグレー表示領域において交差する。これにより図 4 に示した特性カーブに比べて、グレーから白表示領域において移動度  $\mu$  のばらつきに起因する出力電流の変動を抑制することができる。輝度にばらつきのないユニフォーミティに優れた有機 E L パネルを得ることができる。

#### 【 0 0 4 7 】

以上の説明から明らかな様に閾電圧  $V_{th}$  と移動度  $\mu$  の両方を同時に補正する為、過渡電流がドライブトランジスタを流れている間にゲートとソースとの間に現われる電位を検出し且つ保持する必要がある。従って検出期間を適切な範囲で短く設定する必要がある。この為、画素回路の動作タイミングを制御する周辺のスキャナ側に工夫が必要である。この点につき、以下説明する。まず図 1 に示した参考例であるが、これはスキャナ部に対する入力クロック数を削減する為、ライトスキャナ 4、ドライブスキャナ 5 及び補正用スキャナ 7 でクロック CK, CKX を共用している。この為、画素回路 2 のタイミング制御の分解能がクロック CK, CKX の半周期分より微細にすることは原理上できない。この限界がある為、図 1 に示した周辺スキャナ部の構成は不適当である。

#### 【 0 0 4 8 】

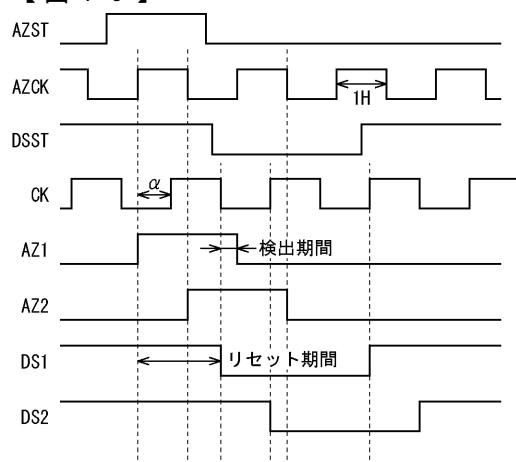

これに対し、図 8 に示した本発明の表示装置は、全部のスキャナに共通のクロック CK, CKX を用いるのではなく、ライトスキャナ 4 と補正用スキャナ 7 とで別のクロックを用いている。図示する様に、ライトスキャナ 4 にはドライブスキャナ 5 と共通のクロック CK, CKX が外部から供給される一方、補正用スキャナ 7 には CK, CKX とは別のクロック AZCK, AZCKX が供給されている。このクロック CK, CKX と別のクロック AZCK, AZCKX は周期が同じで位相が異なっている。この位相が異なる為画素回路 2 の制御タイミングをクロックの半周期未満の分解能で微細に制御することが可能である。

#### 【 0 0 4 9 】

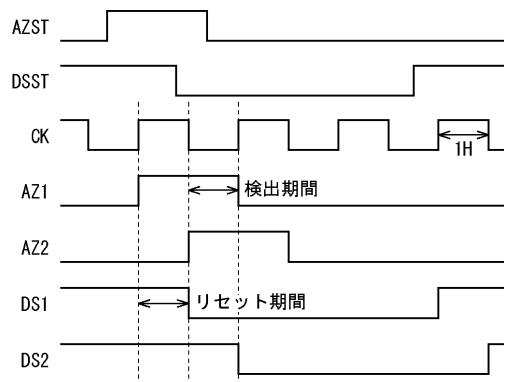

図 9 は、図 1 に示したスキャナ部の動作説明に供するタイミングチャートである。理解を容易にする為、このタイミングチャートは正論理で書かれており、各パルスの波形はハイレベルでオン、ローレベルでオフを表わしてある。前述した様に補正用スキャナ 7 にはスタートパルス AZST が供給され、ドライブスキャナ 5 には別のスタートパルス DSSST が供給される。いずれのスキャナにも共通のクロック CK が供給されている。このクロック CK の周期は 2 H に設定されている。補正用スキャナ 7 はスタートパルス AZST をクロック CK のエッジでラッチし、順次転送して画素の行毎に補正用制御パルス AZ を出力する。タイミングチャートでは 1 番目の行に出力される制御パルス AZ1 と 2 番目の行に出力される制御パルス AZ2 を表わしてある。同様にドライブスキャナ 5 はスタートパルス DSSST をクロック CK に同期して順次転送し、ドライブ用制御パルス DS1, DS2, ... を出力する。例えば 1 番目の行に着目すると、補正期間が AZ1 のパルス幅で規定される。補正期間に含まれるリセット期間と検出期間は、制御パルス DS1 によって区切られる。この結果検出期間の時間幅は最低でも 1 H 分となる。補正用スキャナ 7 とドライブスキャナ 5 で共通のクロック CK を使う限り、検出期間の時間幅を 1 H よりも短く制御することは原理的にできない。

#### 【 0 0 5 0 】

$V_{th}$  と  $\mu$  の情報を両方含んだ有限の  $V_a$  を得る為には、検出期間を短く設定する必要がある。各パラメータにもよるが、移動度  $\mu$  のばらつき補正に最適な検出期間は数  $\mu$  s から 20  $\mu$  s 程度である。一方でフィールド周波数や画素数にもよるが、一般的に 1 H 期間の長さは 20  $\mu$  s ~ 50  $\mu$  s である。つまり最適な移動度ばらつき補正を行なう為には、ほとんどのパネルにおいて検出期間を 1 H 未満とする必要がある。この点、図 9 に示した従来のタイミング制御では困難がある。同位相クロック CK を用いた場合検出期間はクロ

10

20

30

40

50

ックパルスの整数倍となり、その長さは最短でも 1 H である。パネルの周波数にもよるが 1 H 期間は 20 μ s ~ 40 μ s であり、移動度ばらつきの補正には不十分である。

#### 【 0 0 5 1 】

図 10 は、図 8 に示した本発明に係る表示装置のスキャナ部の動作説明に供するタイミングチャートである。理解を容易にする為図 9 に示したタイミングチャートと対応する部分には対応する参照符号を用いてある。異なる点は、補正用スキャナ 7 に入力するクロック AZCK をドライブスキャナ 5 に入力するクロック CK から異ならせている点である。AZCK と CK は周波数が同じで位相が だけ異なる。この位相 を変化させることで、補正用制御パルス AZ1 とドライブ用制御パルス DS1 のオーバーラップ部分を自由に可変させることができる。この結果検出期間を 1 H 未満に設定することができる様になり、十分な移動度ばらつき補正を実行することができる。但し、検出期間を短縮するとその分リセット期間が長くなる。リセット期間中ドライブトランジスタに貫通電流が流れ、これが発光素子 EL に供給される。発光素子 EL は貫通電流により異常発光し、画面に黒浮きが現われる。

#### 【 0 0 5 2 】

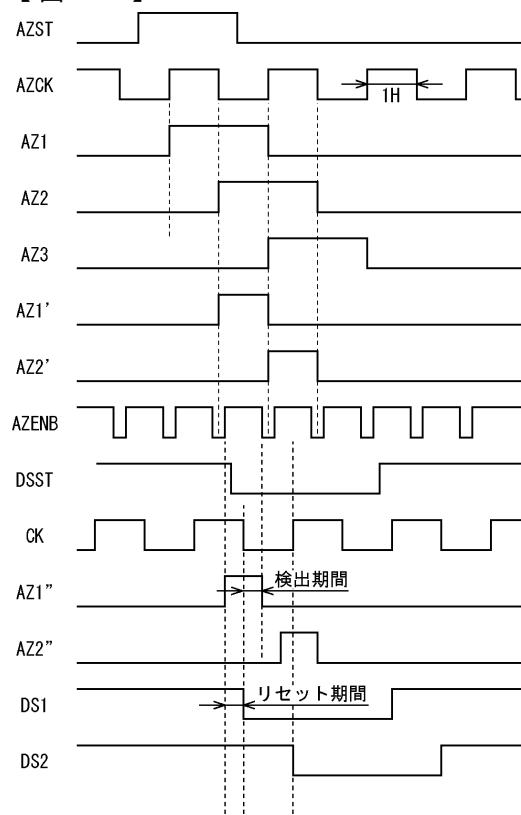

この点を改善し、リセット期間も短縮化可能な実施形態が、図 11 に示す表示装置である。基本的に図 11 の実施形態は、図 8 に示した先の実施形態と同一である。異なる点は、図 11 の実施形態が、リセット期間の短縮化を図る為、補正用スキャナ 7 に制限用の信号 AZENB を入力させている点である。

#### 【 0 0 5 3 】

図 12 のタイミングチャートを参照して、図 11 に示した表示装置のスキャナ部の動作を説明する。理解を容易にする為、図 10 に示した先の実施形態のタイミングチャートと対応する部分には対応する参照符号を用いている。図 11 に示した補正用スキャナ 7 にはスタートパルス AZST とクロックパルス AZCK に加え、制限用のパルス AZENB が供給されている。補正用スキャナ 7 はスタートパルス AZST をクロック AZCK に同期して順次転送し、シフトレジスタの各段から順次 1 H 周期で一次制御パルス AZ1, AZ2, AZ3 . . . を出力する。AZ1 と AZ2 のアンドが取られ二次制御パルス AZ1' が形成される。同様にして一次制御パルス AZ2 及び AZ3 のアンドを取って、二次制御パルス AZ2' が得られる。図示する様に、二次制御信号 AZ1', AZ2', . . . はパルス幅が 1 H となっている。更に二次制御パルス AZ1' を制限用クロックパルス AZENB でアンド処理し、三次制御信号 AZ1'' を得ている。同様に二次制御パルス AZ2' を AZENB でアンド処理し、次の三次制御パルス AZ2'' を得ている。タイミングチャートから明らかな様に、三次制御パルス AZ1'', AZ2'', . . . はパルス幅が 1 H よりも狭くなっている。この三次制御パルス AZ1'', AZ2'', . . . が、画素アレイ側の画素の各行に順次 1 H 周期で供給される。一方ドライブスキャナ 5 は、スタートパルス DSST をクロック CK に同期して順次転送し、制御パルス DS1, DS2, . . . を画素アレイ側の画素の各行に 1 H 周期で供給している。1 行目の画素に対するリセット期間は AZ1'' と DS1 のオーバーラップ部分となるが、これは AZ1'' のパルス幅を 1 H よりも短く制限したことで、リセット期間が 1 H よりも短縮化されている。この様にリセット期間を短くすることで黒浮きを抑制することが可能となり、その上で検出期間も短縮し閾電圧の補正と合わせて移動度の補正を行なうことが可能となり、ユニフォーミティの高い表示装置を得ることができる。

#### 【 0 0 5 4 】

図 2 に示した画素回路は全てのトランジスタが P チャネル型の薄膜トランジスタで構成されている。本発明はこれに限られるものではなく、N チャネル型のトランジスタを用いることもできる。図 13 は、画素回路の他の実施形態を表わしている。理解を容易にする為、図 2 に示した画素回路と対応する部分には対応する参照符号を用いてある。図示する様に本画素回路 2 は 5 個のトランジスタ Tr1 ~ Tr5 と 2 個の容量素子 Cs1, Cs2 と 1 個の発光素子 EL とで構成されている。5 個のトランジスタのうち、ドライブトランジスタ Tr2 のみが P チャネル型であり、残りのサンプリングトランジスタ Tr1、スイ

10

20

30

40

50

ツチングトランジスタTr3、スイッチングトランジスタTr4、検出トランジスタTr5は全てNチャネル型である。ここで容量素子Cs1とCs2が容量部を構成している。又検出トランジスタTr5とスイッチングトランジスタTr3が補正手段を構成している。

【0055】

ドライブトランジスタTr2のソース(S点)は電源電位Vccに接続し、ドレイン(D点)はスイッチングトランジスタTr4を介して発光素子ELのアノードに接続している。ドライブトランジスタTr2のゲート(G点)は検出トランジスタTr5を介してD点に接続している。

【0056】

一方サンプリングトランジスタTr1は信号線SLとA点との間に接続されている。A点と電源電位Vccとの間に容量素子Cs2が接続されている。又A点とG点との間に容量素子Cs1が接続されている。スイッチングトランジスタTr3はA点と所定のオフセット電位Vofsとの間に接続されている。

【0057】

一方周辺のスキャナ部は、ライトスキャナ4とドライブスキャナ5と補正用スキャナ7とを含んでいる。ライトスキャナ4は走査線WSを介してサンプリングトランジスタTr1をオンオフ制御する。ドライブスキャナ5は走査線DSを介してスイッチングトランジスタTr4をオンオフ制御する。補正用スキャナ7は走査線AZを介して検出トランジスタTr5及びスイッチングトランジスタTr3をオンオフ制御する。これらライトスキャナ4、ドライブスキャナ5及び補正用スキャナ7の制御シーケンスを適切に設定することで、検出時間を短縮化でき、ドライブトランジスタTr2のVthに加え $\mu$ も同時に補正できる。

10

【0058】

以上説明した様に、本発明に係る表示装置は、基本的に画素アレイ部1とスキャナ部と信号部とで構成されている。画素アレイ部1は、行状に配された走査線WS, DS, AZと列状に配された信号線SLと両者が交差する部分に配された行列状の画素回路2とからなる。信号部は水平セレクタ3からなり、信号線DSに映像信号Vsigを供給する。スキャナ部は、各走査線WS, DS, AZに制御パルスを供給して順次行毎に画素回路2を走査する。

20

【0059】

各画素回路2は、少なくともサンプリングトランジスタTr1と容量部Cs1, Cs2とドライブトランジスタTr2と発光素子ELとを含む。サンプリングトランジスタTr1は、所定のサンプリング期間に走査線WSから供給されるサンプリング用制御パルスに応じ導通して信号線SLから供給された映像信号Vsigをサンプリングする。容量部Cs1, Cs2は、サンプリングされた映像信号Vsigに応じた入力電位Vgsを保持する。ドライブトランジスタTr2は、容量部Cs1, Cs2に保持された入力電位Vgsに応じて所定の発光期間に出力電流Idsを供給する。この出力電流Idsは特性式1で示す様にドライブトランジスタTr2のチャネル領域のキャリア移動度 $\mu$ 及び閾電圧Vthに対して依存性を有する。発光素子ELは、ドライブトランジスタTr2から供給された出力電流Idsにより映像信号Vsigに応じた輝度で発光する。

30

【0060】

画素回路2は、出力電流Idsのキャリア移動度 $\mu$ 及び閾電圧Vthに対する依存性を両方同時に補正する為の補正手段を備えている。この補正手段は検出トランジスタTr5とスイッチングトランジスタTr3とで構成されている。尚画素回路2はこの他にトランジスタTr4を有し、発光素子ELの発光期間と非発光期間を切換制御している。この補正手段(Tr5, Tr3)は、ドライブトランジスタTr2及び容量部(Cs1, Cs2)に接続しており、サンプリング期間T4-T5に先行して設定された補正期間T1-T3に動作する。補正期間T1-T3はリセット期間T1-T2と検出期間T2-T3とに分かれている。リセット期間T1-T2で、補正手段(Tr5, Tr3)は容量部(Cs

40

50

1, C s 2) に通電して容量部が保持していた電位を一旦リセットする。続く検出期間 T 2 - T 3 で、補正手段 (T r 5, T r 3) は通電を遮断し、ドライブトランジスタ T r 2 に過渡電流 I ref が流れている間に、ドライブトランジスタ T r 2 のソース (S 点) とゲート (G 点) 間に現われる電位差を検出する。容量部 (C s 1, C s 2) は検出した電位差に応じた電位 V th + V a を保持する。保持した電位 V th + V a は、ドライブトランジスタ T r 2 の出力電流 I ds に対する閾電圧 V th の影響を減殺する分とキャリア移動度  $\mu$  の影響を減殺する分 V a の両方を含む。

#### 【0061】

一方スキャナ部は、少なくともライトスキャナ 4 とドライブスキャナ 5 と補正用スキャナ 7 を含む。ライトスキャナ 4 は、サンプリング期間 T 4 - T 5 にサンプリング用制御パルスを走査線 W S に供給する。補正用スキャナ 7 は、補正期間 T 1 - T 3 を規定する補正用制御パルスを走査線 A Z に供給する。ドライブスキャナ 5 は、補正期間 T 1 - T 3 内でリセット期間 T 1 - T 2 と検出期間 T 2 - T 3 を区切るとともに、発光期間 T 6 - T 8 とこれ以外の非発光期間 T 2 - T 6 を区切る為のドライブ用制御パルスを走査線 D S に供給する。

#### 【0062】

補正用スキャナ 7 は、第 1 のクロック A Z C K に同期して動作し、1 水平期間 (1 H) 每補正用制御パルス A Z 1, A Z 2 . . . を順次各行の走査線 A Z に供給する。ドライブスキャナ 5 は、第 2 のクロック C K に同期して動作し、1 水平期間 (1 H) 每ドライブ用制御パルス D S 1, D S 2 . . . を順次各行の走査線 D S に供給する。ここで第 2 のクロック C K は、第 1 のクロック A Z C K に対して周期 (2 H) が同じで位相  $\phi$  が異なっており、以って補正用制御パルス A Z 1 及びドライブ用制御パルス D S 1 によって規定される検出期間を 1 水平期間 (1 H) よりも短い時間幅に設定することで、出力電流 I ds のキャリア移動度  $\mu$  及び閾電圧 V th に対する依存性を両方同時に補正可能にしている。更にスキャナ部は、第 1 のクロック A Z C K と第 2 のクロック C K の位相差  $\phi$  を可変調整可能であり、検出期間の時間幅を最適に設定し、以って出力電流 I ds のキャリア移動度  $\mu$  及び閾電圧 V th に対する依存性を両方同時に補正可能にしている。好ましくは、補正用スキャナ 7 は補正用制御パルス A Z 1, A Z 2 . . . の時間幅を制限する手段を備えており、これによりリセット期間の時間幅を短縮して、通電によりリセット期間中ドライブトランジスタ T r 2 を通じて発光素子 E L に流れる貫通電流を抑制し、以って貫通電流に起因する発光素子 E L の異常発光を抑制している。

#### 【図面の簡単な説明】

#### 【0063】

【図 1】本発明に係る表示装置の元となる基本構成を示すブロック図である。

【図 2】図 1 に示した表示装置に含まれる画素回路の構成を示す回路図である。

【図 3】図 2 に示した画素回路の動作説明に供する参考タイミングチャートである。

【図 4】ドライブトランジスタの入力電圧 / 出力電流特性を示すグラフである。

【図 5】図 2 に示した画素回路の本発明に従った動作説明に供するタイミングチャートである。

【図 6】図 2 に示した画素回路の本発明に従った動作説明に供する回路図である。

【図 7】本発明に従ったドライブトランジスタの入力電圧 / 出力電流特性を示すグラフである。

【図 8】本発明に係る表示装置の実施形態を示すブロック図である。

【図 9】図 1 に示した表示装置の動作説明に供するタイミングチャートである。

【図 10】図 8 に示した表示装置の動作説明に供するタイミングチャートである。

【図 11】本発明に係る表示装置の他の実施形態を示すブロック図である。

【図 12】図 11 に示した表示装置の動作説明に供するタイミングチャートである。

【図 13】本発明に係る画素回路の他の実施形態を示す回路図である。

#### 【符号の説明】

10

20

30

40

50

【 0 0 6 4 】

1 . . . 画素アレイ、2 . . . 画素回路、3 . . . 水平セレクタ、4 . . . ライトスキャナ、5 . . . ドライブスキャナ、7 . . . 補正用スキャナ、Tr1 . . . サンプリングトランジスタ、Tr2 . . . ドライブトランジスタ、Tr3 . . . スイッチングトランジスタ、Tr4 . . . スイッチングトランジスタ、Tr5 . . . 検出トランジスタ、EL . . . 発光素子、Cs1 . . . 容量素子、Cs2 . . . 容量素子

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

$$I_{ref} = \frac{1}{2} k \mu (V_s - V_{ofs} - |V_{th}|)^2 \quad \text{式4}$$

$$V_a = V_s - V_{ofs} - |V_{th}| = \sqrt{\frac{2I_{ref}}{k \mu}} \quad \text{式5}$$

$$I_{ds} = \frac{1}{2} \mu \frac{W}{L} Cox \left( V_{cc} - V_{sig} + \sqrt{\frac{2I_{ref}}{k \mu}} \right)^2 \quad \text{式6}$$

【図7】

【図8】

【図9】

【図10】

【図11】

【図 1 2】

【図 1 3】

---

フロントページの続き

(51)Int.Cl. F I

H 05 B 33/14 A

(72)発明者 山本 哲郎

東京都品川区北品川6丁目7番35号 ソニー株式会社内

(72)発明者 豊村 直史

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 福村 拓

(56)参考文献 特開2003-202834 (JP, A)

特開2003-255897 (JP, A)

特開2004-133240 (JP, A)

特開2004-246204 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 30

G 09 G 3 / 20