(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-61501

(P2011-61501A)

(43) 公開日 平成23年3月24日(2011.3.24)

(51) Int.Cl.

|             |             |                  |

|-------------|-------------|------------------|

| <b>H04N</b> | <b>5/66</b> | <b>(2006.01)</b> |

| <b>G09G</b> | <b>5/36</b> | <b>(2006.01)</b> |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> |

| <b>G09G</b> | <b>5/00</b> | <b>(2006.01)</b> |

F 1

|        |      |         |           |

|--------|------|---------|-----------|

| HO 4 N | 5/66 | D       | 5 C 0 5 8 |

| G0 9 G | 5/36 | 5 2 O F | 5 C 0 8 0 |

| G0 9 G | 3/20 | 6 6 O C | 5 C 0 8 2 |

| G0 9 G | 3/20 | 6 3 2 F |           |

|        | 3/20 | 6 3 1 H |           |

テーマコード(参考)

審査請求 未請求 請求項の数 9 O L (全 17 頁) 最終頁に続く

(21) 出願番号

特願2009-209039 (P2009-209039)

(22) 出願日

平成21年9月10日 (2009. 9. 10)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100093241

弁理士 宮田 正昭

(74) 代理人 100101801

弁理士 山田 英治

(74) 代理人 100095496

弁理士 佐々木 榮二

(74) 代理人 100086531

弁理士 澤田 俊夫

(74) 代理人 110000763

特許業務法人大同特許事務所

最終頁に続く

(54) 【発明の名称】 画像信号処理装置と画像信号処理方法および画像表示装置

## (57) 【要約】

【課題】拡大表示で広い階調表現を可能とする。

【解決手段】画像拡大処理部21は、画素の繰り返しを行い拡大された画像の画像信号を生成する。多階調化処理部22のパターンデータ出力部は、画素を繰り返した繰り返し領域毎に、拡大された画像の画像信号から上位側の所定ビット数を除いた信号に基づく階調を繰り返し領域の画素で再現するためのパターンデータを出力する。多階調化処理部22の加算部は、繰り返し領域毎に、拡大された画像の画像信号における上位側の所定ビット数の信号に対してパターンデータを加算して出力する。

【選択図】

図3

**【特許請求の範囲】****【請求項 1】**

画素の繰り返しを行って、拡大された画像の画像信号を生成する画像拡大処理部と、前記画素を繰り返した繰り返し領域毎に、該繰り返し領域の画素によって前記画像信号から上位側の所定ビット数を除いた信号に基づく階調を再現するためのパターンデータを、前記所定ビット数を除いた信号に応じて出力するパターンデータ出力部と、前記繰り返し領域毎に、前記画像信号における上位側の前記所定ビット数の信号に対して前記パターンデータを加算する加算部とを備える画像信号処理装置。

**【請求項 2】**

前記パターンデータ出力部は、前記所定ビット数を除いた信号に応じたパターンデータとして異なるパターンのデータを記憶しており、パターン切り替えを行ってパターンデータを出力する

請求項 1 記載の画像信号処理装置。

**【請求項 3】**

前記パターンデータ出力部は、空間方向に対して前記パターンデータのパターン切り替えを行う

請求項 2 記載の画像信号処理装置。

**【請求項 4】**

前記パターンデータ出力部は、時間方向に対して前記パターンデータのパターン切り替えを行う

請求項 2 記載の画像信号処理装置。

**【請求項 5】**

前記パターンデータ出力部は、前記繰り返し領域の画素毎にテーブルを有しており、前記所定ビット数を除いた信号に応じて前記テーブルからパターンデータを選択して出力する

請求項 1 記載の画像信号処理装置。

**【請求項 6】**

前記画像信号から上位側の所定ビット数を除いた信号が $m$ ビットであるとき、前記繰り返し領域の画素数は「 $2^m$ 」以上とする

請求項 1 記載の画像信号処理装置。

**【請求項 7】**

前記繰り返し領域の画素数が「 $2^n$ 」であるとき、前記画像信号から上位側の所定ビット数を除いた信号の上位側から $n$ ビットの信号に応じた前記パターンデータの出力を行う

請求項 1 記載の画像信号処理装置。

**【請求項 8】**

画像拡大処理部によって、画素の繰り返しを行い拡大された画像の画像信号を生成するステップと、

パターンデータ出力部によって、前記画素を繰り返した繰り返し領域毎に、前記画像信号から上位側の所定ビット数を除いた信号に基づく階調を前記繰り返し領域の画素で再現するためのパターンデータを出力するステップと、

加算部によって、前記繰り返し領域毎に、前記画像信号における上位側の前記所定ビット数の信号に対して前記パターンデータを加算するステップと

を具備する画像信号処理方法。

**【請求項 9】**

所定ビット数の画像信号を用いて画像表示を行う表示部と、

画素の繰り返しを行って、前記表示部の表示解像度に対応した画像信号を生成する画像拡大処理部と、

前記画素を繰り返した繰り返し領域毎に、前記画像信号から上位側の所定ビット数を除いた信号に基づく階調を前記繰り返し領域の画素で再現するためのパターンデータを出力

10

20

30

40

50

するパターンデータ出力部と、

前記繰り返し領域毎に、前記画像信号における上位側の前記所定ビット数の信号に対して前記パターンデータを加算して、前記表示部に出力する加算部とを備える画像表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、画像信号処理装置と画像信号処理方法および画像表示装置に関する。詳しくは、拡大表示を行うときに広い階調表現を可能とする。

【背景技術】

【0002】

従来より画像表示装置の高解像度化が図られており、例えば画素数が  $1920 \times 1080$  である HD サイズから  $3840 \times 2160$  である 4K 2K サイズに画像表示装置の高解像度化が行われている。一方、画像信号は、HD サイズが主流であり、高解像度化が行われた画像表示装置を用いるときは、特許文献 1 のようにスケーラー等を使用することが一般的に行われている。

【0003】

また、画像信号の生成や画像処理では多ビット化が図られており、画像信号の生成では例えば 10 ビットや 12 ビット等の画像信号の生成が行われている。さらに、画像処理では、例えば 8 ビットの画像信号を 10 ビットの画像信号にビット深度変換を行い、変換後の画像信号を用いて輝度補正や色補正、階調特性補正等が行われている。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2005 - 354187 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、画像表示装置では、表示デバイスの高解像度化だけでなく高階調化が図られているものの、多ビット化された画像信号に対応した階調特性を必ずしも満たすものではない。したがって、画像表示装置の階調特性が画像信号に対応していないときは、画像信号の上位ビット側から画像表示装置の階調特性に応じた所定ビット数の信号を抽出して、この抽出した画像信号に基づいて表示デバイスを駆動することが行われる。例えば、画像信号が 10 ビットであり、表示デバイスが 8 ビットの画像信号に対応する階調特性である場合、10 ビットの画像信号の上位ビット側から 8 ビットの信号を抽出して、この抽出した 8 ビットの信号に基づいて表示デバイスの駆動が行われる。このため、画像表示装置では、広い階調表示を行うことができない。

【0006】

そこで、この発明では、拡大表示を行うときに広い階調表現を可能とする画像信号処理装置と画像信号処理方法および画像表示装置を提供する。

【課題を解決するための手段】

【0007】

この発明の第 1 の側面は、画素の繰り返しを行って、拡大された画像の画像信号を生成する画像拡大処理部と、前記画素を繰り返した繰り返し領域毎に、該繰り返し領域の画素によって前記画像信号から上位側の所定ビット数を除いた信号に基づく階調を再現するためのパターンデータを、前記所定ビット数を除いた信号に応じて出力するパターンデータ出力部と、前記繰り返し領域毎に、前記画像信号における上位側の前記所定ビット数の信号に対して前記パターンデータを加算して出力する加算部とを備える画像信号処理装置にある。

【0008】

10

20

30

40

50

この発明においては、画素の繰り返しを行うことで、例えば入力画像が表示画像のサイズに拡大される。また、入力画像の画像信号から上位側の所定ビット数の信号が生成されて、画像表示装置の階調特性に対応したビット数の画像信号に変換される。さらに、入力画像の画像信号から上位側の所定ビット数を除いた信号に応じて、この信号に基づく階調を再現するための例えばディザリングのパターンデータが加算部に出力されて、画素が繰り返されている繰り返し領域の各画素に対応する所定ビット数の画像信号に加算される。また、パターンデータ出力部は、繰り返し領域の画素毎にテーブルを有しており、所定ビット数を除いた信号に応じてテーブルからパターンデータが選択されて出力される。さらに、パターンデータは、予め複数記憶されており、空間方向や時間方向に対してパターン切り替えが行われる。また、拡大された画像の画像信号から上位側の所定ビット数を除いた信号を $m$ ビットとするときは、画像拡大において、繰り返し領域の画素数が「 $2^m$ 」以上とされる。また、繰り返し領域の画素数を「 $2^n$ 」とするとき、上位側の所定ビット数を除いた信号の上位側から $n$ ビットの信号に応じてパターンデータの出力が行われる。

10

#### 【0009】

この発明の第2の側面は、画像拡大処理部によって、画素の繰り返しを行い拡大された画像の画像信号を生成するステップと、パターンデータ出力部によって、前記画素を繰り返した繰り返し領域毎に、前記画像信号から上位側の所定ビット数を除いた信号に基づく階調を前記繰り返し領域の画素で再現するためのパターンデータを出力するステップと、加算部によって、前記繰り返し領域毎に、前記画像信号における上位側の前記所定ビット数の信号に対して前記パターンデータを加算して出力するステップとを具備する画像信号処理方法にある。

20

#### 【0010】

さらに、この発明の第3の側面は、所定ビット数の画像信号を用いて画像表示を行う表示部と、画素の繰り返しを行って、前記表示部の表示解像度に対応した画像信号を生成する画像拡大処理部と、前記画素を繰り返した繰り返し領域毎に、前記画像信号から上位側の所定ビット数を除いた信号に基づく階調を前記繰り返し領域の画素で再現するためのパターンデータを出力するパターンデータ出力部と、前記繰り返し領域毎に、前記画像信号における上位側の前記所定ビット数の信号に対して前記パターンデータを加算して、前記表示部に出力する加算部とを備える画像表示装置にある。

30

#### 【0011】

この発明においては、画素の繰り返しを行うことで、入力画像が表示部の表示画素数に拡大される。また、入力画像の画像信号から上位側の所定ビット数の信号が生成されて、表示部の階調特性に対応したビット数の画像信号に変換される。さらに、入力画像の画像信号から上位側の所定ビット数を除いた信号に応じて、この信号に基づく階調を再現するための例えばディザリングのパターンデータが加算部に出力されて、画素が繰り返されている繰り返し領域の各画素に対応する所定ビット数の画像信号にパターンデータが加算された画像信号に基づいて、表示部で画像表示が行われる。

#### 【発明の効果】

#### 【0012】

この発明によれば、画素の繰り返しを行い拡大された画像の画像信号が画像拡大処理部で生成される。また、画素が繰り返された繰り返し領域毎に、拡大された画像の画像信号から上位側の所定ビット数を除いた信号に基づく階調を繰り返し領域の画素で再現するためのパターンデータがパターンデータ出力部から出力される。さらに、出力されたパターンデータが加算部によって、拡大された画像の画像信号における上位側の所定ビット数の信号に加算される。したがって、画像信号のビット深度を小さくしても広い階調表現の拡大表示を行うことができる。

40

#### 【図面の簡単な説明】

#### 【0013】

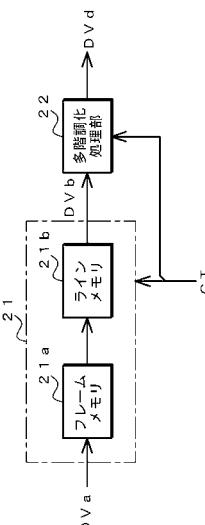

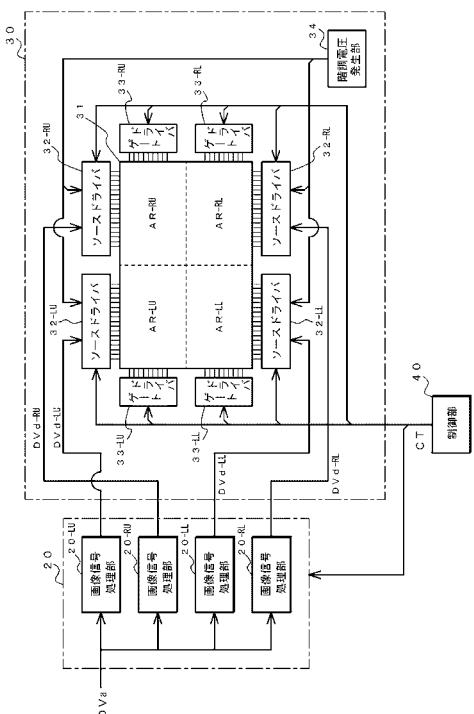

【図1】画像信号処理装置を有した画像表示装置の構成を示す図である。

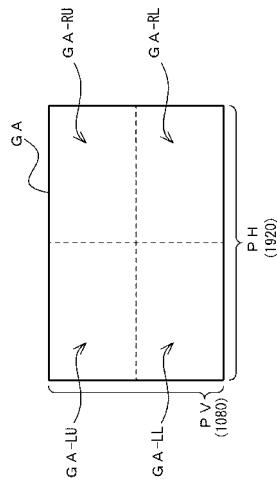

【図2】入力画像を示す図である。

50

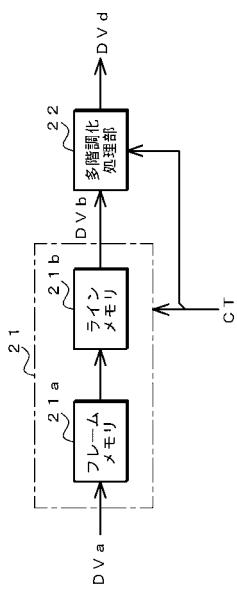

【図3】画像処理装置の構成を示す図である。

【図4】多階調化処理部の構成を示す図である。

【図5】多階調化処理を説明するための図である。

【図6】パターンデータ出力部を説明するための図である。

【図7】画像処理装置の動作(1/2)を示すフローチャートである。

【図8】画像処理装置の動作(2/2)を示すフローチャートである。

【図9】多階調化処理部の動作を説明するための示す図である。

【図10】画像処理装置の動作を説明するための示す図である。

【発明を実施するための形態】

【0014】

10

以下、発明を実施するための形態について説明する。なお、説明は以下の順序で行う。

1. 画像信号処理装置を有した画像表示装置の構成

2. 画像処理装置の動作

【0015】

<1. 画像信号処理装置を有した画像表示装置の構成>

図1は、本発明の画像信号処理装置を有した画像表示装置の構成を例示している。画像表示装置は、画像信号処理装置20と表示部30を有している。なお、以下の説明では、画像信号処理装置20に入力される画像信号DVAは、例えばビット深度が10ビットで画素数が1920×1080であるHDサイズの画像信号とする。また、表示部30は、ビット深度が8ビットの画像信号に対応する階調特性であり、画素数がHDサイズの4倍である3840×2160(4K2Kサイズ)とする。

20

【0016】

画像信号処理装置20は、入力画像の画像信号DVAを表示部30の階調特性に対応したビット深度の画像信号に変換する。また、画像信号処理装置20は、表示部30の解像度に応じて入力画像の拡大を行う。さらに、画像信号処理装置20は、ビット深度の変換を行っても拡大された画像で広い階調表現を行うことができるよう、多階調化処理を行う。

【0017】

ここで、HDサイズの入力画像を拡大して4K2Kサイズで表示する場合、画像信号処理装置20は高い処理性能が必要となる。したがって、入力画像を分割して、分割後の画像をそれぞれ画像信号処理装置で処理することで、高い処理性能の画像信号処理装置を用いることなく4K2Kサイズで画像表示を行えるようにする。なお、図1は、入力画像を4分割して処理する場合の構成を示しており、画像信号処理装置20として、4つの画像信号処理装置20-LU, 20-RU, 20-LL, 20-RLが用いられている。

30

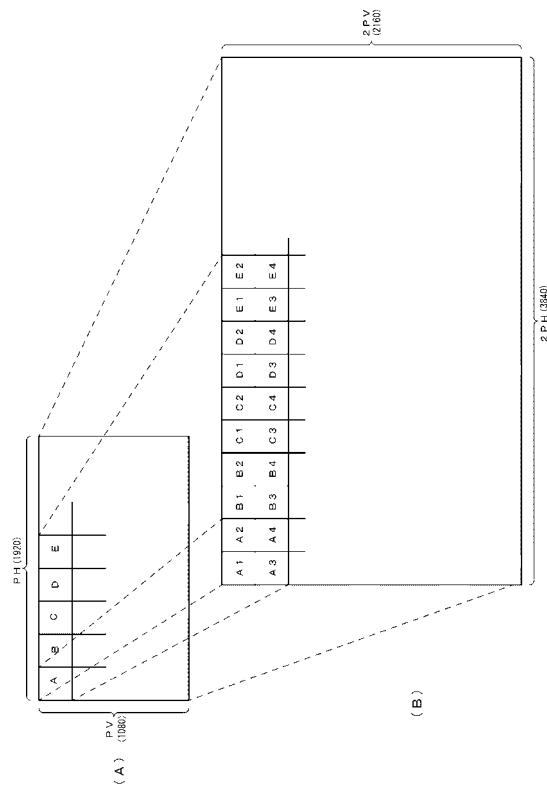

【0018】

画像信号処理装置20-LUは、HDサイズの入力画像の1/4の領域を示す画像信号に対して水平および垂直方向の画素数をそれぞれ2倍とする処理を行い、この1/4の領域の画像がHDサイズとされた画像の画像信号を生成する。同様に、画像信号処理装置20-RU, 20-LL, 20-RLは、入力画像のそれぞれ異なる1/4の領域の画像がHDサイズとされた画像の画像信号を生成する。例えば、画像信号処理装置20-LUは、図2に示すHDサイズ(水平方向の画素数PH=1920画素、垂直方向の画素数PV=1080)の入力画像GAの左上に位置する1/4の領域の画像GA-LUをHDサイズに拡大した画像の画像信号を生成する。また、画像信号処理装置20-RUは、右上に位置する1/4の領域の画像GA-RUをHDサイズに拡大した画像の画像信号を生成する。画像信号処理装置20-LLは、左下に位置する1/4の領域の画像GA-LLをHDサイズに拡大した画像の画像信号を生成する。さらに画像信号処理装置20-RLは、右下に位置する1/4の領域の画像GA-RLをHDサイズに拡大した画像の画像信号を生成する。

40

【0019】

また、画像信号処理装置20-LUは、拡大された画像を示すビット深度が10ビットである画像信号の上位8ビット分を抽出して、ビット深度が8ビットの画像信号に変換する

50

。同様に、画像信号処理装置 20-RU, 20-LL, 20-RLは、それぞれ拡大された画像を示すビット深度が10ビットである画像信号の上位8ビット分を抽出して、ビット深度が8ビットの画像信号に変換する。

#### 【0020】

さらに、画像信号処理装置 20-LUは、拡大ビット深度を10ビットから8ビットに低下させたことによる階調の劣化を補償する多階調化処理を8ビットの画像信号に対して行い、画像の拡大および階調の劣化が補償された画像信号 DVd-LUを出力する。同様に、画像信号処理装置 20-RU, 20-LL, 20-RLは、それぞれ画像の拡大および階調の劣化が補償された画像信号 DVd-RU, DVd-LL, DVd-RLを出力する。

#### 【0021】

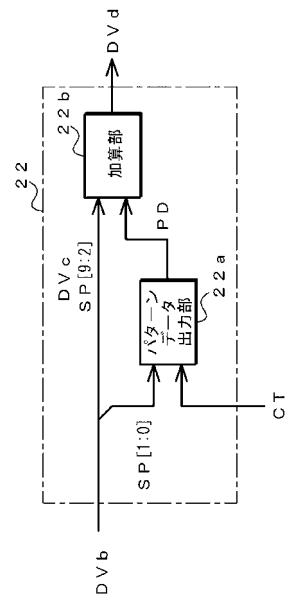

図3は、画像信号処理装置の構成を示している。画像信号処理装置 20-LU, 20-RU, 20-LL, 20-RLは、それぞれ画像拡大処理部21と多階調化処理部22を有している。

#### 【0022】

画像拡大処理部21は、フレームメモリ21aとラインメモリ21bを有している。フレームメモリ21aは、入力画像GAの1/4の領域の画像信号を記憶する。ラインメモリ21bは、フレームメモリ21aから読み出された1ライン分の画像信号を記憶する。このフレームメモリ21aおよびラインメモリ21bの動作は、後述する制御部40からの制御信号CTによって制御される。

#### 【0023】

画像拡大処理部21は、制御部40から供給された制御信号CTに基づき、画像信号の書き込みや読み出しを行い、入力画像における1/4の領域の画像を水平および垂直方向にそれぞれ2倍した画像の画像信号DVbを生成して多階調化処理部22に出力する。

#### 【0024】

多階調化処理部22は、画像拡大処理部21から供給された画像信号DVbを表示部30の階調特性に対応したビット深度の画像信号に変換する。例えば、画像信号DVbのビット深度が10ビットで、表示部30の階調特性が8ビットのビット深度の画像信号に対応する特性であるとする。この場合、多階調化処理部22は、画像信号DVbの上位ビット側から8ビット分を抽出してビット深度が8ビットの画像信号DVcとする。

#### 【0025】

また、多階調化処理部22は、ビット深度の変換を行っても拡大された画像で広い階調表現を行うことができるよう、多階調化を行う。ここで、1/4の領域の画像が水平方向および垂直方向にそれぞれ2倍とされたとき、1/4の領域の画像における1画素は、水平方向および垂直方向にそれぞれ2度繰り返されて、拡大画像における4画素の繰り返し領域に対応する。したがって、多階調化処理部22は、入力画像の1画素を繰り返した4画素単位の繰り返し領域毎に、繰り返し領域内の画素信号レベルを調整して、ビット深度を10ビットから8ビットに低下させたことによる階調の劣化を補償する。

#### 【0026】

図4は、多階調化処理部22の構成を示している。多階調化処理部22は、パターンデータ出力部22aと加算部22bを有している。

#### 【0027】

パターンデータ出力部22aは、ビット深度の変換によって画像信号DVcでは用いられないビット信号に基づく階調をディザリングによって再現するため、画像信号DVcでは用いられなくなったビット信号に応じてパターンデータを出力する。

#### 【0028】

パターンデータ出力部22aは、予めディザリングのためのパターンデータを、繰り返し領域の画素毎にテーブルとして記憶している。パターンデータ出力部22aは、ビット深度の変換によって画像信号DVcでは用いられないビット信号と、繰り返し領域内のいずれの画素であるかに応じてテーブルのパターンデータを選択して加算部22bに出力する。すなわち、パターンデータ出力部22aは、繰り返し領域内のいずれの画素であるかに応じてテーブルの選択を行い、選択したテーブルから10ビットの画像信号DVb

10

20

30

40

50

における下位 2 ビット信号 S P [ 1:0 ] に応じてパターンデータを選択して出力する。加算部 2 2 b は、上位 8 ビット信号 S P [ 9:2 ] に対してパターンデータ出力部 2 2 a から出力されたパターンデータを加算して、画像信号 D V d として出力する。

#### 【 0 0 2 9 】

このように、多階調化処理部 2 2 は、画像信号 D V c では用いられていない下位 2 ビット信号 S P [ 1:0 ] の信号レベルを誤差とする。さらに、多階調化処理部 2 2 は、この誤差を繰り返し領域内の 4 画素に拡散させる誤差拡散を行い、ビット深度を 10 ビットから 8 ビットに低下させたことによる階調の劣化を補償した画像信号 D V d を生成する。

#### 【 0 0 3 0 】

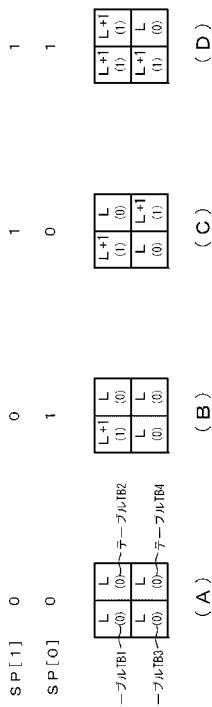

図 5 は、ディザリングの一例を示している。なお、上位 8 ビット信号 S P [ 9:2 ] で示される階調レベルを例えば「 L 」、上位 8 ビット信号 S P [ 9:2 ] に対して「 1 」を加算したときの階調レベルを例えば「 L+1 」とする。

#### 【 0 0 3 1 】

図 5 の ( A ) に示すように、画像信号 D V b の下位 2 ビット信号 S P [ 1:0 ] が「 0 」であるとき、10 ビットの画像信号 D V b から上位 8 ビット信号 S P [ 9:2 ] を抽出して 8 ビットの画像信号に変換しても階調レベルの変化はない。したがって、下位 2 ビット信号 S P [ 1:0 ] が「 0 」である画素に対応した繰り返し領域内の 4 画素は、それぞれ階調レベルを「 L 」とする。

#### 【 0 0 3 2 】

図 5 の ( B ) に示すように、ビット信号 S P [ 1 ] = 「 0 」, S P [ 0 ] = 「 1 」であるとき、10 ビットの画像信号 D V b から上位 8 ビット信号 S P [ 9:2 ] を抽出した画像信号に基づく階調レベルは、10 ビットの画像信号 D V b に基づく階調レベルよりも「 0 . 25 」だけ低下した状態となる。したがって、ビット信号 S P [ 1 ] = 「 0 」, S P [ 0 ] = 「 1 」である画素に対応した繰り返し領域の 4 画素は、いずれか 1 つの画素の階調レベルを「 L+1 」とすることで、繰り返し領域の階調レベルの平均が「 L+0.25 」となり、階調レベルの低下を補償できる。

#### 【 0 0 3 3 】

図 5 の ( C ) に示すように、ビット信号 S P [ 1 ] = 「 1 」, S P [ 0 ] = 「 0 」であるとき、10 ビットの画像信号 D V b から上位 8 ビット信号 S P [ 9:2 ] を抽出した画像信号に基づく階調レベルは、10 ビットの画像信号 D V b に基づく階調レベルよりも「 0 . 5 」だけ低下した状態となる。したがって、ビット信号 S P [ 1 ] = 「 1 」, S P [ 0 ] = 「 0 」である画素に対応した繰り返し領域の 4 画素は、いずれか 2 つの画素の階調レベルを「 L+1 」とすることで、繰り返し領域の階調レベルの平均が「 L+0.5 」となり、階調レベルの低下を補償できる。

#### 【 0 0 3 4 】

図 5 の ( D ) に示すように、ビット信号 S P [ 1 ] = 「 1 」, S P [ 0 ] = 「 1 」であるとき、10 ビットの画像信号 D V b から上位 8 ビット信号 S P [ 9:2 ] を抽出した画像信号に基づく階調レベルは、10 ビットの画像信号 D V b に基づく階調レベルよりも「 0 . 75 」だけ低下した状態となる。したがって、ビット信号 S P [ 1 ] = 「 1 」, S P [ 0 ] = 「 1 」である画素に対応した繰り返し領域の 4 画素は、いずれか 3 つの画素の階調レベルを「 L+1 」とすることで、繰り返し領域の階調レベルの平均が「 L+0.75 」となり、階調レベルの低下を補償できる。

#### 【 0 0 3 5 】

パターンデータ出力部 2 2 a に記憶されているテーブルは、図 5 および図 6 に示すように、10 ビットの画像信号 D V b を 8 ビットの画像信号 D V c に変換したとき、このビット深度の変換によって生じる階調の低下を補正できるように予め設定されている。

#### 【 0 0 3 6 】

ここで、テーブル T B 1 のデータは、繰り返し領域内の 1 番目の画素に対するパターンデータである。また、テーブル T B 2 のデータは、繰り返し領域内の 2 番目の画素に対するパターンデータであり、テーブル T B 3 のデータは、繰り返し領域内の 3 番目の画素に

10

20

30

40

50

対するパターンデータである。さらに、テーブルTB4のデータは、繰り返し領域内の4番目の画素に対するパターンデータである。

#### 【0037】

ビット信号SP[1] = 0, ビット信号SP[0] = 0であるとき、繰り返し領域内の4画素の信号に対して、パターンデータPDとして「0」「0」「0」「0」が順に加算部22bに供給される。したがって、加算部22bから出力される画像信号DVdに基づく画像は、図5の(A)に示すように、繰り返し領域内の1番目から4番目までの画素の階調レベルが「L」となる。なお、上位8ビット信号SP[9:2]で示される階調レベルは「L」とする。

#### 【0038】

ビット信号SP[1] = 0, ビット信号SP[0] = 1であるとき、繰り返し領域内の4画素の信号に対して、パターンデータPDとして「1」「0」「0」「0」が順に加算部22bに供給される。したがって、加算部22bから出力される画像信号DVdに基づく画像は、図5の(B)に示すように、繰り返し領域内の1番目の画素が階調レベル「L+1」となり、2番目から4番目までの画素が階調レベル「L」となる。

#### 【0039】

ビット信号SP[1] = 1, ビット信号SP[0] = 0であるとき、繰り返し領域内の4画素の信号に対して、パターンデータPDとして「1」「0」「0」「1」が順に加算部22bに供給される。したがって、加算部22bから出力される画像信号DVdに基づく画像は、図5の(C)に示すように、繰り返し領域内の1番目と4番目の画素が階調レベル「L+1」となり、2番目と3番目の画素が階調レベル「L」となる。

#### 【0040】

ビット信号SP[1] = 1, ビット信号SP[0] = 1であるとき、繰り返し領域内の4画素の信号に対して、パターンデータPDとして「1」「1」「1」「0」が順に加算部22bに供給される。したがって、加算部22bから出力される画像信号DVdに基づく画像は、図5の(D)に示すように、繰り返し領域内の1番目から3番目の画素が階調レベル「L+1」となり、4番目の画素が階調レベル「L」となる。

#### 【0041】

なお、パターンデータは図6に示すパターンに限られるものではなく、例えばビット信号SP[1] = 0, SP[0] = 1の場合、テーブルTB1～TB4のいずれか1つを「1」とすればよい。また、ビット信号SP[1] = 1, SP[0] = 0の場合、テーブルTB1～TB4のいずれか2つを「1」、ビット信号SP[1] = 1, SP[0] = 1の場合、テーブルTB1～TB4のいずれか3つを「1」とすればよい。

#### 【0042】

図1に示す画像信号処理装置20-LU, 20-RU, 20-LL, 20-RLは、上述のような画像の拡大とビット深度の変換、および階調の劣化を補償する多階調化処理をそれぞれ行い、処理後の画像信号DVd-LU, DVd-RU, DVd-LL, DVd-RLを出力する。

#### 【0043】

画像信号処理装置20から出力された画像信号は、表示部30に供給される。表示部30は、表示デバイス31、ソースドライバ32-LU, 32-RU, 32-LL, 32-RL、ゲートドライバ33-LU, 33-RU, 33-LL, 33-RL、階調電圧生成部34を有している。

#### 【0044】

画像信号処理装置20-LUから出力された画像信号DVd-LUは、ソースドライバ32-LUに供給される。また、画像信号処理装置20-RUから出力された画像信号DVd-RUはソースドライバ32-RU、画像信号処理装置20-LLから出力された画像信号DVd-LLはソースドライバ32-LLにそれぞれ供給される。さらに、画像信号処理装置20-RLから出力された画像信号DVd-RLはソースドライバ32-RLに供給される。

#### 【0045】

表示デバイス31は、例えば液晶表示素子が用いられている。液晶表示素子は、透明な画素電極とTFT(Thin Film Transistor)とを配置した基板と、全体に一つの透明な電

極を形成した対向基板とを有しており、これらの基板間に液晶が封入された構造を有している。そして、スイッチング機能をもつTFTを制御することによって、各画素電極に画素階調に応じた電圧を印加し、各画素電極と対向基板の電極との間の電位差を発生させることにより液晶の透過率を変化させて画像を表示する。

#### 【0046】

表示デバイス31の画素電極は、水平および垂直方向にマトリックス状に配置されておりTFTと接続されている。また、TFTには、階調電圧を印加するためのデータ線と、TFTをスイッチングさせるための制御信号を印加する走査線が接続されている。表示デバイス31は、制御信号によってTFTをスイッチングさせることにより、画素電極に階調電圧を印加させて、各画素電極と対向基板の電極との間の電位差を発生させる。

10

#### 【0047】

ソースドライバ32-LUは、画像信号処理装置20-LUから供給された画像信号DVd-LUの直並列変換を行い、表示デバイス31の領域AR-LUにおける1ライン分の画素に対する表示信号とする。さらに、表示信号のD/A変換や増幅を行いアナログの階調電圧を生成する。ここで、表示信号のD/A変換では、階調電圧生成部34で生成された階調基準電圧を選択して、さらに選択した階調基準電圧を分圧することで、画像信号に応じた階調電圧を生成する。このように、ソースドライバ32-LUは、階調電圧の生成を水平ライン毎に行い、生成した階調電圧を駆動信号として表示デバイス31のデータ線を介して水平ライン毎に順次切り替えてTFTに出力する。

#### 【0048】

ソースドライバ32-RU, 32-LL, 32-RLは、ソースドライバ32-LUと同様な処理を行い、画像信号処理装置20-RU, 20-LL, 20-RLから供給された画像信号に基づいて、領域AR-RU, AR-LL, AR-RLにおける1ライン分の駆動信号を生成して出力する。なお、ソースドライバ32-LU, 32-RU, 32-LL, 32-RLの動作は、制御部40から供給された制御信号に基づいて行う。

20

#### 【0049】

ゲートドライバ33-LUは、表示デバイス31の領域AR-LUにおいて水平ライン毎にTFTをスイッチングさせるための制御信号を生成して、表示デバイス31の走査線を介してTFTに出力する。ゲートドライバ33-RU, 33-LL, 33-RLは、ゲートドライバ33-LUと同様な処理を行い、領域AR-RU, AR-LL, AR-RLにおいて水平ライン毎にTFTをスイッチングさせるための制御信号を生成して、走査線を介してTFTに出力する。なお、ゲートドライバ33-LU, 33-RU, 33-LL, 33-RLの動作は、制御部40から供給された制御信号CTに基づいて行う。

30

#### 【0050】

階調電圧生成部34は、階調基準電圧を生成してソースドライバ32-LU, 32-RU, 32-LL, 32-RLに出力する。

#### 【0051】

制御部40は、入力画像の画像信号DVaに同期した制御信号CTを生成して画像信号処理装置20や表示部30に出力する。制御部40は、制御信号CTとしてタイミング信号例えばクロック信号や同期信号、フレームメモリ21aやラインメモリ21bにおける画像信号の書き込みや読み出しを制御するための信号を生成する。また、制御部40は、制御信号CTとしてソースドライバを駆動するための水平スタート信号や水平クロック信号、ゲートドライバを駆動するための垂直スタート信号や垂直クロック信号等を生成する。

40

#### 【0052】

<2. 画像処理装置の動作>

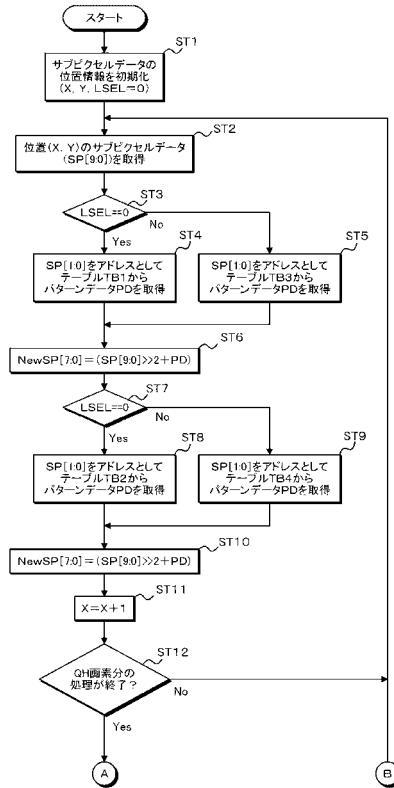

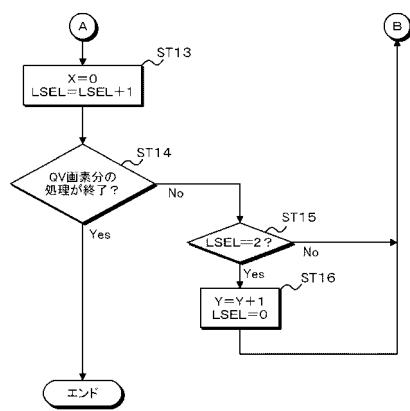

次に、画像信号処理装置の動作について説明する。図7, 図8は、画像信号処理装置における多階調化処理部22の動作を示すフローチャートである。なお、以下の説明は、画像信号処理装置20-LUにおける多階調化処理部の動作についての説明である。

#### 【0053】

50

ステップ S T 1 で多階調化処理部 2 2 は、サブピクセルデータの位置情報を初期化する。多階調化処理部 2 2 は、位置情報の初期化を行い、サブピクセルデータの水平方向の位置 X と垂直方向の位置 Y を「0」とする。また、多階調化処理部 2 2 は、ラインの繰り返しを示すライン情報 L S E L を「0」とする。なお、サブピクセルとは 1 画素が赤、緑、青の画素で構成されるとき、赤、緑、青の各画素がサブピクセルに相当する。また、ライン情報 L S E L は、画像の拡大を行ったときのラインの繰り返し回数を判別可能とする情報である。例えば画像を垂直方向に 2 倍する場合、1 つのラインが二度繰り返される。このとき、1 度目ではライン情報 L S E L が「0」とされて、2 度目ではライン情報 L S E L が「1」とされる。

【0054】

ステップ S T 2 で多階調化処理部 2 2 は、位置 (X, Y) のサブピクセルデータを取得する。多階調化処理部 2 2 は、ラインメモリ 2 1 b から出力された位置 (X, Y) のサブピクセルデータ (10 ビット信号 S P [9:0]) を取得してステップ S T 3 に進む。

【0055】

ステップ S T 3 で多階調化処理部 2 2 は、ライン情報 L S E L が「0」であるか否か判別する。多階調化処理部 2 2 は、ライン情報 L S E L が「0」であるときステップ S T 4 に進み、後述するようにラインの繰り返しが行われてライン情報 L S E L が「0」でなくなったときステップ S T 5 に進む。

【0056】

ステップ S T 4 で多階調化処理部 2 2 は、サブピクセルデータの下位 2 ビット信号 S P [1:0] をアドレスとして、テーブル T B 1 からパターンデータ P D を取得してステップ S T 6 に進む。

【0057】

ステップ S T 5 で多階調化処理部 2 2 は、サブピクセルデータの下位 2 ビット信号 S P [1:0] をアドレスとして、テーブル T B 3 からパターンデータ P D を取得してステップ S T 6 に進む。

【0058】

ステップ S T 6 で多階調化処理部 2 2 は、サブピクセルデータから下位 2 ビットを除いた上位 8 ビット信号 S P [9:2] にパターンデータ P D を加算して、ビット深度が 8 ビットである新たな信号 S P [7:0] を生成してステップ S T 7 に進む。

【0059】

ステップ S T 7 で多階調化処理部 2 2 は、ライン情報 L S E L が「0」であるか否か判別する。多階調化処理部 2 2 は、ライン情報 L S E L が「0」であるときステップ S T 8 に進み、後述するようにラインの繰り返しが行われてライン情報 L S E L が「0」でなくなったときステップ S T 9 に進む。

【0060】

ステップ S T 8 で多階調化処理部 2 2 は、サブピクセルデータの下位 2 ビット信号 S P [1:0] をアドレスとして、テーブル T B 2 からパターンデータ P D を取得してステップ S T 10 に進む。

【0061】

ステップ S T 9 で多階調化処理部 2 2 は、サブピクセルデータの下位 2 ビット信号 S P [1:0] をアドレスとして、テーブル T B 4 からパターンデータ P D を取得してステップ S T 10 に進む。

【0062】

ステップ S T 10 で多階調化処理部 2 2 は、サブピクセルデータから下位 2 ビットを除いた上位 8 ビット信号 S P [9:2] にパターンデータ P D を加算して、ビット深度が 8 ビットである新たな信号 S P [7:0] を生成してステップ S T 11 に進む。

【0063】

ステップ S T 11 で多階調化処理部 2 2 は、サブピクセルデータの水平方向の位置 X に「1」を加算して新たな位置 X としてステップ S T 12 に進む。

10

20

30

40

50

## 【0064】

ステップST12で多階調化処理部22は、1/4の領域の水平方向の画素数QH分の処理が終了したか否か判別する。多階調化処理部22は、位置Xが1/4の領域を超えていないときステップST2に戻り、位置Xが1/4の領域を超えているとき図8のステップST13に進む。

## 【0065】

ステップST13で多階調化処理部22は、繰り返されている2ライン目の処理のための初期化を行う。多階調化処理部22は、2ライン目の処理を開始するため、位置Xの初期化を行い位置Xを「0」とする。また、2ライン目の処理であることを識別可能とするためライン情報LSELに「1」を加算して、新たなライン情報LSELとしてステップST14に進む。10

## 【0066】

ステップST14で多階調化処理部22は、1/4の領域の垂直方向の画素数QV分の処理が終了したか否か判別する。多階調化処理部22は、位置Yが1/4の領域を超えていないときステップST15に進み、位置Yが1/4の領域を超えているとき、1/4の領域の1フレーム画像に対する処理を終了する。

## 【0067】

ステップST15で多階調化処理部22は、ライン情報LSELが「2」であるか否か判別する。多階調化処理部22は、ライン情報LSELが「2」であるときステップST16に進み、ライン情報LSELが「2」となっていないとき、図7のステップST2に戻る。ここで、1ライン目の処理が完了するとステップST13の処理によって、ライン情報LSELは「1」とされる。また、繰り返しが行われている2ライン目の処理が完了するとステップST13の処理によって、ライン情報LSELは「2」とされる。したがって、多階調化処理部22は、ライン情報LSELが「1」であるときステップST2に戻り、繰り返されている2ライン目の処理を行う。また、多階調化処理部22は、繰り返されている2ライン目の処理が完了してライン情報LSELが「2」とされたときステップST16に進む。20

## 【0068】

ステップST16で多階調化処理部22は、サブピクセルデータの垂直方向の位置Yに「1」を加算して新たな位置Yとする。さらに、多階調化処理部22はライン情報LSELの初期化を行い、ライン情報LSELを「0」に設定してステップST2に戻る。30

## 【0069】

このようにすれば、入力画像の1画素を繰り返した領域の各画素において、画像信号の下位2ビット信号SP[1:0]に応じたパターンデータを上位8ビット信号SP[9:2]に加算して、ビット深度が8ビットの画像信号DVd-LUを生成できる。

## 【0070】

なお、画像信号処理装置20-RU, 20-LL, 20-RLにおける多階調化処理部も、それぞれ1/4の領域における最初の画素位置を初期位置として、画像信号処理装置20-LUにおける多階調化処理部と同様な処理を行うことで、画像信号DVd-RU, DVd-LL, DVd-RLを生成できる。40

## 【0071】

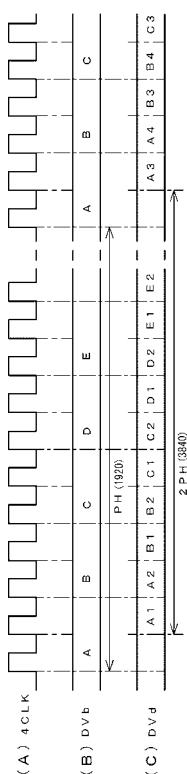

図9は、画像信号処理装置の動作を示している。図9の(A)はクロック信号4CLK、図9の(B)はラインメモリから多階調化処理部に供給される画像信号DVb、図9の(C)は多階調化処理部から出力される画像信号DVdを示している。

## 【0072】

入力画像の画像信号DVaがライン毎に記憶されるラインメモリ21bからは、水平方向の画素数が2倍となるように、画素信号の読み出しを行う。クロック信号4CLKは、例えば入力画像の画像信号DVaの画素タイミングを示すクロック信号CLKの4倍の周波数とされている。このクロック信号4CLKに同期してラインメモリ21bから画像信号を画素毎に2回繰り返して読み出すことで、水平方向の画素数が2倍とされた画像信号50

を生成する。また、クロック信号 4 C L K の 1 / 2 の周波数でラインメモリ 2 1 b から画素信号を順次読み出して、多階調化処理部 2 2 は、クロック信号 4 C L K に同期してパターンデータの出力を行い、水平方向の画素数が 2 倍とされた画像信号 D V d を生成してもよい。なお、図 9 の (B) は、クロック信号 4 C L K の 1 / 2 の周波数でラインメモリ 2 1 b から画像信号を画素毎に順次読み出した場合を示している。

#### 【0073】

また、図 9 の (B) に示すように、ラインメモリ 2 1 b から 1 ライン分の画像信号の出力が完了したときは、同じ 1 ライン分の画像信号の出力を繰り返すことで、垂直方向の画素数が 2 倍とされた画像信号を生成する。

#### 【0074】

画像拡大処理部 2 1 は、このようにラインメモリ 2 1 b から画像信号の読み出しを行い、入力画像の 1 画素を拡大画像において隣り合う 2 画素 × 2 画素にマッピングして、水平および垂直方向の画素数がそれぞれ 2 倍とされた拡大画像の画像信号を生成する。

#### 【0075】

多階調化処理部 2 2 は、クロック信号 4 C L K に同期して、多階調化処理を行う。例えば、ラインメモリ 2 1 b からの 1 ライン分の画像信号の読み出しが 1 回目であるとき、パターンデータ出力部 2 2 a は、読み出された画素 A の下位 2 ビット信号 S P [1:0] をアドレス信号とする。また、パターンデータ出力部 2 2 a は、クロック信号 4 C L K に同期してテーブル T B 1 と T B 2 からアドレス信号によって示されたパターンデータ P D を順に加算部 2 2 b に出力する。加算部 2 2 b は、画素 A の上位 8 ビット信号 S P [9:2] にパターンデータを加算して、繰り返し領域の画素 A 1 , A 2 の画像信号として出力する。また、多階調化処理部 2 2 は同様な処理を画素 B 以降に対しても行い、水平方向の画素数が 2 倍とされた画像信号を生成する。

#### 【0076】

次に、ラインメモリ 2 1 b からの 1 ライン分の画像信号の読み出しが 2 回目であるとき、パターンデータ出力部 2 2 a は、読み出された画素 A の下位 2 ビット信号 S P [1:0] をアドレス信号とする。また、パターンデータ出力部 2 2 a は、クロック信号 4 C L K に同期してテーブル T B 3 と T B 4 からアドレス信号によって示されたパターンデータ P D を順に加算部 2 2 b に出力する。加算部 2 2 b は、画素 A の上位 8 ビット信号 S P [9:2] にパターンデータを加算して、繰り返し領域の画素 A 3 , A 4 の画像信号として出力する。また、多階調化処理部 2 2 は同様な処理を画素 B 以降に対しても行い、水平方向および垂直方向の画素数がそれぞれ 2 倍とされた画像信号 D V d を生成する。

#### 【0077】

このような処理を行うと、図 10 の (A) に示す画像は、図 10 の (B) に示すように、水平方向および垂直方向の画素数がそれぞれ 2 倍とされた画像となる。さらに、入力画像の 1 画素が表示画像における 4 画素とされて、この 4 画素の領域である繰り返し領域の画素でディザリングが行われて、ビット深度を 10 ビットから 8 ビットに低下させることによる階調の劣化を補償した画像信号 D V d を生成できる。したがって、入力画像の画像信号よりも高解像度の表示デバイスを用いて画像表示を行い、この表示デバイスが入力画像の画像信号に対応する階調特性を満たしていくとも、広い階調表現が可能となる。

#### 【0078】

なお、上述の実施の形態では、H D サイズの画像を示す画像信号を用いて 4 K 2 K の表示サイズで画像表示を行う場合、入力画像を 1 / 4 に分割して並列処理を行う場合について説明したが、入力画像を 1 / 2 に分割して並列処理を行ってもよい。また、高速な処理が可能であるときは、画像を分割することなく処理を行ってもよい。また、画像を分割する場合、図 2 に示すように水平方向と垂直方向をそれぞれ分割する場合に限られない。例えば水平方向または垂直方向のいずれか一方のみで画像の分割を行ってもよい。

#### 【0079】

さらに、多階調化処理部 2 2 のパターンデータ出力部 2 2 a では、下位ビット信号 S P [1:0] に応じたパターンデータとして異なるパターンのデータを記憶しておき、パター

10

20

30

40

50

ンデータを切り替えて出力してもよい。パターンデータの切り替えは、空間方向に対して行ってもよく、時間方向に行ってもよい。また、パターンデータの切り替えは、ランダムにパターンを切り替えることが好ましい。

#### 【0080】

例えば図9において、画素Aと画素Bの信号レベルが等しい場合、空間方向に対してパターンデータの切り替えを行う。この場合、画素Aに対応する繰り返し領域では、画素A1の上位8ビット信号SP[9:2]に対してのみ「1」を加算する。また、画素Bに対応する繰り返し領域では、画素B1と異なる画素B2～B4のいずれか1つの画素の上位8ビット信号SP[9:2]に対してのみ「1」を加算する。このようにすれば、拡大画像において上位8ビット信号SP[9:2]に「1」が加算された画素の規則性のためにモアレやビート状のノイズ等が生じてしまうことを防止できる。10

#### 【0081】

また、例えば図9において、画素Aと次のフレームの画素Aの信号レベルが等しい場合、時間方向に対してパターンデータの切り替えを行う。この場合、最初のフレームの画素Aに対応する繰り返し領域では画素A1の上位8ビット信号SP[9:2]に対してのみ「1」を加算する。また、次のフレームの画素Aに対応する繰り返し領域では画素A1と異なる画素A2～A4のいずれか1つの画素の上位8ビット信号SP[9:2]に対してのみ「1」を加算する。このようにすれば、動画像を拡大表示する場合、拡大画像において上位8ビット信号SP[9:2]に「1」が加算された画素の規則性のためにモアレやビート状のノイズ等が生じてしまうことを防止できる。20

#### 【0082】

さらに、ビット深度の変換や画像の拡大は、上述の実施の形態に限られない。例えば、画像信号を所定ビット数の画像信号に変換するとき、上位側の所定ビット数を除いた信号がmビットである場合は、拡大画像における繰り返し領域の画素数を「 $2^m$ 」以上とする。このように画像を拡大すれば、繰り返し領域の画素でmビットの信号に応じた誤差拡散を行うことにより、画像信号を所定ビット数の画像信号に変換させたことによる階調の劣化を補償することができる。

#### 【0083】

また、繰り返し領域の画素数が「 $2^n$ 」であるとき、画像信号から上位側の所定ビット数を除いた信号の上位側からnビットの信号に応じたパターンデータをパターンデータ出力部から出力する。このようにパターンデータの出力を行えば、繰り返し領域の画素数に応じた誤差拡散を行うことが可能となり、画像信号を所定ビット数の画像信号に変換させたことによる階調の劣化を軽減できる。30

#### 【0084】

なお、明細書中において説明した一連の処理はハードウェア、またはソフトウェア、あるいは両者の複合構成によって実行することが可能である。ソフトウェアによる処理を実行する場合は、処理シーケンスを記録したプログラムを、専用のハードウェアに組み込まれたコンピュータ内のメモリにインストールして実行させる。あるいは、各種処理が実行可能な汎用コンピュータにプログラムをインストールして実行させることができる。

#### 【0085】

例えば、プログラムは記録媒体としてのハードディスクやROM(Read Only Memory)に予め記録しておくことができる。あるいは、プログラムはフレキシブルディスク、CD-R OM(Compact Disc Read Only Memory), MO(Magneto optical)ディスク、DVD(Digital Versatile Disc)、磁気ディスク、半導体メモリなどのリムーバブル記録媒体に、一時的あるいは永続的に格納(記録)しておくことができる。このようなリムーバブル記録媒体は、いわゆるパッケージソフトウェアとして提供することができる。40

#### 【0086】

なお、プログラムは、上述したようなリムーバブル記録媒体からコンピュータにインストールする他、ダウンロードサイトから、コンピュータに無線転送したり、LAN(Local Area Network)、インターネットといったネットワークを介して、コンピュータに有線で

10

20

30

40

50

転送し、コンピュータでは、そのようにして転送されてくるプログラムを受信し、内蔵するハードディスク等の記録媒体にインストールすることができる。

### 【0087】

以上、特定の実施例を参照しながら、本発明について詳解してきた。しかしながら、本発明の要旨を逸脱しない範囲で当業者が該実施例の修正や代用を成し得ることは自明である。すなわち、例示という形態で本発明を開示してきたのであり、限定的に解釈されるべきではない。本発明の要旨を判断するためには、特許請求の範囲を参照すべきである。

### 【産業上の利用可能性】

### 【0088】

この発明の画像信号処理装置と画像信号処理方法および画像表示装置では、画素の繰り返しを行い拡大された画像の画像信号が生成される。また、画素を繰り返した繰り返し領域毎に、拡大された画像の画像信号から上位側の所定ビット数を除いた信号に基づく階調を繰り返し領域の画素で再現するためのパターンデータが拡大された画像の画像信号における上位側の所定ビット数の信号に加算されて、画像信号のビット深度を小さくしても広い階調表現の拡大表示を行うことができる。したがって、高解像度の画像表示を行う機器に適している。

### 【符号の説明】

### 【0089】

20 , 20-LU , 20-RU , 20-LL , 20-RL ··· 画像信号処理装置、 21 ··· 画像拡大処理部、 21 a ··· フレームメモリ、 21 b ··· ラインメモリ、 22 ··· 多階調化処理部、 22 a ··· パターンデータ出力部、 22 b ··· 加算部、 30 ··· 表示部、 31 ··· 表示デバイス、 32-LL , 32-LU , 32-RU , 32-LL , 32-RL ··· ソースドライバ、 33-LU , 33-RU , 33-LL , 33-RL ··· ゲートドライバ、 34 ··· 階調電圧生成部、 40 ··· 制御部

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

(A)

(B)

(C)

(D)

【図6】

| SP[1] | SP[0] | テーブル |     |     |     |

|-------|-------|------|-----|-----|-----|

|       |       | TB1  | TB2 | TB3 | TB4 |

| 0     | 0     | 0    | 0   | 0   | 0   |

| 0     | 1     | 1    | 0   | 0   | 0   |

| 1     | 0     | 1    | 0   | 0   | 1   |

| 1     | 1     | 1    | 1   | 1   | 0   |

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 5/36 5 2 0 A |

|              | G 0 9 G | 3/20 6 5 0 C |

|              | G 0 9 G | 3/20 6 4 2 J |

|              | G 0 9 G | 3/20 6 4 1 P |

|              | G 0 9 G | 5/00 5 2 0 A |

(72)発明者 井ノ川 裕幸

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 5C058 BA07 BA17 BB12 BB13

5C080 DD07 EE17 EE21 EE29 JJ02 JJ04 JJ07

5C082 BA12 BB15 CA11 CA33 MM05 MM10