(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7533641号**

**(P7533641)**

(45)発行日 令和6年8月14日(2024.8.14)

(24)登録日 令和6年8月5日(2024.8.5)

(51)国際特許分類

|        |                  |     |        |        |         |

|--------|------------------|-----|--------|--------|---------|

| H 01 L | 29/78 (2006.01)  | F I | H 01 L | 29/78  | 6 5 2 J |

| H 01 L | 21/8234(2006.01) |     | H 01 L | 27/06  | 1 0 2 A |

| H 01 L | 27/06 (2006.01)  |     | H 01 L | 27/088 | C       |

| H 01 L | 27/088(2006.01)  |     | H 01 L | 29/78  | 6 5 5 G |

| H 01 L | 29/739(2006.01)  |     | H 01 L | 29/78  | 6 5 3 A |

請求項の数 11 (全37頁) 最終頁に続く

(21)出願番号 特願2023-3334(P2023-3334)

(22)出願日 令和5年1月12日(2023.1.12)

(62)分割の表示 特願2018-173307(P2018-173307)

)の分割

原出願日 平成30年9月18日(2018.9.18)

(65)公開番号 特開2023-33413(P2023-33413A)

(43)公開日 令和5年3月10日(2023.3.10)

審査請求日 令和5年2月2日(2023.2.2)

(31)優先権主張番号 特願2017-240022(P2017-240022)

(32)優先日 平成29年12月14日(2017.12.14)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000005234

富士電機株式会社

神奈川県川崎市川崎区田辺新田1番1号

(74)代理人 110000877

弁理士法人 R Y U K A 国際特許事務所

(72)発明者 内藤 達也

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

審査官 戸川 匠

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

半導体基板に設けられた第1導電型のドリフト領域と、

前記半導体基板の上面から前記半導体基板の内部まで設けられ、前記半導体基板の上面

において予め定められた延伸方向に延伸して設けられたトレンチ部と、

前記延伸方向と直交する配列方向において前記トレンチ部に挟まれたメサ部と、

活性領域の端部から予め定められた範囲に設けられ、前記トレンチ部よりも深い下端を

有する第2導電型のウェル領域と、

前記半導体基板の上面の上方に設けられた第1電極と、

前記半導体基板の上面と前記第1電極との間に設けられた層間絶縁膜と、

前記層間絶縁膜を貫通して、前記メサ部と前記第1電極とを接続するコンタクトホール

と、

前記メサ部において前記トレンチ部の底部と接して設けられた第2導電型のフローティング領域と、

前記メサ部において前記トレンチ部の上部と接して設けられた、前記ドリフト領域よりもドーピング濃度の高い第1導電型のエミッタ領域と、

を備え、

前記フローティング領域は、前記延伸方向において前記エミッタ領域よりも前記ウェル領域の近くまで設けられており、

前記コンタクトホールは、最も前記ウェル領域側の前記フローティング領域の端よりも

前記ウェル領域から離れた位置から、前記フローティング領域の前記端よりも前記ウェル領域に近い位置まで、前記延伸方向に延伸している

半導体装置。

**【請求項 2】**

半導体基板に設けられた第1導電型のドリフト領域と、

前記半導体基板の上面から前記半導体基板の内部まで設けられ、前記半導体基板の上面において予め定められた延伸方向に延伸して設けられたトレンチ部と、

前記延伸方向と直交する配列方向において前記トレンチ部に挟まれたメサ部と、

活性領域の端部から予め定められた範囲に設けられ、前記トレンチ部よりも深い下端を有する第2導電型のウェル領域と、

前記半導体基板の上面の上方に設けられた第1電極と、

前記半導体基板の上面と前記第1電極との間に設けられた層間絶縁膜と、

前記層間絶縁膜を貫通して、前記メサ部と前記第1電極とを接続するコンタクトホールと、

前記メサ部において前記トレンチ部の底部と接して設けられた第2導電型のフローティング領域と、

前記メサ部において前記トレンチ部の上部と接して設けられ、前記延伸方向に沿って一つ以上配置され、前記ドリフト領域よりもドーピング濃度の高い第1導電型のエミッタ領域と、

を備え、

前記延伸方向に沿って一つ以上配置された前記エミッタ領域のうちの少なくとも一つについて、前記エミッタ領域が前記トレンチ部に接する部分の前記延伸方向の全長が前記フローティング領域と重なっており、

前記コンタクトホールは、最も前記ウェル領域側の前記フローティング領域の端よりも前記ウェル領域から離れた位置から、前記フローティング領域の前記端よりも前記ウェル領域に近い位置まで、前記延伸方向に延伸している

半導体装置。

**【請求項 3】**

半導体基板に設けられた第1導電型のドリフト領域と、

前記半導体基板の上面から前記半導体基板の内部まで設けられ、前記半導体基板の上面において予め定められた延伸方向に延伸して設けられたトレンチ部と、

前記延伸方向と直交する配列方向において前記トレンチ部に挟まれたメサ部と、

活性領域の端部から予め定められた範囲に設けられ、前記トレンチ部よりも深い下端を有する第2導電型のウェル領域と、

前記半導体基板の上面の上方に設けられた第1電極と、

前記半導体基板の上面と前記第1電極との間に設けられた層間絶縁膜と、

前記層間絶縁膜を貫通して、前記メサ部と前記第1電極とを接続するコンタクトホールと、

前記メサ部において前記トレンチ部の底部と接して設けられた第2導電型のフローティング領域と、

を備え、

前記コンタクトホールは、最も前記ウェル領域側の前記フローティング領域の端よりも前記ウェル領域から離れた位置から、前記フローティング領域の前記端よりも前記ウェル領域に近い位置まで、前記延伸方向に延伸しており、

前記ウェル領域は、前記延伸方向に離れて2つ配置されており、

前記フローティング領域は、前記延伸方向において、2つの前記ウェル領域の間で連続している

半導体装置。

**【請求項 4】**

半導体基板に設けられた第1導電型のドリフト領域と、

10

20

30

40

50

前記半導体基板の上面から前記半導体基板の内部まで設けられ、前記半導体基板の上面において予め定められた延伸方向に延伸して設けられたトレンチ部と、

前記延伸方向と直交する配列方向において前記トレンチ部に挟まれたメサ部と、

活性領域の端部から予め定められた範囲に設けられ、前記トレンチ部よりも深い下端を有する第2導電型のウェル領域と、

前記半導体基板の上面の上方に設けられた第1電極と、

前記半導体基板の上面と前記第1電極との間に設けられた層間絶縁膜と、

前記層間絶縁膜を貫通して、前記メサ部と前記第1電極とを接続するコンタクトホールと、

前記メサ部において前記トレンチ部の底部と接して設けられた第2導電型のフローティング領域と、

前記メサ部において前記トレンチ部の上部と接して設けられた、前記ドリフト領域よりもドーピング濃度の高い第1導電型のエミッタ領域と、

を備え、

前記コンタクトホールは、最も前記ウェル領域側の前記フローティング領域の端よりも前記ウェル領域から離れた位置から、前記フローティング領域の前記端よりも前記ウェル領域に近い位置まで、前記延伸方向に延伸しており、

前記コンタクトホールは、最も前記ウェル領域側の前記エミッタ領域の端よりも前記ウェル領域から離れた位置から、前記フローティング領域の前記端よりも前記ウェル領域に近い位置まで、前記延伸方向に延伸している

半導体装置。

【請求項5】

前記ウェル領域は、前記延伸方向に離れて2つ配置されており、

前記フローティング領域は、前記延伸方向において、2つの前記ウェル領域の間で離散的に複数設けられている

請求項1、2および4のいずれか一項に記載の半導体装置。

【請求項6】

前記メサ部において前記フローティング領域の上方に設けられた第2導電型のベース領域を備え、

前記ベース領域の前記延伸方向の端は、前記ウェル領域に接続されている

請求項1から5のいずれか1項に記載の半導体装置。

【請求項7】

前記フローティング領域は、深さ方向において、前記ベース領域から離間している

請求項6に記載の半導体装置。

【請求項8】

前記深さ方向において、前記フローティング領域と前記ベース領域との間には、前記ドリフト領域または第1導電型の他の半導体領域が設けられている

請求項7に記載の半導体装置。

【請求項9】

前記フローティング領域は、前記延伸方向において、前記エミッタ領域よりも広い範囲に渡って設けられている

請求項4に記載の半導体装置。

【請求項10】

前記メサ部に設けられ前記半導体基板の上面から露出した、前記ベース領域よりもドーピング濃度の高い第2導電型のコンタクト領域を備え、

前記コンタクトホールの前記延伸方向の端は、前記コンタクト領域の上方に配置されている

請求項6から8のいずれか1項に記載の半導体装置。

【請求項11】

前記ウェル領域は、前記延伸方向における前記トレンチ部の端の底を覆っている

10

20

30

40

50

請求項 1 から 1\_0 のいずれか 1 項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。

【背景技術】

【0002】

従来、絶縁ゲート型バイポーラトランジスタ（IGBT）等の半導体装置が知られています。（例えば、特許文献1および2参照）。

特許文献1 特開2004-103980号公報

特許文献2 特開2010-114136号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0003】

半導体装置においては、ターンオン損失を低減することが好ましい。

【課題を解決するための手段】

【0004】

本発明の第1の態様においては、半導体基板に設けられた第1導電型のドリフト領域と、前記半導体基板の上面から前記半導体基板の内部まで設けられ、前記半導体基板の上面において予め定められた延伸方向に延伸して設けられたトレンチ部と、前記延伸方向と直交する配列方向において前記トレンチ部に挟まれたメサ部と、活性領域の端部から予め定められた範囲に設けられ、前記トレンチ部よりも深い下端を有する第2導電型のウェル領域と、前記半導体基板の上面の上方に設けられた第1電極と、前記半導体基板の上面と前記第1電極との間に設けられた層間絶縁膜と、前記層間絶縁膜を貫通して、前記メサ部と前記第1電極とを接続するコンタクトホールと、前記メサ部において前記トレンチ部の底部と接して設けられた第2導電型のフローティング領域と、を備え、前記コンタクトホールは、最も前記ウェル領域側の前記フローティング領域の端よりも前記ウェル領域から離れた位置から、前記フローティング領域の前記端よりも前記ウェル領域に近い位置まで、前記延伸方向に延伸している半導体装置を提供する。

20

【0005】

本発明の他の態様においては、半導体装置を提供する。半導体装置は、半導体基板と、半導体基板に設けられた第1導電型のドリフト領域と、半導体基板の上面から半導体基板の内部まで設けられ、半導体基板の上面において予め定められた延伸方向に延伸して設けられたゲートトレンチ部を備える。延伸方向と直交する配列方向には、ゲートトレンチ部と接して設けられたメサ部を備える。メサ部においては、ドリフト領域の上方に設けられ、且つ、ゲートトレンチ部に接して設けられた、ドリフト領域よりもドーピング濃度の高い、一つ以上の第1導電型の蓄積領域と、メサ部において蓄積領域の上方に設けられ、且つ、ゲートトレンチ部に接して設けられた第2導電型のベース領域と、メサ部において蓄積領域の下方に設けられ、ゲートトレンチ部に接して設けられ、且つ、配列方向においてメサ部の一部分に設けられた第2導電型のフローティング領域と、を備える。フローティング領域は、半導体基板の深さ方向において、蓄積領域と離間して設けられてよい。半導体基板の深さ方向におけるフローティング領域の少なくとも一部は、ゲートトレンチ部の底部と接して設けられてよい。

40

【0006】

半導体装置は、蓄積領域を、半導体基板の深さ方向に複数備えてよい。複数の蓄積領域のうち、最も下方に設けられた蓄積領域のドーピング濃度は、最も上方に設けられた蓄積領域のドーピング濃度よりも低くてよい。

【0007】

ベース領域とフローティング領域との半導体基板の深さ方向の距離は、ベース領域の半導体基板の深さ方向の幅よりも大きくてよい。フローティング領域の配列方向の幅は、メ

50

サ部の配列方向の幅の 0 . 1 倍以上 0 . 5 倍以下であってよい。

**【 0 0 0 8 】**

メサ部において、配列方向にフローティング領域と隣接する領域には、ドリフト領域が設けられてよい。フローティング領域の配列方向の幅は、フローティング領域が設けられた深さにおけるドリフト領域の配列方向の幅よりも小さくてよい。

**【 0 0 0 9 】**

フローティング領域のドーピング濃度は、蓄積領域のドーピング濃度よりも高くてよい。フローティング領域のドーピング濃度は、 $1 \times 10^{19} / \text{cm}^3$  以上であってよい。

**【 0 0 1 0 】**

半導体装置は、半導体基板の上面から半導体基板の内部まで設けられ、半導体基板の上面において延伸方向に延伸し、ゲートトレンチ部とメサ部を挟むように設けられたダミートレンチ部と、メサ部において蓄積領域の下方に設けられ、ダミートレンチ部に接して設けられ、且つ、配列方向においてメサ部の一部分に設けられた第 2 導電型のフローティング領域をさらに備えてよい。ゲートトレンチ部に接するフローティング領域と、ダミートレンチ部に接するフローティング領域とは、配列方向において離間して配置されてよい。

10

**【 0 0 1 1 】**

半導体基板には、ゲートトレンチ部を含むトランジスタ部と、ダイオード部とが設けられてよい。ダイオード部は、ドリフト領域と、半導体基板の上面から半導体基板の内部まで設けられ、延伸方向に延伸して設けられたダミートレンチ部と、配列方向に、ダミートレンチ部と接して設けられたメサ部と、メサ部においてドリフト領域の上方に設けられ、且つ、ダミートレンチ部に接して設けられたベース領域を備えてよい。ダイオード部に設けられたダミートレンチ部には、フローティング領域が設けられなくてよい。

20

**【 0 0 1 2 】**

半導体基板には、ゲートトレンチ部を含むトランジスタ部と、トランジスタ部に含まれる境界部とが設けられてよい。境界部は、ドリフト領域と、半導体基板の上面から半導体基板の内部まで設けられ、延伸方向に延伸して設けられたダミートレンチ部と、配列方向に、ダミートレンチ部と接して設けられたメサ部と、メサ部においてドリフト領域の上方に設けられ、且つ、ダミートレンチ部に接して設けられたベース領域を備えてよい。境界部に設けられたダミートレンチ部には、フローティング領域が設けられなくてよい。

**【 0 0 1 3 】**

30

複数のフローティング領域が、ゲートトレンチ部の延伸方向において、離散的に配置されていてよい。

**【 0 0 1 4 】**

ゲートトレンチ部と接するメサ部の上面には、ドリフト領域よりもドーピング濃度の高い第 1 導電型のエミッタ領域と、第 2 導電型のコンタクト領域とが、延伸方向において交互に配置されていてよい。それぞれのフローティング領域は、延伸方向において、エミッタ領域よりも広い範囲に渡って設けられていてよい。

**【 0 0 1 5 】**

本発明の第 2 の態様においては、半導体装置を提供する。半導体装置は、半導体基板と、半導体基板に設けられた第 1 導電型のドリフト領域と、半導体基板の上面から半導体基板の内部まで設けられ、半導体基板の上面において予め定められた延伸方向に延伸して設けられたゲートトレンチ部を備える。延伸方向と直交する配列方向には、ゲートトレンチ部と接して設けられたメサ部を備える。メサ部においては、ドリフト領域の上方に設けられ、且つ、ゲートトレンチ部に接して設けられた第 2 導電型のベース領域と、メサ部においてベース領域の下方に設けられ、ゲートトレンチ部に接して設けられ、且つ、配列方向においてメサ部の一部分に設けられた第 2 導電型のフローティング領域と、を備える。半導体装置において、ベース領域とフローティング領域との半導体基板の深さ方向の距離は、ベース領域の半導体基板の深さ方向の幅よりも大きい。

40

**【 0 0 1 6 】**

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではない。また

50

、これらの特徴群のサブコンビネーションもまた、発明となりうる。

【図面の簡単な説明】

【0017】

【図1a】本実施形態に係る半導体装置100の上面の一例を部分的に示す図である。

【図1b】図1aにおけるa-a'断面の一例を示す図である。

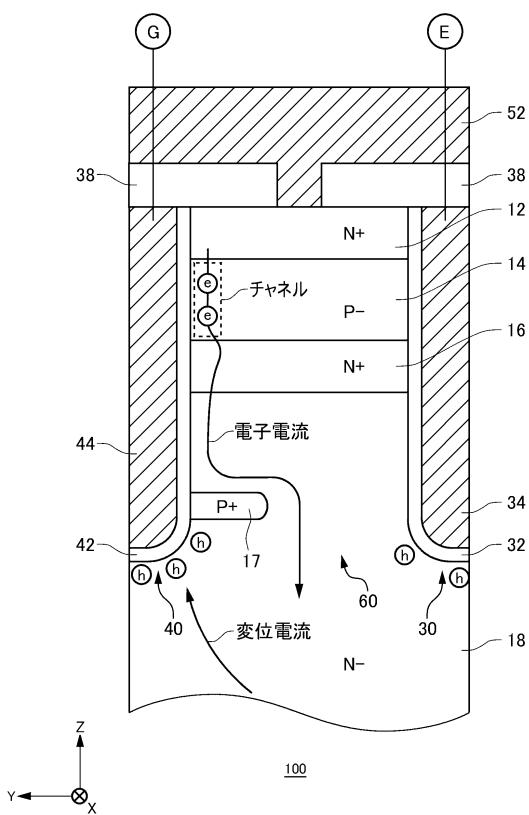

【図2a】第1比較例の半導体装置150における電子電流および変位電流の経路を示す図である。

【図2b】第2比較例の半導体装置160における電子電流および変位電流の経路を示す図である。

【図3】本実施形態の半導体装置100における電子電流および変位電流の経路の一例を示す図である。 10

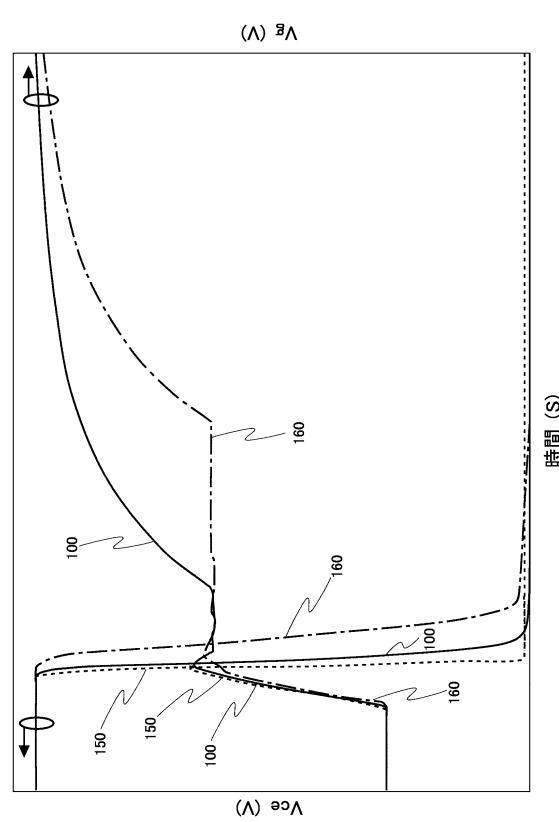

【図4a】ターンオン時におけるゲート電圧V<sub>g</sub>およびCE電圧V<sub>c-e</sub>の時間波形の一例を示す図である。

【図4b】図4aの時間波形において、ゲート電圧V<sub>g</sub>およびCE電圧V<sub>c-e</sub>が遷移波形を拡大した図である。

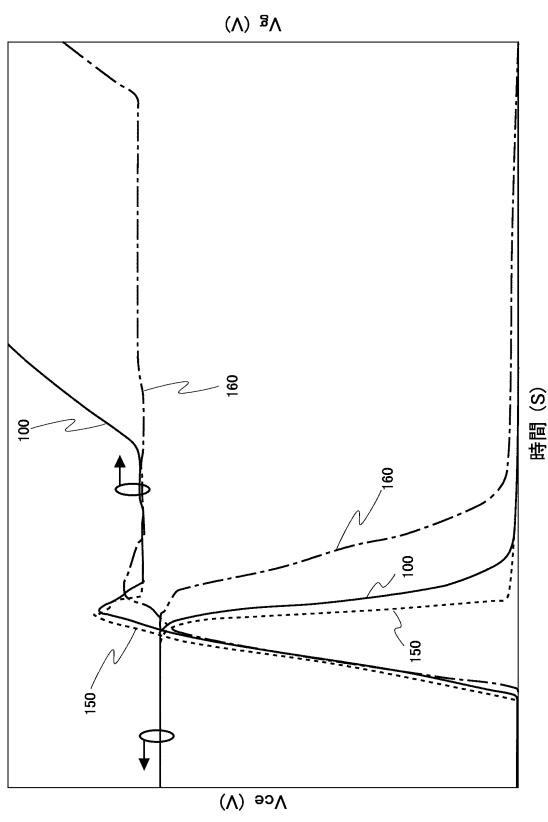

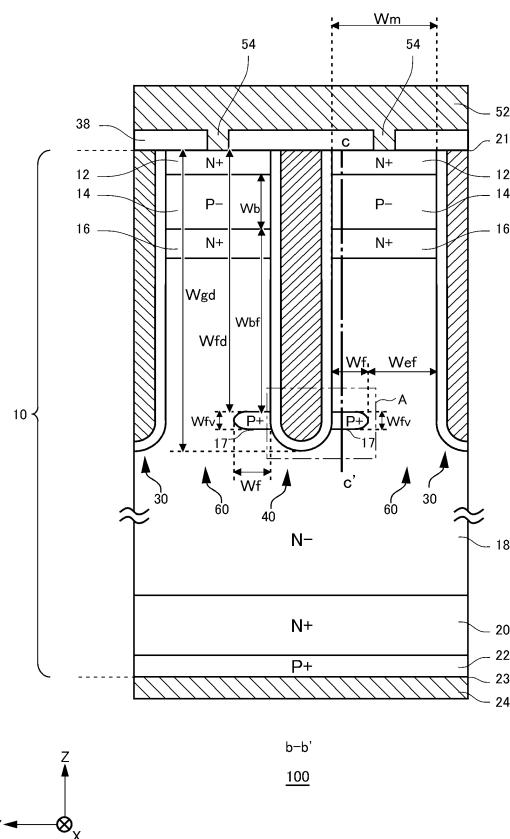

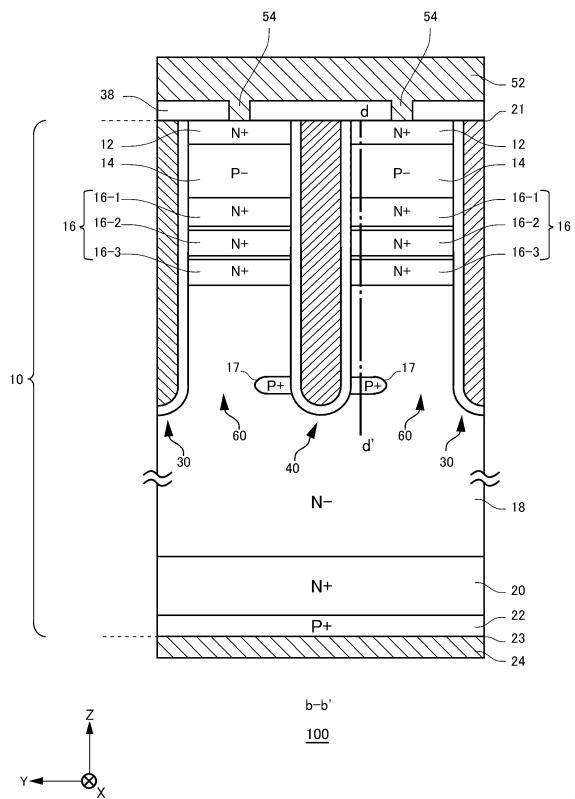

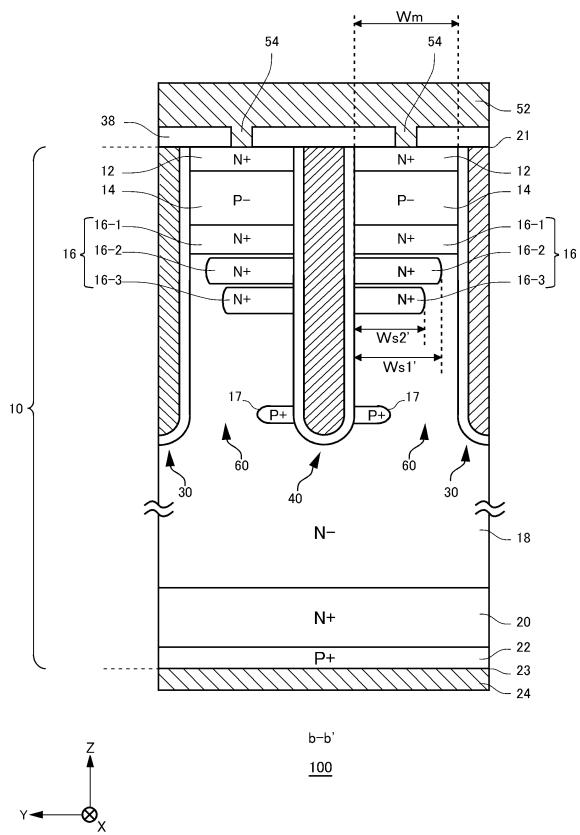

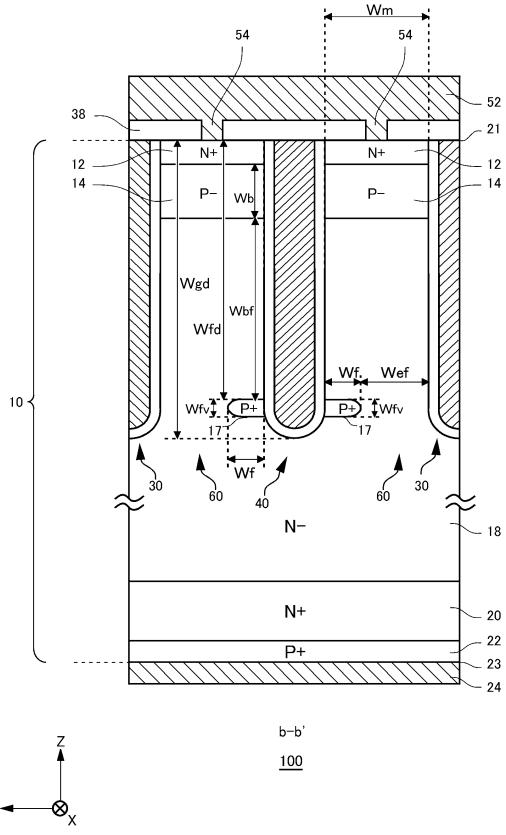

【図5a】図1aにおけるb-b'断面の一例を示す図である。

【図5b】図5aにおける領域Aの拡大図である。

【図6a】本例の半導体装置100における幅比W<sub>f-d</sub>/W<sub>g-d</sub>とオン電圧V<sub>on</sub>との関係の一例を示す図である。

【図6b】本例の半導体装置100における、幅比W<sub>f-d</sub>/W<sub>g-d</sub>とゲート電極に蓄積される電荷Q<sub>g</sub>との関係の一例を示す図である。 20

【図6c】本例の半導体装置100における、幅比W<sub>f-d</sub>/W<sub>g-d</sub>とCE電圧の電圧減少率(dV<sub>c-e</sub>/dt)との関係の一例を示す図である。

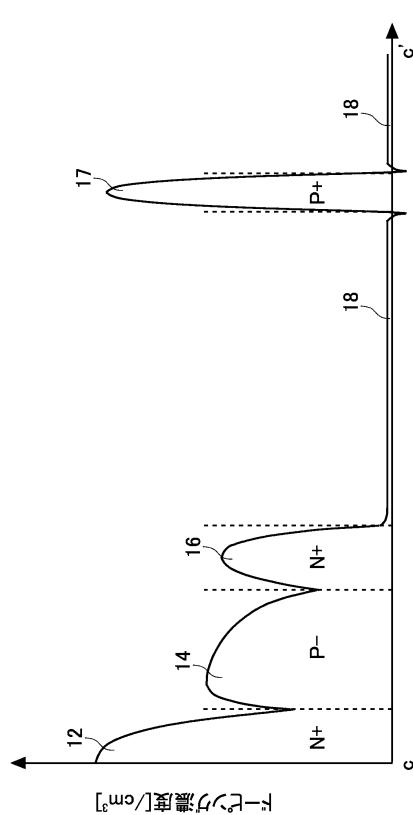

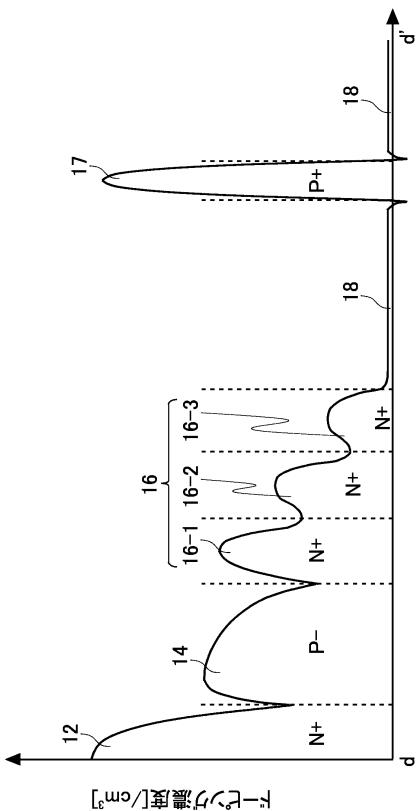

【図7】図5aのc-c'断面におけるドーピング濃度分布の一例を示す図である。

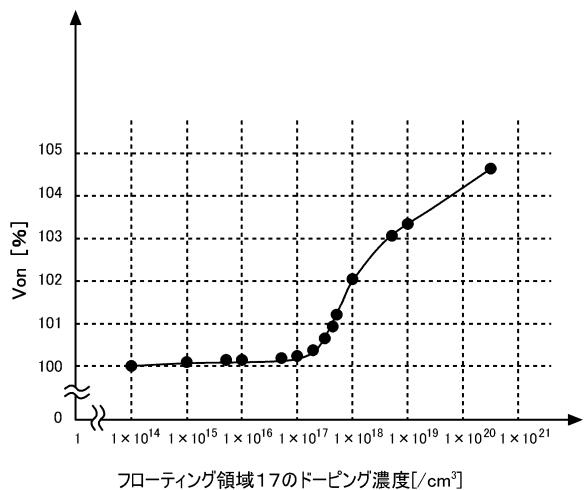

【図8a】本例の半導体装置100における、フローティング領域17のドーピング濃度とオン電圧V<sub>on</sub>との関係の一例を示す図である。

【図8b】本例の半導体装置100における、フローティング領域17のドーピング濃度とCE電圧減少率(dV<sub>c-e</sub>/dt)との関係の一例を示す図である。

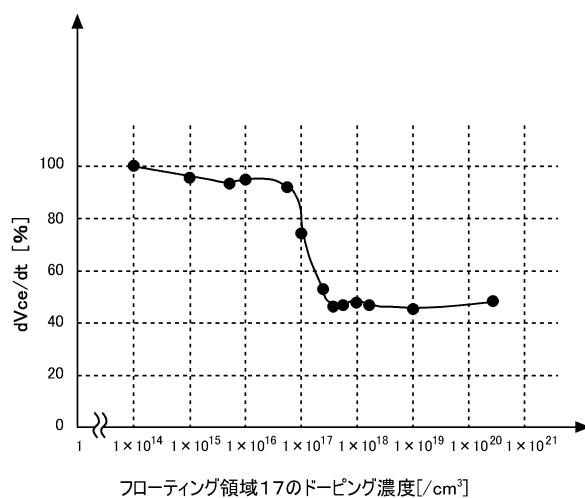

【図9a】本例の半導体装置100における、幅W<sub>m</sub>に占める幅W<sub>f</sub>の割合(W<sub>f</sub>/W<sub>m</sub>)とオン電圧V<sub>on</sub>との関係の一例を示す図である。 30

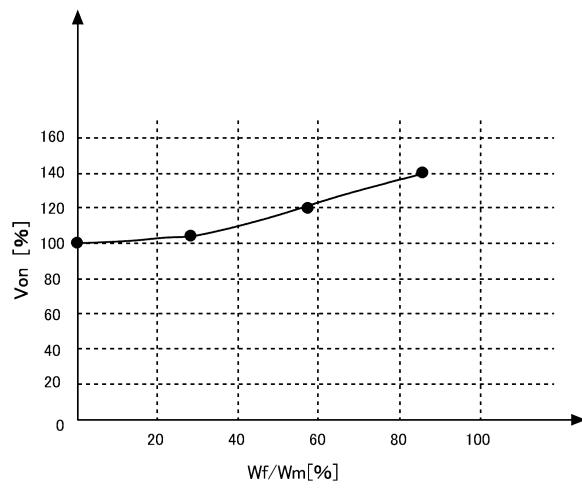

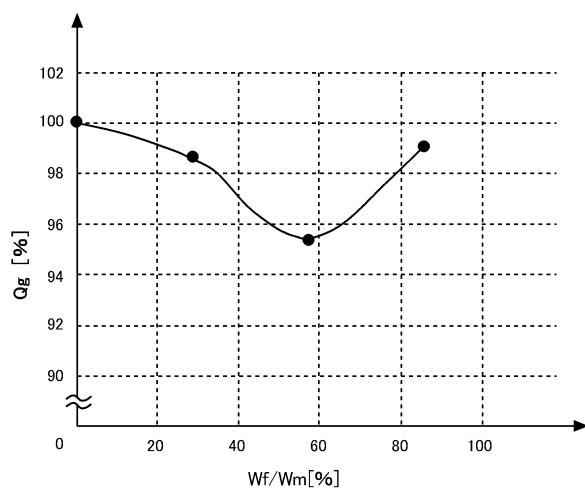

【図9b】本例の半導体装置100における、幅W<sub>m</sub>に占める幅W<sub>f</sub>の割合(W<sub>f</sub>/W<sub>m</sub>)と、ゲート電極に蓄積される電荷Q<sub>g</sub>との関係の一例を示す図である。

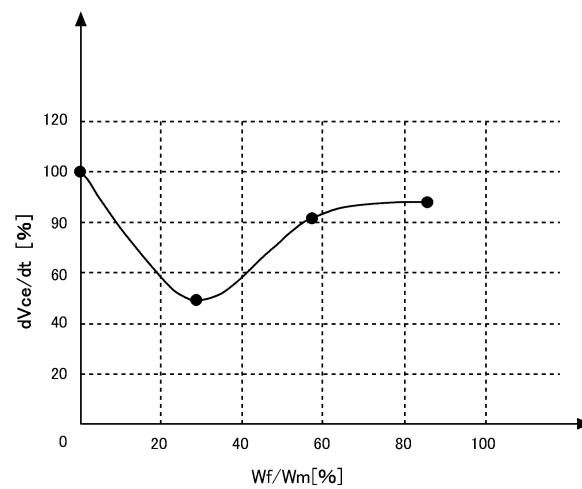

【図9c】本例の半導体装置100における、幅W<sub>m</sub>に占める幅W<sub>f</sub>の割合(W<sub>f</sub>/W<sub>m</sub>)と、CE電圧減少率(dV<sub>c-e</sub>/dt)との関係の一例を示す図である。

【図10】図1におけるb-b'断面の他の一例を示す図である。

【図11】図10のd-d'断面におけるドーピング濃度分布の一例を示す図である。

【図12a】本実施形態に係る半導体装置100の他の上面を部分的に示す図である。

【図12b】図12aにおけるe-e'断面の一例を示す図である。

【図12c】図12におけるe-e'断面の他の一例を示す図である。

【図13a】図1におけるb-b'断面の他の一例を示す図である。 40

【図13b】図1におけるb-b'断面の他の一例を示す図である。

【図14】図1におけるb-b'断面の他の一例を示す図である。

【図15】第1メサ部60におけるフローティング領域17の他の配置例を示す図である。

【図16】半導体基板10の部分的な斜視断面図である。

【発明を実施するための形態】

【0018】

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は特許請求の範囲にかかる発明を限定するものではない。また、実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

【0019】

10

20

30

40

50

本明細書においては半導体基板の深さ方向と平行な方向における一方の側を「上」、他方の側を「下」と称する。基板、層またはその他の部材の2つの主面のうち、一方の面を上面、他方の面を下面と称する。「上」、「下」の方向は重力方向、または、半導体装置の実装時における基板等への取り付け方向に限定されない。

#### 【0020】

本明細書では、X軸、Y軸およびZ軸の直交座標軸を用いて技術的事項を説明する場合がある。本明細書では、半導体基板の上面と平行な面をXY面とし、半導体基板の深さ方向をZ軸とする。

#### 【0021】

各実施例においては、第1導電型をN型、第2導電型をP型とした例を示しているが、

第1導電型をP型、第2導電型をN型としてもよい。この場合、各実施例における基板、

層、領域等の導電型は、それぞれ逆の極性となる。

#### 【0022】

本明細書においてドーピング濃度とは、ドナーまたはアクセプタ化した不純物の濃度を指す。本明細書において、ドナーおよびアクセプタの濃度差をドーピング濃度とする場合がある。また、ドーピングされた領域におけるドーピング濃度分布がピークを有する場合、当該ピーク値を当該ドーピング領域におけるドーピング濃度としてよい。ドーピングされた領域におけるドーピング濃度がほぼ均一な場合等においては、当該ドーピング領域におけるドーピング濃度の平均値をドーピング濃度としてよい。

#### 【0023】

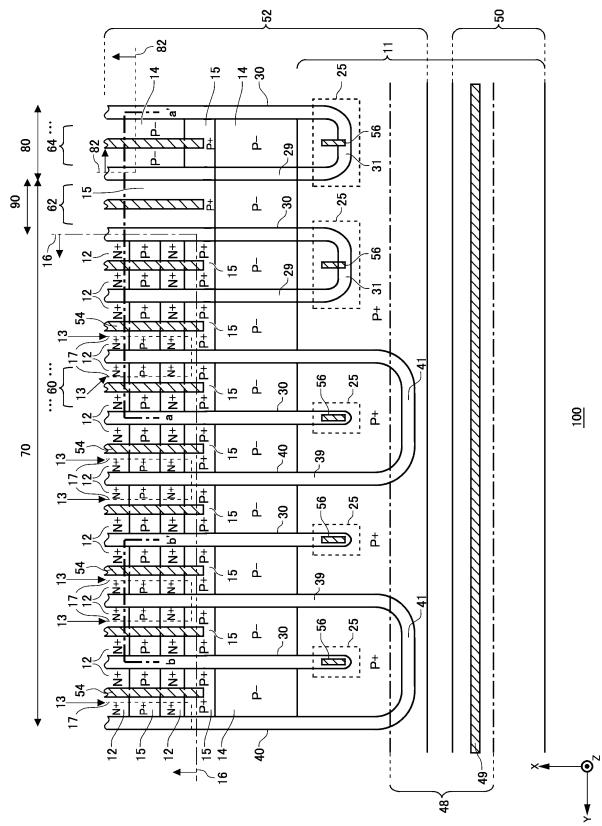

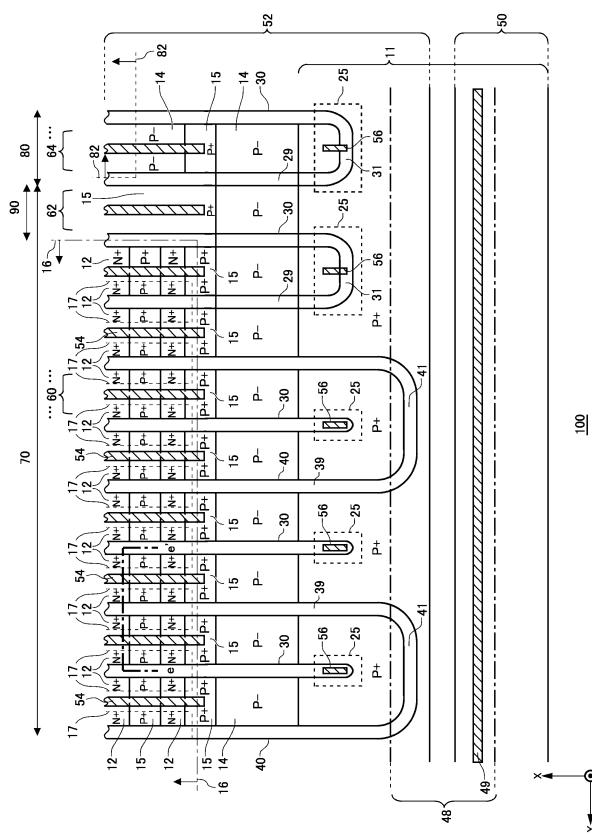

図1aは、本実施形態に係る半導体装置100の上面の一例を部分的に示す図である。本例の半導体装置100は、トランジスタ部70およびダイオード部80を備える半導体チップである。トランジスタ部70は、IGBT等のトランジスタを含む。ダイオード部80は、FWD(Free Wheel Diode)等のダイオードを含む。トランジスタ部70およびダイオード部80は、半導体基板の上面の所定の配列方向(本例ではY軸方向)に並んで配置されている。図1aの例では、トランジスタ部70およびダイオード部80は、配列方向に沿って交互に配置されている。トランジスタ部70およびダイオード部80は、配列方向において接していくよく、離れていてもよい。トランジスタ部70は、境界部90を有してよい。図1aの例では、トランジスタ部70のうち、ダイオード部80との境界に位置する領域が、境界部90である。図1aにおいてはチップ端部周辺のチップ上面を示しており、他の領域を省略している。

#### 【0024】

また、図1aにおいては半導体装置100における半導体基板の活性領域を示すが、半導体装置100は、活性領域を囲んでエッジ終端構造部を有してよい。活性領域は、半導体装置100をオン状態に制御した場合に電流が流れる領域を指す。エッジ終端構造部は、半導体基板の上面側の電界集中を緩和する。エッジ終端構造部は、例えばガードリング、フィールドプレート、リサーフおよびこれらを組み合わせた構造を有する。

#### 【0025】

本例の半導体装置100は、半導体基板の内部に設けられ、且つ、半導体基板の上面に露出するゲートトレニチ部40、ダミートレンチ部30、ウェル領域11、エミッタ領域12、ベース領域14およびコンタクト領域15を備える。また、本例の半導体装置100は、半導体基板の上面の上方に設けられたエミッタ電極52およびゲート金属層50を備える。エミッタ電極52およびゲート金属層50は互いに分離して設けられる。

#### 【0026】

エミッタ電極52およびゲート金属層50と、半導体基板の上面との間には層間絶縁膜が設けられるが、図1aでは省略している。本例の層間絶縁膜には、コンタクトホール56、コンタクトホール49およびコンタクトホール54が、当該層間絶縁膜を貫通して設けられる。

#### 【0027】

また、エミッタ電極52は、コンタクトホール56を通って、ダミートレンチ部30内

10

20

30

40

50

のダミー導電部と接続される。エミッタ電極 52 とダミー導電部との間には、不純物がドープされたポリシリコン等の、導電性を有する材料で形成された接続部 25 が設けられてよい。接続部 25 と半導体基板の上面との間には、酸化膜等の絶縁膜が設けられる。

#### 【 0 0 2 8 】

ゲート金属層 50 は、コンタクトホール 49 を通って、ゲートランナー 48 と接触する。ゲートランナー 48 は、不純物がドープされたポリシリコン等で形成される。ゲートランナー 48 は、半導体基板の上面において、ゲートトレンチ部 40 内のゲート導電部と接続される。ゲートランナー 48 は、ダミートレンチ部 30 内のダミー導電部とは接続されない。本例のゲートランナー 48 は、コンタクトホール 49 の下方から、ゲートトレンチ部 40 の先端部まで設けられる。ゲートランナー 48 と半導体基板の上面との間には、酸化膜等の絶縁膜が設けられる。ゲートトレンチ部 40 の先端部においてゲート導電部は半導体基板の上面に露出しており、ゲートランナー 48 と接触する。

#### 【 0 0 2 9 】

エミッタ電極 52 およびゲート金属層 50 は、金属を含む材料で形成される。例えば、各電極の少なくとも一部の領域はアルミニウムまたはアルミニウムシリコン合金で形成される。各電極は、アルミニウム等で形成された領域の下層にチタンやチタン化合物等で形成されたバリアメタルを有してよく、コンタクトホール内においてタンクステン等で形成されたプラグを有してもよい。

#### 【 0 0 3 0 】

1つ以上のゲートトレンチ部 40 および1つ以上のダミートレンチ部 30 は、所定の配列方向（本例では Y 軸方向）に沿って所定の間隔で配列される。ゲートトレンチ部 40 は、半導体基板の上面に平行であって配列方向と直交する延伸方向（本例では X 軸方向）に沿って延伸する 2 つの延伸部分 39 と、2 つの延伸部分 39 を接続する接続部分 41 を有してよい。接続部分 41 の少なくとも一部は曲線状に設けられることが好ましい。ゲートトレンチ部 40 の 2 つの延伸部分 39 の端部を接続することで、延伸部分 39 の端部における電界集中を緩和することができる。本明細書では、ゲートトレンチ部 40 のそれぞれの延伸部分 39 を、一つのゲートトレンチ部 40 として扱う場合がある。ゲートランナー 48 は、ゲートトレンチ部 40 の接続部分 41 において、ゲート導電部と接続してよい。

#### 【 0 0 3 1 】

少なくとも一つのダミートレンチ部 30 が、ゲートトレンチ部 40 のそれぞれの延伸部分 39 の間に設けられてよい。ダミートレンチ部 30 は、ゲートトレンチ部 40 と同様に半導体基板の上面において U 字形状を有してもよい。即ち、本例のダミートレンチ部 30 は、延伸方向に沿って延伸する 2 つの延伸部分 29 と、2 つの延伸部分 29 を接続する接続部分 31 を有してもよい。

#### 【 0 0 3 2 】

また、少なくとも一つのダミートレンチ部 30 は、長手方向が半導体基板の上面において延伸方向（X 軸方向）である直線形状であってもよい。図 1 a の例では、ダイオード部 80 および境界部 90 において U 字形状のダミートレンチ部 30 が設けられ、トランジスタ部 70 の少なくとも一部において直線形状のダミートレンチ部 30 が設けられている。

#### 【 0 0 3 3 】

エミッタ電極 52 は、ゲートトレンチ部 40 、ダミートレンチ部 30 、ウェル領域 11 、エミッタ領域 12 、ベース領域 14 およびコンタクト領域 15 の上方に設けられる。ウェル領域 11 は第 2 導電型である。本例のウェル領域 11 は、一例として P+ 型である。ウェル領域 11 は、ゲート金属層 50 が設けられる側の活性領域の端部から、予め定められた範囲に設けられる。ウェル領域 11 の拡散深さは、ゲートトレンチ部 40 およびダミートレンチ部 30 の下端よりも深くてよい。ゲートトレンチ部 40 およびダミートレンチ部 30 の、ゲート金属層 50 側の一部の領域は、ウェル領域 11 に設けられる。ゲートトレンチ部 40 およびダミートレンチ部 30 の延伸方向の端の底は、ウェル領域 11 に覆われてよい。

#### 【 0 0 3 4 】

10

20

30

40

50

トランジスタ部 7 0において、コンタクトホール 5 4は、コンタクト領域 1 5およびエミッタ領域 1 2の各領域の上方に設けられる。ダイオード部 8 0において、コンタクトホール 5 4は、ベース領域 1 4の上方に設けられる。いずれのコンタクトホール 5 4も、X 軸方向両端に配置されたベース領域 1 4およびウェル領域 1 1の上方には配置されていない。

#### 【 0 0 3 5 】

半導体基板の上面と平行な方向において、Y 軸方向に各トレンチ部に隣接するメサ部が設けられる。メサ部とは、隣り合う 2 つのトレンチ部に挟まれた半導体基板の部分であって、半導体基板の上面から、各トレンチ部の最も深い底部の深さまでの部分であってよい。各トレンチ部の延伸部分を 1 つのトレンチ部としてよい。即ち、2 つの延伸部分に挟まる領域をメサ部としてよい。

10

#### 【 0 0 3 6 】

トランジスタ部 7 0においては、境界部 9 0を除き、各トレンチ部に接して第 1 メサ部 6 0が設けられる。境界部 9 0には、各トレンチ部に接して第 2 メサ部 6 2が設けられる。また、ダイオード部 8 0においては、隣り合うダミートレンチ部 3 0に挟まれた領域に、ダミートレンチ部 3 0に接して第 3 メサ部 6 4が設けられる。第 1 メサ部 6 0、第 2 メサ部 6 2および第 3 メサ部 6 4の X 軸方向における両端部には、一例としてベース領域 1 4が設けられている。なお、図 1 aにおいては、X 軸方向の一方の端部のみを示している。

20

#### 【 0 0 3 7 】

第 1 メサ部 6 0の上面には、ゲートトレンチ部 4 0と接して第 1 導電型のエミッタ領域 1 2が設けられる。本例のエミッタ領域 1 2は、一例として N + 型である。また、第 1 メサ部 6 0の上面には、ベース領域 1 4よりもドーピング濃度の高い第 2 導電型のコンタクト領域 1 5が設けられる。本例のコンタクト領域 1 5は、一例として P + 型である。第 1 メサ部 6 0において、エミッタ領域 1 2およびコンタクト領域 1 5は、ゲートトレンチ部 4 0の延伸方向に交互に設けられてよい。エミッタ領域 1 2およびコンタクト領域 1 5は、互いに接して設けられてよい。

#### 【 0 0 3 8 】

第 1 メサ部 6 0の上面において、エミッタ領域 1 2はダミートレンチ部 3 0と接して設けられてよく、離れて設けられてもよい。図 1 a の例におけるエミッタ領域 1 2は、ダミートレンチ部 3 0と接して設けられている。

30

#### 【 0 0 3 9 】

第 1 メサ部 6 0の上面において、エミッタ領域 1 2およびコンタクト領域 1 5は、コンタクトホール 5 4の下方にも設けられている。エミッタ領域 1 2およびコンタクト領域 1 5は、第 1 メサ部 6 0の上面において、第 1 メサ部 6 0を挟む一方のトレンチ部から他方のトレンチ部にわたり、Y 軸方向に連続して設けられている。エミッタ領域 1 2およびコンタクト領域 1 5は、第 1 メサ部 6 0を挟む 2 本のトレンチ部の双方に接していてよい。図 1 a の例において第 1 メサ部 6 0を挟む 2 本のトレンチ部は、ゲートトレンチ部 4 0およびダミートレンチ部 3 0である。

#### 【 0 0 4 0 】

第 2 メサ部 6 2の上面には、ベース領域 1 4よりもドーピング濃度の高い第 2 導電型のコンタクト領域 1 5が設けられる。当該コンタクト領域 1 5は、第 2 メサ部 6 2の X 軸方向における両端のベース領域 1 4の間に設けられてよい。コンタクト領域 1 5は、当該両端のベース領域 1 4に挟まれた領域全体に設けられてよい。

40

#### 【 0 0 4 1 】

第 2 メサ部 6 2の上面において、コンタクト領域 1 5は、コンタクトホール 5 4の下方にも設けられている。コンタクト領域 1 5は、第 2 メサ部 6 2の上面において、第 2 メサ部 6 2を挟む一方のダミートレンチ部 3 0から他方のダミートレンチ部 3 0にわたり、Y 軸方向に連続して設けられている。コンタクト領域 1 5は、第 2 メサ部 6 2を挟む 2 本のダミートレンチ部 3 0の双方に接していてよい。

#### 【 0 0 4 2 】

50

本例では、第3メサ部64の上面のうち、X軸方向の両端のベース領域14に挟まれた領域に、2つのコンタクト領域15が設けられる。それぞれのコンタクト領域15は、当該両端のベース領域14に接して配置されていてよい。第3メサ部64の上面のうち、当該コンタクト領域15に挟まれた領域にベース領域14が設けられる。ベース領域14は、当該コンタクト領域15に挟まれる領域全体に設けられてよい。

#### 【0043】

第3メサ部64の上面において、ベース領域14は、コンタクトホール54の下方にも設けられている。ベース領域14は、第3メサ部64の上面において、第3メサ部64を挟む一方のダミートレンチ部30から他方のダミートレンチ部30にわたり、Y軸方向に連続して設けられている。ベース領域14は、2本のダミートレンチ部30の双方に接してよい。10

#### 【0044】

本例の半導体装置100は、ダイオード部80においてダミートレンチ部30が設けられる。本例では、ダイオード部80に配置されたそれぞれのダミートレンチ部30の直線状の延伸部分29が接続部分31で接続される。それぞれの延伸部分29に挟まれる領域に、第3メサ部64が設けられる。

#### 【0045】

第3メサ部64には、エミッタ領域12が設けられなくてよく、設けられてもよい。本例の第3メサ部64には、エミッタ領域12が設けられていない。第3メサ部64には、コンタクト領域15およびベース領域14が、第3メサ部64を挟む一方のダミートレンチ部30から、他方のダミートレンチ部30にわたって設けられている。即ち、半導体基板の上面において、第3メサ部64のY軸方向の幅と、第3メサ部64に設けられたコンタクト領域15またはベース領域14のY軸方向の幅は等しい。20

#### 【0046】

ダイオード部80は、半導体基板の下面側において、第1導電型のカソード領域82を有する。図1aに、カソード領域82が設けられる領域を一点鎖線で示している。ダイオード部80は、カソード領域82を半導体基板の上面に投影した領域であってよい。カソード領域82を半導体基板の上面に投影した領域は、第3メサ部64のコンタクト領域15から、第3メサ部64の内側に離れて配置されていてよい。第3メサ部64の内側とは、X軸方向において、第3メサ部64の中央に近い側を指す。半導体基板の下面に隣接する領域においてカソード領域82が設けられていない領域には、第2導電型のコレクタ領域が設けられてよい。トランジスタ部70は、コレクタ領域を半導体基板の上面に投影した領域のうち、トレンチ部またはメサ部が設けられている領域であってよい。30

#### 【0047】

半導体装置100は、半導体基板の内部において、ドリフト領域よりもドーピング濃度の高い第1導電型の蓄積領域16を有する。蓄積領域16のドーパントは、ドリフト領域のドーパントと同じ導電型である。蓄積領域16のドーパントは、ドリフト領域のドーパントよりも高い濃度で蓄積している。蓄積領域16は、ベース領域14の下方に配置されている。蓄積領域16は、それぞれのトレンチ部の下端よりも上方に配置されてよい。蓄積領域16は、ゲートトレンチ部40に接してよい。蓄積領域16を設けることで、キャリアの注入促進効果（IE効果）を高めて、オン電圧を低減することができる。図1aにおいては、蓄積領域16が設けられる範囲を一点鎖線で示している。なお、図1aにおいては、各トレンチ部の領域も当該鎖線が横切っているが、蓄積領域16は各トレンチ部と重なる領域には形成されなくてよい。40

#### 【0048】

第1メサ部60には、蓄積領域16の下方に、第2導電型のフローティング領域17が設けられる。フローティング領域17は、ゲートトレンチ部40に接している。本例のフローティング領域17は、一例としてP+型である。フローティング領域17のドーピング濃度は、ベース領域14のドーピング濃度よりも高い。図1aにおいて、半導体基板の上面視で、フローティング領域17が設けられる範囲を破線で示している。なお、図1a

においては、各トレンチ部の領域も当該破線が横切っているが、フローティング領域 17 は各トレンチ部と重なる領域には形成されなくてよい。

#### 【 0 0 4 9 】

図 1 a に示すように、フローティング領域 17 は、半導体基板の上面視で、ゲートトレンチ部 40 の延伸方向に直交する配列方向 (Y 軸方向) において、第 1 メサ部 60 の一部分に設けられる。即ち、フローティング領域 17 は、Y 軸方向において第 1 メサ部 60 の全幅にわたっては設けられておらず、Y 軸方向において部分的に設けられている。図 1 a の例では、フローティング領域 17 は、ゲートトレンチ部 40 と接する位置から、第 1 メサ部 60 内の Y 軸方向の所定の位置まで連続して設けられている。フローティング領域 17 は、当該所定の位置よりもゲートトレンチ部 40 から離れた位置には設けられていない。

10

#### 【 0 0 5 0 】

当該所定の位置とは、第 1 メサ部 60 を挟む 2 本のトレンチ部の間にあってよい。第 1 メサ部 60 を挟む 2 本のトレンチ部を、それぞれ第 1 トレンチ部および第 2 トレンチ部と称する。第 1 トレンチ部は、フローティング領域 17 に接するゲートトレンチ部 40 である。第 2 トレンチ部は、ダミートレンチ部 30 であってよく、ゲートトレンチ部 40 であってもよい。本例では、第 2 トレンチ部はダミートレンチ部 30 である。当該所定の位置は、第 2 トレンチ部から配列方向に離れた位置である。半導体基板の上面視で、配列方向におけるフローティング領域 17 の端を、フローティング領域端 13 と称する。フローティング領域端 13 は、当該所定の位置に位置してよい。すなわち、フローティング領域 17 は、第 2 トレンチ部から離れてよい。

20

#### 【 0 0 5 1 】

第 1 メサ部 60 内の Y 軸方向における当該所定の位置は、半導体基板の上面視で、コンタクトホール 54 と重なっていてもよいし、重なっていないなくてもよい。図 1 a は、当該所定の位置がコンタクトホール 54 と重ならない一例を示している。フローティング領域 17 は、Y 軸方向において、コンタクトホール 54 よりもゲートトレンチ部 40 側に設けられてよい。

#### 【 0 0 5 2 】

フローティング領域 17 は、第 1 メサ部 60 の X 軸方向における両端に設けられるコンタクト領域 15 の一方から他方まで連続して設けられてよい。上述したように、フローティング領域 17 は、ゲートトレンチ部 40 に接して設けられてよい。

30

#### 【 0 0 5 3 】

フローティング領域 17 の X 軸方向における両端の位置は、蓄積領域 16 の X 軸方向における両端の位置と一致していてよく、異なっていてもよい。図 1 a においては、フローティング領域 17 の X 軸方向の端と、蓄積領域 16 の X 軸方向の端を、異ならせて示している。

#### 【 0 0 5 4 】

第 1 メサ部 60 において、フローティング領域 17 は、ダミートレンチ部 30 に接しなくてよい。第 2 メサ部 62 および第 3 メサ部 64 には、フローティング領域 17 が設けられなくてよい。

#### 【 0 0 5 5 】

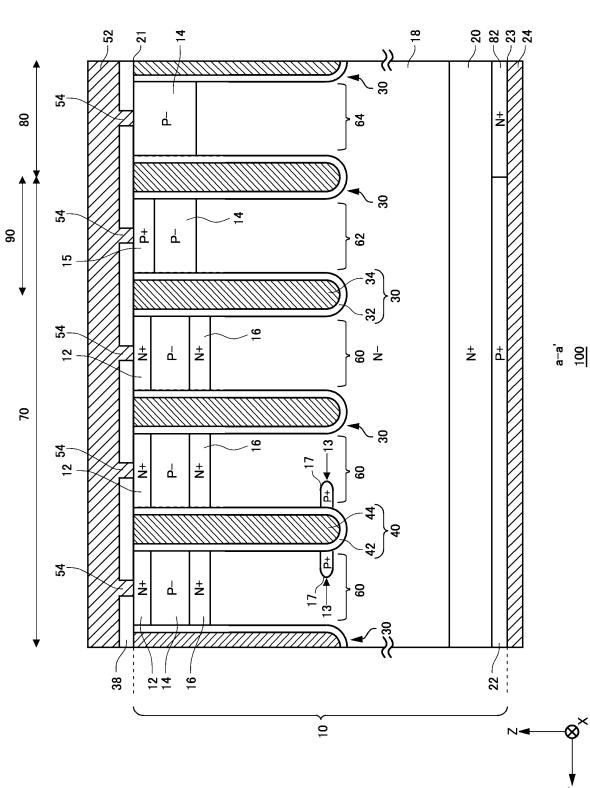

図 1 b は、図 1 a における a - a' 断面の一例を示す図である。a - a' 断面は、第 1 メサ部 60 のエミッタ領域 12 および第 2 メサ部 62 のコンタクト領域 15 を通過する YZ 面である。本例の半導体装置 100 は、a - a' 断面において、半導体基板 10 、層間絶縁膜 38 、エミッタ電極 52 およびコレクタ電極 24 を有する。エミッタ電極 52 は、半導体基板 10 および層間絶縁膜 38 の上面に設けられる。

40

#### 【 0 0 5 6 】

コレクタ電極 24 は、半導体基板 10 の下面 23 に設けられる。エミッタ電極 52 およびコレクタ電極 24 は、金属等の導電材料で形成される。本明細書において、エミッタ電極 52 とコレクタ電極 24 とを結ぶ方向を深さ方向 (Z 軸方向) と称する。

#### 【 0 0 5 7 】

50

半導体基板 10 は、シリコン基板であってよく、炭化シリコン基板であってよく、窒化ガリウム等の窒化物半導体基板または酸化ガリウム基板等であってもよい。本例の半導体基板 10 はシリコン基板である。

#### 【 0 0 5 8 】

半導体基板 10 は、第 1 導電型のドリフト領域 18 を備える。本例のドリフト領域 18 は N - 型である。ドリフト領域 18 は、半導体基板 10 において、他のドーピング領域が設けられずに残存した領域であってよい。

#### 【 0 0 5 9 】

半導体基板 10 の上面 21 には、1 つ以上のゲートトレンチ部 40 および 1 つ以上のダミートレンチ部 30 が設けられる。各トレンチ部は、上面 21 から、ベース領域 14 を貫通して、ドリフト領域 18 に到達して設けられている。10

#### 【 0 0 6 0 】

ゲートトレンチ部 40 は、上面 21 に設けられたゲートトレンチ、ゲート絶縁膜 42 およびゲート導電部 44 を有する。ゲート絶縁膜 42 は、ゲートトレンチの内壁を覆って設けられる。ゲート絶縁膜 42 は、ゲートトレンチの内壁の半導体を酸化または窒化して形成してよい。ゲート導電部 44 は、ゲートトレンチの内部においてゲート絶縁膜 42 よりも内側に設けられる。即ち、ゲート絶縁膜 42 は、ゲート導電部 44 と半導体基板 10 とを絶縁する。ゲート導電部 44 は、ポリシリコン等の導電材料で形成される。

#### 【 0 0 6 1 】

ゲート導電部 44 は、深さ方向において、ゲート絶縁膜 42 を挟んで、少なくとも隣接するベース領域 14 と対向する領域を含む。当該断面におけるゲートトレンチ部 40 は、上面 21 において層間絶縁膜 38 により覆われる。ゲート導電部 44 に所定の電圧が印加されると、ベース領域 14 のうちゲートトレンチに接する界面の表層に電子の反転層によるチャネルが形成される。20

#### 【 0 0 6 2 】

ダミートレンチ部 30 は、当該断面において、ゲートトレンチ部 40 と同一の構造を有してよい。ダミートレンチ部 30 は、上面 21 側に設けられたダミートレンチ、ダミー絶縁膜 32 およびダミー導電部 34 を有する。ダミー絶縁膜 32 は、ダミートレンチの内壁を覆って設けられる。ダミー導電部 34 は、ダミートレンチの内部に設けられ、且つ、ダミー絶縁膜 32 よりも内側に設けられる。ダミー絶縁膜 32 は、ダミー導電部 34 と半導体基板 10 とを絶縁する。30

#### 【 0 0 6 3 】

ダミー導電部 34 は、ゲート導電部 44 と同一の材料で形成されてよい。例えば、ダミー導電部 34 は、ポリシリコン等の導電材料で形成される。ダミー導電部 34 は、深さ方向においてゲート導電部 44 と同一の長さを有してよい。当該断面におけるダミートレンチ部 30 は、上面 21 において層間絶縁膜 38 により覆われる。なお、ダミートレンチ部 30 およびゲートトレンチ部 40 の底部は下方側に凸の曲面状（断面においては曲線状）であってよい。

#### 【 0 0 6 4 】

第 1 メサ部 60 において、ドリフト領域 18 の上方には、一つ以上の第 1 導電型の蓄積領域 16 が設けられる。蓄積領域 16 は、ゲートトレンチ部 40 に接していてよい。蓄積領域 16 が複数設けられる場合、それぞれの蓄積領域 16 は Z 軸方向に並んで配置される。それぞれの蓄積領域 16 の間には、ドリフト領域 18 が設けられてよい。蓄積領域 16 は、一例として N + 型である。蓄積領域 16 のドーピング濃度は、ドリフト領域 18 のドーピング濃度よりも高い。蓄積領域 16 を設けることで、キャリアの注入促進効果（ I E 効果）を高めて、オン電圧を低減することができる。40

#### 【 0 0 6 5 】

一つ以上の蓄積領域 16 は、第 1 メサ部 60 において、ダミートレンチ部 30 に接していてよいが、離れていてもよい。図 1 b は、蓄積領域 16 がダミートレンチ部 30 と接して設けられる一例を示している。なお、第 2 メサ部 62 および第 3 メサ部 64 には、蓄積

10

20

30

40

50

領域 1 6 が設けられなくてよい。

**【 0 0 6 6 】**

第 1 メサ部 6 0 において、蓄積領域 1 6 の上方には、第 2 導電型のベース領域 1 4 が設けられる。ベース領域 1 4 は、ゲートトレンチ部 4 0 に接していてよい。ベース領域 1 4 は、一例として P - 型である。第 1 メサ部 6 0 において、ベース領域 1 4 は、ダミートレンチ部 3 0 に接して設けられてよい。

**【 0 0 6 7 】**

第 1 メサ部 6 0 には、a - a' 断面において、半導体基板 1 0 の上面 2 1 に接してエミッタ領域 1 2 が設けられる。エミッタ領域 1 2 は、ゲートトレンチ部 4 0 と接している。エミッタ領域 1 2 のドーピング濃度は、ドリフト領域 1 8 のドーピング濃度よりも高い。第 1 メサ部 6 0 のコンタクト領域 1 5 を通過する YZ 断面では、図 1 b に示したエミッタ領域 1 2 に代えて、コンタクト領域 1 5 が設けられている。コンタクト領域 1 5 は、半導体基板 1 0 の上面 2 1 に露出している。コンタクト領域 1 5 は、ゲートトレンチ部 4 0 およびダミートレンチ部 3 0 と接していてよい。

10

**【 0 0 6 8 】**

境界部 9 0 の第 2 メサ部 6 2 において、ドリフト領域 1 8 の上方には、第 2 導電型のベース領域 1 4 が設けられる。ベース領域 1 4 は、ダミートレンチ部 3 0 に接していてよい。

**【 0 0 6 9 】**

第 2 メサ部 6 2 において、半導体基板 1 0 の上面 2 1 に接してコンタクト領域 1 5 が設けられる。コンタクト領域 1 5 は、ダミートレンチ部 3 0 と接していてよく、離れていてもよい。図 1 b は、コンタクト領域 1 5 がダミートレンチ部 3 0 と接して設けられる一例を示している。

20

**【 0 0 7 0 】**

ダイオード部 8 0 の第 3 メサ部 6 4 において、ドリフト領域 1 8 の上方には、第 2 導電型のベース領域 1 4 が設けられる。第 3 メサ部 6 4 において、ベース領域 1 4 は上面 2 1 に接して設けられる。ベース領域 1 4 は、ダミートレンチ部 3 0 に接していてよい。

**【 0 0 7 1 】**

ドリフト領域 1 8 の下方には、第 1 導電型のバッファ領域 2 0 が設けられてよい。バッファ領域 2 0 は、一例として N + 型である。バッファ領域 2 0 のドーピング濃度は、ドリフト領域 1 8 のドーピング濃度よりも高い。バッファ領域 2 0 は、ベース領域 1 4 の下面側から広がる空乏層が、P + 型のコレクタ領域 2 2 および N + 型のカソード領域 8 2 に到達することを防ぐフィールドストップ層として機能してよい。

30

**【 0 0 7 2 】**

トランジスタ部 7 0 において、バッファ領域 2 0 の下方には、下面 2 3 に露出する P + 型のコレクタ領域 2 2 が設けられる。ダイオード部 8 0 において、バッファ領域 2 0 の下方には、下面 2 3 に露出する N + 型のカソード領域 8 2 が設けられる。境界部 9 0 において、バッファ領域 2 0 の下には、コレクタ領域 2 2 およびカソード領域 8 2 のいずれかが設けられる。本例の境界部 9 0 において、バッファ領域 2 0 の下は、コレクタ領域 2 2 が設けられる。

**【 0 0 7 3 】**

なお、ダイオード部 8 0 は、下面 2 3 に垂直な方向においてカソード領域 8 2 と重なる領域である。また、トランジスタ部 7 0 は、下面 2 3 に垂直な方向においてコレクタ領域 2 2 と重なる領域のうち、エミッタ領域 1 2 およびコンタクト領域 1 5 を含む所定の単位構成が規則的に配置された領域である。

40

**【 0 0 7 4 】**

トランジスタ部 7 0 の第 1 メサ部 6 0 において、蓄積領域 1 6 の下方にはフローティング領域 1 7 が設けられる。フローティング領域 1 7 は、ゲートトレンチ部 4 0 に接して設けられる。フローティング領域 1 7 は、配列方向 (Y 軸方向) において第 1 メサ部 6 0 の一部分に設けられる。フローティング領域 1 7 は、ダミートレンチ部 3 0 には接しないで離れてよい。

50

**【0075】**

フローティング領域17とダミートレンチ部30との間は、ドリフト領域18であつてよい。また、フローティング領域17と蓄積領域16との間も、ドリフト領域18であつてよい。フローティング領域17は、当該断面において、ゲートトレンチ部40およびドリフト領域18に囲まれていてよい。

**【0076】**

境界部90の第2メサ部62におけるダミートレンチ部30には、フローティング領域17が設けられなくてよい。ダイオード部80の第3メサ部64におけるダミートレンチ部30には、フローティング領域17が設けられなくてよい。

**【0077】**

フローティング領域17のドーピング濃度は、コンタクト領域15のドーピング濃度と略等しくてよく、コンタクト領域15のドーピング濃度よりも低くてよく高くてよい。なおフローティング領域17のドーピング濃度は、ゲート導電部44にゲート電圧が印加された場合においても、ゲートトレンチ部40との界面に電子の反転層(チャネル)が形成されない程度に高い。一例としてフローティング領域17のドーピング濃度は、 $1 \times 10^{17} / \text{cm}^3$ 以上 $5 \times 10^{20} / \text{cm}^3$ 以下であつてよい。

10

**【0078】**

フローティング領域17は、コレクタ電極24およびエミッタ電極52のいずれにも、接していない。フローティング領域17は、ベース領域14とP型の領域でつながっていてよいが、つながっていなくてもよい。

20

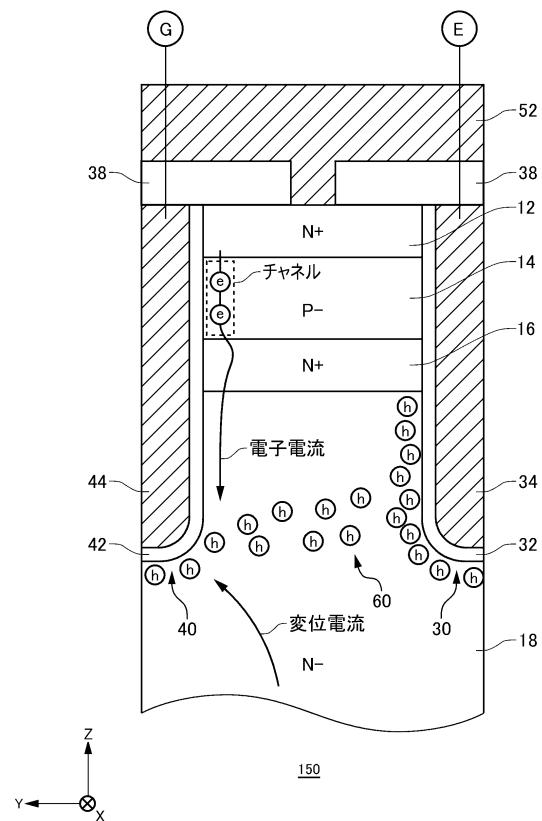

**【0079】**

図2aは、第1比較例の半導体装置150における電子電流および変位電流の経路を示す図である。第1比較例の半導体装置150は、トランジスタ部70の第1メサ部60において、蓄積領域16を一つ有する。第1比較例において、フローティング領域17は設けられない。図2aにおいては、ターンオン時の電流経路を示している。ターンオン時には、ゲート導電部44の電圧が、0[V]から徐々に立上る。これにより、ベース領域14のゲートトレンチ部40近傍には負電荷が誘起することでチャネルが形成される。

**【0080】**

ターンオン時の初期における電流の主体は、正孔電流ではなく電子電流である。初期とは、ゲート電圧Vgが、閾値電圧に達する直前から、ほぼ閾値電圧の値でVgが一定となるミラー期間に入る前までの期間である。Vgが閾値電圧に近くなると、チャネルが開きかけ、電子のドリフト領域18への注入が始まる。

30

**【0081】**

図2aの第1比較例において、チャネルから下方に向かう電子は、第1の蓄積領域16において一旦Y軸方向負側(ゲートトレンチ部40の近傍から第1メサ部60中央に向かう方向)に流れかかる。ただし、第1の蓄積領域16よりも下方のドリフト領域18においては、ゲートトレンチ部40近傍は、電子の蓄積層が既に形成されているため(N型領域の電子の蓄積層が形成される閾値電圧は、P型領域の反転層の閾値電圧よりはるかに小さい)、ドリフト領域18よりも低インピーダンスである。このため、電子電流はゲートトレンチ部40近傍を主として流れる。

40

**【0082】**

電子が裏面のコレクタ領域22に達すると、コレクタ領域22からバッファ領域20およびドリフト領域18にかけて、正孔の注入が開始する。これにより、トレンチ部の下端近傍に正孔が蓄積される。一例として、ゲートトレンチ部40の下端近傍から、第1の蓄積領域16よりも下方のダミートレンチ部30の側部にかけて、正孔が $1 \times 10^{16} / \text{cm}^3$ 以上 $5 \times 10^{18} / \text{cm}^3$ 以下の濃度で存在する。

**【0083】**

正孔は、ゲートトレンチ部40の下端と、ダミートレンチ部30の下端に蓄積する。特にダミー導電部34はエミッタ電極52と同電位であるため、ダミートレンチ部30の側壁には正孔の反転層が形成されやすい。コレクタ領域22から注入された正孔は、この正

50

孔の反転層の近傍に集まる。正孔は、ダミートレンチ部 30 からゲートトレンチ部 40 の下端にかけて連続的に分布する。この正孔分布に起因して、ターンオン時に、ゲートトレンチ部 40 の下端近傍へ、大きな変位電流が流れる。

#### 【 0 0 8 4 】

正孔の蓄積に起因する変位電流は、ゲート絶縁膜 42 を挟んで対向するゲート導電部 44 の充電を生じさせる。このゲート導電部 44 の充電が、ゲート電極 Vg の瞬間的な増加を引き起こす。当該変位電流が大きいほど、ゲート導電部 44 が充電されるため、ゲート導電部 44 の電位がよりすばやく上昇する。その結果、ゲート導電部 44 の電位がゲート閾値を瞬間的に超える。

#### 【 0 0 8 5 】

ゲート導電部 44 の電位がゲート閾値を瞬間的に超えると、電子と正孔の大量の注入が始まり、コレクタ電極 24 とエミッタ電極 52 との間に流れる電流 (CE 電流) が増加する。CE 電流の増加による電流変化率に応じて、コレクタ電極 24 とエミッタ電極 52 との間の電圧 (CE 電圧) の電圧減少率 ( $dV_{ce} / dt$ ) が増加する。変位電流が大きいほど、( $dV_{ce} / dt$ ) が大きくなる。特に、蓄積された正孔がエミッタ電極 52 に流れないと、変位電流は大きく、ゲート導電部 44 の電位の瞬間的な増加は大きくなる。このため、図 2a の第 1 比較例においては、( $dV_{ce} / dt$ ) が大きくなり、電磁ノイズもまた大きくなる。

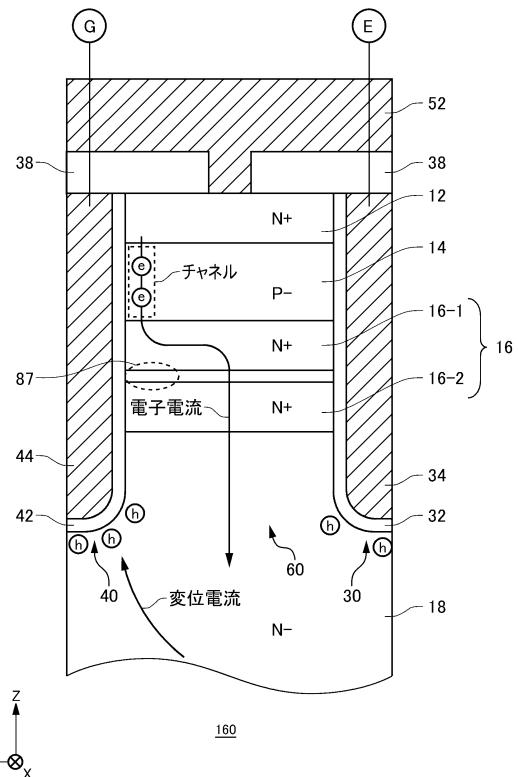

#### 【 0 0 8 6 】

図 2b は、第 2 比較例の半導体装置 160 における電子電流および変位電流の経路を示す図である。第 2 比較例の半導体装置 160 は、トランジスタ部 70 の第 1 メサ部 60 において、第 1 蓄積領域 16-1 および第 2 蓄積領域 16-2 を有する。第 2 蓄積領域 16-2 は、第 1 蓄積領域 16-1 の下方に設けられる。第 2 比較例の半導体装置 160 においては、第 2 蓄積領域 16-2 のドーピング濃度は、第 1 蓄積領域 16-1 のドーピング濃度よりも高く設けられる。また、第 2 比較例において、フローティング領域 17 は設けられない。

#### 【 0 0 8 7 】

チャネルを通過した電子は、第 1 蓄積領域 16-1 において一旦 Y 軸方向負側 (ゲートトレンチ部 40 の近傍から第 1 メサ部 60 中央に向かう方向) に流れかかる。本例において、第 1 蓄積領域 16-1 よりも第 2 蓄積領域 16-2 の方が、ドーピング濃度が高く設けられるので、電子電流にとってのインピーダンスは、第 1 蓄積領域 16-1 の中央付近からゲートトレンチ部 40 近傍に戻って第 2 蓄積領域 16-2 に流れる経路よりも、第 1 蓄積領域 16-1 から第 2 蓄積領域 16-2 に直接流れる経路の方が低い。このため、電子電流は、第 1 蓄積領域 16-1 の中央付近からゲートトレンチ部 40 近傍に戻らず、第 2 蓄積領域 16-2 に流れやすい。

#### 【 0 0 8 8 】

第 1 蓄積領域 16 の下方のうち、ゲートトレンチ部 40 に隣接するホール高濃度領域 87 には正孔が蓄積されやすい。また、電子電流がゲートトレンチ部 40 の近傍ではなく、第 1 メサ部 60 中央付近を流れることで、ホール高濃度領域 87 への正孔の蓄積が促進される。このため、電子電流が第 1 メサ部 60 中央付近に流れることが促進される。

#### 【 0 0 8 9 】

電子電流が第 1 メサ部 60 の中央付近を流れると、第 1 メサ部 60 の底部近傍における正孔分布は、第 1 メサ部 60 中央付近で分断される。このため、電子電流の経路よりもダミートレンチ部 30 側の正孔は、ゲートトレンチ部 40 側には流れない。この第 1 メサ部 60 中央部における正孔分布の分断が、ゲートトレンチ部 40 の下端における正孔の蓄積を抑制する。その結果、変位電流を小さくすることできる。変位電流を小さくすることができるので、ゲート導電部 44 の充電も小さくなり、ゲート電極 Vg の瞬間的な増加も抑制される。これにより、CE 電圧の電圧減少率 ( $dV_{ce} / dt$ ) が抑制される。

#### 【 0 0 9 0 】

蓄積領域 16 は、ベース領域 14 の近傍に設けられるので、ゲートとコレクタとの間に

10

20

30

40

50

おける負性容量（C G 容量）を生じる。第2比較例の半導体装置160は、上述の通り、C E 電圧の電圧減少率（ $dV_{ce}/dt$ ）を抑制することができるが、蓄積領域16が2つ設けられるので、C G 容量が増加する場合がある。C G 容量が増加すると、トランジスタ部70のオン電圧とターンオフ損失のトレードオフが悪化してしまう。

#### 【0091】

図3は、本実施形態の半導体装置100における電子電流および変位電流の経路の一例を示す図である。図3は、ゲートトレンチ部40に接してフローティング領域17が設けられることによる電子電流および変位電流の経路の一例を示している。

#### 【0092】

本例の半導体装置100において、チャネルから下方に向かう電子は、第1の蓄積領域16において一旦Y軸方向負側（ゲートトレンチ部40の近傍から第1メサ部60中央に向かう方向）に流れかかる。ただし、第1の蓄積領域16よりも下方のドリフト領域18においては、ゲートトレンチ部40近傍は、電子の蓄積層が既に形成されているため、ドリフト領域18よりも低インピーダンスである。このため、電子電流はゲートトレンチ部40近傍を主として、半導体基板10の下方に向かって流れる。

10

#### 【0093】

フローティング領域17は、ドリフト領域18よりも電子電流に対する抵抗が大きい。本例の半導体装置100は、蓄積領域16の下方にフローティング領域17を備えるので、ゲートトレンチ部40の近傍を半導体基板10の下方に向かって流れる電子電流は、フローティング領域17により経路を曲げられ、ゲートトレンチ部40近傍から第1メサ部60の中央付近に流れる経路をたどる。

20

#### 【0094】

電子電流が第1メサ部60の中央付近を流れると、第1メサ部60の底部近傍における正孔分布は、第1メサ部60中央付近で分断される。このため電子電流の経路よりもダミートレンチ部30側の正孔は、ゲートトレンチ部40側には流れない。この第1メサ部60中央付近における正孔分布の分断が、ゲートトレンチ部40の下端における正孔の蓄積を抑制する。その結果、変位電流を小さくすることできる。変位電流を小さくすることができるので、ゲート導電部44の充電も小さくなり、ゲート電極Vgの瞬間的な増加も抑制される。これにより、C E 電圧の電圧減少率（ $dV_{ce}/dt$ ）が抑制される。

30

#### 【0095】

さらに、本例の半導体装置100は、フローティング領域17を設けることで、蓄積領域16が一つであっても電子電流を第1メサ部60の中央付近に流すことができる。このため、第2比較例の半導体装置160のように蓄積領域16をZ軸方向に複数設けた場合よりも、C G 容量の増加を防ぐことができる。即ち、本例の半導体装置100は、C E 電圧の電圧減少率（ $dV_{ce}/dt$ ）を抑制しつつ、C G 容量の増加を抑制することができる。このため、本例の半導体装置100は、C E 電圧の電圧減少率（ $dV_{ce}/dt$ ）を抑制しつつ、ターンオン損失を減少させることができる。また、オン電圧とターンオフ損失のトレードオフを維持することができる。

#### 【0096】

なお、図2aから図3において説明した半導体装置の動作は、トランジスタ部70の動作であり、ダイオード部80を備えない半導体装置においても同様に動作するのは当然である。すなわち、半導体装置100がダイオード部80を備えなくとも、フローティング領域17を設けた効果は生じる。半導体装置100は、ダイオード部を備えなくてもよい。

40

#### 【0097】

図4aは、ターンオン時におけるゲート電圧VgおよびC E 電圧Vceの時間波形の一例を示す図である。図4aにおいては、本例の半導体装置100の特性を実線で、第1比較例の半導体装置150の特性を破線で、第2比較例の半導体装置160の特性を一点鎖線で、それぞれ示している。なお、第1比較例150の波形については、VgおよびVceが時間に伴い遷移する箇所以外は、半導体装置100の波形と重なっている。

#### 【0098】

50

図4 bは、図4 aの時間波形において、ゲート電圧V<sub>g</sub>およびCE電圧V<sub>c e</sub>の遷移波形を拡大した図である。ただし図4 bでは、CE電圧V<sub>c e</sub>の電圧軸のスケールと位置を変更している。図4 aおよび図4 bに示すように、半導体装置100は、第1比較例の半導体装置150と比較して、ターンオン時のゲート電圧V<sub>g</sub>およびCE電圧V<sub>c e</sub>の変動が緩やかである。このため、本例の半導体装置100は、第1比較例の半導体装置150よりも、ターンオン損失を低減することができる。また、オン電圧とターンオフ損失のトレードオフを維持することができる。

#### 【0099】

第2比較例の半導体装置160は、本例の半導体装置100よりも、ターンオン時のゲート電圧V<sub>g</sub>およびCE電圧V<sub>c e</sub>の変動が、さらに緩やかになる。しかしながら、上述したとおり、第2比較例の半導体装置160は、CG容量が増加してしまう。CG容量が増加すると、トランジスタ部70のオン電圧とターンオフ損失のトレードオフが悪化してしまう。

10

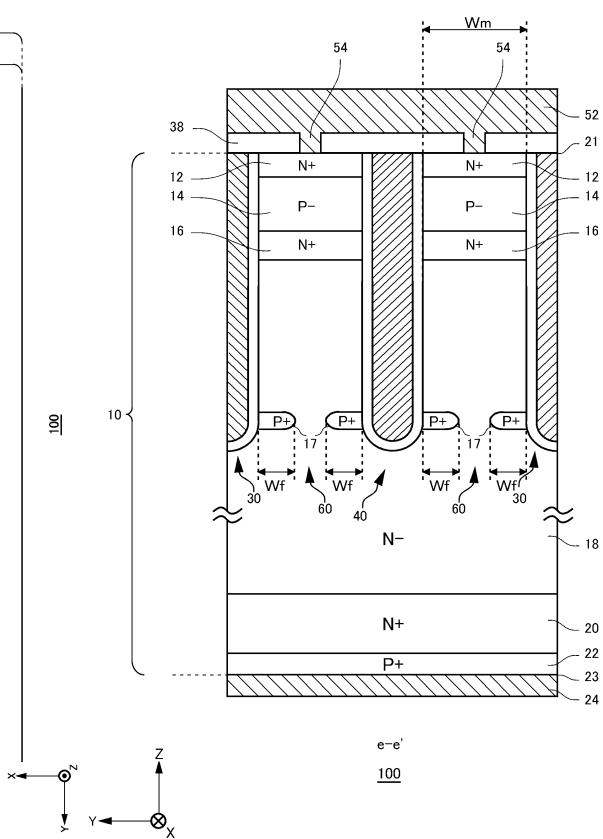

#### 【0100】

図5 aは、図1 aにおけるb - b'断面の一例を示す図である。b - b'断面は、トランジスタ部70において、エミッタ領域12を通過するYZ面である。本例の半導体装置100は、b - b'断面において、半導体基板10、層間絶縁膜38、エミッタ電極52およびコレクタ電極24を有する。エミッタ電極52は、半導体基板10および層間絶縁膜38の上面に設けられる。

20

#### 【0101】

本例の半導体装置100は、b - b'断面において、上面21に接してエミッタ領域12が設けられる。エミッタ領域12は、Y軸方向においてゲートトレンチ部40と接している。エミッタ領域12の下方には、ベース領域14が設けられる。ベース領域14は、Y軸方向においてゲートトレンチ部40と接している。ベース領域14の下方には、蓄積領域16が設けられる。蓄積領域16は、Y軸方向においてゲートトレンチ部40と接している。蓄積領域16の下方には、ドリフト領域18が設けられる。ドリフト領域18の下方にはバッファ領域20が設けられる。バッファ領域20の下方には、コレクタ領域22が設けられる。下面23にはコレクタ電極24が設けられる。

20

#### 【0102】

本例の半導体装置100は、ゲートトレンチ部40に接してフローティング領域17が設けられる。フローティング領域17は、蓄積領域16の下方に、蓄積領域16と離間して設けられてよい。半導体基板10の深さ方向におけるフローティング領域17の少なくとも一部は、ゲートトレンチ部40の底部と接して設けられてよい。ゲートトレンチ部40の底部については、図5 bの説明において詳細に説明する。

30

#### 【0103】

幅W<sub>g d</sub>は、上面21からゲートトレンチ部40の底部の端までのZ軸方向の幅、即ちゲートトレンチ部40の上面21からの深さである。幅W<sub>f d</sub>は、上面21からフローティング領域17の上端までのZ軸方向の幅である。幅W<sub>b</sub>は、トランジスタ部70におけるベース領域14のZ軸方向の幅である。幅W<sub>b</sub>は、ゲートトレンチ部40に接する位置における、ベース領域14のZ軸方向の幅であってよい。幅W<sub>b f</sub>は、ベース領域14の下端からフローティング領域17の上端までのZ軸方向の幅である。幅W<sub>b f</sub>は、ゲートトレンチ部40に接する位置における、ベース領域14の下端からフローティング領域17の下端までのZ軸方向の幅であってよい。

40

#### 【0104】

幅W<sub>m</sub>は、第1メサ部60のメサ幅である。幅W<sub>m</sub>は、半導体基板10の上面21における第1メサ部60のメサ幅であってよい。幅W<sub>f</sub>は、フローティング領域17のY軸方向の幅である。幅W<sub>f</sub>は、フローティング領域17のY軸方向の幅の最大値であってよい。また、幅W<sub>e f</sub>は、フローティング領域17が設けられた深さにおける、ドリフト領域18のY軸方向の幅である。幅W<sub>e f</sub>は、フローティング領域17のY軸方向の先端から、ダミートレンチ部30までのY軸方向の幅であってよい。幅W<sub>f v</sub>は、フローティング

50

領域 1 7 の Z 軸方向の幅、即ちフローティング領域 1 7 の厚みである。幅  $W_{f v}$  は、フローティング領域 1 7 の Z 軸方向の幅の最大値であってよい。また、幅  $W_{f v}$  は、ゲートトレンチ部 4 0 に接する位置の、フローティング領域 1 7 の Z 軸方向の幅であってもよい。幅  $W_{f v}$  は、一例として 0 . 1  $\mu m$  以上、1 . 0  $\mu m$  以下である。幅  $W_{f v}$  は、0 . 3  $\mu m$  以上 0 . 7  $\mu m$  以下であってもよい。

#### 【 0 1 0 5 】

フローティング領域 1 7 は、Y 軸方向において、第 1 メサ部 6 0 の一部分に設けられる。即ち、 $W_{f} < W_m$  である。図 5 a の例では、フローティング領域 1 7 は、第 1 メサ部 6 0 においてゲートトレンチ部 4 0 と接する位置から Y 軸方向の所定の位置まで、幅  $W_f$  にわたって設けられている。フローティング領域 1 7 は、当該所定の位置よりもゲートトレンチ部 4 0 から離れた位置には設けられていない。10

#### 【 0 1 0 6 】

幅  $W_{b f}$  は、幅  $W_b$  よりも大きくてよい。幅  $W_{b f}$  を幅  $W_b$  よりも大きくすることで、トランジスタ部 7 0 がオン状態の場合に、ベース領域 1 4 とドリフト領域 1 8 との接合面から半導体基板 1 0 の深さ方向に拡張する空乏層が、フローティング領域 1 7 に達しにくくなる。このため、本例の半導体装置 1 0 0 は、電子電流を遮断することなく、第 1 メサ部 6 0 の中央付近に流すことができる。幅  $W_{b f}$  は、幅  $W_b$  の 2 倍以上であってよい。幅  $W_{b f}$  は、一例として 2 . 5  $\mu m$  以上 3 . 5  $\mu m$  以下である。

#### 【 0 1 0 7 】

フローティング領域 1 7 には高濃度に正孔が蓄積される。このため、フローティング領域 1 7 を蓄積領域 1 6 に対して Z 軸方向に接して設けると、フローティング領域 1 7 に蓄積された正孔が、蓄積領域 1 6 を上方向に通過しやすくなる。これにより、蓄積領域 1 6 による I E 効果が低減してしまう。本例の半導体装置 1 0 0 は、フローティング領域 1 7 が Z 軸方向に蓄積領域 1 6 と離間して設けられるので、当該 I E 効果の低減を抑制することができる。このため、トランジスタ部 7 0 のオン電圧  $V_{on}$  の増加を抑制することができる。20

#### 【 0 1 0 8 】

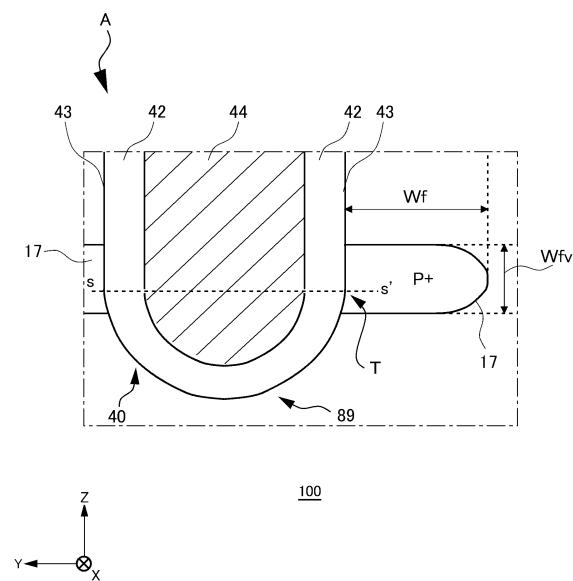

図 5 b は、図 5 a における領域 A の拡大図である。図 5 b は、ゲートトレンチ部 4 0 の底部 8 9 を拡大して示している。本例において、ゲートトレンチ部 4 0 の底部 8 9 とは、YZ 平面内において、ゲートトレンチ部 4 0 の断面における外形を示す線が、下方 (Z 軸方向負側) に凸の曲線となる領域である。即ち、ゲートトレンチ部 4 0 の底部 8 9 は、図 5 b においてゲートトレンチ部 4 0 のうち Y 軸方向の s - s' 線よりも下方の領域である。s - s' 線は特異点 T を通る。特異点 T は、ゲートトレンチ部 4 0 の側壁 4 3 の断面形状が、ほぼ直線から曲線に変化する点である。特異点 T は、側壁 4 3 の傾きが変化し始める点であってもよい。また、ゲートトレンチ部 4 0 の最下端から上側 (Z 軸正側) に 0 . 5  $\mu m$  の範囲を、ゲートトレンチ部 4 0 の底部 8 9 としてよく、ゲートトレンチ部 4 0 の最下端から上側に 0 . 1 ×  $W_{g d}$  の範囲をゲートトレンチ部 4 0 の底部 8 9 としてもよい。30

#### 【 0 1 0 9 】

半導体基板 1 0 の深さ方向におけるフローティング領域 1 7 の少なくとも一部は、ゲートトレンチ部 4 0 の底部 8 9 と接して設けられてよい。即ち、フローティング領域 1 7 の Z 軸方向における位置は、YZ 平面内において、フローティング領域 1 7 の上端が s - s' 線より上側 (すなわち半導体基板 1 0 の上面 2 1 側) 、且つ、フローティング領域 1 7 の下端が s - s' 線より下側 (すなわち半導体基板 1 0 の下面 2 3 側) となる位置であってよい。フローティング領域 1 7 の上端の Z 軸方向における位置は、s - s' 線と一致してもよい。フローティング領域 1 7 の下端の Z 軸方向における位置は、s - s' 線と一致してもよい。40

#### 【 0 1 1 0 】

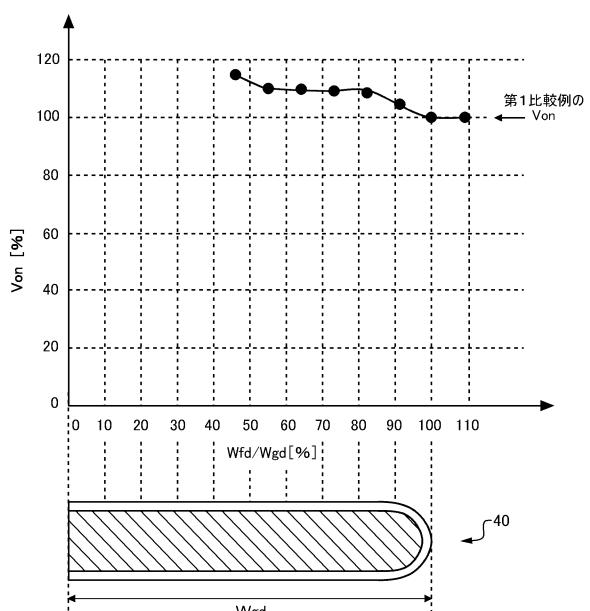

図 6 a は、本例の半導体装置 1 0 0 における幅  $W_{f d}$  とオン電圧  $V_{on}$  との関係の一例を示す図である。図 6 a においては、幅  $W_{f d}$  を幅  $W_{g d}$  に対する比率で示している。即ち、図 6 a における横軸は、 $W_{f d} / W_{g d} [ \% ]$  である。また、半導体装置 1 0 0 の才50

ン電圧  $V_{on}$  を第 1 比較例の半導体装置 150 の  $V_{on}$  に対する比率で示している。即ち、図 6 a における縦軸は、半導体装置 100 の  $V_{on}$  / 半導体装置 150 の  $V_{on}$  [%] である。図 6 a において、ゲートトレンチ部 40 の底部 89 は、幅比  $W_{fd} / W_{gd} = 90\% \sim 100\%$  の範囲に位置する。また、フローティング領域 17 の幅  $W_{fv}$  は、図 6 a の横軸において 10% 程度に相当する幅である。

#### 【0111】

フローティング領域 17 をゲートトレンチ部 40 の底部 89 の近傍に配置することで、図 6 a に示すように、第 1 比較例の  $V_{on}$  と比較してオン電圧  $V_{on}$  を、10% 未満の増加に抑制することができる。一例として、フローティング領域 17 の Z 軸方向における少なくとも一部が、ゲートトレンチ部 40 の底部 89 と接する深さに配置されてよい。この場合、フローティング領域 17 の Z 軸方向における当該少なくとも一部以外の残部は、ゲートトレンチ部 40 の底部 89 よりも上方に配置されていてよい。フローティング領域 17 は、Z 軸方向における全体がゲートトレンチ部 40 の底部 89 と接するように配置されていてもよい。

10

#### 【0112】

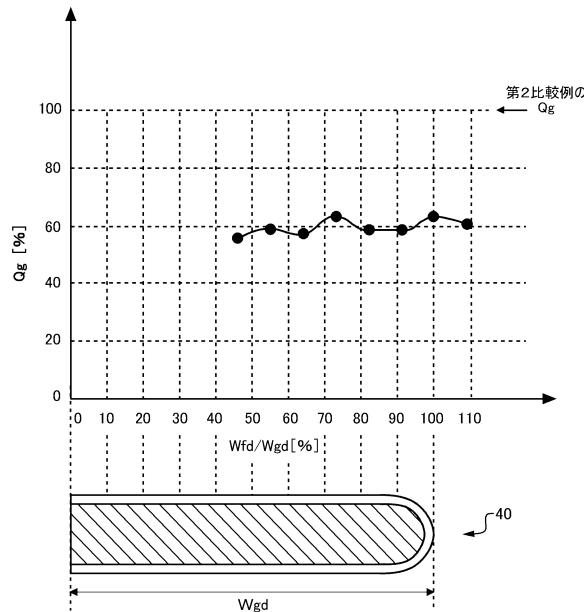

図 6 b は、本例の半導体装置 100 における、幅  $W_{fd}$  と、ターンオン時のゲート電流の積分値（電荷）  $Q_g$  との関係の一例を示す図である。図 6 b における横軸は、図 6 a と同様に  $W_{fd} / W_{gd}$  [%] である。図 6 b において、半導体装置 100 における電荷  $Q_g$  を、第 2 比較例の半導体装置 160 における電荷  $Q_g$  に対する比率で示している。即ち、図 6 b における縦軸は、半導体装置 100 の  $Q_g$  / 半導体装置 160 の  $Q_g$  [%] である。

20

#### 【0113】

半導体装置においては、 $Q_g$  が大きいほど、CG 容量が大きいことを示している。図 6 b に示すように、フローティング領域 17 をいずれの深さに設けても、半導体装置 100 の電荷  $Q_g$  を、第 2 比較例の  $Q_g$  と比較して約 40% 減少させることができる。つまり、半導体装置 100 の CG 容量を小さくできる。

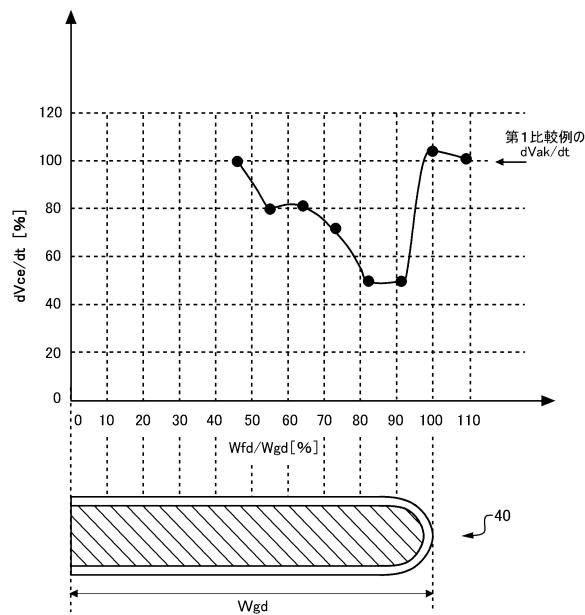

#### 【0114】

図 6 c は、本例の半導体装置 100 における、幅  $W_{fd}$  と、ターンオン時における CE 電圧の電圧減少率 ( $dV_{ce} / dt$ ) との関係の一例を示す図である。図 6 c における横軸は、図 6 a と同様に  $W_{fd} / W_{gd}$  [%] である。図 6 c において、( $dV_{ce} / dt$ ) を第 1 比較例の ( $dV_{ce} / dt$ ) に対する比率で示している。即ち、図 6 c における縦軸は、半導体装置 100 の ( $dV_{ce} / dt$ ) / 半導体装置 150 の ( $dV_{ce} / dt$ ) [%] である。

30

#### 【0115】

本例の半導体装置 100 は、図 6 c に示すように、 $W_{fd} / W_{gd}$  が約 70% (あるいは 73%) より小さい区間と、95% より大きい区間で、電圧減少率 ( $dV_{ce} / dt$ ) が約 80% 以上の値を示す。これに対して、 $W_{fd} / W_{gd}$  が 70% 以上 (あるいは 73% 以上) であって 100% よりも小さい区間で  $dV_{ce} / dt$  が減少している。特に  $W_{fd} / W_{gd}$  が 95% 以下の区間で  $dV_{ce} / dt$  が急激に減少している。また、 $W_{fd} / W_{gd}$  が概ね 80% から 92% までの範囲で、電圧減少率 ( $dV_{ce} / dt$ ) が約 50% の極小となっている。 $dV_{ce} / dt$  が極小となる  $W_{fd} / W_{gd}$  の範囲は、Z 軸方向におけるフローティング領域 17 の少なくとも一部が、ゲートトレンチ部 40 の底部 89 に配置される範囲と概ね一致する。

40

#### 【0116】

フローティング領域 17 をゲートトレンチ部 40 の底部 89 の近傍に配置することで、電子電流をメサ部中央に流しやすくなる。このため、正孔が蓄積されているゲートトレンチ部 40 の底部 89 の近傍において、正孔が分布している領域を電子電流で分断しやすくなり、変位電流を抑制しやすくなる。このため、電圧減少率 ( $dV_{ce} / dt$ ) を小さくすることができる。一例として図 6 c に示すように、CE 電圧の電圧減少率 ( $dV_{ce} / dt$ ) を第 1 比較例の電圧減少率 ( $dV_{ce} / dt$ ) と比較して、約 50% 減少させるこ

50

とができる。

#### 【0117】

フローティング領域17がゲートトレンチ部40の底部89よりも深い位置に配置される(図6cにおいて $W_{fd}/W_{gd}$ が100%より大きい領域)と、ゲートトレンチ部40とフローティング領域17とが離間してしまい、ゲートトレンチ部40とフローティング領域17との間を電子電流が流れる。このため、変位電流を抑制できなくなる。このため、図6cに示すように、 $W_{fd}/W_{gd}$ を100%より大きくすると、半導体装置100の電圧減少率( $dV_{ce}/dt$ )は急激に大きくなり、第1比較例の電圧減少率( $dV_{ce}/dt$ )と略同じ値を示す。以上より、Z軸方向におけるフローティング領域17の少なくとも一部をゲートトレンチ部40の底部89に接して設けると、CE電圧減少率を顕著に改善することができる。

#### 【0118】

以上より、 $W_{fd}/W_{gd}$ は、70%以上で100%未満であってよい。さらに $W_{fd}/W_{gd}$ は73%以上であってよく、80%以上であってもよい。 $W_{fd}/W_{gd}$ は、95%以下であってよく、92%以下であってよい。

#### 【0119】

図7は、図5aのc-c'断面におけるドーピング濃度分布の一例を示す図である。図7において縦軸は対数軸であり、横軸は線形軸である。図7に示すように、本例の半導体装置100において、フローティング領域17のドーピング濃度は、蓄積領域16のドーピング濃度よりも高くてよい。フローティング領域17のドーピング濃度は、蓄積領域16のドーピング濃度よりも10倍以上高くてよく、100倍以上高くててもよい。蓄積領域16のドーピング濃度は、一例として $1 \times 10^{17} / \text{cm}^{-3}$ である。フローティング領域17のドーピング濃度は、 $1 \times 10^{19} / \text{cm}^{-3}$ 以上の濃度であってもよい。

#### 【0120】

図7に示すように、本例の半導体装置100において、フローティング領域17のドーピング濃度は、ベース領域14のドーピング濃度よりも高くてよい。フローティング領域17のドーピング濃度は、ベース領域14のドーピング濃度よりも10倍以上高くてよく、100倍以上高くててもよい。ベース領域14のドーピング濃度は、一例として $3 \times 10^{17} / \text{cm}^{-3}$ である。フローティング領域17のドーピング濃度は、 $1 \times 10^{19} / \text{cm}^{-3}$ 以上の濃度であってもよい。

#### 【0121】

図8aは、本例の半導体装置100における、フローティング領域17のドーピング濃度とオン電圧 $V_{on}$ との関係の一例を示す図である。図8aにおいて、Z軸方向におけるフローティング領域17の少なくとも一部は、ゲートトレンチ部40の底部89に接して設けられている。図8aにおいて、フローティング領域17の各濃度におけるオン電圧 $V_{on}$ を、フローティング領域17の濃度が $1 \times 10^{14} / \text{cm}^{-3}$ の場合のオン電圧 $V_{on}$ に対する比率で示している。即ち、図8aにおける縦軸は、オン電圧 $V_{on}$ /(フローティング領域17の濃度が $1 \times 10^{14} / \text{cm}^{-3}$ の場合のオン電圧 $V_{on}$ )[%]である。

#### 【0122】

本例の半導体装置100のオン電圧 $V_{on}$ は、図8aに示すように、フローティング領域17のドーピング濃度が $1 \times 10^{17} / \text{cm}^{-3}$ を超えると増加し始める。ドーピング濃度が $1 \times 10^{20} / \text{cm}^{-3}$ から $1 \times 10^{21} / \text{cm}^{-3}$ の間ににおいて、 $V_{on}$ は104%から105%を示す。すなわち、フローティング領域17のドーピング濃度を10<sup>3</sup>倍から10<sup>4</sup>倍増加させても、オン電圧 $V_{on}$ は5%未満の増加に抑制することができることから、本例の半導体装置100のオン電圧 $V_{on}$ は、フローティング領域17のドーピング濃度に略影響を受けずに済むと言つてもよい。

#### 【0123】

図8bは、本例の半導体装置100における、フローティング領域17のドーピング濃度とCE電圧減少率( $dV_{ce}/dt$ )との関係の一例を示す図である。図8bにおいて、Z軸方向におけるフローティング領域17の少なくとも一部は、ゲートトレンチ部40

10

20

30

40

50

の底部 8 9 に接して設けられている。図 8 bにおいて、フローティング領域 1 7 の各濃度における C E 電圧減少率 ( $dV_{ce}/dt$ ) を、フローティング領域 1 7 の濃度が  $1 \times 10^{14} / cm^{-3}$  の場合の C E 電圧減少率 ( $dV_{ce}/dt$ ) に対する比率で示している。即ち、図 8 b における縦軸は、C E 電圧減少率 ( $dV_{ce}/dt$ ) / (フローティング領域 1 7 の濃度が  $1 \times 10^{14} / cm^{-3}$  の場合の C E 電圧減少率 ( $dV_{ce}/dt$ )) [%] である。

#### 【 0 1 2 4 】

本例の半導体装置 1 0 0 の C E 電圧減少率 ( $dV_{ce}/dt$ ) は、図 8 b に示すように、フローティング領域 1 7 のドーピング濃度が  $1 \times 10^{16} / cm^{-3}$ 、特に  $8 \times 10^{16} / cm^{-3}$  を超えると減少し始める。ドーピング濃度が  $3 \times 10^{17} / cm^{-3}$  に達すると、C E 電圧減少率 ( $dV_{ce}/dt$ ) は、ドーピング濃度が  $1 \times 10^{14} / cm^{-3}$  の場合の C E 電圧減少率 ( $dV_{ce}/dt$ ) と比較して、約 55% の C E 電圧減少率 ( $dV_{ce}/dt$ ) を示す。さらに、ドーピング濃度が  $1 \times 10^{18} / cm^{-3}$  を超えると、ドーピング濃度が  $1 \times 10^{14} / cm^{-3}$  の場合の C E 電圧減少率 ( $dV_{ce}/dt$ ) と比較して、約 50% の C E 電圧減少率 ( $dV_{ce}/dt$ ) を示す。即ち、本例の半導体装置 1 0 0 は、フローティング領域 1 7 のドーピング濃度を  $1 \times 10^{18} / cm^{-3}$  以上にすると、C E 電圧減少率 ( $dV_{ce}/dt$ ) を顕著に抑制することができる。

#### 【 0 1 2 5 】

フローティング領域 1 7 のドーピング濃度は、 $8 \times 10^{16} / cm^{-3}$  以上であってよく、 $3 \times 10^{17} / cm^{-3}$  以上であってよく、 $1 \times 10^{18} / cm^{-3}$  以上であってよく、 $1 \times 10^{19} / cm^{-3}$  以上であってもよい。フローティング領域 1 7 のドーピング濃度は、 $3 \times 10^{20} / cm^{-3}$  以下であってよく、 $3 \times 10^{20} / cm^{-3}$  以下であってよく、 $3 \times 10^{20} / cm^{-3}$  以下であってよく、 $3 \times 10^{20} / cm^{-3}$  以下であってもよい。

#### 【 0 1 2 6 】

一方、オン電圧の増加を約 3% 以下に抑える場合は、図 8 a より、フローティング領域 1 7 のドーピング濃度の上限値を、 $1 \times 10^{19} / cm^{-3}$  以下（あるいは未満）としてもよい。この場合、フローティング領域 1 7 のドーピング濃度の下限値は、図 8 a より、 $1 \times 10^{17} / cm^{-3}$  であってよい。

#### 【 0 1 2 7 】

図 9 a は、本例の半導体装置 1 0 0 における、幅 W m に占める幅 W f の割合 ( $W_f/W_m$  [%]) とオン電圧 V on との関係の一例を示す図である。図 9 a は、Z 軸方向におけるフローティング領域 1 7 の少なくとも一部が、ゲートトレンチ部 4 0 の底部 8 9 に接して設けられている場合における、( $W_f/W_m$  [%]) とオン電圧 V on との関係を示している。 $(W_f/W_m)$  が 0% の場合とは、W f がゼロの場合、即ちフローティング領域 1 7 が設けられない場合である。また、( $W_f/W_m$ ) が 100% の場合とは、フローティング領域 1 7 がメサ幅全体にわたり設けられている場合である。図 9 a において、オン電圧 V on を、( $W_f/W_m$ ) が 0% の場合のオン電圧 V on に対する比率で示している。即ち、図 9 a における縦軸は、オン電圧 V on / ( $W_f/W_m$ ) が 0% の場合のオン電圧 V on [%] である。

#### 【 0 1 2 8 】

( $W_f/W_m$ ) が約 60% の場合、( $W_f/W_m$ ) が 0% の場合と比較して、オン電圧 V on が約 20% 増加する。また、( $W_f/W_m$ ) が約 85% の場合、( $W_f/W_m$ ) が 0% の場合と比較してオン電圧 V on が約 40% 増加する。( $W_f/W_m$ ) が 10% 以上 50% 以下、即ち幅 W f がメサ幅 W m の 0.1 倍以上 0.5 倍以下の場合、オン電圧 V on の増加を 20% 未満に抑制することができる。

#### 【 0 1 2 9 】

図 9 b は、本例の半導体装置 1 0 0 における、幅 W m に占める幅 W f の割合 ( $W_f/W_m$  [%]) と、ゲート電極に蓄積される電荷 Q g との関係の一例を示す図である。図 9 b は、Z 軸方向におけるフローティング領域 1 7 の少なくとも一部が、ゲートトレンチ部 4 0 の底部 8 9 に接して設けられている場合における、( $W_f/W_m$  [%]) と電荷 Q g と

10

20

30

40

50

の関係を示している。図 9 bにおいて、電荷  $Q_g$  を、 $(W_f / W_m)$  が 0 % の場合の電荷  $Q_g$  に対する比率で示している。即ち、図 9 bにおける縦軸は、電荷  $Q_g / (W_f / W_m)$  が 0 % の場合の電荷  $Q_g$  [%] である。

#### 【0130】

$(W_f / W_m)$  が約 60 % の場合、 $(W_f / W_m)$  が 0 % の場合と比較して、電荷  $Q_g$  は約 5 % 減少する。 $(W_f / W_m)$  が約 60 % を超えると電荷  $Q_g$  は増加傾向にある。即ち、 $(W_f / W_m)$  が約 60 % の場合に、電荷  $Q_g$  は極小値を示す。以上より、本例の半導体装置 100 のゲート電極に蓄積される電荷  $Q_g$  は、フローティング領域 17 を設けることで低減できることが明らかである。

#### 【0131】

図 9 c は、本例の半導体装置 100 における、幅  $W_m$  に占める幅  $W_f$  の割合 ( $W_f / W_m$  [%]) と、CE 電圧減少率 ( $dV_{ce} / dt$ ) との関係の一例を示す図である。図 9 c は、Z 軸方向におけるフローティング領域 17 の少なくとも一部が、ゲートトレンチ部 40 の底部 89 に接して設けられている場合における、 $(W_f / W_m$  [%]) と CE 電圧減少率 ( $dV_{ce} / dt$ ) との関係を示している。図 9 c において、CE 電圧減少率 ( $dV_{ce} / dt$ ) を、 $(W_f / W_m)$  が 0 % の場合の CE 電圧減少率 ( $dV_{ce} / dt$ ) に対する比率で示している。即ち、図 9 c における縦軸は、CE 電圧減少率 ( $dV_{ce} / dt$ ) /  $(W_f / W_m)$  が 0 % の場合の CE 電圧減少率 ( $dV_{ce} / dt$ ) [%] である。

#### 【0132】

本例の半導体装置 100 の CE 電圧減少率 ( $dV_{ce} / dt$ ) は、 $(W_f / W_m)$  が約 30 % の場合に極小値を示す。 $(W_f / W_m)$  が約 30 % の場合に、 $(W_f / W_m)$  が 0 % の場合と比較して、CE 電圧減少率 ( $dV_{ce} / dt$ ) を約 50 % に抑制することができる。図 3 において説明したように、フローティング領域 17 を設けることにより、電子電流はゲートトレンチ部 40 近傍から第 1 メサ部 60 の中央付近に流れる経路をたどる。第 1 メサ部 60 の中央付近に流れる電子電流が正孔分布を分断し、変位電流の抑制をもたらす。このため、CE 電圧減少率 ( $dV_{ce} / dt$ ) を抑制することができる。

#### 【0133】

$(W_f / W_m)$  が小さすぎると（例えば 10 % よりも小さい場合）、電子電流の経路が中央付近を十分に流れず、正孔分布の分断が不十分となるので、CE 電圧減少率 ( $dV_{ce} / dt$ ) が十分に抑制されない。反対に、 $(W_f / W_m)$  が大きすぎても（例えば 60 % よりも大きい場合）、電子電流の経路が中央付近を十分に流れず、正孔分布の分断が不十分となるので、CE 電圧減少率 ( $dV_{ce} / dt$ ) が十分に抑制されない。 $(W_f / W_m)$  が約 30 % の場合、電子電流の経路を中央付近にすることができるので、正孔分布が分断され、CE 電圧減少率 ( $dV_{ce} / dt$ ) が極小値を示す。このことから、 $(W_f / W_m)$  は 10 % 以上 60 % 以下であることが好ましい。 $(W_f / W_m)$  は、20 % 以上であってよく、25 % 以上であってもよい。 $(W_f / W_m)$  は、50 % 以下であってよく、40 % 以下であってもよく、35 % 以下であってもよい。

#### 【0134】

幅  $W_f$  は幅  $W_{ef}$  よりも小さいことが好ましい。幅  $W_f$  は、幅  $W_{ef}$  の 11 % (幅  $W_{ef}$  の 1 / 9) 以上 50 % 以下であってよい。幅  $W_f$  は 0.07 μm 以上 0.35 μm 以下であってよい。

#### 【0135】

図 10 は、図 1 a における b - b' 断面の他の一例を示す図である。図 10 に示す半導体装置 100 は、蓄積領域 16 が半導体基板 10 の深さ方向に複数設けられる点で、図 5 a に示す半導体装置 100 と異なる。蓄積領域 16 以外の構造は、図 5 a において説明した半導体装置 100 と同一であってよい。本例の半導体装置 100 は、深さ方向に蓄積領域 16 - 1、蓄積領域 16 - 2 および蓄積領域 16 - 3 を有する。蓄積領域 16 - 1 と蓄積領域 16 - 2 との Z 軸方向の間、および蓄積領域 16 - 2 と蓄積領域 16 - 3 との Z 軸方向の間には、それぞれドリフト領域 18 が設けられてよい。

#### 【0136】

10

20

30

40

50

第1メサ部60には、第3蓄積領域16-3の下方にフローティング領域17が設けられる。フローティング領域17は、ゲートトレンチ部40と接している。また、フローティング領域17は、第1メサ部60のY軸方向における一部分にだけ設けられている。即ち、フローティング領域17は、Y軸方向において第1メサ部60の全幅にわたっては設けられておらず、Y軸方向において部分的に設けられている。図10の例では、フローティング領域17は、ゲートトレンチ部40と接する位置から、第1メサ部60内のY軸方向の所定の位置まで連続して設けられており、当該所定の位置よりもゲートトレンチ部40から離れた位置には設けられていない。

#### 【0137】

図11は、図10のd-d'断面におけるドーピング濃度分布の一例を示す図である。図11に示すように、本例の半導体装置100において、最も下方に設けられる第3蓄積領域16-3のドーピング濃度は、最も上方に配置される第1蓄積領域16-1のドーピング濃度よりも低くてよい。第1蓄積領域16-1、第2蓄積領域16-2および第3蓄積領域16-3のドーピング濃度は、下方に配置される第3蓄積領域16-3ほど低くてよい。

10

#### 【0138】

第2蓄積領域16-2のドーピング濃度は、第1蓄積領域16-1のドーピング濃度の1/3以上2/3以下であってよい。第3蓄積領域16-3のドーピング濃度は、第1蓄積領域16-1のドーピング濃度の1/10以上であってよい。第1蓄積領域16-3のドーピング濃度は、第1蓄積領域16-1のドーピング濃度の3/10以下であってよい。第1蓄積領域16-1のドーピング濃度は、 $8 \times 10^{16} / \text{cm}^3$ 以上 $2 \times 10^{17} / \text{cm}^3$ 以下であってよい。第1蓄積領域16-1のドーピング濃度は、一例として $1 \times 10^{17} / \text{cm}^3$ である。第2蓄積領域16-2のドーピング濃度は、 $3 \times 10^{16} / \text{cm}^3$ 以上 $7 \times 10^{16} / \text{cm}^3$ 以下であってよい。第2蓄積領域16-2のドーピング濃度は、一例として $5 \times 10^{16} / \text{cm}^3$ である。第3蓄積領域16-3のドーピング濃度は、 $1 \times 10^{16} / \text{cm}^3$ 以上 $3 \times 10^{16} / \text{cm}^3$ 以下であってよい。第3蓄積領域16-3のドーピング濃度は、一例として $2 \times 10^{16} / \text{cm}^3$ である。

20

#### 【0139】

本例の半導体装置100は、蓄積領域16のドーピング濃度が、下方に配置される第3蓄積領域16-3ほど低い。従って、第1蓄積領域16-1、第2蓄積領域16-2および第3蓄積領域16-3のドーピング濃度を略等しく設けた場合、または下方に配置される第3蓄積領域16-3ほどドーピング濃度を高く設けた場合に比べて、半導体装置100は、CG容量の増加を抑制することができる。

30

#### 【0140】

本例の半導体装置100は、第3蓄積領域16-3の下方にフローティング領域17が設けられるので、電子電流は、図3に示したように第1メサ部60の中央付近を流れる。また第1メサ部60中央付近において正孔分布が分断されるので、ゲート導電部44が充電されることによる変位電流を抑制することができる。このため、CE電圧の電圧減少率( $dV_{ce}/dt$ )を抑制することができる。即ち、本例の半導体装置100は、CE電圧の電圧減少率( $dV_{ce}/dt$ )を抑制しつつ、CG容量の増加を抑制することができる。このため、本例の半導体装置100は、CE電圧の電圧減少率( $dV_{ak}/dt$ )を抑制しつつ、ターンオン損失を減少させることができる。また、オン電圧とターンオフ損失のトレードオフを維持することができる。

40

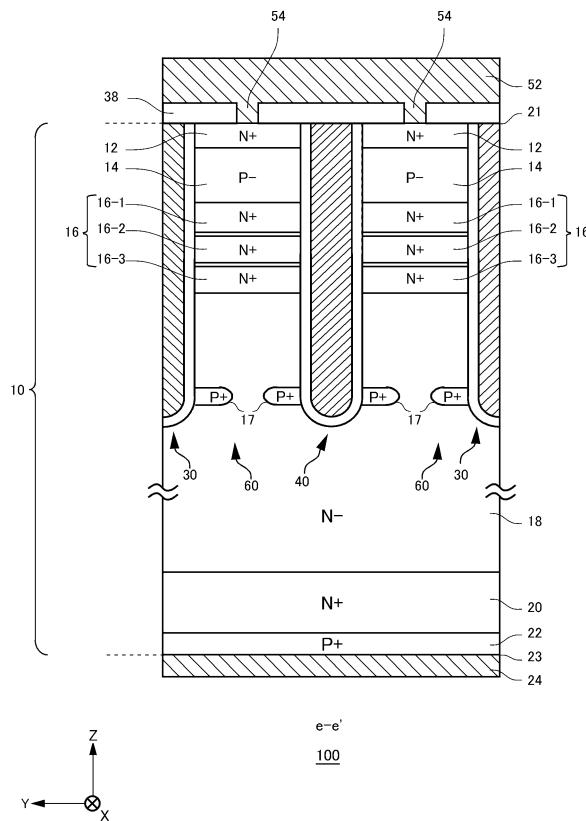

#### 【0141】

図12aは、本実施形態に係る半導体装置100の他の上面の一例を部分的に示す図である。図12aに示す半導体装置100は、図1aに示す半導体装置100において、トランジスタ部70の第1メサ部60における蓄積領域16の下方に、ダミートレンチ部30に接してフローティング領域17が更に設けられる点で、図1aに示す半導体装置100と異なる。図12aにおいて、半導体基板10の上面視で、フローティング領域17が設けられる範囲を破線で示している。

50

**【 0 1 4 2 】**

フローティング領域 17 は、図 12 a に示すように、配列方向（Y 軸方向）において、第 1 メサ部 60 の一部分に設けられる。即ち、フローティング領域 17 は、Y 軸方向において第 1 メサ部 60 の全幅にわたっては設けられておらず、Y 軸方向において部分的に設けられている。図 12 a の例では、第 1 メサ部 60 において、ダミートレンチ部 30 と接する位置から当該第 1 メサ部 60 内の Y 軸方向の所定位置まで、フローティング領域 17 が連続して設けられている。また、当該第 1 メサ部 60 において、ゲートトレンチ部 40 と接する位置から当該第 1 メサ部 60 内の Y 軸方向の所定位置まで、フローティング領域 17 が連続して設けられている。ゲートトレンチ部 40 と接するフローティング領域 17 の先端位置と、ダミートレンチ部 30 と接するフローティング領域 17 の先端位置は、Y 軸方向において異なる。また、Y 軸方向における 2 つのフローティング領域 17 の間には、別のフローティング領域 17 が設けられない。

10

**【 0 1 4 3 】**

各フローティング領域 17 の Y 軸方向における先端位置は、半導体基板の上面視で、コンタクトホール 54 と重なっていてもよいし、重なっていないてもよい。図 12 a は、各フローティング領域 17 の先端位置が、共にコンタクトホール 54 と重ならない一例を示している。

**【 0 1 4 4 】**

ダミートレンチ部 30 に接するフローティング領域 17 は、第 1 メサ部 60 の X 軸方向における両端に設けられるコンタクト領域 15 の一方から他方まで連続して設けられてよい。上述したように、フローティング領域 17 はダミートレンチ部 30 に接して設けられてよい。

20

**【 0 1 4 5 】**

ダミートレンチ部 30 に接するフローティング領域 17 の X 軸方向における両端の位置は、蓄積領域 16 の X 軸方向における両端の位置と一致していてよく、異なっていてもよい。図 12 a においては、ダミートレンチ部 30 に接するフローティング領域 17 の X 軸方向の端と、蓄積領域 16 の X 軸方向の端を、異ならせて示している。

**【 0 1 4 6 】**

図 12 b は、図 12 a における e - e' 断面の一例を示す図である。フローティング領域 17 は、Y 軸方向において、第 1 メサ部 60 の一部分に設けられる。即ち、 $W_f < W_m$  である。図 12 b の例では、ダミートレンチ部 30 に接するフローティング領域 17 が、当該ダミートレンチ部 30 と接する位置から幅  $W_f$  にわたって設けられている。また、ゲートトレンチ部 40 に接する別のフローティング領域 17 が、当該ゲートトレンチ部 40 と接する位置から幅  $W_f$  にわたって設けられている。

30

**【 0 1 4 7 】**

ダミートレンチ部 30 に接して設けられるフローティング領域 17 は、ゲートトレンチ部 40 に接して設けられるフローティング領域 17 と、Y 軸方向において離間して配置される。即ち、同じ第 1 メサ部 60 内に設けられる、ダミートレンチ部 30 に接するフローティング領域 17 と、ゲートトレンチ部 40 に接する別のフローティング領域 17 とは、当該第 1 メサ部 60 内において接しない。

40

**【 0 1 4 8 】**

また、ダミートレンチ部 30 に接するフローティング領域 17 は、ゲートトレンチ部 40 に接する別のフローティング領域 17 と、略同じ深さに設けられてよい。Y 軸方向において、ダミートレンチ部 30 に接するフローティング領域 17 と、ゲートトレンチ部 40 に接するフローティング領域 17 との間には、ドリフト領域 18 が設けられてよい。

**【 0 1 4 9 】**

本例の半導体装置 100 は、ダミートレンチ部 30 に接して設けられるフローティング領域 17 が、ゲートトレンチ部 40 に接して設けられるフローティング領域 17 と、Y 軸方向において離間して配置されるので、図 3 と同様の作用により、電子電流はフローティング領域 17 の深さにおいて、第 1 メサ部 60 の中央付近を流れる。電子電流が第 1 メサ

50

部 6 0 の中央付近を流れると、第 1 メサ部 6 0 の底部近傍における正孔分布が第 1 メサ部 6 0 の中央付近で分断されるので、ゲートトレンチ部 4 0 の下端における正孔の蓄積が抑制される。このため、変位電流を小さくすることできる。このため、C E 電圧の電圧減少率 ( $d V_a k / d t$ ) を抑制することができる。

#### 【 0 1 5 0 】

図 1 2 c は、図 1 2 a における e - e' 断面の他の一例を示す図である。図 1 2 c に示す半導体装置 1 0 0 は、図 1 2 b に示す半導体装置 1 0 0 において、蓄積領域 1 6 が複数設けられる点で、図 1 2 b に示す半導体装置 1 0 0 と異なる。蓄積領域 1 6 - 1 と蓄積領域 1 6 - 2 との Z 軸方向の間、および蓄積領域 1 6 - 2 と蓄積領域 1 6 - 3 との Z 軸方向の間には、それぞれドリフト領域 1 8 が設けられてよい。蓄積領域 1 6 - 1 、蓄積領域 1 6 - 2 および蓄積領域 1 6 - 3 のドーピング濃度は、それぞれ図 1 0 に示す半導体装置 1 0 0 における蓄積領域 1 6 - 1 、蓄積領域 1 6 - 2 および蓄積領域 1 6 - 3 のドーピング濃度と同じドーピング濃度に設けられてよい。

10

#### 【 0 1 5 1 】

ダミートレンチ部 3 0 に接して設けられるフローティング領域 1 7 は、ゲートトレンチ部 4 0 に接して設けられるフローティング領域 1 7 と、Y 軸方向において離間して配置される。ダミートレンチ部 3 0 に接して設けられるフローティング領域 1 7 は、ゲートトレンチ部 4 0 に接して設けられるフローティング領域 1 7 と、略同じ深さに設けられてよい。

20

#### 【 0 1 5 2 】

本例の半導体装置 1 0 0 は、フローティング領域 1 7 がダミートレンチ部 3 0 に接して設けられ、且つ蓄積領域 1 6 が複数設けられる。このため、ダミートレンチ部 3 0 に接するフローティング領域 1 7 に蓄積された正孔が、ダミートレンチ部 3 0 近傍を上面 2 1 に向かって進んでも、当該フローティング領域 1 7 の上方に蓄積領域 1 6 が設けられているので、蓄積領域 1 6 に蓄積されやすい。このため、当該正孔がエミッタ電極 5 2 まで抜けてしまうことを抑制することができる。

20

#### 【 0 1 5 3 】

また、本例の半導体装置 1 0 0 は、ダミートレンチ部 3 0 に接して設けられるフローティング領域 1 7 が、ゲートトレンチ部 4 0 に接して設けられるフローティング領域 1 7 と、Y 軸方向において離間して配置されるので、図 1 2 b に示す半導体装置 1 0 0 と同様に、電子電流はフローティング領域 1 7 の深さにおいて、第 1 メサ部 6 0 の中央付近を流れる。このため、図 1 2 b に示す半導体装置 1 0 0 と同様に、C E 電圧の電圧減少率 ( $d V_a k / d t$ ) を抑制することができる。

30

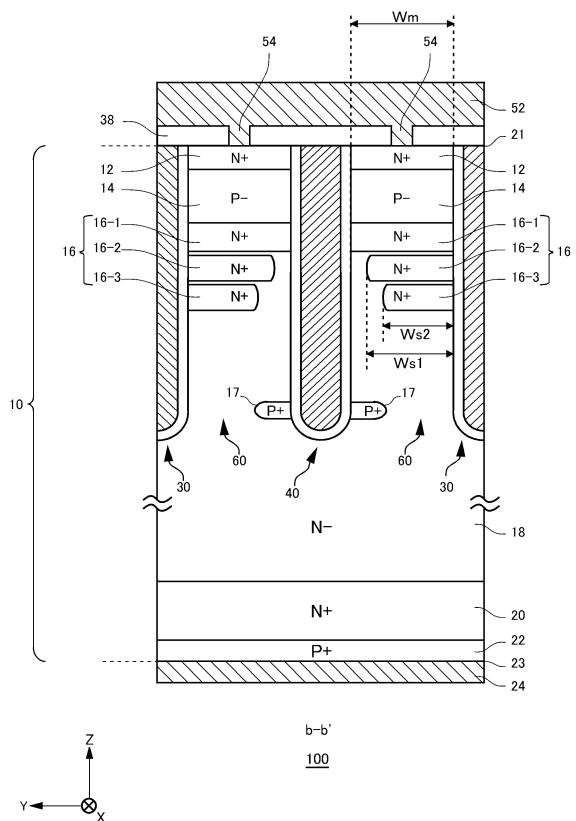

#### 【 0 1 5 4 】

図 1 3 a は、図 1 a における b - b' 断面の他の一例を示す図である。図 1 3 a に示す半導体装置 1 0 0 は、図 1 0 に示す半導体装置 1 0 0 において、第 2 蓄積領域 1 6 - 2 および第 3 蓄積領域 1 6 - 3 がゲートトレンチ部 4 0 と離間して設けられる点で、図 1 0 に示す半導体装置 1 0 0 と異なる。蓄積領域 1 6 - 1 と蓄積領域 1 6 - 2 との Z 軸方向の間、および蓄積領域 1 6 - 2 と蓄積領域 1 6 - 3 との Z 軸方向の間には、それぞれドリフト領域 1 8 が設けられてよい。

30

#### 【 0 1 5 5 】

本例において、幅 W s 1 は、第 2 蓄積領域 1 6 - 2 の Y 軸方向の幅である、幅 W s 2 は、第 3 蓄積領域 1 6 - 3 の Y 軸方向の幅である。本例において、幅 W s 1 および幅 W s 2 は、共に幅 W m よりも小さい。

40

#### 【 0 1 5 6 】

図 2 b において説明したように、第 1 蓄積領域 1 6 - 1 の下方に設けられる第 2 蓄積領域 1 6 - 2 は、第 1 蓄積領域 1 6 - 1 の中央付近からゲートトレンチ部 4 0 に戻りかけた電子電流を、第 1 メサ部 6 0 の中央付近に流れやすくする。このため、第 2 蓄積領域 1 6 - 2 は、第 1 メサ部 6 0 の Y 軸方向における全体に設けられなくても、第 1 メサ部 6 0 の中央付近に設けられれば、電子電流の経路を第 1 メサ部 6 0 の中央付近にし得る。

50

#### 【 0 1 5 7 】

第3蓄積領域16-3は、第2蓄積領域16-2により第1メサ部60の中央付近に流れやすくなった電子電流を、さらに第1メサ部60の中央付近に流れやすくする。第2蓄積領域16-2からゲートトレンチ部40に戻りかける電子電流は、第1蓄積領域16-1からゲートトレンチ部40に戻りかける電子電流よりも小さい。このため、幅W<sub>s2</sub>は幅W<sub>s1</sub>よりも小さくてよい。

#### 【0158】

幅W<sub>s1</sub>および幅W<sub>s2</sub>は、幅W<sub>m</sub>の60%以上90%以下であってよい。幅W<sub>s2</sub>は幅W<sub>s1</sub>よりも小さくてよいが、大きくてよい。図13aは、幅W<sub>s2</sub>が幅W<sub>s1</sub>よりも小さい一例を示している。

#### 【0159】

また、第2蓄積領域16-2および第3蓄積領域16-3は、ダミートレンチ部30に接していてよいが、離れていてもよい。図13aは、第2蓄積領域16-2および第3蓄積領域16-3が、ダミートレンチ部30に接する一例を示している。

#### 【0160】

図13bは、図1aにおけるb-b'断面の他の一例を示す図である。図13bに示す半導体装置100は、図10に示す半導体装置100において、第2蓄積領域16-2および第3蓄積領域16-3がダミートレンチ部30と離間して設けられる点で、図10に示す半導体装置100と異なる。蓄積領域16-1と蓄積領域16-2とのZ軸方向の間、および蓄積領域16-2と蓄積領域16-3とのZ軸方向の間には、それぞれドリフト領域18が設けられてよい。

10

#### 【0161】

本例において、幅W<sub>s1'</sub>は、第2蓄積領域16-2のY軸方向の幅である、幅W<sub>s2'</sub>は、第3蓄積領域16-3のY軸方向の幅である。本例において、幅W<sub>s1'</sub>および幅W<sub>s2'</sub>は、共に幅W<sub>m</sub>よりも小さい。

#### 【0162】

図2bにおいて説明したように、本例の半導体装置100において、電子電流は、ゲートトレンチ部40近傍から第1メサ部60の中央付近にかけて、半導体基板10の深さ方向に流れる。このため、第2蓄積領域16-2および第3蓄積領域16-3は、第1メサ部60の中央付近に設けられれば、ダミートレンチ部30と離間していてよい。

#### 【0163】

幅W<sub>s1'</sub>および幅W<sub>s2'</sub>は、幅W<sub>m</sub>の60%以上90%以下であってよい。幅W<sub>s2'</sub>は幅W<sub>s1'</sub>よりも小さくてよいが、大きくてよい。図13aは、幅W<sub>s2'</sub>が幅W<sub>s1'</sub>よりも小さい一例を示している。

20

#### 【0164】

また、第2蓄積領域16-2および第3蓄積領域16-3は、ゲートトレンチ部40に接していてよいが、離れていてもよい。図13bは、第2蓄積領域16-2および第3蓄積領域16-3が、ゲートトレンチ部40に接する一例を示している。

#### 【0165】

図14は、図1aにおけるb-b'断面の他の一例を示す図である。図14に示す半導体装置100は、図5aに示す半導体装置100において、蓄積領域16が設けられない点で、図5aに示す半導体装置100と異なる。本例の半導体装置100において、幅W<sub>m</sub>、幅W<sub>f</sub>、幅W<sub>e f</sub>、幅W<sub>g d</sub>、幅W<sub>f d</sub>、幅W<sub>b</sub>および幅W<sub>b f</sub>は、図5aに示す半導体装置100と同じであってよい。

30

#### 【0166】

本例の半導体装置100においても、幅W<sub>b f</sub>は幅W<sub>b</sub>よりも大きくてよい。幅W<sub>b f</sub>を幅W<sub>b</sub>よりも大きくすることで、トランジスタ部70がオン状態の場合に、ベース領域14とドリフト領域18との接合面から半導体基板10の深さ方向に拡張する空乏層が、フローティング領域17に達しにくくなる。当該空乏層がフローティング領域17に達すると、電子電流が遮断されてしまう。本例の半導体装置100は、幅W<sub>b f</sub>が幅W<sub>b</sub>よりも大きいので、電子電流を遮断することなく、第1メサ部60の中央付近に流すことがで

40

50

きる。幅  $W_{bf}$  は、幅  $W_b$  の 2 倍以上であってよい。幅  $W_{bf}$  は、一例として  $3 \mu m$  である。

#### 【0167】

本例の半導体装置 100 は、蓄積領域 16 が設けられないので、電子電流は、半導体基板 10 の深さ方向に、ベース領域 14 のゲートトレンチ部 40 近傍におけるチャネルを通過した後、ゲートトレンチ部 40 の近傍を流れ続ける。ゲートトレンチ部 40 の近傍を半導体基板 10 の深さ方向に流れ続けた電子電流は、図 3 において説明したように、フローティング領域 17 により経路を曲げられ、ゲートトレンチ部 40 近傍から第 1 メサ部 60 の中央付近に流れる経路をたどる。

#### 【0168】

電子電流が第 1 メサ部 60 の中央付近を流れると、第 1 メサ部 60 の底部近傍における正孔分布は、第 1 メサ部 60 中央付近で分断されるので、ゲートトレンチ部 40 の下端における正孔の蓄積が抑制される。その結果、変位電流を小さくすることできる。本例の半導体装置 100 は、変位電流を小さくすることができるので、ゲート導電部 44 の充電も小さくなり、ゲート電圧  $V_g$  の瞬間的な増加も抑制される。これにより、CE 電圧の電圧減少率 ( $dVak/dt$ ) が抑制される。

10

#### 【0169】

さらに、本例の半導体装置 100 は、ゲートトレンチ部 40 に接して蓄積領域 16 が設けられない。このため、本例の半導体装置 100 は、図 5a に示す半導体装置 100 よりも CG 容量の増加を防ぐことができる。即ち、本例の半導体装置 100 は、CE 電圧の電圧減少率 ( $dVak/dt$ ) を抑制しつつ、CG 容量の増加を抑制することができる。このため、本例の半導体装置 100 は、CE 電圧の電圧減少率 ( $dVak/dt$ ) を抑制しつつ、ターンオン損失を減少させることができる。また、オン電圧とターンオフ損失のトレードオフを維持することができる。

20

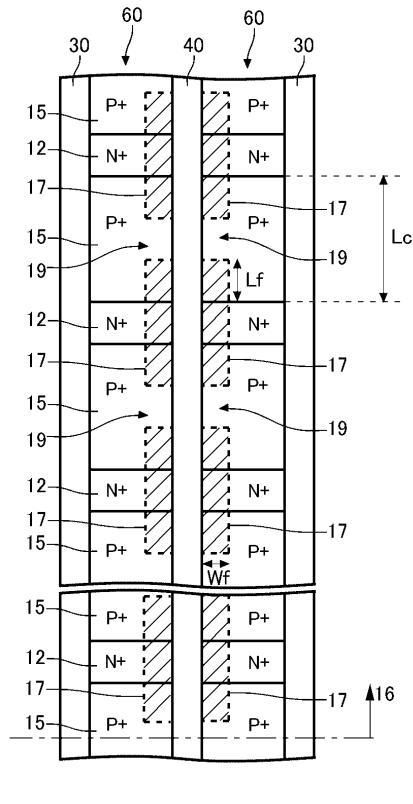

#### 【0170】

図 15 は、第 1 メサ部 60 におけるフローティング領域 17 の他の配置例を示す図である。図 15 は、第 1 メサ部 60 の部分的な上面図である。図 15 においては、フローティング領域 17 が設けられている領域に、斜線のハッティングを付している。フローティング領域 17 以外の構造については、図 1a から図 14 において説明したいずれかの態様の半導体装置 100 と同一であってよい。例えば図 15 においては、フローティング領域 17 がゲートトレンチ部 40 に設けられ、ダミートレンチ部 30 には設けられていないが、ゲートトレンチ部 40 と同様のフローティング領域 17 が、ダミートレンチ部 30 にも設けられていてよい。

30

#### 【0171】

本例のフローティング領域 17 は、ゲートトレンチ部 40 の延伸方向 (X 軸方向) において、離散的に配置されている。つまり、複数のフローティング領域 17 が、X 軸方向において間隔を有して配置されている。フローティング領域 17 の Y 軸方向における幅  $W_f$  は、図 1a から図 14 において説明したいずれかの態様のフローティング領域 17 と同一である。

40

#### 【0172】

それぞれのフローティング領域 17 は、X 軸方向において、エミッタ領域 12 よりも広い範囲に渡って設けられていてよい。つまり、それぞれのフローティング領域 17 は、X 軸方向において、エミッタ領域 12 の全体を覆うように配置されていてよい。この場合、フローティング領域 17 の X 軸方向における端部は、コンタクト領域 15 と重なる位置に配置されている。X 軸方向において、2 つのフローティング領域 17 の間の領域を隙間 19 とする。隙間 19 は、全体がコンタクト領域 15 と重なっていてよい。コンタクト領域 15 の下側には、フローティング領域 17 は形成されていない。特に、延伸方向に沿ったコンタクト領域 15 の中央の下側には隙間 19 が配置されて、フローティング領域 17 は形成されていない。

#### 【0173】

50

それぞれのコンタクト領域 15 の X 軸方向の長さを  $L_c$  とする。X 軸方向において、1 つのフローティング領域 17 が、1 つのコンタクト領域 15 と重なる長さ  $L_f$  は、コンタクト領域 15 の長さ  $L_c$  の半分より小さい。長さ  $L_f$  は、長さ  $L_c$  の 1 / 3 以下であってよい。

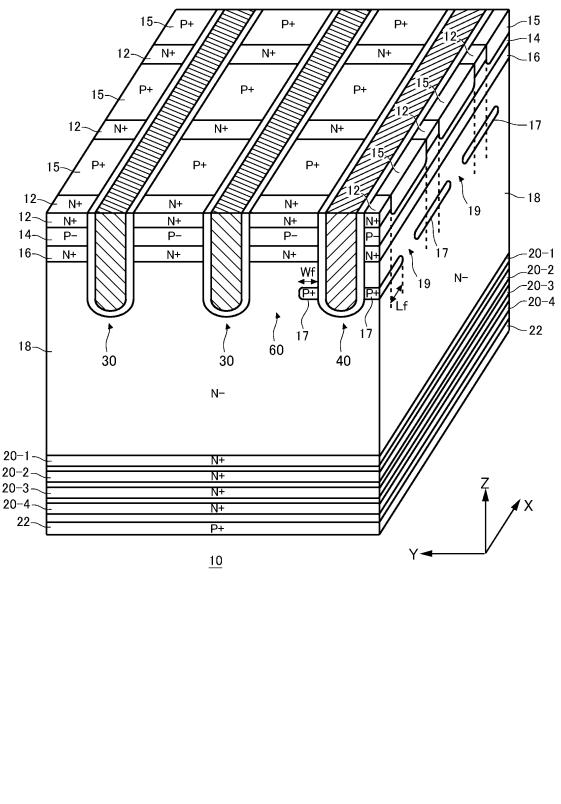

#### 【0174】

図 16 は、半導体基板 10 の部分的な斜視断面図である。図 16 においては、エミッタ領域 12 を通過する YZ 面、ゲートトレンチ部 40 に隣接する第 1 メサ部 60 の Y 軸方向における中央を通過する XZ 面、および、半導体基板 10 の上面 21 の各面を示している。

#### 【0175】

また、XZ 面において、エミッタ領域 12 と重なる範囲を破線で示している。それぞれのフローティング領域 17 は、X 軸方向において、エミッタ領域 12 の全体およびコンタクト領域 15 の一部と重なるように配置されている。フローティング領域 17 を、エミッタ領域 12 を覆うように選択的に配置することで、オン電圧  $V_{on}$  の増加を抑えて、CE 電圧の電圧減少率 ( $dV_{ce} / dt$ ) を小さくできる。また、オン電圧  $V_{on}$  と、ターンオフ損失のトレードオフを維持することができる。

10

#### 【0176】

X 軸方向において、フローティング領域 17 とコンタクト領域 15 とが重なる長さ  $L_f$  は、Y 軸方向におけるフローティング領域 17 の幅  $W_f$  に比べて、小さくてよい。長さ  $L_f$  は、幅  $W_f$  と同一であってよく、幅  $W_f$  より大きくてよい。

#### 【0177】

フローティング領域 17 の近傍では、静電ポテンシャル分布は、正孔がフローティング領域 17 に集まりやすい分布となる。そのため、コンタクト領域 15 の下側にフローティング領域 17 があると、フローティング領域 17 を介して正孔がコンタクト領域 15 に分散されやすい。そのため、IE 効果が減少し、オン電圧  $V_{on}$  が増加する場合がある。本例のように、コンタクト領域 15 の下側にフローティング領域 17 を形成しないことで、ホールをエミッタ領域 12 に集中しやすくでき、IE 効果を維持してオン電圧  $V_{on}$  の増加を抑えることができる。

20

#### 【0178】

なお本例の半導体装置 100 は、Z 軸方向に複数のバッファ領域 20 を有している。それぞれのバッファ領域 20 は、Z 軸方向のドーピング濃度分布においてピークを有している。それぞれのバッファ領域 20 の間には、Z 軸方向のドーピング濃度分布において谷が配置されていてよい。バッファ領域 20 の構造は、図 1a から図 14 において説明した例と同様であってもよい。

30

#### 【0179】

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

#### 【0180】

特許請求の範囲、明細書、および図面中において示した装置、システム、プログラム、および方法における動作、手順、ステップ、および段階等の各処理の実行順序は、特段「より前に」、「先立って」等と明示しておらず、また、前の処理の出力を後の処理で用いるのでない限り、任意の順序で実現しうることに留意すべきである。特許請求の範囲、明細書、および図面中の動作フローに関して、便宜上「まず、」、「次に、」等を用いて説明したとしても、この順で実施することが必須であることを意味するものではない。

40

#### 【符号の説明】

#### 【0181】

10 . . . 半導体基板、11 . . . ウェル領域、12 . . . エミッタ領域、13 . . . フローティング領域端、14 . . . ベース領域、15 . . . コンタクト領域、16 . . . 蓄積領域、16 - 1 . . . 第 1 蓄積領域、16 - 2 . . . 第 2 蓄積領域、16 - 3 . . . 第

50

3 蓄積領域、17・・・フローティング領域、18・・・ドリフト領域、19・・・間隙

、20・・・バッファ領域、21・・・上面、22・・・コレクタ領域、23・・・下面

、24・・・コレクタ電極、25・・・接続部、29・・・延伸部分、30・・・ダミー<sup>トレンチ</sup>部、31・・・接続部分、32・・・ダミー絶縁膜、34・・・ダミー導電部、

38・・・層間絶縁膜、39・・・延伸部分、40・・・ゲートトレンチ部、41・・・接

続部分、42・・・ゲート絶縁膜、43・・・側壁、44・・・ゲート導電部、48・・・

・ゲートランナー、49・・・コンタクトホール、50・・・ゲート金属層、52・・・

エミッタ電極、54・・・コンタクトホール、56・・・コンタクトホール、60・・・

第1メサ部、62・・・第2メサ部、64・・・第3メサ部、70・・・トランジスタ部

、80・・・ダイオード部、82・・・カソード領域、87・・・ホール高濃度領域、8

9・・・底部、90・・・境界部、100・・・半導体装置、150・・・半導体装置、

160・・・半導体装置

10

〔 図 面 〕

【 囮 1 a 】

【図 1 b】

20

30

40

50

【図 2 a】

【図 2 b】

【図 3】

【図 4 a】

【図 4 b】

【図 5 a】

【図 5 b】

【図 6 a】

【図 6 b】

【図 6 c】

【図 7】

【図 8 a】

10

20

30

40

50

【図 8 b】

【図 9 a】

【図 9 b】

【図 9 c】

10

20

30

40

50

【図10】

【 図 1 1 】

【図12a】

【図 1-2-b】

10

20

30

40

50

【図 1 2 c】

【図 1 3 a】

10

20

【図 1 3 b】

【図 1 4】

30

40

50

【図15】

【図16】

10

20

30

40

50

---

**フロントページの続き****(51)国際特許分類**

| F I    |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 5 B |

| H 01 L | 29/78 | 6 5 5 D |

| H 01 L | 29/78 | 6 5 7 D |

**(56)参考文献**

特開2016-225566 (JP, A)

国際公開第2017/155122 (WO, A1)

特開2004-103980 (JP, A)

特開2008-198652 (JP, A)

特開2005-116822 (JP, A)

特開2009-004655 (JP, A)

特開2007-311627 (JP, A)

**(58)調査した分野** (Int.Cl., DB名)

H 01 L 27 / 06

H 01 L 27 / 088

H 01 L 29 / 78

H 01 L 21 / 8234

H 01 L 29 / 739