(19) 日本国特許庁(JP)

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第4077337号 (P4077337)

(45) 発行日 平成20年4月16日 (2008.4.16)

(24) 登録日 平成20年2月8日 (2008.2.8)

(51) Int.Cl. F 1

HO3K

17/16

(2006.01)

HO3K

17/16

L

HO3K

17/687

(2006.01)

HO3K

17/687

F

請求項の数 12 (全 15 頁)

(21) 出願番号 特願2003-51504 (P2003-51504) (22) 出願日 平成15年2月27日 (2003.2.27)

(65) 公開番号 特開2004-260730 (P2004-260730A)

(43) 公開日 平成16年9月16日 (2004. 9. 16) 審査請求日 平成15年5月26日 (2003. 5. 26)

||(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

|(74)代理人 100092820

弁理士 伊丹 勝

[(72) 発明者 印東 忍

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセ

ンター内

審査官 白井 亮

最終頁に続く

(54) 【発明の名称】パルス発生回路及びそれを用いたハイサイドドライバ回路

## (57)【特許請求の範囲】

### 【請求項1】

入力信号の第 1 状態から第 2 状態への変化に基づいてリセットパルスを出力するリセットパルス発生回路と、

前記入力信号の前記第2状態から前記第1状態への変化に基づいてセットパルスを出力するセットパルス発生回路と

を有するパルス発生回路において、

前記リセットパルス発生回路は、

電源線と接地線との間に相補対接続された一対のトランジスタを含む第1のインバータ 回路と、

前記第1のインバータ回路の出力端と前記電源線との間に接続された第1のキャパシタを含み前記入力信号の状態変化を遅延させた遅延出力信号を出力する第1の遅延部とを備え、

前記セットパルス発生回路は、

電源線と接地線との間に相補対接続された一対のトランジスタを含む第2のインバータ 回路と、

前記第2のインバータ回路の出力端と前記接地線との間に接続された第2のキャパシタを含み前記入力信号の状態変化を遅延させた遅延出力信号を出力する第2の遅延部とを備え、

前記第1のインバータ回路は、前記入力信号が前記第1状態のときは前記電源線のレベ

ルの信号を出力し、前記入力信号が前記第2状態のときは前記接地線のレベルの信号を出 力するように構成されている

ことを特徴とするパルス発生回路。

#### 【請求項2】

前記入力信号を反転させる反転回路を備え、

前記リセットパルス発生回路およびセットパルス発生回路の一方に前記入力信号が入力 され、他方に前記反転回路の出力が入力されている

ことを特徴とする請求項1記載のパルス発生回路。

#### 【請求項3】

前記第1及び第2のインバータ回路のそれぞれは、ソースが前記電源線に接続されたP MOSトランジスタと、ソースが接地線に接続されゲートが前記PMOSトランジスタの ゲートに接続されたNMOSトランジスタとからなり、

前記第1及び第2の遅延部は、前記NMOSトランジスタのドレインと前記インバータ 回路の出力端子との間に接続された抵抗を更に具備する

ことを特徴とする請求項1に記載のパルス発生回路。

#### 【請求項4】

前記キャパシタは、MOSキャパシタであることを特徴とする請求項1記載のパルス発 牛回路。

#### 【請求項5】

前記リセットパルス発生回路は、前記入力信号と前記遅延出力信号とを論理演算して前 記リセットパルスを生成出力する論理演算回路を更に備えた請求項1に記載のパルス発生 回路。

### 【請求項6】

前記セットパルス発生回路は、前記入力信号と前記遅延出力信号とを論理演算して前記 セットパルスを生成出力する論理演算回路を更に備えた請求項1に記載のパルス発生回路

#### 【請求項7】

ハイサイドパワートランジスタとローサイドパワートランジスタとがブリッジ接続され たパワーデバイスの前記ハイサイドパワートランジスタを駆動するハイサイドドライバ回 路において、

入力信号の第1状態から第2状態への変化に基づいてリセットパルスを出力するリセッ トパルス発生回路および前記入力信号の前記第2状態から前記第1状態への変化に基づい てセットパルスを出力するセットパルス発生回路を有するパルス発生回路と、

電源復帰時に前記パルス発生回路の入力信号としてパワーオンリセット信号を出力する パワーオンリセット回路と、

前記パルス発生回路から出力されるリセットパルスおよびセットパルスのレベルをシフ トさせるレベルシフト回路と、

前記レベルシフトされたリセットパルスおよびセットパルスでそれぞれ出力状態がリセ ットおよびセットされるラッチ回路と、

このラッチ回路の出力に応じて前記ハイサイドパワートランジスタを駆動するための駆 動信号を出力する出力回路と

前記リセットパルス発生回路は、

電源線と接地線との間に相補対接続された一対のトランジスタを含む第1のインバータ

前記第1のインバータ回路の出力端と前記電源線との間に接続された第1のキャパシタ を含み前記入力信号の状態変化を遅延させた遅延出力信号を出力する第1の遅延部とを備

前記セットパルス発生回路は、

電源線と接地線との間に相補対接続された一対のトランジスタを含む第2のインバータ

20

10

30

40

回路と、

前記第2のインバータ回路の出力端と前記接地線との間に接続された第2のキャパシタを含み前記入力信号の状態変化を遅延させた遅延出力信号を出力する第2の遅延部とを備え、

前記第1のインバータ回路は、前記入力信号が前記第1状態のときは前記電源線のレベルの信号を出力し、前記入力信号が前記第2状態のときは前記接地線のレベルの信号を出力するように構成されており、

前記第2のインバータ回路は、前記入力信号が第2状態のときは前記電源線のレベルの信号を出力し、前記入力信号が第1状態のときは前記接地線のレベルの信号を出力し、前記パワーオンリセット信号が出力された間は前記電源線のレベルの信号を出力するものである

ことを特徴とするハイサイドドライバ回路。

#### 【請求項8】

前記入力信号を反転させる反転回路を備え、

前記リセットパルス発生回路およびセットパルス発生回路の一方に前記入力信号が入力され、他方に前記反転回路の出力が入力されている

ことを特徴とする請求項フ記載のハイサイドドライバ回路。

#### 【請求項9】

前記第1及び第2のインバータ回路のそれぞれは、ソースが前記電源線に接続されたPMOSトランジスタと、ソースが接地線に接続されゲートが前記PMOSトランジスタのゲートに接続されたNMOSトランジスタとからなり、

前記<u>第1及び第2の</u>遅延部は、前記NMOSトランジスタのドレインと前記インバータ 回路の出力端子との間に接続された抵抗を更に具備する

ことを特徴とする請求項7に記載のハイサイドドライバ回路。

#### 【請求項10】

前記キャパシタは、MOSキャパシタであることを特徴とする請求項<u>7</u>記載のハイサイドドライバ回路。

#### 【請求項11】

前記リセットパルス発生回路は、前記入力信号と前記遅延出力信号とを論理演算して前記リセットパルスを生成出力する論理演算回路を更に備えた請求項 7 に記載のハイサイドドライバ回路。

## 【請求項12】

前記セットパルス発生回路は、前記入力信号と前記遅延出力信号とを論理演算して前記セットパルスを生成出力する論理演算回路を更に備えた請求項7に記載のハイサイドドライバ回路。

【発明の詳細な説明】

### [0001]

### 【発明の属する技術分野】

本発明は、リセットパルス、セットパルス等を出力するパルス発生回路に関し、特にパワートランジスタがブリッジ接続されたパワーデバイスのハイサイドパワートランジスタを駆動するハイサイドドライバ回路に適したパルス発生回路およびそれを用いたハイサイドドライバ回路に関する。

## [0002]

#### 【従来の技術】

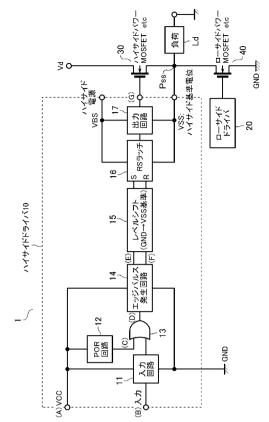

上述したパワーデバイスを用いた半導体回路1の構成例を図7に示す。図7に示す半導体回路1は、ハーフブリッジ接続されたハイサイドMOSトランジスタ30とローサイドMOSトランジスタ40とをそれぞれ駆動するハイサイドドライバ10とローサイドドライバ20とを備えたものである。

ハイサイドパワーMOSトランジスタ30とローサイドパワーMOSトランジスタ40とは、ハイサイドドライバ10とローサイドドライバ20とにより交互に導通状態とされ、

10

20

30

40

負荷Ldに交番電力を供給する。

## [0003]

ハイサイドパワーMOSトランジスタ30とローサイドパワーMOSトランジスタ40とは、高圧電源Vdと接地電位GND(ローサイド基準電位)との間に、中間端子Pssを介してカスケード接続されている。以下では、この中間端子Pssの電位をハイサイド基準電位Vssと称する。ハイサイド基準電位Vssは、ローサイドパワーMOSトランジスタ40のスイッチング状態に応じて振動する。すなわち、ローサイドパワーMOSトランジスタ40が導通(ON)されハイサイドパワーMOSトランジスタ30が非導通(OFF)とされている場合には、ハイサイド基準電位Vssは接地電位GNDに略等しくなり、また、ハイサイドパワーMOSトランジスタ30が導通されローサイドパワーMOSトランジスタ40が非導通とされている場合には、ハイサイド基準電位Vssは電源電圧Vdに略等しくなる。

#### [0004]

そして、ハイサイドドライバ 1 0 は、このハイサイドパワーMOSトランジスタ 3 0 のゲートに出力信号 G (スイッチング信号)を出力してハイサイドパワーMOSトランジスタ 3 0 の導通、非導通を切り替えている。

同様に、ローサイドドライバ20は、このローサイドパワーMOSトランジスタ40のゲートに出力信号を出力してローサイドパワーMOSトランジスタ40の導通、非導通を切り替えている。

## [0005]

次に、ハイサイドドライバ10の構成を説明する。ハイサイドドライバ10は、入力回路 11、パワーオンリセット回路(POR回路)12、論理和回路13、エッジパルス発生 回路14、レベルシフト回路15、RSラッチ回路16、出力回路17を備えている。入 力回路11、エッジパルス発生回路14には、接地電位GNDを基準とした電源電圧Vc cが供給されている。

### [0006]

入力回路11は、所定のタイミングで「H」、「L」の切り替わる入力信号Bを入力させ出力するものである。ここでは、入力回路11に入力される入力信号Bは負論理の信号であり、従って、入力信号が「L」から「H」に立ち上がったときにハイサイドパワーMOSトランジスタ30が非導通とされ、入力信号が「H」から「L」に立ち下がったときにハイサイドパワーMOSトランジスタ30が導通されるものとする。

## [0007]

POR回路12は、電源電圧Vccの立ち上がりを検出してパワーオンリセットパルスCを出力するものである。電源電圧Vccが閾値以上で安定している場合には、POR回路12の出力は「L」のままであり、閾値以下となり、再度復帰した場合に初めてPOR回路12からパワーオンリセットパルスCが出力される。これによりPOR回路12は、電源電圧Vccの状態を監視する機能を果たす。論理和回路13は、入力回路11からの入力信号Bと、POR回路12からの入力信号(パワーオンリセットパルスC)の論理和としての出力信号Dを出力するものである。

#### [00008]

エッジパルス発生回路14は、この論理和回路13から出力される出力信号 D を入力として、この出力信号 D の立ち上がりに応じて、ハイサイドパワーMOSトランジスタ30を非導通にするためのリセットパルス F を出力するとともに、出力信号 D の立ち下がりに応じて、ハイサイドパワーMOSトランジスタ30を導通するためのセットパルス E を出力するものである。レベルシフト回路15は、エッジパルス発生回路14から出力されるリセットパルス F 及びセットパルス E を、接地電位 G N D 基準からハイサイド基準電位 V s s 基準にシフトするためのものである。

#### [0009]

また、 R S ラッチ回路 1 6 は、このレベルシフトされたリセットパルス及びセットパルスをラッチするためのものである。また出力回路 1 7 は、このラッチされたリセットパルス

10

20

30

40

10

20

30

40

50

又はセットパルスに対応して、ハイサイドパワーMOSトランジスタ30のゲートに出力される出力信号(スイッチング信号)Gを「H」と「L」の間で切り替えるものである。この出力信号Gが切り替わることにより、ハイサイドパワーMOSトランジスタ30の導通、非導通が切り替えられる。なお、RSラッチ16と出力回路17とは、ハイサイド基準電位Vssを基準としたハイサイド電源VBSにより駆動される。

なお、ローサイドドライバ20は、レベルシフト回路15の構成等を除き、ほぼハイサイドドライバ10と同様の構成を有している。

### [0010]

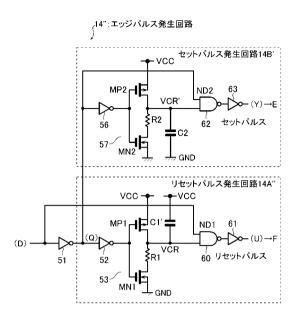

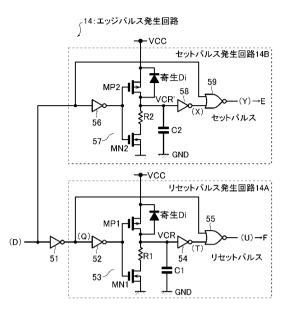

次に、図7のエッジパルス発生回路14の詳細な構成例を図8に示す。図8に示すように、エッジパルス発生回路14は、リセットパルス発生回路14Aと、セットパルス発生回路14Bと、インバータ回路51とから構成される。

リセットパルス発生回路 1 4 A とセットパルス発生回路 1 4 B とは、前者がインバータ回路 5 1 を介して論理和回路 1 3 の出力信号 D を入力させているのに対し、後者はインバータ回路 5 1 を介さずに出力信号 D を入力させている点において異なり、その他の構成は同一である。

#### [0011]

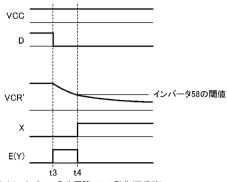

リセットパルス発生回路14Aは、インバータ回路52、53、54と、NOR回路55とから構成される。インバータ回路53は、PMOSトランジスタMP1とNMOSトランジスタMN1からなるCMOSインバータ回路と、抵抗R1とキャパシタC1からなりこのCMOSインバータ回路の出力側に接続されるRC遅延回路とから構成されている。RC遅延回路は、RC時定数により決まる過渡現象曲線に沿って出力信号を徐々に変化させ、インバータ回路54の閾値に達したところでインバータ回路54の出力信号の論理を切り替えることにより入力信号を所定時間遅延させるものである。なお、このような遅延回路を開示するものとして、特許文献1が知られている。

## [0012]

また、NOR回路55は、インバータ回路54の出力信号Tと、インバータ回路51の出力信号Qの論理和の否定値Uを出力するものである。セットパルス発生回路14Bは、インバータ回路56、57、58とNOR回路59とから構成されており、これらはそれぞれ、インバータ回路52、53、54及びNOR回路55と同様の機能を有している。インバータ回路57は、PMOSトランジスタMP2とNMOSトランジスタMN2からなるCMOSインバータ回路と、抵抗R2とキャパシタC2からなりこのCMOSインバータ回路の出力側に接続されるRC遅延回路とから構成されている。なお、図1中、X、Yはそれぞれ、インバータ回路58の出力信号、NOR回路59の出力信号を示している。

#### [0013]

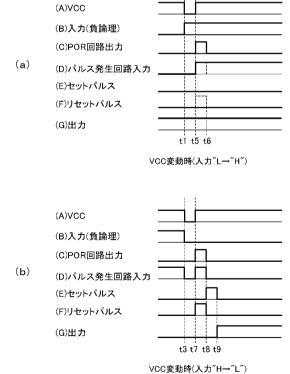

次に、この図7に示す回路の正常時の動作を示すタイミングチャートを図9に示す。図9(a)は、入力信号Bが「L」から「H」に切り替わる場合のタイミングチャートを示しており、図9(b)は、入力信号Bが逆に「H」から「L」に切り替わる場合のタイミングチャートを示している。

### [0014]

図9(a)に示すように、時刻 t 1 にて入力回路 1 1 への入力信号 B が「 L 」から「 H 」に切り替わると、この時点から時刻 t 2 まで、リセットパルス発生回路 1 4 A がリセットパルス F を出力する。このリセットパルス F はレベルシフト回路 1 5 にて高圧側に伝達され R S ラッチ回路 1 6 をリセットし、出力回路 1 7 の出力信号 G を「 H 」から「 L 」にする。

また、図9(b)に示すように、時刻t3にて入力信号Bが「H」から「L」に切り替わると、この時点から時刻t4まで、セットパルス発生回路は14BがセットパルスEを出力する。このセットパルスEはレベルシフト回路15にて高圧側に伝達されRSラッチ回路16をセットし、出力回路17の出力信号Gを「L」から「H」にする。

#### [0015]

## 【特許文献1】

10

20

30

40

50

特開2002-124858号公報(第4~5頁、図1等)

### [0016]

### 【発明が解決しようとする課題】

図7に示す半導体回路1では、セットパルスEとリセットパルスFが入力信号Bの論理が切り替わるごとに交互に出力され、これにより、ハイサイドパワーMOSトランジスタ30の導通、非導通が制御される。

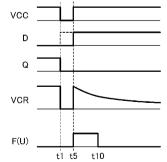

しかし、図10(a)に示すように、電源電圧Vccが変動する場合、例えば、入力信号Bが「L」から「H」に切り替わると同時に外来ノイズ等の影響により電源電圧Vccが0となるような場合がある。このような場合には、時刻t5とt6の間でリセットパルス発生回路14Aから出力されるべきリセットパルスF(図10(a)に点線で示す)が出力されず、この結果出力回路17からの出力信号Gが刻「H」から「L」に切り替わらない、という問題が生ずる。

#### [0017]

一方、図10(a)とは逆に、図10(b)に示すように、入力信号Bが「H」から「L」に切り替わると同時に、外来ノイズ等の影響により電源電圧Vccが、0となるような場合がある。この場合には、時刻t7とt8の間でリセットパルスFが出力され(ただし、これ自体は出力信号Gには影響を与えない)、一方、セットパルスEは、図10(b)に示す場合と同様に時刻t8とt9の間で出力される(ただし、出力タイミングは遅れる)。

このように、出力されるべきリセットパルスFが出力されないこととなると、ハイサイドパワーMOSトランジスタ30が導通から非導通に切り替えることが出来ないこととなり、ローサイドドライバ20の制御状態によっては、ハイサイドパワーMOSトランジスタ30、ローサイドパワーMOSトランジスタ40が同時に導通してしまうこととなり、これにより両トランジスタ30及び40に貫通電流が流れてしまうという問題がある。

#### [0018]

このリセットパルス F が出力されなくなる理由を、図 8 のリセットパルス発生回路 1 4 A 及びセットパルス発生回路 1 4 B の構成を参照しつつ、図 1 1 及び図 1 2 に示すタイミングチャートを用いて説明する。

図 1 1 は、リセットパルス発生回路 1 4 A の動作を示すタイミングチャートであり、(a) は正常動作時(電源電圧 V c c が安定している時)を示し、(b) は電源電圧 V c c が変動した場合を示している。

## [0019]

電源電圧Vccが安定している場合には、図11(a)に示すように、論理和回路13の出力信号Dが時刻t1で立ち上がり、同時にその反転信号であるインバータ回路51の出力信号Qが立ち下がると、インバータ回路53のトランジスタMN1が導通、MP1が非導通とされ、キャパシタC1の電荷が、放電により、RC遅延回路の時定数に沿って徐々に減少する。そして、インバータ回路53の出力信号VCRは、時刻t1以降、RC遅延回路の時定数で決まる過渡現象曲線に沿って「L」に漸近する。時刻t2において出力信号VCRがインバータ回路54の閾値以下となると、インバータ回路54の出力信号Tが「L」から「H」に切り替わる。この出力信号Tと出力信号Qの論理和の否定値である出力信号UがNOR回路55から出力される。この出力信号Uが、リセットパルスFとして出力される。

### [0020]

しかし、図11(b)に示すように電源電圧Vccが変動した場合、例えば、時刻t1において入力信号Bが立ち上がるのと同時に電源電圧Vccが外来ノイズ等の影響で0になった場合(この場合、出力信号Dは立ち上がらない)には、同時にインバータ回路53の出力信号VCRが瞬時に「L」になってしまい、時刻t5に電源電圧Vccが元の値に復帰したとしても、「L」のままとなる。このようなことが生じるのは、以下の理由による。すなわち、電源電圧Vccが0になると、これによりインバータ回路53のトランジスタMP1の寄生ダイオードDiが導通する。そして、この寄生ダイオードDiを通じて、

キャパシタ C 1 に蓄積された電荷が瞬時に放電され、これにより出力信号 V C R が瞬時に「L」になってしまう。このため、時刻 t 5 で電源電圧 V c c が元の大きさに復帰しても、キャパシタ C 1 に電荷が無いので、出力信号 V C R は「L」のままとなる。一方、インバータ回路 5 4 の出力信号 T は、時刻 t 3 の電源電圧 V c c の復帰により「L」から「H」に立ち上がる。このため、N O R 回路 5 5 の出力信号 U は「L」のままとされ、従ってリセットパルス F は発生しない。

#### [0021]

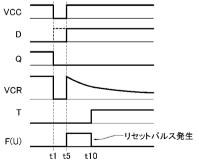

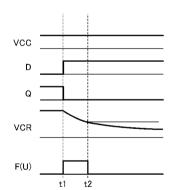

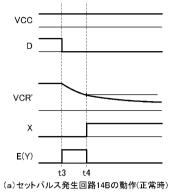

なお、セットパルス発生回路14Bの方では、電源電圧Vccに変動があっても、セットパルスEが発生しないという事態は生じない。図12(a)は、正常時(電源電圧Vccが安定しているとき)のセットパルス発生回路14Bの動作を示すタイミングチャートであり、同図(b)は、電源電圧Vccが変動した場合のセットパルス発生回路14Bの動作を示すタイミングチャートである。セットパルス発生回路14Bでは、電源電圧Vccが変動しても、POR回路12のパワーオンリセットパルスCにより時刻t7、t8の間に出力信号VCR´が充電により回復する。このため、図12(b)に示すように、多少発生タイミングの遅延は生じるものの(t3~t4のところがt8~t9となる)、電源変動がある場合にもセットパルスEは発生する。

### [0022]

このように、図7に示す従来技術に係るエッジパルス発生回路によると、リセットパルス発生回路14Aが、電源電圧Vccの不安定さによりリセットパルスFを発生することができないことが生じ得る一方、セットパルス発生回路14Bに関しては、電源電圧Vccが不安定であってもセットパルスEを発生する。このため、ローサイドドライバ20の制御状態によっては、ハイサイドパワーMOSトランジスタ30、ローサイドパワーMOSトランジスタ40が同時に導通してしまうこととなり、これにより両トランジスタ30及び40が破壊される等、システムの安定性に影響を与えてしまうという問題がある。

## [0023]

本発明は、この問題に鑑みてなされたものであり、電源電圧が変動した場合においても確実にリセットパルスを出力させ、回路の誤動作を防止することが可能なパルス発生回路、およびそれを用いたハイサイドドライバ回路を目的とする。

## [0024]

### 【課題を解決するための手段】

上記目的達成のため、本発明に係るパルス発生回路は、入力信号の第1状態から第2状態への変化に基づいてリセットパルスを出力するリセットパルス発生回路と、前記入力信号の前記第2状態から前記第1状態への変化に基づいてセットパルスを出力するセットパルス発生回路とを有するパルス発生回路において、前記リセットパルス発生回路は、電源線と接地線との間に相補対接続された一対のトランジスタを含む第1のインバータ回路と、前記第1のインバータ回路の出力端と前記電源線との間に接続された第1のキャパシタを含み前記入力信号の状態変化を遅延させた遅延出力信号を出力する第1の遅延部とを備え、前記セットパルス発生回路は、電源線と接地線との間に相補対接続された一対のトランジスタを含む第2のインバータ回路と、前記第2のインバータ回路の出力端と前記接地線との間に接続された第2のキャパシタを含み前記入力信号の状態変化を遅延させた遅延出力信号を出力する第2の遅延部とを備え、前記第1のインバータ回路は、前記入力信号が前記第1状態のときは前記電源線のレベルの信号を出力し、前記入力信号が前記第2状態のときは前記接地線のレベルの信号を出力するように構成されていることを特徴とする

## [0025]

この発明によれば、リセットパルス発生回路の前記<u>第1の</u>キャパシタが前記インバータ回路の出力端と前記電源線との間に接続され、前記<u>第1の</u>インバータ回路は、前記入力信号が前記<u>第1状態のときは前記電源線のレベルの信号を出力</u>し、前記入力信号<u>が前記第2状</u>態のときは前記接地線のレベルの信号を出力するので、電源電圧が0となっても、電源電

10

20

30

40

圧の復帰後インバータ回路の出力端はただちに復帰前の状態に戻すことができ、パルスを発生させることができる。このため、電源電圧の不安定さに起因して、出力されるべきパルスが出力されないという事態を回避することができ、これにより回路の動作を安定なものにすることができる。

## [0026]

また、本発明において、前記入力信号を反転させる反転回路を更に備え、前記リセットパルス発生回路およびセットパルス発生回路の一方に前記入力信号が入力され、他方に前記反転回路の出力が入力されているように構成することが出来る。また、前記<u>第1及び第2のインバータ回路のそれぞれ</u>は、ソースが前記電源線に接続されたPMOSトランジスタと、ソースが接地線に接続され<u>ゲート</u>が前記PMOSトランジスタの<u>ゲート</u>に接続されたNMOSトランジスタとからなり、前記遅延部は、前記NMOSトランジスタ<u>のドレインと前記インバータ回路の出力端子との</u>間に接続された抵抗<u>を更に具備する</u>ように構成することが出来る。また、前記キャパシタは、MOSキャパシタとすることが出来る。

また、<u>前記リセットパルス発生回路及びセットパルス回路は、前記入力信号と前記遅延出力信号とを論理演算して前記リセットパルスを生成出力する論理演算回路を更に備えるよ</u>うにすることができる。

### [0027]

上記目的達成のため、本発明に係るハイサイドドライバ回路は、ハイサイドパワートラン ジスタとローサイドパワートランジスタとがブリッジ接続されたパワーデバイスの前記ハ イサイドパワートランジスタを駆動するハイサイドドライバ回路において、入力信号の第 1 状態から第2 状態への変化に基づいてリセットパルスを出力するリセットパルス発生回 路および前記入力信号の前記第2状態から前記第1状態への変化に基づいてセットパルス を出力するセットパルス発生回路を有するパルス発生回路と、電源復帰時に前記パルス発 生回路の入力信号としてパワーオンリセット信号を出力するパワーオンリセット回路と、 前記パルス発生回路から出力されるリセットパルスおよびセットパルスのレベルをシフト させるレベルシフト回路と、前記レベルシフトされたリセットパルスおよびセットパルス でそれぞれ出力状態がリセットおよびセットされるラッチ回路と、このラッチ回路の出力 に応じて前記ハイサイドパワートランジスタを駆動するための駆動信号を出力する出力回 路とを備え、前記リセットパルス発生回路は、電源線と接地線との間に相補対接続された 一対のトランジスタを含む第1のインバータ回路と、 前記第1のインバータ回路の出力 端と前記電源線との間に接続された第1のキャパシタを含み前記入力信号の状態変化を遅 延させた遅延出力信号を出力する第1の遅延部とを備え、前記セットパルス発生回路は、 電源線と接地線との間に相補対接続された一対のトランジスタを含む第2のインバータ回 路と、 前記第2のインバータ回路の出力端と前記接地線との間に接続された第2のキャ パシタを含み前記入力信号の状態変化を遅延させた遅延出力信号を出力する第2の遅延部 とを備え、前記第1のインバータ回路は、前記入力信号が前記第1状態のときは前記電源 線のレベルの信号を出力し、前記入力信号が前記第2状態のときは前記接地線のレベルの 信号を出力するように構成されており、前記第2のインバータ回路は、前記入力信号が第 2 状態のときは前記電源線のレベルの信号を出力し、前記入力信号が第 1 状態のときは前 記接地線のレベルの信号を出力し、前記パワーオンリセット信号が出力された間は前記電 <u>源線のレベルの信号を出</u>力するものであることを特徴とする。

#### [0028]

### 【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて説明する。

#### [第1の実施の形態]

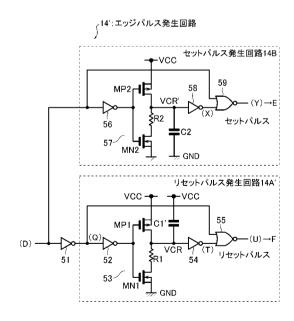

図1は、本発明の第1の実施の形態を示す。本実施の形態に係る半導体回路は、図8に示す従来技術のハイサイドドライバ10中のエッジパルス発生回路14を図1に示すエッジパルス発生回路14~で置き換えたものである。その他の部分は同一であるので、説明を省略する。また、本実施の形態に係るエッジパルス発生回路14~中の構成のうち、従来技術のものと共通するものには同一の符号を付して説明は省略する。

10

20

30

#### [0029]

本実施の形態に係るエッジパルス発生回路 1 4 ´は、リセットパルス発生回路 1 4 A ´において、インバータ回路 5 3 を構成する R C 遅延回路のキャパシタ C 1 ´の一端子が電源電圧 V c c と接続されており、この点、従来技術(図 8 )においてはキャパシタ C 1 の一端子が接地電位 G N D 側に接続されているのと異なる。

## [0030]

一方、セットパルス発生回路14Bは、従来技術のものと同様の構成を備えており、キャパシタC2の接続も従来技術のものと同様、キャパシタC2の一端を接地電位GND側に接続している。このセットパルス発生回路14Bでは、キャパシタC2の一端を電源電圧Vccに接続するよりも、むしろ従来技術と同様に、接地電位GND側に接続するのが好ましい。キャパシタC2の一端を接地電位GND側に接続すると、電源電圧Vccが復帰した時刻において出力信号Dが不定の状態となった場合であっても、コンデンサC2の初期状態(放電状態)により、NOR回路59への入力信号Xが確実に「H」となり、これにより、セットパルスEが誤って出力されることが防止できるためである。キャパシタC2の一端を電源電圧Vcc側に接続しておくと、同様のことが生じた場合、入力信号Xが「L」となることが生じ、誤ってセットパルスEが発生することがあり得る。

### [0031]

次に、この実施の形態に係る半導体回路の作用を説明する。エッジパルス発生回路 1 4 以外の部分の作用は従来技術の場合と同様であるので、以下ではエッジパルス発生回路 1 4 の作用について説明する。

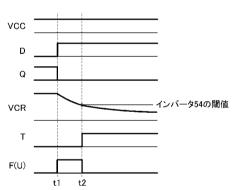

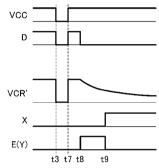

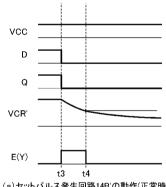

図 2 は、リセットパルス発生回路 1 4 A の動作を示すタイミングチャートであり、( a )は正常動作時(電源電圧 V c c が安定している時)を示し、( b )は電源電圧 V c c が変動した場合を示している。

電源電圧Vccが安定している場合には、図2(a)に示すように、論理和回路13の出力信号Dが時刻t1で立ち上がり、同時にその反転信号であるインバータ回路51の出力信号Qが立ち下がると、インバータ回路53中のトランジスタMP1が非導通とされ、トランジスタMN1が導通する。これにより、コンデンサC1´に電荷が徐々に充電されていき、このため、出力信号VCRは、時刻t1以降、RC遅延回路の時定数で決まる過渡現象曲線に沿って「L」に漸近する。時刻t2において出力信号VCRがインバータ回路54の閾値以下となると、インバータ回路54の出力信号Tが「L」から「H」に切り替わる。この出力信号Tと出力信号Qの論理和の否定値である出力信号Uが、時刻t1とt2の間で立ち上がる。この出力信号Uが、リセットパルスFとして出力される。

#### [0032]

また、図2(b)に示すように、電源電圧Vccが変動した場合、例えば、時刻t1において出力信号Dが「L」から「H」へ立ち上がるのと同時に電源電圧Vccが外来ノイズ等の影響で0になった場合には、次のように動作する。

まず、出力信号 V C R は時刻 t 1 において瞬時に「 L 」に変化する。この時刻 t 1 ではキャパシタ C 1 ´には電荷が無いためである。しかし、時刻 t 5 において電源電圧 V c c が定常値に復帰すると、キャパシタ C 1 ´に電荷が無いことから、出力信号 V C R も瞬時に「 H 」に復帰する。この時刻 t 5 で出力信号 D が「 H 」であることから、出力信号 V C R は、時刻 t 5 以降、抵抗 R 1 とキャパシタ C 1 ´で構成される R C 遅延回路の時定数で決定される過渡現象曲線に沿って「 L 」へ漸近する。

### [0033]

インバータ回路 5 4 の出力信号 T は、出力信号 V C R が閾値以下となった時刻 t 1 0 において「L」から「H」へ立ち上がる。

このため、NOR回路55の出力信号Uは、時刻t5で立ち上がり時刻t10で立ち下がるパルス信号となり、これがリセットパルスFとして出力される。

なお、セットパルス発生回路14Bの構成は図10に示す従来技術のものと同一であるので、その作用も、図3に示すように、従来技術の動作(図12)と同様となる。

このように、この実施の形態によれば、電源電圧Vccが変動した場合であっても、リセ

10

20

30

40

ットパルス発生回路14AよりリセットパルスFを発生させることができ、ハイサイドドライバ10の動作の安定性を確保することができる。

### [0034]

[第2の実施の形態]

図4は、本発明の第2の実施の形態を示す回路図である。この実施の形態のエッジパルス発生回路14''は、リセットパルス発生回路14A''と、セットパルス発生回路14B´とならなる。

リセットパルス発生回路 1 4 A ' 'は、第 1 の実施の形態のリセットパルス発生回路 1 4 A ´ のインバータ回路 5 4 及び N O R 回路 5 5 を、 N A N D 回路 6 0 及びインバータ回路 6 1 で置き換えたものである。

また、セットパルス発生回路14B´は、第1の実施の形態のセットパルス発生回路14Bのインバータ回路58及びNOR回路59を、NAND回路62及びインバータ回路63により置き換えたものである。NAND回路60には、出力信号Dと、インバータ回路53からの出力信号VCRが入力され、NAND回路62には、出力信号Dのインバータ回路51による反転信号Qと、インバータ回路53からの出力信号VCR´が入力される。これにより、出力信号U、Yも、正常動作時、電源電圧Vccが変動するときともに、第1の実施の形態と同様に出力されることができる(図5及び図6参照)。

#### [0035]

以上、発明の実施の形態について説明したが、本発明は、これに限定されるものではなく、本発明の趣旨を逸脱しない範囲において、様々な変更、追加が可能である。例えば、上記実施の形態では、説明の簡単化のため、出力信号 D の変化と同時に電源電圧 V c c が変動する場合について説明したが、本発明は、このような入力信号と同時に生じる電源電圧 V c c の変動に限らず、あらゆる時刻での電源電圧 V c c の変動に対応できるものである。また、上記の実施の形態では、ハーフブリッジ接続のインバータ回路を駆動する例を示しているが、本発明はこれに限らず、ハイサイドスイッチング素子、ローサイドスイッチング素子を有するフルブリッジ回路や、3 相インバータ回路等を駆動する場合にも適用可能である。また、論理回路も、図 1、図 4 に示したものに限られず、様々な形式のものが利用できる。

なお、ハイサイドドライバ10、ローサイドドライバ20を1つのICチップ上に内蔵させることにより、回路全体の部品点数の削減、信頼性の向上を図ることも可能である。また、ハイサイドドライバ10、ローサイドドライバ20に加え、ハイサイドパワーMOSトランジスタ40も1つのICチップ上に内蔵させることにより、一層の部品点数の削減、信頼性の向上を図ることも可能である。

## [0036]

【発明の効果】

以上述べたように、本発明に係る半導体回路によれば、電源電圧が変動した場合において も確実にパルスを出力させ、回路の誤動作を防止するパルス発生回路、およびそれを用い たハイサイドドライバ回路を提供することができる。

## 【図面の簡単な説明】

- 【図1】 本発明の第1の実施の形態に係る半導体回路の構成を示す回路図である。

- 【図2】 図1のリセットパルス発生回路14A'の動作を示すタイミングチャートである。

- 【図3】 図1のセットパルス発生回路14Bの動作を示すタイミングチャートー例である。

- 【図4】 本発明の第2の実施の形態に係る半導体回路の構成を示す回路図である。

- 【図 5 】 図 4 のリセットパルス発生回路 1 4 A ' 'の動作を示すタイミングチャートである。

- 【図 6 】 図 4 のセットパルス発生回路 1 4 B 'の動作を示すタイミングチャートである

【図7】 従来の半導体回路1の構成例を示す。

10

20

30

40

10

- 【図8】 図7のエッジパルス発生回路14の詳細な構成例を示す。

- 【図9】 図7に示す半導体回路1の正常時の動作を示すタイミングチャートである。

- 【図10】 電源電圧 V c c が変動した場合の、半導体回路 1 の動作を示すタイミングチャートである。

- 【図11】 図8に示すリセットパルス発生回路14Aの動作を示すタイミングチャートである。

- 【図12】 図8に示すセットパルス発生回路14Bの動作を示すタイミングチャートである。

### 【符号の説明】

1・・・半導体動回路、 10…ハイサイドドライバ、 11・・・入力回路、 12・・・パワーオンリセット回路(POR回路)、 13・・・論理和回路、 14、14 ~・・・エッジパルス発生回路、 14 A ~・・・リセットパルス発生回路、 14 B・・・セットパルス発生回路、 15・・・レベルシフト回路、 16・・・RSラッチ回路、 17・・・出力回路、 20・・・ローサイドドライバ、 30・・・ハイサイドパワーMOSトランジスタ、 40・・・ローサイドパワーMOSトランジスタ、 51、52、53、54、61、63・・・インバータ回路、 55、59・・・NOR回路、 60、62・・・NAND回路

## 【図1】

## 【図2】

(a)リセットパルス発生回路14A'の動作(正常時)

(b)リセットパルス発生回路14A'の動作(VCC変動時)

## 【図3】

(a)セットパルス発生回路14Bの動作(正常時)

(b)セットパルス発生回路14Bの動作(VCC変動時)

## 【図4】

# 【図5】

(a)リセットパルス発生回路14A"の動作(正常時)

(b)リセットパルス発生回路14A"の動作(VCC変動時)

## 【図6】

(a)セットパルス発生回路14B'の動作(正常時)

(b)セットパルス発生回路14B'の動作(VCC変動時)

【図7】

【図8】

【図9】

(A)VCC

【図10】

# 【図11】

(b)リセットパルス発生回路14Aの動作(VCC変動時)

(b)セットパルス発生回路14Bの動作(VCC変動時)

## フロントページの続き

## (56)参考文献 特開昭 6 2 - 1 2 0 1 1 7 ( J P , A )

特開2001-258268(JP,A)

特開昭55-150026(JP,A)

特開平09-320274(JP,A)

特開平05-110396(JP,A)

特開2000-022510(JP,A)

## (58)調査した分野(Int.CI., DB名)

H03K 17/00-17/70

5/00- 5/02

5/08- 5/12

5/15- 5/26