(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-139967

(P2007-139967A)

(43) 公開日 平成19年6月7日(2007.6.7)

| (51) Int.C1.                | F 1       | テマコード (参考) |

|-----------------------------|-----------|------------|

| <b>G09F 9/30</b> (2006.01)  | G09F 9/30 | 338 3K107  |

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | Z 5C080    |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 621M 5C094 |

| <b>H01L 27/32</b> (2006.01) | G09G 3/20 | 641D       |

| <b>H01L 51/50</b> (2006.01) | G09F 9/30 | 365Z       |

審査請求 未請求 請求項の数 7 O L (全 12 頁) 最終頁に続く

|           |                              |          |                                            |

|-----------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号 | 特願2005-331601 (P2005-331601) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日  | 平成17年11月16日 (2005.11.16)     | (74) 代理人 | 100065385<br>弁理士 山下 橋平                     |

|           |                              | (74) 代理人 | 100122921<br>弁理士 志村 博                      |

|           |                              | (74) 代理人 | 100130029<br>弁理士 永井 道雄                     |

|           |                              | (72) 発明者 | 郷田 達人<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

|           |                              | (72) 発明者 | 川崎 素明<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】電流駆動型装置及び表示装置

## (57) 【要約】

【課題】配線、回路等を効率よく配置することによって額縁サイズの増大を低減する表示装置を提供する。

【解決手段】EL素子、トランジスタおよび電極を含む画素がマトリクス状に配置された表示領域1と、画素を駆動する駆動回路2、3と、映像信号や制御信号を入力したり電力を供給したりする端子部とを有する。また表示領域1の周囲を囲んで配置された共通配線5と、画素の電極と共に共通配線との接続をとるコンタクトホールと、共通配線と端子部の一部を接続する配線引出部と、を有する。配線引出部からの距離が遠い辺(B側)におけるコンタクトホールおよび共通配線は配線引出部からの距離が相対的に近い辺(A側)のコンタクトホールおよび共通配線より幅が小さい。また、配線引出部からの距離が遠い辺の共通配線の付近に駆動回路を配置する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

基板上に、電流駆動型素子と前記電流駆動型素子に流す電流を制御する素子制御回路とを備えた構成要素が複数配置された領域と、前記領域の周囲を囲んで配置された共通配線と、外部と電気的接続するための端子部と、前記共通配線と前記端子部とを接続する配線引出部と、を有する電流駆動型装置において、

前記電流駆動型素子は、前記基板に対して下層の第1電極と上層の第2電極との間に設けられ、前記第1電極は前記素子制御回路に電気的に接続され、

前記第2電極はコンタクトホールを介して前記共通配線に電気的に接続され、

前記配線引出部からの距離が遠い辺における前記共通配線の幅は、前記配線引出部からの距離が相対的に近い辺の前記共通配線の幅より小さいことを特徴とする電流駆動型装置。

10

**【請求項 2】**

前記配線引出部からの距離が遠い辺における前記共通配線に接続される前記コンタクトホールの幅は、前記配線引出部からの距離が相対的に近い辺の前記共通配線に接続される前記コンタクトホールの幅より小さいことを特徴とする請求項1に記載の電流駆動型装置。

。

**【請求項 3】**

前記配線引出部からの距離が遠い辺の前記共通配線の、前記領域から見て外側の第2の領域に、前記素子制御回路を駆動する駆動回路を配置することを特徴とする請求項1又は2に記載の電流駆動型装置。

20

**【請求項 4】**

前記素子制御回路は少なくとも一つのトランジスタを含んでいる請求項1から請求項3のいずれか1項に記載の電流駆動型装置。

**【請求項 5】**

請求項1から4のいずれか1項に記載の電流駆動型装置を用いた表示装置であって、前記電流駆動型素子は発光素子であることを特徴とする表示装置。

**【請求項 6】**

前記発光素子は、エレクトロルミネッセンス素子であることを特徴とする請求項5に記載の表示装置。

30

**【請求項 7】**

請求項5又は6に記載の表示装置と、被写体を撮像する撮像部と、前記撮像部で撮像された信号を処理する映像信号処理部と、を備え、前記映像信号処理部で信号処理された映像信号を前記表示装置で表示してなるカメラ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、基板上に、電流駆動型素子と前記電流駆動型素子に流す電流を制御する素子制御回路とを備えた構成要素が複数個配置された領域を有する電流駆動型装置、表示装置およびカメラに係わる。そして本発明は、電流を注入して発光するエレクトロルミネッセンス素子(以後EL素子と言う)を用いた表示装置に好適に用いられるものである。

40

**【背景技術】****【0002】**

周辺回路又は信号処理回路を内蔵したアクティブマトリクス型EL表示装置においては、表示領域だけでなく周辺回路又は信号処理回路においてもアナログスイッチやインバータ等のトランジスタとして薄膜トランジスタ(TFT)が使用されている。

**【0003】**

周辺回路又は信号処理回路内のTFTは、通常ポリシリコンTFTが用いられている。ポリシリコンTFTは低温結晶化技術により製造され、高性能・低価格の周辺駆動回路TFTの製造に用いられるものである。現在実用化されている代表的な結晶化技術はエキシマレ

50

ーザを用いた低温結晶化法であり、エキシマレーザを用いることにより良質なシリコン結晶薄膜を低融点ガラス上に形成することが可能になる（特許文献1参照）。

また、表示パネルの製造コストを下げるため、対角寸法1m以上の大型ガラス基板上に多面取り方式が採用される。しかし、基板が大きいためにガラス基板自身のシュリンクエージが大きく、パターン形成のための位置合わせ精度が1μm程度と高くはない。また、現状大型パターン加工装置（エッティング装置等）は2μm以下の加工精度で各メタル層パターンを形成することが困難である。このため、比較的緩いデザインルールで周辺回路又は信号処理回路を形成することが求められる。

#### 【0004】

一方、有機EL表示パネルにおけるEL素子に水分が進入してしまうと、その画素が滅点欠陥となる。それだけでなく、画素に進入した水分が隣接する画素に次々と影響して非発光領域となるダーカススポットが増え、最終的に1つのパネルすべてが表示できなくなるため、EL素子と外気および水分の遮断が求められる。

#### 【0005】

そのため、水分防止や物理的保護の観点から、内面に乾燥剤を塗布した封止基板を有機EL素子の配置された表示領域を覆い被せるように固着している。この固着にはシール剤と呼ばれるエポキシやアクリル系の接着剤を用いており、表示領域の外周を囲う接着領域に塗布して封止基板を貼り付ける（特許文献2参照）。

#### 【0006】

このような構造において封止能力を高め、水分透過量を減らす方法として、シール幅を太くすることでEL素子への外気の進入を防ぐ構造も採用される。しかし、この場合には基板エッジからシール剤外周までは、信頼性の観点から一定のマージンを確保する必要がある。また、表示領域はシール剤の内側に配置されるので、パネル外形を同一のまま、封止能力を高めるためにシール剤の幅を太くすると、当然ながら広額縁になり、表示領域の面積が低減してしまう。

#### 【0007】

また、有機ELパネルは、有機EL素子の陰極側に接続される共通の矩形形状の透明な共通電極の角にコンタクトホールを設けて共通配線と接続し、共通配線を外部端子につなげることの記載が特許文献3にある。

【特許文献1】特開平09-082641号公報

【特許文献2】特開平01-313892号公報

【特許文献3】特開2001-109395号公報（米国特許第6690110号明細書）

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

近年、表示パネルには軽量化とコンパクト化の要求により、ますます狭額縁化が求められている。その額縁のサイズとしては、ガラス基板の縁から数mm程度の範囲であり、数百μmの縮小であってもその効果は大きい。

この狭額縁化には、周辺回路又は信号処理回路の微細化、封止基板を固着させる接着領域の縮小が必要となってくる。しかし、周辺回路又は信号処理回路の微細化は、位置合わせ精度、加工精度等の製造上の問題から困難である。また、封止基板の接着領域を細くすると、封止能力が低下し、欠陥画素の増加による表示状態の悪化を招く可能性がある。

#### 【0009】

そこで、本発明の目的は、配線、回路等を効率よく配置することによって額縁サイズの増大を低減する表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0010】

本発明の電流駆動型装置は、基板上に、電流駆動型素子と前記電流駆動型素子に流す電流を制御する素子制御回路とを備えた構成要素が複数配置された領域と、前記領域の周囲を囲んで配置された共通配線と、外部と電気的接続するための端子部と、前記共通配線と

10

20

30

40

50

前記端子部とを接続する配線引出部と、を有する電流駆動型装置において、

前記電流駆動型素子は、前記基板に対して下層の第1電極と上層の第2電極との間に設けられ、前記第1電極は前記素子制御回路に電気的に接続され、

前記第2電極はコンタクトホールを介して前記共通配線に電気的に接続され、

前記配線引出部からの距離が遠い辺における前記共通配線の幅は、前記配線引出部からの距離が相対的に近い辺の前記共通配線の幅より小さいことを特徴とする。

#### 【発明の効果】

#### 【0011】

本発明によれば、電流駆動型素子と素子制御回路とを備えた構成要素が複数個配置された領域の周囲を囲んで配置された共通配線における電流量の少ない領域の幅を小さくし、レイアウト面積を縮小できる。したがって基板の額縁サイズを小さくすることが可能となる。また、電流経路を考慮した配線によって、素子制御回路を駆動する駆動回路を配置した側の共通配線幅を小さくし、回路面積による額縁サイズの拡大を抑制することが可能となる。こうして装置の軽量化とコンパクト化に向けて、額縁サイズの増大を低減する装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0012】

本発明の電流駆動型装置において、電流駆動型素子は下層の第1電極と上層の第2電極との間に設けられる機能素子であればよく、発光素子、発熱素子（抵抗素子）等が挙げられる。特に電流駆動型素子として、有機EL素子に代表されるEL素子（電流駆動型発光素子となる）が好適に用いられる。

#### 【0013】

電流駆動型発光素子とスイッチ素子とを組み合わせた構成要素を一次元状又は二次元状に配して表示装置を構成することができる。

#### 【0014】

表示装置としては、画像情報を表示する線状表示装置、アクティブマトリクス型表示装置等がある。画像情報を示す線状表示装置はスキャナとして感光体と組み合わせて光プリンタ、複写機等の画像記録装置を構成することができる。アクティブマトリクス型表示装置は平面型テレビ、デジタルカメラ、デジタルビデオカメラ等に用いられるビューア、携帯電話機の表示部等に用いることができる。

#### 【0015】

素子制御回路は上記電流駆動型素子に流す電流を制御する回路であり、最も簡単な構成は1つのトランジスタである。後述する実施形態においては、素子制御回路は電流駆動型素子に電流を流すトランジスタの制御電極（ゲート等）に予め流す電流値をプログラミングする回路構成となっている。そして、電流駆動型素子に電流を流すトランジスタと、その制御電極（ゲート等）に電流を書き込むためのトランジスタとを含んでいる。

#### 【0016】

電流駆動型素子に流れる電流は、コンタクトホールを通って共通配線に流れ、配線引出部から端子部へ向かう。また、電流駆動型素子に流れる電流は共通配線からコンタクトホールを通って電流駆動型素子に流入する場合もある。

#### 【0017】

電流駆動型素子と素子制御回路とを備えた構成要素が複数配置された領域に対して配線引出部とは反対の辺にある共通配線では流れる電流量が配線引出部のある側の辺の共通配線と比べて少ない。そのため、共通配線幅（又は共通配線幅とコンタクトホール幅）を小さくしてレイアウト面積を削減できる。このレイアウト面積を削減した辺にデータ線駆動回路、走査線駆動回路等の駆動回路を配置する。レイアウト面積の大きいデータ線駆動回路を配置する方がより好ましい。

#### 【0018】

本発明を実施するための最良の形態は、有機EL素子に代表されるEL素子を用いたアクティブマトリクス型表示装置に適用される。以下、本発明に係わるアクティブマトリク

10

20

30

40

50

ス型表示装置の実施形態について図面を用いて説明する。

【0019】

(実施形態1)

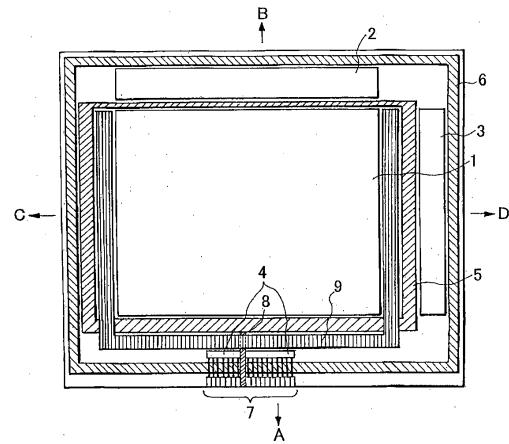

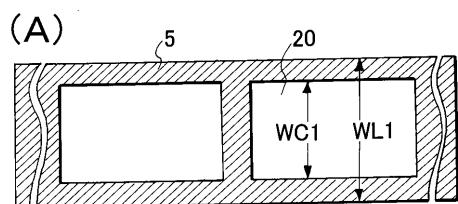

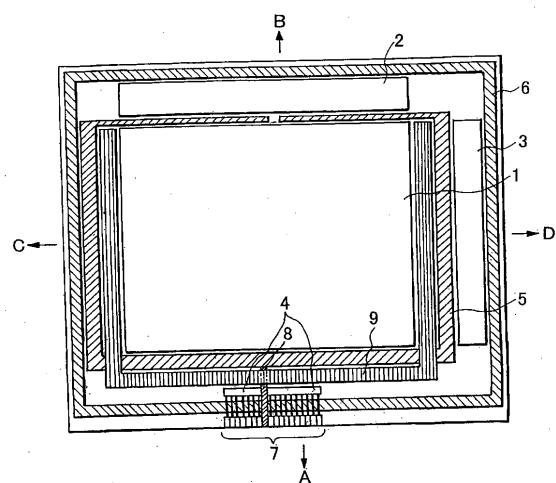

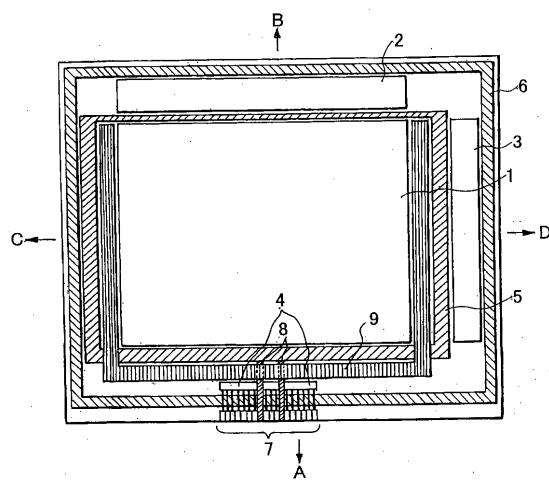

図1は本発明による表示装置の第1実施形態の概略レイアウト図を示している。

【0020】

図1に示す表示装置は、有機EL素子等のEL素子と、薄膜トランジスタ(TFT)を含む画素回路(素子制御回路となる)とからなる画素(構成要素となる)が、マトリクス状に配置された表示領域1を有する。そして、画素列ごとに接続されるデータ線にデータ信号を出力するデータ線駆動回路2と、画素行ごとに走査線に走査信号を出力する走査線駆動回路3を有する。また、映像信号や制御信号を入力したり電力を供給したりする端子部7と、入力された制御信号を表示パネル内の動作電圧レベルに変化する入力回路4とを有する。さらに、封止基板を固着させる接着領域6と、各画素のEL素子と接続された共通配線5と、を有する。

10

【0021】

共通配線5は表示領域1の周辺を囲んで配置されており、配線引出部8から配線を引いて端子部4の一部と接続される。入力回路4からの出力信号はデータ線駆動回路2や走査線駆動回路3へ伝送されるが、その配線は図1において省略している。電力供給線9は各画素回路に電力(電圧又は電流)を供給するものである。電力供給線9と各画素回路とは、まず画素行の各画素回路のトランジスタM1(図2に図示)のソースが画素行ごとに設けられた電力線に接続される。そして、この電力線が図1の領域1と共通配線5との間に設けられた電力供給線9に接続されることで電力供給線9と各画素回路と接続される。ここでは、電力線と電力供給線9とは、はしご状に接続され、電力供給線9は「コ」の字状になっている。

20

【0022】

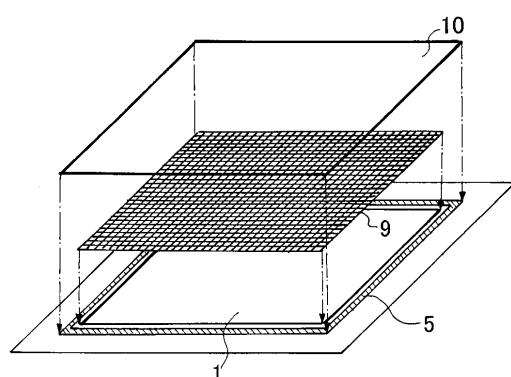

図2にEL素子を含んだ電流設定方式の画素回路を示す。走査線104、105に走査信号P1及びP2が入力され、データ線102に電流データIdataが入力される。EL素子の陽極(A)はトランジスタM4のドレインに接続されており、陰極(K)は接地電位GNDに接続されている。

20

電流データIdataはデータ信号線102を介してトランジスタM3のソースに入力され、トランジスタM3のゲートとトランジスタM4のゲートは走査線104に接続される。トランジスタM4のソースはトランジスタM3のドレインとトランジスタM2のドレイン、トランジスタM1のドレインと接続される。トランジスタM1のゲートは一端が電力供給線(電圧VCC)に接続された容量C1の他端と、トランジスタM2のソースと接続され、トランジスタM2のゲートは走査線105、トランジスタM1のソースは電力供給線(電圧VCC)に接続されている。電流をEL素子に供給するトランジスタはトランジスタM1、M4であり、EL素子は共通電位線によりGNDに接続されている。トランジスタM1のゲートにEL素子に流す電流の電流値を書き込むトランジスタはトランジスタM2、M3である。トランジスタM1のゲートに電流値を書き込む電圧プログラミング期間にスイッチ素子となるトランジスタM2、M3をオン、スイッチ素子となるトランジスタM4をオフする。それに続くEL素子に電流を供給する発光期間にスイッチ素子となるトランジスタM2、M3をオフ、スイッチ素子となるトランジスタM4をオンする。

30

【0023】

本実施形態においては画素回路としては図2の構成を一例に挙げたが、これに限るものではなく、その他の電流設定方式の画素回路や電圧設定方式の画素回路にも適用できる。

40

【0024】

本実施形態では、EL光の取出し面を陰極側とし、ITO(酸化インジウム+酸化スズ)やIZO(酸化インジウム+酸化亜鉛)などの透明導電材で形成する。また、その陰極を図1の共通配線5と接続しており、EL素子の発光時の駆動電流は共通配線5へ流れ行く。

【0025】

50

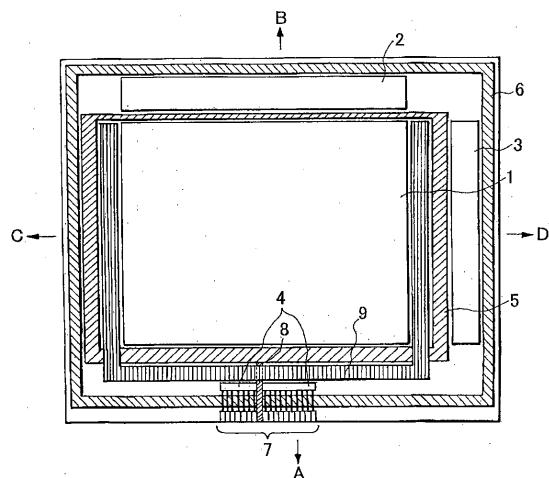

次に、共通配線 5 と各画素の E L 素子との接続について詳細に説明する。図 2 では E L 素子、接地電位 C G N D は画素回路内部に含めて記述してあるが、図 3 を用いてその立体的な配置を含めて説明する。簡単のため、データ線駆動回路 2、走査線駆動回路 3、入力回路 4、接着領域 6、端子部 7、配線引出部 8 は省略する。

## 【0026】

表示領域 1 には画素回路、例えば図 2 のトランジスタ M 1 ~ M 4 と容量 C 1 が形成されており、トランジスタ (TFT) M 4 と接続した E L 素子の陽極 (A) が形成されている。その陽極上に画素配列に合わせて E L 素子 9 を蒸着し、陽極と E L 素子 9 を接合する。それから E L 素子 9 上に透明導電材による陰極 10 を成膜している。陰極 10 は表示領域 1 の周辺に配置された共通電極 5 の上にも形成される。その際、共通電極 5 上の絶縁層 (不図示) はコンタクトホール (不図示) を形成して共通電極 5 の表面を剥き出し状態にする。こうして E L 素子の陰極 10 と共通電極 5 はコンタクトホールを介して電気的な接続が取られて接地されることになる。

## 【0027】

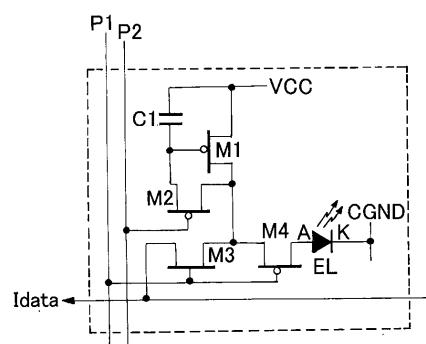

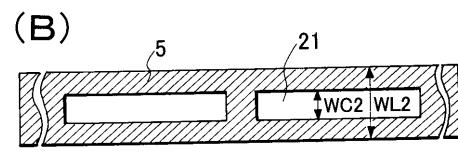

図 4 を用いて共通配線 5 と陰極 10 との接続部について説明する。図 4 (A) は図 1 における A 側の共通配線 5 の部分拡大図を示している。共通配線 5 の上にコンタクトホール 20 が形成されており、その上に陰極 10 が形成されている。共通配線幅 W L 1 はコンタクトホール幅 W C 1 よりもプロセスマージン分だけ大きくなっている。図 4 (B) は図 1 における B 側の共通配線 5 の部分拡大図を示している。B 側の共通配線 5 は、図 1 の概略レイアウト図によれば、表示領域 1 を挟んで配線引出部 8 と反対側に位置する。図 4 (A) と同様の構成であるが、コンタクトホール幅 W C 2 と共通配線幅 W L 2 が異なっている。つまり、コンタクトホール幅 W C 1、W C 2 と共通配線幅 W L 1、W L 2 の関係は、W C 1 > W C 2、W L 1 > W L 2 というように A 側に対して B 側のコンタクトホール幅と共通配線幅が小さくなっている。なお、コンタクトホールは透明電極の四辺に沿って四角状に開口されていてもよい。

## 【0028】

ここで B 側のコンタクトホール幅と共通配線幅を小さくできる理由について説明する。E L 素子を流れた電流は表示領域 1 上に形成された陰極 10、次に共通配線 5、そして配線引出部 8 を通って端子部 7 へ流れて行く。陰極 10 を流れる電流は配線引出部 8 に向かって流れ、また B 側の共通配線は表示領域 1 から見て配線引出部 8 と反対側の辺に位置することを考慮すると、A, C, D 側へ流れる電流量よりも、B 側へ流れる電流量は少なくなる。すなわち、B 側の陰極 10 と共通配線 5 のコンタクト部の電流量は少ないため、そのコンタクトホール幅を小さくすることが可能となる。それに伴って共通配線幅も小さくできるのである。

## 【0029】

なお、図 4 において、共通配線幅及びコンタクトホール幅は、共に図 1 の A 側よりも B 側が小さくなっているが、共通配線幅のみ小さくてもよい。一般的には共通配線幅を小さくすればコンタクトホール幅も小さくなる。したがって、図 1 の B 側の共通配線幅を A 側の共通配線幅より小さくすれば、図 1 の B 側のコンタクトホール幅も A 側のコンタクト幅より小さくなる。しかし、例えば、コンタクトホール部分の抵抗値の増大が問題とならない場合や共通配線幅の差が小さい場合には、図 1 の A 側のコンタクトホール幅を B 側のコンタクトホール幅と同じにしておくこともできる。また、B 側は共通配線のみを設けて、コンタクトホールを設けなくとも良い。

## 【0030】

さらに図 1 のレイアウトの場合、B 側にはデータ線駆動回路 2 が配置されている。データ線駆動回路 2 を配置することで額縁領域の面積の拡大につながるが、B 側の共通配線幅を小さくできるので額縁サイズの拡大を抑制することにもなる。

## 【0031】

(実施形態 2)

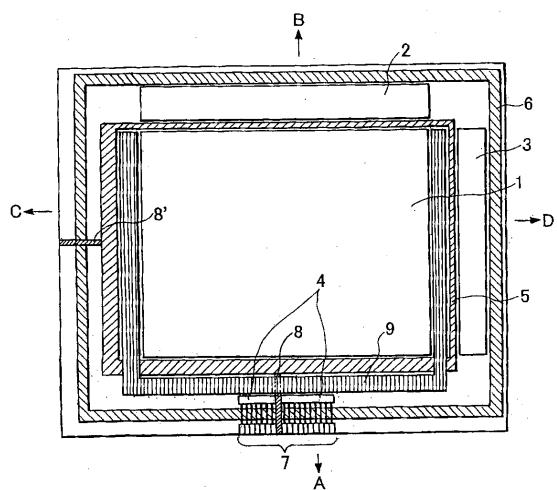

また、図 5 に本発明による表示装置の第 2 実施形態の概略レイアウト図を示す。

10

20

30

40

50

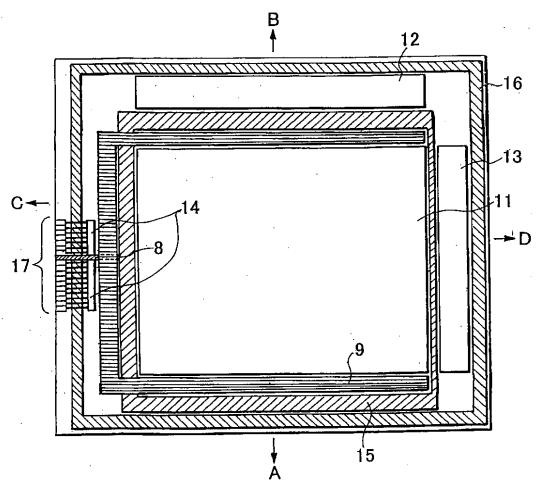

## 【0032】

図5に示す表示装置は、有機EL素子等のEL素子と、薄膜トランジスタ(TFT)を含む画素回路(素子制御回路となる)とからなる画素(構成要素となる)が、マトリクス状に配置された表示領域11を有する。画素の構成は図2に示した構成と同じである(後述する各実施形態の画素も同様に図2に示した構成と同じである)。そして、画素列ごとに接続されるデータ線にデータ信号を出力するデータ線駆動回路12と、画素行ごとに走査線に走査信号を出力する走査線駆動回路13を有する。また、映像信号や制御信号を入力したり電力を供給したりする端子部17と、入力された制御信号を表示パネル内の動作電圧レベルに変化する入力回路14とを有する。さらに、封止基板を固着させる接着領域16と、各画素のEL素子と接続された共通配線15と、を有する。

10

## 【0033】

共通配線15は表示領域11の周辺を囲んで配置されており、配線引出部18から配線を引いて端子部14の一部と接続される。入力回路14からの出力信号はデータ線駆動回路12や走査線駆動回路13へ伝送されるが、その配線は図5において省略している。

## 【0034】

図5の構成が図1と異なる点は、端子部17および配線引出部18が図5のC側に配置されているところである。この場合、表示領域11を挟んでC側と反対側の辺に位置するD側の共通配線15の電流量は少なくなる。そのためD側の共通配線15の電流供給量は少なくて良いため、その幅を小さくすることが可能となる。

## 【0035】

さらに図5のレイアウトの場合、D側には走査線駆動回路13が配置されている。走査線駆動回路13を配置することで額縁領域の面積の拡大につながるが、D側の共通配線幅を小さくできるので額縁サイズの拡大を抑制することにもなる。

20

## 【0036】

## (実施形態3)

また、図6に本発明による表示装置の第3実施形態の概略レイアウト図を示す。本実施形態の図1に示す第1実施形態との違いは、表示領域1を挟んで配線引出部8と反対側の辺に位置する、B側の共通配線5が切断されていてつながっていない点である。このように、B側の共通配線5の一部が切断されてつながれなくても、A,C,D側へ流れる電流量よりも、B側へ流れる電流量は少ないためその影響は少ない。

30

## 【0037】

## (実施形態4)

また、図7に本発明による表示装置の第4実施形態の概略レイアウト図を示す。本実施形態の図1に示す第1実施形態との違いは、図7のA側の共通配線5と接続する配線引出部8が2つ(3以上でもよい)設けられている点である。このように、配線引出部8を2つ(3以上でもよい)設けることで、配線引出部に流れる電流密度を低減できる。

40

## 【0038】

## (実施形態5)

また、図8に本発明による表示装置の第5実施形態の概略レイアウト図を示す。本実施形態の図1に示す第1実施形態との違いは、配線引出部8,8'が図8のA側、C側に設けられ、共通配線幅及びコンタクトホール幅は、図8のA側、C側よりもB側、D側が小さくなっている点である。

## 【0039】

本実施形態においても、第4実施形態と同様に配線引出部を2つ(3以上でもよい)設けることで、配線引出部に流れる電流密度を低減できる。また、共通配線幅及びコンタクトホール幅を、図8のA側、C側よりもB側、D側が小さくなるようにすることで、図8のB方向及びD方向の額縁サイズの拡大を抑制することができる。

## 【0040】

以上説明した各実施形態1～5において、表示装置の構成は、図1、図5～図8の概略レイアウト図に示した例に限るものではない。表示領域を挟んで配線引出部と反対側の辺

50

に共通配線幅（又は共通配線幅とコンタクトホール幅）を小さくする形態であれば良い。さらには共通配線の引き回し、配線引出部、端子部の位置に依って電流量が少なくなる共通配線の幅を小さくする形態であれば良い。

#### 【0041】

また各実施形態において、電流の制御を行う画素回路を構成するトランジスタを介してEL素子に電流を流し、共通電位線を介して電流を流出するものとした。しかし、共通電位線からEL素子に電流を流し、その電流を制御を行う画素回路を構成するトランジスタを介して電力供給線に電流を流してもよい。例えば、図2の画素回路において、トランジスタM1はここではPMOSトランジスタを用いている。しかし、NMOSトランジスタを用い、EL素子の陰極側をトランジスタM4に接続し、陽極側を電位VCCとされた共通電位線に接続し、トランジスタM1を接地された電力供給線に接続してもよい。

10

#### 【0042】

また、本発明の表示装置ではEL素子を用いた例を挙げたが、これに限るものではない。

#### 【0043】

また、上記の各実施形態の表示装置は、トップエミッション型の有機EL表示装置であるが、画素回路が形成された透明基板側から光を取り出すボトムエミッション型の有機EL表示装置でも適用可能である。この場合、基板に対して下層の第1電極となる画素電極は透明電極が用いられる。上層の第2電極は透明電極であってもよいが、反射光を用いる場合にはアルミ等の金属の電極が用いられる。

20

#### 【0044】

##### （実施形態6）

上述した各実施形態の表示装置は情報表示装置を構成できる。この情報表示装置は携帯電話、携帯コンピュータ、スチルカメラもしくはビデオカメラ等、もしくはそれらの各機能の複数を実現する装置である。情報表示装置は情報入力部を備えている。例えば、携帯電話の場合には情報入力部はアンテナを含んで構成される。PDAや携帯パソコンの場合には情報入力部はネットワークに対するインターフェース部を含んで構成される。スチルカメラやムービーカメラの場合には情報入力部はCCDやCMOSなどによるセンサ部を含んで構成される。

#### 【0045】

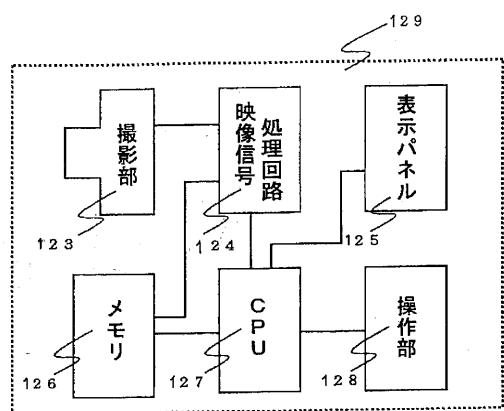

以下本発明の好適な実施形態として、上述した実施形態1～5のいずれかの表示装置を用いたデジタルカメラについて説明する。

30

図9はデジタルスチルカメラの一例のブロック図である。図中、129はシステム全体、123は被写体を撮像する撮影部、124は映像信号処理回路、125は表示パネル、126はメモリ、127はCPU、128は操作部を示す。撮像部123で撮影した映像または、メモリ126に記録された映像を、映像信号処理回路124で信号処理し、表示パネル125で見ることができる。CPU127では、操作部128からの入力によって、撮影部123、メモリ126、映像信号処理回路124などを制御して、状況に適した撮影、記録、再生、表示を行う。

#### 【産業上の利用可能性】

#### 【0046】

本発明の電流駆動型装置は電流駆動型素子としては例えば有機EL素子に代表されるEL素子（電流駆動型発光素子となる）を用いることができ、これらを用いて表示装置を構成することができる。

40

#### 【図面の簡単な説明】

#### 【0047】

【図1】本発明による表示装置の第1実施形態の概略レイアウト図である。

【図2】EL素子を含んだ電流設定方式の画素回路の例を示す図である。

【図3】EL素子と陰極の立体的な配置を説明する図である。

【図4】共通配線の部分拡大図である。

【図5】本発明による表示装置の第2実施形態の概略レイアウト図である。

50

【図6】本発明による表示装置の第3実施形態の概略レイアウト図である。

【図7】本発明による表示装置の第4実施形態の概略レイアウト図である。

【図8】本発明による表示装置の第5実施形態の概略レイアウト図である。

【図9】デジタルスチルカメラの一例のブロック図である。

【符号の説明】

【0048】

- 1, 11 表示領域

- 2, 12 データ線駆動回路

- 3, 13 走査線駆動回路

- 4, 14 入力回路

- 5, 15 共通配線

- 6, 16 接着領域

- 7, 17 端子部

- 8, 18 配線引出部

- 9 EL素子

- 10 陰極

- 20 コンタクトホール

- 21 走査信号

- 22 データ信号

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 05 B 33/14 A

G 09 G 3/20 680V

(72)発明者 井関 正己

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 3K107 AA01 BB01 CC43 DD38 DD39 EE04 HH00 HH05

5C080 AA06 BB05 DD22 FF11 JJ02 JJ03 JJ06

5C094 AA15 BA03 BA27 DB04 DB10 EA05 EA07