(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2023-44647

(P2023-44647A)

(43)公開日 令和5年3月30日(2023.3.30)

(51)国際特許分類

H 0 1 L 27/146 (2006.01)F I

H 0 1 L 27/146

H 0 1 L 27/146テーマコード(参考)

4 M 1 1 8

D

審査請求 未請求 請求項の数 10 O L (全28頁)

(21)出願番号 特願2022-137001(P2022-137001)

(22)出願日 令和4年8月30日(2022.8.30)

(31)優先権主張番号 10-2021-0125031

(32)優先日 令和3年9月17日(2021.9.17)

(33)優先権主張国・地域又は機関

韓国(KR)

(71)出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

100107766

弁理士 伊東 忠重

100070150

弁理士 伊東 忠彦

100135079

最終頁に続く

(54)【発明の名称】 イメージセンサー

(57)【要約】 (修正有)

【課題】ゲート電極のサイズを増加と同時にピクセル間のクロストークを最小化するイメージセンサーを提供する。

【解決手段】イメージセンサー500は、第1面1aとそれに反対になる第2面1bを有し、第1ピクセル及び隣接する第2ピクセルを含む基板1、基板内に配置され、第1ピクセル及び第2ピクセルを分離する深い素子分離部DTI、第1面上に配置される伝送ゲート、第1ピクセル及び第2ピクセルの中で何れか1つに選択的に配置される接地領域、第2面上に順に積層される第1カラーフィルターCF1及びマイクロレンズアレイ層MLを含む。深い素子分離部は、垂直に重畳され、互いに離隔する第1分離部20及び第2分離部30を含む。第1分離部は、第1面から第2面に延長される導電パターン24、導電パターン上の高濃度ドーピングパターン26及び導電パターンと高濃度ドーピングパターンとの間のライナーアルゴンパターン25を含む。

【選択図】図5A

**【特許請求の範囲】****【請求項 1】**

第1面とそれに反対になる第2面を有する基板であって、第1ピクセル、及び前記第1ピクセルと隣接する第2ピクセルを含む基板と、

前記基板内に配置され、前記第1ピクセル及び前記第2ピクセルを分離する深い素子分離部と、

前記第1ピクセル及び前記第2ピクセルで各々前記第1面上に配置される伝送ゲートと、

前記第1ピクセル及び前記第2ピクセルの中でいずれか1つに選択的に配置される接地領域と、

10

前記第2面上に順に積層される第1カラーフィルターとマイクロレンズアレイ層と、を含み、

前記深い素子分離部は、

垂直に重畠され、互いに離隔する第1分離部及び第2分離部を含み、

前記第1分離部は、前記第1面から前記第2面に延長される第1導電パターンと、

前記第1導電パターン上の前記基板内に提供される高濃度ドーピングパターンと、

前記第1導電パターンと前記高濃度ドーピングパターンとの間の絶縁パターンと、を含み、

20

前記接地領域及び前記高濃度ドーピングパターンは、互いに同一な導電型を有する不純物でドーピングされる、イメージセンサー。

**【請求項 2】**

前記第1ピクセル及び第2ピクセルは、同一な色のカラーフィルターを共有する、請求項1に記載のイメージセンサー。

**【請求項 3】**

前記第1ピクセルには接地領域が提供され、

前記第2ピクセルには接地領域が提供されない、請求項1又は2に記載のイメージセンサー。

20

**【請求項 4】**

前記基板内に提供される第3ピクセルであって、前記第2ピクセルを介して前記第1ピクセルと第1方向に沿って互いに離隔する第3ピクセルと、

30

前記第3ピクセル上の第2カラーフィルターと、をさらに含み、

前記深い素子分離部は、

前記基板内に配置され、前記第2ピクセル及び前記第3ピクセルを分離し、垂直に重畠する第3分離部及び第4分離部をさらに含み、

前記第1カラーフィルター及び前記第2カラーフィルターは、互いに異なる色を含む、請求項1に記載のイメージセンサー。

**【請求項 5】**

前記第3分離部及び前記第4分離部は、互いに離隔する、請求項4に記載のイメージセンサー。

40

**【請求項 6】**

前記第3分離部及び前記第4分離部は、互いに接触する、請求項4に記載のイメージセンサー。

**【請求項 7】**

第1面とそれに反対になる第2面を有する基板を含むイメージセンサーであって、

前記基板は、前記基板の第1面に平行である第1方向及び前記第1面と平行であり、前記第1方向と交差する第2方向に沿って2次元的に配列される第1ピクセルグループ、第2ピクセルグループ、及び一対の第3ピクセルグループを含み、

前記第1ピクセルグループの上には第1カラーフィルターが配置され、

前記第2ピクセルグループの上には第2カラーフィルターが配置され、

前記一対の第3ピクセルグループの上には第3カラーフィルターが各々配置され、

50

前記第1乃至第3ピクセルグループの各々は、第1方向及び第2方向に沿って $N \times N$ 配列をなす $N^2$ 個のピクセルを含み、

前記 $N^2$ 個のピクセルの間で及び前記第1乃至第3ピクセルグループの間で前記基板内には深い素子分離部が提供され、

前記深い素子分離部は、前記第1面から前記第2面に向かって延長される第1分離部及び前記第2面から前記第1面に向かって延長される第2分離部を含み、

前記第1分離部は、前記 $N^2$ 個のピクセルの間に提供される第1分離パターン及び前記第1乃至第3ピクセルグループの間に提供される第2分離パターンを含み、

前記第2分離部は、前記 $N^2$ 個のピクセルの間に提供される第3分離パターン及び前記第1乃至第3ピクセルグループの間に提供される第4分離パターンを含み、

前記第1分離パターン及び前記第3分離パターンは、垂直方向に整列され(a1ingn

ed)、互いに離隔し、

前記第2分離パターン及び前記第4分離パターンは、垂直方向に整列され、

第1乃至第4ピクセルの中でいずれか1つは、選択的に接地領域を含み、

前記第1分離部は、前記第1面から前記第2面に延長される第1導電パターンと、

前記第1導電パターン上の高濃度ドーピングパターンと、

前記第1導電パターンと前記高濃度ドーピングパターンとの間の絶縁パターンと、を含み、

前記Nは2以上の自然数である、イメージセンサー。

#### 【請求項8】

前記第1分離パターンは、前記第1方向に沿う第1幅を有し、

前記第3分離パターンは、前記第1方向に沿う第2幅を有し、

前記第1幅は、前記第2幅より小さい、請求項7に記載のイメージセンサー。

#### 【請求項9】

前記第1分離パターンの長さは、前記第2分離パターンの長さより小さい、請求項7又は8に記載のイメージセンサー。

#### 【請求項10】

第1面とそれに反対になる第2面を有する基板であって、第1ピクセル、及び前記第1ピクセルと隣接する第2ピクセルを含む基板と、

前記基板内に配置され、前記第1ピクセル及び前記第2ピクセルを分離する深い素子分離部と、

前記第1ピクセル及び前記第2ピクセルで各々前記第1面上に配置される伝送ゲートと、

前記第1ピクセル及び前記第2ピクセルの中でいずれか1つに選択的に配置される接地領域と、

前記第2面上に順に積層されるカラーフィルターとマイクロレンズアレイ層と、を含み、

前記深い素子分離部は、

垂直に重畠され、互いに離隔する第1分離部及び第2分離部を含み、

前記第1分離部は、前記第1面から前記第2面に延長される第1導電パターンと、

前記第1導電パターン上の高濃度ドーピングパターンと、

前記第1導電パターンと前記高濃度ドーピングパターンとの間の絶縁パターンと、を含み、

前記高濃度ドーピングパターンは、前記第1ピクセル及び前記第2ピクセルの間で連続する(continuous)、イメージセンサー。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明はイメージセンサーに関する。

#### 【背景技術】

10

20

30

40

50

**【 0 0 0 2 】**

イメージセンサーは光学映像 (Optical image) を電気信号に変換する半導体素子である。最近になって、コンピュータ産業と通信産業の発達につれてデジタルカメラ、ビデオカメラ、PCS (Personal Communication System)、ゲーム機器、警備用カメラ、医療用マイクロカメラ等の様々な分野で性能が向上されたイメージセンサーの需要が増大している。イメージセンサーはCCD (Charge coupled device) 型及びCMOS (Complementary metal oxide semiconductor) 型に分類されることができる。CMOS型イメージセンサーはCIS (CMOS image sensor) と略称される。前記CISは2次元的に配列された複数のピクセルを具備する。前記ピクセルの各々はフォトダイオード (photodiode、PD) を含む。前記フォトダイオードは入射される光を電気信号に変換する役割をする。前記複数のピクセルはこれらの間に配置される深い素子分離パターン (deep isolation pattern) によって定義される。

10

**【先行技術文献】****【特許文献】****【 0 0 0 3 】**

【特許文献1】米国特許第10,868,070B2号公報

20

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 4 】**

本発明に達成しようとする一つの技術的課題はゲート電極のサイズを増加させることと同時にピクセル間のクロストーク (cross talk) を最小化するイメージセンサーの構造及び製造方法を提供することにある。

**【 0 0 0 5 】**

本発明が解決しようとする他の技術的課題は高集積化が容易であるイメージセンサー及びその製造方法を提供することにある。

**【課題を解決するための手段】****【 0 0 0 6 】**

本発明の実施形態によるイメージセンサーは第1面とそれに反対になる第2面を有する基板であって、第1ピクセル及び前記第1ピクセルと隣接する第2ピクセルを含む基板と、前記基板内に配置され、前記第1ピクセル及び前記第2ピクセルを分離する深い素子分離部と、前記第1ピクセル及び前記第2ピクセルで各々前記第1面上に配置される伝送ゲートと、前記第1ピクセル及び前記第2ピクセルの中でいずれか1つに選択的に配置される接地領域と、前記第2面上に順に積層される第1カラーフィルターとマイクロレンズアレイ層とを含み、前記深い素子分離部は、垂直に重畳され、互いに離隔する第1分離部及び第2分離部を含み、前記第1分離部は、前記第1面から前記第2面に延長される第1導電パターン、前記第1導電パターン上の前記基板内に提供される高濃度ドーピングパターン、及び前記第1導電パターンと前記高濃度ドーピングパターンとの間の絶縁パターンを含み、前記接地領域及び前記高濃度ドーピングパターンは、互いに同一な導電型を有する不純物でドーピングができる。

30

**【 0 0 0 7 】**

一部の実施形態によるイメージセンサーは第1面とそれに反対になる第2面を有する基板を含むイメージセンサーであって、前記基板は前記基板の第1面に平行である第1方向及び前記第1面と平行であり、前記第1方向と交差する第2方向に沿って2次元的に配列される第1ピクセルグループ、第2ピクセルグループ、及び一対の第3ピクセルグループを含み、前記第1ピクセルグループの上には第1カラーフィルターが配置され、前記第2ピクセルグループの上には第2カラーフィルターが配置され、前記一対の第3ピクセルグループの上には第3カラーフィルターが各々配置され、前記第1乃至第3ピクセルグループの各々は第1方向及び第2方向に沿ってN×N配列をなすN<sup>2</sup>個のピクセルを含み、前記第1ピクセルグループの各々は第1方向及び第2方向に沿ってN×N配列をなすN<sup>2</sup>個のピクセルを含み、前記第2ピクセルグループの各々は第1方向及び第2方向に沿ってN×N配列をなすN<sup>2</sup>個のピクセルを含み、前記第3ピクセルグループの各々は第1方向及び第2方向に沿ってN×N配列をなすN<sup>2</sup>個のピクセルを含み、前記第1カラーフィルターは第1方向及び第2方向に沿ってN×N配列をなすN<sup>2</sup>個のピクセルを含み、前記第2カラーフィルターは第1方向及び第2方向に沿ってN×N配列をなすN<sup>2</sup>個のピクセルを含み、前記第3カラーフィルターは第1方向及び第2方向に沿ってN×N配列をなすN<sup>2</sup>個のピクセルを含み、前記高濃度ドーピングパターンは、互いに同一な導電型を有する不純物でドーピングができる。

40

50

記  $n^2$  個のピクセルの間で及び前記第1乃至第3ピクセルグループの間で前記基板内には深い素子分離部が提供され、前記深い素子分離部は前記第1面から前記第2面に向かって延長される第1分離部及び前記第2面から前記第1面に向かって延長される第2分離部を含み、前記第1分離部は前記  $N^2$  個のピクセルの間に提供される第1分離パターン及び前記第1乃至第3ピクセルグループの間に提供される第2分離パターンを含み、前記第2分離部は前記  $N^2$  個のピクセルの間に提供される第3分離パターン及び前記第1乃至第3ピクセルグループの間に提供される第4分離パターンを含み、前記第1分離パターン及び前記第3分離パターンは垂直方向に整列され (aligned) され、互いに離隔し、前記第2分離パターン及び前記第4分離パターンは垂直方向に整列され、第1乃至第4ピクセルの中でいずれか1つは選択的に接地領域を含み、前記第1分離部は前記第1面から前記第2面に延長される第1導電パターン、前記第1導電パターン上の高濃度ドーピングパターン、及び前記第1導電パターンと前記高濃度ドーピングパターンとの間の絶縁パターンを含み、前記  $N$  は2以上の自然数であり得る。

10

20

30

40

50

#### 【0008】

一部の実施形態によるイメージセンサーは第1面とそれに反対になる第2面を有する基板であって、第1ピクセル及び前記第1ピクセルと隣接する第2ピクセルを含む基板と、前記基板内に配置され、前記第1ピクセル及び前記第2ピクセルを分離する深い素子分離部と、前記第1ピクセル及び前記第2ピクセルで各々前記第1面上に配置される伝送ゲートと、前記第1ピクセル及び前記第2ピクセルの中でいずれか1つに選択的に配置される接地領域と、前記第2面上に順に積層されるカラーフィルターとマイクロレンズアレイ層とを含み、前記深い素子分離部は、垂直に重畳され、互いに離隔する第1分離部及び第2分離部を含み、前記第1分離部は、前記第1面から前記第2面に延長される第1導電パターン、前記第1導電パターン上の高濃度ドーピングパターン、及び前記第1導電パターンと前記高濃度ドーピングパターンとの間の絶縁パターンを含み、前記高濃度ドーピングパターンは前記第1ピクセル及び前記第2ピクセル間で連続的であり得る。

#### 【発明の効果】

#### 【0009】

本発明の概念によれば、ピクセルグループの各々は接地領域を共有することができる。4つのピクセルが1つのピクセルグループをなす場合、4つのピクセルの中で1つのピクセルに選択的に接地領域が提供されることができる。ピクセルを分離する深い素子分離部は互いに垂直に重畳され、離隔する第1、第2分離パターンを含むことができる。接地領域が提供されないピクセルであっても、第1分離パターンの高濃度ドーピングパターンを通じて正電荷が移動されることができる。結果的に、3つのピクセルは接地領域が無くとも、第1分離パターンを通じて正電荷が接地領域を通じて抜け出すことができる。また、残りの3つのピクセルは接地領域が不要であるので、これに代えてイメージセンサーを構成するゲート電極の面積が増加することができる。

#### 【図面の簡単な説明】

#### 【0010】

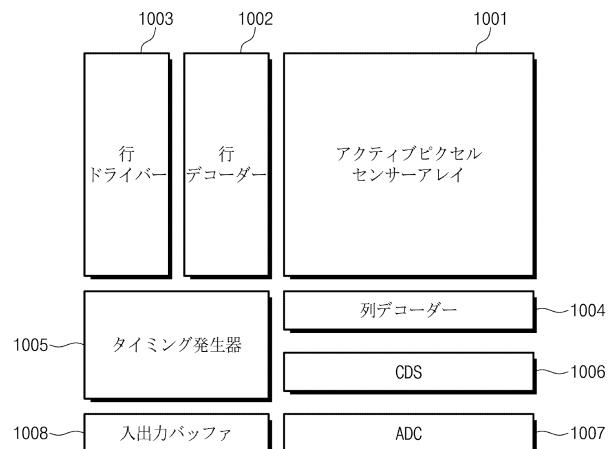

【図1】本発明の実施形態によるイメージセンサーを説明するためのプロック図である。

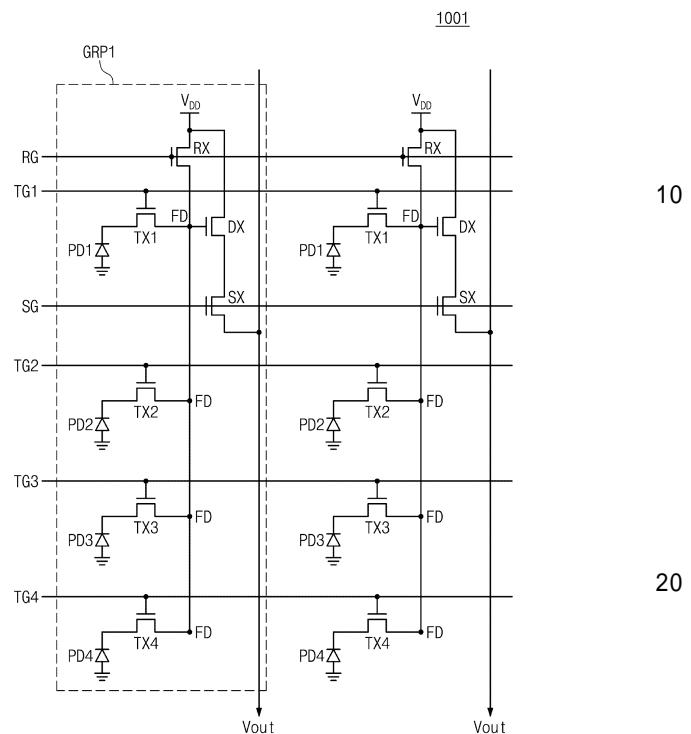

【図2】本発明の実施形態によるイメージセンサーのアクティブピクセルセンサーアレイの回路図である。

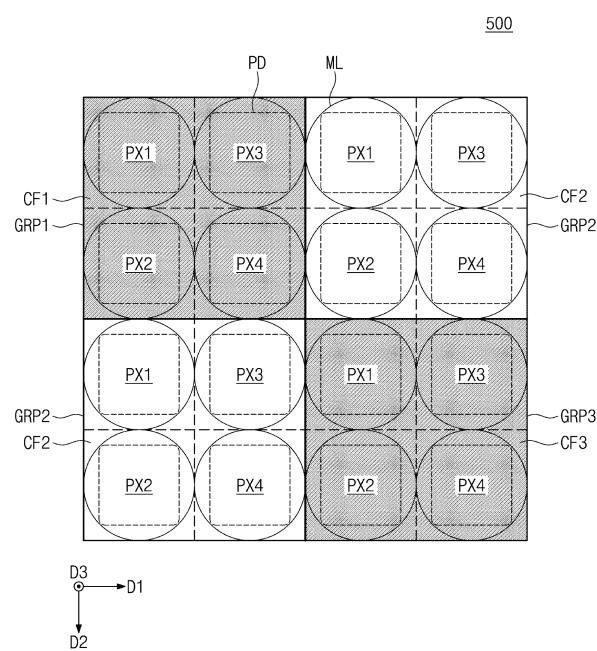

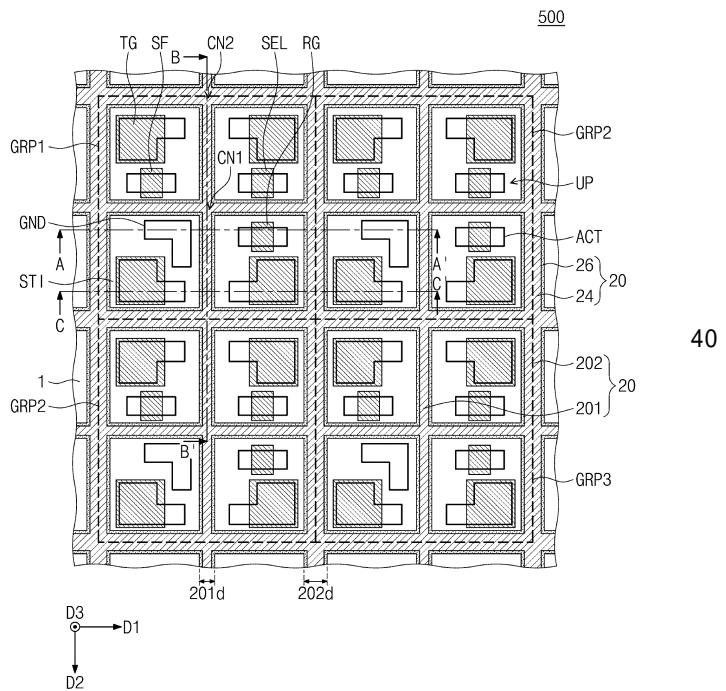

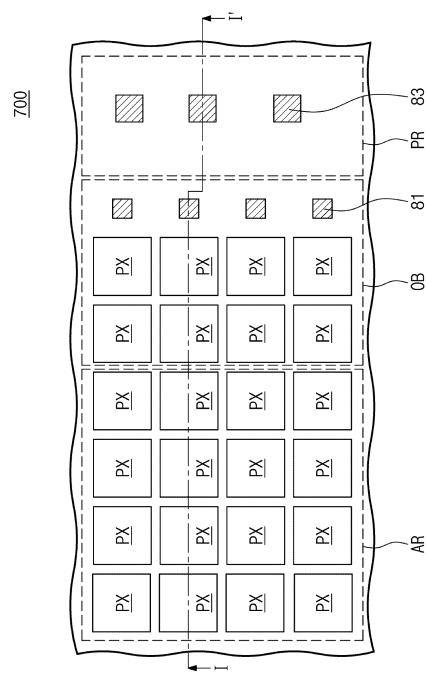

【図3】本発明の実施形態によるイメージセンサーの平面図である。

【図4】図3に対応するイメージセンサーの平面図である。

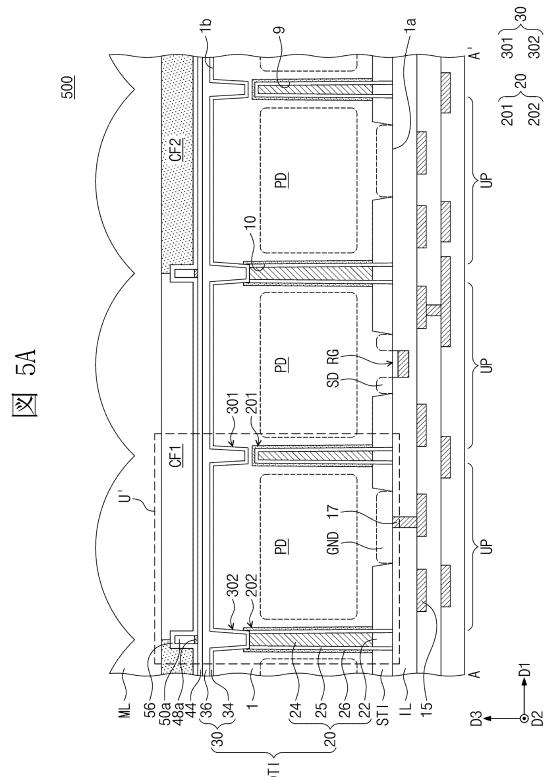

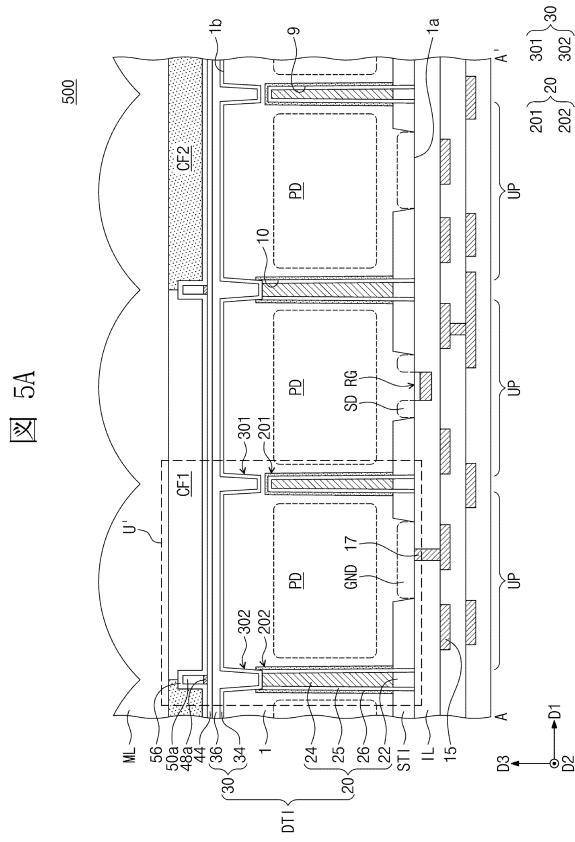

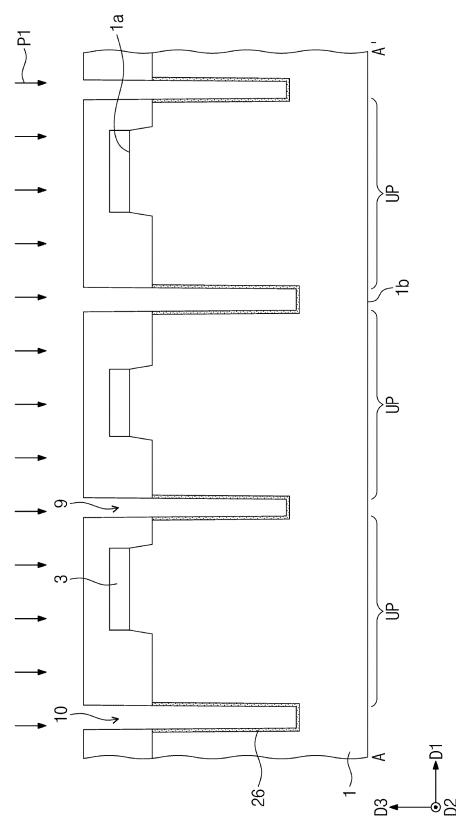

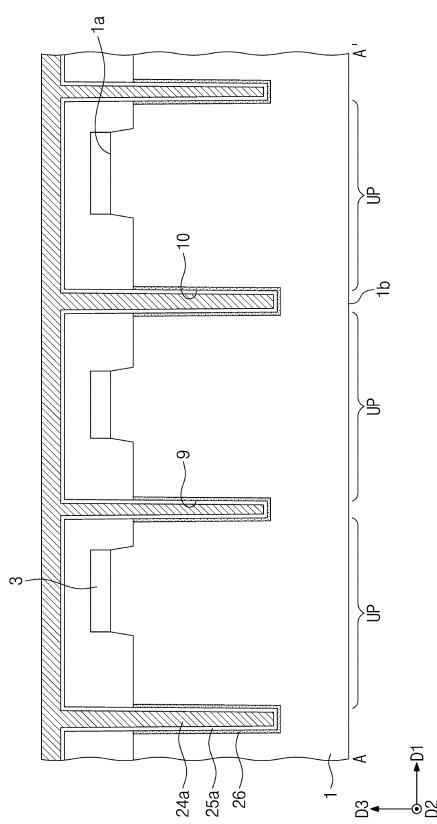

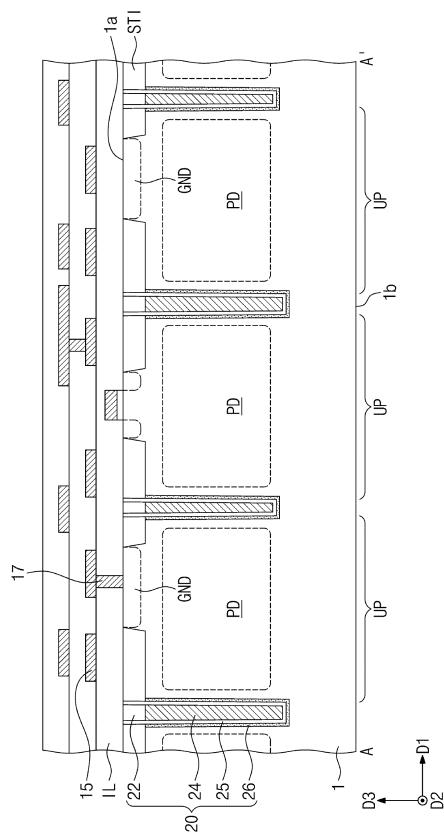

【図5A】本発明の実施形態にしたがって図4をA-A'線に沿って切断した断面図である。

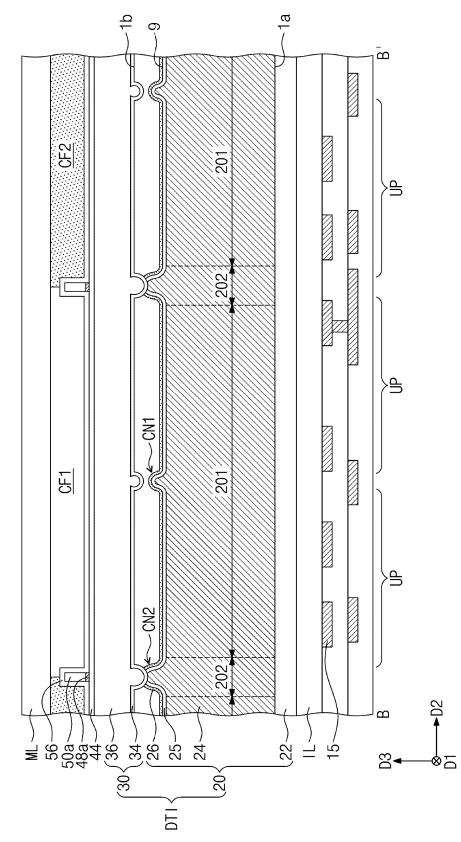

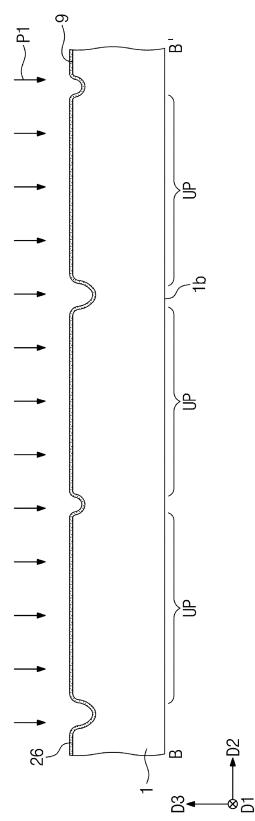

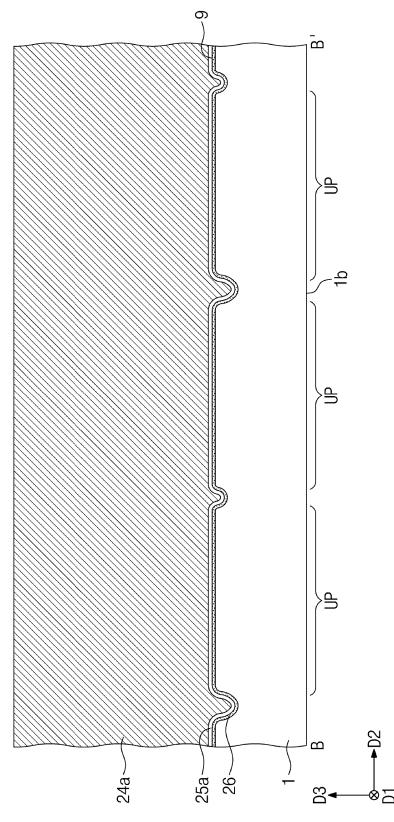

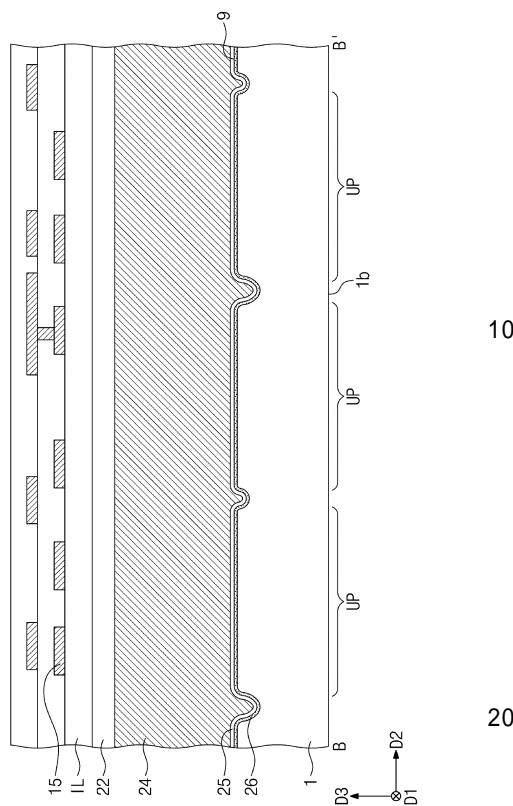

【図5B】本発明の実施形態にしたがって図4をB-B'線に沿って切断した断面図である。

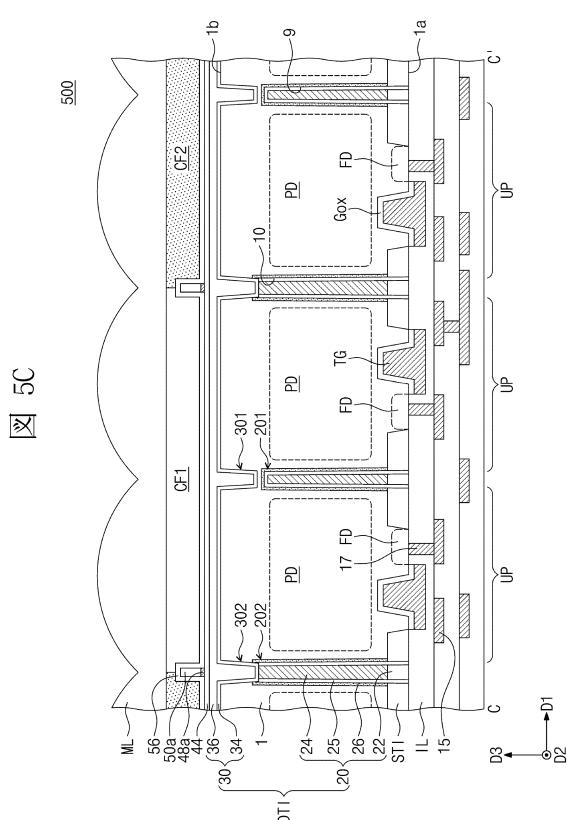

【図5C】本発明の実施形態にしたがって図4をB-B'線に沿って切断した断面図である。

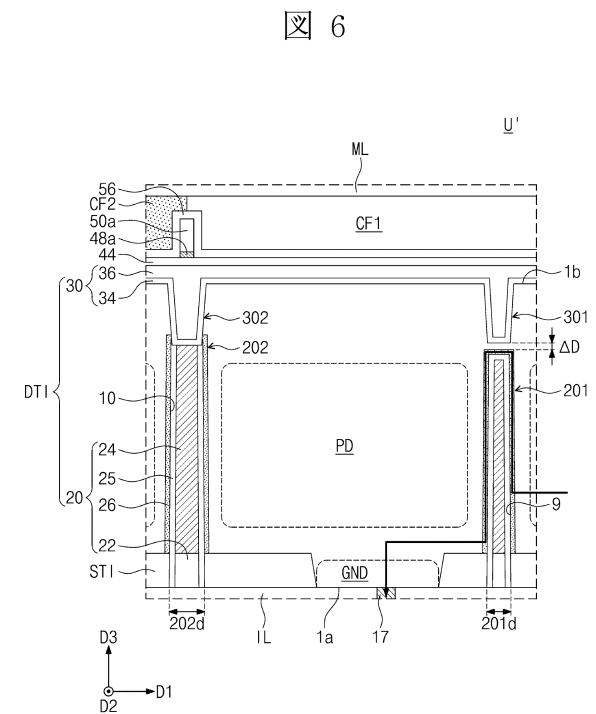

【図6】図5AのU'の拡大図である。

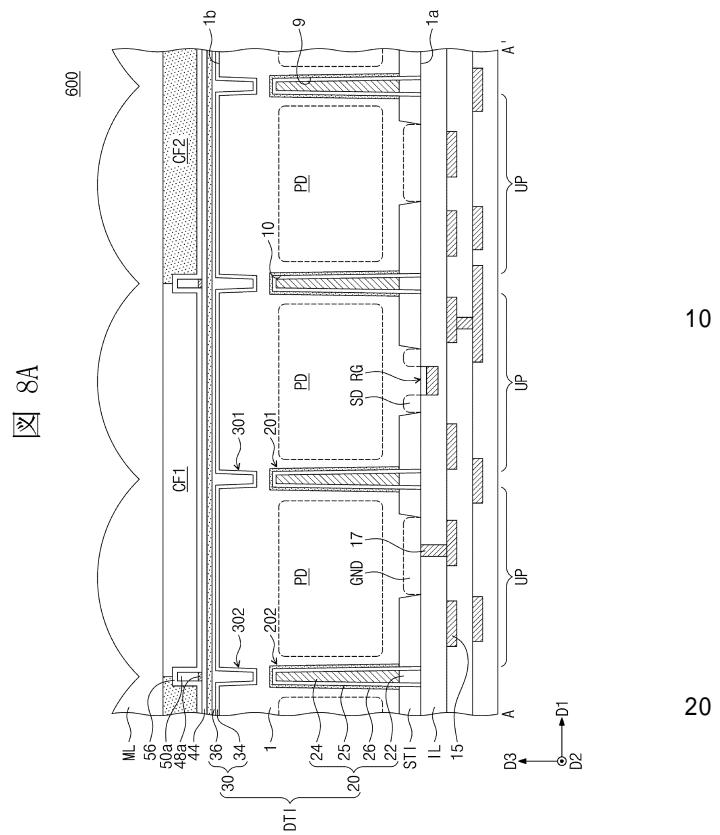

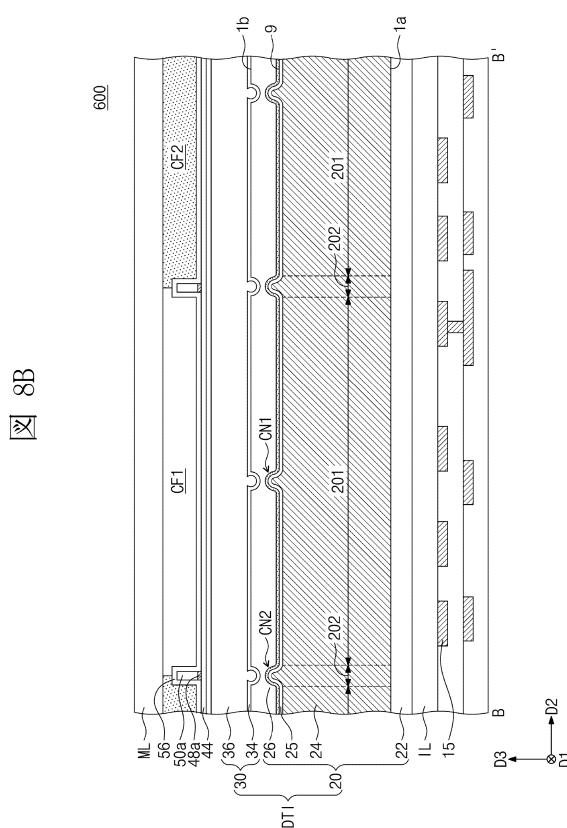

【図7】本発明の一部の実施形態によるイメージセンサーの平面図である。

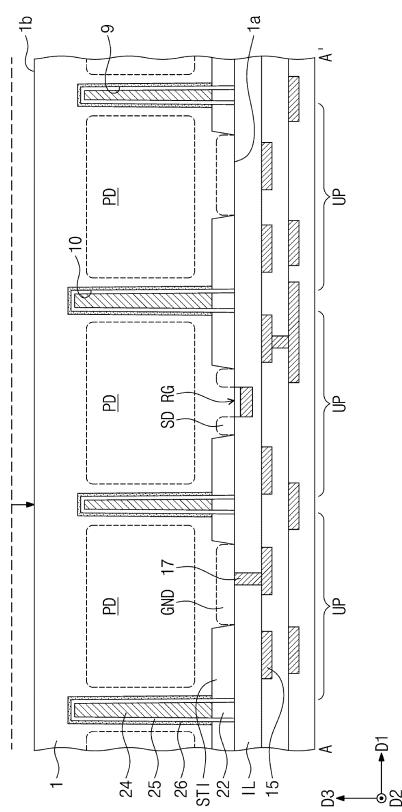

【図8A】本発明の実施形態にしたがって図7をA-A'線に沿って切断した断面図である。

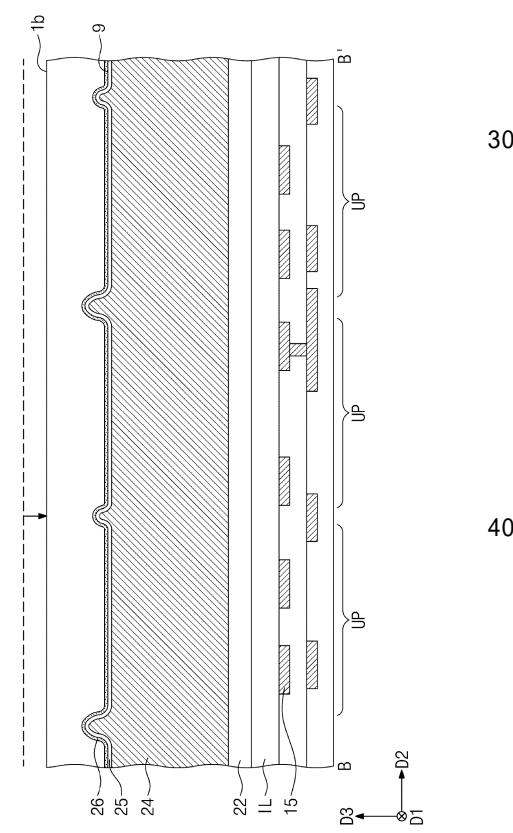

【図8B】本発明の実施形態にしたがって図7をB-B'線に沿って切断した断面図である。

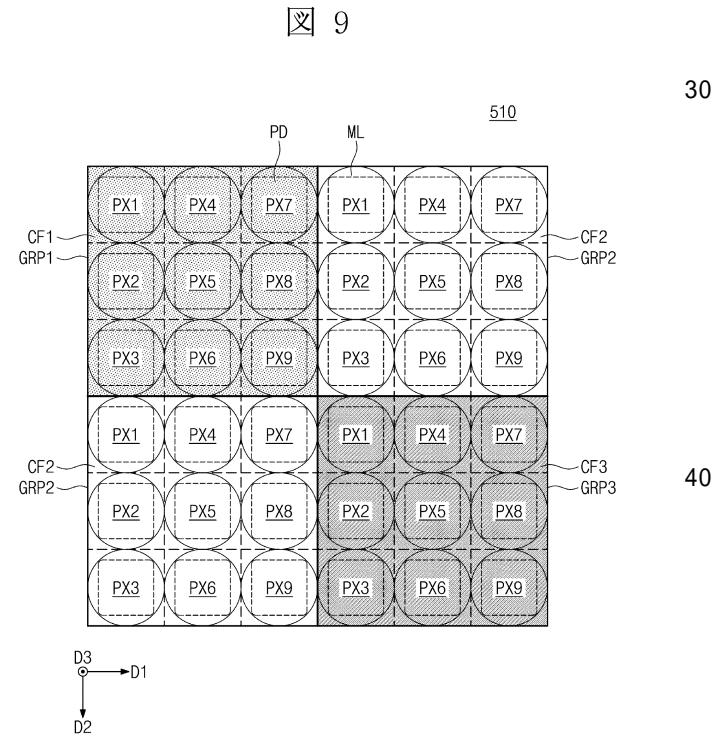

【図9】一部の実施形態によるイメージセンサーの平面図である。

【図10A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図10B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図11A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

10

【図11B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図12A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図12B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図13A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図13B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図14A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図14B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図15A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図15B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図16A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

20

【図16B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図17A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図17B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図18A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図18B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図19A】図5Aのイメージセンサーを製造する過程を順次的に示す断面図である。

【図19B】図5Bのイメージセンサーを製造する過程を順次的に示す断面図である。

【図20】本発明の一部の実施形態によるイメージセンサーの平面図である。

【図21】図20のI-I'線に沿って切断した断面図である。

【発明を実施するための形態】

【0011】

30

以下、本発明をより具体的に説明するために本発明による実施形態を添付図面を参照しながら、より詳細に説明する。

【0012】

図1は本発明の実施形態によるイメージセンサーを説明するためのプロック図である。

【0013】

図1を参照すれば、イメージセンサーは、アクティブピクセルセンサーアレイ(Active Pixel Sensor array)1001、行デコーダー(row decoder)1002、行ドライバー(row driver)1003、列デコーダー(column decoder)1004、タイミング発生器(timing generator)1005、相関二重サンプラー(CDS:Correlated Double Sampler)1006、アナログデジタルコンバータ(ADC:Analog to Digital Converter)1007、及び入出力バッファ(I/O buffer)1008を含むことができる。

【0014】

アクティブピクセルセンサーアレイ1001は、2次元的に配列された複数の単位ピクセルを含み、光信号を電気的信号に変換することができる。アクティブピクセルセンサーアレイ1001は、行ドライバー1003からピクセル選択信号、リセット信号、及び電荷伝送信号のような複数の駆動信号によって駆動されることがある。また、変換された電気的信号は、相関二重サンプラー1006に提供されることがある。

【0015】

40

50

行ドライバー 1003 は、行デコーダー 1002 でデコーディングされた結果に応じて多数の単位ピクセルを駆動するための多数の駆動信号をアクティブピクセルセンサーアレイ 1001 に提供することができる。単位ピクセルが行列形状に配列された場合には各行別に駆動信号が提供されることができる。

#### 【0016】

タイミング発生器 1005 は、行デコーダー 1002 及び列デコーダー 1004 にタイミング (t i m i n g) 信号及び制御信号を提供することができる。

#### 【0017】

相関二重サンプラー (C D S) 1006 は、アクティブピクセルセンサーアレイ 1001 で生成された電気信号を受信して維持 (h o l d) 及びサンプリングすることができる。相関二重サンプラー 1006 は、特定の雑音レベル (n o i s e l e v e l) と電気的信号による信号レベルを二重にサンプリングして、雑音レベルと信号レベルの差分に該当する差分レベルを出力することができる。10

#### 【0018】

アナログデジタルコンバータ (A D C) 1007 は、相関二重サンプラー 1006 から出力された差分レベルに該当するアナログ信号をデジタル信号に変換して出力することができる。

#### 【0019】

入出力バッファ 1008 は、デジタル信号をラッチ (l a t c h) し、ラッチされた信号は、列デコーダー 1004 でのデコーディング結果に応じて順次的に映像信号処理部 (未図示) にデジタル信号を出力することができる。20

#### 【0020】

図 2 は、本発明の実施形態によるイメージセンサーの回路図である。具体的には、図 1 のアクティブピクセルセンサーアレイ 1001 の回路図である。図 2 を参照すれば、複数のピクセルグループ（例えば、G R P 1：第 1 ピクセルグループ）の各々は、第 1 乃至第 4 光電変換部 P D 1、P D 2、P D 3、P D 4、第 1 乃至第 4 トランスファートランジスタ T X 1、T X 2、T X 3、T X 4、及びロジックトランジスタ R X、S X、D X を含むことができる。ここで、ロジックトランジスタは、リセットトランジスタ R X (r e s e t t r a n s i s t o r)、選択トランジスタ S X (s e l e c t i o n t r a n s i s t o r)、及びドライブトランジスタ D X を含むことができる。第 1 乃至第 4 トランスファートランジスタ T X 1、T X 2、T X 3、T X 4、リセットトランジスタ R X、及び選択トランジスタ S X のゲート電極は、駆動信号ライン T G 1、T G 2、T G 3、T G 4、R G、S G に各々連結されることができる。30

#### 【0021】

第 1 乃至第 4 トランスファートランジスタ T X 1、T X 2、T X 3、T X 4 の各々は、第 1 乃至第 4 ゲート電極 T G 1、T G 2、T G 3、T G 4 及び第 1 乃至第 4 光電変換部 P D 1、P D 2、P D 3、P D 4 を含むことができる。実施形態によれば、第 1 乃至第 4 トランスファートランジスタ T X 1、T X 2、T X 3、T X 4 は、フローティング拡散領域 F D (F l o a t i n g D i f f u s i o n r e g i o n) と各々連結されることがある。

#### 【0022】

ピクセルグループ（例えば、G R P 1）内にトランスファートランジスタ T X 1、T X 2、T X 3、T X 4 と各々連結される複数のフローティング拡散領域 F D が提供されることができる。他の一例によれば、1 つのピクセルグループ（例えば、G R P 1）内に 1 つのフローティング拡散領域 F D が形成されることがある。1 つのピクセルグループ（例えば、G R P 1）内のトランスファートランジスタ T X 1、T X 2、T X 3、T X 4 は、1 つのフローティング拡散領域 F D を共有することができる。40

#### 【0023】

第 1 乃至第 4 光電変換部 P D 1、P D 2、P D 3、P D 4 は、外部から入射された光の量に比例して光電荷を生成及び蓄積することができる。第 1 乃至第 4 光電変換部 P D 1、50

P D 2、P D 3、P D 4は、フォトダイオード(photodiode)、フォトトランジスタ(photo transistor)、フォトゲート(photo gate)、ピン留めフォトダイオード(Pinned Photo Diode; P P D)又はこれらの組合を含むことができる。

#### 【0024】

フローティング拡散領域F Dは、第1乃至第4光電変換部P D 1、P D 2、P D 3、P D 4で生成された電荷が伝送されて累積的に格納することができる。フローティング拡散領域F Dに蓄積された光電荷の量に応じてドライブトランジスタD Xが制御することができる。

#### 【0025】

リセットトランジスタR Xは、フローティング拡散領域F Dに蓄積された電荷を周期的にリセットさせることができる。詳細には、リセットトランジスタR Xのドレーン電極はフローティング拡散領域F Dと連結され、ソース電極は電源電圧V D Dに連結されることができる。リセットトランジスタR Xがターンオンされれば、リセットトランジスタR Xのソース電極と連結された電源電圧V D Dがフローティング拡散領域F Dに伝達されることができる。したがって、リセットトランジスタR Xがターンオン(turn-on)されるととき、フローティング拡散領域F Dに蓄積された電荷が排出されてフローティング拡散領域F Dがリセットされることができる。

#### 【0026】

ドライブトランジスタD Xは、フローティング拡散領域F Dでの電位変化を増幅し、選択トランジスタS Xを通じて増幅された又はピクセル信号を出力ラインV O U Tに出力することができる。ドライブトランジスタD Xは、ゲート電極に入力される光電荷量に比例してソース-ドレーン電流を発生させるソースフォロワーバッファ增幅器(source follower buffer amplifier)であり得る。ドライブトランジスタD Xのゲート電極はフローティング拡散領域F Dに連結され、ドライブトランジスタD Xのドレーンは電源電圧V D Dに連結され、ドライブトランジスタD Xのソースは選択トランジスタS Xのドレーンと連結されることができる。

#### 【0027】

選択トランジスタS Xは、行単位に読み出すピクセルを選択することができる。選択トランジスタS Xがターンオンされるとき、ドライブトランジスタD Xのドレーン電極と連結された電源電圧V D Dが選択トランジスタS Xのドレーン電極に伝達されることがある。

#### 【0028】

図3は本発明の実施形態によるイメージセンサーの平面図を示す。

#### 【0029】

図3を参照すれば、本例によるイメージセンサー500は、第1方向D 1と第2方向D 2に沿って2次元的に配列される第1乃至第3ピクセルグループG R P 1、G R P 2、G R P 3を含むことができる。前記第1ピクセルグループG R P 1上には第1カラーフィルターC F 1が配置されることができる。前記第2ピクセルグループG R P 2上には第2カラーフィルターが配置されることができる。前記第3ピクセルグループG R P 3上には第3カラーフィルターが配置されることができる。前記第1乃至第3カラーフィルターは互いに異なる色であり得る。例えば、前記第2カラーフィルターは緑色であり得る。前記第1カラーフィルターと前記第3カラーフィルターの中で1つは赤色であり、他の1つは青色であり得る。図3の第1乃至第3ピクセルグループG R P 1、G R P 2、G R P 3の配列は、1つのグループ単位をなし、複数のグループ単位で提供されて第1方向D 1と第2方向D 2に沿って2次元的に配列されることができる。

#### 【0030】

前記第1乃至第3ピクセルグループG R P 1、G R P 2、G R P 3は、各々第2方向D 2に沿ってN行を成し、第1方向D 1に沿ってN列をなすN × N配列のN<sup>2</sup>個のピクセルを含むことができる。Nは2以上の自然数であり得る。

10

20

30

40

50

## 【0031】

一例として、図3のように、第1乃至第3ピクセルグループGRP1、GRP2、GRP3は、各々第2方向D2に沿って2行を成し、第1方向D1に沿って2列をなす $2 \times 2$ 配列の第1乃至第4ピクセルPX1～PX4を含むことができる。前記第1乃至第3ピクセルグループGRP1、GRP2、GRP3で各々前記第1及び第2ピクセルPX1、PX2は、第2方向D2に沿って順に配列され、第1列を構成することができる。前記第3及び第4ピクセルPX3、PX4は、第2方向D2に沿って順に配列され、第2列を構成することができる。第1、3ピクセルPX1、PX3は、第1方向D1に沿って順に配列され、第1行を構成することができる。第2、4ピクセルPX2、PX4は、第1方向D1に沿って順に配列され、第2行を構成することができる。第1乃至第4ピクセルPX1～PX4内には各々光電変換部PDが配置されることがある。第1乃至第4ピクセルPX1～PX4の光電変換部PDは各々、図5A乃至図5Cの光電変換部PDに対応することができる。

10

## 【0032】

第1乃至第4ピクセルPX1～PX4上には各々マイクロレンズアレイ層MLが配置されることができる。第1乃至第4ピクセルPX1～PX4の間、そして前記第1乃至第3ピクセルグループGRP1、GRP2、GRP3の間で基板1内には深い素子分離部DTIが介在されることがある。

20

## 【0033】

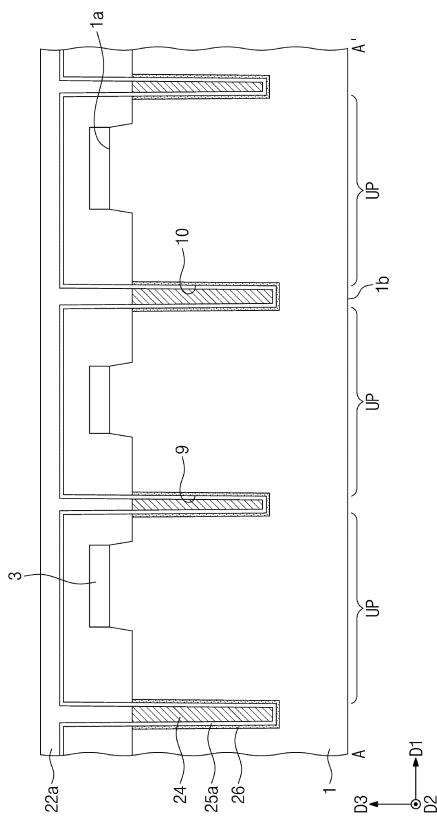

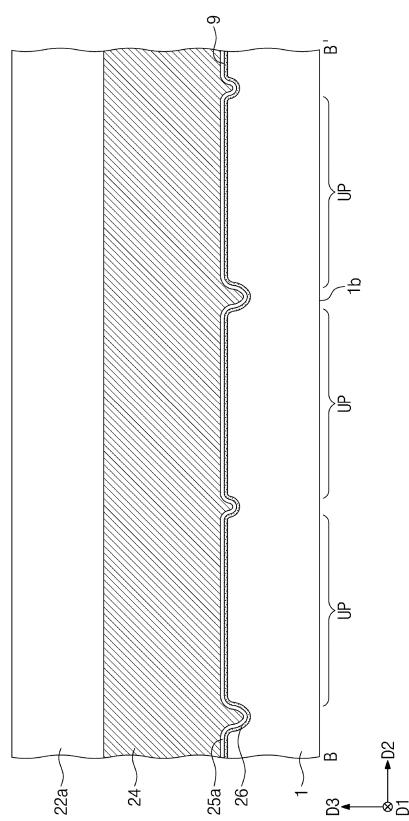

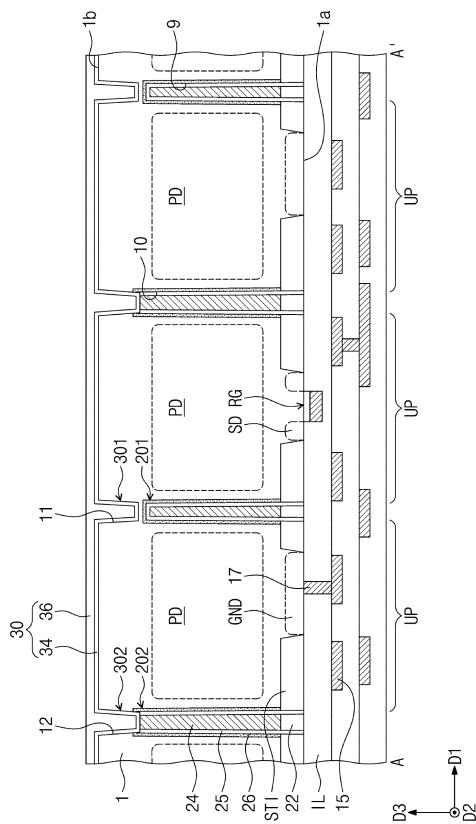

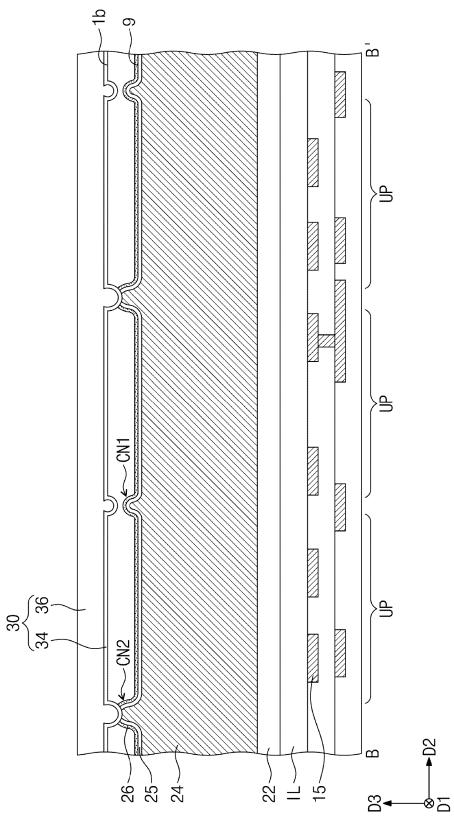

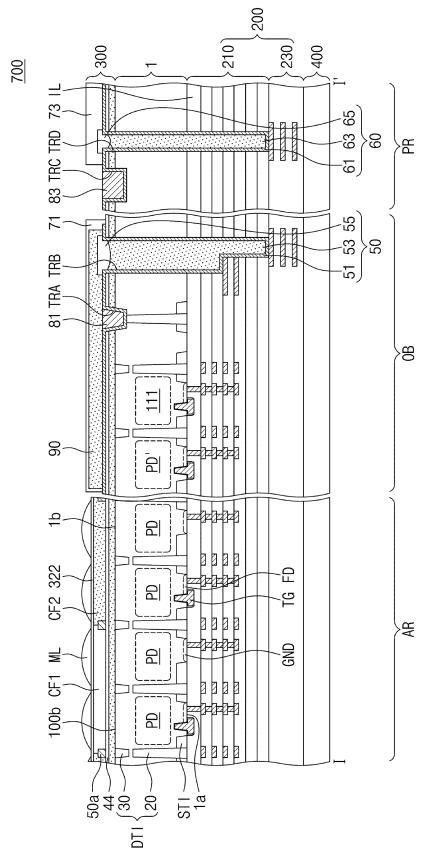

図4は図3に対応するイメージセンサーの平面図を示す。図5Aは本発明の実施形態にしたがって図4をA-A'線に沿って切断した断面図である。図5Bは本発明の実施形態にしたがって図4をB-B'線に沿って切断した断面図である。図5Cは本発明の実施形態にしたがって図4をC-C'線に沿って切断した断面図である。図6は図5AのU'の拡大図である。

20

## 【0034】

図4、図5A、図5B、及び図5Cを参照すれば、本発明の実施形態によるイメージセンサー500は基板1を含む。前記基板1は、例えばシリコン単結晶ウエハ、シリコンエピタキシャル層又はSOI(silicon on insulator)基板であり得る。前記基板1は、例えば第1導電型の不純物でドーピングされることがある。例えば、前記第1導電型はP型であり得る。前記基板1は互いに反対になる第1面1aと第2面1bを含む。前記基板1は図1のようなアクティブピクセルセンサーアレイ1001を含み、図3の第1乃至第4ピクセルPX1～PX4が各々単位ピクセルUPに対応することができる。

30

## 【0035】

前記ピクセルで前記基板1には深い素子分離部DTIが配置されて前記単位ピクセルUPを分離／限定することができる。前記深い素子分離部DTIは平面的にネットの形状を有することができる。

## 【0036】

前記単位ピクセルUPで前記基板1内には光電変換部PDが各々配置されることがある。前記光電変換部PDは前記第1導電型と反対になる第2導電型の不純物でドーピングされることがある。前記第2導電型は、例えばN型であり得る。前記光電変換部PDにドーピングされたN型の不純物は、周辺の基板1にドーピングされたP型の不純物とPN接合を成してフォトダイオードを提供することができる。

40

## 【0037】

前記基板1内には前記第1面1aに隣接する浅い素子分離部STIが配置されることがある。前記浅い素子分離部STIは前記深い素子分離部DTIによって貫通されることがある。前記浅い素子分離部STIは各単位ピクセルUPで前記第1面1aに隣接する活性領域ACTを限定することができる。前記活性領域ACTは、図2のトランジスタTX、RX、DX、SXのために提供されることがある。

## 【0038】

50

各単位ピクセル U P で前記基板 1 の前記第 1 面 1 a 上には伝送ゲート T G が配置されることがある。前記伝送ゲート T G の一部は前記基板 1 内に延長されることができる。前記伝送ゲート T G は Vertical ( 垂直 ) タイプである。又は前記伝送ゲート T G は前記基板 1 内に延長されなく、平坦な形状である Planar ( 平面 ) タイプであってもよい。前記伝送ゲート T G と前記基板 1 との間にはゲート絶縁膜 G o x が介在されることができる。前記伝送ゲート T G の一側で前記基板 1 内にはフローティング拡散領域 F D が配置されることができる。前記フローティング拡散領域 F D には、例えば前記第 2 導電型 ( 一例として、 N 型 ) の不純物がドーピングされることがある。

#### 【 0 0 3 9 】

前記イメージセンサー 5 0 0 は背面受光イメージセンサーであり得る。光は、前記基板 1 の第 2 面 1 b を通じて前記基板 1 内に入射されることがある。入射された光によって前記 P N 接合で電子 - 正孔対が生成されることがある。このように生成された電子は、前記光電変換部 P D に移動されることがある。前記伝送ゲート T G に電圧を印加すれば、前記電子は前記フローティング拡散領域 F D に移動されることがある。

#### 【 0 0 4 0 】

1 つの単位ピクセル ( 第 1 単位ピクセル ) U P で前記第 1 面 1 a 上に伝送ゲート T G に隣接して接地領域 G N D が提供されることがある。接地領域 G N D は、基板 1 と同一の導電型を有することができる。接地領域 G N D は、第 1 導電型の不純物がドーピングされた領域であり得る。他の 1 つの単位ピクセル ( 第 2 単位ピクセル ) U P で伝送ゲート T G に隣接してリセットゲート R G が配置されることがある。その他の単位ピクセル ( 第 3 単位ピクセル ) U P で前記第 1 面 1 a 上に伝送ゲート T G に隣接してソースフォロワーゲート S F が配置されることがある。その他の単位ピクセル ( 第 4 単位ピクセル ) U P で伝送ゲート T G に隣接して選択ゲート S E L が配置されることがある。前記ゲート T G 、 R G 、 S F 、 S E L は各々図 2 のトランジスタ T X 、 R X 、 D X 、 S X のゲートに対応することができる。リセットゲート R G 、ソースフォロワーゲート S F 、及び選択ゲート S E L の各々のゲートを基準にソース / ドレーン領域 S D が提供されることがある。前記接地領域 G N D 及びゲート T G 、 R G 、 S F 、 S E L は、前記活性領域 A C T と重畠されることがある。第 1 乃至第 4 単位ピクセル U P は、ピクセルグループ ( 例えば、 G R P 1 、 G R P 2 、 G R P 3 ) を構成することができる。

#### 【 0 0 4 1 】

前記第 1 面 1 a は、第 1 層間絶縁膜 I L で覆われることができる。前記第 1 層間絶縁膜 I L は、シリコン酸化膜、シリコン窒化膜、シリコン酸化窒化膜、多孔性低誘電膜の中から選択される少なくとも 1 つの膜の多層膜で形成されることがある。前記第 1 層間絶縁膜 I L の間又は内には配線 1 5 が配置されることがある。接地領域 G N D は、コントラクトプラグ 1 7 及び配線 1 5 の内で対応する配線 1 5 と電気的に連結されることがある。前記コントラクトプラグ 1 7 は、前記第 1 層間絶縁膜 I L の内で前記第 1 面 1 a に最も近い ( 最下層の ) 第 1 層間絶縁膜 I L を貫通することができる。接地電圧が、前記対応する配線 1 5 及び接地領域 G N D を通じて基板 1 に印加されることがある。接地領域 G N D は、深い素子分離部 D T I と隣接するように配置されることがある。接地領域 G N D のレイアウト形状は、多様にすることができ、一例として

( 外 1 )

“ 1 、 L ”

のような形状を有することができる。フローティング拡散領域 F D は、コントラクトプラグ 1 7 及び配線 1 5 の内で対応する配線 1 5 と電気的に連結されることがある。

#### 【 0 0 4 2 】

前記深い素子分離部 D T I は、第 1 分離部 2 0 及び第 2 分離部 3 0 を含むことができる。第 1 分離部 2 0 は、第 1 分離パターン 2 0 1 及び第 2 分離パターン 2 0 2 を含むことができる。第 2 分離部 3 0 は、第 3 分離パターン 3 0 1 及び第 4 分離パターン 3 0 2 を含む

10

20

30

40

50

ことができる。第1分離部20は、第1面1aから第2面1bに向かって延長されることができる。第2分離部30は、第2面1bから第1面1aに向かって延長されることができる。

#### 【0043】

第1分離部20は、第1分離パターン201及び第2分離パターン202を含むことができる。第1分離パターン201は、ピクセルグループGRP1、GRP2、GRP3の各々で、隣接する2つの単位ピクセルUPの間に提供されることがある。第2分離パターン202は、ピクセルグループGRP1、GRP2、GRP3の間に提供されることがある。

#### 【0044】

第1分離パターン201の第1方向D1への幅201dは、第2分離パターン202の第1方向D1への幅202dより小さくすることができる。第1分離パターン201は、第2分離パターン202より第1面1aから第2面1bに向かってより少なく延長されることがある。第1分離パターン201の長さは、第2分離パターン202の長さよりさらに短くすることができる。第1分離パターン201及び第2分離パターン202の長さは、基板1の第1面1aから、前記第1面1aと垂直になる第3方向D3への長さを意味する。

#### 【0045】

第2分離部30は、第3分離パターン301及び第4分離パターン302を含むことができる。第3分離パターン301は、ピクセルグループGRP1、GRP2、GRP3の各々で、隣接する2つの単位ピクセルUPの間に提供されることがある。第4分離パターン302は、ピクセルグループGRP1、GRP2、GRP3の間に提供されることがある。

#### 【0046】

第1分離パターン201及び第3分離パターン301は、垂直に重畳（又は整列（a1i g n e d））し、互いに離隔することができる。第1分離パターン201及び第3分離パターン301の間の距離Dは、100nm乃至300nmであり得る（図6参照）。第2分離パターン202及び第4分離パターン302は、垂直に重畳（又は整列（a1i g n e d））し、互いに接触することができる。

#### 【0047】

第1分離部20は、埋め込み絶縁パターン22、導電パターン24、ライナー絶縁パターン25、及び高濃度ドーピングパターン26を含むことができる。前記埋め込み絶縁パターン22は、前記層間絶縁膜IL上に配置されることがある。導電パターン24は、前記埋め込み絶縁パターン22上に提供され、前記埋め込み絶縁パターン22を介して前記層間絶縁膜ILと離隔することができる。ライナー絶縁パターン25は、前記導電パターン24と前記基板1との間、そして前記埋め込み絶縁パターン22と素子分離部STIとの間に介在されることがある。

#### 【0048】

埋め込み絶縁パターン22及び/又は前記ライナー絶縁パターン25は、例えばシリコン酸化物を含むことができる。前記導電パターン24は前記基板1と離隔されることができる。前記導電パターン24は、不純物がドーピングされたポリシリコン膜やシリコンゲルマニウム膜を含むことができる。前記ポリシリコンやシリコンゲルマニウム膜にドーピングされた不純物は、例えばホウ素、リン、ヒ素の中で1つであり得る。

#### 【0049】

埋め込み絶縁パターン22、導電パターン24、及びライナー絶縁パターン25は、第1深いトレンチ9及び第2トレンチ10を満たすことができる。高濃度ドーピングパターン26は、第1深いトレンチ9及び第2トレンチ10の内壁領域に形成されることがある。高濃度ドーピングパターン26は、第1導電型の不純物でドーピングされた基板1の一領域であり得る。高濃度ドーピングパターン26は、基板1の不純物濃度よりさらに高い不純物濃度を有し、一例として $1 \times 10^{17} / \text{cm}^3$ 乃至 $1 \times 10^{19} / \text{cm}^3$ の濃度

10

20

30

40

50

を有することができる。

#### 【0050】

前記第2分離部30は、第1固定電荷膜34と絶縁パターン36を含むことができる。前記第1固定電荷膜34は、化学量論比より不足している量の酸素又はフッを含む金属酸化膜又は金属フッ化膜の単一膜又は多重膜で構成されることがある。したがって、前記第1固定電荷膜は負の固定電荷を有することができる。前記第1固定電荷膜34は、ハフニウム(Hf)、ジルコニウム(Zr)、アルミニウム(Al)、タンタル(Ta)、チタニウム(Ti)、イットリウム、及びランタノイドを含むグループで選択される少なくとも1つの金属を含む金属酸化物(metal oxide)又は金属フッ化物(metal fluoride)の単一膜又は多重膜で構成されることがある。具体的な例として、前記第1固定電荷膜34は、ハフニウム酸化膜及び/又はアルミニウム酸化膜を含むことができる。前記第1固定電荷膜34によって暗電流とホワイトスポットを改善することができる。第1固定電荷膜34上に絶縁パターン36が提供されることがある。絶縁パターンはシリコン酸化膜を含むことができる。

10

20

30

40

50

#### 【0051】

前記第1固定電荷膜34は前記基板1の表面と接することができる。前記第1固定電荷膜34は、基板1の第2面1bに形成されたトレンチを覆うことができる。第1固定電荷膜34は、第2分離パターン202のライナー絶縁パターン25及び/又は導電パターン24と接触することができる。第2分離パターン202の高濃度ドーピングパターン26は、第1固定電荷膜34によって連結されなくともよい。これに反して、第1分離パターン201の高濃度ドーピングパターン26は、隣接する単位ピクセルUPの間で連続的(continuous)であり得る。

20

#### 【0052】

図5Bのように、ピクセルグループ(例えば、GRP1)内で隣接する2つの単位ピクセルUPの間で第2面1bから第1分離パターン201の上部面の間までの第1距離は、ピクセルグループ(例えば、GRP1、GRP2、GRP3)内で隣接する4つの単位ピクセルUPが同時に隣接する所CN1での前記第2面1bから第1分離パターンの上部面までの第2距離より大きくすることができる。また、隣接するピクセルグループ(例えば、GRP1、GRP2)の間で隣接する4つの単位ピクセルUPが同時に隣接する所CN2での第2面1bの最下部のレベルは、第2分離パターン202の上部面のレベルより下に位置することができる。

#### 【0053】

本発明の概念によれば、ピクセルグループ(例えば、GRP1、GRP2、GRP3)の各々は接地領域GNDを共有することができる。一例として、図3及び図4のように4つのピクセルが1つのピクセルグループをなす場合、4つのピクセルの中で1つのピクセル(例えば、PX2)に選択的に接地領域GNDが提供されることがある。第1分離パターン201及び第3分離パターン301が互いに接触しないので、接地領域GNDが提供されないピクセル(例えば、PX1、PX3、PX4)があるとしても、第1分離パターン201の連続的な(continuous)高濃度ドーピングパターン26を通じて接地領域GNDが提供されたピクセル(例えば、PX2)に正陽電荷が移動されることがある(図6参照)。結果的に、3つのピクセルは、接地領域GNDが無くとも、第1分離パターン201を通じて正電荷が接地領域GNDを通じて抜け出すことができる。また、残りの3つのピクセルは、接地領域GNDが無くとも良いので、ゲート電極TG、RG、SEL、SFの面積が増加することができる。一例として、伝送ゲートTGが占める平面上の面積は単位ピクセル面積の10%以上あり得る。

#### 【0054】

本発明の他の一概念によれば、ピクセルグループの間には第2分離パターン202及び第4分離パターン302が互いに接触するので、受光された光が他のピクセルグループに移動できない(図6参照)。したがって、他の色のカラーフィルターを共有する隣接するピクセルの間でのクロストークを防止することができる。

## 【0055】

前記第2面1b上には第1保護膜44が提供されることがある。一部の実施形態によれば、第1保護膜44及び絶縁パターン36の間に第2固定電荷膜が介在されることがある。前記第2固定電荷膜は、金属酸化膜又は金属フッ化膜の単一膜又は多重膜を含むことができる。前記第2固定電荷膜は、例えばハフニウム酸化膜及び/又はアルミニウム酸化膜を含むことができる。前記第2固定電荷膜は、前記第1固定電荷膜34を補強するか、又は接着膜として機能することができる。前記第1保護膜44は、PETEOS、SiOC、SiO<sub>2</sub>、SiNの中で少なくとも1つを含むことができる。前記第1保護膜44は、反射防止膜及び/又は平坦化膜として機能することができる。

## 【0056】

前記第1保護膜44上には遮光パターン48aと低屈折パターン50aが順に積層されることがある。遮光パターン48aと低屈折パターン50aは、平面的にネットの形状を有することができ、前記深い素子分離部DTIと重畳されることがある。前記遮光パターン48aは、例えばチタニウムを含むことができる。前記低屈折パターン50aは有機物質を含むことができる。前記低屈折パターン50aは、カラーフィルターCF1、CF2、CF3より小さい屈折率を有することができる。例えば、前記低屈折パターン50aは、約1.3以下の屈折率を有することができる。前記低屈折パターン50aの側壁は、前記遮光パターン48aの側壁と整列されることがある。前記遮光パターン48aと前記低屈折パターン50aは、隣接するピクセルの間のクロストークを防止することができる。

10

20

## 【0057】

前記第1保護膜44上には第2保護膜56が積層される。前記第2保護膜45は、前記低屈折パターン50a、前記遮光パターン48a、及び前記連結コンタクトBCAをコンフォーマルに覆うことができる。前記低屈折パターン50aの間にカラーフィルターCF1、CF2、CF3が配置されることがある。前記カラーフィルターCF1、CF2、CF3上にはマイクロレンズアレイ層MLが配置されることがある。前記マイクロレンズアレイ層MLは、前記単位ピクセルUPと各々重畳される膨らんでいるレンズ部を含むことができる。

30

## 【0058】

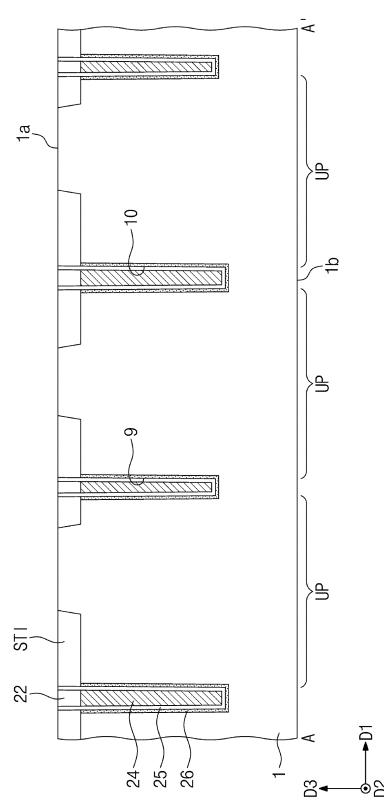

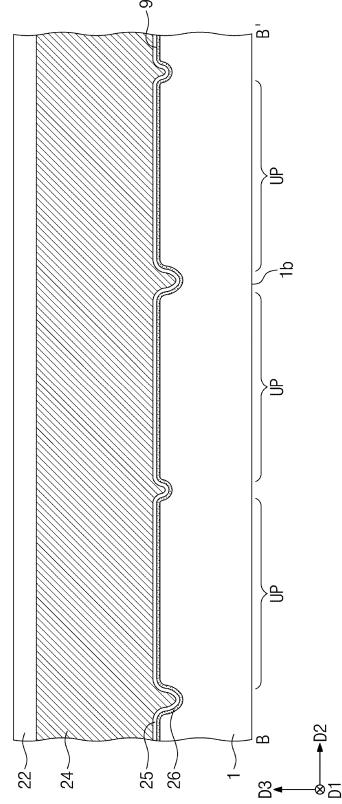

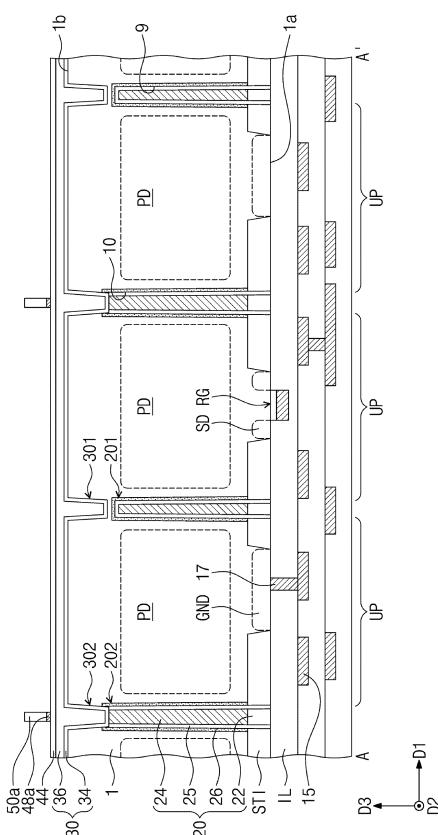

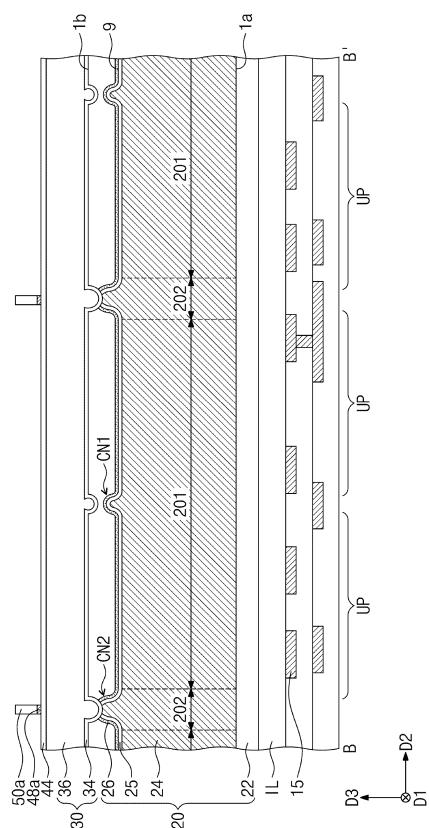

図7は本発明の一部の実施形態によるイメージセンサーの平面図である。図8Aは本発明の実施形態にしたがって図7をA-A'線に沿って切断した断面図である。図8Bは本発明の実施形態にしたがって図7をB-B'線に沿って切断した断面図である。以下では説明することを除けば、図4乃至図6を通じて説明しているので同じ説明を省略する。

40

## 【0059】

図7、図8A、及び図8Bを参照すれば、第2分離パターン202の第1方向D1への幅202dは、第1分離パターン201の第1方向D1への幅201dと実質的に同一であることがある。第2分離パターン202は、第1面1aから第2面1bに向かって第1分離パターン201と実質的に同一な深さに延長されることがある。即ち、第2分離パターン202の長さは、第1分離パターン201の長さと実質的に同一であることができる。

40

## 【0060】

第1分離パターン201及び第3分離パターン301は、垂直に重畳（又は整列（aligned））し、互いに離隔することができる。第2分離パターン202及び第4分離パターン302は、垂直に重畳（又は整列（aligned））し、互いに離隔することができる。

## 【0061】

図8Bのように、隣接するピクセルグループ（例えば、GRP1、GRP2）の間で隣接する4つの単位ピクセルUPが同時に隣接する所CN2での第2面1bの最下部のレベルは、第2分離パターン202の上部面のレベルより上（above）に位置することができる。したがって、第1分離パターン201の高濃度ドーピングパターン26及び第2

50

分離パターン 202 の高濃度ドーピングパターン 26 は、互いに連結することができる。

#### 【0062】

即ち、本発明の一概念によれば、第1ピクセルグループGRP1内で接地領域GNDが提供されないピクセルであるとしても、第1分離パターン201の高濃度ドーピングパターン26及び第2分離パターン202の連続的な(continuous)高濃度ドーピングパターン26を通じて、第2ピクセルグループGRP2の接地領域GNDに正電荷が移動することができる。上のように、接地領域GNDを共有するピクセルの数が増加するにつれ、共有するピクセルのゲート電極TG、RG、SEL、SFの面積が増加することができる。

10

#### 【0063】

図9は、一部の実施形態によるイメージセンサーの平面図を示す。

#### 【0064】

図9を参照すれば、第1乃至第3ピクセルグループGRP1、GRP2、GRP3は、各々第2方向D2に沿って3行を成し、第1方向D1に沿って3列をなす3×3配列の第1乃至第9ピクセルPX1～PX9を含むことができる。

20

#### 【0065】

一部の実施形態によるイメージセンサー510は、また図3乃至図8を通じて説明した同一ピクセルグループ内での接地領域GNDの共有、及び深い素子分離膜DTIの構造的特徴を含むことができる。

#### 【0066】

一部の実施形態によれば、第1乃至第3ピクセルグループGRP1、GRP2、GRP3は、各々第2方向D2に沿って4行を成し、第1方向D1に沿って4列をなす4×4配列の第1乃至第16ピクセルを含むことができる。

#### 【0067】

図10A乃至図19Aは図4Aのイメージセンサーを製造する過程を順次的に示す断面図であって、図4AのA-A'に対応する。図10B乃至図19Bは図4Bのイメージセンサーを製造する過程を順次的に示す断面図であって、図4BのB-B'に対応する。

#### 【0068】

図10A及び図10Bを参照すれば、基板1を準備する。基板1に第1蝕刻マスク3を利用して、蝕刻工程を進行して第1トレンチ5を形成する。

30

#### 【0069】

図11A及び図11Bを参照すれば、基板1の第2面1bを覆う第1絶縁膜8を形成する。第1絶縁膜8は、第1トレンチ5を満たすことができる。第1絶縁膜8は、一例としてシリコン酸化膜を含むことができる。続いて、第1トレンチ5を貫通する第1深いトレンチ9及び第2深いトレンチ10を形成することができる。第1深いトレンチ9及び第2深いトレンチ10は、第2マスクパターンの形成、及び第2マスクパターンを利用した第1絶縁膜8及び基板1の蝕刻工程を含むことができる。第1深いトレンチ9及び第2深いトレンチ10は、グループが交差するネット形状に形成されることができる。第1方向D1への幅9Dは、第2深いトレンチ10の第1方向D1への幅10Dより小さくすることができる。第1深いトレンチ9の深さ9Hは、第2深いトレンチ10の深さ10Hはより小さくすることができる(loadinging effect)。

40

#### 【0070】

このとき、隣接する2つのピクセルUPの間で前記基板1が蝕刻される量より隣接する4つのピクセルUPの間で前記基板1が蝕刻される量がさらに多くすることができる。即ち、一対の第1深いトレンチ9が交差する地点9a及び第2深いトレンチ10と第1深いトレンチ9又は第2深いトレンチ10が交差する地点10aで前記基板1の蝕刻量がさらに多くすることができる。第2深いトレンチ10と第1深いトレンチ9又は第2深いトレンチ10が交差する地点10aでの前記基板1の蝕刻量H2は、一対の第1深いトレンチ9が交差する地点9aでの蝕刻量H1よりさらに多くすることができる(loadinging effect)。

50

effect)。

#### 【0071】

図12A及び図12Bを参照すれば、基板1の第2面1bに向かって、プラズマドーピング工程(PLAD: plasma doping)P1を通じて、前記半導体基板1の一部に第1導電型(例えば、p型)の不純物が注入されることができる。一例として、第1導電型の不純物は、一例としてホウ素であり得る。プラズマドーピング工程P1の結果、第1深いトレンチ9及び第2深いトレンチ10内壁にドーピングパターン26が形成されることがある。

#### 【0072】

図13A及び図13Bを参照すれば、第1深いトレンチ9及び第2深いトレンチ10を満たすライナー絶縁膜25a及び導電膜24aが形成されることがある。一例としてライナー絶縁膜25aはシリコン酸化膜を含むことができ、導電膜24aは、第1導電型(例えば、p型)の不純物がドーピングされたポリシリコンを含むことができる。

#### 【0073】

図14A及び図14Bを参照すれば、導電膜24aの一部が除去されることがある。導電膜24aの除去工程は、エッチバック(etch-back)工程を含むことができる。エッチバック工程によって、導電パターン24が形成されることがある。続いて、ライナー絶縁膜25a上に第2絶縁膜22aが形成されることがある。第2絶縁膜22aは、シリコン酸化膜を含むことができる。

#### 【0074】

図15A及び図15Bを参照すれば、基板1の第2面1b上に平坦化工程が行われることができる。第2絶縁膜22aの一部が除去されて浅い素子分離部STI及び埋め込み絶縁パターン22が形成されることがある。また、ライナー絶縁膜25aの一部が除去されてライナー絶縁パターン25が形成されることがある。浅い素子分離部STIによって活性領域が定義されることがある。

#### 【0075】

図16A及び図16Bを参照すれば、基板1にイオン注入工程等を進行して光電変換部PDを形成する。したがって、単位ピクセルUPが分離されることがある。そして、通常の工程を進行して前記基板1の第1面1aにゲート絶縁膜Gox、伝送ゲートTG、フローティング拡散領域FD、コンタクトプラグ17、配線15、及び層間絶縁膜ILを形成することができる。

#### 【0076】

図17A及び図17Bを参照すれば、前記基板1を覆して第2面1bが上に向かうようになる。グラインディング又はCMP(chemical mechanical polishing)工程を進行して前記基板1の厚さを薄くすることができる。このグラインディング又はCMP工程は、高濃度ドーピングパターン26が露出されないように進行することができる。一部の実施形態によれば、当該工程は省略されることがある。

#### 【0077】

図18A及び図18Bを参照すれば、基板1の第2面1b上に第3蝕刻マスクパターンを形成することができる。第3蝕刻マスクパターンは、第1分離パターン201及び第2分離パターン202と重畠される開口部を有するように形成されることがある。第3蝕刻マスクパターンを蝕刻マスクとして利用して、基板1を蝕刻して第3トレンチ11及び第4トレンチ12を形成することができる。第3トレンチ11は、第3トレンチ11の底面が第1分離パターン201の最上部と離隔されるように形成されることがある。第4トレンチ12は、第4トレンチ12の底面が第2分離パターン202の最上部を露出させるように形成されることがある。第4トレンチ12の底面のレベルは、第3トレンチ11の底面のレベルより低くすることができる。一部の実施形態によれば、第4トレンチ12の底面も第2分離パターン202の最上部を露出させないことがある(図8A参照)。

#### 【0078】

10

20

30

40

50

このとき、隣接する 2 つのピクセル U P の間で前記基板 1 が蝕刻される量より隣接する 4 つのピクセル U P の間で前記基板 1 が蝕刻される量がさらに多くすることができる。即ち、一対の第 3 トレンチ 1 1 が交差する地点及び第 4 トレンチ 1 2 と第 3 トレンチ 1 1 又は第 4 トレンチ 1 2 が交差する地点で前記基板 1 の蝕刻量がさらに多くすることができる。

#### 【 0 0 7 9 】

続いて、第 3 蝕刻マスクパターンを除去することができる。そして、第 2 面 1 b 上に第 1 固定電荷膜 3 4 をコンフォーマルに積層することができる。第 1 固定電荷膜 3 4 は、第 3 トレンチ 1 1 の内壁と底及び第 4 トレンチ 1 2 の内壁と底をコンフォーマルに覆うことができる。第 1 固定電荷膜 3 4 上に絶縁パターン 3 6 を形成して第 3 トレンチ 1 1 及び第 4 トレンチ 1 2 を満たすことができる。10

#### 【 0 0 8 0 】

図 19 A 及び図 19 B を参照すれば、第 2 固定電荷膜（図示せず）及び第 1 保護膜 4 4 を順に積層する。前記第 1 保護膜 4 4 上に拡散防止膜と第 1 金属膜を順に積層する。前記第 1 金属膜を蝕刻して低屈折パターン 5 0 a を形成する。そして、前記拡散防止膜を蝕刻して遮光パターン 4 8 a を形成することができる。

#### 【 0 0 8 1 】

再び、図 5 A 及び図 5 B を参照すれば、前記第 1 保護膜 4 4 上に第 2 保護膜 5 6 をコンフォーマルに形成することができる。そして、前記第 2 保護膜 5 6 上に前記低屈折パターン 5 0 a の間でカラーフィルター C F 1、C F 2、C F 3 を形成することができる。前記カラーフィルター C F 1、C F 2、C F 3 上にマイクロレンズアレイ層 M L を形成する。したがって、図 5 A 及び図 5 B のイメージセンサー 5 0 0 を製造することができる。20

#### 【 0 0 8 2 】

図 20 は本発明の一部の実施形態によるイメージセンサーの平面図であり、図 21 は図 20 の I - I' 線に沿って切断した断面図である。

#### 【 0 0 8 3 】

図 20 及び図 21 を参照すれば、イメージセンサー 7 0 0 は、ピクセルアレイ領域 A R、光学ブラック領域 O B、及びパッド領域 P R を含む基板 1、前記基板 1 の第 1 面 1 0 0 a 上の配線層 2 0 0、前記配線層 2 0 0 上のベース基板 4 0 0、及び前記基板 1 の第 2 面 1 b 上の光透過層 3 0 0 を含むことができる。前記配線層 2 0 0 は、前記基板 1 の前記第 1 面 1 a と前記ベース基板 4 0 0との間に配置することができる。前記配線層 2 0 0 は、前記基板 1 の前記第 1 面 1 a に隣接する上部配線層 2 1 0、及び前記上部配線層 2 1 0 と前記ベース基板 4 0 0との間の下部配線層 2 3 0 を含むことができる。前記ピクセルアレイ領域 A R は、複数のピクセル P X、及びこれらの間に配置される深い素子分離部 D T I を含むことができる。前記深い素子分離部 D T I は、先に説明したイメージセンサー 5 0 0、6 0 0 と実質的に同様に構成されることがある。30

#### 【 0 0 8 4 】

第 1 連結構造体 5 0、第 1 コンタクト 8 1、及びバルクカラーフィルター 9 0 が、前記基板 1 の前記光学ブラック領域 O B 上に配置されることができる。前記第 1 連結構造体 5 0 は、第 1 遮光パターン 5 1、第 1 低屈折残余膜 5 3、及び第 1 キャッピングパターン 5 5 を含むことができる。前記第 1 遮光パターン 5 1 は、前記基板 1 の前記第 2 面 1 b 上に配置されることができる。前記第 1 遮光パターン 5 1 は、前記第 1 保護膜 4 4 を覆うことができ、第 1 トレンチ T R A 及び第 2 トレンチ T R B の各々の内壁をコンフォーマルに覆うことができる。前記第 1 遮光パターン 5 1 は、基板 1 及び前記上部配線層 2 1 0 を貫通することができる。前記第 1 遮光パターン 5 1 は、前記基板 1 の前記深い素子分離部 D T I の前記第 1 分離部 2 0 に連結されることができ、前記上部配線層 2 1 0 及び前記下部配線層 2 3 0 内の配線に連結されることができる。したがって、前記第 1 連結構造体 5 0 は、前記基板 1 及び前記配線層 2 0 0 を電気的に連結することができる。前記第 1 遮光パターン 5 1 は、金属物質（一例として、タングステン）を含むことができる。前記第 1 遮光パターン 5 1 は、前記光学ブラック領域 O B 内に入射される光を遮断することができる。40

## 【 0 0 8 5 】

前記第1コンタクト81は、前記第1トレンチT R Aの残部を満たすことができる。前記第1コンタクト81は、金属物質（一例として、アルミニウム）を含むことができる。前記第1コンタクト81は、前記深い素子分離部D T Iの前記第1分離部20に連結されることがある。前記第1コンタクト81を通じて前記第1分離部20にバイアスが印加されることがある。前記第1低屈折残余膜53は、前記第2トレンチT R Bの残部を満たすことができる。前記第1低屈折残余膜53は、前記基板1を貫通することができ、前記配線層200の一部を貫通することができる。前記第1低屈折残余膜53は絶縁材料を含むことができる。前記第1キャッピングパターン55は、前記第1低屈折残余膜53上に配置されることがある。前記第1キャッピングパターン55は、前記深い素子分離部D T Iの前記埋め込み絶縁パターン22と同一な物質を含むことができる。

10

## 【 0 0 8 6 】

前記バルクカラーフィルター90が、前記第1連結構造体50及び前記第1コンタクト81上に配置されることがある。前記バルクカラーフィルター90は、前記第1連結構造体50及び前記第1コンタクト81を覆うことができる。第1保護膜71が前記バルクカラーフィルター90上に提供されて前記バルクカラーフィルター90を覆うことができる。

## 【 0 0 8 7 】

追加的な光電変換部P D' 及びダミー領域111が、前記光学ブラック領域O Bの対応するピクセルP X内に提供されることがある。前記追加的な光電変換部P D' は、前記基板100の前記第1導電型と異なる第2導電型の不純物（一例として、N型不純物）でドーピングされた領域であり得る。前記追加的な光電変換部P D' は、前記ピクセルアレイ領域A Rの前記複数のピクセルP X内光電変換部P Dと類似の構造を有することができるが、前記光電変換部P Dのような動作（即ち、光を受けて電気的信号を発生させる動作）を遂行しないことがあり得る。前記ダミー領域111は不純物でドーピングされなくともよい。

20

## 【 0 0 8 8 】

第2連結構造体60、第2コンタクト83、及び第2保護膜73が、前記基板100の前記パッド領域P R上に配置されることがある。前記第2連結構造体60は、第2遮光パターン61、第2低屈折残余膜63、及び第2キャッピングパターン65を含むことができる。

30

## 【 0 0 8 9 】

前記第2遮光パターン61は、前記基板1の前記第2面1b上に配置されることがある。前記第2遮光パターン61は、前記第1保護膜44を覆うことができ、第3トレンチT R C及び第4トレンチT R Dの各々の内壁をコンフォーマルに覆うことができる。前記第2遮光パターン61は、前記基板1及び前記上部配線層210を貫通することができる。前記第2遮光パターン61は、前記下部配線層230内の配線に連結されることがある。したがって、前記第2連結構造体60は、前記基板1及び前記配線層200を電気的に連結することができる。前記第2遮光パターン61は金属物質、タンゲステン(W)を含むことができる。前記第2遮光パターン61は、前記パッド領域P R内に入射される光を遮断することができる。

40

## 【 0 0 9 0 】

前記第2コンタクト83は、前記第3トレンチT R Cの残部を満たすことができる。前記第2コンタクト83は、金属物質（一例として、アルミニウム）を含むことができる。前記第2パッド端子83は、イメージセンサーと外部素子との間の電気的連結通路の役割をすることができる。前記第2低屈折残余膜63は、前記第4トレンチT R Dの残部を満たすことができる。前記第2低屈折残余膜63は、前記基板1を貫通することができ、前記配線層200の一部を貫通することができる。前記第2低屈折残余膜63は、絶縁材料を含むことができる。前記第2キャッピングパターン65は、前記第2低屈折残余膜63上に配置されることがある。前記第2キャッピングパターン65は、前記深い素子分離

50

部 D T I の前記埋め込み絶縁パターン 2 2 と同一な物質を含むことができる。前記第 2 保護膜 7 3 は、前記第 2 連結構造体 6 0 を覆うことができる。

#### 【 0 0 9 1 】

前記第 2 コンタクト 8 3 を通じて印加された電流は、前記第 2 遮光パターン 6 1 、前記配線層 2 0 0 内の配線、及び前記第 1 遮光パターン 5 1 を通じて前記深い素子分離部 D T I の前記第 1 分離部 2 0 に流れることができる。前記ピクセルアレイ領域 A R の前記複数のピクセル P X 内の前記光電変換部 P D から発生した電気的信号は、前記配線層 2 0 0 内の配線、前記第 2 遮光パターン 6 1 、及び前記第 2 コンタクト 8 3 を通じて外部に伝送されることができる。

#### 【 0 0 9 2 】

10

以上、添付された図面を参照して本発明の実施形態を説明したが、本発明が属する技術分野で通常の知識を有する者は本発明がその技術的思想や必須の特徴を変更しなくとも他の具体的な形態に実施されることができることを理解することができる。したがって、以上で記述した実施形態はすべての面で例示的なものであり、限定的ではないことと理解しなければならない。

#### 【 符号の説明 】

#### 【 0 0 9 3 】

|                       |             |    |

|-----------------------|-------------|----|

| 1 5                   | 配線          |    |

| 1 7                   | コンタクトプラグ    |    |

| 2 0                   | 第 1 分離部     | 20 |

| 3 0                   | 第 2 分離部     |    |

| 5 0 0                 | イメージセンサー    |    |

| A C T                 | 活性領域        |    |

| C F 1 、 C F 2 、 C F 3 | カラーフィルター    |    |

| D T I                 | 深い素子分離部     |    |

| F D                   | フローイング拡散領域  |    |

| G N D                 | 接地領域        |    |

| I L                   | 層間絶縁膜       |    |

| M L                   | マイクロレンズアレイ層 |    |

| P D                   | 光電変換部       | 30 |

| P X 1 ~ P X 4         | ピクセル        |    |

| S T I                 | 浅い素子分離部     |    |

| T G                   | 伝送ゲート       |    |

| U P                   | 単位ピクセル      |    |

30

40

50

【図面】

【図1】

図 1

【図2】

図 2

【図3】

図 3

【図4】

図 4

【図 5 A】

【図 5 B】

【図 5 C】

【図 6】

10

20

30

40

50

【図7】

【図8A】

【図8B】

【図9】

【図 10A】

【 四 10 B 】

【図 1 1 A】

【 図 1 1 B 】

【図 1 2 A】

図 12A

【図 1 2 B】

図 12B

【図 1 3 A】

図 13A

【図 1 3 B】

図 13B

10

20

30

40

50

【図 14A】

図 14A

【図 14B】

図 14B

【図 15A】

図 15A

【図 15B】

図 15B

10

20

30

40

50

【図 16A】

図 16A

【図 16B】

図 16B

【図 17A】

図 17A

【図 17B】

図 17B

【図 18A】

図 18A

【図 18B】

図 18B

10

20

30

40

【図 19A】

図 19A

【図 19B】

図 19B

50

【 図 20 】

【 図 21 】

10

20

30

40

50

---

フロントページの続き

弁理士 宮崎 修

(72)発明者 朴 海龍

大韓民国京畿道水原市靈通区三星路 1 2 9

(72)発明者 崔 性洙

大韓民国京畿道水原市靈通区三星路 1 2 9

(72)発明者 朴 鍾銀

大韓民国京畿道水原市靈通区三星路 1 2 9

F ターム(参考) 4M118 AA05 AA10 AB01 BA14 CA03 CA04 CA07 CA09 CA22 CA34

CB13 DD04 EA01 EA14 FA06 FA27 FA28 FA33 GA02 GB03 GB07

GB09 GB11 GC08 GD04