(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4921011号

(P4921011)

(45) 発行日 平成24年4月18日(2012.4.18)

(24) 登録日 平成24年2月10日(2012.2.10)

(51) Int.Cl.

F 1

H04N 5/357 (2011.01)

H04N 5/335 570

H04N 5/374 (2011.01)

H04N 5/335 740

H01L 27/146 (2006.01)

H01L 27/14 A

請求項の数 6 (全 11 頁)

(21) 出願番号 特願2006-86311 (P2006-86311)

(22) 出願日 平成18年3月27日 (2006.3.27)

(65) 公開番号 特開2007-266760 (P2007-266760A)

(43) 公開日 平成19年10月11日 (2007.10.11)

審査請求日 平成21年3月17日 (2009.3.17)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 山内 横子

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が光電変換素子を含み2次元に配置された複数の画素と、前記複数の画素の各列毎に設けられ各々同じ列の画素が接続された複数の信号出力線と、前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力される光信号を保持する第1の保持手段と、前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力されるノイズ信号を保持する第2の保持手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号との差分処理を行う差分手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号を前記差分手段に出力する出力手段とを備えた撮像素子と、

前記複数の画素の各行毎に、第1のタイミングで所定の列の画素から光信号を読み出して前記所定の列の前記第1の保持手段に保持するとともに、前記第1のタイミングで同じ行の前記所定の列と異なる列の画素からノイズ信号を読み出して前記異なる列の前記第2の保持手段に保持し、前記差分手段が前記所定の列の前記第1の保持手段に保持された光信号と前記異なる列の前記第2の保持手段に保持されたノイズ信号との差分処理を行うよう制御し、前記第1のタイミングと異なる第2のタイミングで前記異なる列の画素から光信号を読み出して前記異なる列の前記第1の保持手段に保持するとともに、前記第2のタイミングで同じ行の前記異なる列以外の列の画素からノイズ信号を読み出して前記異なる列以外の列の前記第2の保持手段に保持し、前記差分手段が前記異なる列の前記第1の

10

20

保持手段に保持された光信号と前記異なる列以外の列の第2の保持手段に保持されたノイズ信号との差分処理を行うように制御する制御手段と、

を有することを特徴とする撮像装置。

【請求項2】

前記出力手段は、互いに隣り合う2列を1組として、互いの前記第1の保持手段に保持された前記光信号と前記第2の保持手段に保持された前記ノイズ信号を同じタイミングで出力することを特徴とする請求項1に記載の撮像装置。

【請求項3】

前記出力手段は複数の出力チャンネルからなることを特徴とする請求項1または2に記載の撮像装置。

10

【請求項4】

前記各信号出力線には、クランプ回路が接続され、

前記制御手段は、前記画素のリセット電位を前記クランプ回路においてクランプし、前記クランプ回路を介して、前記光信号及び前記ノイズ信号を読み出すように制御することを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。

【請求項5】

前記複数の画素に光を結像するレンズと、前記差分手段から出力された信号を処理する信号処理部とを有する請求項1乃至4のいずれか1項に記載の撮像装置。

【請求項6】

各々が光電変換素子を含み、2次元に配置された複数の画素と、前記複数の画素の各列毎に設けられ各々同じ列の画素が接続された複数の信号出力線と前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力される光信号を保持する第1の保持手段と、前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力されるノイズ信号を保持する第2の保持手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号との差分処理を行う差分手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号を前記差分手段に出力する出力手段とを備えた撮像素子を有する撮像装置の駆動方法であって、

20

前記複数の画素の各行毎に、第1のタイミングで所定の列の画素から光信号を読み出して前記所定の列の前記第1の保持手段に保持するとともに、前記第1のタイミングで同じ行の前記所定の列と異なる列の画素からノイズ信号を読み出して前記異なる列の前記第2の保持手段に保持し、前記差分手段が前記所定の列の前記第1の保持手段に保持された光信号と前記異なる列の前記第2の保持手段に保持されたノイズ信号との差分処理を行うように制御する工程と、

30

前記第1のタイミングと異なる第2のタイミングで前記異なる列の画素から光信号を読み出して前記異なる列の前記第1の保持手段に保持するとともに、前記第2のタイミングで同じ行の前記異なる列以外の列の画素からノイズ信号を読み出して前記異なる列以外の列の前記第2の保持手段に保持し、前記差分手段が前記異なる列の前記第1の保持手段に保持された光信号と前記異なる列以外の列の前記第2の保持手段に保持されたノイズ信号との差分処理を行うように制御する工程と、

40

を有することを特徴とする撮像装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は撮像装置及びその駆動方法に関し、特に、外乱ノイズを削減することを可能にした撮像装置及びその駆動方法に関する。

【背景技術】

【0002】

従来市販されている、CCD、CMOS等の固体撮像素子で撮像した静止画像や動画像を記録・再生する電子カメラ等の撮像装置においては、撮像素子で発生する暗電流ノイズ

50

や撮像素子固有の微小なキズ等の画素欠損等による画質劣化が起きる。

【0003】

このような画質劣化に対し、従来の撮像装置では、各画素について前述の暗電流やキズに由来するノイズ成分と、撮像素子を露光して得られた光信号成分とを読み出して減算することにより、高品位な画像を得ることができる。

【0004】

しかし、上記従来の撮像装置では、外乱ノイズによる画質劣化についての対策が行われておらず、画質劣化が起きることがあった。外乱ノイズとは、ストロボや電源回路の電圧変更を行うDC/DCコンバータの電圧変動によるノイズ、撮像素子の電源変動によるノイズ、レンズや絞りを動かすモータなどから発生する磁気の変動によるノイズ、デジタル回路から発生するノイズ等のことである。外乱ノイズは、信号線や出力線等の配線に特に影響を与える。CMOSセンサではフォトダイオード近傍で信号電荷を信号電圧に変換するため、CCDに比べ配線が長く、外乱ノイズの影響を受けやすい。

10

【0005】

近年では、電子カメラの小型化により上記ノイズ源と撮像素子の距離が近づき、外乱ノイズがより発生しやすくなっている。また、撮像素子の高感度化が進むことで、撮像素子のノイズ成分が増幅され、外乱ノイズは目立ちやすくなる。

【0006】

このような外乱ノイズによる画質劣化を防ぐ手段として、例えば、特許文献1に記載のものが提案されている。この提案においては、各画素毎に画素内に光信号用とノイズ信号用のサンプルホールド回路を設け、光信号とノイズ信号をそれぞれに保存し、保存した信号を各画素から順次同時に出力（各列2線出力）することにより、ノイズ補正を行う。

20

【0007】

【特許文献1】特開2002-344809号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1の構成では、1画素につき、通常の画素と比較して画素の構成要素（サンプルホールド回路を構成する、サンプルスイッチ×2、選択MOS×2、増幅MOS×2、光信号用ホールド容量×1、ノイズ信号用ホールド容量×1）が多い。従って、1画素のサイズが通常の画素と比較して大きくなってしまう。また、垂直方向の各読み出し列につき出力線が2本ずつ必要であるため、配線に必要な面積も広くなる。このため、特許文献1を画素サイズの小さい撮像素子に適用することは難しい。

30

【0009】

本発明は上記問題点を鑑みてなされたものであり、1画素のサイズを大きくすることなく、外乱ノイズを抑制することのできる構成を有する撮像素子及びその駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記目的を達成するために、本発明の撮像装置は、各々が光電変換素子を含み2次元に配置された複数の画素と、前記複数の画素の各列毎に設けられ各々同じ列の画素が接続された複数の信号出力線と、前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力される光信号を保持する第1の保持手段と、前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力されるノイズ信号を保持する第2の保持手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号との差分処理を行う差分手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号を前記差分手段に出力する出力手段とを備えた撮像素子と、前記複数の画素の各行毎に、第1のタイミングで所定の列の画素から光信号を読み出して前記所定の列の前記第1の保持手段に保持するとともに、前記第1のタイミングで同じ行の前記所定の列と異なる列の画

40

50

素からノイズ信号を読み出して前記異なる列の前記第2の保持手段に保持し、前記差分手段が前記所定の列の前記第1の保持手段に保持された光信号と前記異なる列の前記第2の保持手段に保持されたノイズ信号との差分処理を行うように制御し、前記第1のタイミングと異なる第2のタイミングで前記異なる列の画素から光信号を読み出して前記異なる列の前記第1の保持手段に保持するとともに、前記第2のタイミングで同じ行の前記異なる列以外の列の画素からノイズ信号を読み出して前記異なる列以外の列の前記第2の保持手段に保持し、前記差分手段が前記異なる列の前記第1の保持手段に保持された光信号と前記異なる列以外の列の第2の保持手段に保持されたノイズ信号との差分処理を行うように制御する制御手段と、を有する。

【0011】

10

また、各々が光電変換素子を含み、2次元に配置された複数の画素と、前記複数の画素の各列毎に設けられ各々同じ列の画素が接続された複数の信号出力線と前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力される光信号を保持する第1の保持手段と、前記複数の信号出力線の各々に対して設けられ前記複数の画素から前記複数の信号出力線を介して出力されるノイズ信号を保持する第2の保持手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号との差分処理を行う差分手段と、前記第1の保持手段に保持された光信号と前記第2の保持手段に保持されたノイズ信号を前記差分手段に出力する出力手段とを備えた撮像素子を有する撮像装置の本発明の駆動方法は、前記複数の画素の各行毎に、第1のタイミングで所定の列の画素から光信号を読み出して前記所定の列の前記第1の保持手段に保持するとともに、前記第1のタイミングで同じ行の前記所定の列と異なる列の画素からノイズ信号を読み出して前記異なる列の前記第2の保持手段に保持し、前記差分手段が前記所定の列の前記第1の保持手段に保持された光信号と前記異なる列の前記第2の保持手段に保持されたノイズ信号との差分処理を行うように制御する工程と、前記第1のタイミングと異なる第2のタイミングで前記異なる列の画素から光信号を読み出して前記異なる列の前記第1の保持手段に保持するとともに、前記第2のタイミングで同じ行の前記異なる列以外の列の画素からノイズ信号を読み出して前記異なる列以外の列の前記第2の保持手段に保持し、前記差分手段が前記異なる列の前記第1の保持手段に保持された光信号と前記異なる列以外の列の前記第2の保持手段に保持されたノイズ信号との差分処理を行うように制御する工程と、を有する。

20

30

【発明の効果】

【0012】

本発明によれば、1画素のサイズを大きくすることなく、外乱ノイズを抑制することができる構成を有する撮像素子及びその駆動方法を提供することが可能となる。

【発明を実施するための最良の形態】

【0013】

以下、添付図面を参照して本発明を実施するための最良の形態を詳細に説明する。

【0014】

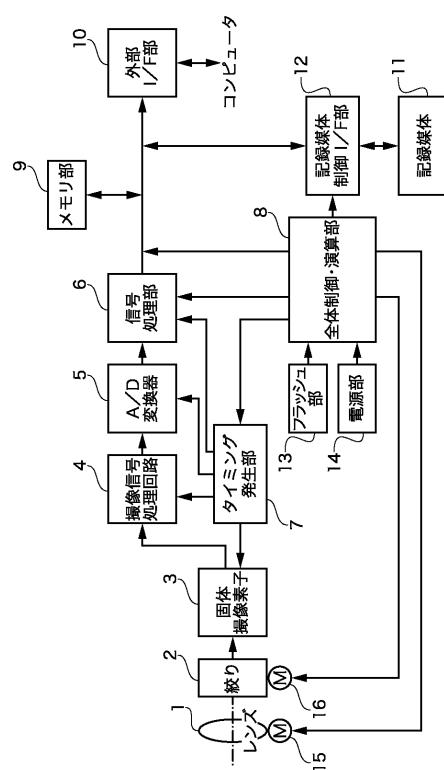

図1は実施の形態における撮像装置の構成を示すブロック図である。

【0015】

40

図1において、1は被写体の光学像を固体撮像素子3に結像させるレンズ、2はレンズ1を通った光量を変化させるための絞り、3はレンズ1で結像された被写体を画像信号として取り込むための固体撮像素子である。4は固体撮像素子3から出力される画像信号を増幅するゲイン可変アンプ部及びゲイン値を補正するためのゲイン補正回路部等を含む撮像信号処理回路、5は固体撮像素子4より出力される画像信号のアナログ デジタル変換を行うA/D変換器である。6はA/D変換器5より出力された画像データに各種の補正を行ったりデータを圧縮したりする信号処理部、7は固体撮像素子3、撮像信号処理回路4、A/D変換器5、信号処理部6に、各種タイミング信号を出力するタイミング発生部である。

【0016】

50

8は各種演算と撮像装置全体を制御する全体制御・演算部、9は画像データを一時的に記憶するためのメモリ部、10は外部コンピュータ等と通信するための外部インターフェース( I / F )部である。11は画像データを記録するための半導体メモリ等からなる着脱可能な記録媒体、12は記録媒体11に対して記録及び読み出しを行うための記録媒体制御インターフェース( I / F )部である。13はAF補助光の投光やフラッシュ調光を行うフラッシュ部、14は必要な電圧を必要な期間、記録媒体11を含む各部に供給する電源部、15はレンズ1を駆動するためのモータ、16は絞り2を駆動するためのモータである。

【0017】

<第1の実施形態>

10

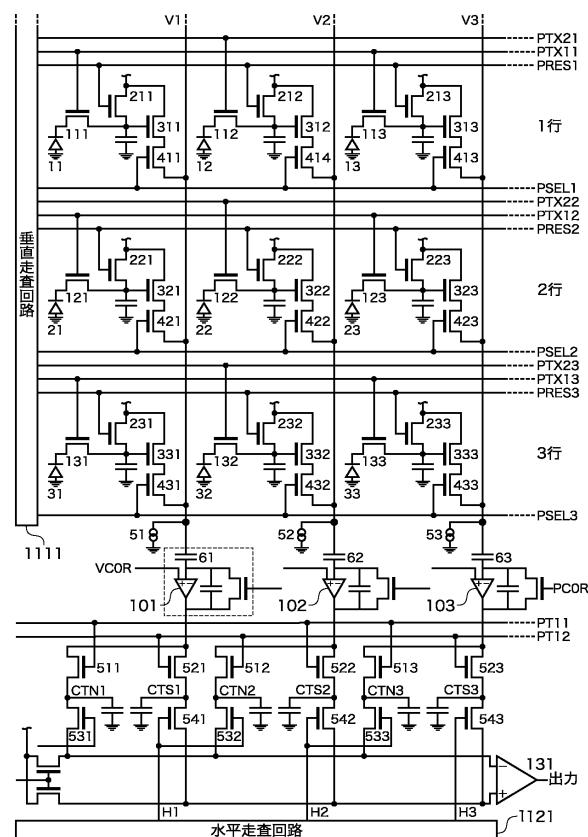

図2は、本発明の固体撮像素子3の第1の実施形態の等価回路図である。固体撮像素子3を構成する各回路素子は、半導体集積回路の製造技術によって、特に制限されないが、単結晶シリコンのような1個の半導体基板上において形成される。また図2では、3行3列の画素アレイのみを示しているが、画素アレイの行数及び列数は任意であることは言うまでもない。

【0018】

図2において、光信号を発生するフォトダイオード(PD)11～33は、この例では陽極側が接地されている。PDの陰極側は、PDに蓄積された光信号電荷を転送するための転送MOS111～133を介して、増幅MOS311～333のゲートに接続されている。増幅MOS311～333のゲートには、これをリセットするためのリセットMOS211～233のソースが接続され、リセットMOS211～233のドレインは、リセット電源に接続されている。また、増幅MOS311～333のドレインは直接、電源に接続されている。

20

【0019】

転送MOS111～133のうち、1行目奇数列の転送MOS111、113のゲートは、横方向に延長して配置される第1の行選択線PTX11に接続される。また、1行目偶数列の転送MOS112のゲートは第2の行選択線PTX21に共通に接続される。

【0020】

また、1行目のリセットMOS211のゲートは、横方向に延長して配置される行リセット線PRES1に接続される。1行目に配置された他の画素セルのリセットMOS212、213のゲートも、行リセット線PRES1に共通に接続される。

30

【0021】

また、1行目の選択MOS411のゲートは、横方向に延長して配置される垂直走査線PSEL1に接続される。1行目に配置された他の画素セルの選択MOS412、413のゲートも、垂直走査線PSEL1に共通に接続される。

【0022】

上述した第1、第2の行選択線、行リセット線、垂直走査線は垂直走査回路1111に接続され、後述するタイミングに基づいて信号電圧が供給される。なお、各配線に対して印可される信号は、各配線の前に「」を付加して配線と区別する。

【0023】

40

また、図2に示されている残りの行についても、同様な構成の画素セルと、第1、第2の行選択線、行リセット線、垂直走査線が設けられる。これらの第1、第2の行選択線、行リセット線、垂直走査線には、垂直走査回路ブロック1111により形成されたPTX12～PTX13、PTX22～PTX23、PRES2～PRES3、PSEL2～PSEL3が供給される。

【0024】

増幅MOS311のソースは、縦方向に延長して配置される垂直信号線V1に上記選択MOS411を介して接続される。同じ列に配置される画素セルの増幅MOS321、331のソースも、選択MOS421、431を介して垂直信号線V1に接続される。図2に示されている残りの垂直信号線V2～V3においても同様に増幅MOS、選択MOSが

50

接続される。

【0025】

垂直信号線 V 1 は、負荷手段である定電流源 5 1 に接続されると共に、クランプ容量 6 1 を介して演算増幅器 101 の反転端子に接続される。演算増幅器 101 の非反転端子はクランプ電圧 V C 0 R ( V R E F ) に接続される。演算増幅器 101 の出力端子は、ノイズ信号転送スイッチ 511 を介してノイズ信号を一時保持するための容量 C T N 1 に、また、光信号転送スイッチ 521 を介して光信号を一時保持するための容量 C T S 1 に接続されている。ノイズ信号保持容量 C T N 1 と光信号保持容量 C T S 1 の逆側の端子は接地されている。ノイズ信号転送スイッチ 511 とノイズ信号保持容量 C T N 1 との接続点と、光信号転送スイッチ 521 と光信号保持容量 C T S 1 との接続点はそれぞれ、水平転送スイッチ 531、541 を介して光信号とノイズ信号の差をとるための差動回路ブロック 131 に接続される。図 2 に示されている残りの列 V 2 ~ 3 においても同様な構成の読み出し回路が設けられる。

【0026】

奇数列に配置されたノイズ信号転送スイッチ 511、513 と、偶数列に配置された光信号転送スイッチ 522 のゲートは第 1 の転送信号入力線 P T 1 1 にそれぞれ共通に接続される。また、偶数列に配置されたノイズ信号転送スイッチ 512 と、奇数列に配置された光信号転送スイッチ 521、523 のゲートは第 2 の転送信号入力線 P T 2 1 にそれぞれ共通に接続される。P T 1 1、P T 2 1 には、後述するタイミングに基づいてそれぞれ信号電圧 P T 1 1、P T 2 1 が供給される。

【0027】

垂直信号線 V 1 に配置された水平転送スイッチ 541 と、垂直信号線 V 2 に配置された水平転送スイッチ 532 のゲートは列選択線 H 1 に共通に接続され、水平走査回路 112 1 に接続される。垂直信号線 V 2 に配置された光信号水平転送スイッチ 542 と、垂直信号線 V 3 に配置されたノイズ信号水平転送スイッチ 533 のゲートは列選択線 H 3 に共通に接続され、水平走査回路ブロック 121 に接続される。

【0028】

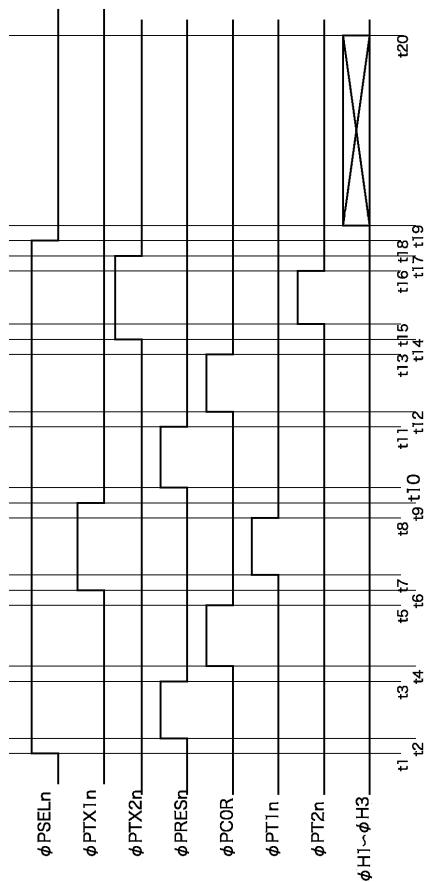

次に、図 2 に示す構成を有する固体撮像素子 3 の本第 1 の実施形態における動作について、図 3 を用いて説明する。なお、図 3 における「n」は行数 ( 1 ~ 3 ) を示し、以下に説明するようにして各行毎に順次駆動される。ここでは、代表的に 1 行目の動作について説明する。

【0029】

時刻 t 1 に行選択パルス P S E L 1 がハイレベルとなった後、時刻 t 2 に画素リセットパルス P R E S 1 がハイレベルとなり、増幅 M O S 311 ~ 313 のゲートがリセット電位にリセットされる。

【0030】

時刻 t 3 に画素リセットパルス P R E S 1 がローレベルとなった後、時刻 t 4 にクランプパルス P C 0 R がハイレベルとなり、リセット電位が垂直信号線 V 1 ~ V 3 に読み出され、容量 61 ~ 63 にクランプされる。

【0031】

時刻 t 5 にクランプパルス P C 0 R がローレベルとなった後、時刻 t 6 の転送パルス P T X 1 1 がハイレベルとなり、P D 1 1、P D 1 3 の光信号が増幅 M O S 311、313 のゲートに転送されると同時に光信号が垂直信号線 V 1、V 3 に読み出される。また、垂直信号線 V 2 には、垂直信号線 V 1、V 3 に光信号が読み出された時に発生していたノイズ信号 ( 外乱ノイズを含む ) が読み出される。

【0032】

時刻 t 7 に転送パルス P T 1 1 がハイレベルとなり、垂直信号線 V 1、V 3 に読み出された P D 1 1、P D 1 3 の光信号が C T S 1、C T S 3 に転送され、垂直信号線 V 2 のノイズ信号が C T N 2 に転送される。

【0033】

10

20

30

40

50

時刻  $t_8$  に転送パルス  $P_{T11}$  がローレベルとなり、時刻  $t_9$  で転送パルス  $P_{TX11}$  がローレベルとなる。

【0034】

ここまで動作で、第1行目に接続された奇数列の画素セルの光信号が、光信号保持容量  $CTS1$ 、 $CTS3$  に保持され、偶数列の画素セルのノイズ信号が、信号保持容量  $CTN2$  に保持される。

【0035】

次に、時刻  $t_{10}$  に画素リセットパルス  $PRE_S1$  がハイレベルとなり、増幅  $MOS311 \sim 313$  のゲートが再びリセット電源にリセットされ、時刻  $t_{11}$  に画素リセットパルス  $PRE_S$  がローレベルとなる。

10

【0036】

時刻  $t_{12}$  にクランプパルス  $PCR$  がハイレベルとなり、時刻  $t_{12}$  の時のリセット電位が垂直信号線  $V1 \sim V3$  に読み出され、ゲイン倍されて容量  $61 \sim 63$  にクランプされた後、時刻  $t_{13}$  にクランプパルス  $PCR$  がローレベルとなる。

【0037】

時刻  $t_{14}$  に転送パルス  $P_{TX21}$  がハイレベルとなり、 $PD12$  の光信号が増幅  $MOS312$  のゲートに転送されると同時に光信号が垂直信号線  $V2$  に読み出される。また、垂直信号線  $V1$ 、 $V3$  には垂直信号線  $V2$  に光信号が読み出された時に発生していたノイズ信号（外乱ノイズを含む）が読み出される。

20

【0038】

時刻  $t_{15}$  に転送パルス  $P_{T21}$  がハイレベルとなり、垂直信号線  $V2$  に読み出されていた  $PD12$  の光信号が  $CTS2$  に転送される。また、垂直信号線  $V1$ 、 $V3$  のノイズ信号が  $CTN1$ 、 $CTN3$  に転送される。

【0039】

時刻  $t_{16}$  に転送パルス  $P_{T21}$  がローレベルとなり、時刻  $t_{17}$  に転送パルス  $P_{TX21}$  がローレベルとなる。

【0040】

ここまで動作で、第1行目に接続された偶数列の画素セルの光信号が、光信号保持容量  $CTS2$  に保持され、奇数列の画素セルのノイズ信号が、信号保持容量  $CTN1$ 、 $CTN3$  に保持される。

30

【0041】

時刻  $t_{18}$  に行選択パルス  $PSEL1$  がローレベルとなる。その後、時刻  $t_{19}$  から  $t_{20}$  の間に、水平走査回路7からの信号  $H1 \sim H3$  によって、各列の水平転送スイッチ  $531 \sim 533$ 、 $541 \sim 543$  のゲートが順時ハイレベルとなる。これにより、光信号保持容量  $CTS1 \sim CTS3$ 、ノイズ信号保持容量  $CTN1 \sim CTN3$  に保持されていた電圧が順次差動回路  $131$  に読み出され、出力端子に出力される。具体的には、図2の配線から分かるように、例えば  $H1$  がハイレベルとなると、1列目の光信号保持容量  $CTS1$  と2列目のノイズ信号保持容量  $CTN2$  から電圧が読み出されて、差動回路  $131$  により差分される。このように、同じタイミングで読み出された光信号からノイズ信号が差し引かれるため、光信号から、光信号の読み出し時に発生していた外乱ノイズ分を削減することが可能になる。

40

【0042】

時刻  $t_{20}$  で読み出しが終了すると、次に2行目について、上述した動作を繰り返し、第2行目の読み出しが終了すると、第3行目について上述した動作を繰り返す。

【0043】

なお、本第1の実施形態では、奇数列のノイズ信号と偶数列の光信号を先に読み出した後、偶数列のノイズ信号と奇数列の光信号を読み出している。しかしながらこれに限るものではなく、偶数列のノイズ信号と奇数列の光信号を先に読み出した後、奇数列のノイズ信号と偶数列の光信号を読み出してもよい。

【0044】

50

上記の通り本第1の実施形態によれば、各画素の構成要素を増やすことなく、垂直信号線に発生した外乱ノイズ分を、光信号から削減することが可能となる。

【0045】

<第2の実施形態>

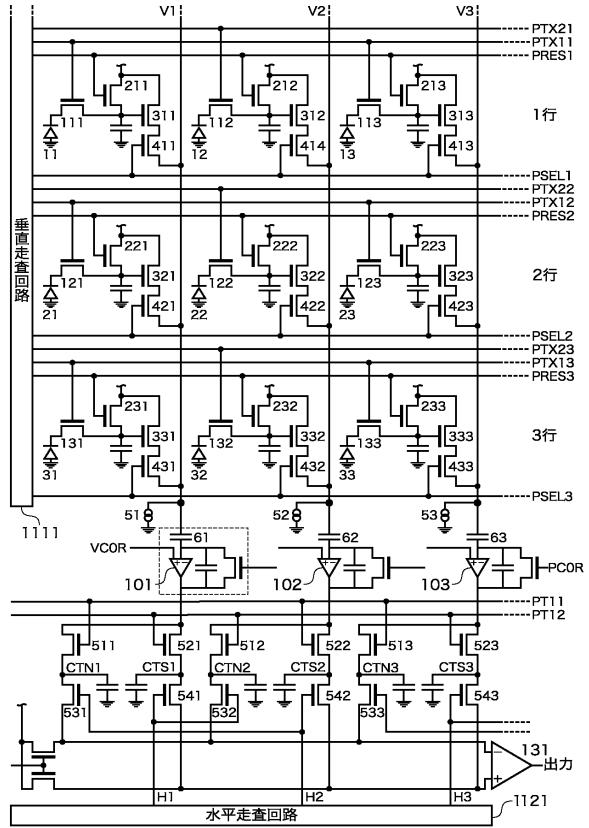

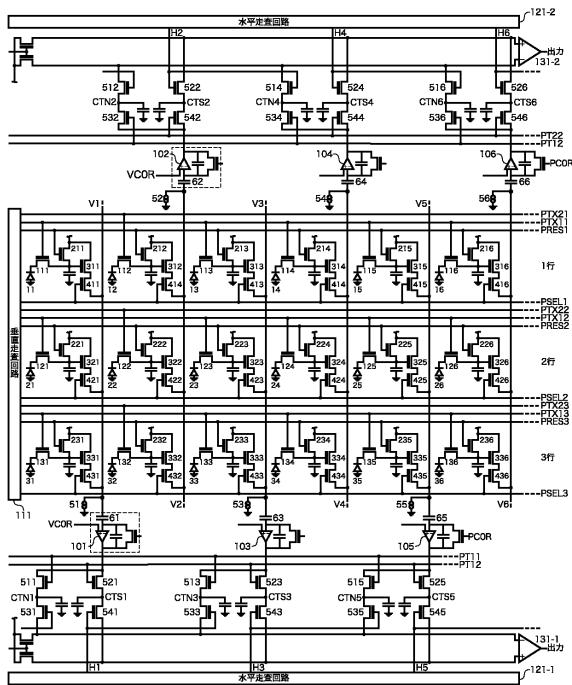

図4は、本発明の第2の実施形態における固体撮像素子の等価回路図である。

【0046】

図4に示す固体撮像素子では、垂直信号線V1に配置された水平転送スイッチ5531と、垂直信号線V2に配置された水平転送スイッチ42のゲートが列選択線H1に共通に接続され、水平走査回路<sub>1121</sub>に接続される。また、垂直信号線V2に配置された光信号水平転送スイッチ532と、垂直信号線V1に配置されたノイズ信号水平転送スイッチ541のゲートが列選択線H3に共通に接続され、水平走査回路<sub>1121</sub>に接続される。また、垂直信号線V3に配置された水平転送スイッチ33と、垂直信号線V4に配置された水平転送スイッチ544のゲートが列選択線H3に共通に接続され、水平走査回路<sub>1121</sub>に接続される。また、垂直信号線V4に配置された光信号水平転送スイッチ534と、垂直信号線V3に配置されたノイズ信号水平転送スイッチ543のゲートが列選択線H4に共通に接続され、水平走査回路<sub>1121</sub>に接続される。

【0047】

その他の構成及び駆動方法は第1実施形態と同様であるため、ここでは説明を省略する。図4に示すように固体撮像素子を構成することにより、第2の実施形態では、2列ずつ互いに、光信号からノイズ信号を差し引くことになる。

【0048】

従って、本第2の実施形態によれば、上記第1の実施形態と同様の効果を得ることが可能となる。

【0049】

<第3の実施形態>

図5は、本発明の第3の実施形態における固体撮像素子の等価回路図である。

【0050】

図5に示す固体撮像素子では、垂直信号線の読み出し方向が一列おきに異なる2チャンネルで信号の読み出しを行う。垂直信号線V1、V3、V5の水平転送スイッチ531、533、535、541、543、545のゲートは列選択線H1、H3、H5に接続され、第1の水平走査回路<sub>121-1</sub>に接続される。一方、垂直信号線V2、V4、V6の水平転送スイッチ532、534、536、542、544、546のゲートは列選択線H2、H4、H6に接続され、第2の水平走査回路ブロック<sub>121-2</sub>に接続される。

【0051】

垂直信号線V1、V3、V5では、ノイズ信号転送スイッチ511、513、515とノイズ信号保持容量CTN1、CTN3、CTN5との接続点は、それぞれ転送スイッチ531、533、535を介して第1の差動回路<sub>131-1</sub>に接続される。また、光信号転送スイッチ521、523、525と光信号保持容量CTS1、CTS3、CTS5との接続点は、それぞれ転送スイッチ541、543、545を介して、第1の差動回路<sub>131-1</sub>に接続される。これにより、第1の差動回路<sub>131-1</sub>では、奇数列の光信号とノイズ信号の差をとる。その他の構成は第1の実施形態あるいは第2の実施形態と同様であるため、ここでは説明を省略する。

【0052】

また、図5に示されている残りの垂直信号線V2、V4、V6についても同様な構成の読み出し回路が設けられる。第3の実施形態においても、駆動の仕方は第1の実施形態あるいは第2の実施形態と同様である。ただし、本第3の実施形態においては、1列おきに読み出しチャンネルが異なっている。そのため、垂直信号線V1の光信号と垂直信号線V3のノイズ信号、垂直信号線V3の光信号と垂直信号線V5のノイズ信号というように、ある列の光信号と同じチャンネル内で隣の列のノイズ信号とが同時に読み出される。

【0053】

10

20

30

40

50

上記構成によれば、上記第1の実施形態と同様の効果に加えて、読み出しチャンネルを2系統としたため、より高速に固体撮像素子から電荷を読み出すことが可能となる。

【0054】

なお、上記第3の実施形態では、1行おきに垂直信号線の読み出し方向が異なる2チャンネル読み出しの場合について説明しているが、これに限るものではない。例えば、2行おきに読み出し方向を変えたり、また水平方向の中央付近でチャンネルを分割する等、チャンネルの分け方については様々な方法が考えられる。何れの場合においても、本願発明では、各チャンネルにおいて隣接する2列について、同じタイミングで光信号とノイズ信号を読み出せるように構成する。

【0055】

10

また、上記第1～第3の実施形態においては、差動回路ブロック131が固体撮像素子と同一の半導体基板上に形成されている場合について説明したが、各画素の光信号とノイズ信号とを別々に撮像素子から出力し、外部の差動回路で差分を取るようにしてよい。

【図面の簡単な説明】

【0056】

【図1】本発明の実施の形態における撮像装置の構成を示すブロック図である。

【図2】本発明の第1の実施形態における固体撮像素子の概略構成を示す等価回路図である。

【図3】本発明の第1の実施形態における固体撮像素子の動作を説明するためのタイミング図である。

20

【図4】本発明の第2の実施形態における固体撮像素子の概略構成を示す等価回路図である。

【図5】本発明の第3の実施形態における固体撮像素子の概略構成を示す等価回路図である。

【図1】

【図2】

【図3】

【 図 4 】

【 図 5 】

---

フロントページの続き

審査官 鈴木 肇

(56)参考文献 特開昭61-264971(JP,A)

特開2004-153682(JP,A)

特開平10-224696(JP,A)

特開2006-101394(JP,A)

特開2005-086260(JP,A)

特開2006-014107(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762