(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6042187号

(P6042187)

(45) 発行日 平成28年12月14日(2016.12.14)

(24) 登録日 平成28年11月18日(2016.11.18)

(51) Int.Cl.

F 1

|             |              |                  |             |             |             |

|-------------|--------------|------------------|-------------|-------------|-------------|

| <b>G09F</b> | <b>9/30</b>  | <b>(2006.01)</b> | <b>G09F</b> | <b>9/30</b> | <b>330</b>  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>624B</b> |

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>680F</b> |

| <b>H01L</b> | <b>27/32</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b> | <b>680G</b> |

| <b>H05B</b> | <b>33/12</b> | <b>(2006.01)</b> | <b>G09G</b> | <b>3/30</b> | <b>J</b>    |

請求項の数 22 (全 16 頁) 最終頁に続く

(21) 出願番号

特願2012-261961 (P2012-261961)

(22) 出願日

平成24年11月30日(2012.11.30)

(65) 公開番号

特開2014-106507 (P2014-106507A)

(43) 公開日

平成26年6月9日(2014.6.9)

審査請求日

平成27年4月15日(2015.4.15)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110000408

特許業務法人高橋・林アンドパートナーズ

(72) 発明者 山田 泰之

千葉県茂原市早野3300番地 株式会社

ジャパンディスプレイイースト内

審査官 田辺 正樹

最終頁に続く

(54) 【発明の名称】OLED表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素と、平面的に見て前記複数の画素と重畳する表示領域と、前記表示領域を囲む周辺領域と、を備える第1基板と、

前記第1基板に対向する第2基板と、

前記複数の画素の各々に形成され、第1電極と、前記第1電極の前記第2基板の側に配置された第2電極と、前記第1電極と前記第2電極との間に配置された発光層と、を具備する発光素子と、

前記第1基板に形成された第1配線及び第2配線と、

前記第2基板に形成され、平面的に見て前記表示領域と重畳しない第3配線と、

前記周辺領域に配置され、前記第1基板と前記第2基板との間に設けられた第1導電性部材と、

前記周辺領域の前記第1導電性部材とは異なる位置に配置され、前記第1基板と前記第2基板との間に設けられた第2導電性部材と、を有し、

前記第1導電性部材は、前記第1基板上で前記第1配線と接続され、前記第2基板上で前記第3配線と接続され、

前記第2導電性部材は、前記第1基板上で前記第2配線と接続され、前記第2基板上で前記第3配線と接続され、

前記第2配線は、互いに離間して位置する複数箇所で前記第2電極と接続されていることを特徴とするOLED表示装置。

10

20

**【請求項 2】**

前記複数の箇所の少なくとも 2 つは、表示領域が有する 1 つの辺に位置することを特徴とする請求項 1 に記載の O L E D 表示装置。

**【請求項 3】**

前記第 1 導電性部材及び前記第 2 導電性部材は、それぞれ複数個配置され、

前記第 1 配線、前記第 2 配線、前記第 3 配線は、それぞれ複数本形成されていることを特徴とする請求項 1 又は請求項 2 に記載の O L E D 表示装置。

**【請求項 4】**

前記表示領域は、第 1 の辺と、前記第 1 の辺と対向する第 2 の辺と、を有し、

前記第 1 導電性部材は前記第 1 の辺の側に配置され、

前記第 2 導電性部材は前記第 2 の辺の側に配置されていることを特徴とする請求項 1 から請求項 3 の何れか 1 項に記載の O L E D 表示装置。

**【請求項 5】**

前記第 1 導電性部材及び前記第 2 導電性部材は、それぞれ複数個配置され、

前記第 1 導電性部材は、前記第 1 の辺の一方の端部の側と他方の端部の側とに配置され、

前記第 2 導電性部材は、前記第 2 の辺の一方の端部の側と他方の端部の側とに配置されていることを特徴とする請求項 4 に記載の O L E D 表示装置。

**【請求項 6】**

前記表示領域は、前記第 1 の辺及び前記第 2 の辺と交差する第 3 の辺と、前記第 3 の辺と対向する第 4 の辺と、を有し、

前記第 2 配線は、前記第 1 の辺の側、前記第 2 の辺の側、前記第 3 の辺の側、及び前記第 4 の辺の側のそれぞれで、前記第 2 電極と接続されることを特徴とする請求項 4 又は請求項 5 に記載の O L E D 表示装置。

**【請求項 7】**

前記周辺領域は、駆動回路が配置された周辺回路領域を含み、

前記第 2 配線は、前記周辺回路領域と前記第 1 基板の端部との間を延在する部分を有することを特徴とする請求項 1 から請求項 6 の何れか 1 項に記載の O L E D 表示装置。

**【請求項 8】**

前記周辺領域は、駆動回路が配置された周辺回路領域を含み、

前記第 2 配線は、前記周辺回路領域と前記表示領域との間を延在する部分を有する第 4 配線と、前記周辺回路領域と前記第 1 基板の端部との間を延在する部分を有する第 5 配線とを含むことを特徴とする請求項 1 から請求項 6 の何れか 1 項に記載の O L E D 表示装置。

**【請求項 9】**

前記第 1 導電性部材は、第 3 導電性部材と前記第 3 導電性部材よりも前記端部の近くに配置された第 4 導電性部材とを含み、

前記第 3 導電性部材は前記第 4 配線と接続され、前記第 4 導電性部材は前記第 5 配線と接続されることを特徴とする請求項 8 に記載の O L E D 表示装置。

**【請求項 10】**

前記第 2 導電性部材は、第 5 導電性部材と前記第 5 導電性部材よりも前記端部の近くに配置された第 6 導電性部材とを含み、

前記第 5 導電性部材は前記第 4 配線と接続され、前記第 6 導電性部材は前記第 5 配線と接続されることを特徴とする請求項 8 又は請求項 9 に記載の O L E D 表示装置。

**【請求項 11】**

前記周辺回路領域は、前記表示領域を挟んで互いに対向する第 1 周辺回路領域と第 2 周辺回路領域とを含み、

前記第 4 配線は、前記第 1 周辺回路領域の側に位置する配線と前記第 2 周辺回路領域の側に位置する配線とを含み、

前記第 5 配線は、前記第 1 周辺回路領域の側に位置する配線と前記第 2 周辺回路領域の

10

20

30

40

50

側に位置する配線とを含むことを特徴とする請求項 8 から請求項 10 の何れか 1 項に記載の O L E D 表示装置。

【請求項 12】

前記第 1 配線は、第 6 配線と第 7 配線とを含み、

前記第 1 導電性部材は、前記第 6 配線と接続される第 7 導電性部材と、前記第 7 配線と接続される第 8 導電性部材とを含み、

前記第 6 配線と前記第 7 配線とは、互いに異なる電圧が印加されることを特徴とする請求項 1 から請求項 11 の何れか 1 項に記載の O L E D 表示装置。

【請求項 13】

前記表示領域は、第 1 の辺を有し、

10

前記第 7 導電性部材は前記第 1 の辺の一方の端部に配置され、

前記第 8 導電性部材は前記第 1 の辺の他方の端部に配置されていることを特徴とする請求項 12 に記載の O L E D 表示装置。

【請求項 14】

前記第 2 電極は前記複数の画素に跨って形成されていることを特徴とする請求項 1 から請求項 13 の何れか 1 項に記載の O L E D 表示装置。

【請求項 15】

前記第 1 基板上にドライバ I C が配置され、

前記第 1 配線は、前記ドライバ I C と接続されていることを特徴とする請求項 1 から請求項 14 の何れか 1 項に記載の O L E D 表示装置。

20

【請求項 16】

複数の画素と、平面的に見て前記複数の画素と重畳する表示領域と、前記表示領域を囲む周辺領域と、を備える第 1 基板と、

前記第 1 基板に対向する第 2 基板と、

前記複数の画素の各々に形成され、第 1 電極と、前記第 1 電極の前記第 2 基板の側に配置された第 2 電極と、前記第 1 電極と前記第 2 電極との間に配置された発光層と、を具備する発光素子と、

前記第 1 基板に形成された第 1 配線、第 2 配線、第 3 配線、及び第 4 配線と、

前記第 2 基板に形成され、平面的に見て前記表示領域と重畳しない第 5 配線及び第 6 配線と、

30

前記周辺領域に配置され、前記第 1 基板と前記第 2 基板との間に設けられた第 1 導電性部材、第 2 導電性部材、第 3 導電性部材、及び第 4 導電性部材と、を有し、

前記第 1 導電性部材は、前記第 1 基板上で前記第 1 配線と接続され、前記第 2 基板上で前記第 5 配線と接続され、

前記第 2 導電性部材は、前記第 1 基板上で前記第 2 配線と接続され、前記第 2 基板上で前記第 5 配線と接続され、

前記第 3 導電性部材は、前記第 1 基板上で前記第 3 配線と接続され、前記第 2 基板上で前記第 6 配線と接続され、

前記第 4 導電性部材は、前記第 1 基板上で前記第 4 配線と接続され、前記第 2 基板上で前記第 6 配線と接続され、

40

前記第 1 配線、前記第 1 導電性部材、前記第 5 配線、前記第 2 導電性部材、及び前記第 2 配線には、第 1 の電圧が印加され、

前記第 3 配線、前記第 3 導電性部材、前記第 6 配線、前記第 4 導電性部材、及び前記第 4 配線には、前記第 1 の電圧とは異なる第 2 の電圧が印加され、

前記第 2 配線と前記第 4 配線とは、前記第 2 電極と接続されていることを特徴とする O L E D 表示装置。

【請求項 17】

前記表示領域は、第 1 の辺と前記第 1 の辺に対向する第 2 の辺とを有し、

前記第 1 導電性部材は前記第 1 の辺の一方の端部に配置され、

前記第 3 導電性部材は前記第 1 の辺の他方の端部に配置され、

50

前記第2導電性部材は前記第2の辺の前記一方の端部と同じ側に配置され、前記第4導電性部材は前記第2の辺の前記他方の端部と同じ側に配置されていることを特徴とする請求項16に記載のOLED表示装置。

**【請求項18】**

複数の画素と、平面的に見て前記複数の画素と重畳する表示領域と、前記表示領域を囲む周辺領域と、を備える第1基板と、

前記第1基板に対向する第2基板と、

前記複数の画素の各々に形成され、第1電極と、前記第1電極の前記第2基板の側に配置された第2電極と、前記第1電極と前記第2電極との間に配置された発光層と、を具備する発光素子と、

10

前記第1基板に形成された第1配線及び第2配線と、

前記第2基板に形成され、平面的に見て前記周辺領域と重畳する第3配線と、

前記周辺領域に配置され、前記第1基板と前記第2基板との間に設けられた第1導電性部材と、

前記周辺領域の前記第1導電性部材とは異なる位置に配置され、前記第1基板と前記第2基板との間に設けられた第2導電性部材と、を有し、

前記周辺領域は、駆動回路が配置された周辺回路領域を含み、

前記第2配線は、前記周辺回路領域と前記第1基板の端部との間を延在する部分を有し、

前記第1導電性部材は、前記第1基板上で前記第1配線と接続され、前記第2基板上で前記第3配線と接続され、

20

前記第2導電性部材は、前記第1基板上で前記第2配線と接続され、前記第2基板上で前記第3配線と接続され、

前記第2配線は、前記第2電極と接続されていることを特徴とするOLED表示装置。

**【請求項19】**

複数の画素と、平面的に見て前記複数の画素と重畳する表示領域と、前記表示領域を囲む周辺領域と、を備える第1基板と、

前記第1基板に対向する第2基板と、

前記複数の画素の各々に形成され、第1電極と、前記第1電極の前記第2基板の側に配置された第2電極と、前記第1電極と前記第2電極との間に配置された発光層と、を具備する発光素子と、

30

前記第1基板に形成された第1配線及び第2配線と、

前記第2基板に形成され、平面的に見て前記周辺領域と重畳する第3配線と、

前記周辺領域に配置され、前記第1基板と前記第2基板との間に設けられた第1導電性部材と、

前記周辺領域の前記第1導電性部材とは異なる位置に配置され、前記第1基板と前記第2基板との間に設けられた第2導電性部材と、を有し、

前記周辺領域は、駆動回路が配置された周辺回路領域を含み、

前記第2配線は、前記周辺回路領域と前記表示領域との間を延在する部分を有する第4配線と、前記周辺回路領域と前記第1基板の端部との間を延在する部分を有する第5配線とを含み、

40

前記第1導電性部材は、前記第1基板上で前記第1配線と接続され、前記第2基板上で前記第3配線と接続され、

前記第2導電性部材は、前記第1基板上で前記第2配線と接続され、前記第2基板上で前記第3配線と接続され、

前記第2配線は、前記第2電極と接続されていることを特徴とするOLED表示装置。

**【請求項20】**

前記第1導電性部材は、第3導電性部材と前記第3導電性部材よりも前記端部の近くに配置された第4導電性部材とを含み、

前記第3導電性部材は前記第4配線と接続され、前記第4導電性部材は前記第5配線と

50

接続されることを特徴とする請求項 19 に記載の O L E D 表示装置。

【請求項 21】

前記第 2 導電性部材は、第 5 導電性部材と前記第 5 導電性部材よりも前記端部の近くに配置された第 6 導電性部材とを含み、

前記第 5 導電性部材は前記第 4 配線と接続され、前記第 6 導電性部材は前記第 5 配線と接続されることを特徴とする請求項 19 又は請求項 20 に記載の O L E D 表示装置。

【請求項 22】

前記周辺回路領域は、前記表示領域を挟んで互いに対向する第 1 周辺回路領域と第 2 周辺回路領域とを含み、

前記第 4 配線は、前記第 1 周辺回路領域の側に位置する配線と前記第 2 周辺回路領域の側に位置する配線とを含み、

前記第 5 配線は、前記第 1 周辺回路領域の側に位置する配線と前記第 2 周辺回路領域の側に位置する配線とを含むことを特徴とする請求項 19 から請求項 21 の何れか 1 項に記載の O L E D 表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、O L E D (organic light-emitting diode) 素子を備えた O L E D 表示装置に関する。

【背景技術】

【0002】

近年、O L E D 表示装置など、供給される電流に応じた強度で発光する素子（以下、「電流発光素子」という。）を用いた表示装置が開発されている。このような表示装置は、電流発光素子に供給される電流量を、各画素における駆動トランジスタにより制御して、表示の階調が制御される。

【0003】

このような表示装置のうち、O L E D 表示装置には、各画素に対応した複数の O L E D 素子及び駆動トランジスタがマトリクス状に形成された基板（以下、「アレイ基板」という。）の上に、O L E D 素子からの光を透過させる対向基板を貼り合わせた構造を有するものがある。O L E D 素子は発光（E L）層を有し、発光層の上下には発光のための電流を供給するアノード及びカソード電極が配置され、これらの電極は、アレイ基板上の電源配線を介してドライバ I C あるいはその他の外部電源と接続されて電源電圧の供給を受ける。

【0004】

このような電源と電極間の伝達損失を最小限にするために、従来の表示装置には、アレイ基板上の電源配線の厚膜化、線幅増加、複線化、多層化等により、電源配線の低抵抗化を実現しようとするものがある（例えば、特許文献 1 参照。）。

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開 2001-154218 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、大画面化に伴う配線長の増加、高精細化・狭額縫化に伴う電源配線領域の縮小等により、アレイ基板上の電源配線が高抵抗化し、上述したような従来の表示装置では、電圧降下による輝度不足や、電圧の電源近端/遠端差による画面内輝度分布（輝度傾斜）が原因となり、画質劣化を生じさせる虞があった。

【0007】

本発明は上述した課題に鑑みてなされてものであり、大画面・高精細・狭額縫の表示装

10

20

30

40

50

置を設計する際に課題となる、電源配線の高抵抗化に伴う輝度傾斜に対し、電源配線を配置可能なアレイ基板上の領域の制約を受けることなく、電源配線を低抵抗化し、画質向上を実現するOLED表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の一実施形態に係るOLED表示装置は、複数の制御信号線と複数のデータ信号線とが交差して配置された位置に複数の画素がマトリクス状に配置された第1基板と、前記第1基板と対向して配置される第2基板と、を備え、前記複数の画素の各々は、前記制御信号線から供給される制御信号に応じて前記データ信号線から供給されるデータ電圧が書き込まれる画素回路と、前記画素回路から前記データ電圧に応じた電流が供給される第1電極及び電源電圧が供給される第2電極を備えたOLED素子と、を含み、前記第1基板及び前記第2基板は、それぞれ複数の電源配線を備え、前記第1基板の前記複数の電源配線と前記第2基板の前記複数の電源配線とは、それぞれ導電性部材を介して接続され、前記複数の電源配線の各々は、前記OLED素子の前記第2電極に接続されることを特徴とする。

【0009】

また、前記第2基板の前記複数の電源配線は、前記第1基板の前記複数の画素が配置された表示領域と重畳しない位置に配置されてもよい。

【0010】

前記導電性部材は、前記第1基板の前記複数の画素が配置された表示領域と重畳しない位置に、前記第1基板と前記第2基板とを接続して配置されてもよい。

【0011】

前記導電性部材は、導電性樹脂又は異方性導電膜であってもよい。

【0012】

前記OLED素子の前記第2電極は、前記複数の画素に対応して一つ配置される共通電極であり、前記複数の電源配線と複数個所において接続されて前記電源電圧を給電されてもよい。

【発明の効果】

【0013】

本発明によれば、対向基板の額縁領域に電源配線を設けることにより、電源配線を配置可能なアレイ基板上の領域の制約を受けることなく、電源配線を低抵抗化して給電することができるため、電源配線の高抵抗化に伴う輝度傾斜を生じさせずに、画質を向上させることができ、且つ、大画面化、高精細化、狭額縁化が可能なOLED表示装置を提供することができる。

【図面の簡単な説明】

【0014】

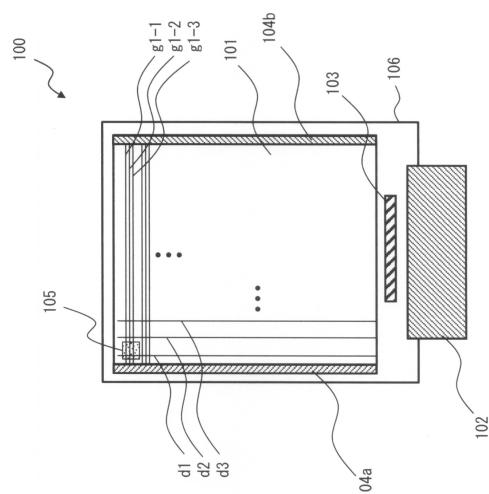

【図1】本発明の一実施形態に係るOLED表示装置の概略構成を示す平面図である。

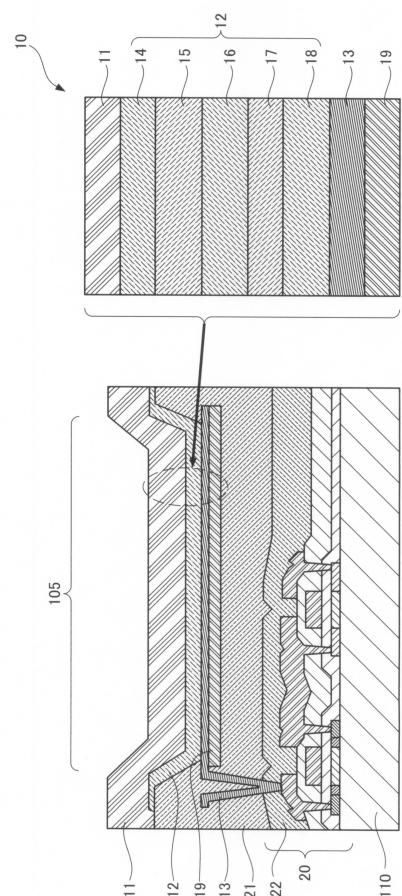

【図2A】本発明の一実施形態に係るOLED表示装置の画素の概略構成を示す断面図である。

【図2B】本発明の一実施形態に係るOLED表示装置に用いられる画素回路の一例を示す回路図である。

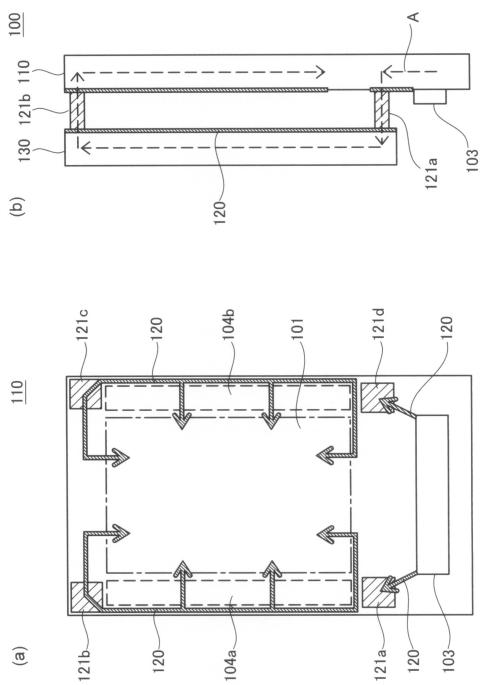

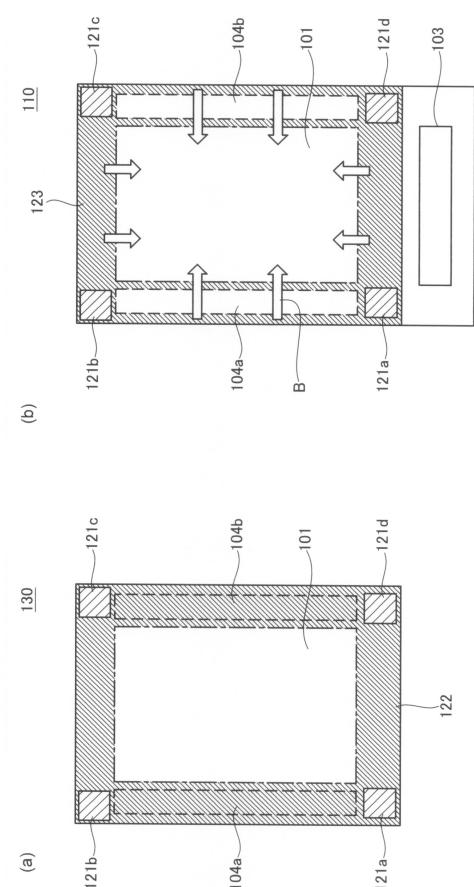

【図3】本発明の第1の実施形態に係るOLED表示装置の構成を説明するための図であり、(a)は、アレイ基板を示す平面図であり、(b)は、OLED表示装置を示す断面図である。

【図4】本発明の第1の実施形態に係るOLED表示装置の構成を説明するための図であり、(a)は、対向基板の平面図であり、(b)は、アレイ基板の平面図である。

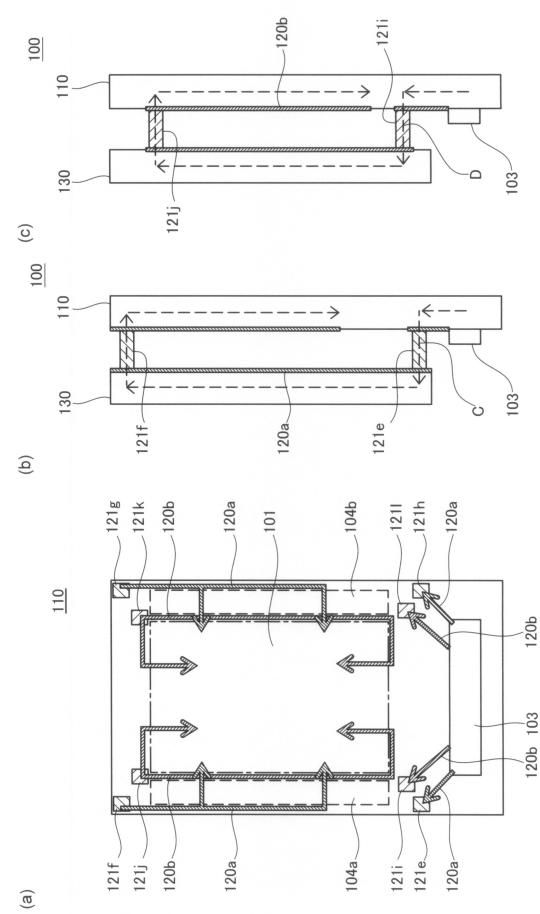

【図5】本発明の第2の実施形態に係るOLED表示装置の構成を説明するための図であり、(a)は、アレイ基板を示す平面図であり、(b)及び(c)は、OLED表示装置を示す断面図である。

【図6】本発明の第2の実施形態に係るOLED表示装置の構成を説明するための図であ

10

20

30

40

50

り、(a)は、対向基板の平面図であり、(b)は、アレイ基板の平面図である。

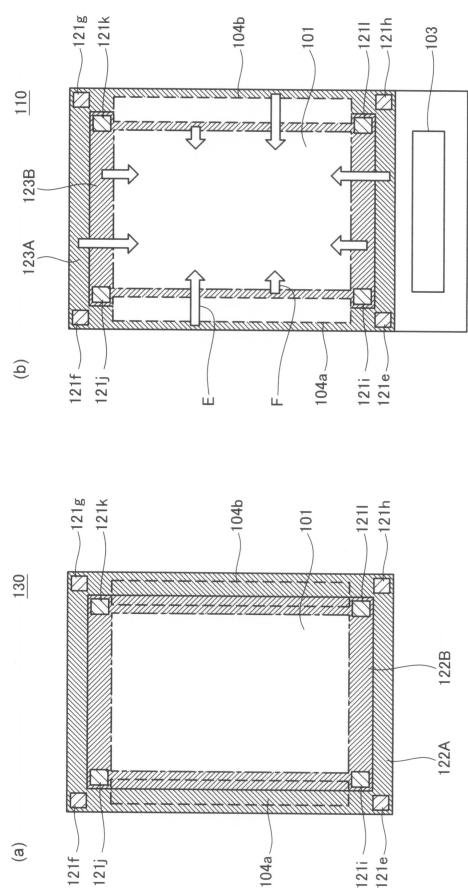

【図7】本発明の第3の実施形態に係るOLED表示装置の構成を説明するための図であり、(a)は、アレイ基板を示す平面図であり、(b)及び(c)は、OLED表示装置を示す断面図である。

【図8】本発明の第3の実施形態に係るOLED表示装置の構成を説明するための図であり、(a)は、対向基板の平面図であり、(b)は、アレイ基板の平面図である。

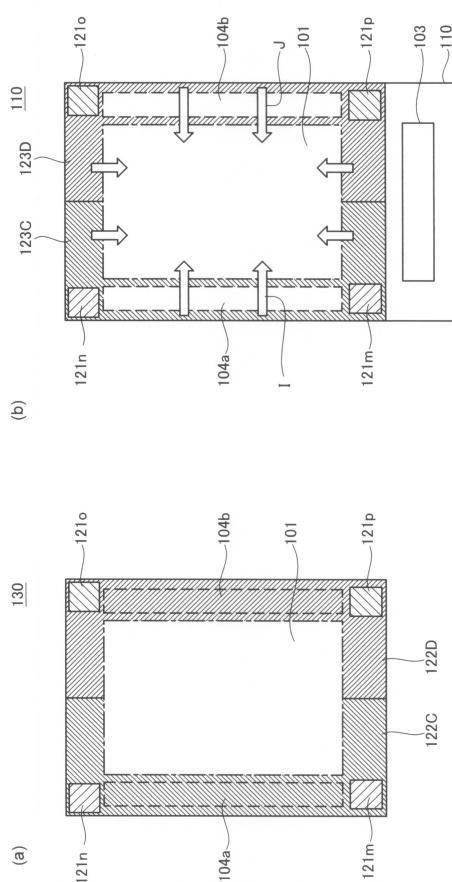

【図9】従来のOLED表示装置の構成を説明するための図であり、(a)は、アレイ基板を示す平面図であり、(b)は、OLED表示装置を示す断面図である。

【発明を実施するための形態】

【0015】

10

以下、図面を参照しながら、本発明のOLED表示装置の実施形態について説明する。なお、本発明のOLED表示装置は、以下の実施形態に限定されることはなく、種々の変形を行ない実施することが可能である。

【0016】

20

図1に、本発明の一実施形態に係るOLED表示装置100の概略構成を示す。本実施形態に係るOLED表示装置100は、基板110上に形成された、表示領域101、FPC(Flexible printed circuits)102、ドライバIC103、及び走査線駆動回路104aを備える。表示領域101には、図中の横方向に走る複数の制御信号線g1-1～g1-3と縦方向に走る複数のデータ信号線d1～d3とが互いに交差して配置され、制御信号線g1-1～g1-3とデータ信号線d1～d3との交差部に対応する位置に、複数の画素105がマトリクス状に配置される。図1には、一例として、一画素105あたり3本の制御信号線g1-1～g1-3と1本のデータ信号線d1とが交差して配置される構成を図示しているが、この構成に限定されるものではない。

【0017】

30

また、OLED表示装置100は、表示領域101を挟んで走査線駆動回路104aと対向する位置に、図1に図示したように、走査線駆動回路104a以外の周辺回路及び配線等が形成される領域104bを有していてもよい。走査線駆動回路104aとその他の周辺回路及び配線が形成される領域104bの位置は、図1に図示した位置に限定されず、いずれか一方の位置にのみ形成されるものであってもよい。また、以下、走査線駆動回路104a、及び他の周辺回路等が形成される領域104bについて、周辺回路領域104a、104bという。

【0018】

各画素105には、データ信号線d1～d3から供給されるデータ電圧を保持するコンデンサと、制御信号線g1-1～g1-3から供給される制御信号に応じて各画素105に供給されるデータ電圧の書き込みを制御することにより各画素105の発光を制御する薄膜トランジスタとを備えた画素回路が配置される。

【0019】

以下、図2A及び図2Bを参照し、画素105の構成についてより詳細に説明する。

【0020】

40

図2Aは、本発明の一実施形態に係るOLED表示装置100に用いられる画素105の概略構成を示す断面図である。図2Bは、本発明の一実施形態に係るOLED表示装置100に用いられる画素回路20の一例を示した回路図である。

【0021】

図2Aに図示したように、画素105は、基板110上に形成された画素回路20と、画素回路20上に絶縁膜22及び平坦化膜21を介して形成されたOLED素子10とを含む。OLED素子10は、反射膜19上に形成されたアノード(陽極)13と、アノード13上に形成された、ホール注入層(HIL)18、ホール輸送層(HTL)17、発光層(EML)16、電子輸送層(ETL)15、及び電子注入層(EIL)14が順次積層されて構成される有機EL(Organic Electro-Luminescence)層12と、有機EL

50

層12上に形成されたカソード(陰極)11と、を備える。アノード13は、画素105ごとに配置され、有機EL層12に電流を供給して発光を制御する電極である。また、カソード11は、全ての画素105に対応して一つ配置され、共通電極として機能する電極である。なお、図2Aに図示した画素回路20を備えたOLED表示装置100は、トップエミッション型のOLED表示装置を構成するため、カソード11は、有機EL層12から出射される光を透過させるように透光性を有する材料を用いて形成される。

#### 【0022】

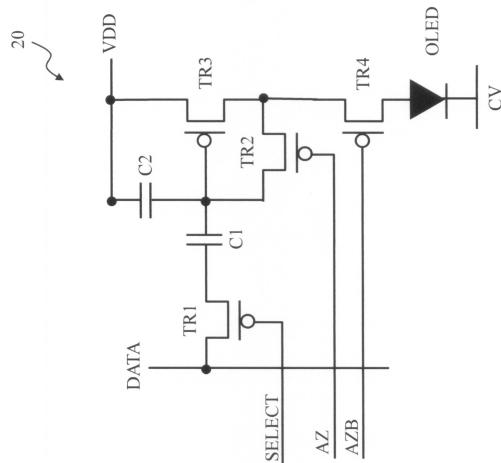

図2Bに図示したように、各画素105の画素回路20は、4つのトランジスタTR1～TR4と、2つのコンデンサC1、C2と、OLED素子10(図2Bに示したOLED)とを備えるものであってもよい。トランジスタTR1は、ソースがデータ電圧ラインDATA(図1に示したデータ信号線d1)に接続され、ドレインがコンデンサC1の一方の電極に接続され、ゲートが走査電極ラインSELLECT(図1に示した制御信号線g1-1)に接続される。トランジスタTR2は、ソースがコンデンサC1の他方の電極、コンデンサC2の一方の電極、及びトランジスタTR3のゲートに共通接続されているとともに、ドレインがトランジスタTR3のドレインとトランジスタTR4のソースに共通接続され、ゲートが制御信号ラインAZ(図1に示した制御信号線g1-2)に接続される。トランジスタTR4は、ドレインがOLED素子10のアノード13に接続され、ゲートが制御信号ラインAZB(図1に示した制御信号線g1-3)に接続される。トランジスタTR3のソース及びコンデンサC2の他方の電極には第1電源電圧が印加され、OLED素子10のカソード11には第2電源電圧が印加される。本発明の実施形態では、第1電源電圧はアノード電圧VDDとし、第2電源電圧はカソード電圧CVとした。また、カソード電圧CVには基準電圧又は負電圧が用いられる。

#### 【0023】

このような構成を備える画素回路20は、トランジスタTR3の動作しきい値電圧のばらつきを補正した後、コンデンサC1、C2等に電圧を保持させることにより、データ電圧ラインDATAから供給されるデータ電圧に応じた輝度でOLED素子10を発光させることができるように構成されている。このため、図2Bに図示した構成を備える画素回路20は、トランジスタの特性ばらつきや電源電圧の降下等が表示に直接的に現れてしまうOLED表示装置等に用いられている。

#### 【0024】

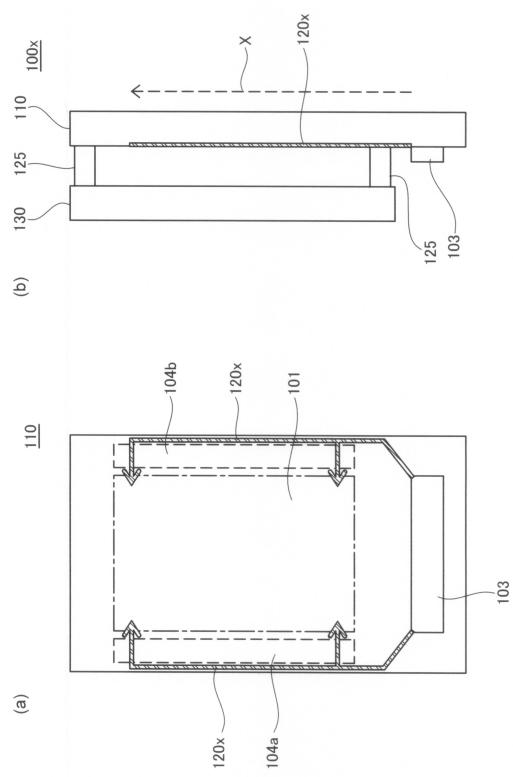

このような画素回路20を備えた従来のOLED表示装置100xの構成について、以下、図9を参照して説明する。図9は、従来のOLED表示装置100xの構成を説明するための図であり、(a)は、アレイ基板110を示す平面図であり、(b)は、OLED表示装置100xを示す断面図である。なお、従来のOLED表示装置100xについて、図1を参照して上述したOLED表示装置100と同じ構成については同じ符号を付し、その説明を省略する。

#### 【0025】

図9に図示した従来のOLED表示装置100xは、OLED表示装置100と同様に、複数の画素105を含む表示領域101、周辺回路領域104a、104b、及びドライバIC103を備えた基板110(以下、「アレイ基板110」という。)と、アレイ基板110にシール材125等を介して貼り合される対向基板130とを含む。アレイ基板110及び対向基板130は、いずれもガラス基板を用いて形成されたものであってもよい。また、対向基板130は、カラーフィルタを含むものであってもよく、タッチパネル機能を備えた薄膜デバイス等であってもよい。

#### 【0026】

図9に図示したように、従来のOLED表示装置100xにおいては、例えばドライバIC103のような電源から、表示領域101に配置されたカソード11に、アレイ基板110に配置された電源配線120xを介して電源電圧が供給される。なお、電源は、図9に図示したドライバIC103から給電される構成に限らず、外部電源(図示せず)から給電される構成であってもよい。また、図9に図示した120xは、電源配線120x

10

20

30

40

50

の電流経路を簡略化して図示したものであり、図9(a)に図示した電源配線120xの矢印の方向、及び図9(b)に点線で図示した矢印Xの方向は、電源電圧の伝達方向を図示したものである。図9(a)には、カソード11の配置位置を図示していないが、カソード11は、表示領域101内において全ての画素105を覆うように配置されて共通電極として機能する。従って、図9(a)に図示した構成は一例に過ぎないが、カソード11は、電源配線120xの矢印が表示領域101内において示すように、複数の個所において電源配線120xと接続され、電源電圧を給電されてもよい。なお、図9(a)は、電源配線120xが、矩形の表示領域101における4隅からカソード11に接続された構成を図示したものである。

## 【0027】

10

図9(a)に図示したように、表示領域101のカソード11に接続される電源配線120xは、アレイ基板110上において、図9(a)に点線で図示した表示領域101及び周辺回路領域104a、104bを除いた領域に配置される。このとき、電源配線120xは、表示領域101の全体にわたっていずれの画素105にも一様に、且つ過不足なく電源電圧を供給することが求められる。このため、電源配線120xを低抵抗化する必要がある。

## 【0028】

20

しかしながら、従来のOLED表示装置100xにおいて、電源配線120xは、アレイ基板110上の表示領域101及び周辺回路領域104a、104bを除いた余白領域に配置せざるを得ず、その配線幅に制約を受けるものであった。また、大画面化による配線長増加、高精細化による電源配線120x以外の回路の複雑化及び肥大化、及び狭額縁化による配線領域の縮小化等に伴い、配線幅の制約はますます大きくなる傾向があり、低抵抗化が難しい状況であった。一方、配線の複線化や多層化することにより一定の低抵抗効果は得られるものの、構造が複雑化し、表示性能の改善効果にも限界があった。そこで、本発明者は、電源配線120xの高抵抗化に伴う輝度傾斜を生じさせずに、画質向上させることができ、且つ、大画面化、高精細化、狭額縁化を実現可能なOLED表示装置の構成を検討し、本発明に至った。

## 【0029】

## &lt;第1の実施形態&gt;

以下、図3及び図4を参照し、本発明の第1の実施形態に係るOLED表示装置100の構成について説明する。図3は、本発明の第1の実施形態に係るOLED表示装置100の構成を説明するための図であり、(a)は、アレイ基板110を示す平面図であり、(b)は、OLED表示装置100を示す断面図である。図4は、本発明の第1の実施形態に係るOLED表示装置100の構成を説明するための図であり、(a)は、対向基板130の平面図であり、(b)は、アレイ基板110の平面図である。なお、以下、図9を参照して上述した従来のOLED表示装置100xと同じ構成については同じ符号を付し、その説明を省略する。

## 【0030】

30

図3に図示したように、第1の実施形態に係るOLED表示装置100は、複数の画素105を含む表示領域101、周辺回路領域104a、104b、及びドライバIC103を備えたアレイ基板110と、アレイ基板110にシール材125(図3に図示せず)等を介して貼り合される対向基板130とを含む。また、第1の実施形態に係るOLED表示装置100は、アレイ基板110と対向基板130との間に、導電性部材121a～121dが配置され、アレイ基板110上に形成された電源配線120と、対向基板130上に形成された電源配線120とが、導電性部材121a～121dを介して導通される。

## 【0031】

40

電源配線120は、公知の材料を用いて形成することができ、ITOを用いて形成してもよく、アルミ、金、銀、銅等を用いて形成してもよい。導電性部材121a～121dには、例えば、導電性樹脂や異方性導電膜(ACF)を用いる。なお、図3(a)には、

50

説明の便宜上、導電性部材 121a～121d の内側を電源配線 120 が通過するように図示しているが、実際には、アレイ基板 110 及び対向基板 130 にそれぞれ形成された電源配線 120 上に導電性部材 121a～121d が形成され、導電性部材 121a～121d を介してアレイ基板 110 と対向基板 130 とが接続されるように構成される。また、電源配線 120 及び導電性部材 121a～121d の配置される位置は、後述するように、図 3 に図示した構成に限定されるものではない。

#### 【 0 0 3 2 】

図 3 (a) に図示した電源配線 120 の矢印の方向及び図 3 (b) に点線で図示した矢印 A の方向は、カソード電源電圧の伝達方向を示している。カソード電源電圧は、アレイ基板 110 上のドライバ I C 103 から、アレイ基板 110 上の電源配線 120 に伝達された後、導電性部材 121a、121d を介して対向基板 130 上の電源配線 120 に伝達され、さらに導電性部材 121b、121c を介してアレイ基板上の電源配線 120 に伝達され、表示領域 101 のカソード 11 に給電される。

#### 【 0 0 3 3 】

電源配線 120 は、図 4 (a) に図示したように、対向基板 130 上においては、表示領域 101 と重畠しない対向基板 130 の額縁領域である領域 122 に配置することができる。従って、対向基板 130 の額縁領域の幅を最大限利用して電源配線 120 の配線幅を決定することができ、電源配線 120 の低抵抗化を図ることが可能となる。また、電源配線 120 は、図 4 (b) に図示したように、アレイ基板 110 上においては、表示領域 101 及び周辺回路領域 104a、104b を除いた余白領域 123 のいずれの位置に配置されてもよい。これにより、カソード電源電圧を、図 4 (b) に矢印 B として電源電圧の伝達方向を図示したように、矩形の表示領域 101 の 4 辺からいずれの位置に配置された画素 105 に対しても偏りがないように低抵抗給電することが可能となる。従って、電源側に位置する表示領域 101 の近端部と、電源と対向する位置にある表示領域 101 の遠端部とで輝度傾斜が生じないように給電することができ、OLED 表示装置 100 の画質劣化を低減させることができるとなる。

#### 【 0 0 3 4 】

なお、電源配線 120 は、図 3 及び図 4 に図示したアレイ基板 110 と対向基板 130 とに敷設して導電性部材 121a～121d を介して接続する電源配線 120 の構成に、図 9 に図示したアレイ基板 110 のみに敷設する電源配線 120x の構成を組み合わせて構成してもよい。

#### 【 0 0 3 5 】

また、図 3 (a) には、対向基板 130 のアレイ基板 110 と対向する側の面上に電源配線 120 が配置される構成を図示しているが、図示した構成に限定されず、対向基板 130 のアレイ基板 110 と対向しない側の面上に電源配線 120 が配置されてもよい。例えば、対向基板 130 がカラーフィルタ基板である場合には、カラーフィルタを含む積層膜を覆う保護膜上に電源配線 120 が配置されてもよい。

#### 【 0 0 3 6 】

また、図 3 及び図 4 には、導電性部材 121a～121d が表示領域 101 を囲む額縁状の領域 122、123 の 4 隅に配置された構成を図示しているが、OLED 表示装置 100 の狭額縁化との兼ね合いで、導電性部材 121a～121d の数は 4 つに限らず 1 つ以上の複数であってもよく、配置位置についても電源配線 120 が配置可能な領域 122、123 であればいずれの位置に配置されてもよい。

#### 【 0 0 3 7 】

以上のように、本発明の第 1 の実施形態に係る OLED 表示装置 100 によれば、アレイ基板 110 上に形成された電源配線 120 と対向基板 130 上に形成された電源配線 120 とを、導電性部材 121a～121d を介して接続し、且つ、対向基板 130 上の額縁領域 122 を利用して電源配線 120 を低抵抗化するように構成することにより、アレイ基板 110 上での配線幅制約を受けずに、電源配線 120 を低抵抗化することが可能となる。

10

20

30

40

50

## 【0038】

従って、本発明の第1の実施形態に係るOLED表示装置100によれば、電源配線120の高抵抗化に伴う輝度傾斜を生じさせずに画質を向上させることができ、且つ、大画面・高精細・狭額縁のOLED表示装置100を実現できる。

## 【0039】

## &lt;第2の実施形態&gt;

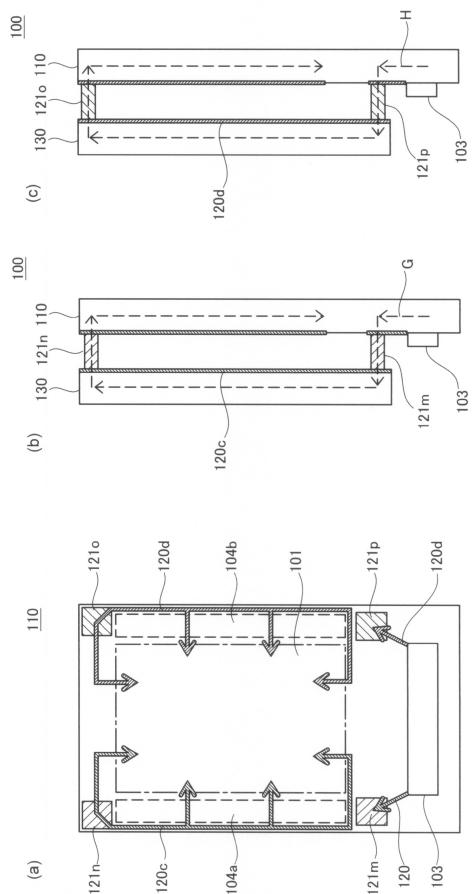

以下、図5及び図6を参照し、本発明の第2実施形態に係るOLED表示装置100の構成について説明する。図5は、本発明の第2の実施形態に係るOLED表示装置100の構成を説明するための図であり、(a)は、アレイ基板110を示す平面図であり、(b)及び(c)は、OLED表示装置100を示す断面図である。図6は、本発明の第2の実施形態に係るOLED表示装置100の構成を説明するための図であり、(a)は、対向基板130の平面図であり、(b)は、アレイ基板110の平面図である。なお、以下、図3及び図4を参照して上述した第1の実施形態に係るOLED表示装置100と同じ構成については同じ符号を付し、その説明を省略する。

## 【0040】

第2の実施形態に係るOLED表示装置100は、図5及び図6に図示したように、アレイ基板110及び対向基板130にそれぞれ配置された2つの電源配線120a、120bと、8つの導電性部材121e～121hとを備える。第2の実施形態に係るOLED表示装置100は、電源配線120a、120bを複線化することにより、複数電源の低抵抗給電を実現しようとするものである。

10

20

## 【0041】

図5及び図6に図示したように、アレイ基板110上に配置された電源配線120aは、アレイ基板110及び対向基板130の額縁領域のうち外縁側の領域122A、123Aに配置された導電性部材121e～121hを介して、対向基板130に配置された電源配線120aと接続される。また、アレイ基板110上に配置された電源配線120bは、アレイ基板110及び対向基板130の額縁領域のうち表示領域101に近い側の領域122B、123Bに配置された導電性部材121e～121hを介して、対向基板130に配置された電源配線120aと接続される。

## 【0042】

このような構成を備えることにより、第2の実施形態に係るOLED表示装置100は、図5(b)及び(c)に点線で示したカソード電源電圧の伝達方向を表す矢印C、Dのように、カソード電源電圧を、アレイ基板110上のドライバIC103から、アレイ基板110上の電源配線120a、120bにそれぞれ伝達した後、導電性部材121e、121h又は導電性部材121i、121lを介して対向基板130上の電源配線120a、120bにそれぞれ伝達し、さらに導電性部材121f、121g又は導電性部材121j、121kを介してアレイ基板110上の電源配線120a、120bにそれぞれ伝達し、表示領域101のカソード11に給電する構成を備える。なお、図示していないが、複数の電源配線120a、120bの接続先はカソード11に限定されるものではなく、他の電源供給用途に電源配線120a、120bを用いてもよい。

30

## 【0043】

以上のように、本発明の第2の実施形態に係るOLED表示装置100は、対向基板130上の額縁領域122A、122Bを利用して電源配線120a、120bをそれぞれ低抵抗化するように構成することにより、図6(b)に電源電圧の伝達方向を示す矢印E、Fとして図示したように、電源電圧を矩形の表示領域101の4辺から各画素105にに対して偏りなく低抵抗給電することができる。

40

## 【0044】

従って、本発明の第2の実施形態に係るOLED表示装置100によれば、電源配線120a、120bを複線化した場合にも、第1の実施形態に係るOLED表示装置100と同様に、対向基板130上の額縁領域122A、122Bを利用して電源配線120a、120bをそれぞれ低抵抗化することができるため、輝度傾斜を生じさせずに表示領域

50

101の各画素105に電源電圧を給電することができる。

【0045】

<第3の実施形態>

以下、図7及び図8を参照し、本発明の第3実施形態に係るOLED表示装置100の構成について説明する。図7は、本発明の第3の実施形態に係るOLED表示装置100の構成を説明するための図であり、(a)は、アレイ基板110を示す平面図であり、(b)及び(c)は、OLED表示装置100を示す断面図である。図8は、本発明の第2の実施形態に係るOLED表示装置100の構成を説明するための図であり、(a)は、対向基板130の平面図であり、(b)は、アレイ基板110の平面図である。なお、以下、図3乃至図6を参照して上述した第1及び第2の実施形態に係るOLED表示装置100と同じ構成については同じ符号を付し、その説明を省略する。

【0046】

第3の実施形態に係るOLED表示装置100は、図7及び図8に図示したように、アレイ基板110及び対向基板130にそれぞれ配置された2つの電源配線120c、120dと、4つの導電性部材121m～121pとを備える。第3の実施形態に係るOLED表示装置100は、第2の実施形態に係るOLED表示装置100と同様に、複数電源の低抵抗給電を実現しようとするものである。

【0047】

第3の実施形態に係るOLED表示装置100は、図7(b)及び(c)に点線で示したカソード電源電圧の伝達方向を表す矢印G、Hのように、カソード電源電圧を、アレイ基板110上のドライバIC103から、アレイ基板110上の電源配線120c、120dにそれぞれ伝達した後、それぞれ導電性部材121m、121pを介して対向基板130上の電源配線120c、120dにそれぞれ伝達し、さらにそれぞれ導電性部材121n、121oを介してアレイ基板110上の電源配線120c、120dにそれぞれ伝達し、表示領域101のカソード11に給電する構成を備える。なお、第2の実施形態に係るOLED表示装置100と同様に、複数の電源配線120c、120dの接続先はカソード11に限定されるものではなく、他の電源供給用途に電源配線120c、120dを用いてもよい。

【0048】

図8に図示したように、電源配線120c、120dは、それぞれ対向基板130及びアレイ基板110において、表示領域101を囲む額縁領域のうち中央部を境に左側の領域123C、123Cと右側の領域122D、123Dとにそれぞれ配置される。従って、左側の領域123C、123Cと右側の領域122D、123Dとで異なる電源配線120c、120dを配置することにより、表示領域101の左側の画素105と右側の画素105とで異なる電源電圧を供給することも可能となる。また、図8(b)に電源電圧の伝達方向を示す矢印I、Jとして図示したように、電源電圧を矩形の表示領域101の4辺から各画素105に対して偏りなく低抵抗給電することも可能となる。

【0049】

なお、図8には、表示領域101を囲む額縁領域のうち中央部を境に左側の領域123C、123Cと右側の領域122D、123Dとに分け、電源配線120c、120dがそれぞれ配置される構成を図示したが、図示した中央部を境とする構成に限定されるものではなく、電源配線120c、120dの配置位置は仕様に応じて適宜変更され得る。

【0050】

以上のように、本発明の第3の実施形態に係るOLED表示装置100によれば、対向基板130上の額縁領域122C、122Dを利用して電源配線120c、120dをそれぞれ低抵抗化するように構成することにより、電源配線120c、120dを複線化した場合にも、第1及び第2の実施形態に係るOLED表示装置100と同様に、輝度傾斜を生じさせずに表示領域101の各画素105に電源電圧を給電することが可能となる。

【0051】

以上のとおり、本発明の第1乃至第3の実施形態に係るOLED表示装置100によれ

10

20

30

40

50

ば、対向基板 130 の額縁領域に電源配線 120、120a～120d を設けることにより、電源配線 120、120a～120d を配置可能なアレイ基板 110 上の領域の制約を受けることなく、電源配線 120、120a～120d を低抵抗化して給電することができるため、電源配線 120、120a～120d の高抵抗化に伴う輝度傾斜を生じさせずに、画質を向上させることができ、且つ、狭額縁化された OLED 表示装置を提供することができる。

## 【符号の説明】

## 【0052】

100 OLED 表示装置

101 表示領域

10

103 ドライバ IC

104a、104b 周辺回路領域

105 画素

110 アレイ基板

120、120a～121d 電源配線

121a～121p 導電性部材

130 対向基板

10 OLED 素子

11 カソード

13 アノード

20

20 画素回路

【図1】

【図2A】

## 【図2B】

【 3 】

【 四 4 】

【 図 5 】

【図6】

【図8】

【図7】

【図9】

---

フロントページの続き

| (51)Int.Cl.  |              | F I              |              |              |

|--------------|--------------|------------------|--------------|--------------|

| <i>H 01L</i> | <i>51/50</i> | <i>(2006.01)</i> | <i>G 09G</i> | <i>3/30</i>  |

| <i>H 05B</i> | <i>33/04</i> | <i>(2006.01)</i> | <i>G 09G</i> | <i>3/20</i>  |

|              |              |                  | <i>G 09F</i> | <i>9/30</i>  |

|              |              |                  | <i>G 09F</i> | <i>9/30</i>  |

|              |              |                  | <i>H 05B</i> | <i>33/12</i> |

|              |              |                  | <i>H 05B</i> | <i>33/14</i> |

|              |              |                  | <i>H 05B</i> | <i>33/04</i> |

- (56)参考文献 特開2006-215550 (JP, A)

特開2010-145661 (JP, A)

特開2010-212108 (JP, A)

特開2008-311239 (JP, A)

特開2006-309223 (JP, A)

特開2007-234706 (JP, A)

特開2005-173579 (JP, A)

## (58)調査した分野(Int.Cl., DB名)

*G 09F 9/30 - 9/46*

*G 09G 3/00 - 3/34, 3/38*

*H 01L 27/32, 51/50*

*H 05B 33/00 - 33/28*