(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.<sup>6</sup>

H01L 27/115

(45) 공고일자 1999년03월20일

(11) 등록번호 특0184632

(24) 등록일자 1998년12월21일

(21) 출원번호

특1995-008330

(65) 공개번호 특1995-034805

(22) 출원일자

1995년04월11일

(43) 공개일자 1995년12월28일

(30) 우선권주장

237,761 1994년05월04일 미국(US)

(73) 특허권자

니쁜 프레시즌 써키츠 가부시끼 가이샤 다부찌 노리오

일본 도오꼬도 죠오꾸 교바시 2죠메 6반 21고제임스 티. 첸

미국 캘리포니아 95014 세인트 앤드류스 애비뉴 쿠파르티노 22409

(72) 발명자

제임스 티. 첸

미국 캘리포니아 95014 세인트 앤드류스 애비뉴 쿠파르티노 22409

야기 아쯔오

일본 도찌기켄 나스꾼 시오바라마찌 오아자 시모따노 531-1 니쁜 프레시즌

써키츠 가부시끼 가이샤 나이

(74) 대리인

이병호, 최달용

**심사관 : 임동우****(54) 반도체 소자와 그 제조방법****요약**

이중층의 부유 게이트를 포함하는 우수한 셀 신뢰도를 갖는 본 발명의 반도체 메모리 셀은 부유 게이트의 얇은 상부층이 이 층을 둘러싸는 필드 절연 영역들의 모서리를 덮고 있으며, 누출 문제를 최소화하기 위해 둥글게 된 모서리를 갖는다. 이중층의 부유 게이트를 기판으로부터 분리시키는 터널 절연체는 필드 절연 영역들의 형성 이전에 성장되는 균일 두께의 층을 포함한다. 프로그래밍 공정 순서에서 본 발명의 셀들을 프로그래밍하고 소거하는 데에는 파울러 노르드하임 터널링 메카니즘이 사용되며, 이 공정 순서는 워드라인상의 모든 셀을 플래시 프로그래밍 하는 단계와, 선택된 셀상의 전류를 감지하는 단계 및 감지된 전류가 소망 값에 될 때까지 워드라인이 아닌 비트라인상에 고전압을 인가하여 셀상의 전하를 선택자으로 소거하는 단계를 포함한다.

**대표도****명세서**

[발명의 명칭]

반도체 소자와 그 제조방법

[도면의 간단한 설명]

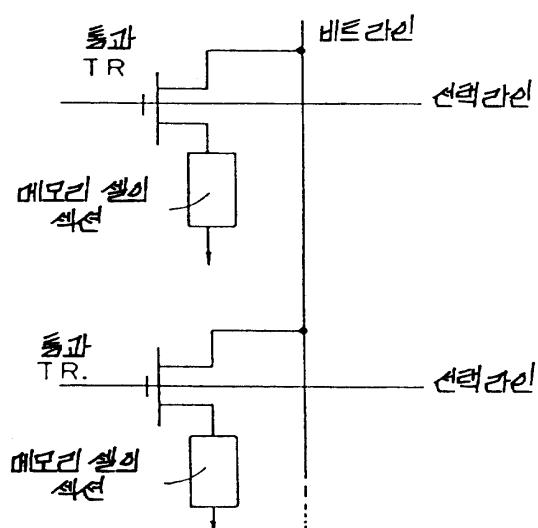

제1도는 다중 셀 메모리 어레이의 세그먼트를 나타낸 도면.

제2a 및 2b도는 종래기술에 따른 메모리 셀용 적층 게이트 및 분할 게이트의 종단면을 비트라인 투시도를

따라 나타낸 종단면도.

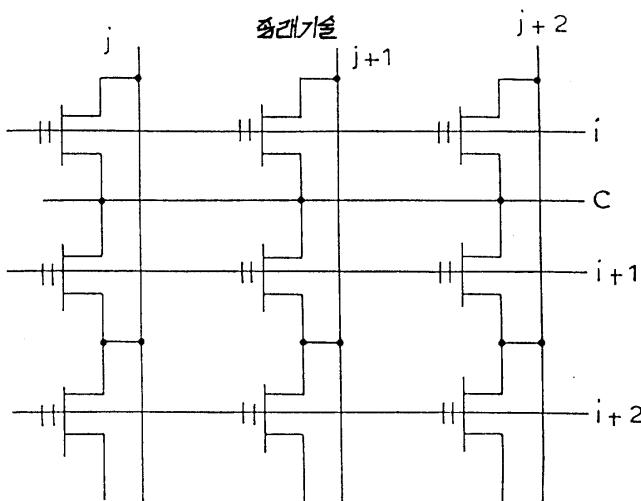

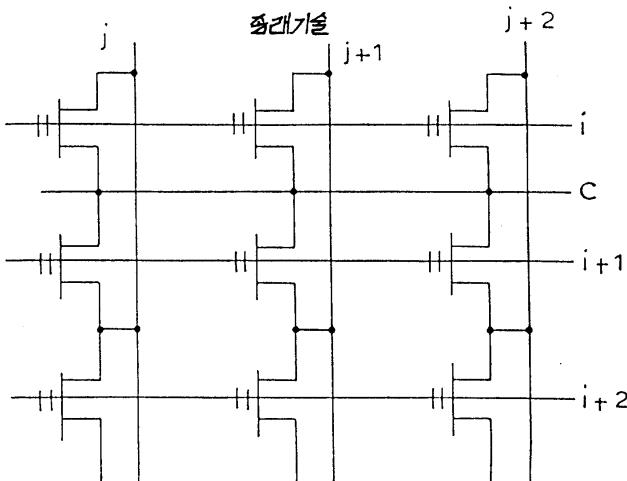

제3도는 종래. 기술에 따른 적층 게이트 메모리 셀의 워드라인도면.

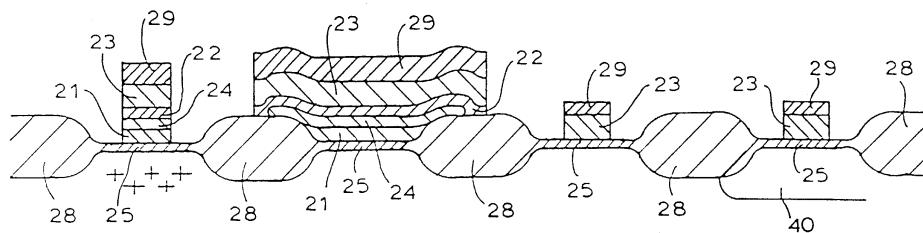

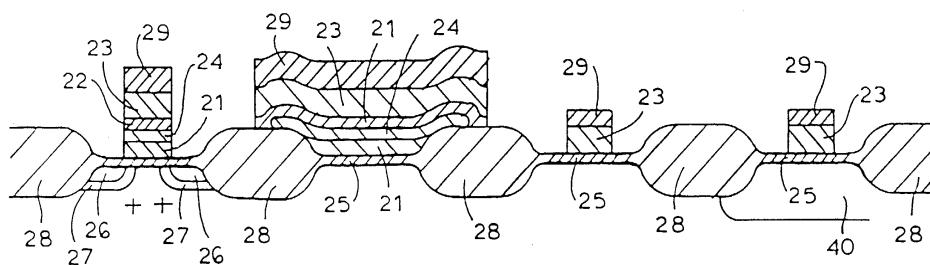

제4a 및 4b도는 각각 워드라인 및 비트라인을 따라 도시한 본 발명의 적층 게이트 메모리 셀 소자의 도면.

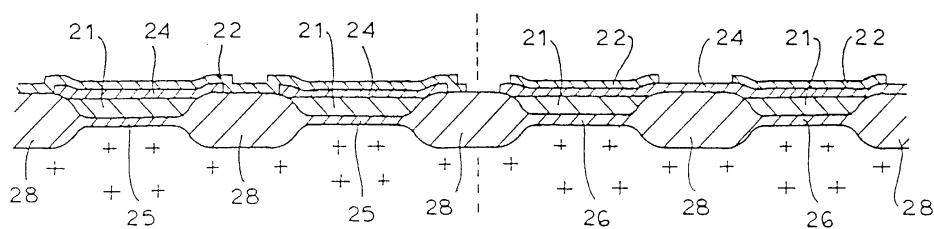

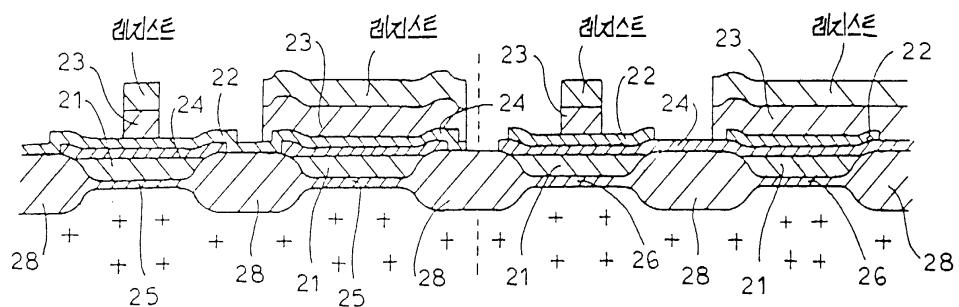

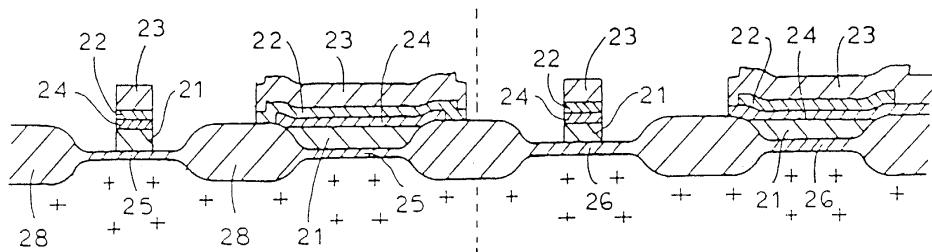

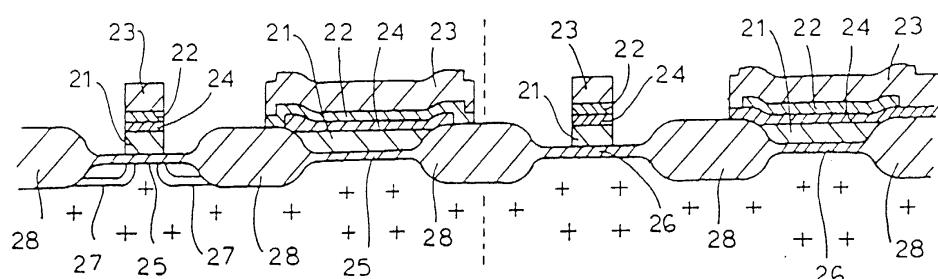

제5a 및 5j도는 본 발명의 메모리 셀 구조가 제조되는 공정순서를 나타낸 도면.

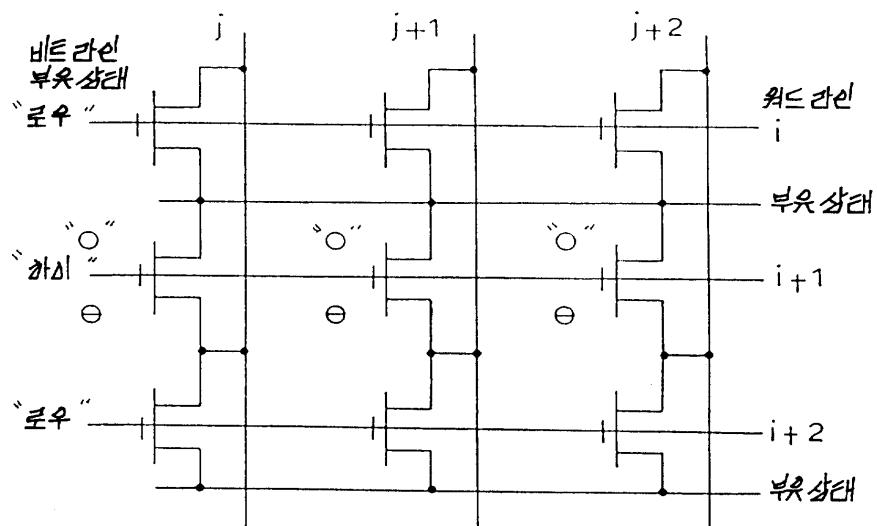

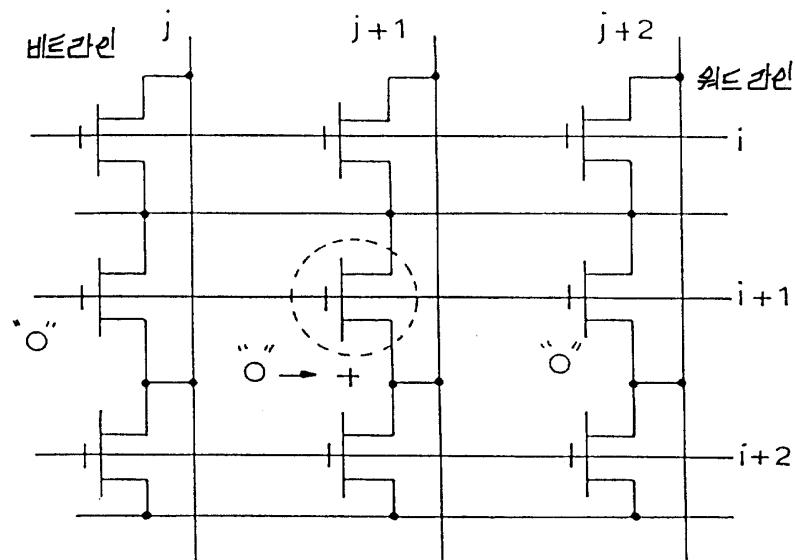

제6a 내지 6c도는 본 발명에 따라 이루어지는 바이트 레벨의 메모리 셀 프로그래밍 및 소거 기능을 나타내는 도면.

제7도는 메모리 어레이를 더 작은 섹터 또는 블럭들로 분할하는 것에 대한 도면.

제8도는 본 발명의 일 실시예에 따라 동시에 형성되는 주변소자의 전형적인 배치도.

제9a 및 9j도는 메모리 셀 제조와 동시에 주변 소자를 형성시키기 위한 대안적 공정 순서를 나타낸 도면.

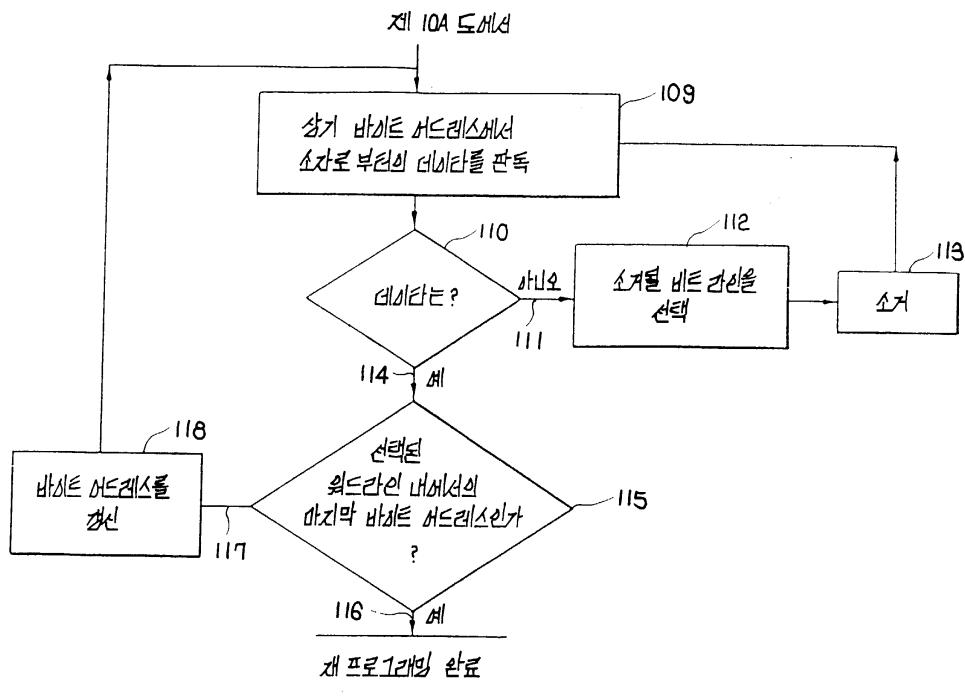

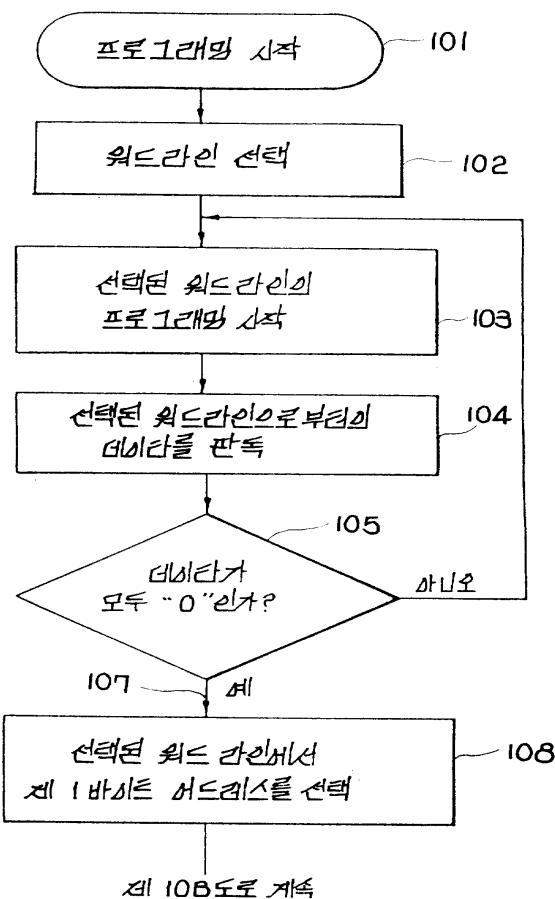

제10a 및 10b도는 본 발명의 대표적 공정 순서도.

#### \* 도면의 주요부분에 대한 부호의 설명

|              |                |

|--------------|----------------|

| 20 : 기판      | 22 : 폴리간 절연층   |

| 23 : 제어 게이트  | 24 : 폴리 1층     |

| 25 : 터널 산화물층 | 26 : 제1도편트     |

| 27 : 제2도편트   | 28 : 필드 산화물 영역 |

| 30 : 소스 영역   | 31 : 드레인 영역    |

#### [발명의 상세한 설명]

본 발명은 일반적으로 반도체 메모리 소자의 제조 및 이용에 관한 것으로, 특히 본 발명의 공정 순서를 사용하여 고유한 단일 트랜지스터 EEPROM을 제조하는 것에 관한 것이다. 또한, 본 발명의 메모리 어레이는 공통 워드라인을 공유하는 메모리 셀을 플래시 프로그래밍(flash programming)하고, 파울러-노르드하임 터널링(Fowler-Nordheim tunneling)을 통해 각 메모리 셀을 선택적으로 소거 가능케 하도록 제공된다.

반도체 산업에서, 비휘발성 반도체 메모리는 긴급한 프로그램과 컴퓨터, 전기 통신, 산업 및 의료용 기구 등과 같은 전자 시스템에 필수적인 데이터를 저장하는데 사용된다.

비휘발성 메모리는 관련 기술에 따라 여러 형태로 나누어지는데, 즉 제조자에 의해 1회 프로그램 되는 ROM(read-only memory)과; 사용자에 의해 1회 프로그램 될 수 있는 PROM(programmable read-only memory)과; 소자상의 UV(자외선)노출의 누적 효과 및 소자의 신뢰도가 주어지는 경우, 사용자에 의해 일반적으로 1백회 이하로 프로그램, UV 소거 및 재프로그래밍 될 수 있는 EPROM(erasable programmable read-only memory); 및 사용자에 의해 대략 1,000-1,000,000회 정도 프로그램 및 전기적인 소거가 가능한 EEPROM(electrically erasable programmable read-only memory)으로 대별된다.

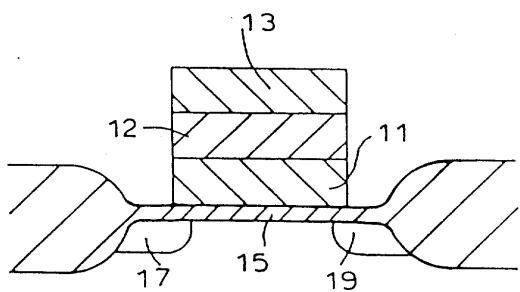

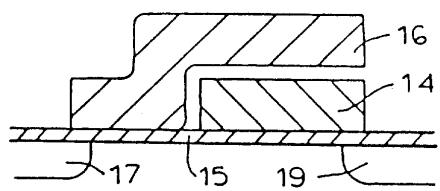

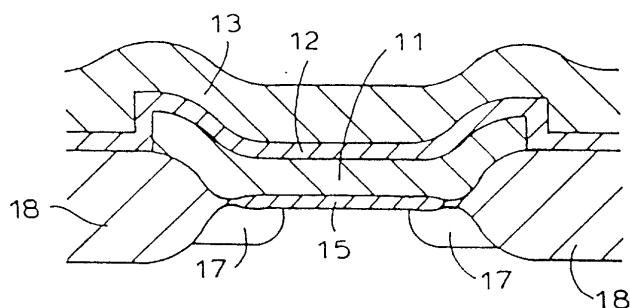

소위 플래시 메모리(flash memory)는 고집적 제조용 EEPROM의 구현물로 구성되는데, 이 메모리는 바이트 레벨이 아닌 블록 또는 섹터 단위로 전기적으로 소거될 수 있다. 제1도는 워드라인 및 비트라인을 따라 연결되는 다수의 메모리 셀들로 구성되는 메모리 어레이를 도시하고 있다. 이 어레이의 블록 또는 섹터들은, 예를 들어 공통 소스 라인을 따라 존재하는 모든 셀들과 같은 것으로 정의된다. 플래시 메모리 기술은 적층게이트(stacked gate) 또는 분할/계단 게이트(split/step gate) 셀 종단면적 (제 2a 및 2b도에 도시됨)으로 실현되는 보다 작은 셀크기로 인하여, 고 집적도를 이룰수 있다. 제2a도는 부유게이트(floating gate)(11)와 제어 게이트(13)를 갖는 적층게이트 메모리 셀 종단면을 나타내고 있으며, 이들은 적당한 도핑 재료로 도핑되는 다결정 실리콘으로부터 제조되어, 다결정실리콘(각각 폴리 1 및 폴리 2)이 도전성을 띄게 만든다.

부유 게이트는 절연 재료로된 산화물층(15)에 의해 기판 영역과 전기적으로 분리된다. 이 중간 산화물층은 특정 소자에 따라 게이트 또는 터널 산화물로 표기된다. 여기에서 당업자들이라면, 제조 단계를 상세화하기 위하여 이후 터널산화물(tunnel oxide)이 터널과 관련 게이트 산화물 모두를 고유하게 포함하는 것으로 이해할 것이다. 제2a도는 기판내의 채널을 규정하는 확산된 소스 및 드레인 영역(17, 19)을 추가로 도시하고 있다. 부유 게이트와 제어 게이트는 일반적으로 실리콘 이산화물의 폴리간층(interpoly layer)인 절연 재료로된 층에 의해 분리된다. 동작에 있어서, 전자들은 부유 게이트에서 전기 용량방식으로 저장된다. 이와 유사하게 제2b도의 분할게이트 종단면에는 부유 폴리 실리콘 게이트(14)와 제어 게이트(16)(각각 폴리 1과 폴리 2)가 포함되며, 이들은 폴리간 유전체(절연체)로 분리된다.

적층 게이트 종단면은 보다 작은 치수라는 분명한 장점을 지니지만, 과 소거(over-erasing)되기 쉽기 때문에, 셀들이 부의 임계 전압에 노출될때 즉시 공핍형 메모리 소자로 된다. 반면, 분할 게이트 종단면은 셀의 신뢰도면에서 우수하지만, 적층 게이트 셀 보다 더 큰 표면 영역이 필요하다. 적층 게이트 종단면의 셀 신뢰도 문제는 당분야의 현행 공정표준에 따라 제조되는 적층 게이트 종단면에 내재하는 셀구조상의 특성에 기인한다. 예를 들어, 제3도에 도시된 전형적인 적층 게이트 셀 구조는 두 셀요부와 소자 신뢰도에 해로운 영향을 끼치는 산화물의 얇아짐(oxide thinning) 및 모서리 누출(edge leakage)을 보여준다. 제3도의 적층 게이트구조는 비트라인 방향에서 본 동일 구조의 투시도인 제2a도와 직각으로 되는, 워드라인 방향에서 바라본 것이다. 제3도에서, 제2a도에서와 동일한 셀 특징부에는 제2a도와 동일한 도면 부호가 병기된다.

제2a도를 참조로 설명한 바와 같이 터널산화물층(15)은 제1폴리 실리콘 층 (폴리 1)을 기판으로부터 분리시킨다. 또한 제3도에는 필드 산화물 영역(18)이 도시되었는데, 이 영역은 어레이내의 인접 셀들을 서로

분리시킨다.

종래의 표준 공정에서는, 필드 산화물 영역들이 먼저 제조되고, 이후 기판위에서 필드 산화물 영역들 사이에 터널 산화물이 성장된다. 공지된 기하학적 버즈 비크(bird's beak)효과와 쿠이(kooi)효과 때문에, 소위 화이트 리본(white ribbon)효과와 터널 산화물층의 얇아짐이 터널 산화물층(15)과 필드 산화물영역(18)사이의 접합점에서 관찰된다. 기하학적 효과에 의한 두께의 감소는 일반적으로 최소 10%내지 15%이지만, 쿠이 효과가 추가되면 두개의 감소가 20%와 30%사이로 될 수 있다.

EEPROM 또는 플래시 EEPROM 메모리 소자와 같이 게이트 산화물을 또는 터널 산화물이 120옴스트롬(angstrom)이하의 범위에 있는 진보된 MOS 소자에서, 20% 내지 30%의 산화물을 두께의 감소는 터널 산화물층과 필드 산화물 영역간의 접합점에 존재하는 강한 전기장의 존재 때문에 심각한 소자의 신뢰성 문제를 야기시킨다.

또한, 각 필드 산화물 영역(18)을 덮는 폴리 1층(11)의 부분들의 모서리(edge)에서는 전류 누출에 의한 신뢰성 문제가 관찰된다. 이 폴리 1층은 등각으로 피착되어 부유 게이트구조를 생성하기 때문에, 비교적 두꺼운 폴리 1층이 필드 산화물 영역을 덮는다. 또한, 최적의 폴리 1층의 두께로 1,000 내지 2,500옴스트롬의 범위가 사용되면, 폴리 1층중 필드 산화물 영역을 덮는 부분은 뾰족한 모서리나 모퉁이를 갖는 경향이 있다. 이러한 급격한 모서리는 폴리간층이 비교적 저온(1050°C이하)의 표준 산화 단계를 거쳐 폴리 1층상에 형성된 이후에 두드러진다. 뾰족한 모서리 또는 거친 표면은 폴리 1과 폴리 2층간의 과도한 전류 누출을 유도하여 필연적으로 소자 신뢰도에 악영향을 끼친다.

따라서, 본 발명의 목적은 적층 게이트 메모리 셀의 고집적 어레이를 제조하되, 이 어레이가 상기 셀 신뢰도 문제를 일으키지 않도록 하는데 있다.

본 발명의 다른 목적은 메모리 어레이 구조와 프로그래밍 능력을 제공하여, 개별 셀들이 신뢰성과 프로그래밍 가능성 및 다가논리(mulit-valued logic)를 획득하는 부수적 잇점을 가지고 소거될 수 있도록 하는데 있다.

이상과 그 이외의 목적들은 신규의 적층 게이트 셀종단면을 갖는 메모리 셀이 본 발명의 공정 순서에 따라 제조되는 본 발명으로 실현된다.

본 소자의 종단면은 터널 산화물층의 모서리에 연결되도록 형성되는 필드 산화물 영역과 함께 기판상에 형성되는 터널 산화물을 갖는다. 이 필드 산화물 영역이 터널 산화물의 형성 이후에 형성되면, 터널 산화물 모서리의 얇아짐은 관찰되지 않는다. 제1게이트 또는 부유 게이트는 2개의 폴리실리콘 또는 그 유사재료의 층으로 구성되며, 이때 제1층은 필드 산화물 영역들 사이의 터널 산화물상에 피착되고, 제2층은 이 필드 산화물 영역들을 덮는 모서리를 갖는다. 위를 덮는 부유 게이트의 재료는 종래 기술로 이루어지는 것 보다 더 얇고, 이후 공정에서 매끄러운 모서리를 나타내게 된다. 폴리간 절연 재료는 부유 게이트와 폴리간 종단면에 피착되며, 소스와 드레인 영역은 적층 게이트 부근에서 대칭 또는 비대칭적 관계를 가지고 기판에 형성된다.

메모리 어레이내의 본 발명의 구조에 대한 고유 프로그래밍은 선택된 웨드라인을 선택된 메모리 셀의 바이트 어드레스에서 분할하는 비트라인을 따라 적당한 전압을 인가하여 선택적으로 소거함과 함께, 선택된 웨드라인을 따라 플래시 프로그래밍하는 것을 포함한다.

이하 본 발명의 구조, 어레이 및 공정 순서를 첨부도면을 참조하여 상세히 설명한다.

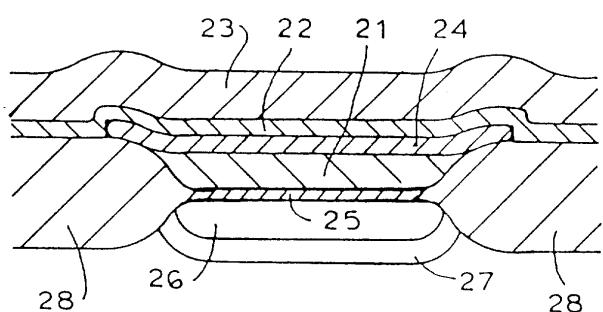

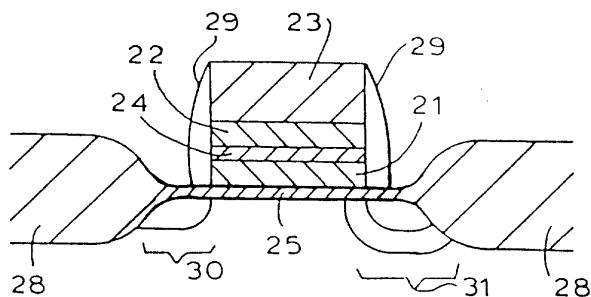

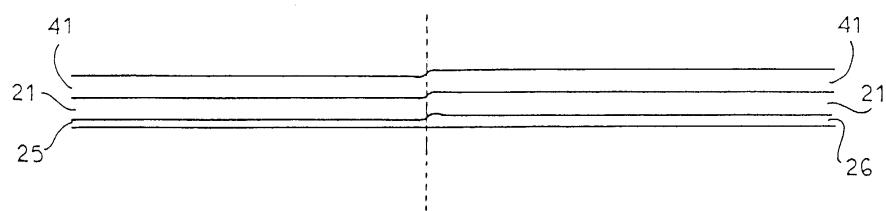

제4a 및 4b도에 도시된 바와 같이 본 발명에 따라 제조된 적층 게이트 메모리 셀은 폴리 2층을 포함하는 제어게이트(23)와 폴리간 절연층(22) 및 2개의 층(21, 24)을 포함하는 폴리 1부유 게이트를 구비하며, 동근모서리를 지닌 폴리 1층(24)의 얇은 제2층만이 필드 산화물 영역을 부분적으로 덮는다. 부유 게이트와 기판 사이에 위치하고 필드산화물 영역(28)의 산화물을 연결되는 터널 산화물층(25)은 필드산화물 영역에 접촉하는 부분이 얇아지지 않는다. 소스영역(30)은 P형 실리콘 기판의 한 영역을 포함하는데, 이 영역내로 제1도편트(26)(예로서, 비소)가 유입되며, 반면에 드레인 영역(31)은 기판 영역을 포함하는데, 이 영역내로 제1도편트(26)와 제2도편트(27)(예로서, 각각 비소 및 인)가 주입된다. 상기 도편트에 있어서, 당업자라면 다양한 도편트, 이를 도편트의 조합 및 도편트 높도가 소스와 드레인 영역을 위해 대칭 또는 비대칭 방식으로 효과적으로 이용될 수 있음을 알 수 있을 것이다. 제4a도의 웨드라인 투시도에는 드레인영역의 도핑만이 도시되어 있는 반면, 제4b도에는 제4a도에 도시되지 않은 산화물 스페이서 코팅(oxide spacer coating)(29)이 추가로 도시되어 있다.

이하 특정한 신뢰도 결함을 보이지 않는 본 발명의 메모리 셀 제조에 대해 제5a 내지 5j도를 참조하여 상세히 설명한다. 당업자라면 알 수 있듯이, 메모리 어레이의 제조는 각 개별 셀에 대하여 적층 게이트 형성과 관련 주변 소자들을 동일 기판내에서 동시에 효과적으로 형성하는 것을 포함하며, 제한적이지는 않지만 N-MOS 및 P-MOS 트랜지스터의 형성을 포함한다. 또한, 본 공정 순서는 EPROM 메모리 소자의 제조를 위해 이용될 수 있으며 이때 당업자에게 명백한 여려 변형이 가능하다. 도시된 공정 순서는 따라서, 제5j도에 도시된 최종구조를 제공하며, 이 도면에는 다음이 기판내에서와 표면에서 제조된다. 즉, 비트라인을 따르는 횡단면을 지닌 제1메모리 셀과, 웨드라인을 따르는 횡단면을 지닌 인접한 제1메모리셀과, N-MOS 논리 소자, 및 P-MOS 논리 소자들이 기판 내부와 표면상에 제조된다.

본 발명은 우선 N 우울(N-well) C-MOS기술에 따라 형성되는 주변 소자들에 대해 설명하는데, 이는 도해의 목적상 선택된 것이다. 따라서, 특별히 도시된 주변 소자와 관련하여 본 발명의 메모리 소자 및 어레이를 제조하는데 본 출원인이 제한적 의미를 둔 것이 아니고, 다만 본 발명의 대표적 실시예들에 대한 완전하고도 가능한 설명을 가장 예시적으로 제공하기 위하여 주변 요소들의 설명과 공정이 포함되도록 한 것이다.

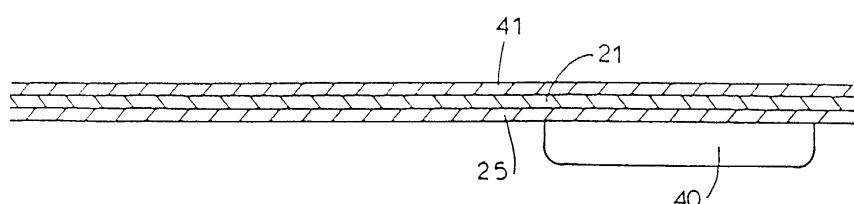

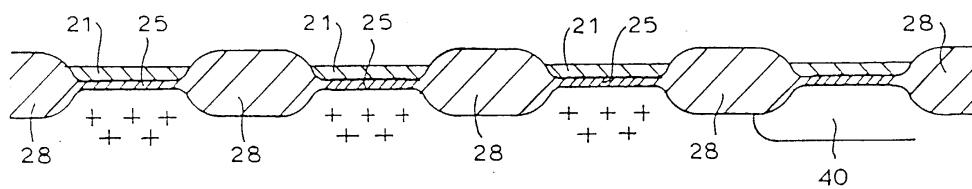

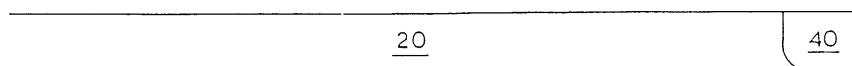

제5a도는 종래기술에 따른 N 우울 영역(40)의 형성완료시에서의 기판(20)을 나타내고 있다. 상기한 바와 같이 기판은 P형 실리콘으로서, 이제까지 메모리 셀과 어레이의 제조 및 동작으로 가장 바람직한 것이다. 제5b도에서 터널산화물(25)의 형성은 기판(20)상에서 6-12nm의 터널 절연층을 얻기 위해 수행된다. 본 실시예의 P형 실리콘 기판에 대해, 터널 절연체는 하나의 실리콘 이산화물층으로서, 섭씨 900 내지

1070도에서 20 내지 50분 동안 건조한 산소층에서의 열적산화와 같은 공지의 공정 조건에 따라, 실리콘 기판의 표면을 산화 환경에 노출시켜 형성될 수 있다.

이후 제5b도에 도시된 것처럼 함께 연장되는 비정질 실리콘층이 터널 절연체 위에 침착된다. 이 비정질 실리콘은 제1폴리 층(21)의 역할을 하는 것으로 추후 상세히 설명된다. 50 내지 150nm사이의 두께를 지닌 비정질 실리콘 층은, 예를 들어 섭씨 550도의 감압 기상 반응법(*low pressure chemical vapor deposition* : LPCVD)에 의해 형성된다. 폴리 실리콘은 섭씨 620도에서 LPCVD에 의해 폴리 1층에 대해 대안적으로 침착될 수 있으나, 비정질 실리콘은 우수한 평탄성(*planarity*) 때문에 현재 선호되고 있다.

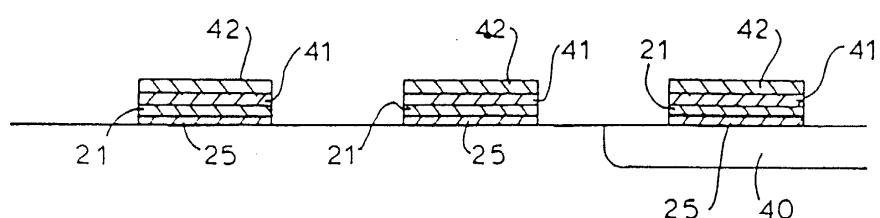

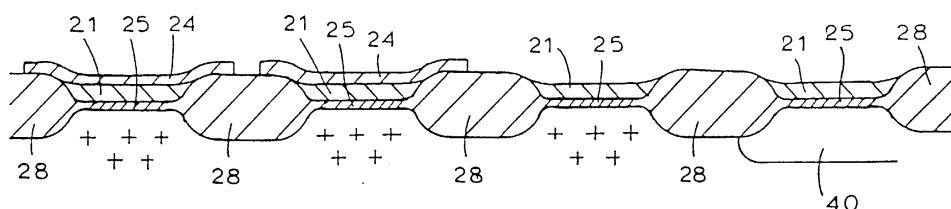

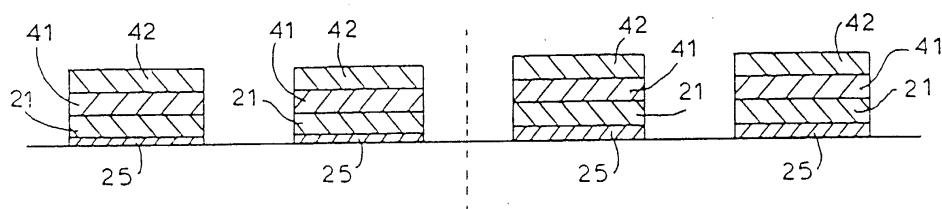

이후 LPCVD가 완료되어, 비정질 실리콘상에 100 내지 200nm의 동공간 연장되는 질화물층(41)이 침착된다. 다음, 공지의 공정 단계에 따라 질화물층 위에 포토레지스트 재료(42)가 침착되고 패턴화(pattern)된 후, 질화물과 비정질 실리콘 및 절연체는 활성 영역(*active region*)으로 역할을 하지 않는 모든 영역에서 제거된다. 최종 구조는 제5c도에 도시되며, 이 도면에서 기판 표면은 비활성(*non-active*)영역들 내에서 선택적으로 노출되어 있다. 패턴화된 레지스트(42)는 질화물, 비정질 실리콘 및 절연체의 드라이에칭(dry etching)이후 질화물 표면에서 제거된다. 이때, 상기 절연체는 이 공정 단계에서 제거되는 질화물과 실리콘만을 대체하여, 남아 있을 수 있다.

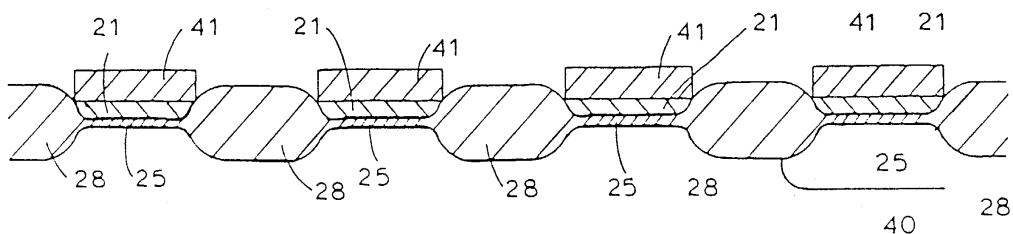

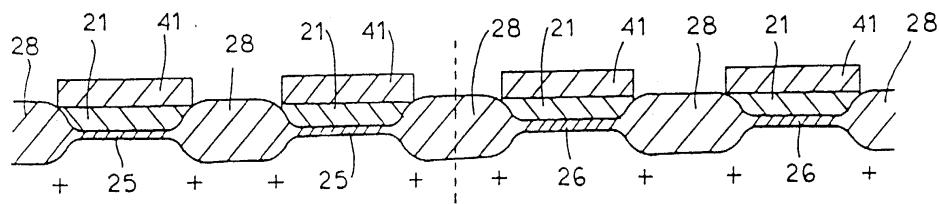

이후 기판 구조는 바람직하다면 드라이-웨트-드라이 공정을 이용하는 섭씨 900 내지 1100도에서의 열적 산화에 의한 다른 산화 공정에 노출되고, 이로써 이 기판의 모든 노출된 비활성 영역들이 산화된다. 이러한 산화 단계로 형성되는 필드산화물 영역(28)은 모든 활성 영역과 소자들을 전기적으로 서로 절연시킨다. 제5d도로부터 알 수 있듯이, 필드 산화물 영역의 상측 표면은 기판 표면 보다 높은 곳에서 연장되었는데, 그 이유는 산화 단계가 기판 내부 200 내지 500nm의 깊이까지의 산화 및 기판 표면상에 이 표면 위 300 내지 400nm로 산화물의 성장을 제공하기 때문인데, 이에 의하여 필드 산화물의 총 두께의 거의 반이 표면위에 존재하게 된다. 필드 산화물 영역의 상측 표면의 높이는 최적화됨으로써, 상측 표면이 비정질 실리콘의 상측 표면 높이를 초과하여 연장된다. 상기에서 알 수 있듯이, 본 발명의 구조는 터널 산화물층과 필드 산화물 영역의 접합 부분에서 터널 산화물이 얇아지는 것에 대해 걱정할 필요가 없는데, 이는 종래기술의 제조 공정 순서와 반대로 필드 산화물이 터널 산화물의 형성 이후에 성장되기 때문이다.

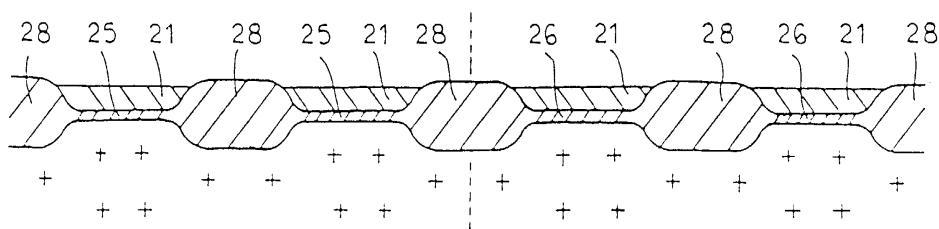

필드 산화물 영역이 형성된 이후, 질화물이 벗겨져서 활성 영역내의 비정질 실리콘이 노출된다. 제5e도의 다음 단계는 실리콘 기판을 도핑하기 위한 셀 임계 주입(*cell threshold implant*)을 포함한다. 바람직하다면 이 공정은 50 내지 150KeV의 주입 에너지를 사용하는 실리콘 내부로의 붕소(boron) 주입을 포함한다. 이때 주입은 비정질 실리콘 및 터널 절연체를 통해 수행된다. 필드 산화물 영역은 어떤 영역내의 붕소를 차단하며, 또한 N-MOS 및 P-MOS영역이 차폐(*screened*)될 수 있으므로, 기판의 영역은 선택적으로 도핑될 수 있다.

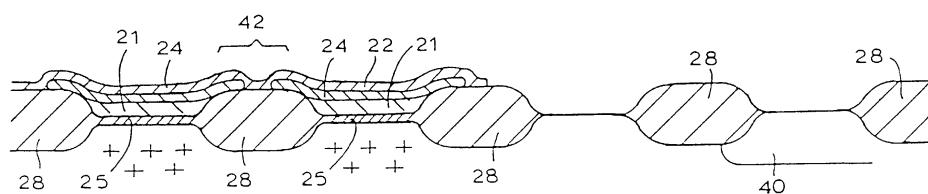

30 내지 70nm의 얇은 제2비정질 실리콘층은 이후, 전체 기판상에 공형으로 침착된 다음, 비정질 실리콘층을 도전성으로 만들기 위하여 선택적인 도핑이 수행된다.

$1 \times 10^{15} / \text{cm}^2$ 에서  $5 \times 10^{15} / \text{cm}^2$ 의 비소 주입

선량(*arsenic implant dosage*)을 층(21, 24)에 제공하는 비소 주입은 30 및 50KeV 사이에서 수행될 수 있다. 주입 에너지는 우선, 관련층들이 충분히 도핑되어 도전성을 갖고, 다음으로 비소(또는 다른 도펀트)가 폴리 1층에 남게 되는 것을 보장하도록 최적화되어야 함을 당업자들이라면 이해할 수 있을 것이다.

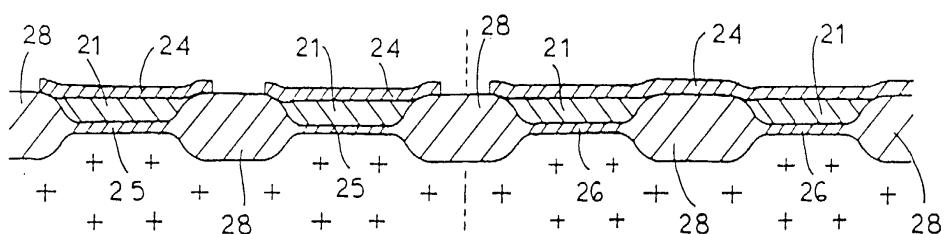

층(24)은 선택적으로 에칭되어 메모리 셀의 부유게이트를 부분적으로 규정한다. 도핑된 실리콘의 에칭은 포토레지스트 마스크를 통한 드라이 에칭 공정에 의해 수행되고, 이에 따라 층(24)이 메모리 셀 영역이 아닌 모든 영역에서 제거된다. 메모리 셀을 분리시키는 필드 산화물 영역 위에서 패턴화된 층(24)의 모서리가 이 필드 산화물을 덮는다. 두 개의 인접하는 메모리 셀을 분리시키는 필드 산화물 위에서, 이 필드 산화물은 층(24)내의 개구 또는 채널(42)의 에칭을 통해 노출되며, 개구는 다음 단계에서 막히게 된다. 제5f도에 도시되어 있는 것과 같이, 층(21, 24)은 모두 적층 게이트 메모리 셀의 폴리 1층 부유 게이트를 포함한다.

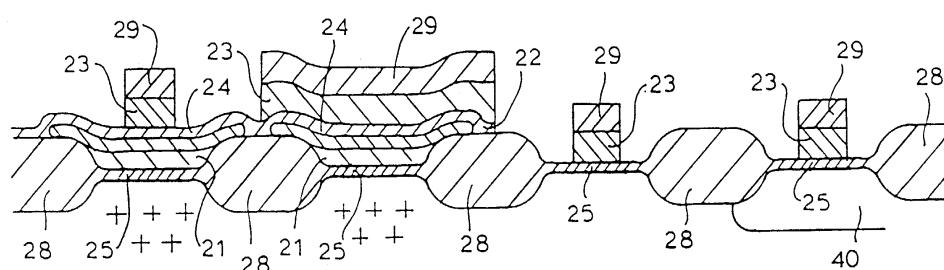

폴리 산화물 또는 도시된 바와같은 산화물-질화물-산화물(*oxide-nitride-oxide* : ONO)의 폴리간 절연층(22)은 제5g도에서와 같이 형성된다. 양호한 공정에는 5 내지 20nm의 두께까지 섭씨 1000 내지 1100도의 건조한 산소에서의 열적 산화와 이후 섭씨 750 내지 790도에서 10 내지 25nm의 LPCVD 질화물 침착 및 최종적인 습한산소에서 섭씨 900 내지 1000도의 열적 산화를 포함하며, 2 내지 6nm의 산화물층을 질화물층의 최상부에 성장시킨다. 상기 ONO는 필드 산화물 영역위의 개구(42)를 채우고 폴리 1층 위에 형성되며, 이에 따라 폴리 1층을 완전히 분리시켜, 폴리 1층의 모서리에서 전하의 유출 가능성을 제거한다. 이에 부가하여, ONO 폴리간 절연체의 형성에 있어서, 패턴화된 층(24)의 모서리는 층(24)이 비교적 얇으므로 필드 산화물 위의 층(24)의 모서리를 따라 산화가 모든 방향으로 발생하기 때문에 둥글어지게 된다. 얇은 폴리 1겹층의 둥근 모서리는 유출 감소라는 상기한 장점을 제공하는데, 이 유출은 폴리간 절연층을 아래에 덮고 있는 두꺼운 폴리 1층의 날카로운 모서리 때문에 종래기술에서 직면하게 되는 문제점이다.

제5g도에서 관찰되듯이, ONO 층의 형성 이후 레지스트층이 적용되어 패턴화 되고, 이후 ONO가 메모리 셀의 위치를 제외한 모든 표면에서 제거된다. 부가적으로, 잔여 폴리 1층은 주변 소자 형성용 영역에서 제거된다. 일단 주변 소자 영역이 노출되면, 공지의 방법으로 게이트 산화가 수행될 수 있는데, 이때 게이트 산화가 관련 기판 영역내에서 15 내지 35nm의 깊이로 기판을 투과하는 반면, 기타의 모든 영역들은 이 단계에서 ONO 층에 의해 효과적으로 절연된다.

이후, 비정질 실리콘 또는 폴리 실리콘의 등각(공형) 층(23)(conformal layer)이 전체 기판위에 침착되어 메모리 셀영역과 주변 소자 영역 모두가 덮히게 된다. 제어 게이트를 위한 폴리 실리콘 또는 비정질 실리콘의 폴리 2층은 LPCVD에 의해 250 내지 400nm의 층 두께로 침착된 후, 비소 또는 인 이온 주입 또는 확산에 의한 폴리 2의 도핑이 수행된다. 다음 단계에서는 100 내지 150nm의 산화물층이 침착된다. 이후 레지스트 마스크가 형성되고 산화물과 폴리 2층(29, 23)이 드라이 에칭에 의해 에칭되며, 순차적으로 이들 재료들이 에칭되어 N-MOS, P-MOS 및 메모리 소자가 제5h도에서와 같이 지정된다. 이후 다른 레지스트 마스크가 주변 트랜지스터 위에서 사용되고, 자기 정합(*self-aligning*)에칭 마스크로서 폴리 2를 사용하여

ONO 및 폴리 1층(22, 24, 21)이 제5i도에서와 같이 지정된 메모리 영역내에서 제거된다.

적층 게이트 메모리 셀 제조 공정의 최종 단계로서, 셀의 소스 및 드레인 주입이 메모리 소자와 관련된 적당한 영역내의 기판에 제공된다. 주변 소자들은 주입 단계에서 마스크되며, 이 마스크는 이전 단계의 동일 위치에 있었던 것과 같은 것이 될 수 있다. 제5j도에 도시되어 있는 것과 같은 최종구조에는, 예를 들어 인과 비소의 주입 영역(27, 26)이 포함되며, 이 영역들은 대칭형 메모리 셀들을 위한 소스 및 드레인 영역을 형성한다. 상기에서 알 수 있고 당업자에게 자명하듯이, 소스 및 드레인 주입들은 본문에서 상세히 설명되는 비소 및 이느이 조합 이외의 것이 될 수도 있다. 예를 들어, 제4b도에 도시된 메모리 셀은 비소로만 된 비대칭형 셀 소스 영역(30)과 비소 및 인으로 된 셀 드레인 영역(31)을 구비한다. 이후 표준 C-MOS 공정 기술을 이용하여 N-MOS 및 P-MOS 소자와 배선을 포함하는 전 구조를 완결하기 위한 공정을 진행할 수 있지만, 이것은 본 발명의 일부가 아니다.

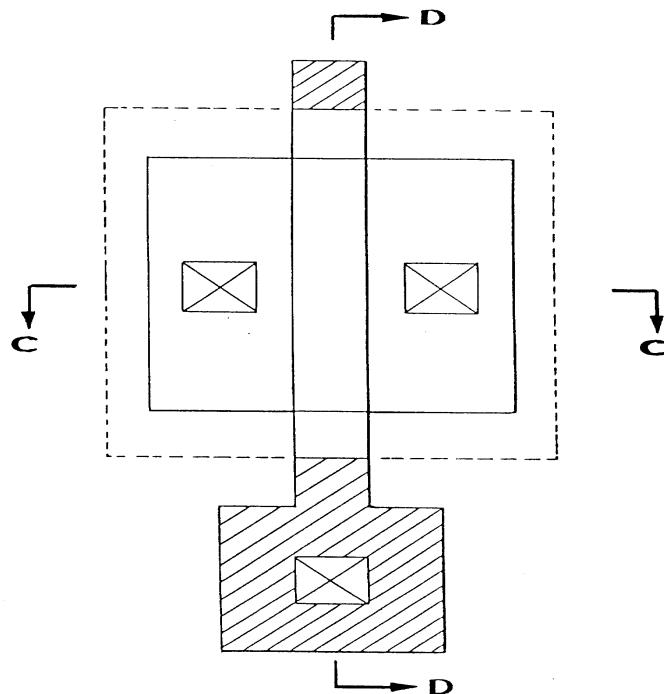

이 공정 순서는 대안적으로, 주변 소자를 EEPROM 또는 EPROM 과 함께 동일 기판에 동시에 제조하기 위해 적합화 될 수 있다. 제8도는 본 발명에 따른 EEPROM 주변 소자의 배치도를 나타내고 있다. 제9a도 내지 제9j도는 다양한 공정 진행 단계에서 C-C 와 D-D를 따른 소자의 횡단면도를 나타내며, 여기에서 횡단면 C-C는 소스-드레인 방향에 따른 주변 소자의 구조를 나타내고, 횡단면 D-D는 폴리 실리콘 게이트 방향에 따른 주변 소자의 구조를 나타낸다.

제9a내지 제9j도는 변형된 공정 순서를 나타내는데, 이 도면들에서 주변 소자들은 메모리 소자와 동시에 제조된다. 이 도면들에서 공정과 재료들은 제5a 내지 5j도를 참조로 이전에 설명된 것과 동일하며, 동일한 참조번호가 사용되어 상세한 설명의 반복은 하지 않는다. 제1단계에서, 제9a도는 N 우물 영역(40)이 기판(26)에서 생성되는 점에서 제5a도와 유사하다. 이후 제5b도를 참조로 상세히 설명했듯이, 산화물의 균일층(25)이 기판 표면상에 형성되어 게이트 산화물로서 역할을 한다. EEPROM 형 소자에서, 게이트 또는 터널 산화물(25)의 두께는 주변 소자에 필요한 게이트 산화물(26)의 두께와 다르다. 그러므로, EEPROM 응용에 있어서 약 10 내지 25nm의 두께인 게이트 산화물의 제1부분이 전체 기판위에서 성장되고, 종래의 레지스트 마스크는 메모리 소자 영역에서 게이트 산화물의 제1부분을 제거하기 위해 사용된다.

이후 레지스트가 기판에서 제거되고, 나머지 제2게이트 산화물층(25)이 6 내지 12nm사이의 게이트 산화물의 두께로 메모리 소자를 위해 성장된다. 동시에, 이 산화동안 주변 소자 영역상의 게이트 산화물의 두께는 제9b도에 도시된 계단 종단면도에서 알 수 있듯이, 15 내지 35nm범위의 최종 두께에 도달한다.

EPROM 또는 OTP(one-time program ePROM : 1회 프로그램 ePROM) 소자에 대해, 메모리 소자용 게이트 산화물의 두께는 주변 소자용과 동일해도 된다. 이 경우, 제5b도에 도시된 것과 같이 균일하게 성장된 게이트 산화물이 단일 단계에서 10 내지 30nm범위의 두께로 성장된다. 이하에서는 공정 설명을 단순하게 하기 위하여 EEPROM소자와 주변N-MOS 트랜지스터만을 제9b 내지 9j도를 더 참조하여 설명할 것이다.

게이트 산화물(25)이 형성된 다음, 비정질 실리콘층(21)과 LPCVD 질화물층 (41)이 제9b도에 도시된 바와 같이 기판상에 순차적으로 침착된다. 이후, 제9c내지 9e도에 도시된 공정은 제5c 내지 5e도를 참조로 설명한 것과 동일하게 수행되고, 여기서 반복 설명하지 않는다.

제9f도에서의 공정은 제5f도를 참조로 상세히 설명된 공정과 다르다. 30 내지 70nm 두께의 얇은 폴리 1층(24)이 제9e도의 구조위에 공형으로 침착된다. 이후 레지스트 마스크가 인가되어 30 내지 70nm의 얇은 폴리 1층이 지정된 후, 드라이 에칭에 의해 선택적으로 제거된다. 이 단계는 제5f도에서의 단계와 차이가 있는데, 그 이유는 얇은 폴리 1층이 제9f도의 주변 소자 영역위에 남아 있기 때문이다. 제9g도에서 폴리 산화물 또는 ONO(도시되어 있음)의 폴리간 층이 형성되고, 레지스트 마스크가 적용되어 이 ONO 층이 드라이 에칭 단계를 통해 어떤 영역에서 선택적으로 제거된다. 제 9g도는 주변 소자의 확산 영역을 완전히 덮고 있는 ONO 층(22)을 나타내고 있다.

제9h도에서는 대응 도면인 제5h도와 달리, 본 공정순서에 필요한 산화물 침착(예로서, 층(29))이 없다. 레지스트 마스크는 도핑된 폴리 2층의 최상부에 직접 인가된다. 본 공정에서는 제9j도에 도시된 바와같이 메모리와 주변 소자 모두를 위해 ONO와 폴리 1층을 연속적으로 에칭하기 위해 제9h도에서 설명된 동일한 레지스트 마스크가 사용되므로, 공정 순서가 단순화된다.

최종적으로, 제9j도는 메모리 소자의 소스 및 드레인 형성을 위한 주입 단계 이후의 소자 구조를 나타내고 있다. 이후 공기 기술에 따라 C-MOS 공정이 수행되어 주변 소자의 제조가 완료된다.

나중에 인용된 공정 순서의 장점에는 비휘발성 메모리 소자의 제조를 위한 단순화된 공정 기술과, EEPROM 및 EEPROM 소자의 제조를 위한 융통성, 및 동일 기판에 EPROM 및 EEPROM 모두를 제조하기 위한 경제적인 실행 가능성이 포함된다.

본 발명의 적층 게이트 메모리 셀은 파울러-노르드하임(Fowler-Nordheim : F-N) 터널링 메카니즘에 따라 동작하며, 이를 제4b도에 도시된 구조를 참조하여 이하 설명한다. 예로서, 메모리 셀의 부유 게이트에 저장을 위한 전자를 제공하는 셀 프로그래밍을 위하여, 소스 및 드레인 영역(30, 31)에 의해 지정되는 셀의 채널 영역으로부터의 전자는 얇은 터널링 절연체(25)를 가로지르는 터널링에 의해, 셀 채널위의 층(21, 24)으로 구성되는 부유 게이트 폴리 1대로 주입된다. 전자를 채널 영역에서 부유 게이트로 주입시키기 위하여 고전압이 폴리 2층(23)에 인가되는 반면, 기판(20)은 접지 또는 음의 바이어스로 유지되고, 셀의 소스 및 드레인(30, 31)은 부유 상태(전원이 연결되지 않은 상태) 또는 접지로 남는다. 폴리 2에 인가되는 고전압은 부유 게이트 폴리 1에 용량성으로 결합되어, F-N 터널링이 유효하게 되기 위하여, 터널링 절연체의 두께가 상기 제조 공정 순서에서 언급했듯이 10nm이하로 유지되어야 한다.

저장된 전자들은 셀 소거 동작의 수행을 위해, 역 F-N 터널링 효과를 사용해서 부유 게이트 폴리 1에서 하부에 있는 드레인 영역(31)으로 이동되어야 한다.

원칙적으로 셀은 셀 소스 영역을 통해 소거될 수 있는데, 이는 블럭 또는 어레이 소거가 소망될 때 유용하다. 그러나 지금 서술하는 공정을 위하여는 바이트 소거 모드를 실행하고, 메모리 셀에 다가의 논리 상태를 제공하는 것이 바람직하다.

그러므로, 셀 드레인을 통해 소거하는 것이 바람직하다.

전자들을 부유 게이트에서 셀 드레인으로 이동시키기 위하여, 고전압(예로서, 폴리 2층(23)의 전압 보다 높은 전압)이 셀드레인 영역에 인가되고, 층(24, 21)으로 구성되는 부유 게이트와 셀 드레인(31)간의 터널링 절연체(25) 양단에 전기장이 형성되어야 한다. 셀 소거 동작중에 기판(20)은 접지 전위로 유지되는 반면, 셀 소스 영역(30)은 부유 상태로 남는다.

상술한 메모리 셀 프로그래밍과 소거 능력은 제1도에서와 같은 메모리 어레이내에서 구현될 수 있으며, 제6a 내지 6c도에 도시된 것을 참조로 하여 설명된다. 제1도 및 제6a 내지 6c도의 메모리 어레이에는 다수의 메모리 셀로 구성되는데, 여기에서 동일 열내의 모든 셀 드레인은 비트라인 j, j+1 등에 의해 함께 연결되고, 동일 행 내의 모든 폴리 2게이트는 워드라인 i, i+1 등에 의해 함께 연결되며, 셀 소스들은 공통라인 C에 의해 연결된다. 또한, 비트라인과 워드라인은 어드레스 디코더 회로들에 연결되어, 어레이내의 메모리 셀의 위치를 판정한다. 비트라인은 선택된 메모리 셀로부터의 셀 정보를 판독하기 위하여 감지 증폭기 또는 이와 유사한 회로에 추가로 연결된다. 메모리 어레이는 초기에 버진 상태(virgin state)에 있는데, 이 상태는 부유 게이트에 어레이내의 어떤 메모리 셀을 위한 별도의 전하가 없는 상태이다. 메모리 셀은 프로그래밍 동작을 수행하는데 필요한 정보를 포함할 수 있는데, 이에 대해서는 제6a 및 6b도를 참조로 하여 이하에서 설명한다.

제6a도는 플래시 프로그래밍을 나타내는 도면으로, 여기에서 워드라인 i+1이 선택되어 다음의 정보, 즉 셀 j용 0과 셀 j+1 및 셀 j+2 용 1을 저장한다. 선택된 워드라인 i+1에 대하여, 이 워드라인 i+1에 고전압이 인가되는 반면, 선택된 나머지 모든 워드라인은 접지로 될 것이다.

모든 비트라인과 공통 소스라인은 제6a도에 나타나 있듯이 접지 또는 음의 바이어스에 있는 기판과 함께 부유 상태로 남게 될 것이다. 워드라인 i+1이 고전압에 있기 때문에, 워드라인 i+1을 공유하는 모든 메모리 셀을 위해 전자가 셀 채널에서 부유 게이트로 주입된다. 그러므로, 선택 워드라인 i+1상에서의 플래시 프로그래밍 이후, 전자들이 제6b도에 도시된 바와같이 부유 게이트에 저장된다. 메모리 셀은 부유 게이트상에 여분의 전자를 갖는데, 이는 높은 셀 임계 전압을 의미하는 것으로 제6b도에서 상태 0으로 표기된다.

워드라인 i+1에 저장될 소망 정보는 선택된 셀 j, j+1 및 j+2에 대해 각각 0 1 0이기 때문에, 비트라인 j+1과 워드라인 i+1에 위치되는 특정 셀이 이제 소거되어(예로서, 여분의 전자들이 부유 게이트에서 제거되어), 상태 1에서 중성으로(예로서, 낮은 셀 임계 전압을 의미하는 여분의 전자가 없는 상태)될 필요가 있다. 이러한 일을 달성하기 위해서 제2어레이 동작, 선택 소거가 수행되어야 한다.

저장된 전하를 선택된 메모리 셀에서 선택적으로 소거하기 위해, 어레이는 워드라인 i+1과 비트라인 j+1에 위치되는 메모리 셀에서의 도시예에서 제6c도에서와 같이 바이어스 된다. 선택된 워드라인 i+1에는 -7V에서-10V사이의 역 바이어스가 공급되고, 선택되지 않은 워드라인은 접지 또는 3 내지 5V로 유지되며, 선택된 비트라인 j+1은 3 내지 5V로 바이어스 되고, 비선택 비트라인은 접지 또는 부유 상태로 유지되며, 또한 소스 라인도 부유 상태 또는 접지로 유지된다. 따라서 전자들은 -7V 내지 -10V의 바이어스에 의한 저 전위 상태인 선택된 셀의 부유 게이트로부터 양 전위의 기판의 드레인 영역으로 통과된다. 그러므로 상기의 방식에 있어서, 플래시 프로그래밍을 통한 바이트 레벨의 메모리 프로그래밍과 1 또는 다수의 고밀도 적층 게이트 셀의 선택 소거가 달성될 수 있다.

상술한 바와같이, 개별 메모리 셀의 소거는 다가의 논리 상태 구현을 위한 가능성을 제공한다. 피드백 제어는 각 소거 필스가 선택된 비트라인에 인가된 후에 셀 전류를 감시함으로써, 예를 들어 기준 셀의 셀 전류에 감지된 전류를 비교함으로써 셀의 소거를 방지하기 위해 제공된다. 셀 소거 동작 동안에 피드백 루프 제어 회로를 구현하여, 셀 전류를 신뢰성 있게 제어하고, 따라서 셀 임계 전압을 어떤 범위내에 둘 수 있다. 또한, 다양한 전류 범위를 I<sub>0</sub>를 셀 전류로 하는 불연속 구간들, 예를 들어 150μA, 50μA ≤ I ≤ 100μA, 100μA ≤ I ≤ 15μA 및 150μA ≤ I ≤ 1로 설정할 수 있다. 이후 각 전류 구간은 논리상태, 예를 들어 00 ; 01 ; 10 ; 11로 표기될 수 있다. 이러한 4가 논리에 대해, 해당 전류 레벨이 각각 하나씩 4개의 기준셀의 피드백 제어 감지용으로 사용될 수 있다.

어레이의 집적도와 터널 절연체 및 폴리간 절연막이 모두 다소 얇다는 조건이 주어진다면, 메모리 셀의 장애 문제가 어레이 프로그래밍과 판독 동작시 발생할 수 있어서, 얼마나 많은 메모리 셀이 동일한 비트라인 또는 워드라인을 공유할 수 있는가에 대한 어떤 제한 요소에 부딪히게 된다. 이러한 경우, 예로서 비트라인이 여러개의 섹션으로 분리될 수 있는데, 이를 각 섹션은 보다 적은 수의 메모리 셀로 구성되고, 이 메모리 셀은 제7도에 도시된 바와같이 비트라인에 연결시키기 위한 통과 트랜지스터(pass transistor)를 구비한다. 통과 트랜지스터에 의해 연결되는 섹션은 고 전압을 통과 트랜지스터의 게이트에 인가함으로써 선택되며, 이와 유사하게 통과 트랜지스터의 게이트에 인가함으로써 선택되며, 이와 유사하게 통과 트랜지스터 배열은 게이트 장애가 문제시되면 워드라인을 따라 적용될 수 있다.

이상 설명된 셀 구조, 어레이 구조 및 어레이 동작으로부터, 지능형 어레이 프로그래밍 알고리즘이 회로 설계와 함께 침에 내장되어 구현되거나 외부 마이크로 제어기(예로서, 소프트웨어 구현)와 함께 체 외부에서 구현될 수 있다. 제10a 및 10b도는 상기한 프로그래밍 기능을 수행하는 대표적인 프로그래밍 알고리즘을 나타낸다.

본 발명의 프로그래밍 처리 순서 단계 101은 프로그래밍 시작으로 표기되어 있다. 메모리 어레이에 대한 프로그래밍 시작 이전에, 저장될 디지털 정보는 오퍼레이터/프로그래머에게 알려져 있거나, 프로그램에 의해 오퍼레이터 입력에서 적당한 디지털 패턴으로 변환된다.

그러므로, 프로그래밍될 셀들의 위치와 셀들에 관련된 워드 및 비트라인들도 또한 알려진 것으로 가정한다. 그러므로, 단계 102에서는 프로그램될 제1셀이 발견되는 워드라인을 프로그램이 선택한다. 선택된 워드라인의 플래시 프로그래밍은 단계 103에서 수행되고, 이후 단계 104에서 선택된 워드라인으로부터 데이터가 판독된다. 제6a 내지 6c도를 참조로 설명된 바와같이, 플래시 프로그래밍은 고전압을 선택된 워드라인에 인가하는 반면 다른 라인들을 부유 상태, 접지, 또는 저전압으로 유지시킴으로써 수행된다. 워드라인을 따라 데이터를 판독하자마자, 프로그램은 단계 105의 판단에서, 선택된 워드라인을 따르는 모든 데

이터가 값 0을 갖는지에 대한 검증을 시도한다. 또한, 이 시스템은 당업자에게 자명하듯이, 만약 값 1을 원한다면, 모든 셀이 값 1을 갖는지에 대해 검증할 수 있다. 이후의 단계는 판단문인 단계 105의 결과에 따라 진행된다. 만일 선택된 워드라인을 따른 모든 데이터가 값 0을 갖지 않는다면, 단계 103의 플래시 프로그래밍으로 진행하고, 이 플래시 프로그래밍은 선택된 워드라인을 따르는 모든 셀들이 동일한 값을 가질때까지 반복된다. 그러나, 만일 데이터 검증에 따라 모든 관련 셀들이 라인 107를 다른 적당한 값을 갖는 것으로 되면, 필요시 선택적이 소거가 시작된다.

단계 108에서 워드라인을 따른 제 1바이트 어드레스가 선택되고, 단계 109에서는 선택된 어드레스에서 셀로부터 데이터가 판독된다. 단계 110에서, 시스템은 바이트 어드레스에서의 데이터 값이 의도된 값(예로서, 본 실시예에서는, 선택된 바이트 어드레스에서의 선택은 워드라인을 따른 셀이 0인가?)인 것을 다음에 검증한다.

만일 그 값이 의도된 값이 아니라면, 라인 111을 따라 지적된 것처럼 프로그램은 단계 112에서 관련 바이트 어드레스를 갖는 셀이 위치되는 비트라인을 선택한다. 이후 단계 113에서 제6a내지 6c도를 참조로 상술된 것에 따라서 소거 동작이 수행된다.

여기에서 논의된 것처럼, 단일 바이트 어드레스에 대한 데이터 검증 단계가 셀이 적당한 데이터 값을 갖는 것을 나타낼때까지, 다수의 반복 소거가 필요할 수도 있다.

만일, 바이트 어드레스에서의 데이터가 라인 114를 따라 표시되듯이 의도한 바와같다면, 프로그램은 선택된 워드라인내의 모든 바이트 어드레스들이 판독되고 검증 되었는가에 대해 단계 115에서 판단을 한다. 만일, 라인 117로 표시되듯이 모든 바이트 어드레스들이 검증되지 않았다면, 바이트 어드레스가 단계 118에서 갱신(예로서, 워드라인을 따른 다음(Next)바이트 어드레스가 선택된다)되고, 이후 필요에 따라 단계 109부터 115가 반복된다. 일단 선택된 워드라인상의 마지막 바이트 어드레스에서의 데이터 값이 검증되면, 판단 블럭 115의 외부라인 116으로 표시되듯이 프로그래밍이 완료된다.

본 발명은 부속 청구범위에서 정의된 본 발명의 사상과 영역을 벗어나지 않는 범위내에서, 상술한 프로그래밍 순서, 구조, 재료 및 공정에 다양한 변형을 가할 수 있음을 당업자라면 알 수 있을 것이다.

### (57) 청구의 범위

#### 청구항 1

제1도전형의 반도체 기판과; 상기 기판에 형성되는 제2도전형의 소스영역과; 상기 기판에 형성되는 제2도전형의 영역으로서, 상기 제1도전형의 반도체의 채널 영역에 의해 상기 소스영역과 분리되는 드레인 영역과; 상기 소스 영역, 채널 영역 또는 드레인 영역에 대한 상기 기판 표면들 위에 성장되고, 상기 기판의 표면 위와 아래로 연장되는 2개의 필드 절연 영역과; 상기 필드 절연 영역들 사이에서, 상기 소스영역, 채널영역 및 드레인 영역의 표면위에 성장되는 균일한 두께의 제1절연층과; 상기 제1절연층위에 형성되는 제1반도체 층과; 상기 제1반도체 층위에 형성되고, 상기 필드 절연 영역들 위에 부분적으로 연장되는 층으로서, 상기 제1반도체층과 함께 부유 게이트를 포함하는 제2반도체 층과; 상기 부유 게이트 위에 형성되는 제2절연층; 및 상기 제2절연층 위에 형성되고, 제어 게이트를 포함하는 제3반도체층을 포함하는 것을 특징으로 하는 반도체 소자.

#### 청구항 2

제1항에 있어서, 상기 제1 및 제2 반도체들을 폴리 실리콘과 비정질 실리콘을 포함하는 그룹중에서 선택되는 것을 특징으로 하는 반도체 소자.

#### 청구항 3

제1항에 있어서, 상기 제3반도체는 폴리 실리콘과 비정질 실리콘을 포함하는 그룹중에서 선택되는 것을 특징으로 하는 반도체 소자.

#### 청구항 4

제1항에 있어서, 상기 제1절연층은 실리콘 이산화물을 포함하는 것을 특징으로 하는 반도체 소자.

#### 청구항 5

제1항에 있어서, 상기 필드 절연 영역들은 실리콘 이산화물을 포함하는 것을 특징으로 하는 반도체 소자.

#### 청구항 6

제1항에 있어서, 상기 제2절연층은 폴리 산화물을 포함하는 것을 특징으로 하는 반도체 소자.

#### 청구항 7

제1항에 있어서, 상기 제2절연층은 산화물-질화물-산화물의 샌드위치형 층을 포함하는 것을 특징으로 하는 반도체 소자.

#### 청구항 8

제1항에 있어서, 상기 소스 영역 및 드레인 영역은 비소 및 인 도핑된 실리콘을 포함하는 것을 특징으로 하는 반도체 소자.

#### 청구항 9

제1항에 있어서, 상기 소스 영역은 비소 도핑된 실리콘을 포함하고, 상기 드레인 영역은 비소 및 인 도핑

된 실리콘을 포함하는 것을 특징으로 하는 반도체 소자.

#### 청구항 10

한 기판에 형성되는 전기적 소거 가능한 메모리 어레이에 있어서, 복수행의 워드라인들과: 상기 워드라인들과 직교하여 배열되는 복수열의 비트라인들과; 상기 워드라인들과 평행한 복수행의 공통 소스라인들: 및 상기 기판에 형성되는 소스 영역과, 상기 기판에 형성되는 드레인 영역과, 반도체 재료로된 제1층을 포함하는 제1게이트, 및 반도체 재료로된 제2 및 제3층을 포함하고 상기 제1반도체 게이트와 상기 소스 및 드레인 영역 사이에 위치되는 제2게이트로 각각 구성되는 복수의 메모리 셀을 포함하며; 한 행내의 각 셀의 드레인이 동일 비트라인에 연결되고, 한 행내의 각 셀의 제1반도체 게이트가 한 워드라인에 연결되며, 한 행내의 각 셀의 소스가 한 공통 소스 라인에 연결되는 것을 특징으로 하는 전기적 소거 가능한 메모리 어레이.

#### 청구항 11

제10항에 있어서, 상기 제2반도체 게이트는 제1절연층에 의해 상기 제1반도체 게이트로부터 절연되며, 상기 제2반도체 게이트는 제2절연층에 의해 상기 소스 및 드레인 영역으로부터 절연되는 것을 특징으로 하는 전기적 소거 가능한 메모리 어레이.

#### 청구항 12

제10항에 있어서, 상기 복수의 메모리 셀들 사이에 위치되고, 상기 복수의 셀들 각각을 전기적으로 절연시키기 위한 복수의 절연 영역을 더 포함하는 것을 특징으로 하는 전기적 소거 가능한 메모리 어레이.

#### 청구항 13

제12항에 있어서, 상기 반도체 재료로 된 제2층은 2개의 인접 절연 영역 사이에서 상기 소스 및 드레인 영역 위에 배치되고, 상기 제3반도체층은 상기 제2반도체층과 상기 2개의 인접 절연 영역 위에 배치되는 것을 특징으로 하는 전기적 소거 가능한 메모리 어레이.

#### 청구항 14

제12항에 있어서, 상기 기판과 반도체 재료로 된 상기 제2층 사이에서, 균일 두께의 얇은 절연층이 상기 복수의 절연 영역들의 인접 절연 영역들 사이에 배치되는 것을 특징으로 하는 전기적 소거 가능한 메모리 어레이.

#### 청구항 15

한 기판상에 소거 가능한 메모리 소자를 제조하기 위한 공정에 있어서, 제1절연체로 된 얇은 공형의 층을 상기 기판의 표면상에 형성하는 단계와; 반도체 재료로 된 제1층을 상기 절연체의 표면위에 ;침착시키는 단계와; 제1질화물층을 상기 제1반도체 층위에 침착시키는 단계와; 상기 제1질화물과 제1반도체를 선택적으로 제거하여, 상기 기판 표면의 선택된 영역들내에서 노출시키는 단계와; 상기 선택된 영역들에 제1절연 영역들을 형성하는 단계와; 상기 질화물층을 제거하는 단계와; 상기 제1반도체, 상기 제1절연체 및 상기 제1절연영역을 통해 도편트를 상기 기판으로 주입시키는 단계와; 제2의 공형 반도체 층을 상기 제1반도체와 상기 제1절연 영역들 위에 제공하는 단계와; 상기 제2반도체 층을 도핑시키는 단계와; 상기 제2반도체 층을 선택적으로 에칭하며, 각각의 상기 제1절연 영역의 중앙 부분을 노출시키는 단계와; 제2절연층을 상기 제2반도체 위에 침착시키는 단계와, 제3반도체 층을 상기 제2절연층 위에 침착시키는 단계와, 상기 제3반도체 층을 상기 제2절연층 위에 침착시키는 단계와; 상기 제3반도체 층을 도핑하는 단계; 및 주입에 의해 상기 기판내에 소스 및 드레인 영역을 형성하는 단계를 포함하는 것을 특징으로 하는 소거 가능 메모리 소자 제조 공정.

#### 청구항 16

제15항에 있어서. 주변 소자들을 상기 기판에 동시에 제조하는 단계를 더 포함하는 것을 특징으로 하는 소거 가능 메모리 소자 제조 공정.

#### 청구항 17

소스 및 드레인 영역과 제1게이트와 부유 게이트를 가지며, 복수의 워드라인과 상기 워드라인들과 직교하는 복수의 비트라인 및 복수의 공통 소스라인에 의해 상호 접속되는 복수의 메모리 셀들을 포함하는 메모리 어레이내에서 선택된 셀에 기록을 하기 위한 방법에 있어서, 상기 선택된 연결되는 워드라인과 비트라인을 식별하는 단계와; 상기 식별된 워드라인에 연결된 셀들을 플래시 프로그래밍 하는 단계와; 상기 선택된 셀상의 전류를 감지하는 단계와; 상기 감지된 전류를 소망 값에 비교하는 단계; 및 상기 감지된 전류가 상기 소망의 기준 값 보다 더 작은 경우 상기 프로그래밍을 반복하는 단계를 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 18

제17항에 있어서, 상기 프로그래밍 단계는 상기 기판상의 전압보다 더 높은 전압을 상기 식별된 워드라인에 인가하는 단계를 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 19

제17항에 있어서, 상기 프로그래밍 단계는 전자들을 상기 셀의 부유 게이트로 주입하는 단계를 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 20

제17항에 있어서, 상기 감지된 전류가 상기 기준 값 보다 더 큰 경우 상기 선택된 셀을 선택적으로 소거하는 단계를 더 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 21

제20항에 있어서, 상기 소거 단계는 상기 선택된 웨드라인상의 전압 보다 더 큰 전압을 상기 식별된 비트 라인에 인가하는 단계를 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 22

제20항에 있어서, 상기 소거 단계는 전자들을 상기 부유 게이트에서 제거하는 단계 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 23

전류 기준 값들의 복수의 범위를 식별하는 단계를 더 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 24

제23항에 있어서, 상기 선택된 셀을 소거하는 단계는, 상기 선택된 셀을 위한 적당한 전류 기준 값을 상기 전류 기준 값들의 복수의 범위로부터 결정하는 단계와; 전자를 상기 선택된 셀에서 제거하는 단계와; 상기 선택된 셀상의 전류를 감지하는 단계와; 감지된 전류를 상기 적당한 전류 기준 값에 비교하는 단계; 및 상기 감지된 전류가 상기 적당한 기준 범위내에 있을때까지 상기 제거, 감지, 비교 단계를 반복하는 단계를 포함하는 것을 특징으로 하는 셀로의 기록 방법.

#### 청구항 25

전기적으로 프로그래밍 가능한 ROM트랜지스터와 주변 소자용 MOS 트랜지스터를 동일 기판내에서 제조하기 위한 반도체 소자 제조 공정에 있어서, 균일 두께의 제1절연막을 상기 기판의 제1 및 제2영역 위에 형성하는 단계와; 제1반도체 층을 상기 제1절연막 위에 침착시키는 단계와; 상기 제1반도체 층과 제1절연막을 선택적으로 에칭하여, 상기 기판의 제1 및 제2활성 영역을 지정하는 단계와; 상기 제1 및 제1 활성 영역을 포함하지 않는 상기 기판 영역내에 필드 절연 영역을 설치하는 단계와; 제2반도체 층을 상기 제1반도체 층과 필드 절연 영역 위에 침착시키는 단계로서, 상기 제1 및 제2 반도체 층이 상기 기판내에서 부유 게이트를 포함하는 단계와; 상기 제2반도체 층을 선택적으로 에칭하여, 상기 제1활성 영역내에서 상기 필드 절연 영역들의 일부를 노출시키는 단계와; 제2절연층을 상기 제2반도체 층과 상기 필드 절연 영역들의 노출된 부분 위에 형성하는 단계와; 상기 제2절연층을 선택적으로 에칭하여 상기 제2활성 영역내의 상기 필드 절연 영역들의 부분 위에서 상기 제2반도체 층을 노출시키는 단계와; 제3반도체 층을 상기 제2절연층 위에 침착시키는 단계와; 상기 제3반도체 층과, 상기 제2 절연층, 및 상기 제2 및 제1 반도체 층을 선택적으로 에칭하여, 상기 제1 및 제2활성 영역의 부분들을 선택적으로 노출시키는 단계; 및 도편트들을 상기 제1활성 영역내로 주입하는 단계를 포함하는 것을 특징으로 하는 전기적으로 프로그래밍 가능한 ROM트랜지스터와 주변 소자용 MOS트랜지스터 제조 공정.

#### 청구항 26

제25항에 있어서, 상기 ROM 트랜지스터는 EEPROM을 포함하며, 상기 제1반도체 층의 침착 이전에 제3절연 층을 상기 제1절연층 위에 선택적으로 형성시키는 단계를 더 포함하는 것을 특징으로 하는 전기적으로 프로그래밍 가능한 ROM 트랜지스터와 주변 소자용 MOS 트랜지스터 제조 공정.

#### 도면

##### 도면1

도면2a

도면2b

도면3

도면4a

도면4b

도면5a

도면5b

도면5c

도면5d

도면5e

도면5f

도면5g

도면5h

도면5i

도면5j

도면6a

도면6b

도면6c

도면7

도면8

도면9a

도면9b

도면9c

도면9d

도면9e

도면9f

도면9g

도면9h

도면9i

도면9j

도면10a

## 도면 10b