(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7650293号**

**(P7650293)**

(45)発行日 令和7年3月24日(2025.3.24)

(24)登録日 令和7年3月13日(2025.3.13)

(51)国際特許分類

H 01 L 25/10 (2006.01)

H 01 L 25/18 (2023.01)

H 10 B 80/00 (2023.01)

H 01 L 25/07 (2006.01)

H 01 L 25/065 (2023.01)

F I

H 01 L 25/14 B

H 10 B 80/00

H 01 L 25/08 H

請求項の数 17 (全23頁)

(21)出願番号 特願2022-566266(P2022-566266)

(86)(22)出願日 令和4年8月4日(2022.8.4)

(65)公表番号 特表2024-527645(P2024-527645)

A)

(43)公表日 令和6年7月26日(2024.7.26)

(86)国際出願番号 PCT/CN2022/110253

(87)国際公開番号 WO2024/007405

(87)国際公開日 令和6年1月11日(2024.1.11)

審査請求日 令和4年10月28日(2022.10.28)

(31)優先権主張番号 202210853472.6

(32)優先日 令和4年7月8日(2022.7.8)

(33)優先権主張国・地域又は機関

中国(CN)

(73)特許権者 522246670

チャンシン メモリー テクノロジーズ

インコーポレイテッド

C H A N G X I N M E M O R Y T E C

H N O L O G I E S , I N C .

中華人民共和国 2 3 0 6 0 1 アンファイ

プロヴィンス ハーフェイ シティ エコ

ノミック アンド テクノロジカル ディ

ベロップメント エリア エアポート イ

ンダストリアル パーク シンイエ アベ

ニュー ナンバー 3 8 8

100205659

弁理士 斎藤 拓也

100185269

弁理士 小菅 一弘

最終頁に続く

(54)【発明の名称】 半導体パッケージ構造及び製造方法

**(57)【特許請求の範囲】****【請求項1】**

半導体パッケージ構造であつて、第1パッケージ構造及び第2パッケージ構造を備え、前記第1パッケージ構造は、介在層及び成形材料を備え、前記介在層に第1接続パッドが設けられ、前記成形材料は、前記介在層を包み、前記第1接続パッドと共に面であり、前記第2パッケージ構造は、前記介在層の上に設けられ、前記第1接続パッドに電気接続され、

前記第1パッケージ構造と前記第2パッケージ構造との間に隙間があり、

前記第1パッケージ構造は更に、

基板、少なくとも1つの第1チップ積層体及び少なくとも1つの第2チップ積層体を備え、

前記少なくとも1つの第1チップ積層体は、前記基板の上に設けられ、

前記少なくとも1つの第2チップ積層体は、前記基板の上に設けられ、前記第1チップ積層体から間隔をあけて設けられ、

前記介在層は、前記第1チップ積層体及び前記第2チップ積層体上に設けられ、前記第1チップ積層体と前記第2チップ積層体は、前記介在層を介して電気接続され、前記第1チップ積層体の最上部のチップ又は前記第2チップ積層体の最上部のチップは、リード線を介して前記基板に接続される、

半導体パッケージ構造。

**【請求項2】**

前記第1チップ積層体は1つの第1チップを備え、前記第2チップ積層体は1つの第2

チップを備え、

前記第1チップは、前記介在層を介して前記第2チップに電気接続される、

請求項1に記載の半導体パッケージ構造。

**【請求項3】**

前記第1チップ又は前記第2チップは、リード線を介して前記基板に接続される、

請求項2に記載の半導体パッケージ構造。

**【請求項4】**

前記第1チップ積層体は、積み重ねられた第1下部チップ及び第1上部チップを備え、

前記第2チップ積層体は、積み重ねられた第2下部チップ及び第2上部チップを備え、

前記介在層は、前記第1上部チップ及び前記第2上部チップの上に設けられ、前記第1

上部チップ及び前記第2上部チップは、介在層を介して電気接続される、

請求項1に記載の半導体パッケージ構造。

**【請求項5】**

前記第1上部チップ又は前記第2上部チップは、リード線を介して前記基板に接続され

る、

請求項4に記載の半導体パッケージ構造。

**【請求項6】**

前記第1下部チップ及び前記第2下部チップはそれぞれ、リード線を介して前記基板に

接続される、

請求項5に記載の半導体パッケージ構造。

10

**【請求項7】**

前記第1下部チップは、前記第1上部チップに電気接続され、前記第2下部チップは、

前記第2上部チップに電気接続される、

請求項5に記載の半導体パッケージ構造。

**【請求項8】**

前記介在層は、

第1表面、第2表面及び信号チャネルを備え、

前記第1表面の上に、前記第1接続パッドが設けられ、

前記第2表面は、前記第1表面に対向して設けられ、前記第2表面の上に第2接続パッ

ドが設けられ、

20

前記信号チャネルは、前記第1接続パッド及び前記第2接続パッドに接続される、

請求項1～7のいずれか一項に記載の半導体パッケージ構造。

**【請求項9】**

前記第1チップ積層体及び前記第2チップ積層体はリード線パッドを備え、前記リード

線パッドは、再配線層を介して前記第2接続パッドに接続される、

請求項8に記載の半導体パッケージ構造。

**【請求項10】**

前記第1チップ積層体と前記第2チップ積層体とを接続する前記第2接続パッド同士は

、再配線層を介して接続される、

請求項8に記載の半導体パッケージ構造。

30

**【請求項11】**

前記第1チップ積層体及び前記第2チップ積層体は、接着層を介して前記基板の上に設

けられる、

請求項1に記載の半導体パッケージ構造。

**【請求項12】**

前記基板は仮想チャネルを備え、前記接着層は前記仮想チャネルの上に位置し、前記仮

想チャネルの熱伝導係数は、前記接着層の熱伝導係数より大きい、

請求項1に記載の半導体パッケージ構造。

**【請求項13】**

前記半導体パッケージ構造は更に、充填層を備え、前記充填層は前記隙間を充填する、

40

請求項 1 に記載の半導体パッケージ構造。

**【請求項 1 4】**

前記充填層の熱伝導係数は、前記成形材料の熱伝導係数より大きい、

請求項 1\_3 に記載の半導体パッケージ構造。

**【請求項 1 5】**

前記充填層の充填材体積は、前記成形材料の充填材体積より小さい、

請求項 1\_3 に記載の半導体パッケージ構造。

**【請求項 1 6】**

前記接着層は、第 1 接着層及び第 2 接着層を備え、前記第 2 接着層は、前記第 1 接着層の上に位置し、前記第 2 接着層の弾性率は、前記第 1 接着層の弾性率より大きい、

請求項 1\_1 に記載の半導体パッケージ構造。

**【請求項 1 7】**

半導体パッケージ構造の製造方法であって、

第 1 パッケージ構造を提供することであって、前記第 1 パッケージ構造は、介在層及び成形材料を備え、前記介在層に第 1 接続パッドが設けられ、前記成形材料は、前記介在層を包み、前記第 1 接続パッドと共に面である、ことと、

第 2 パッケージ構造を前記介在層の上に設けるように前記第 2 パッケージ構造を提供することであって、前記第 2 パッケージ構造は、前記第 1 接続パッドに電気接続される、ことと、を含み、

前記第 1 パッケージ構造と前記第 2 パッケージ構造との間に隙間があり、

前記第 1 パッケージ構造は更に、

基板、少なくとも 1 つの第 1 チップ積層体及び少なくとも 1 つの第 2 チップ積層体を備え、前記少なくとも 1 つの第 1 チップ積層体は、前記基板の上に設けられ、

前記少なくとも 1 つの第 2 チップ積層体は、前記基板の上に設けられ、前記第 1 チップ積層体から間隔をあけて設けられ、

前記介在層は、前記第 1 チップ積層体及び前記第 2 チップ積層体上に設けられ、前記第 1 チップ積層体と前記第 2 チップ積層体は、前記介在層を介して電気接続され、前記第 1 チップ積層体の最上部のチップ又は前記第 2 チップ積層体の最上部のチップは、リード線を介して前記基板に接続される、

半導体パッケージ構造の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

( 関連出願への相互参照 )

本願は、2022年7月8日に中国特許局に提出された、出願番号が 202210853472.6 であり、発明の名称が「半導体パッケージ構造及び製造方法」である中国特許出願に基づいて提出されるものであり、当該中国特許出願の優先権を主張し、当該中国特許出願の全ての内容が参照として本願に援用される。

**【0 0 0 2】**

本開示は、半導体技術分野に関し、特に、半導体パッケージ構造及び製造方法に関する。

**【背景技術】**

**【0 0 0 3】**

あらゆる部門、業種及び地域において、電子業界は、より軽く、より速く、より小さく、より信頼度が高く、よりコスト効率の高く、多機能の製品が追求されている。このように多様化する消費者の需要に応えるために、より多くの回路を集積して必要な機能を提供する必要がある。ほとんどの応用において、集積回路の小型化、高性能化、高機能化の需要が高まっている。

**【発明の概要】**

**【0 0 0 4】**

これを鑑みて、本開示の実施例は、半導体パッケージ構造及び製造方法を提供する。

10

20

30

40

50

**【 0 0 0 5 】**

本開示の実施例の第1態様によれば、半導体パッケージ構造を提供し、前記半導体パッケージ構造は、

第1パッケージ構造及び第2パッケージ構造を備え、

前記第1パッケージ構造は、介在層及び成形材料を備え、前記介在層に第1接続パッドが設けられ、前記成形材料は、前記介在層を包み、前記第1接続パッドと共に面であり、

前記第2パッケージ構造は、前記介在層の上に設けられ、前記第1接続パッドに電気接続され、

ここで、前記第1パッケージ構造と前記第2パッケージ構造との間に隙間がある。

**【 0 0 0 6 】**

10

いくつかの実施例では、前記第1パッケージ構造は更に、

基板、少なくとも1つの第1チップ積層体及び少なくとも1つの第2チップ積層体を備え、

前記少なくとも1つの第1チップ積層体は、前記基板の上に設けられ、

前記少なくとも1つの第2チップ積層体は、前記基板の上に設けられ、前記第1チップ積層体から間隔をあけて設けられ、

ここで、前記介在層は、前記第1チップ積層体及び前記第2チップ積層体上に設けられる。

**【 0 0 0 7 】**

20

いくつかの実施例では、前記第1チップ積層体は1つの第1チップを備え、前記第2チップ積層体は1つの第2チップを備え、

ここで、前記第1チップは、前記介在層を介して前記第2チップに電気接続される。

**【 0 0 0 8 】**

いくつかの実施例では、前記第1チップ又は前記第2チップは、リード線を介して前記基板に接続される。

**【 0 0 0 9 】**

いくつかの実施例では、前記第1チップ積層体は、積み重ねられた第1下部チップ及び第1上部チップを備え、前記第2チップ積層体は、積み重ねられた第2下部チップ及び第2上部チップを備え、

ここで、前記介在層は、前記第1上部チップ及び前記第2上部チップの上に設けられ、前記第1上部チップ及び前記第2上部チップは、介在層を介して電気接続される。

30

**【 0 0 1 0 】**

いくつかの実施例では、前記第1上部チップ又は前記第2上部チップは、リード線を介して前記基板に接続される。

**【 0 0 1 1 】**

いくつかの実施例では、前記第1下部チップ及び前記第2下部チップはそれぞれ、リード線を介して前記基板に接続される。

**【 0 0 1 2 】**

いくつかの実施例では、前記第1下部チップは、前記第1上部チップに電気接続され、前記第2下部チップは、前記第2上部チップに電気接続される。

40

**【 0 0 1 3 】**

いくつかの実施例では、前記介在層は、

第1表面、第2表面及び信号チャネルを備え、

前記第1表面の上に、前記第1接続パッドが設けられ、

前記第2表面は、前記第1表面に対向して設けられ、前記第2表面の上に第2接続パッドが設けられ、

前記信号チャネルは、前記第1接続パッド及び前記第2接続パッドに接続される。

**【 0 0 1 4 】**

いくつかの実施例では、前記第1チップ積層体及び前記第2チップ積層体はリード線パッドを備え、前記リード線パッドは、再配線層を介して前記第2接続パッドに接続される。

50

**【0015】**

いくつかの実施例では、前記第1チップ積層体及び前記第2チップ積層体に接続される前記第2接続パッド同士は再配線層を介して接続される。

**【0016】**

いくつかの実施例では、前記第1チップ積層体及び前記第2チップ積層体は、接着層を介して前記基板の上に設けられる。

**【0017】**

いくつかの実施例では、前記基板は仮想チャネルを備え、前記接着層は前記仮想チャネルの上に位置し、前記仮想チャネルの熱伝導係数は、前記接着層の熱伝導係数より大きい。

**【0018】**

いくつかの実施例では、前記半導体パッケージ構造は更に、充填層を備え、前記充填層は前記隙間を充填する。

**【0019】**

いくつかの実施例では、前記充填層の熱伝導係数は、前記成形材料の熱伝導係数より大きい。

**【0020】**

いくつかの実施例では、前記充填層の充填材体積は、前記成形材料の充填材体積より小さい。

**【0021】**

いくつかの実施例では、前記接着層は、第1接着層及び第2接着層を備え、前記第2接着層は、前記第1接着層の上に位置し、前記第2接着層の弾性率は、前記第1接着層の弾性率より大きい。

**【0022】**

本開示の実施例の第2態様によれば、半導体パッケージ構造の製造方法を提供し、前記半導体パッケージ構造の製造方法は、

第1パッケージ構造を提供することであって、前記第1パッケージ構造は、介在層及び成形材料を備え、前記介在層に第1接続パッドが設けられ、前記成形材料は、前記介在層を包み、前記第1接続パッドと共に面である、ことと、

前記第2パッケージ構造を前記介在層の上に設けるように第2パッケージ構造を提供することであって、前記第2パッケージ構造は、前記第1接続パッドに電気接続される、ことと、を含み、

ここで、前記第1パッケージ構造と前記第2パッケージ構造との間に隙間がある。

**【0023】**

本開示の実施例では、介在層を設けることにより、介在層を介して第1パッケージ構造と第2パッケージ構造を接続し、このように、異なる容量のパッケージ構造間の相互接続を実現し、これによって、異なるパッケージ構造間の組み合わせはより柔軟になり、これにより、当該半導体パッケージ構造は異なる適用場面に適用することができる。さらに、第1パッケージ構造と第2パッケージ構造は個別にパッケージングされたものであるため、第1パッケージ構造及び第2パッケージ構造をそれぞれ検証することができ、これにより、失効分析をより迅速に行うことができ、それによって、半導体パッケージ構造が形成された後、構造全体を検証しなくてもよい。第2パッケージ構造と第1パッケージ構造との間に隙間があり、したがって、両者の間隔を増加し、これにより、第2パッケージ構造の発熱効率を向上させ、チップに対する熱の影響を低減させることができる。

**【図面の簡単な説明】****【0024】**

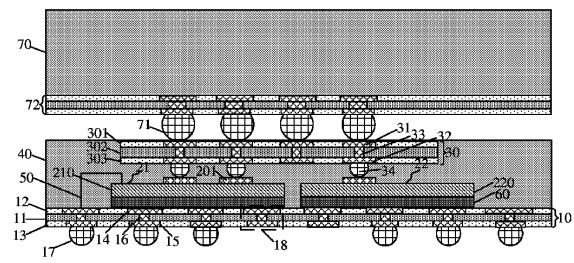

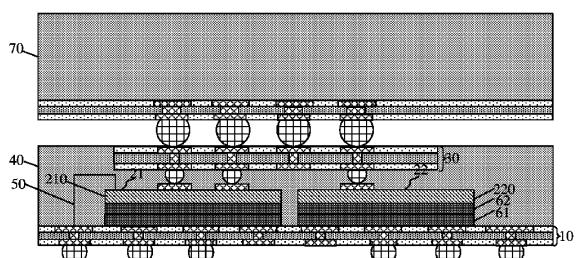

【図1】本開示の実施例で提供される半導体パッケージ構造の概略構造図である。

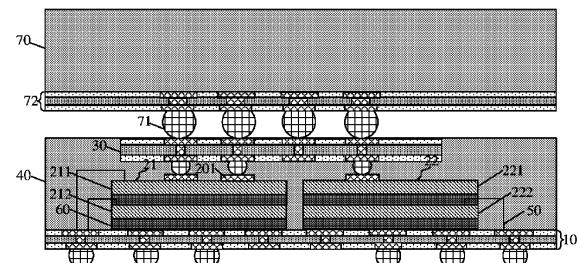

【図2】本開示の実施例で提供される半導体パッケージ構造の他の例である。

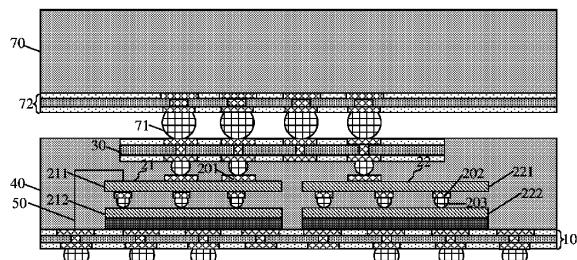

【図3】本開示の実施例で提供される半導体パッケージ構造の他の例である。

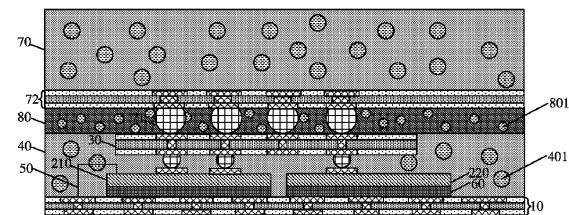

【図4】本開示の実施例で提供される半導体パッケージ構造の他の例である。

【図5】本開示の実施例で提供される半導体パッケージ構造の他の例である。

10

20

30

40

50

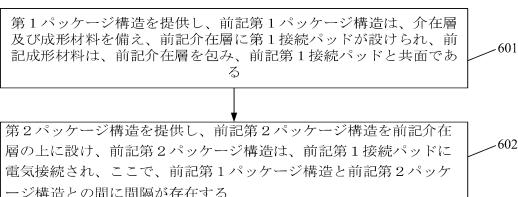

【図6】本開示の実施例で提供される半導体パッケージ構造の製造方法の例示的なフローチャートである。

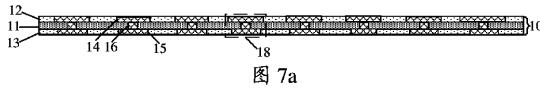

【図7a】本開示の実施例で提供される、製造過程における半導体パッケージ構造のデバイスの概略構造図である。

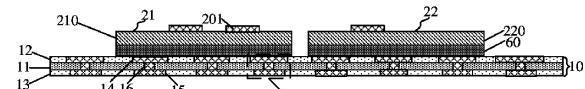

【図7b】本開示の実施例で提供される、製造過程における半導体パッケージ構造のデバイスの概略構造図である。

【図7c】本開示の実施例で提供される、製造過程における半導体パッケージ構造のデバイスの概略構造図である。

【図7d】本開示の実施例で提供される、製造過程における半導体パッケージ構造のデバイスの概略構造図である。

【図7e】本開示の実施例で提供される、製造過程における半導体パッケージ構造のデバイスの概略構造図である。

【図7f】本開示の実施例で提供される、製造過程における半導体パッケージ構造のデバイスの概略構造図である。

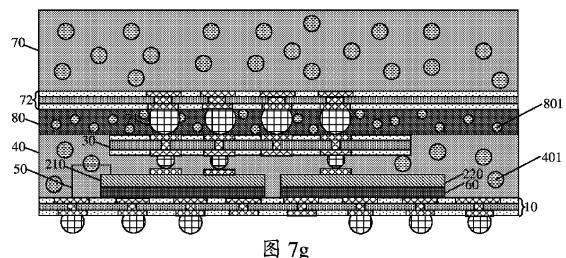

【図7g】本開示の実施例で提供される、製造過程における半導体パッケージ構造のデバイスの概略構造図である。

#### 【発明を実施するための形態】

##### 【0025】

本開示の実施例又は従来技術における技術的解決策をより明確に説明するために、以下は、実施例で使用される図面について簡単に紹介する。上記に説明される図面は、本開示のいくつかの実施例に過ぎず、当業者にとって、創造的な労力を払わなくても、これらの図面に従って他の図面を得ることもできることは自明である。

##### 【0026】

以下、図面を参照して本開示で開示される例示的な実施形態をより詳細に説明する。図面において、本開示の例示的な実施形態を示しているが、理解すべきこととして、本開示は様々な形態で実施でき、本明細書に記載された具体的な実施形態に限定されるべきではない。むしろ、これらの実施形態は、本開示をより徹底的に理解させるために提供され、本開示で開示される完全な範囲を当業者に伝えることができる。

##### 【0027】

下記では、本開示を徹底的に理解させるために多くの具体的な詳細を提供する。しかし、当業者にとって、これらの1つ又は複数の詳細が記載されてなくても本開示が実施できることは自明である。他の例では、本開示との混同を避けるために、当技術分野でよく知られているいくつかの技術的特徴について説明しておらず、つまり、本明細書では、実際の実施例の全ての特徴を説明しておらず、周知の機能及び構造を詳細に説明しない。

##### 【0028】

図面において、層、領域、要素のサイズ及びその相対的なサイズは、明確にするために誇張されている可能性がある。同じ符号は同じ要素を表す。

##### 【0029】

理解すべきこととして、要素又は層が「他の要素又は層の上に位置する」、「他の要素又は層に隣接する」、「他の要素又は層に接続される」又は「他の要素又は層に結合される」場合、当該要素又は層は、他の要素又は層の上に直接に位置してもよいし、他の要素又は層に直接に隣接してもよいし、他の要素又は層に直接に接続されてもよいし、他の要素又は層に直接に結合されてもよく、或いは、両者間に介在する要素又は層が存在してもよい。逆に、要素が「他の要素又は層の上に直接に位置する」、「他の要素又は層に直接に隣接する」、「他の要素又は層に直接に接続される」又は「他の要素又は層に直接に結合される」場合、介在する要素又は層が存在しない。理解すべきこととして、第1、第2、第3などの用語を使用して各要素、構成要素、領域、層及び/又は部分を説明することができるが、これらの要素、要素、領域、層及び/又は部分は、これらの用語に限定されるべきではない。これらの用語は、ある要素、構成要素、領域、層又は部分を別の要素、構成要素、領域、層又は部分と区別するためにのみ使用される。したがって、本開示の教

10

20

30

40

50

示から逸脱することなく、後述する第1要素、構成要素、領域、層又は部分は、第2要素、構成要素、領域、層又は部分として表されてもよい。第2要素、構成要素、領域、層又は部分について論じる場合、第1要素、構成要素、領域、層又は部分は本開示において必ずしも存在することを示すものではない。

#### 【0030】

本明細書では、「…下に位置する」、「…下にある」、「下の…」、「…の下に位置する」、「…の上に位置する」、「上の」などの空間関係用語は、説明を容易にするために、図面の1つの要素又は特徴と他の要素又は特徴との関係を説明するために使用されてもよい。理解すべきこととして、図に示されている向きに加えて、空間関係用語は、使用中及び動作中のデバイスの異なる向きを更に含む。例えば、図面におけるデバイスが裏返される場合、「他の要素下に位置する」又は「他の要素の下に位置する」又は「他の要素の下にある」という要素又は特徴の向きが他の要素又は特徴の「上」に位置するという向きになると説明される。したがって、「…下に位置する」及び「…下にある」という用語は、上と下の2つの向きを含み得る。デバイスは、他の向き(90度回転又は他の向き)を含んでもよく、本明細書で使用される空間用語はそれに応じて解釈される。

10

#### 【0031】

本明細書で使用される用語は、具体的な実施例を説明することを目的としたものであり、本開示を限定するものではない。本明細書において、単数形の「1」、「1つ」及び「前記／当該」は、文脈で他の方式を明記しない限り、複数形を含んでもよい。更に理解すべきこととして、「構成」及び／又は「含む」という用語が本明細書で使用される場合、記載された特徴、整数、ステップ、動作、要素及び／又は構成要素の存在が明確化されている以外に、1つ又は複数の他の特徴、整数、ステップ、動作、要素及び／又は構成要素の存在又は追加は除外されない。本明細書において、「及び／又は」という用語は、記載されている関連の項目の任意及び全ての組み合わせを含む。

20

#### 【0032】

本開示を徹底的に理解させるために、以下の説明では、本開示の技術的解決策を詳説するために詳細なステップ及び詳細な構造を提供する。本開示の好ましい実施例の詳細な説明は以下のとおりであり、しかし、本開示は、これらの詳細な説明に加えて、他の実施形態を有してもよい。

30

#### 【0033】

本開示の実施例は半導体パッケージ構造を提供する。図1は、本開示の実施例で提供される半導体パッケージ構造の概略構造図である。

#### 【0034】

図1を参照すると、前記半導体パッケージ構造は、第1パッケージ構造及び第2パッケージ構造を備え、

前記第1パッケージ構造は、介在層30及び成形材料40を備え、前記介在層30に第1接続パッド31が設けられ、前記成形材料40は、前記介在層30を包み、前記第1接続パッド31と共に面であり、

前記第2パッケージ構造70は、前記介在層30上に設けられ、前記第1接続パッド31に電気接続され、

40

ここで、前記第1パッケージ構造と前記第2パッケージ構造70との間に隙間がある。

#### 【0035】

本開示の実施例では、介在層を設けることにより、介在層を介して第1パッケージ構造と第2パッケージ構造を接続し、このように、異なる容量のパッケージ構造間の相互接続を実現し、これによって、異なるパッケージ構造間の組み合わせはより柔軟になり、これにより、当該半導体パッケージ構造は異なる適用場面に適用することができる。さらに、第1パッケージ構造と第2パッケージ構造は個別にパッケージングされたものであるため、第1パッケージ構造及び第2パッケージ構造をそれぞれ検証することができ、これにより、失効分析をより迅速に行うことができ、それによって、半導体パッケージ構造が形成された後、構造全体を検証しなくてもよい。第2パッケージ構造と第1パッケージ構造と

50

の間に隙間があり、したがって、両者の間隔を増加し、これにより、第2パッケージ構造の発熱効率を向上させ、チップ（第1パッケージ構造）に対する熱の影響を低減させることができる。第2パッケージ構造は第1パッケージ構造上に着脱可能に設けられ、したがって、異なる容量の第2パッケージ構造を第1パッケージ構造上に設け、第1パッケージ構造の使用率を向上させる。

#### 【0036】

1つの実施例では、前記第1パッケージ構造は更に、基板10、少なくとも1つの第1チップ積層体21及び少なくとも1つの第2チップ積層体22を備え、前記少なくとも1つの第1チップ積層体21は、前記基板10上に設けられ、前記少なくとも1つの第2チップ積層体22は、前記基板10上に設けられ、前記第1チップ積層体21から間隔を開けて設けられ、ここで、前記介在層30は、前記第1チップ積層体21及び前記第2チップ積層体22上に設けられる。

10

#### 【0037】

本開示の実施例では、介在層を介して第1チップ積層体と第2チップ積層体とを接続し、配線の数量を低減し、ワイヤーボンディング工程を省くことができる。

#### 【0038】

いくつかの実施例では、前記基板10は再配線（REDISTRIBUTION）基板であってもよい。

20

#### 【0039】

前記基板10は、基板ベース11と、前記基板ベース11の上面及び下面にそれぞれ設けられる基板上部絶縁誘電体層12と基板下部絶縁誘電体層13と、を備える。

#### 【0040】

前記基板ベース11は、シリコン基板、ゲルマニウム基板、シリコン・ゲルマニウム基板、炭化ケイ素基板、シリコン・オン・インシュレータ（SOI：Silicon On Insulator）基板又はゲルマニウム・オン・インシュレータ（GOI：Germanium On Insulator）基板等であってもよく、或いは、他の元素半導体又は化合物半導体を含む基板（例えば、ガラス基板又はIII-V族化合物基板（例えば、窒化ガリウム基板又はヒ化ガリウム基板等））であってもよく、或いは、積層構造（例えば、Si/SiGe等）であってもよく、或いは、他の外延構造（例えば、ゲルマニウム・シリコン・オン・インシュレータ（SGOI））等であってもよい。

30

#### 【0041】

前記基板上部絶縁誘電体層12及び前記基板下部絶縁誘電体層13はソルダーマスク層であってもよく、例えば、前記基板上部絶縁誘電体層12及び前記基板下部絶縁誘電体層13の材料はソルダーレジストであってもよい。

#### 【0042】

前記基板10は更に、前記基板上部絶縁誘電体層12内の基板上部接続パッド14と、前記基板下部絶縁誘電体層13内の基板下部接続パッド15と、前記基板ベース11を貫通して前記基板上部接続パッド14及び前記基板下部接続パッド15を接続する基板接続貫通ビア16と、を備える。

40

#### 【0043】

前記基板上部接続パッド14及び前記基板下部接続パッド15の材料は、アルミニウム、銅、ニッケル、タンクステン、白金、金のうちの少なくとも1つを含み得る。前記基板接続貫通ビア16はシリコン貫通ビア（TSV）であってもよい。

#### 【0044】

基板上部接続パッド14と基板下部接続パッド15は基板接続貫通ビア16を介して接続され、これにより、信号を伝送することができる。同時に、隣接する2つの基板上部接続パッド14は、再配線層を介して接続されてもよく、これにより、基板における信号の伝送を遂行することができる。

#### 【0045】

前記基板10は更に、基板接続バンプ17を備え、前記基板接続バンプ17は、半導体

50

パッケージ構造を外部装置に電気接続し、外部装置からチップ積層体を動作させるための制御信号、電力信号及び接地信号のうちの少なくとも1つを受信するか、又は外部装置からチップ積層体に記憶されているデータ信号を受信してもよく、チップ積層体内のデータを外部装置に提供してもよい。

#### 【0046】

前記基板接続バンプ17は導電材料を含む。本開示の実施例では、前記基板接続バンプ17はハンダボールであり、理解できることとして、本開示の実施例で提供される基板接続バンプの形状は本開示の実施例における従属的かつ実現可能な具体的な実施形態に過ぎず、本開示を限定するものではなく、前記基板接続バンプは他の形状構造であってもよい。基板接続バンプの数、間隔及び位置は、何らかの特定の配置に限定されず、様々な変更が行われてもよい。

10

#### 【0047】

1つの実施例では、前記第1チップ積層体21及び前記第2チップ積層体22は、接着層60を介して前記基板10に設けられる。

#### 【0048】

前記第1チップ積層体21及び前記第2チップ積層体22のチップは、動的ランダムアクセスメモリ(DRAM)チップ、静的ランダムアクセスメモリ(SRAM)チップ、フラッシュメモリチップ、電気消去可能プログラマブル読み取り専用メモリ(EEPROM)チップ、相変化ランダムアクセスメモリ(PRAM)チップ、磁気ランダムアクセスメモリ(MRAM)チップ又は抵抗ランダムアクセスメモリ(RRAM)チップであってもよい。

20

#### 【0049】

前記接着層60はDAF膜であってもよい。

#### 【0050】

1つの実施例では、図5に示すように、前記接着層は、第1接着層61、及び前記第1接着層61の上に位置する第2接着層62を備え、前記第2接着層62の弾性率は前記第1接着層61の弾性率より大きい。

#### 【0051】

本開示の実施例では、第1接着層は基板に接続されており、主として接着の役割を果たし、第2接着層は、チップに接続されており、主としてチップの反りを防止する役割を果たす。第2接着層の弾性率が比較的高いため、切断中に反りが生じず、第1接着層は比較的低い弾性率を有するため、後続の工程で基板とチップ的の接合力に影響を与えない。前記基板10は更に、仮想チャネル18を備え、前記接着層60は、前記仮想チャネル18の上に位置し、前記仮想チャネル18の熱伝導係数は前記接着層60の熱伝導係数より大きい。

30

#### 【0052】

本開示の実施例では、仮想チャネルの熱伝導係数は接着層の熱伝導係数より大きく、チップの動作によって生じる熱を仮想チャネルでより多く放散することができ、放熱能力を向上させ、デバイス性能への影響を低減することができる。

#### 【0053】

前記仮想チャネル18は、基板上部接続パッド14、基板下部接続パッド15及び基板接続貫通ビア16で構成されるが、仮想チャネル18の下に基板接続バンプ17が形成されず、信号伝送を実現できず、発熱処理にのみ使用される。

40

#### 【0054】

いくつかの実施例では、仮想チャネルの熱伝導係数は、信号伝送の役割を果たす、基板上部接続パッド14、基板下部接続パッド15及び基板接続貫通ビア16で構成された構造の熱伝導係数より大きく、信号伝送に対する熱の影響を低減することができる。

#### 【0055】

図1に示すように、前記第1チップ積層体21は1つの第1チップ210を備え、前記第2チップ積層体22は1つの第2チップ220を備え、ここで、前記第1チップ210

50

は、前記介在層 3 0 を介して前記第 2 チップ 2 2 0 に電気接続される。

**【 0 0 5 6 】**

1 つの実施例では、前記第 1 チップ 2 1 0 又は前記第 2 チップ 2 2 0 は、リード線 5 0 を介して前記基板 1 0 に接続される。

**【 0 0 5 7 】**

図 1 に示す実施例では、前記第 1 チップ 2 1 0 及び前記第 2 チップ 2 2 0 は、介在層 3 0 を介して接続され、前記第 1 チップ 2 1 0 は、リード線 5 0 を介して基板 1 0 に接続され、第 2 チップ 2 2 0 を基板 1 0 に間接的に接続する。他の実施例では、第 2 チップがリード線を介して基板に接続され、第 1 チップを基板に間接的に接続してもよい。

**【 0 0 5 8 】**

この実施例では、第 1 チップ及び第 2 チップは介在層を介して信号伝送を行うため、第 1 チップ及び第 2 チップのうちの 1 つのみをワイヤーボンディングすることができ、ワイヤーボンディング工程を削減することができる。

**【 0 0 5 9 】**

図 2 は、本開示の別の実施例で提供される半導体パッケージ構造の概略構造図であり、図 3 は、本開示の更に別の実施例で提供される半導体パッケージ構造の概略構造図である。図 2 及び図 3 に示すように、前記第 1 チップ積層体 2 1 は、積み重ねられた第 1 下部チップ 2 1 2 及び第 1 上部チップ 2 1 1 を備え、前記第 2 チップ積層体 2 2 は、積み重ねられた第 2 下部チップ 2 2 2 及び第 2 上部チップ 2 2 1 を備え、

ここで、前記介在層 3 0 は、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 の上に設けられ、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 は、介在層 3 0 を介して電気接続される。

**【 0 0 6 0 】**

1 つの実施例では、図 2 に示すように、前記第 1 上部チップ 2 1 1 又は前記第 2 上部チップ 2 2 1 は、リード線 5 0 を介して前記基板 1 0 に接続される。

**【 0 0 6 1 】**

前記第 1 下部チップ 2 1 2 及び前記第 2 下部チップ 2 2 2 は、リード線 5 0 を介して前記基板 1 0 にそれぞれ接続される。

**【 0 0 6 2 】**

図 2 に示す実施例では、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 は、介在層 3 0 を介して接続され、前記第 1 上部チップ 2 1 1 は、リード線 5 0 を介して基板 1 0 に接続され、第 2 上部チップ 2 2 1 を基板 1 0 に間接的に接続する。他の実施例では、第 2 上部チップがリード線を介して基板に接続され、第 1 上部チップを基板に間接的に接続してもよい。

**【 0 0 6 3 】**

この実施例では、第 1 上部チップ及び第 2 上部チップは介在層を介して信号伝送を行うため、第 1 上部チップ及び第 2 上部チップのうちの 1 つのみをワイヤーボンディングすることができ、ワイヤーボンディング工程を削減することができる。同時に、第 1 下部チップと第 2 下部チップは、接着層で第 1 上部チップ及び第 2 上部チップから隔離され、信号伝送を実現していないため、第 1 下部チップ及び第 2 下部チップはワイヤーボンディングすることにより基板に接続され、これによって、信号伝送を実現する。

**【 0 0 6 4 】**

1 つの実施例では、図 3 に示すように、前記第 1 下部チップ 2 1 2 は、前記第 1 上部チップ 2 1 1 に電気接続され、前記第 2 下部チップ 2 2 2 は、前記第 2 上部チップ 2 2 1 に電気接続される。

**【 0 0 6 5 】**

具体的に、前記第 1 下部チップ 2 1 2 と前記第 1 上部チップ 2 1 1との間、及び前記第 2 下部チップ 2 2 2 と前記第 2 上部チップ 2 2 1との間は、チップ接続パッド 2 0 2 及びチップ接続ハンダボール 2 0 3、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 内のシリコン貫通ビア（未図示）を介して接続される。

10

20

30

40

50

**【 0 0 6 6 】**

この実施例では、第1下部チップ及び第1上部チップは信号伝送を直接に行うことができ、第2下部チップ及び第2上部チップは信号伝送を直接に行うことができ、第1上部チップ及び第2上部チップは、介在層を介して信号伝送を行ってもよく、したがって、4チップのワイヤーボンディングは一度で済み、ワイヤーボンディング工程を低減し、コストを削減することができる。

**【 0 0 6 7 】**

1つの実施例では、前記介在層30は、第1表面、第2表面及び信号チャネル33を備え、前記第1表面の上に前記第1接続パッド31が設けられ、前記第2表面は、前記第1表面に対向して設けられ、前記第2表面の上に第2接続パッド32が設けられ、前記信号チャネル33は、前記第1接続パッド31及び前記第2接続パッド32に接続される。10

**【 0 0 6 8 】**

前記第1接続パッド31及び前記第2接続パッド32の材料は、アルミニウム、銅、ニッケル、タングsten、白金、金のうちの少なくとも1つを含み得る。

**【 0 0 6 9 】**

前記介在層30は、介在基板302と、前記介在基板302の上面及び下面にそれぞれ位置する介在上部絶縁誘電体層301と介在下部絶縁誘電体層303と、を備える。前記第1接続パッド31は、前記介在上部絶縁誘電体層301内にあり、前記第2接続パッド32は、前記介在下部絶縁誘電体層303内にある。

**【 0 0 7 0 】**

前記介在基板は、シリコン基板、ゲルマニウム基板、シリコン・ゲルマニウム基板、炭化ケイ素基板、シリコン・オン・インシュレータ(SOI: Silicon On Insulator)基板又はゲルマニウム・オン・インシュレータ(GOI: Germanium On Insulator)基板等であってもよく、或いは、他の元素半導体又は化合物半導体を含む基板(例えば、ガラス基板又はIII-V族化合物基板(例えば、窒化ガリウム基板又はヒ化ガリウム基板等))であってもよく、或いは、積層構造(例えば、Si/SiGe等)であってもよく、或いは、他の外延構造(例えば、ゲルマニウム・シリコン・オン・インシュレータ(SGOI))等であってもよい。20

**【 0 0 7 1 】**

前記介在上部絶縁誘電体層301及び前記介在下部絶縁誘電体層303はソルダーマスク層であってもよく、例えば、前記介在上部絶縁誘電体層及び前記介在下部絶縁誘電体層の材料はソルダーレジストであってもよい。30

**【 0 0 7 2 】**

1つの実施例では、前記第1チップ積層体21及び前記第2チップ積層体22はリード線パッド201を備え、前記リード線パッド201は、再配線層を介して前記第2接続パッド32に接続される。

**【 0 0 7 3 】**

この実施例では、前記再配線層(未図示)は、前記第1チップ積層体及び前記第2チップ積層体の表面に位置してもよいし、前記第1チップ積層体及び前記第2チップ積層体の内部に位置してもよい。

**【 0 0 7 4 】**

図1に示すように、前記第2接続パッド32と前記リード線パッド201との間に第1ハンダボール34が形成され、前記第1チップ積層体21及び前記第2チップ積層体22におけるリード線パッド201は、第1ハンダボール34を介して第2接続パッド32に接続される。40

**【 0 0 7 5 】**

1つの実施例では、前記第1チップ積層体21及び前記第2チップ積層体22を接続する前記第2接続パッド32同士は再配線層を介して接続される。

**【 0 0 7 6 】**

この実施例では、前記再配線層は、前記介在層の表面に位置してもよいし、前記介在層

10

20

30

40

50

の内部に位置してもよい。

【0077】

1つの実施例では、前記成形材料40は、前記第1接続パッド31と共に面であり、こうすると、後続に第2パッケージ構造と第1パッケージ構造とが接続された後、第1パッケージ構造と第2パッケージ構造との間に大きな隙間があり、第2パッケージ構造の発熱効率を保証することができる。

【0078】

成形材料の表面が第1接続パッドの表面より高い場合、第1パッケージ構造と第2パッケージ構造との間の隙間が小さくなり、発熱に不利であるとともに、後続に充填層を形成するときに、充填層の充填に不利であり、第1接続パッドの表面が成形材料の表面より高い場合、隙間が大きくなる可能性があるが、成形材料が配線を覆うことができず、配線が露出し、配線の保護に不利である。

10

【0079】

1つの実施例では、前記第2パッケージ構造70は、第2ハンダボール71を備え、前記第2ハンダボール71は、前記介在層30における第1接続パッド31に電気接続される。

【0080】

前記第2パッケージ構造70は、ユニバーサル・ファイル・ストア(UFS:Universal File Store)であってもよい。

20

【0081】

前記第2パッケージ構造70は更に、第2基板72を備え、前記第2基板72の構造は前記基板10の構造と同じであり、ここでは繰り返して説明しない。

【0082】

前記第2ハンダボール71は、前記第2基板72上に位置する。

【0083】

図4は、本開示の別の実施例で提供される半導体パッケージ構造の概略構造図である。図4に示すように、前記半導体パッケージ構造は更に、充填層80を備え、前記充填層80は前記隙間を充填する。

【0084】

前記充填層80の熱伝導係数は、前記成形材料40の熱伝導係数より大きい。

30

【0085】

充填層を設けることにより、第1パッケージ構造と第2パッケージ構造との間に密封した界面を有することができ、第1パッケージ構造及び第2パッケージ構造の金属構造と外気又は他の材料との接触を減らすことができ、熱伝導の役割を果たすことができる。充填層の熱伝導係数が比較的大きいため、充填層からより多くの熱が発散され、第1パッケージ構造に対する熱の影響を低減することができる。充填層の熱伝導係数は大きいが、充填層の熱膨張係数が第1パッケージ構造及び第2パッケージ構造の熱膨張係数と一致するので、充填層の体積変化が小さく、第1パッケージ構造及び第2パッケージ構造に向かって圧を及ぼさないので、構造の安定性を確保することができる。

40

【0086】

いくつかの実施例では、例えば、充填層80内にカーボンナノチューブ充填材が充填されているため、第2パッケージ構造からより多くの熱を吸収するのに役に立ち、第1パッケージ構造に対する熱の影響を低減することができる。

【0087】

前記充填層80の充填材体積は、前記成形材料の充填材体積より小さい。

【0088】

図4に示すように、前記成形材料40における充填材は第1充填材401であり、前記充填層80における充填材は第2充填材801であり、第2充填材801の体積は第1充填材401の体積より小さい。

【0089】

50

前記成形材料 4 0 及び前記充填層 8 0 の主材料はエポキシ樹脂であってもよく、充填材は二酸化ケイ素であってもよい。

#### 【 0 0 9 0 】

この実施例では、成形材料に充填される隙間は比較的大きく、第 1 パッケージ構造と第 2 パッケージ構造との間の隙間は比較的小さいので、流動性の大きい充填層を選択し、充填層の充填材体積は小さく、主体材料の流動性が大きい。

#### 【 0 0 9 1 】

本開示の実施例で提供される半導体パッケージ構造は、パッケージ・オン・パッケージ (P o P : P a c k a g e o n P a c k a g e ) 構造のマルチチップパッケージ (U M C P : U F S M u l t i C h i p P a c k a g e ) に適用することができる。 10

#### 【 0 0 9 2 】

本開示の実施例は、半導体パッケージ構造の製造方法を更に提供し、具体的に、図 6 を参照すると、図 6 に示すように、前記半導体パッケージ構造の製造方法は、以下のステップを含む。

#### 【 0 0 9 3 】

ステップ 6 0 1 において、第 1 パッケージ構造を提供し、前記第 1 パッケージ構造は、介在層及び成形材料を備え、前記介在層に第 1 接続パッドが設けられ、前記成形材料は、前記介在層を包み、前記第 1 接続パッドと共に面である。

#### 【 0 0 9 4 】

ステップ 6 0 2 において、第 2 パッケージ構造を提供し、前記第 2 パッケージ構造を前記介在層の上に設け、前記第 2 パッケージ構造は、前記第 1 接続パッドに電気接続され、ここで、前記第 1 パッケージ構造と前記第 2 パッケージ構造との間に間隔が存在する。 20

#### 【 0 0 9 5 】

以下、具体的な実施例を参考して、本開示の実施例で提供される半導体パッケージ構造の製造方法を更に詳細に説明する。

#### 【 0 0 9 6 】

図 7 a ~ 図 7 g は、本開示の実施例で提供される、製造過程における半導体パッケージ構造の概略構造図である。

#### 【 0 0 9 7 】

先ず、図 7 a ~ 図 7 e を参照すると、ステップ 6 0 1 を実行し、第 1 パッケージ構造を提供し、前記第 1 パッケージ構造は、介在層 3 0 及び成形材料 4 0 を備え、前記介在層 3 0 に第 1 接続パッド 3 1 が設けられ、前記成形材料 4 0 は、前記介在層 3 0 を包み、前記第 1 接続パッド 3 1 と共に面である。 30

#### 【 0 0 9 8 】

具体的に、図 7 a を参照すると、基板 1 0 を提供する。

#### 【 0 0 9 9 】

いくつかの実施例では、前記基板 1 0 は再配線基板であってもよい。

#### 【 0 1 0 0 】

前記基板 1 0 は、基板ベース 1 1 と、前記基板ベース 1 1 の上面及び下面にそれぞれ設けられる基板上部絶縁誘電体層 1 2 と基板下部絶縁誘電体層 1 3 と、を備える。 40

#### 【 0 1 0 1 】

前記基板ベース 1 1 は、シリコン基板、ゲルマニウム基板、シリコン - ゲルマニウム基板、炭化ケイ素基板、シリコン・オン・インシュレータ (S O I : S i l i c o n O n I n s u l a t o r ) 基板又はゲルマニウム・オン・インシュレータ (G O I : G e r m a n i u m O n I n s u l a t o r ) 基板等であってもよく、或いは、他の元素半導体又は化合物半導体を含む基板（例えば、ガラス基板又はI I I - V 族化合物基板（例えば、窒化ガリウム基板又はヒ化ガリウム基板等））であってもよく、或いは、積層構造（例えば、S i / S i G e 等）であってもよく、或いは、他の外延構造（例えば、ゲルマニウム・シリコン・オン・インシュレータ (S G O I ) ）等であってもよい。

#### 【 0 1 0 2 】

10

30

40

50

前記基板上部絶縁誘電体層12及び前記基板下部絶縁誘電体層13はソルダーマスク層であってもよく、例えば、前記基板上部絶縁誘電体層12及び前記基板下部絶縁誘電体層13の材料はソルダーレジストであってもよい。

#### 【0103】

前記基板10は更に、前記基板上部絶縁誘電体層12内の基板上部接続パッド14と、前記基板下部絶縁誘電体層13内の基板下部接続パッド15と、前記基板ベース11を貫通して前記基板上部接続パッド14及び前記基板下部接続パッド15を接続する基板接続貫通ビア16と、を備える。

#### 【0104】

前記基板上部接続パッド14及び前記基板下部接続パッド15の材料は、アルミニウム、銅、ニッケル、タンゲステン、白金、金のうちの少なくとも1つを含み得る。前記基板接続貫通ビア16はシリコン貫通ビア(TSV)であってもよい。

10

#### 【0105】

基板上部接続パッド14と基板下部接続パッド15は基板接続貫通ビア16を介して接続され、これにより、信号を伝送することができる。同時に、隣接する2つの基板上部接続パッド14は、再配線層を介して接続されてもよく、これにより、基板における信号の伝送を遂行することができる。

#### 【0106】

前記基板10は更に、仮想チャネル18を備え、前記仮想チャネル18は、基板上部接続パッド14、基板下部接続パッド15及び基板接続貫通ビア16で構成されるが、仮想チャネル18の下に基板接続バンプが形成されず、信号伝送を実現できず、発熱処理にのみ使用される。

20

#### 【0107】

いくつかの実施例では、仮想チャネルの熱伝導係数は、信号伝送の役割を果たす、基板上部接続パッド14、基板下部接続パッド15及び基板接続貫通ビア16で構成された構造の熱伝導係数より大きく、信号伝送に対する熱の影響を低減することができる。

#### 【0108】

引き続いて、図7bを参照すると、前記基板10上に少なくとも1つの第1チップ積層体21及び少なくとも1つの第2チップ積層体22が形成され、第1チップ積層体21は、前記第2チップ積層体22から間隔をあけて設けられる。

30

#### 【0109】

具体的に、前記基板10上に接着層60が形成されてから、前記接着層60上に第1チップ積層体21及び第2チップ積層体22が形成される。

#### 【0110】

前記接着層60はDAF膜であってもよい。

#### 【0111】

1つの実施例では、図5に示すように、前記接着層60は、第1接着層61、及び前記第1接着層61の上に位置する第2接着層62を備え、前記第2接着層62の弾性率は前記第1接着層61の弾性率より大きい。

#### 【0112】

本開示の実施例では、第1接着層は基板に接続されており、主として接着の役割を果たし、第2接着層は、チップに接続されており、主としてチップの反りを防止する役割を果たす。第2接着層の弾性率が比較的高いため、切断中に反りが生じず、第1接着層は比較的低い弾性率を有するため、後続の工程で基板とチップ的の接合力に影響を与えない。

40

#### 【0113】

1つの実施例では、前記接着層60は、前記仮想チャネル18上に位置し、前記仮想チャネル18の熱伝導係数は前記接着層60の熱伝導係数より大きい。

#### 【0114】

本開示の実施例では、仮想チャネルの熱伝導係数は接着層の熱伝導係数より大きく、チップの動作によって生じる熱を仮想チャネルでより多く放散することができ、放熱能力を

50

向上させ、デバイス性能への影響を低減することができる。

**【0115】**

図7bを引き続き参照すると、前記第1チップ積層体21及び前記第2チップ積層体22にリード線パッド201を形成し、前記リード線パッド201は、再配線層を介して、後続に形成される介在層における第2接続パッドに接続できる。

**【0116】**

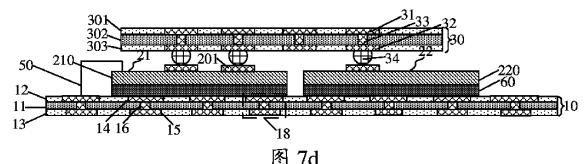

引き続いて、図7c及び図7dを参照すると、前記第1チップ積層体21及び前記第2チップ積層体22の上に介在層30が形成される。

**【0117】**

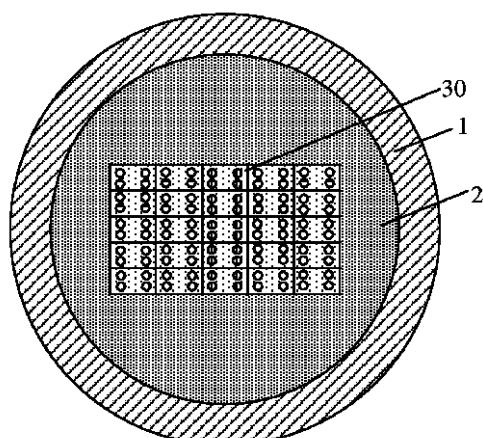

具体的に、先ず、図7cを参照すると、円環1にキャリアテープ2を粘着し、その後、介在層をキャリアテープ2に粘着し、この時の介在層全体は帯状であり、介在層を切断して、図7cに示されるそれぞれのセルを形成する。

10

**【0118】**

実際の操作では、前記介在層の介在上部絶縁誘電体層が形成された一面をキャリアテープに粘着し、介在下部絶縁誘電体層が形成された一面に第1ハンダボールを形成する。

**【0119】**

引き続いて、図7dを参照すると、前記介在層30を反転して前記第1チップ積層体21及び前記第2チップ積層体22に装着し、これによって、第1ハンダボール34を前記第1チップ積層体21及び前記第2チップ積層体22に接続させる。

**【0120】**

本開示の実施例では、介在層を介して第1チップ積層体と第2チップ積層体とを接続し、配線の数量を低減し、ワイヤーボンディング工程を省くことができる。

20

**【0121】**

前記介在層30は、第1表面、第2表面及び信号チャネル3を備え、前記第1表面の上に前記第1接続パッド31が設けられ、前記第2表面は、前記第1表面に対向して設けられ、前記第2表面の上に第2接続パッド32が設けられ、前記信号チャネル33は、前記第1接続パッド31及び前記第2接続パッド32に接続される。

**【0122】**

前記第1接続パッド31及び前記第2接続パッド32の材料は、アルミニウム、銅、ニッケル、タンゲステン、白金、金のうちの少なくとも1つを含み得る。

30

**【0123】**

前記介在層30は、介在基板302と、前記介在基板302の上面及び下面にそれぞれ位置する介在上部絶縁誘電体層301と介在下部絶縁誘電体層303と、を更に備える。前記第1接続パッド31は、前記介在上部絶縁誘電体層301内にあり、前記第2接続パッド32は、前記介在下部絶縁誘電体層303内にある。

**【0124】**

図7dに示すように、前記第1チップ積層体は1つの第1チップ210を備え、前記第2チップ積層体22は1つの第2チップ220を備え、ここで、前記第1チップ210は、前記介在層30を介して前記第2チップ220に電気接続される。

**【0125】**

引き続いて、リード線50を介して前記第1チップ210又は前記第2チップ220を前記基板10に接続させる。

40

**【0126】**

図7dに示す実施例では、前記第1チップ210及び前記第2チップ220は、介在層30を介して接続され、前記第1チップ210は、リード線50を介して基板10に接続され、第2チップ220を基板10に間接的に接続する。他の実施例では、第2チップがリード線を介して基板に接続され、第1チップを基板に間接的に接続してもよい。この実施例では、第1チップ及び第2チップは介在層を介して信号伝送を行うため、第1チップ及び第2チップのうちの1つのみをワイヤーボンディングすることができ、ワイヤーボンディング工程を削減することができる。

50

**【 0 1 2 7 】**

説明すべきこととして、図 7 a ~ 図 7 g に示される実施例では、第 1 チップ積層体が 1 つの第 1 チップを含み、第 2 チップ積層体が 1 つの第 2 チップを含む半導体パッケージ構造の製造方法のみを示しているが、第 1 チップ積層体及び第 2 チップ積層体は、他の積層構造を更に含む。

**【 0 1 2 8 】**

例えば、図 2 及び図 3 に示すように、前記第 1 チップ積層体 2 1 は、積み重ねられた第 1 下部チップ 2 1 2 及び第 1 上部チップ 2 1 1 を備え、前記第 2 チップ積層体 2 2 は、積み重ねられた第 2 下部チップ 2 2 2 及び第 2 上部チップ 2 2 1 を備え、ここで、前記介在層 3 0 は、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 上に設けられ、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 は、介在層 3 0 を介して電気接続される。

10

**【 0 1 2 9 】**

図 2 に示すように、前記第 1 上部チップ 2 1 1 又は前記第 2 上部チップ 2 2 1 は、リード線 5 0 を介して前記基板 1 0 に接続される。

**【 0 1 3 0 】**

前記第 1 下部チップ 2 1 2 及び前記第 2 下部チップ 2 2 2 は、リード線 5 0 を介して前記基板 1 0 にそれぞれ接続される。

20

**【 0 1 3 1 】**

図 2 に示す実施例では、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 は、介在層 3 0 を介して接続され、前記第 1 上部チップ 2 1 1 は、リード線 5 0 を介して基板 1 0 に接続され、第 2 上部チップ 2 2 1 を基板 1 0 に間接的に接続する。他の実施例では、第 2 上部チップがリード線を介して基板に接続され、第 1 上部チップを基板に間接的に接続してもよい。

20

**【 0 1 3 2 】**

この実施例では、第 1 上部チップ及び第 2 上部チップは介在層を介して信号伝送を行うため、第 1 上部チップ及び第 2 上部チップのうちの 1 つのみをワイヤーボンディングすることができ、ワイヤーボンディング工程を削減することができる。同時に、第 1 下部チップと第 2 下部チップは、接着層を介して第 1 上部チップ及び第 2 上部チップから隔離され、信号伝送を実現していないため、第 1 下部チップ及び第 2 下部チップはワイヤーボンディングすることにより基板に接続され、これによって、信号伝送を実現する。

30

**【 0 1 3 3 】**

図 3 に示すように、前記第 1 下部チップ 2 1 2 は、前記第 1 上部チップ 2 1 1 に電気接続され、前記第 2 下部チップ 2 2 2 は、前記第 2 上部チップ 2 2 1 に電気接続される。

**【 0 1 3 4 】**

具体的に、前記第 1 下部チップ 2 1 2 と前記第 1 上部チップ 2 1 1 との間、及び前記第 2 下部チップ 2 2 2 と前記第 2 上部チップ 2 2 1 との間は、チップ接続パッド 2 0 2 及びチップ接続ハンダボール 2 0 3、前記第 1 上部チップ 2 1 1 及び前記第 2 上部チップ 2 2 1 内のシリコン貫通ビア（未図示）を介して接続される。

30

**【 0 1 3 5 】**

この実施例では、第 1 下部チップ及び第 1 上部チップは信号伝送を直接に行うことができ、第 2 下部チップ及び第 2 上部チップは信号伝送を直接に行うことができ、第 1 上部チップ及び第 2 上部チップは、介在層を介して信号伝送を行ってもよく、したがって、4 チップのワイヤーボンディングは一度で済み、ワイヤーボンディング工程を低減し、コストを削減することができる。

40

**【 0 1 3 6 】**

図 7 d を引き続き参照すると、1 つの実施例では、前記第 1 チップ積層体 2 1 及び前記第 2 チップ積層体 2 2 に接続される前記第 2 接続パッド 3 2 同士は再配線層を介して接続される。

**【 0 1 3 7 】**

50

この実施例では、前記再配線層は、前記介在層の表面に位置してもよいし、前記介在層の内部に位置してもよい。

#### 【0138】

引き続いて、図7eを参照すると、前記第1チップ積層体21、前記第2チップ積層体22及び前記介在層30を包む成形材料40を形成する。

#### 【0139】

本開示の実施例では、最終的に形成される成形材料は介在層の第1接続パッドと共に面であるため、成形材料を形成する過程では、異形の金型を用いる必要がなく、通常形状の金型のみを用いればよく、通常形状の金型は形状が単純なため、製作が容易であり、コストが低い。

10

#### 【0140】

後続に第2パッケージ構造と第1パッケージ構造と接続された後、第1パッケージ構造と第2パッケージ構造との間に大きな隙間があり、第2パッケージ構造の発熱効率を保証することができる。

#### 【0141】

成形材料の表面が第1接続パッドの表面より高い場合、第1パッケージ構造と第2パッケージ構造との間の隙間が小さくなり、発熱に不利であるとともに、後続に充填層を形成するときに、充填層の充填に不利であり、第1接続パッドの表面が成形材料の表面より高い場合、隙間が大きくなる可能性があるが、成形材料がワイヤーボンディングを覆うことができず、ワイヤーボンディングが露出し、ワイヤーボンディングの保護に不利である。

20

#### 【0142】

図7eを引き続き参照すると、成形材料40を形成した後、前記基板10の基板下部接続パッド15上に基板接続バンプ17を形成し、前記基板接続バンプ17は導電材料を含む。

#### 【0143】

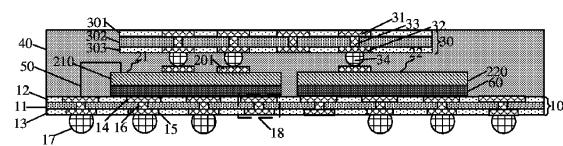

引き続いて、図7fを参照すると、ステップ602を実行し、第2パッケージ構造70を提供し、前記第2パッケージ構造70を前記介在層30上に設け、前記第2パッケージ構造70は、前記第1接続パッド31に電気接続され、ここで、前記第1パッケージ構造と前記第2パッケージ構造70との間に間隔が存在する。

30

#### 【0144】

具体的に、前記第2パッケージ構造70上に第2ハンダボール71を形成し、前記第2ハンダボール71は前記介在層30上の第1接続パッド31に電気接続される。

#### 【0145】

前記第2パッケージ構造は更に、第2基板72を備え、前記第2基板72の構造は前記基板10の構造と同じであり、ここでは繰り返して説明しない。

#### 【0146】

前記第2ハンダボール71は、前記第2基板72上に位置する。

#### 【0147】

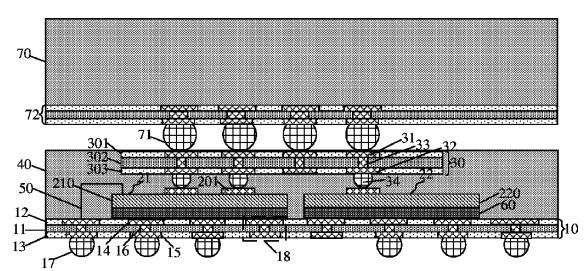

引き続いて、図7gを参照すると、前記第1パッケージ構造と前記第2パッケージ構造70との間の隙間に充填層80を形成する。

40

#### 【0148】

前記充填層80の熱伝導係数は、前記成形材料40の熱伝導係数より大きい。

#### 【0149】

充填層を設けることにより、第1パッケージ構造と第2パッケージ構造との間に密封した界面を有することができ、第1パッケージ構造及び第2パッケージ構造の金属構造と外気又は他の材料との接触を減らすことができ、熱伝導の役割を果たすことができる。充填層の熱伝導係数が比較的大きいため、充填層からより多くの熱が発散され、第1パッケージ構造に対する熱の影響を低減することができる。同時に、充填層の熱伝導係数は大きいが、充填層の熱膨張係数が第1パッケージ構造及び第2パッケージ構造の熱膨張係数と一致するので、充填層の体積変化が小さく、第1パッケージ構造及び第2パッケージ構造に

50

向外圧を及ぼさないので、構造の安定性を確保することができる。

**【0150】**

前記充填層80の充填材体積は、前記成形材料の充填材体積より小さい。

**【0151】**

図7gに示すように、前記成形材料40の充填材は第1充填材401であり、前記充填層80中的充填材は第2充填材801であり、第2充填材801の体積は第1充填材401の体積より小さい。

**【0152】**

前記成形材料40及び前記充填層80の主材料はエポキシ樹脂であってもよく、充填材は二酸化ケイ素であってもよい。

10

**【0153】**

この実施例では、成形材料に充填される隙間は比較的大きく、第1パッケージ構造と第2パッケージ構造との間の隙間は比較的小さいので、流動性の大きい充填層を選択し、充填層の充填材体積は小さく、主体材料の流動性が大きい。

**【0154】**

前述の説明は、本開示の好ましい実施例に過ぎず、本開示を限定することを意図するものではなく、本開示の趣旨及び原則の範囲内で行われるあらゆる変形、同等の置き換え、改善などは、すべて本開示の保護範囲に含まれるべきである。

**【産業上の利用可能性】**

**【0155】**

本開示の実施例では、介在層を設けることにより、介在層を介して第1パッケージ構造と第2パッケージ構造を接続し、このように、異なる容量のパッケージ構造間の相互接続を実現し、これによって、異なるパッケージ構造間の組み合わせはより柔軟になり、これにより、当該半導体パッケージ構造は異なる適用場面に適用することができる。さらに、第1パッケージ構造と第2パッケージ構造は個別にパッケージングされたものであるため、第1パッケージ構造及び第2パッケージ構造をそれぞれ検証することができ、これにより、失効分析をより迅速に行うことができ、それによって、半導体パッケージ構造が形成された後、構造全体を検証しなくてもよい。第2パッケージ構造と第1パッケージ構造との間に隙間があり、したがって、両者の間隔を増加し、これにより、第2パッケージ構造の発熱効率を向上させ、チップに対する熱の影響を低減させることができる。

20

**【符号の説明】**

**【0156】**

1 円環

2 キャリアテープ

10 基板

11 基板ベース

12 基板上部絶縁誘電体層

13 基板下部絶縁誘電体層

14 基板上部接続パッド

15 基板下部接続パッド

16 基板接続貫通ビア

17 基板接続バンプ

18 仮想チャネル

21 第1チップ積層体

22 第2チップ積層体

210 第1チップ

220 第2チップ

211 第1上部チップ

212 第1下部チップ

221 第2上部チップ

40

50

- 2 2 2 第 2 下部チップ

2 0 1 リード線パッド

2 0 2 チップ接続パッド

2 0 3 チップ接続ハンダボール

3 0 介在層

3 1 第 1 接続パッド

3 2 第 2 接続パッド

3 3 信号チャネル

3 4 第 1 ハンダボール

3 0 1 介在上部絶縁誘電体層

3 0 2 介在基板

3 0 3 介在下部絶縁誘電体層

4 0 成形材料

4 0 1 第 1 充填材

5 0 リード線

6 0 接着層

6 1 第 1 接着層

6 2 第 2 接着層

7 0 第 2 パッケージ構造

7 1 第 2 ハンダボール

7 2 第 2 基板

8 0 充填層

8 0 1 第 2 充填材

- 10

- 20

- 30

- 40

## 【図面】

## 【図 1】

图 1

## 【図 2】

图 2

【図3】

图3

【図4】

图4

10

【図5】

图5

【図6】

601

602

20

【図7a】

图7a

【図7b】

图7b

30

40

50

【図 7 c】

图 7c

【図 7 d】

图 7d

10

【図 7 e】

图 7e

【図 7 f】

图 7f

20

30

40

50

【図 7 g】

图 7g

10

20

30

40

50

---

フロントページの続き

(72)発明者 スン シャオフェイ

中華人民共和国 230601 アンファイ プロヴィンス ヘーフェイ シティ エコノミック アンド

テクノロジカル ディベロップメント エリア エアポート インダストリアル パーク シンイエ ア

ベニュー ナンバー 388

(72)発明者 チュアン チャンハオ

中華人民共和国 230601 アンファイ プロヴィンス ヘーフェイ シティ エコノミック アンド

テクノロジカル ディベロップメント エリア エアポート インダストリアル パーク シンイエ ア

ベニュー ナンバー 388

審査官 鹿野 博司

(56)参考文献 米国特許出願公開第2010/0072593(US, A1)

特開2005-026680(JP, A)

米国特許出願公開第2020/0381406(US, A1)

特開2011-233672(JP, A)

米国特許出願公開第2011/0127662(US, A1)

米国特許出願公開第2022/0199593(US, A1)

特表2006-522478(JP, A)

米国特許出願公開第2018/0269187(US, A1)

米国特許出願公開第2019/0206827(US, A1)

特開2012-156238(JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 25/10

H10B 80/00

H01L 25/07