(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7232628号**

**(P7232628)**

(45)発行日 令和5年3月3日(2023.3.3)

(24)登録日 令和5年2月22日(2023.2.22)

## (51)国際特許分類

|         |                 |     |         |       |       |

|---------|-----------------|-----|---------|-------|-------|

| G 1 1 C | 16/34 (2006.01) | F I | G 1 1 C | 16/34 | 1 6 6 |

| G 1 1 C | 16/04 (2006.01) |     | G 1 1 C | 16/04 | 1 7 0 |

| G 1 1 C | 16/14 (2006.01) |     | G 1 1 C | 16/14 | 1 0 0 |

| G 1 1 C | 11/56 (2006.01) |     | G 1 1 C | 11/56 | 2 2 0 |

| G 1 1 C | 16/26 (2006.01) |     | G 1 1 C | 11/56 | 2 1 5 |

請求項の数 18 (全33頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2018-226638(P2018-226638) |

| (22)出願日           | 平成30年12月3日(2018.12.3)       |

| (65)公開番号          | 特開2019-114320(P2019-114320) |

|                   | A)                          |

| (43)公開日           | 令和1年7月11日(2019.7.11)        |

| 審査請求日             | 令和3年12月2日(2021.12.2)        |

| (31)優先権主張番号       | 10-2017-0177848             |

| (32)優先日           | 平成29年12月22日(2017.12.22)     |

| (33)優先権主張国・地域又は機関 | 韓国(KR)                      |

|          |                                     |

|----------|-------------------------------------|

| (73)特許権者 | 390019839                           |

|          | 三星電子株式会社                            |

|          | S a m s u n g E l e c t r o n i c s |

|          | C o . , L t d .                     |

|          | 大韓民国京畿道水原市靈通区三星路 1 2                |

|          | 9                                   |

|          | 1 2 9 , S a m s u n g - r o , Y e o |

|          | n g t o n g - g u , Suw o n - s i   |

|          | , Gyeonggi - d o , Repub            |

|          | l i c o f K o r e a                 |

| (74)代理人  | 100107766                           |

|          | 弁理士 伊東 忠重                           |

| (74)代理人  | 100070150                           |

|          | 弁理士 伊東 忠彦                           |

| (74)代理人  | 100091214                           |

最終頁に続く

(54)【発明の名称】 不揮発性メモリ装置、不揮発性メモリ装置の動作方法、及び貯蔵装置

**(57)【特許請求の範囲】****【請求項 1】**

物理ブロックより小さなサブブロック単位でメモリセルを選択し、基板の上に垂直に積層されたワードラインに各々連結されたメモリセルを各々備えるメモリブロックを含むメモリセルアレイと、

前記メモリブロックのうち、第1メモリブロックのサブブロックの各々のエラー発生頻度に基づいて前記サブブロックを隣り合う少なくとも1つのバッドサブブロックと少なくとも1つのノーマルサブブロックに区分し、外部からのコマンド及びアドレスに基づいて前記少なくとも1つのバッドサブブロックと前記少なくとも1つのノーマルサブブロックに亘り異なるプログラム／消去サイクルを適用する制御回路とを含み、

前記制御回路は、

前記アドレスが前記少なくとも1つのノーマルサブブロックを指定する場合には、第1プログラム／消去サイクルを前記少なくとも1つのノーマルサブブロックに適用し、

前記アドレスが前記少なくとも1つのバッドサブブロックを指定する場合には、第1基準値までは前記第1プログラム／消去サイクルより頻度が小さな第2プログラム／消去サイクルを前記少なくとも1つのバッドサブブロックに適用し、前記第1基準値の以後には前記第2プログラム／消去サイクルより頻度が小さな第3プログラム／消去サイクルを前記少なくとも1つのバッドサブブロックに適用することを特徴とする、不揮発性メモリ装置。

**【請求項 2】**

前記制御回路は、

前記アドレスが前記少なくとも 1 つのノーマルサブプロックを指定する場合には、第 1 プログラム / 消去サイクルを前記少なくとも 1 つのノーマルサブプロックに適用し、

前記アドレスが前記少なくとも 1 つのバッドサブプロックを指定する場合には、前記第 1 プログラム / 消去サイクルより頻度が小さな第 2 プログラム / 消去サイクルを前記少なくとも 1 つのバッドサブプロックに適用することを特徴とする、請求項 1 に記載の不揮発性メモリ装置。

#### 【請求項 3】

前記不揮発性メモリ装置は、

制御信号に基づいてワードライン電圧を生成する電圧生成器と、

ローアドレスに基づいて前記ワードライン電圧を前記少なくとも 1 つのバッドサブプロックと前記少なくとも 1 つのノーマルサブプロックに提供するアドレスデコーダをさらに含み、

前記制御回路は、前記コマンド及び前記アドレスに基づいて前記電圧生成器と前記アドレスデコーダを制御することを特徴とする、請求項 1 又は 2 に記載の不揮発性メモリ装置。

#### 【請求項 4】

前記制御回路は、

前記少なくとも 1 つのバッドサブプロックに含まれるワードラインのバッドローアドレスを貯蔵するバッドサブプロック情報レジスタと、

前記コマンドをデコーディングし、デコーディングされたコマンドを提供するコマンドデコーダと、

前記ローアドレスと前記バッドローアドレスを比較し、前記比較の結果を示すマッチ信号を出力するアドレス比較器と、

前記第 1 プログラム / 消去サイクル及び前記第 2 プログラム / 消去サイクルと関連したプログラム / 消去サイクル情報を貯蔵するプログラム / 消去サイクル情報レジスタと、

前記デコーディングされたコマンドと前記マッチ信号に応答し、前記プログラム / 消去サイクル情報を参照して前記制御信号と前記アドレスデコーダを制御する第 1 モード信号と第 2 モード信号を生成する制御信号生成器と、

を含むことを特徴とする、請求項 3 に記載の不揮発性メモリ装置。

#### 【請求項 5】

前記制御回路は、

前記少なくとも 1 つのバッドサブプロックに含まれるワードラインのバッドローアドレスを貯蔵するバッドサブプロック情報レジスタと、

前記コマンドをデコーディングし、デコーディングされたコマンドを提供するコマンドデコーダと、

前記ローアドレスと前記バッドローアドレスを比較し、前記比較の結果を示すマッチ信号を出力するアドレス比較器と、

前記デコーディングされたコマンド及び前記マッチ信号に基づいて前記バッドサブプロックに対するプログラム / 消去サイクル回数をカウンティングし、カウンティング値を出力するプログラム / 消去サイクルカウンターと、

前記カウンティング値と基準カウンティング値を比較して比較信号を提供する比較器と、

前記少なくとも 1 つのノーマルサブプロック及び前記少なくとも 1 つのバッドサブプロックと関連したプログラム / 消去サイクル情報を貯蔵するプログラム / 消去サイクル情報レジスタと、

前記デコーディングされたコマンドと前記マッチ信号に応答し、前記プログラム / 消去サイクル情報を参照して前記制御信号と前記アドレスデコーダを制御する第 1 モード信号と第 2 モード信号を生成する制御信号生成器とを含むことを特徴とする、請求項 3 に記載の不揮発性メモリ装置。

#### 【請求項 6】

前記コマンドが前記第 1 メモリプロックに対する消去コマンドである場合、

10

20

30

40

50

前記制御回路は、前記少なくとも 1 つのパッドサブプロックのプログラム可否によって前記第 1 メモリプロックに対する消去動作時に前記第 1 メモリプロックに適用される消去バイアス条件が変わるように前記電圧生成器と前記アドレスデコーダを制御することを特徴とする、請求項 3 に記載の不揮発性メモリ装置。

#### 【請求項 7】

前記少なくとも 1 つのパッドサブプロックがプログラムされていない場合、

前記制御回路は、前記電圧生成器と前記アドレスデコーダを制御して前記基板に消去電圧を印加し、

前記少なくとも 1 つのノーマルサブプロックのワードラインには第 1 ワードライン消去電圧を印加し、

前記少なくとも 1 つのパッドサブプロックのワードラインには第 2 ワードライン消去電圧を印加し、

前記第 2 ワードライン消去電圧のレベルは前記第 1 ワードライン消去電圧のレベルより大きいことを特徴とする、請求項 6 に記載の不揮発性メモリ装置。

#### 【請求項 8】

前記少なくとも 1 つのパッドサブプロックがプログラムされている場合、

前記制御回路は前記電圧生成器と前記アドレスデコーダを制御して前記基板に印加される消去電圧のレベルを第 1 区間で第 1 レベルに維持させ、

前記第 1 区間後の第 2 区間で前記消去電圧を前記第 1 レベルより高い第 2 レベルに維持させて、前記少なくとも 1 つのパッドサブプロックを前記少なくとも 1 つのノーマルサブプロックより先に消去させることを特徴とする、請求項 6 に記載の不揮発性メモリ装置。

#### 【請求項 9】

前記コマンドが前記少なくとも 1 つのノーマルサブプロックに対する読み出コマンドである場合、

前記制御回路は、前記少なくとも 1 つのパッドサブプロックのプログラム可否によって前記ノーマルサブプロックに対する読み出動作時に前記第 1 メモリプロックに適用される読み出バイアス条件が変わるように前記電圧生成器と前記アドレスデコーダを制御することを特徴とする、請求項 3 に記載の不揮発性メモリ装置。

#### 【請求項 10】

前記メモリセルの各々は M ( M は、2 以上の自然数 ) ビットを貯蔵することができ、

前記少なくとも 1 つのノーマルサブプロックのワードラインのうち、前記少なくとも 1 つのパッドサブプロックに隣接する境界ワードラインに連結されるメモリセルは M より小さな N ビットを貯蔵することを特徴とする、請求項 3 に記載の不揮発性メモリ装置。

#### 【請求項 11】

前記少なくとも 1 つのパッドサブプロックに含まれるワードライン数は前記メモリセルアレイで前記第 1 メモリプロックが形成される位置によって変わることを特徴とする、請求項 1 ないし 10 のうち何れか一項に記載の不揮発性メモリ装置。

#### 【請求項 12】

物理プロックより小さなサブプロック単位でメモリセルを選択し、基板の上に垂直に積層されたワードラインに各々連結されたメモリセルを各々備えるメモリプロックを含むメモリセルアレイを備える不揮発性メモリ装置の動作方法であって、

前記メモリプロックのうち、第 1 メモリプロックのサブプロックの各々のエラー発生頻度に基づいて前記サブプロックを隣り合う少なくとも 1 つのパッドサブプロックと少なくとも 1 つのノーマルサブプロックに区分するステップと、

外部からのコマンド及びアドレスに基づいて前記少なくとも 1 つのパッドサブプロックと前記少なくとも 1 つのノーマルサブプロックに互いに異なるプログラム / 消去サイクルを適用するステップを含み、

前記互いに異なるプログラム / 消去サイクルを適用するステップは、

前記アドレスが前記少なくとも 1 つのパッドサブプロックを指定するか否かを判断する

ステップと、

10

20

30

40

50

前記アドレスが前記少なくとも 1 つのノーマルサブブロックを指定する場合、前記少なくとも 1 つのノーマルサブブロックに第 1 プログラム / 消去サイクルが適用されるように前記少なくとも 1 つのノーマルサブブロックに対してプログラム動作及び消去動作を遂行するステップと、

前記アドレスが前記少なくとも 1 つのバッドサブブロックを指定する場合、前記少なくとも 1 つのバッドサブブロックに前記第 1 プログラム / 消去サイクルより頻度が小さな少なくとも第 2 プログラム / 消去サイクルが適用されるように前記少なくとも 1 つのバッドサブブロックに対してプログラム動作及び消去動作を遂行するステップとを含むことを特徴とする不揮発性メモリ装置の動作方法。

**【請求項 1 3】**

10

前記少なくとも 1 つのバッドサブブロックのプログラム可否によって前記第 1 メモリブロックに対するメモリ動作時に前記第 1 メモリブロックに適用されるバイアス条件を調節するステップと、

前記調節されたバイアス条件によって前記第 1 メモリブロックに対する前記メモリ動作を遂行するステップとをさらに含むことを特徴とする、請求項 1 2 に記載の不揮発性メモリ装置の動作方法。

**【請求項 1 4】**

前記メモリ動作は前記少なくとも 1 つのノーマルサブブロックに対する読み出動作であり、前記バイアス条件を調節するステップは、

前記少なくとも 1 つのバッドサブブロックがプログラムされていない場合に、前記少なくとも 1 つのノーマルサブブロックの非選択ワードラインに第 1 読み出バス電圧を印加するステップと、

20

前記少なくとも 1 つのバッドサブブロックがプログラムされた場合に、前記非選択ワードラインに第 2 読み出バス電圧を印加するステップとを含み、

前記第 2 読み出バス電圧のレベルは、前記第 1 読み出バス電圧のレベルより高いことを特徴とする、請求項 1 3 に記載の不揮発性メモリ装置の動作方法。

**【請求項 1 5】**

前記メモリ動作は前記第 1 メモリブロックに対する消去動作であり、前記少なくとも 1 つのバッドサブブロックがプログラムされていない場合、

前記バイアス条件を調節するステップは、

30

前記基板に消去電圧を印加するステップと、

前記少なくとも 1 つのノーマルサブブロックのワードラインに第 1 ワードライン消去電圧を印加するステップと、

前記少なくとも 1 つのバッドサブブロックのワードラインに第 2 ワードライン消去電圧を印加するステップとを含み、

前記第 2 ワードライン消去電圧のレベルは、前記第 1 ワードライン消去電圧のレベルより大きいことを特徴とする、請求項 1 3 に記載の不揮発性メモリ装置の動作方法。

**【請求項 1 6】**

前記メモリ動作は前記第 1 メモリブロックに対する消去動作であり、前記少なくとも 1 つのバッドサブブロックがプログラムされている場合、

前記バイアス条件を調節するステップは、

40

前記基板に印加される消去電圧のレベルを第 1 区間の間に第 1 レベルに維持するステップと、

前記第 1 区間後の第 2 区間の間に前記消去電圧のレベルを第 2 レベルに維持するステップとを含み、

前記第 2 レベルは前記第 1 レベルより大きいことを特徴とする、請求項 1 3 に記載の不揮発性メモリ装置の動作方法。

**【請求項 1 7】**

少なくとも 1 つの不揮発性メモリ装置と、

前記少なくとも 1 つの不揮発性メモリ装置を制御するメモリコントローラとを含み、

50

前記少なくとも 1 つの不揮発性メモリ装置は、物理ブロックより小さなサブブロック単位でメモリセルを選択し、基板の上に垂直に積層されたワードラインに各々連結されたメモリセルを各々備えるメモリブロックを含むメモリセルアレイと、

前記メモリコントローラからのコマンド及びアドレスに応答して前記メモリセルアレイに対するアクセスを制御する制御回路とを含み、

前記メモリコントローラは、前記メモリブロックの各々に含まれるバッドサブブロックに関するバッドサブブロック情報を前記少なくとも 1 つの不揮発性メモリ装置に転送し、

前記制御回路は前記バッドサブブロック情報に基づいて前記メモリブロックのうち、第 1 メモリブロックのサブブロックの各々のエラー発生頻度に基づいて前記サブブロックを隣り合う少なくとも 1 つのバッドサブブロックと少なくとも 1 つのノーマルサブブロックに区分し、前記第 1 メモリブロックに対するメモリ動作時に互いに異なるバイアス条件を前記少なくとも 1 つのバッドサブブロックと前記少なくとも 1 つのノーマルサブブロックに適用し、

前記制御回路は、

前記アドレスが前記少なくとも 1 つのノーマルサブブロックを指定する場合には、第 1 プログラム / 消去サイクルを前記少なくとも 1 つのノーマルサブブロックに適用し、

前記アドレスが前記少なくとも 1 つのバッドサブブロックを指定する場合には、第 1 基準値までは前記第 1 プログラム / 消去サイクルより頻度が小さな第 2 プログラム / 消去サイクルを前記少なくとも 1 つのバッドサブブロックに適用し、前記第 1 基準値の以後には前記第 2 プログラム / 消去サイクルより頻度が小さな第 3 プログラム / 消去サイクルを前記少なくとも 1 つのバッドサブブロックに適用することを特徴とする、貯蔵装置。

#### 【請求項 18】

前記メモリコントローラは前記不揮発性メモリ装置から読み出されたデータに対するエラー検出及び訂正を遂行し、前記バッドサブブロック情報を生成するエラー訂正コードエンジンを含むことを特徴とする、請求項 17 に記載の貯蔵装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明はメモリ装置に関し、より詳しくは、不揮発性メモリ装置、不揮発性メモリ装置の動作方法、及び貯蔵装置に関する。

##### 【背景技術】

##### 【0002】

メモリ装置はデータを貯蔵するために使用され、大別して揮発性メモリ装置と不揮発性メモリ装置とに区分される。不揮発性メモリ装置の一例として、フラッシュメモリ装置は、携帯電話、デジタルカメラ、携帯用情報端末機（PDA）、移動式コンピュータ装置、固定式コンピュータ装置、及びその他の装置で使用することが可能である。

##### 【0003】

最近、不揮発性メモリ装置の集積度を向上させるためにメモリセルが 3 次元に積層される不揮発性メモリ装置が活発に研究されている。しかしながら、大容量化によって既存のメモリ管理政策との不整合による問題が懸念される。

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

本発明の一目的は、性能を高めて、寿命短縮を防止することができる不揮発性メモリ装置を提供することにある。

##### 【0005】

本発明の一目的は、性能を高めて、寿命短縮を防止することができる不揮発性メモリ装置の動作方法を提供することにある。

##### 【0006】

10

20

30

40

50

本発明の一目的は、不揮発性メモリ装置を含む貯蔵装置を提供することにある。

**【課題を解決するための手段】**

**【0007】**

前述した本発明の一目的を達成するために、本発明の実施形態に係る不揮発性メモリ装置は、メモリセルアレイ及び制御回路を含む。メモリセルアレイは物理ブロックより小さなサブブロック単位でメモリセルを選択し、基板の上に垂直に積層されたワードラインに各々連結されたメモリセルを各々備えるメモリブロックを含む。制御回路は、メモリブロックのうち、第1メモリブロックのサブブロックの各々のエラー発生頻度に基づいてサブブロックを隣り合う少なくとも1つのバッドサブブロックと少なくとも1つのノーマルサブブロックに区分し、外部からのコマンド及びアドレスに基づいて少なくとも1つのバッドサブブロックと少なくとも1つのノーマルサブブロックに互いに異なるプログラム／消去サイクルを適用する。

10

**【0008】**

前述した本発明の一目的を達成するために、本発明の実施形態に係る物理ブロックより小さなサブブロック単位でメモリセルを選択し、基板の上に垂直に積層されたワードラインに各々連結されたメモリセルを各々備えるメモリブロックを含むメモリセルアレイを備える不揮発性メモリ装置の動作方法では、メモリブロックのうち、第1メモリブロックのサブブロックの各々のエラー発生頻度に基づいてサブブロックを隣り合う少なくとも1つのバッドサブブロックと少なくとも1つのノーマルサブブロックに区分し、外部からのコマンド及びアドレスに基づいて少なくとも1つのバッドサブブロックと少なくとも1つのノーマルサブブロックに互いに異なるプログラム／消去サイクルを適用する。

20

**【0009】**

前述した本発明の一目的を達成するために、本発明の実施形態に係る貯蔵装置は、少なくとも1つの不揮発性メモリ装置及び少なくとも1つの不揮発性メモリ装置を制御するメモリコントローラを含む。少なくとも1つの不揮発性メモリ装置は、メモリセルアレイ及び制御回路を含む。メモリセルアレイは、物理ブロックより小さなサブブロック単位でメモリセルを選択し、基板の上に垂直に積層されたワードラインに各々連結されたメモリセルを各々備えるメモリブロックを含む。制御回路は、メモリコントローラからのコマンド及びアドレスに応答してメモリセルアレイに対するアクセスを制御する。メモリコントローラは、メモリブロックの各々に含まれるバッドサブブロックに関するバッドサブブロック情報を少なくとも1つの不揮発性メモリ装置に転送する。制御回路は、バッドサブブロック情報に基づいてメモリブロックのうち、第1メモリブロックのサブブロックの各々のエラー発生頻度に基づいてサブブロックを隣り合う少なくとも1つのバッドサブブロックと少なくとも1つのノーマルサブブロックに区分し、第1メモリブロックに対するメモリ動作時に互いに異なるバイアス条件を少なくとも1つのバッドサブブロックと少なくとも1つのノーマルサブブロックに適用する。

30

**【発明の効果】**

**【0010】**

本発明の実施形態によれば、サブブロックのエラー発生頻度またはサブブロックの位置に従う耐久性特性に基づいて1つのメモリブロックのサブブロックを少なくとも1つのノーマルサブブロックと少なくとも1つのバッドサブブロックに区分し、ノーマルサブブロックとバッドサブブロックに互いに異なるプログラム／消去サイクルを適用し、第1メモリブロックに対するメモリ動作時にバッドサブブロックのプログラム可否によって異なるバイアス条件を第1メモリブロックに適用することにより、不揮発性メモリ装置の性能を高めることができ、寿命が短縮されることを防止することができる。

40

**【図面の簡単な説明】**

**【0011】**

**【図1】**本発明の実施形態に係る電子装置を示す概略的なブロック図である。

**【図2】**本発明の実施形態に係る図1の電子装置における貯蔵装置の構成を示す。

**【図3】**本発明の実施形態に係る図2の貯蔵装置におけるメモリコントローラの構成を示す。

50

すブロック図である。

【図4】本発明の実施形態に係る図2の貯蔵装置における不揮発性メモリ装置を示すブロック図である。

【図5】図4のメモリセルアレイを示すブロック図である。

【図6】図5のメモリブロック(BLK1～BLKz)のうちの1つ(BLKi)を示す斜視図である。

【図7】図6のメモリブロックを示す等価回路図である。

【図8】本発明の実施形態に係る図4のメモリセルアレイが形成されるセル領域を示す。

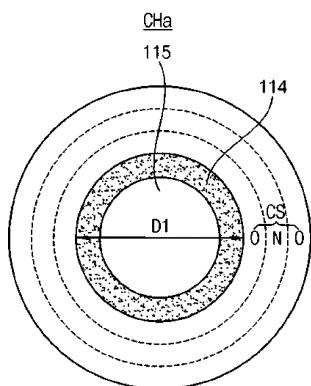

【図9A】図8のメモリブロックに各々含まれたセルストリングの断面を例示的に示す。

【図9B】図8のメモリブロックに各々含まれたセルストリングの断面を例示的に示す。

【図10】図8のメモリブロックに対するプログラム動作及び消去動作の遂行結果を示すグラフである。

【図11】図8の1つのチャンネルの垂直構造を示す。

【図12】本発明の実施形態に係る図4の不揮発性メモリ装置における制御回路の構成を示す。

【図13】本発明の実施形態に係る図4の不揮発性メモリ装置における制御回路の構成を示す。

【図14】本発明の実施形態に係る図4の不揮発性メモリ装置における電圧生成器の構成を示すブロック図である。

【図15】本発明の実施形態に係る図4の不揮発性メモリ装置におけるアドレスデコーダの構成を示す。

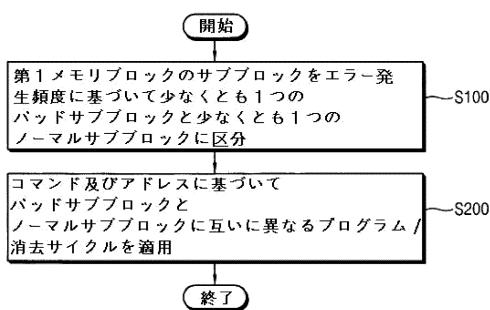

【図16】本発明の実施形態に係る不揮発性メモリ装置の動作方法を示すフローチャートである。

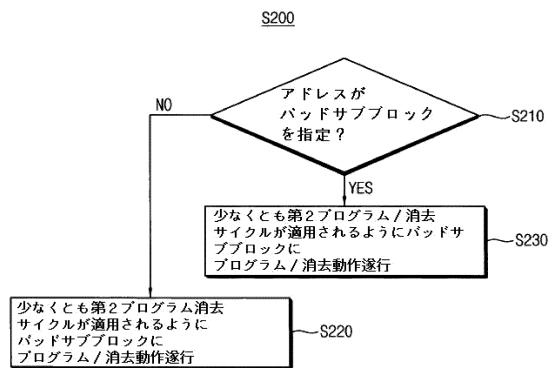

【図17】図16でステップ(S200)をより詳細に示すフローチャートである。

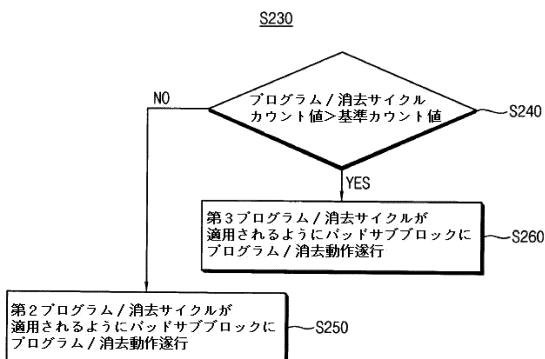

【図18】図17で少なくとも第2プログラム／消去サイクルが適用されるステップを詳細に示す。

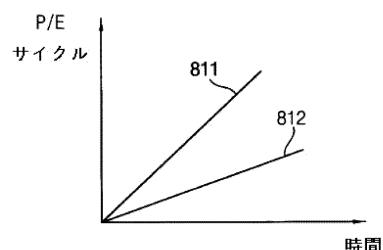

【図19A】各々ノーマルサブブロックとバッドサブブロックに適用されるプログラム消去サイクルを示す。

【図19B】各々ノーマルサブブロックとバッドサブブロックに適用されるプログラム消去サイクルを示す。

【図20】本発明の実施形態に係る不揮発性メモリ装置の動作方法を示すフローチャートである。

【図21A】図7のメモリブロックのサブブロックのプログラム状態を示す。

【図21B】図7のメモリブロックのサブブロックのプログラム状態を示す。

【図22A】バッドサブブロックがプログラムされていない場合、第1メモリブロックに対する消去動作時の消去バイアス条件を示す。

【図22B】バッドサブブロックがプログラムされていない場合、第1メモリブロックに対する消去動作時の消去バイアス条件を示す。

【図23A】図22Bのバイアス条件が適用される場合のバッドサブブロック電圧と基板電圧を示す。

【図23B】図22Bのバイアス条件が適用される場合に図13の第1スイッチ回路を示す。

【図24】バッドサブブロックがプログラムされていない場合、第1メモリブロックに対する消去動作時の消去バイアス条件を示す。

【図25】図24のバイアス条件が適用される場合の基板電圧を示す。

【図26A】バッドサブブロックがプログラムされていない場合、第1メモリブロックに対する読出動作時の読出バイアス条件を示す。

【図26B】バッドサブブロックがプログラムされた場合、第1メモリブロックに対する読出動作時の読出バイアス条件を示す。

【図27】本発明の実施形態に係るモバイル装置を示すブロック図である。

10

20

30

40

50

**【発明を実施するための形態】**

**【0012】**

以下、添付した図面を参照して、本発明の好ましい実施形態をより詳細に説明する。図面上の同一な構成要素に対しては同一な参照符号を使用し、同一な構成要素に対して重複説明は省略する。

**【0013】**

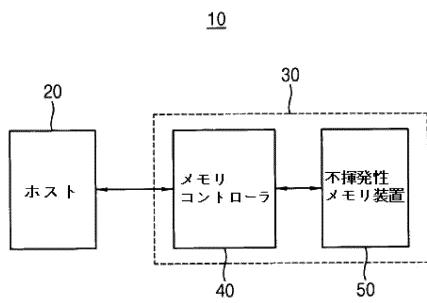

図1は、本発明の実施形態に係る電子装置を示す概略的なブロック図である。

**【0014】**

図1を参照すると、電子装置10はホスト20及び貯蔵装置30を含むことができる。

貯蔵装置30は、メモリコントローラ40及び少なくとも1つの不揮発性メモリ装置50を含むことができる。ホスト20は、貯蔵装置30の動作を全般的に制御する。メモリコントローラ40は、ホスト20とコマンド、アドレス、データのような信号を交換することができる。メモリコントローラ40は、ホスト20のコマンドによって不揮発性メモリ装置50にデータを書き込むか、または不揮発性メモリ装置50からデータを読み出すことができる。

10

**【0015】**

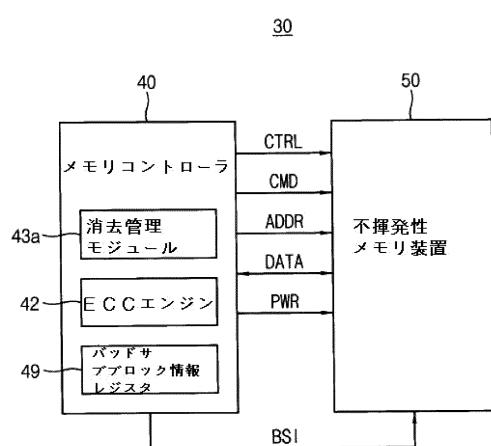

図2は、本発明の実施形態に係る図1の電子装置における貯蔵装置の構成を示す。

**【0016】**

図2を参照すると、貯蔵装置（ストレージデバイスまたはメモリシステム）30は、メモリコントローラ40及び少なくとも1つの不揮発性メモリ装置50を含むことができる。

実施形態において、メモリコントローラ40及び不揮発性メモリ装置50の各々は1つのチップ、1つのパッケージ、1つのモジュールなどに提供できる。または、メモリコントローラ40及び不揮発性メモリ装置50は多様なパッケージに基づいて実装されてメモリカードのような貯蔵装置に提供できる。

20

**【0017】**

不揮発性メモリ装置50は、メモリコントローラ40の制御によって消去、書込または読出動作などを遂行することができる。このために、不揮発性メモリ装置50は入出力ラインを介してコマンド（CMD）、アドレス（ADDR）、そしてデータ（DATA）の入力を受ける。また、不揮発性メモリ装置50は制御ラインを介して制御信号（CTRL）の提供を受けることができる。また、不揮発性メモリ装置50はメモリコントローラ40からパワー（PWR）の提供を受けることができる。

30

**【0018】**

不揮発性メモリ装置50に含まれたメモリセルは、プログラム後の経過時間、温度、プログラム搅乱、読出搅乱などの要因によって、しきい電圧ばらつきが変化する物理的特性を有する。即ち、前述した要因によって不揮発性メモリ装置50に貯蔵されたデータに誤謬が発生することがある。メモリコントローラ40は、このような誤謬を訂正するために、多様なエラー訂正技法を使用することができる。例えば、メモリコントローラ40はエラー訂正コード（ECC；Error Correction Code）エンジン42を含むことができる。

**【0019】**

また、不揮発性メモリ装置50に対する消去動作時、メモリコントローラ40は物理ブロックより小さなサブブロック単位で不揮発性メモリ装置50に対する消去動作を遂行することができる。サブブロック単位の消去動作を管理するために、メモリコントローラ40は消去管理モジュール43aを含むことができる。

40

**【0020】**

消去管理モジュール43aは、サブブロック単位の消去動作を遂行した後に、消去されたサブブロックまたは消去されたサブブロックと隣接したサブブロックに対する消去状態をモニタリングすることができる。例えば、消去管理モジュール43aは消去されたサブブロックから読み出されたデータを参照してビットエラー率（BER）を検出することができる。または、消去管理モジュール43aは消去されたサブブロックに対するウェアレベリング情報（例えば、Erase count）を獲得しモニタリングすることができる。これだ

50

けでなく、消去管理モジュール 4 3 a は消去されたサブブロックのデータを読み出して選択されたメモリセルのしきい電圧変化やビットエラー率（B E R）変化をモニタリングすることができる。また、消去管理モジュール 4 3 a は非選択サブ・ブロックのデータを読み出してしきい電圧の変化を検出することができる。メモリコントローラ 4 0 は、消去管理モジュール 4 3 a から提供される消去状態情報を参照して選択されたサブブロック単位の消去動作時の影響を緩和させるための多様な手続を遂行することができる。

#### 【 0 0 2 1 】

ここで、メモリブロック（memory block）は同時に消去可能な最大メモリ単位である。ワードラインが基板に垂直方向に積層される 3 次元不揮発性メモリ装置において、メモリブロックは積層された全てのワードラインを共有するセルストリングのグループと定義できる。サブブロック（Sub-block）は 1 つのメモリブロック（または、物理ブロック）をワードライン単位または選択ライン単位に区分した細部メモリ単位に該当する。例えば、サブブロック（Sub-block）はメモリブロックのうち、一部ワードラインを共有するメモリセルの単位と定義できる。10

#### 【 0 0 2 2 】

不揮発性メモリ装置 5 0 に対する読み出動作時、メモリコントローラ 4 0 はデフォルト読み出電圧セット（default read voltage set）に基づいて不揮発性メモリ装置 2 0 0 の第 1 ページに貯蔵されたデータを読み取ることができる。例示的に、デフォルト読み出電圧セットは予め定まった読み出電圧を示す。E C C エンジン 4 2 は、不揮発性メモリ装置 5 0 から読み出したデータに含まれた誤謬を検出及び訂正することができる。例示的に、E C C エンジン 4 2 はハードウェア形態に提供できる。E C C エンジン 4 2 は、メモリ装置 5 0 から読み出したデータに含まれた誤謬の検出頻度をサブブロック別に判断し、一定時間の間の誤謬の検出頻度が基準値以上になるサブブロックをバッドサブブロックに指定することができる。20

#### 【 0 0 2 3 】

メモリコントローラ 4 0 は、サブブロックのうち、バッドサブブロックの情報を貯蔵するバッドサブブロック情報レジスタ 4 9 を含むことができ、バッドサブブロックのアドレスを含むバッドサブブロック情報（B S I）を不揮発性メモリ装置 5 0 に提供することができる。

#### 【 0 0 2 4 】

図 3 は、本発明の実施形態に係る図 2 の貯蔵装置におけるメモリコントローラの構成を示すブロック図である。30

#### 【 0 0 2 5 】

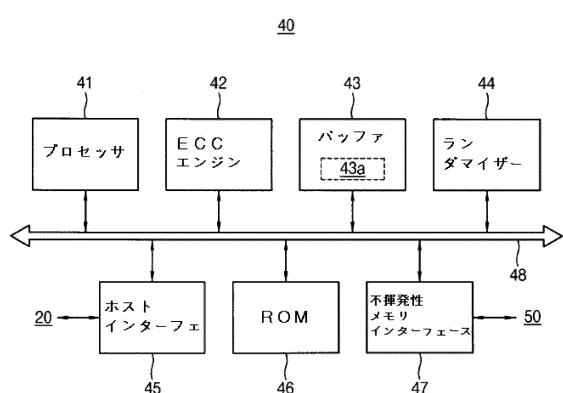

図 2 及び図 3 を参考すると、メモリコントローラ 4 0 は、バス 4 8 を介して互いに連結されるプロセッサ 4 1、E C C エンジン 4 2、バッファ 4 3、消去管理モジュール 4 3 a、ランダマイザー 4 4、ホストインターフェース 4 5、R O M 4 6、及び不揮発性メモリインターフェース 4 7 を含むことができる。E C C エンジン 4 2 及び消去管理モジュール 4 3 a は、図 2 を参照して説明されたので、これに対する詳細な説明は省略する。

#### 【 0 0 2 6 】

プロセッサ 4 1 は、メモリコントローラ 4 0 の諸般動作を制御する。例えば、消去管理モジュール 4 3 a はソフトウェア形態に提供され、バッファ 4 3 に貯蔵できる。バッファ 4 3 に貯蔵された消去管理モジュール 4 3 a は、プロセッサ 4 1 により駆動できる。R O M 4 6 はメモリコントローラ 4 0 が動作することに要求される多様な情報をファームウェア形態に貯蔵することができる。バッファ 4 3 は、不揮発性メモリ装置 5 0 から読み出されたデータを貯蔵するか、または消去管理モジュール 4 3 a を含むことができる。40

#### 【 0 0 2 7 】

例えば、データランダマイジングは 1 つのワードラインに連結されたメモリセルが同一な比率のプログラム状態を有するようにデータを処理することを示す。例えば、1 つのワードラインに連結されたメモリセルが各々 2 - ビットのデータを貯蔵するマルチレベルセル（M L C；Multi Level Cell）である場合、メモリセルの各々は消去状態及び第 1 乃

至第3プログラム状態のうち、いずれか1つの状態を有する。この際、ランダマイザー44は1つのワードラインに連結されたメモリセルのうち、消去状態を有するメモリセルの個数、第1プログラム状態を有するメモリセルの個数、第2プログラム状態を有するメモリセルの個数、及び第3プログラム状態を有するメモリセルの個数が互いに同一であるようデータをランダマイジングすることができる。即ち、ランダマイジングされたデータ(*randomized data*)が貯蔵されたメモリセルは実質的に互いに同一な個数のプログラム状態を有する。例示的に、ランダマイザー44は不揮発性メモリ装置50から読み取ったデータをデランダマイジングすることができる。

#### 【0028】

例えば、ランダマイザー44はページデータをランダマイジングすることができる。例示的に、簡潔な説明のために理想的な(*ideal*)ランダマイザー44の構成が説明された。しかしながら、本発明の技術的思想がこれに限定されるものではなく、実際のランダマイザー44は1つのワードラインに連結されたメモリセルのうち、消去状態を有するメモリセルの個数、第1プログラム状態を有するメモリセルの個数、第2プログラム状態を有するメモリセルの個数、及び第3プログラム状態を有するメモリセルの個数が実質的に互いに同一な値に近いようにデータをランダマイジングすることができる。即ち、実際ランダマイジングされたデータ(*randomized data*)が貯蔵されたメモリセルは実質的に互いに類似の個数のプログラム状態を有することができる。

#### 【0029】

メモリコントローラ40は、ホストインターフェース45を介してホスト20と通信することができる。例えば、ホストインターフェース45は、USB(Universal Serial Bus)、MMC(multimedia card)、PCI(peripheral component interconnection)、PCI-E(PCI-express)、ATA(Advanced Technology Attachment)、Serial-ATA、Parallel-ATA、SCSI(small computer small interface)、ESDI(enhanced small disk interface)、IDE(Integrated Drive Electronics)、MIPI(Mobile Industry Processor Interface)、NVMe(Nonvolatile Memory-express)、UFS(Universal Flash Storage Interface)などの多様なインターフェースのうち、少なくとも1つに提供できる。メモリコントローラ40は、不揮発性メモリインターフェース47を介して不揮発性メモリ装置50と通信することができる。

#### 【0030】

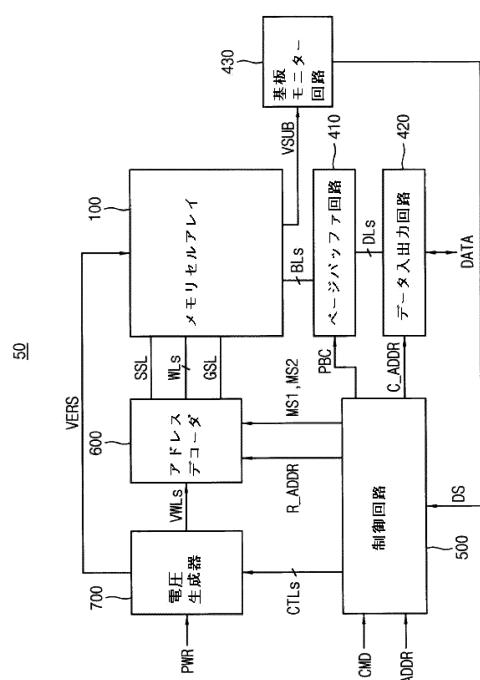

図4は、本発明の実施形態に係る図2の貯蔵装置における不揮発性メモリ装置を示すブロック図である。

#### 【0031】

図4を参照すると、不揮発性メモリ装置50は、メモリセルアレイ100、アドレスデコーダ600、ページバッファ回路410、データ入出力回路420、基板モニター回路430、制御回路500、及び電圧生成器700を含むことができる。

#### 【0032】

メモリセルアレイ100は、ストリング選択ライン(SSL)、複数のワードライン(WLs)、及び接地選択ライン(GSL)を介してアドレスデコーダ600と連結できる。また、メモリセルアレイ100は複数のビットライン(BLs)を介してページバッファ回路410と連結できる。メモリセルアレイ100は、複数のワードライン(WLs)及び複数のビットライン(BLs)に連結される複数のメモリセルを含むことができる。実施形態において、メモリセルアレイ100は基板上に積層されるワードラインの各々に連結されるメモリセルを含むことができる。

#### 【0033】

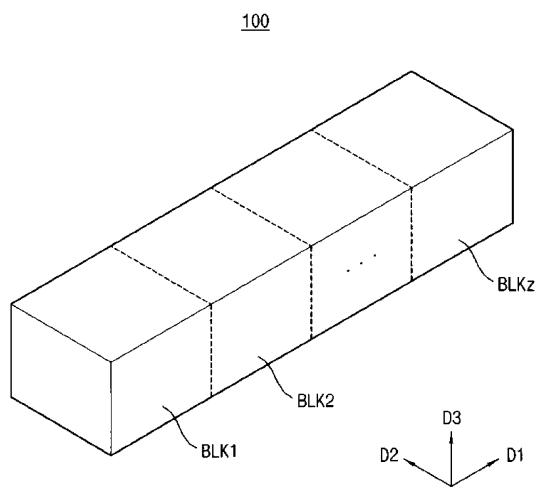

図5は、図4のメモリセルアレイを示すブロック図である。

#### 【0034】

図5を参照すると、メモリセルアレイ100は方向(D1～D3)に沿って伸張される複数のメモリブロック(BLK1～BLKz、zは3以上の自然数)を含む。実施形態に

10

20

30

40

50

おいて、メモリブロック (B L K 1 ~ B L K z) は図 4 に図示されたアドレスデコーダ 6 0 0 により選択される。例えば、アドレスデコーダ 6 0 0 はメモリブロック (B L K 1 ~ B L K z) のうち、ブロックアドレスに対応するメモリブロック (B L K) を選択することができる。アドレスデコーダ 6 0 0 は、ロードアドレス (R\_A D D R) に応答してメモリブロック (B L K) で少なくとも 1 つのサブブロックを選択することができる。

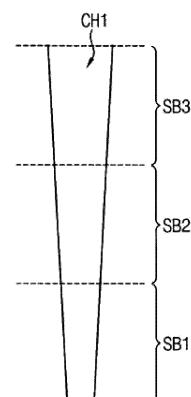

#### 【0035】

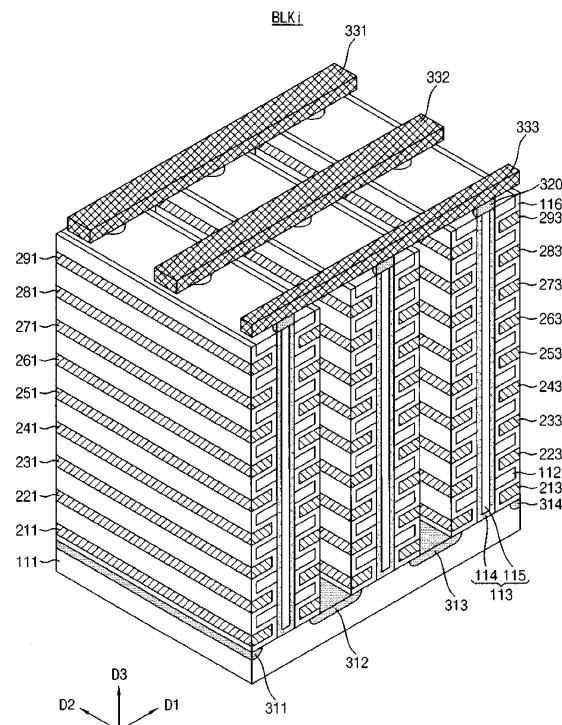

図 6 は、図 5 のメモリブロック (B L K 1 ~ B L K z) のうちの 1 つ (B L K i) を示す斜視図である。

#### 【0036】

図 6 を参照すると、メモリブロック (B L K i) は 3 次元構造または垂直構造で形成されるセルストリングを含む。メモリブロック (B L K i) は、複数の方向 (D 1、D 2、D 3) に沿って伸張された構造物を含む。10

#### 【0037】

メモリブロック (B L K i) を形成するためには、まず基板 1 1 1 が提供される。例えば、基板 1 1 1 はホウ素 (B、Boron) のような 5 族元素が注入されて形成された P - ウエルで形成できる。基板 1 1 1 上に、D 1 方向に沿って複数のドーピング領域 3 1 1 ~ 3 1 4 が形成される。例えば、複数のドーピング領域 3 1 1 ~ 3 1 4 は基板 1 1 1 と相異する n タイプの導電体で形成できる。

#### 【0038】

第 1 及び第 2 ドーピング領域 3 1 1、3 1 2 の間の基板 1 1 1 の領域上に、D 2 方向に沿って伸張される複数の絶縁物質 1 1 2 が D 3 方向に沿って順次に提供される。例えば、複数の絶縁物質 1 1 2 は D 3 方向に沿って特定距離だけ離隔して形成される。第 1 及び第 2 ドーピング領域 3 1 1、3 1 2 の間の基板 1 1 1 の上部に、D 2 方向に沿って順次に配置され、D 3 方向に沿って絶縁物質 1 1 2 を貫通するフィラー 1 1 3 が形成される。例示的に、フィラー 1 1 3 は絶縁物質 1 1 2 を貫通して基板 1 1 1 と連結される。ここで、フィラー 1 1 3 は第 2 及び第 3 ドーピング領域 3 1 2、3 1 3 の間の基板の上部と、第 3 及び第 4 ドーピング領域 3 1 3、3 1 4 の間の基板の上部にも形成される。20

#### 【0039】

例示的に、各フィラー 1 1 3 は複数の物質で構成される。例えば、各フィラー 1 1 3 の表面層 1 1 4 は第 1 タイプを有するシリコン物質を含む。例えば、各フィラー 1 1 3 の表面層 1 1 4 は基板 1 1 1 と同一なタイプを有するシリコン物質を含む。各フィラー 1 1 3 の内部層 1 1 5 は絶縁物質で構成される。例えば、各フィラー 1 1 3 の内部層 1 1 5 はシリコン酸化物 (Silicon Oxide) のような絶縁物質を含む。例えば、各フィラー 1 1 3 の内部層 1 1 5 はエアーギャップ (Air gap) を含むことができる。30

#### 【0040】

第 1 及び第 2 ドーピング領域 3 1 1、3 1 2 の間の領域で、絶縁物質 1 1 2、フィラー 1 1 3、そして基板 1 1 1 の露出した表面に沿って絶縁膜 1 1 6 が提供される。例示的に、D 3 方向に沿って提供される最後の絶縁物質 1 1 2 の D 3 方向側の露出面に提供されてもよい絶縁膜 1 1 6 は除去されてもよい。

#### 【0041】

第 1 及び第 2 ドーピング領域 3 1 1、3 1 2 の間の領域で、絶縁膜 1 1 6 の露出した表面上に第 1 導電物質 2 1 1 ~ 2 9 1 が提供される。例えば、基板 1 1 1 に隣接した絶縁物質 1 1 2 及び基板 1 1 1 の間に D 2 方向に沿って伸張される第 1 導電物質 2 1 1 が提供される。より詳しくは、基板 1 1 1 に隣接した絶縁物質 1 1 2 の下部面の絶縁膜 1 1 6 及び基板 1 1 1 の間に、D 1 方向に伸張される第 1 導電物質 2 1 1 が提供される。絶縁物質 1 1 2 のうち、特定の絶縁物質の上部面の絶縁膜 1 1 6 及び特定の絶縁物質の上部に配置された絶縁物質の下部面の絶縁膜 1 1 6 の間に、D 2 方向に沿って伸張される第 1 導電物質が提供される。例示的に、絶縁物質 1 1 2 の間に D 2 方向に伸張される複数の第 1 導電物質 2 2 1 ~ 2 8 1 が提供される。40

#### 【0042】

10

20

30

40

50

第2及び第3ドーピング領域312、313の間の領域で、第1及び第2ドーピング領域311、312上の構造物と同一な構造物が提供される。例示的に、第2及び第3ドーピング領域312、313の間の領域で、D2方向に伸張される複数の絶縁物質112、D2方向に沿って順次に配置され、D1方向に沿って複数の絶縁物質112を貫通する複数のフィラー113、複数の絶縁物質112及び複数のフィラー113の露出した表面に提供される絶縁膜116、そしてD2方向に沿って伸張される複数の第1導電物質212～292が提供される。第3及び第4ドーピング領域313、314の間の領域で、第1及び第2ドーピング領域311、312上の構造物と同一な構造物が提供される。例示的に、第3及び第4ドーピング領域312、313の間の領域で、D2方向に伸張される複数の絶縁物質112、D2方向に沿って順次に配置され、D3方向に沿って複数の絶縁物質112を貫通する複数のフィラー113、複数の絶縁物質112及び複数のフィラー113の露出した表面に提供される絶縁膜116、そしてD2方向に沿って伸張される複数の第1導電物質213～293が提供される。

#### 【0043】

複数のフィラー113上にドレイン320が各々提供される。ドレイン320上に、D1方向に伸張された第2導電物質331～333が提供される。第2導電物質331～333は、D2方向に沿って順次に配置される。第2導電物質331～333の各々は対応する領域のドレイン320と連結される。例示的に、ドレイン320及びD1方向に伸張された第2導電物質333は各々コンタクトプラグ(Contact plug)を介して連結できる。

#### 【0044】

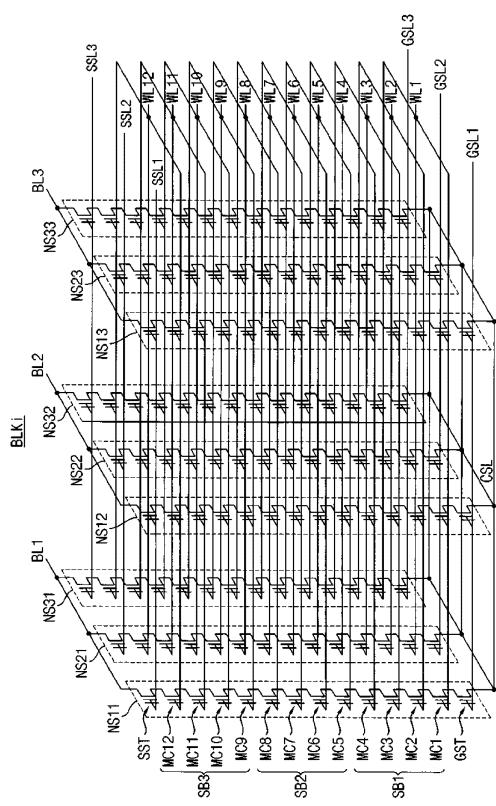

図7は、図6のメモリブロックを示す等価回路図である。

#### 【0045】

図7に図示されたメモリブロック(BLK<sub>i</sub>)は基板上に三次元構造で形成される三次元メモリブロックを示す。例えば、メモリブロック(BLK<sub>i</sub>)に含まれる複数のメモリセルストリングは基板と垂直な方向に形成できる。

#### 【0046】

図7を参照すると、メモリブロック(BLK<sub>i</sub>)はビットライン(BL1、BL2、BL3)と共にソースライン(CSL)の間に連結される複数のメモリセルストリング(NS11～NS33)を含むことができる。複数のメモリセルストリング(NS11～NS33)の各々は、ストリング選択トランジスタ(SST)、複数のメモリセル(MC1、MC2, . . . , MC12)、及び接地選択トランジスタ(GST)を含むことができる。

#### 【0047】

ストリング選択トランジスタ(SST)は、相応するストリング選択ライン(SSL1、SSL2、SSL3)に連結できる。複数のメモリセル(MC1、MC2, . . . , MC12)は、各々相応するワードライン(WL1、WL2, . . . , WL12)に連結できる。接地選択トランジスタ(GST)は、相応する接地選択ライン(GSL1、GSL2、GSL3)に連結できる。ストリング選択トランジスタ(SST)は相応するビットライン(BL1、BL2、BL3)に連結され、接地選択トランジスタ(GST)は共通ソースライン(CSL)に連結できる。同一高さのワードライン(例えば、WL1)は共通に連結され、接地選択ライン(GSL1、GSL2、GSL3)及びストリング選択ライン(SSL1、SSL2、SSL3)は各々分離できる。

#### 【0048】

以上で例示的に説明された1つのメモリブロック(BLK<sub>i</sub>)はそれより小さな複数のサブブロック(SB1、SB2、SB3)に区分できる。各々のサブブロック(SB1、SB2、SB3)はワードライン方向に区分できる。如何なる基準でサブブロックが区分されたとしても、各々のサブブロックはメモリブロック(BLK<sub>i</sub>)内で他のサブブロックとは独立的に消去できる。

#### 【0049】

サブブロック(SB1)は、メモリブロック(BLK<sub>i</sub>)に含まれたメモリセルのうち

、ワードライン (WL 1、WL 2、WL 3、WL 4) に連結されたメモリセルを含むことができる。サブブロック (SB 2) は、メモリブロック (BLKi) に含まれたメモリセルのうち、ワードライン (WL 5、WL 6、WL 7、WL 8) に連結されたメモリセルを含むことができる。サブブロック (SB 3) は、メモリブロック (BLKi) に含まれたメモリセルのうち、ワードライン (WL 9、WL 10、WL 11、WL 12) に連結されたメモリセルを含むことができる。即ち、サブブロック (SB 1、SB 2、SB 3) のうちの 1 つまたは 2 つ以上が同時に選択又は消去の対象とされることが可能である。このために、不揮発性メモリ装置 50 (図 4 参照) のアドレスデコーダ 600 は、サブブロック (SB) 単位でメモリセルを消去するためのバイアスを提供することができる。

#### 【0050】

また図 4 を参照すると、制御回路 500 はメモリコントローラ 40 からコマンド (CMD) 及びアドレス (ADDR) を受信し、コマンド (CMD) 及びアドレス (ADDR) に基づいて不揮発性メモリ装置 40 の消去動作、プログラム動作、及び読出動作を制御することができる。

#### 【0051】

例えば、制御回路 500 はコマンド (CMD) に基づいて電圧生成器 700 を制御するための制御信号 (CTLs) を生成し、アドレス信号 (ADDR) に基づいてローアドレス (R\_ADDR) 及びコラムアドレス (C\_ADDR) を生成することができる。制御回路 500 はローアドレス (R\_ADDR) をアドレスデコーダ 600 に提供し、コラムアドレス (C\_ADDR) をデータ入出力回路 420 に提供することができる。また、制御回路 500 は基板モニター回路 430 から提供される感知信号 (DS) に基づいて基板の電圧レベルが基準レベルに到達したか、または基板の電圧レベルが一定のレベルで基準時間の間維持されたことを示す第 1 モード信号 (MS) をアドレスデコーダ 600 に提供することができる。また、制御回路 500 はコマンド (CMD) が指示する動作を示す第 2 モード信号 (MS2) をアドレスデコーダ 600 に提供することができる。

#### 【0052】

アドレスデコーダ 600 は、ストリング選択ライン (SSL)、複数のワードライン (WLs)、及び接地選択ライン (GSL) を介してメモリセルアレイ 100 と連結できる。電圧生成器 700 は、制御回路 500 から提供される制御信号 (CTLs) に基づいて不揮発性メモリ装置 50 の動作に必要なワードライン電圧 (VWLs) を生成することができる。電圧生成器 700 から生成されるワードライン電圧 (VWLs) は、アドレスデコーダ 600 を介して複数のワードライン (WLs) に印加できる。

#### 【0053】

サブブロック単位の消去動作時、電圧生成器 700 はメモリブロックのウェルまたは基板に消去電圧 (VERS) を印加し、選択されたサブブロックのワードラインにワードライン消去電圧、即ち接地電圧を印加することができる。消去検証動作時、電圧生成器 700 は選択されたサブブロックのワードラインに消去検証電圧を印加するか、またはワードライン単位で消去検証電圧を印加することができる。

#### 【0054】

例えば、プログラム動作時、電圧生成器 700 は選択ワードラインにプログラム電圧を印加し、非選択ワードラインにはプログラムバス電圧を印加することができる。また、プログラム検証動作時、電圧生成器 700 は選択ワードラインにプログラム検証電圧を印加し、非選択ワードラインには検証バス電圧を印加することができる。また、読出動作時、電圧生成器 700 は選択ワードラインに読出電圧を印加し、非選択ワードラインには読出バス電圧を印加することができる。

#### 【0055】

ページバッファ回路 410 は、複数のビットライン (BLs) を介してメモリセルアレイ 100 と連結できる。ページバッファ回路 410 は、複数のページバッファを含むことができる。ページバッファ回路 410 は、プログラム動作時、選択されたページにプログラムされるデータを臨時に貯蔵し、読出動作時、選択されたページから読み出されたデータを出力する。

10

20

30

40

50

タを臨時に貯蔵することができる。

**【 0 0 5 6 】**

データ入出力回路 420 は、データライン (D L s) を介してページバッファ回路 410 と連結できる。プログラム動作時、データ入出力回路 420 はメモリコントローラ 40 からプログラムデータ (DATA) を受信し、制御回路 500 から提供されるコラムアドレス (C\_ADDR) に基づいてプログラムデータ (DATA) をページバッファ回路 410 に提供することができる。読み動作時、データ入出力回路 420 は制御回路 500 から提供されるコラムアドレス (C\_ADDR) に基づいてページバッファ回路 410 に貯蔵された読みデータ (DATA) をメモリコントローラ 40 に提供することができる。

**【 0 0 5 7 】**

基板モニター回路 430 は、消去動作時に、基板 111 に印加される消去電圧 (VER S) による基板電圧 (V SUB) の電圧レベルをモニタリングし、基板電圧 (V SUB) が基準レベルに到達する場合、または基板の電圧 (V SUB) が一定レベルで一定時間の間維持される場合、これを示す感知信号 (DS) を制御回路 500 に提供することができる。

10

**【 0 0 5 8 】**

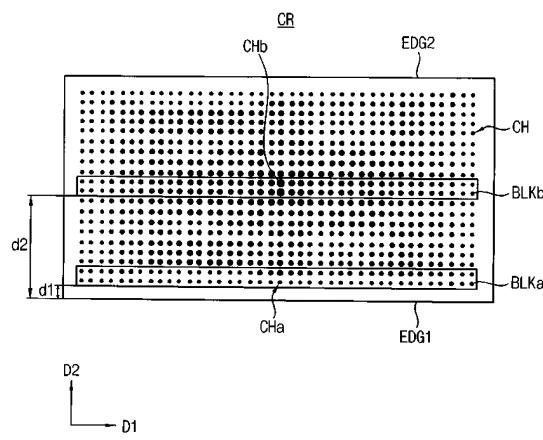

図 8 は、本発明の実施形態に係る図 4 のメモリセルアレイが形成されるセル領域を示す。

**【 0 0 5 9 】**

図 8 を参照すると、セル領域 CR は複数のチャンネルホール (CH) を含む。

**【 0 0 6 0 】**

チャンネルホールサイズ、例えば、チャンネルホール直径 (diameter) はセル領域 CR 内の位置によって異なることがある。具体的に、第 1 及び第 2 エッジ EDG1、EDG2 に隣接したチャンネルホール (CHa) の場合、周辺の密度が低いので、工程上の理由により他のチャンネルホール (CHb) と直径が異なることがある。セル領域 CR の中心領域に位置したチャンネルホール (CHb) の直径は、第 1 及び第 2 エッジ EDG1、EDG2 に隣接したチャンネルホール (CHa) の直径より大きいことがある。メモリブロック (BLKa) は第 2 エッジ EDG2 に隣接し、第 2 エッジ EDG2 から第 1 距離 (d1) だけ離隔している。メモリブロック (BLKb) は、第 1 及び第 2 エッジ EDG1、EDG2 に隣接せず、セル領域 CR の中心に位置し、第 2 エッジ EDG2 から第 2 距離 (d2) だけ離隔している。メモリブロック (BLKa) に含まれた第 1 チャンネルホール CHa の第 1 直径 (D1) は、メモリブロック (BLKb) に含まれた第 2 チャンネルホール CHb の第 2 直径 (D2) より小さいかもしれない。

20

**【 0 0 6 1 】**

図 9 A 及び図 9 B は、図 8 のメモリブロックに各々含まれたセルストリングの断面を例示的に示す。

**【 0 0 6 2 】**

図 9 A を参照すると、メモリブロック (BLKa) に含まれた第 1 チャンネルホール CHa には表面層 114 及び内部層 115 を含むフィラーが形成されることができ、第 1 チャンネルホール CHa の周りには電荷貯蔵層 CS が形成されることができ、電荷貯蔵層 CS は ONO 構造を有することができる。

30

**【 0 0 6 3 】**

図 9 B を参照すると、メモリブロック (BLKb) に含まれた第 2 チャンネルホール CHb には表面層 114 及び内部層 115 を含むフィラーが形成されることができ、第 2 チャンネルホール CHb の周りには電荷貯蔵層 CS が形成されることができ、電荷貯蔵層 CS は ONO 構造を有することができる。

40

**【 0 0 6 4 】**

実施形態において、メモリブロック (BLKb) に含まれた電荷貯蔵層 CS の厚さは、メモリブロック (BLKa) に含まれた電荷貯蔵層 CS の厚さと異なることがある。このようなチャンネルホール直径の差によって、メモリセルの特性の差が発生することがある。具体的に、チャンネルホールの周りにゲート電極が位置するゲートオールアラウンド (g

50

ate all around) 形態の垂直型メモリ装置の場合、チャンネルホール直径が小さくなれば、ゲート電極（例えば、図 6 の 213）からチャンネル領域 114 に形成される電場の集束度が高まるようになる。したがって、第 1 チャンネルホール CH a のようにチャンネルホール直径の小さいメモリセルは、第 2 チャンネルホール CH b のようにチャンネルホール直径が大きいメモリセルに比べて、プログラム及び消去動作の速度が速くなる。

#### 【0065】

また、図 8 を参照すると、セル領域 CR 内で 1 つのメモリブロックは第 1 方向 (D1) に、即ち、ワードライン方向に 1 ページに該当する全てのメモリセルを含み、第 2 方向 (D2) に、即ち、ビットライン方向に幾つかのストリングを含むように構成される。したがって、各メモリブロックは第 1 方向に長く構成されて、チャンネルホールサイズ、即ち、直径の差はメモリブロック単位で表れることができる。したがって、メモリブロック (BLKa) に含まれたメモリセルのプログラム速度及び消去速度は、メモリブロック (BLKb) に含まれたメモリセルのプログラム速度及び消去速度より速いことがある。

10

#### 【0066】

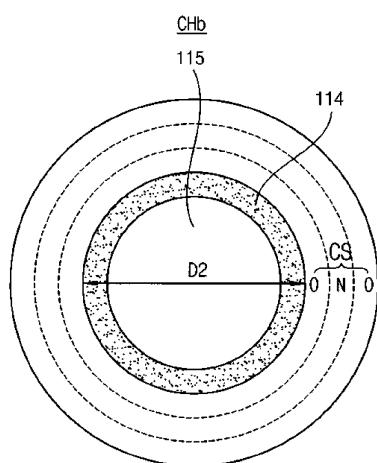

図 10 は、図 8 のメモリブロックに対するプログラム動作及び消去動作の遂行結果を示すグラフである。

#### 【0067】

図 10 を参照すると、横軸は図 8 の第 2 方向、即ち、ビットライン方向に従うメモリブロックの位置を示し、縦軸は電圧を示す。具体的に、実線 71 はプログラムされたメモリセルのメモリブロック位置に従うしきい電圧の中心値を示し、点線 72 は消去されたメモリセルのメモリブロック位置に従うしきい電圧の中心値を示す。

20

#### 【0068】

前述したように、プログラム速度及び消去速度の差によって実線 71 のように、プログラムされたメモリセルのしきい電圧はメモリブロック位置に沿って U 字形態を有し得る。また、点線 72 のように、消去されたメモリセルのしきい電圧はメモリブロック位置に沿って上下反転した I 字形態を有し得る。

#### 【0069】

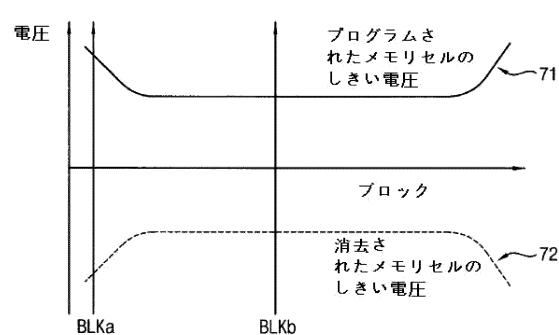

図 11 は、図 8 の 1 つのチャンネルの垂直構造を示す。

#### 【0070】

図 11 を参照すると、垂直型メモリ装置に含まれた 1 つのセルストリングに対応するチャンネルホール CH 1 が図示されている。チャンネルホール CH 1 は基板上に積層されたゲート電極及び絶縁膜の一部領域をエッチングすることによって形成されるので、表面から深さが大きくなるにつれてエッチングが進行しにくくなることがある。これによって、チャンネルホール CH 1 の直径は基板側に行くほど小さくなることがある。

30

#### 【0071】

一実施形態において、チャンネルホール CH 1 のチャンネルホール直径によって 3 個の区域に区分することができる。例えば、チャンネルホール直径が第 1 値より小さな区域を第 1 区域 (Z1) と決定し、チャンネルホール直径が第 1 値以上であり、第 2 値よりより小さな区域を第 2 区域 (Z2) と決定し、チャンネルホール直径が第 2 値以上であり、第 3 値より小さな区域を第 3 区域 (Z3) と決定することができる。第 1 区域 (Z1) はサブブロック (SB1) に該当し、第 2 区域 (Z2) はサブブロック (SB2) に該当し、第 3 区域 (Z3) はサブブロック (SB3) に該当することができる。したがって、1 つのセルストリングでもサブブロックの位置に従うチャンネルホール直径の差によって、メモリセルの特性の差が発生することができる。したがって、1 つのセルストリングでもサブブロックの位置によってプログラム速度及び消去速度の差が発生することができる。

40

#### 【0072】

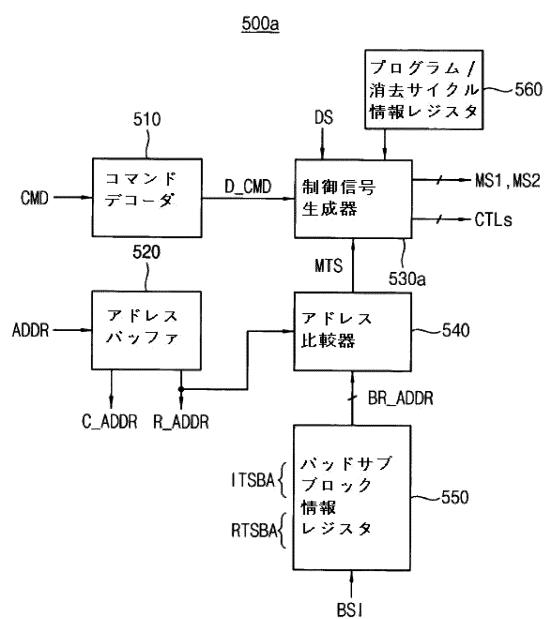

図 12 は、本発明の実施形態に係る図 4 の不揮発性メモリ装置における制御回路の構成を示す。

#### 【0073】

図 12 を参照すると、制御回路 500a は、コマンドデコーダ 510、アドレスバッフ

50

ア520、制御信号生成器530a、アドレス比較器540、バッドサブロック情報レジスタ550、及びプログラム／消去サイクル情報レジスタ560を含む。

#### 【0074】

コマンドデコーダ510は、コマンド(CMD)をデコーディングし、デコーディングされたコマンド(D\_CMD)を制御信号生成器530aに提供する。アドレスバッファ520はアドレス(ADDR)を受信し、アドレス(ADDR)のうち、ローアドレス(R\_ADDR)はアドレスデコーダ600とアドレス比較器540に提供され、コラムアドレス(C\_ADDR)はデータ入出力回路420に提供される。

#### 【0075】

バッドサブロック情報レジスタ550はバッドサブロック情報(BSI)を貯蔵し、バッドサブロック情報(BSI)は初期バッドサブロックアドレス(ITSBA)及びラン-タイムバッドサブロックアドレス(RTSBA)を含む。初期バッドサブロックアドレス(ITSBA)は不揮発性メモリ装置50が出荷される時に指定されたバッドサブロックのアドレスであり、ラン-タイムバッドサブロックアドレス(RTSBA)は不揮発性メモリ装置50の動作中に指定されたバッドサブロックのアドレスである。

10

#### 【0076】

アドレス比較器540はバッドサブロック情報レジスタ550に貯蔵された少なくとも1つのバッドサブロックローアドレス(BR\_ADDR)とローアドレス(R\_ADDR)を比較し、比較結果を示すマッチ信号(MTS)を制御信号生成器530aに提供する。

20

#### 【0077】

制御信号生成器530aはデコーディングされたコマンド(D\_CMD)及びマッチ信号(MS)を受信し、デコーディングされたコマンド(D\_CMD)が指示する動作がバッドサブロックに関連したものかに基づいて制御信号(CTLs)を生成して電圧生成器700に提供することができる。また、制御信号生成器530aは感知信号(DS)を受信し、感知信号(DS)に基づいて基板の電圧(VSUB)レベルが基準レベルに到達したか、または基板の電圧(VSUB)が一定レベルで維持されたことを示す第1モード信号(MS)をアドレスデコーダ600に提供する。また、制御信号生成器530aはデコーディングされたコマンド(D\_CMD)が指示する動作を示す第2モード信号(MS2)をアドレスデコーダ600に提供する。

30

#### 【0078】

制御信号生成器530aは、マッチ信号(MS)がローアドレス(R\_ADDR)がノーマルサブロックをアクセスすることを示す場合、プログラム／消去サイクル情報レジスタ560を参照して第1プログラム／消去サイクルがノーマルサブロックに適用されるように制御信号(CTLs)を生成し、マッチ信号(MS)がローアドレス(R\_ADDR)がバッドサブロックをアクセスすることを示す場合、プログラム／消去サイクル情報レジスタ560を参照して第2プログラム／消去サイクルがバッドサブロックに適用されるように制御信号(CTLs)を生成する。第1プログラム／消去サイクルは、第2プログラム／消去サイクルより頻度が大きいことがある。したがって、バッドサブロックに対するプログラム／消去サイクルが緩和されて、不揮発性メモリ装置50の寿命を増加させることができる。

40

#### 【0079】

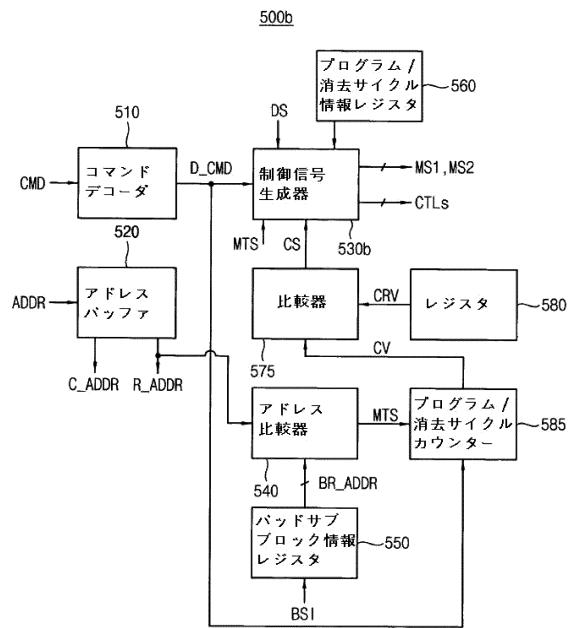

図13は、本発明の実施形態に係る図4の不揮発性メモリ装置における制御回路の構成を示す。

#### 【0080】

図13を参照すると、制御回路500bは、コマンドデコーダ510、アドレスバッファ520、制御信号生成器530b、アドレス比較器540、バッドサブロック情報レジスタ550、プログラム／消去サイクル情報レジスタ560、比較器575、レジスタ580、及びプログラム／消去サイクルカウンター585を含む。

50

**【0081】**

図13の制御回路500bは、比較器575、レジスタ580、及びプログラム／消去サイクルカウンター585をさらに含み、アドレス比較器540がマッチ信号(MTS)をプログラム／消去サイクルカウンター585に提供するという点が図12の制御回路500bと主に相違している。

**【0082】**

プログラム／消去サイクルカウンター585は、マッチ信号(MTS)及びデコーディングされたコマンド(D\_CMD)に基づいてロードアドレス(R\_ADDR)がバッドサブロックをアクセスし、デコーディングされたコマンド(D\_CMD)がプログラムコマンドであるか、または消去コマンドである場合に、カウントイング値(CV)を増加させる。比較器575は、カウントイング値(CV)とレジスタ580に貯蔵された基準カウンティング値(CRV)を比較して、その比較結果を示す比較信号(CS)を制御信号生成器530bに提供する。制御信号生成器530bは、デコーディングされたコマンド(D\_CMD)、マッチ信号(MTS)、及び比較信号(CS)を受信し、バッドサブロックに対して基準カウンティング値(CRV)までは第2プログラム／消去サイクルが適用され、基準カウンティング値(CRV)を超過する場合には第2プログラム／消去サイクルより頻度が小さな第3プログラム消去／サイクルが適用されるように制御信号(CTLs)、第1モード信号(MS1)、及び第2モード信号(MS)を生成する。

10

**【0083】**

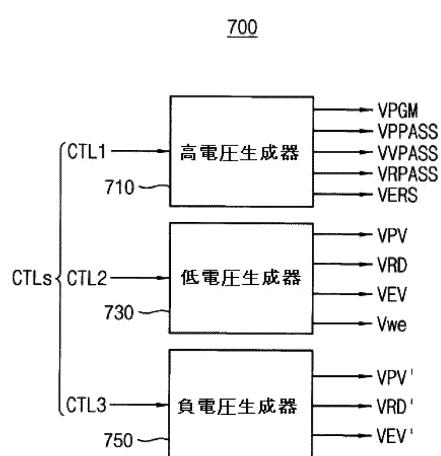

図14は、本発明の実施形態に係る図4の不揮発性メモリ装置における電圧生成器の構成を示すブロック図である。

20

**【0084】**

図14を参照すると、電圧生成器700は高電圧生成器710及び低電圧生成器730を含むことができる。実施形態において、電圧生成器700は負電圧(negative voltage)生成器750をさらに含むことができる。

**【0085】**

高電圧生成器710は、第1制御信号(CTL1)に応答してコマンド(CMD)が指示する動作によってプログラム電圧(VPGM)、プログラムバス電圧(VPPASS)、検証バス電圧(VVPASS)、読出バス電圧(VRPASS)、及び消去電圧(VERS)を生成することができる。プログラム電圧(VPGM)は選択ワードラインに印加され、プログラムバス電圧(VPPASS)、プログラム検証バス電圧(VVPASS)、読出バス電圧(VRPASS)は非選択ワードラインに印加され、消去電圧(VERS)はメモリブロックのウェルまたは基板に印加できる。第1制御信号(CTL1)は複数のビットを含んでコマンド(CMD)が指示する動作を示すことができる。

30

**【0086】**

低電圧生成器730は、第2制御信号(CTL2)に応答してコマンド(CMD)が指示する動作によってプログラム検証電圧(VPV)、読出電圧(VRD)、消去検証電圧(VEV)、及びワードライン消去電圧(Vwe)を生成することができる。プログラム検証電圧(VPV)、読出電圧(VRD)、及び消去検証電圧(VEV)は、動作によって選択ワードラインに印加できる。消去電圧(Vwe)は、選択されたサブブロックのワードラインに印加できる。第2制御信号(CTL2)は、複数のビットを含んでコマンド(CMD)が指示する動作を示すことができる。

40

**【0087】**

負電圧生成器750は、第3制御信号(CTL3)に応答してコマンド(CMD)が指示する動作によって負のレベルを有するプログラム検証電圧(VPV')、読出電圧(VRD')、及び消去検証電圧(VEV')を生成することができる。第3制御信号(CTL3)は複数のビットを含んでコマンド(CMD)が指示する動作を示すことができる。

**【0088】**

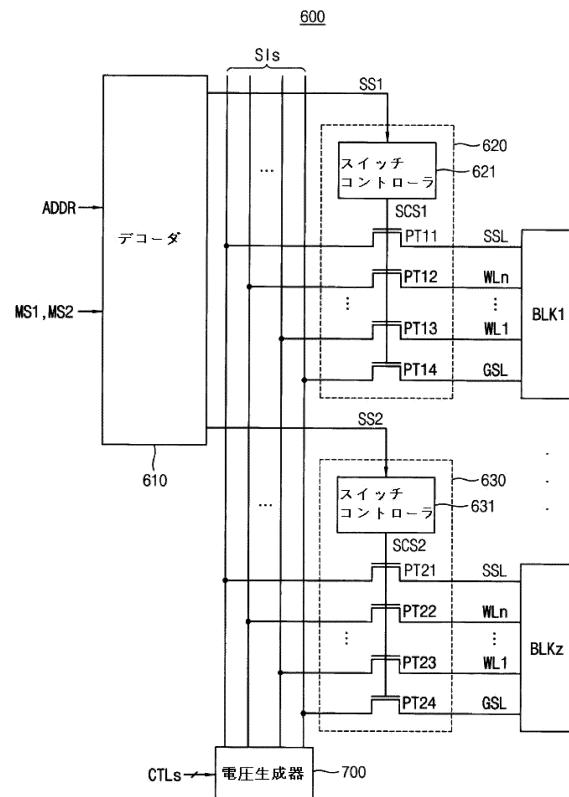

図15は、本発明の実施形態に係る図4の不揮発性メモリ装置におけるアドレスデコーダの構成を示す。

50

**【 0 0 8 9 】**

図15では、説明の便宜のために、メモリブロック（B L K 1、B L K z）を共に図示する。図15を参照すると、アドレスデコーダ600は、デコーダ610、第1スイッチ回路620、及び第2スイッチ回路630を含むことができる。

**【 0 0 9 0 】**

デコーダ610は、アドレス（ADD R）、第1モード信号（M S 1）、及び第2モード信号（M S 2）を受信し、アドレス（ADD R）が指定するサブブロックと第1モード信号（M S 1）が示す基板電圧（V S U B）のレベルや維持時間、及び第2モード信号（M S 2）が示す動作によって、第1選択信号（S S 1）及び第2選択信号（S S 2）を生成し、第1選択信号（S S 1）と第2選択信号（S S 2）を第1スイッチ回路620及び第2スイッチ回路630の各々に提供することができる。10

**【 0 0 9 1 】**

第1スイッチ回路620及び第2スイッチ回路630は、電圧生成器700に連結される選択ライン（S I s）に連結できる。第1スイッチ回路620は、メモリブロック（B L K 1）と少なくとも1つのストリング選択ライン（S S L）、複数のワードライン（W L 1 ~ W L n）、及び少なくとも1つの接地選択ライン（G S L）を介して連結できる。第2スイッチ回路630は、メモリブロック（B L K z）と少なくとも1つのストリング選択ライン（S S L）、複数のワードライン（W L 1 ~ W L n）、及び少なくとも1つの接地選択ライン（G S L）を介して連結できる。

**【 0 0 9 2 】**

第1スイッチ回路620は、選択ライン（S I s）及び第1メモリブロック（B L K 1）のストリング選択ライン（S S L）、複数のワードライン（W L 1 ~ W L n）、及び接地選択ライン（G S L）の各々と連結される複数のパストランジスタ（P T 1 1 ~ P T 1 4）及びスイッチコントローラ621を含むことができる。スイッチコントローラ621は、第1選択信号（S S 1）に応答してパストランジスタ（P T 1 1 ~ P T 1 4）のターン-オンとターン-オフを制御することができる。第2スイッチ回路630は、選択ライン（S I s）及びメモリブロック（B L K z）のストリング選択ライン（S S L）、複数のワードライン（W L 1 ~ W L n）及び接地選択ライン（G S L）の各々と連結される複数のパストランジスタ（P T 2 1 ~ P T 2 4）及びスイッチコントローラ631を含むことができる。スイッチコントローラ631は、第2選択信号（S S 2）に応答してパストランジスタ（P T 2 1 ~ P T 2 4）のターン-オンとターン-オフを制御することができる。20

**【 0 0 9 3 】**

図16は、本発明の実施形態に係る不揮発性メモリ装置の動作方法を示すフローチャートである。

**【 0 0 9 4 】**

以下では、図7のメモリブロック（B L K i）のサブブロック（S B 1、S B 2、S B 3）のうち、基板に隣接した第1サブブロック（S B 1）が少なくとも1つのバッドサブブロックに該当し、サブブロック（S B 2、S B 3）が少なくとも1つのノーマルサブブロックに該当すると仮定する。30

**【 0 0 9 5 】**

不揮発性メモリ装置のメモリブロックは、プログラムフェールや消去フェールなどに起因して誤動作を起こすことがある。この場合に、該当メモリブロックはランタイムバッドブロックと見なされて、既にリザーブ（reserved）された他のブロックと代替される。また、ランタイムバッドブロックの以外にも不揮発性メモリ装置が工場で出荷される時、既にバッドブロックとして知られている初期バッドブロックもある。ランタイムバッドブロックの場合に、N A N D フラッシュメモリを使用するに当たって、長期間に亘って少量しか発生しないことが一般的である。そして、初期バッドブロックの場合にも、工場で出荷される時、存在しない又は少量しか存在しないのが通常である。しかしながら、ランタイムバッドブロックが短期間に数多く発生する場合、または初期バッドブロックが初期から40

多い場合に、全てのリザーブドブロック (reserved block) が枯渇してしまうことが懸念され、その場合、不揮発性メモリ装置はそれ以上使用できなくなる。このような理由によっても半導体貯蔵装置の寿命は制限を受ける。

#### 【 0 0 9 6 】

第1サブブロック (S B 1) は基板に隣接して形成され、チャンネル幅が狭いため、第1サブブロック (S B 1) のメモリセルはプログラム電圧や消去電圧によるストレスを最も多く受ける。したがって、第1サブブロック (S B 1) でエラーが発生する確率が高まるので、第1サブブロック (S B 1) はバッドサブブロックと指定できる。

#### 【 0 0 9 7 】

図2乃至図16を参照すると、このような寿命の制限を克服するために、本発明の実施形態では、第1メモリブロックに含まれるサブブロックをエラー発生頻度に基づいて少なくとも1つのノーマルサブブロック (ノーマルサブブロック) と少なくとも1つのバッドサブブロック (バッドサブブロック) に区分する (S 1 0 0)。バッドサブブロックの情報はバッドサブブロック情報レジスタ49、550に貯蔵できる。制御回路500は、コマンド (C M D) 及びアドレス (A D D R) に応答してノーマルサブブロック及びバッドサブブロックに互いに異なるプログラム / 消去サイクルを適用し (S 2 0 0)、バッドサブブロックに緩和されたプログラム / 消去サイクルを適用することにより、不揮発性メモリ装置50の寿命を延長させることができる。

#### 【 0 0 9 8 】

図17は、図16でステップ (S 2 0 0) をより詳細に示すフローチャートである。

#### 【 0 0 9 9 】

図18は、図17で少なくとも第2プログラム / 消去サイクルが適用されるステップを詳細に示す。

#### 【 0 1 0 0 】

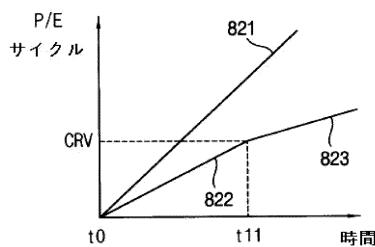

図19A及び図19Bは、各々ノーマルサブブロックとバッドサブブロックに適用されるプログラム消去サイクル (カウント値) を示す。

#### 【 0 1 0 1 】

図17乃至図19Bを参照すると、ノーマルサブブロック及びバッドサブブロックに互いに異なるプログラム / 消去サイクルを適用するために (S 2 0 0)、制御回路500はローアドレス (R\_A D D R) がバッドサブブロックをアクセスするかを判断する (S 2 1 0)。ローアドレス (R\_A D D R) がノーマルサブブロックをアクセスすれば (S 2 0 0でN O)、制御回路500はプログラム / 消去サイクル情報レジスタ560を参照して、第1プログラム消去サイクル811、821がノーマルサブブロックに適用されるように電圧生成器700及びアドレスデコーダ600を制御する (S 2 2 0)。ローアドレス (R\_A D D R) がバッドサブブロックをアクセスすれば (S 2 0 0でY E S)、制御回路500はプログラム / 消去サイクル情報レジスタ560を参照して、少なくとも第2プログラム消去サイクル812、823がバッドサブブロックに適用されるように電圧生成器700及びアドレスデコーダ600を制御する (S 2 3 0)。

#### 【 0 1 0 2 】

図18を参照すると、少なくとも第2プログラム / 消去サイクルがバッドサブブロックに適用されるようにするために (S 2 3 0)、制御回路500はバッドサブブロックに対するプログラム / 消去サイクルカウント値が基準カウント値 (C R V) を超過したか否かを判断する (S 2 4 0)。バッドサブブロックに対するプログラム / 消去サイクルカウント値が基準カウント値 (C R V) を超過しなければ (S 2 3 0でN O)、制御回路500は第2プログラム / 消去サイクル822がバッドサブブロックに適用されるように電圧生成器700及びアドレスデコーダ600を制御する (S 5 0)。バッドサブブロックに対するプログラム / 消去サイクルカウント値が基準カウント値 (C R V) を超過する第1時点 (t 1 1) 以後から (S 2 3 0でY E S)、制御回路500は第3プログラム / 消去サイクル823がバッドサブブロックに適用されるように電圧生成器700及びアドレスデコーダ600を制御する (S 2 6 0)。

10

20

30

40

50

**【0103】**

図19Aで、第2プログラム／消去サイクル812は第1プログラム／消去サイクル811より小さく、図19Bで第2プログラム／消去サイクル822は第1プログラム／消去サイクル821より小さく、第3プログラム／消去サイクル823は第2プログラム／消去サイクル822より小さい。

**【0104】**

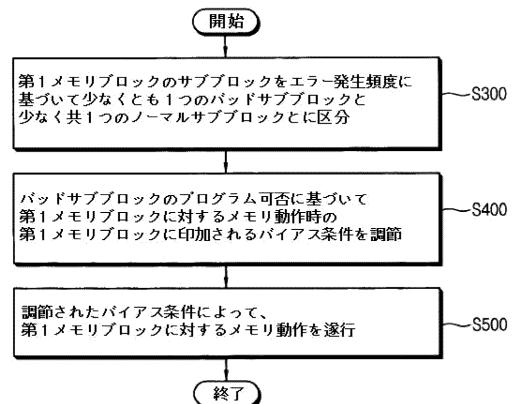

図20は、本発明の実施形態に係る不揮発性メモリ装置の動作方法を示すフローチャートである。

**【0105】**

以下では、図7のメモリブロック(BLK<sub>i</sub>)のサブブロック(SB1、SB2、SB3)のうち、基板に隣接した第1サブブロック(SB1)がバッドサブブロックに該当し、サブブロック(SB2、SB3)がノーマルサブブロックに該当すると仮定する。

10

**【0106】**

図2乃至図15及び図20を参照すると、第1メモリブロックに含まれるサブブロックをエラー発生頻度に基づいてノーマルサブブロックとバッドサブブロックに区分する(S300)。制御回路500はコマンド(CMD)及びアドレス(ADDR)に応答して、バッドサブブロックのプログラム可否に基づいて第1メモリブロックに対するメモリ動作時に第1メモリブロックに適用されるバイアス条件を調節する(S400)。制御回路500は調節されたバイアス条件によって、第1メモリブロックに対するメモリ動作が遂行されるよう電圧生成器700とアドレスデコーダ600を制御する(S500)。メモリ動作は消去動作または読出動作でありうる。

20

**【0107】**

図21A乃至図26Bは、サブブロックに対するバイアス条件を示す。

**【0108】**

図21A乃至図26Bでは、図7のメモリブロックでビットライン(BL1)に連結されたサブブロック(SB1～SB3)を対象として説明する。

**【0109】**

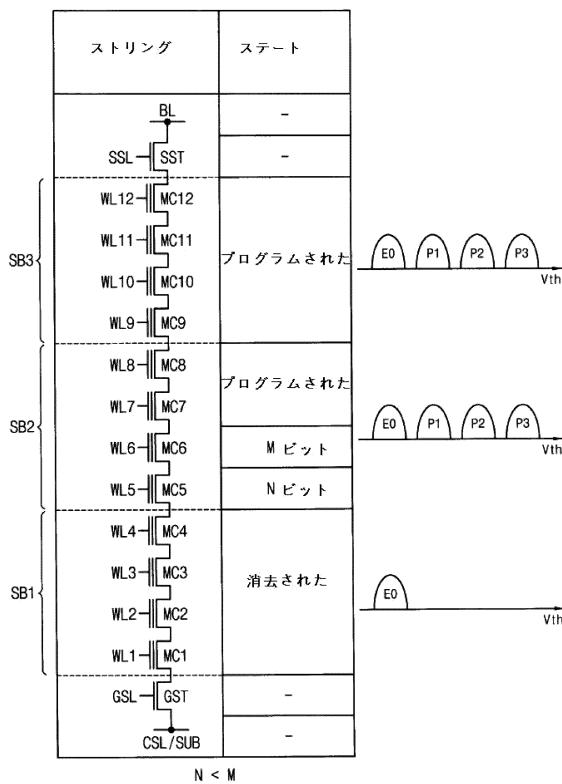

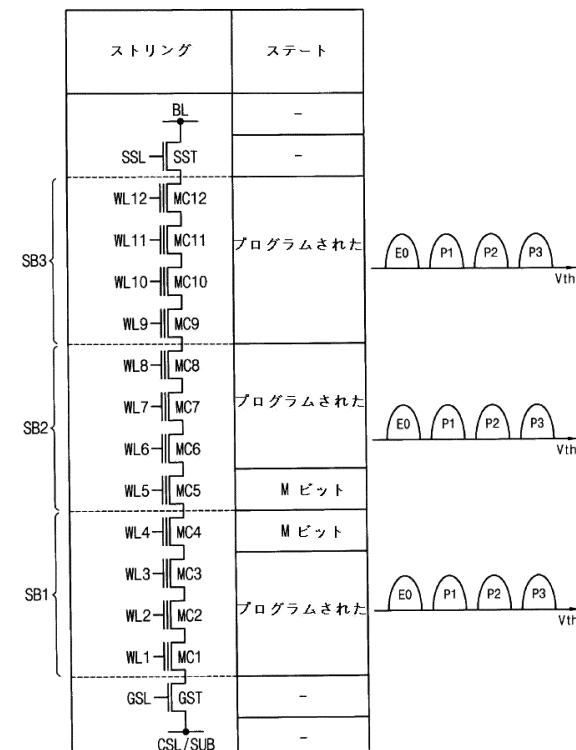

図21A及び図21Bは、図7のメモリブロックのサブブロックのプログラム状態を示す。

**【0110】**

30

図21Aは、第2及び第3サブブロック(SB2、SB3)が消去状態(E0)及びプログラム状態(P1、P2、P3)でプログラムされた場合を示し、図21Bは第1乃至第3サブブロック(SB1、SB2、SB3)が消去状態(E0)及びプログラム状態(P1、P2、P3)でプログラムされた場合を示す。メモリブロック(BLK<sub>i</sub>)に対するメモリ動作時に、バッドサブブロックである第1サブブロック(SB1)のプログラム可否は第2及び第3サブブロック(SB2、SB3)のしきい電圧が影響を受ける程度に応じて変わる。したがって、このような影響を考慮して、バッドサブブロックのプログラム可否に基づいて第1メモリブロックに対するメモリ動作時のバイアス条件を調節する。即ち、バッドサブブロックがプログラムされていれば、サブブロック(SB2)が受ける影響が大きく、バッドサブブロックがプログラムされていなければ、サブブロック(SB2)が受ける影響が小さいことがある。

40

**【0111】**

メモリセルの各々がM(Mは、2以上の自然数)ビットを貯蔵することができる時、図21Aのようにバッドサブブロック(SB1)をプログラムせず、第1メモリブロックに対するプログラム動作を完了する場合、バッドサブブロック(SB1)に隣接した境界ワードライン(WL5)にはN(Nは、Mより小さい自然数)ビットのみをプログラムすることができる。境界ワードライン(WL5)にNビットのみをプログラムして境界ワードライン(WL5)に連結されるメモリセルのプログラム状態の間のマージンを増加させることができる。また、図21Bのように、バッドサブブロック(SB1)をプログラムし、第1メモリブロックに対するプログラム動作を完了する場合には、境界ワードライン(

50

W L 5 ) に連結されるメモリセルにも M ビットをプログラムする。

【 0 1 1 2 】

図 2 2 A は、バッドサブブロックがプログラムされていない場合、第 1 メモリブロックに対する消去動作時の消去バイアス条件を示す。

【 0 1 1 3 】

図 2 2 A を参照すると、制御回路 5 0 0 はセルストリングのビットライン ( B L ) 、ストリング選択ライン ( S S L ) 、接地選択ライン ( G S L ) はフローティングさせ、サブブロック ( S B 2 、 S B 3 ) のワードライン ( W L 5 ~ W L 1 2 ) には第 1 ワードライン消去電圧 ( V w e 1 ) を印加し、バッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) には第 2 ワードライン消去電圧 ( V w e 2 ) を印加し、基板 S U B には消去電圧 ( V R E S ) を印加する。第 1 ワードライン消去電圧 ( V w e 1 ) は接地電圧と同一であるか、または接地電圧より若干高いレベルを有することができ、第 2 ワードライン消去電圧 ( V w e 2 ) は第 1 ワードライン消去電圧 ( V w e 1 ) より高い。したがって、バッドサブブロック ( S B 1 ) のメモリセルが過消去されることを防止することができる。

10

【 0 1 1 4 】

図 2 2 B は、バッドサブブロックがプログラムされた場合、第 1 メモリブロックに対する消去動作時の消去バイアス条件を示し、図 2 3 A は図 2 2 B のバイアス条件が適用される場合のバッドサブブロック電圧と基板電圧を示し、図 2 3 B は図 2 2 B のバイアス条件が適用される場合に図 1 3 の第 1 スイッチ回路を示す。

【 0 1 1 5 】

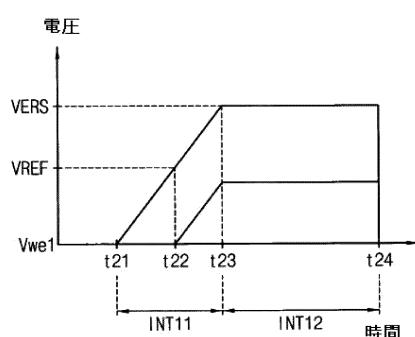

図 2 2 B 及び図 2 3 A を参照すると、制御回路 5 0 0 は、セルストリングのビットライン ( B L ) 、ストリング選択ライン ( S S L ) 、接地選択ライン ( G S L ) はフローティングさせ、サブブロック ( S B 2 、 S B 3 ) のワードライン ( W L 5 ~ W L 1 2 ) には第 1 ワードライン消去電圧 ( V w e 1 ) を印加する。基板 1 1 1 に印加される消去電圧 ( V E R S ) により基板電圧 ( V S U B ) のレベルが線形的に増加する第 1 区間 ( I N T 1 1 ) で、バッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) に第 1 ワードライン消去電圧 ( V w e 1 ) を印加する。第 1 区間 ( I N T 1 1 ) は、基板 1 1 1 に消去電圧 ( V E R S ) が印加され始める時点 ( t 2 1 ) から消去電圧 ( V E R S ) により基板電圧 ( V S U B ) が消去電圧 ( V E R S ) のレベルに到達する時点 ( t 2 3 ) までであつてよい。第 2 区間 ( I N T 1 2 ) は基板 1 1 1 に消去電圧 ( V E R S ) が印加され始める時点 ( t 2 3 ) から時点 ( t 2 4 ) まで一定であつてもよい。第 1 区間 ( I N T 1 1 ) でバッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) に第 1 ワードライン消去電圧 ( V w e 1 ) を印加してから、第 1 区間 ( I N T 1 1 ) の第 1 時点 ( t 2 2 ) でバッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) をフローティングさせる。

20

【 0 1 1 6 】

第 1 時点 ( t 2 2 ) でバッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) がフローティングされれば、バッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) の電圧レベルは基板電圧 ( V S U B ) レベルを追従するようになる。第 1 時点 ( t 2 2 ) は消去電圧 ( V E R S ) の印加によって上昇する基板電圧 ( V S U B ) のレベルが基準レベル ( V R E F ) に到達する時点であつてもよい。バッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) は時点 ( t 2 3 ) から時点 ( t 2 4 ) まで一定のレベルに維持できる。

30

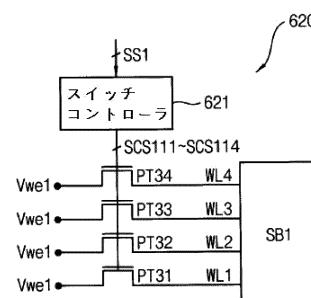

【 0 1 1 7 】

図 2 3 B を参照すると、バッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) は各々パストランジスタ ( P T 3 1 ~ P T 3 4 ) に連結され、パストランジスタ ( P T 3 1 ~ P T 3 4 ) の各々のゲートにはスイッチング制御信号 ( S C S 1 1 1 ~ S C S 1 1 4 ) が印加される。第 1 選択信号 ( S S 1 ) に応答して第 1 区間 ( I N T 1 1 ) の第 1 時点 ( t 2 2 ) までスイッチコントローラ 6 2 1 はスイッチング制御信号 ( S C S 1 1 1 ~ S C S 1 1 4 ) を活性化し、第 1 時点 ( t 2 2 ) でスイッチング制御信号 ( S C S 1 1 1 ~ S C S 1 1 4 ) を非活性化してバッドサブブロック ( S B 1 ) のワードライン ( W L 1 ~ W L 4 ) を

40

50

1 ~ WL 4 ) をフロー ティングさせることができ。10

#### 【 0 1 1 8 】

図 2 4 はバッドサブブロックがプログラムされていない場合、第 1 メモリブロックに対する消去動作時の消去バイアス条件を示し、図 2 5 は図 2 4 のバイアス条件が適用される場合の基板電圧を示す。20

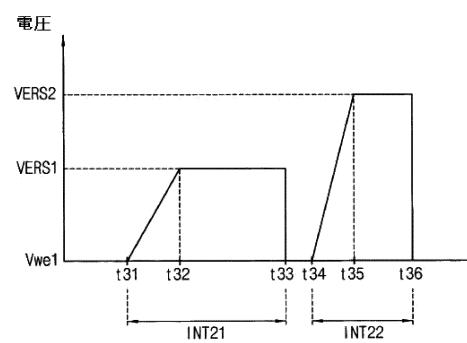

#### 【 0 1 1 9 】

図 2 4 及び図 2 5 を参照すると、制御回路 5 0 0 はセルストリングのビットライン ( BL ) 、ストリング選択ライン ( SSL ) 、接地選択ライン ( GSL ) はフロー ティングさせ、第 1 乃至第 3 サブブロック ( SB 1 ~ SB 3 ) のワードライン ( WL 1 ~ WL 1 2 ) には第 1 ワードライン消去電圧 ( Vwe1 ) を印加する。制御回路 5 0 0 は電圧生成器 7 0 0 を制御して時点 ( t 3 1 ) から基板 1 1 1 に消去電圧 ( VRES ) を印加し始めて、時点 ( t 3 2 ) に基板 1 1 1 電圧のレベルが第 1 レベル ( VERS1 ) に到達すれば、時点 ( t 3 3 ) まで第 1 レベル ( VERS1 ) に維持し、バッドサブブロック ( SB 1 ) を優先的に消去する。制御回路 5 0 0 は、時点 ( t 3 3 ) から時点 ( t 3 4 ) まで消去電圧 ( VRES ) の印加を遮断し、時点 ( t 3 4 ) から基板 1 1 1 に消去電圧 ( VRES ) を再び印加し始め、時点 ( t 3 5 ) で基板 1 1 1 電圧のレベルが第 2 レベル ( VERS2 ) に到達すると、時点 ( t 3 6 ) まで第 2 レベル ( VERS2 ) に維持し、ノーマルサブブロック ( SB 2 、 SB 3 ) を消去する。時点 ( t 3 1 ) から時点 ( t 3 3 ) までが第 1 区間 ( INT21 ) に該当し、時点 ( t 3 4 ) から時点 ( t 3 6 ) までは第 2 区間 ( INT22 ) に該当し得る。バッドサブブロック ( SB 1 ) を優先的に消去することによって、バッドサブブロック ( SB 1 ) に対する消去電圧 ( VERS ) のストレスを減少させることができる。20

#### 【 0 1 2 0 】

図 2 6 A は、バッドサブブロックがプログラムされていない場合、第 1 メモリブロックに対する読出動作時の読出バイアス条件を示す。

#### 【 0 1 2 1 】

図 2 6 B は、バッドサブブロックがプログラムされた場合、第 1 メモリブロックに対する読出動作時の読出バイアス条件を示す。

#### 【 0 1 2 2 】

図 2 6 A 及び図 2 6 B では、ノーマルサブブロックである第 2 サブブロック ( SB 2 ) のワードライン ( WL 6 ) に連結されるメモリセルに対する読出動作を仮定する。30

#### 【 0 1 2 3 】

図 2 6 A を参照すると、制御回路 5 0 0 はセルストリングのストリング選択ライン ( SSL ) 、接地選択ライン ( GSL ) 、ワードライン ( WL 5 、 WL 7 ~ WL 1 2 ) には第 1 読出バス電圧 ( VRPASS11 ) を印加し、ワードライン ( WL 6 ) には読出電圧 ( VRD ) を印加し、バッドサブブロック ( SB 1 ) のワードライン ( WL 1 ~ WL 4 ) には第 2 読出バス電圧 ( VRPASS12 ) を印加することができる。ここで、第 1 読出バス電圧 ( VRPASS11 ) のレベルは第 2 読出バス電圧 ( VRPASS12 ) のレベルより大きいことがある。バッドサブブロック ( SB 1 ) のメモリセルは消去状態であるので、第 2 読出バス電圧 ( VRPASS12 ) に印加により全てターン - オンできる。40

#### 【 0 1 2 4 】

図 2 6 B を参照すると、制御回路 5 0 0 はセルストリングのストリング選択ライン ( SSL ) 、接地選択ライン ( GSL ) 、ワードライン ( WL 5 、 WL 7 ~ WL 1 2 ) には第 1 読出バス電圧 ( VRPASS21 ) を印加し、ワードライン ( WL 6 ) には読出電圧 ( VRD ) を印加し、バッドサブブロック ( SB 1 ) のワードライン ( WL 1 ~ WL 4 ) には第 2 読出バス電圧 ( VRPASS22 ) を印加することができる。ここで、第 1 読出バス電圧 ( VRPASS21 ) のレベルは第 2 読出バス電圧 ( VRPASS22 ) のレベルより大きいか等しいことがある。また、第 2 読出バス電圧 ( VRPASS22 ) のレベルは第 2 読出バス電圧 ( VRPASS12 ) より大きいことがある。バッドサブブロック ( SB 1 ) のメモリセルがプログラムされているので、第 2 読出バス電圧 ( VRPASS1

10

20

30

40

50

2) はプログラムされたバッドサブブロック (SB1) のメモリセルを全てターン - オンさせることができるべき有しなければならない。

#### 【0125】

本発明の実施形態によれば、サブブロックのエラー発生頻度またはサブブロックの位置に従う耐久性特性に基づいて1つのメモリブロックのサブブロックを少なくとも1つのノーマルサブブロックと少なくとも1つのバッドサブブロックに区分し、ノーマルサブブロックとバッドサブブロックに互いに異なるプログラム / 消去サイクルを適用し、第1メモリブロックに対するメモリ動作時にバッドサブブロックのプログラム可否に従って異なるバイアス条件を第1メモリブロックに適用することにより、不揮発性メモリ装置の性能を高めることができ、寿命が短縮されることを防止することができる。

10

#### 【0126】

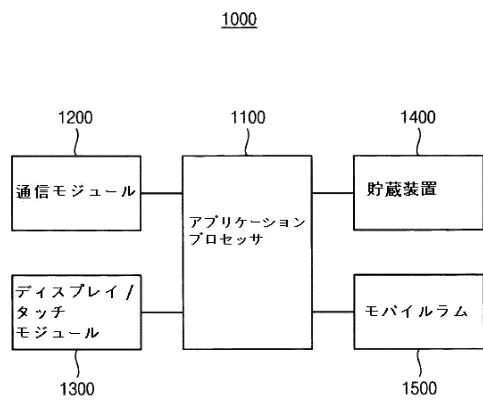

図27は、本発明の実施形態に係るモバイル装置を示すブロック図である。

#### 【0127】

図27を参照すると、モバイル装置1000は、アプリケーションプロセッサ1100、通信モジュール1200、ディスプレイ / タッチモジュール1300、貯蔵装置1400、及びモバイルラム1500を含む。

20

#### 【0128】

アプリケーションプロセッサ1100は、モバイル装置1000の全般的な動作を制御する。通信モジュール1200は外部との有線 / 無線通信を制御するように具現できる。ディスプレイ / タッチモジュール1300は、アプリケーションプロセッサ1100で処理されたデータをディスプレイするか、またはタッチパネルからデータの入力を受けるように具現できる。貯蔵装置1400は、ユーザのデータを貯蔵するように具現できる。

20

#### 【0129】

貯蔵装置1400は、eMMC、SSD、UFS装置でありうる。貯蔵装置1400は、図2の貯蔵装置30で具現できる。したがって、貯蔵装置1400はメモリコントローラと少なくとも1つの不揮発性メモリ装置を含むことができ、少なくとも1つの不揮発性メモリ装置は、図4の不揮発性メモリ装置50で具現できる。モバイルラム1500は、モバイル装置1000の処理動作時、必要なデータを臨時に貯蔵するように具現できる。

#### 【0130】

本発明の実施形態に従う不揮発性メモリ装置または貯蔵装置は、多様な形態のパッケージを用いて実装できる。

30

#### 【産業上の利用可能性】

#### 【0131】

本発明は、不揮発性メモリ装置を備える任意の電子装置に有用に利用できる。例えば、本発明は不揮発性メモリ装置を備える携帯電話 (Mobile Phone)、スマートフォン (Smart Phone)、個人情報端末機 (Personal Digital Assistant; PDA)、携帯型マルチメディアプレーヤー (Portable Multimedia Player; PMP)、デジタルカメラ (Digital Camera)、音楽再生機 (Music Player)、携帯用ゲームコンソール (Portable Game Console)、ナビゲーション (Navigation) システムなどに適用できる。

40

#### 【0132】

前述したように、本発明の好ましい実施形態を参照して説明したが、該当技術分野で通常の知識を有する者であれば、以下の特許請求範囲に記載された本発明の思想及び領域から逸脱しない範囲内で本発明を多様に修正及び変更させできることを理解することができる。

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

10

20

【図 7】

【図 8】

30

40

50

【図 9 A】

【図 9 B】

10

【図 10】

【図 11】

20

30

40

50

【図 1 2】

【図 1 3】

10

20

【図 1 4】

【図 1 5】

30

40

50

【図16】

【図17】

10

【図18】

【図19A】

20

30

40

50

【図 19 B】

【図 20】

10

【図 21 A】

【図 21 B】

20

30

40

50

【図 2 2 A】

| ストリング       | 消去 BIAS |

|-------------|---------|

|             | MB1 消去  |

| SB3         | FLOAT   |

| SSL — SST   | FLOAT   |

| WL12 — MC12 | Vwe1    |

| WL11 — MC11 | Vwe1    |

| WL10 — MC10 | Vwe1    |

| WL9 — MC9   | Vwe1    |

| WL8 — MC8   | Vwe1    |

| WL7 — MC7   | Vwe1    |

| WL6 — MC6   | Vwe1    |

| WL5 — MC5   | Vwe1    |

| WL4 — MC4   | Vwe2    |

| WL3 — MC3   | Vwe2    |

| WL2 — MC2   | Vwe2    |

| WL1 — MC1   | Vwe2    |

| GSL — GST   | FLOAT   |

| CSL/SUB     | VERS    |

Vwe1 &lt; Vwe2 &lt; VERS

【図 2 2 B】

| ストリング       | 消去 BIAS            |

|-------------|--------------------|

|             | MB1 消去             |

| SB3         | FLOAT              |

| SSL — SST   | FLOAT              |

| WL12 — MC12 | Vwe1               |

| WL11 — MC11 | Vwe1               |

| WL10 — MC10 | Vwe1               |

| WL9 — MC9   | Vwe1               |

| WL8 — MC8   | Vwe1               |

| WL7 — MC7   | Vwe1               |

| WL6 — MC6   | Vwe1               |

| WL5 — MC5   | Vwe1               |

| WL4 — MC4   | Vwe1 → FLOAT AT T1 |

| WL3 — MC3   | Vwe1 → FLOAT AT T1 |

| WL2 — MC2   | Vwe1 → FLOAT AT T1 |

| WL1 — MC1   | Vwe1 → FLOAT AT T1 |

| GSL — GST   | FLOAT              |

| CSL/SUB     | VERS               |

Vwe1 &lt; VERS

10

20

30

【図 2 3 A】

【図 2 3 B】

40

50

【図 2 4】

| ストリング       | 消去 BIAS             |

|-------------|---------------------|

|             | MB1 消去              |

| BL          | FLOAT               |

| SSL - SST   | FLOAT               |

| WL12 - MC12 | Vwe1                |

| WL11 - MC11 | Vwe1                |

| WL10 - MC10 | Vwe1                |

| WL9 - MC9   | Vwe1                |

| WL8 - MC8   | Vwe1                |

| WL7 - MC7   | Vwe1                |

| WL6 - MC6   | Vwe1                |

| WL5 - MC5   | Vwe1                |

| WL4 - MC4   | Vwe1                |

| WL3 - MC3   | Vwe1                |

| WL2 - MC2   | Vwe1                |

| WL1 - MC1   | Vwe1                |

| GSL - GST   | FLOAT               |

| CSL/SUB     | VERS1 → VERS2 AT T2 |

Vwe1 &lt; VERS1 &lt; VERS2

【図 2 5】

10

20

【図 2 6 A】

| ストリング       | 読取 BIAS  |

|-------------|----------|

|             | WL6 読取   |

| BL          | -        |

| SSL - SST   | VRPASS11 |

| WL12 - MC12 | VRPASS11 |

| WL11 - MC11 | VRPASS11 |

| WL10 - MC10 | VRPASS11 |

| WL9 - MC9   | VRPASS11 |

| WL8 - MC8   | VRPASS11 |

| WL7 - MC7   | VRPASS11 |

| WL6 - MC6   | VRD      |

| WL5 - MC5   | VRPASS11 |

| WL4 - MC4   | VRPASS12 |

| WL3 - MC3   | VRPASS12 |

| WL2 - MC2   | VRPASS12 |

| WL1 - MC1   | VRPASS12 |

| GSL - GST   | VRPASS11 |

| CSL/SUB     | GND      |

VRPASS12 &lt; VRPASS11

【図 2 6 B】

| ストリング       | 読取 BIAS  |

|-------------|----------|

|             | WL6 読取   |

| BL          | -        |

| SSL - SST   | VRPASS21 |

| WL12 - MC12 | VRPASS21 |

| WL11 - MC11 | VRPASS21 |

| WL10 - MC10 | VRPASS21 |

| WL9 - MC9   | VRPASS21 |

| WL8 - MC8   | VRPASS21 |

| WL7 - MC7   | VRPASS21 |

| WL6 - MC6   | VRD      |

| WL5 - MC5   | VRPASS21 |

| WL4 - MC4   | VRPASS22 |

| WL3 - MC3   | VRPASS22 |

| WL2 - MC2   | VRPASS22 |

| WL1 - MC1   | VRPASS22 |

| GSL - GST   | VRPASS21 |

| CSL/SUB     | GND      |

VRPASS22 &lt; VRPASS21

30

40

50

【図 2 7】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|         |                 |     |         |       |       |

|---------|-----------------|-----|---------|-------|-------|

| G 1 1 C | 16/10 (2006.01) | F I | G 1 1 C | 16/26 | 1 0 0 |

| G 1 1 C | 29/52 (2006.01) |     | G 1 1 C | 16/10 | 1 5 0 |

|         |                 |     | G 1 1 C | 29/52 |       |

弁理士 大貫 進介

## (72)発明者 金 承範

大韓民国京畿道華城市東灘面東部大路 シボム - ギル 1 2 2 1 4 6 3 - 7 0 4

## 審査官 小林 紀和

(56)参考文献

|                       |

|-----------------------|

| 特開2015-176624 (JP, A) |

| 特開2009-015978 (JP, A) |

| 特開2009-266349 (JP, A) |

| 特開2005-025891 (JP, A) |

| 特開2010-160816 (JP, A) |

## (58)調査した分野 (Int.Cl., DB名)

|         |           |

|---------|-----------|

| G 1 1 C | 1 6 / 3 4 |

| G 1 1 C | 1 6 / 0 4 |

| G 1 1 C | 1 6 / 1 4 |

| G 1 1 C | 1 1 / 5 6 |

| G 1 1 C | 1 6 / 2 6 |

| G 1 1 C | 1 6 / 1 0 |

| G 1 1 C | 2 9 / 5 2 |