(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6624101号

(P6624101)

(45) 発行日 令和1年12月25日(2019.12.25)

(24) 登録日 令和1年12月6日(2019.12.6)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 29/78 29/78

652N

H01L 29/739 (2006.01)

H01L 29/78

653A

H01L 29/06 (2006.01)

H01L 29/78

655F

H01L 29/78

652P

H01L 29/06

301G

請求項の数 2 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2017-18672(P2017-18672)

(22) 出願日

平成29年2月3日(2017.2.3)

(65) 公開番号

特開2018-125490(P2018-125490A)

(43) 公開日

平成30年8月9日(2018.8.9)

審査請求日

平成31年3月29日(2019.3.29)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 110001128

特許業務法人ゆうあい特許事務所

(72) 発明者 宮田 征典

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 高橋 茂樹

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

(72) 発明者 住友 正清

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

素子部(1)と、前記素子部を取り囲む外周部(2)とを有する半導体装置において、一面(10a)および前記一面と反対側の他面(10b)を有し、第1導電型のドリフト層(11)を構成する半導体基板(10)と、

前記素子部における前記ドリフト層上であって、前記半導体基板の一面側に形成された第2導電型のベース層(12)と、

前記ベース層を貫通して前記ドリフト層に達し、前記半導体基板の面方向に沿って延設された複数のトレンチ(13)と、

前記トレンチの壁面に形成されたゲート絶縁膜(14)と、

前記ゲート絶縁膜上に形成されたゲート電極(15)と、

前記ベース層の表層部に形成され、前記トレンチと接する第1導電型のエミッタ領域(16)と、

前記外周部における前記ドリフト層の表層部であって、前記半導体基板の一面側に形成され、前記ベース層よりも深さが深くされた第2導電型のディープ層(23)と、

少なくとも前記素子部における前記半導体基板の他面側に形成された第2導電型のコレクタ層(21)と、

前記エミッタ領域および前記ベース層と電気的に接続される第1電極(19)と、

前記コレクタ層と電気的に接続される第2電極(22)と、を備え、

前記ゲート電極に所定のゲート電圧が印加されることにより、前記第1電極から前記工

10

前記ゲート電極に所定のゲート電圧が印加されることにより、前記第1電極から前記工

20

ミッタ領域を介して前記ドリフト層に第1キャリアが注入されると共に前記第2電極から前記コレクタ層を介して前記ドリフト層に第2キャリアが注入されることで前記第1電極と前記第2電極との間に電流を流し、

前記半導体基板の一面において、前記ディープ層における最も前記素子部側の位置を境界位置（K）とし、前記境界位置と、前記第1電極から前記第1キャリアが注入され得る前記エミッタ領域のうちの最も前記外周部側の位置との間の距離を第1距離（L1）とし、前記境界位置と、前記コレクタ層のうちの前記半導体基板の面方向における端部の位置との間の距離を第2距離（L2）とすると、

前記第1距離および前記第2距離は、前記ディープ層によって低下した前記外周部の耐圧に基づいて当該外周部におけるキャリア密度が低下するように調整されていると共に、

隣接する前記トレンチの間隔（L4）に基づいて調整されており、

10

前記半導体基板における厚さを第3距離とし、前記第2距離において、前記コレクタ層の端部が前記素子部内に位置する場合を正の距離とすると共に前記コレクタ層の端部が前記外周部内に位置する場合を負の距離とし、前記第1距離をL1、前記第2距離をL2、前記第3距離をL3、および隣接する前記トレンチの間隔をL4とすると、

前記第1距離、前記第2距離、前記第3距離、および隣接する前記トレンチの間隔は、

$L_1 = L_3 \times (-0.30 \times L_4 + 1.53) - L_2$  を満たしている半導体装置。

#### 【請求項2】

前記第1距離、前記第2距離、前記第3距離、および隣接する前記トレンチの間隔は、

$L_1 = L_3 \times (-0.30 \times L_4 + 1.53) - L_2$  である請求項1に記載の半導体装置。

20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、絶縁ゲートバイポーラトランジスタ（以下では、単にIGBTという）素子が形成された素子部と、素子部を取り囲む外周部とを有する半導体装置に関するものである。

##### 【背景技術】

##### 【0002】

従来より、IGBT素子が形成された素子部と、この素子部を取り囲む外周部とを有する半導体装置が提案されている（例えば、特許文献1参照）。具体的には、この半導体装置は、一面および一面と反対側の他面を有し、ドリフト層を構成する半導体基板を備えている。そして、素子部では、ドリフト層上にP型のベース層が形成され、ベース層の表層部にN<sup>+</sup>型のエミッタ領域が形成されている。また、ゲート絶縁膜を介してベース層と接するように、ゲート電極が形成されている。そして、ドリフト層のうちのベース層と反対側には、コレクタ層が形成されている。なお、このコレクタ層は、素子部から外周部に渡って形成されている。また、半導体基板の一面側には、ベース層およびエミッタ領域と電気的に接続されるように上部電極が形成され、半導体基板の他面側には、コレクタ層と電気的に接続されるように下部電極が形成されている。

30

##### 【0003】

外周部では、半導体基板の一面側に複数のP<sup>+</sup>型のディープ層が多重リング構造を構成するように形成されている。なお、複数のディープ層は、素子部の電界集中が抑制されるように、ベース層よりも深くまで形成されている。

##### 【0004】

このような半導体装置では、ゲート電極に所定のゲート電圧が印加されると、ベース層のうちのゲート電極と隣接する部分に反転層（すなわち、チャネル領域）が形成される。これにより、エミッタ領域から反転層を介して電子がドリフト層に供給されると共に、コレクタ層からホールがドリフト層に供給され、伝導度変調によってドリフト層の抵抗値が低下して電流が流れる。

#### 【先行技術文献】

**【特許文献】****【0005】**

【特許文献1】特開2001-217420号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

しかしながら、上記半導体装置では、外周部にベース層よりも深いディープ層が形成されているため、外周部では、ドリフト層の実質的な厚さが素子部よりも薄くなつて耐圧が低下してしまう。また、上記半導体装置では、コレクタ層が外周部にも形成されており、外周部に形成されたコレクタ層からもホールがドリフト層に供給される。このため、上記半導体装置では、電流が流れている状態から当該電流を遮断する際、外周部でブレークダウンが発生し易くなる。そして、外周部では素子部よりも電流を掃き出し難いため、ブレークダウンが発生すると半導体装置が破壊されてしまう可能性が高くなる。10

**【0007】**

本発明は上記点に鑑み、外周部にベース層よりも深くまで形成されたディープ層を有する半導体装置において、外周部でブレークダウンが発生することを抑制できる半導体装置を提供することを目的とする。

**【課題を解決するための手段】****【0008】**

上記目的を達成するための請求項1では、素子部(1)と、素子部を取り囲む外周部(2)とを有する半導体装置において、一面(10a)および一面と反対側の他面(10b)を有し、第1導電型のドリフト層(11)を構成する半導体基板(10)と、素子部におけるドリフト層上であつて、半導体基板の一面側に形成された第2導電型のベース層(12)と、ベース層を貫通してドリフト層に達し、半導体基板の面方向に沿つて延設された複数のトレンチ(13)と、トレンチの壁面に形成されたゲート絶縁膜(14)と、ゲート絶縁膜上に形成されたゲート電極(15)と、ベース層の表層部に形成され、トレンチと接する第1導電型のエミッタ領域(16)と、外周部におけるドリフト層の表層部であつて、半導体基板の一面側に形成され、ベース層よりも深さが深くされた第2導電型のディープ層(23)と、少なくとも素子部における半導体基板の他面側に形成された第2導電型のコレクタ層(21)と、エミッタ領域およびベース層と電気的に接続される第1電極(19)と、コレクタ層と電気的に接続される第2電極(22)と、を備え、ゲート電極に所定のゲート電圧が印加されることにより、第1電極からエミッタ領域を介してドリフト層に第1キャリアが注入されると共に第2電極からコレクタ層を介してドリフト層に第2キャリアが注入されることで第1電極と第2電極との間に電流を流し、半導体基板の一面において、ディープ層における最も素子部側の位置を境界位置(K)とし、境界位置と、第1電極から第1キャリアが注入され得るエミッタ領域のうちの最も外周部側の位置との間の距離を第1距離(L1)とし、境界位置と、コレクタ層のうちの半導体基板の面方向における端部の位置との間の距離を第2距離(L2)とすると、第1距離および第2距離は、ディープ層によって低下した外周部の耐圧に基づいて当該外周部におけるキャリア密度が低下するように調整されていると共に、隣接するトレンチの間隔(L4)に基づいて調整されており、半導体基板における厚さを第3距離とし、第2距離において、コレクタ層の端部が素子部内に位置する場合を正の距離とするとコレクタ層の端部が外周部内に位置する場合を負の距離とし、第1距離をL1、第2距離をL2、第3距離をL3、および隣接するトレンチの間隔をL4とすると、第1距離、第2距離、第3距離、および隣接するトレンチの間隔は、 $L_1 = L_3 \times (-0.30 \times L_4 + 1.53) - L_2$ を満たしている。3040

**【0009】**

これによれば、電流が流れている状態から当該電流を遮断する際、外周部でブレークダウンが発生することを抑制でき、半導体装置が破壊されることを抑制できる。

**【0010】**

なお、上記および特許請求の範囲における括弧内の符号は、特許請求の範囲に記載された用語と後述の実施形態に記載される当該用語を例示する具体物等との対応関係を示すものである。

**【図面の簡単な説明】**

**【0011】**

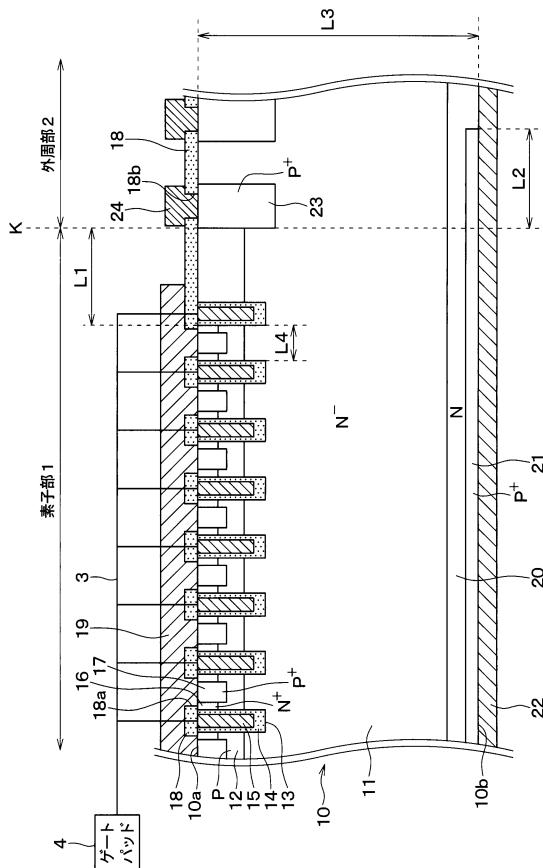

【図1】第1実施形態における半導体装置の断面図である。

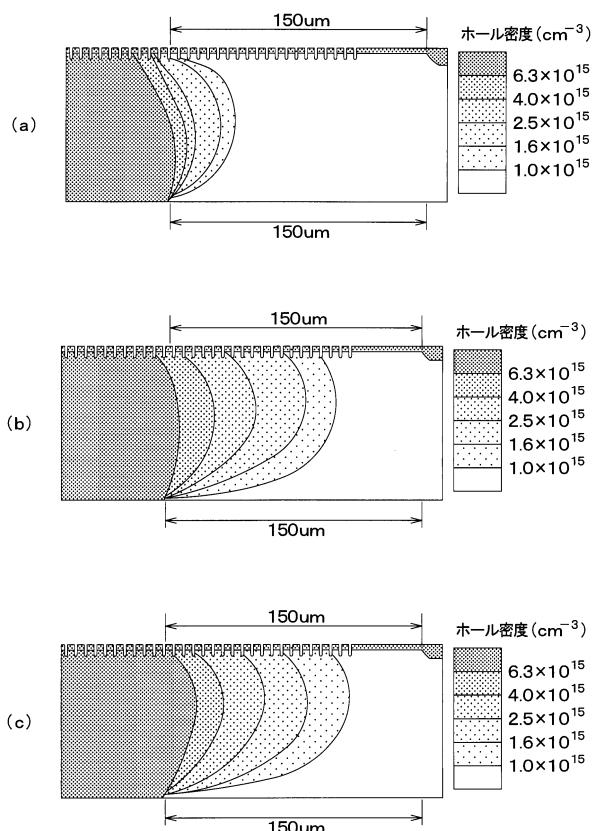

【図2】ホール密度を示すシミュレーション結果であり、(a)は隣接するトレンチの間隔が $4 \mu m$ とされたシミュレーション結果を示す図、(b)は隣接するトレンチの間隔が $2 \mu m$ とされたシミュレーション結果を示す図、(c)は隣接するトレンチの間隔が $1.2 \mu m$ とされたシミュレーション結果を示す図である。

10

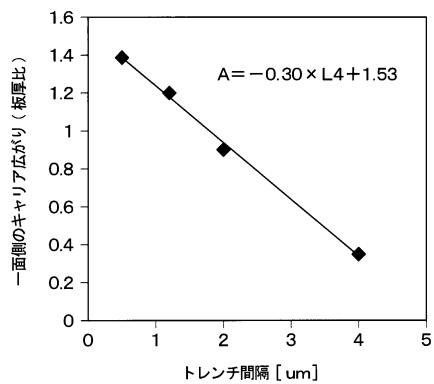

【図3】隣接するトレンチの間隔と、半導体基板の一面側のキャリア広がりとの関係を示す図である。

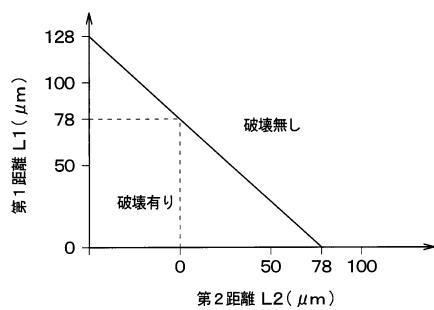

【図4】第1距離および第2距離と、半導体装置の破壊の有無との関係を示す図である。

【図5】第1実施形態における他の半導体装置の断面図である。

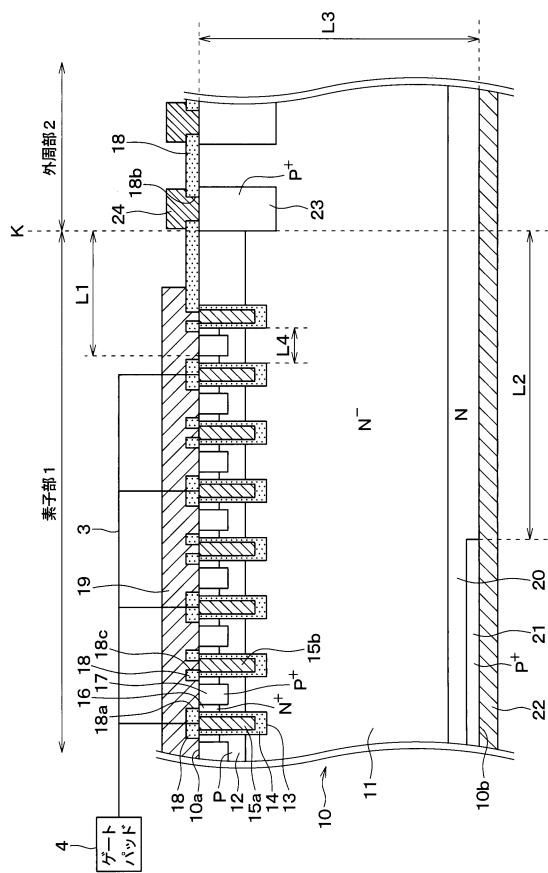

【図6】第2実施形態における半導体装置の断面図である。

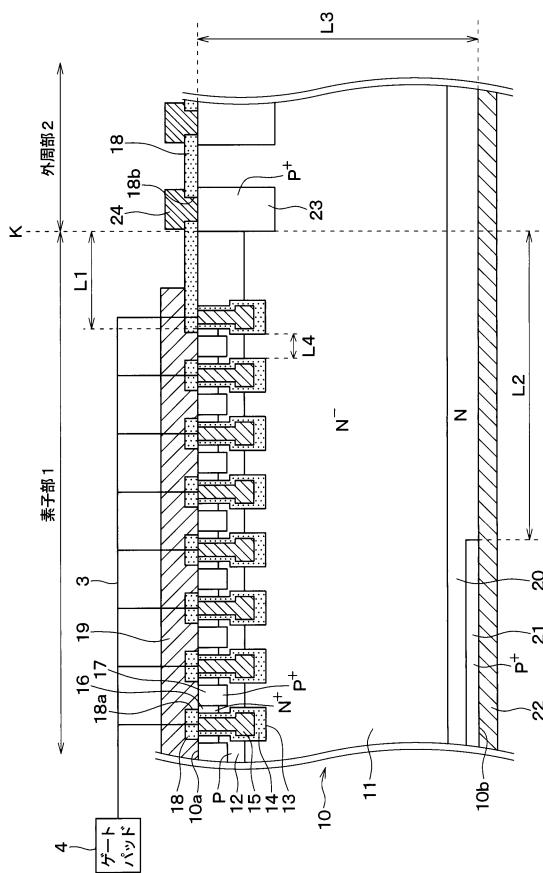

【図7】第3実施形態における半導体装置の断面図である。

**【発明を実施するための形態】**

**【0012】**

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

20

**【0013】**

(第1実施形態)

第1実施形態の半導体装置について図1を参照しつつ説明する。図1に示されるように、本実施形態の半導体装置は、一面10aおよび一面10aと反対側の他面10bを有する半導体基板10を備え、IGBT素子が形成された素子部1と、この素子部1を取り囲む外周部2とが形成されている。まず、素子部1の基本的な構成について説明する。

**【0014】**

素子部1は、N<sup>-</sup>型のドリフト層11を有し、ドリフト層11上(すなわち、半導体基板10の一面10a側)にP型のベース層12が形成されている。また、ベース層12を貫通してドリフト層11に達する複数のトレンチ13が形成されており、ベース層12は複数のトレンチ13によって分断されている。本実施形態では、複数のトレンチ13は、半導体基板10の一面10aの面方向のうちの一方向(すなわち、図1中紙面奥行き方向)に沿ってストライプ状に等間隔に形成されている。

30

**【0015】**

なお、本実施形態では、ドリフト層11の不純物濃度が $1.0 \times 10^{14} cm^{-3}$ とされている。また、複数のトレンチ13は、それぞれ対向する側面の間隔が一定となるように形成されている。つまり、隣接するトレンチ13の間隔は、トレンチ13の開口部側から底部側に沿って一定とされている。

**【0016】**

複数のトレンチ13は、それぞれトレンチ13の壁面を覆うように形成されたゲート絶縁膜14と、当該ゲート絶縁膜14の上に形成されたゲート電極15により埋め込まれている。これにより、トレンチゲート構造が構成されている。なお、本実施形態では、各ゲート電極15は、適宜ゲート配線3を介してゲートパッド4と電気的に接続され、外部のゲート回路から所定のゲート電圧が印加され得るようになっている。

40

**【0017】**

ベース層12の表層部には、N<sup>+</sup>型のエミッタ領域16およびP<sup>+</sup>型のボディ領域17が形成されている。具体的には、エミッタ領域16は、ドリフト層11よりも高不純物濃度で構成され、ベース層12内において終端し、かつ、トレンチ13の側面に接するように形成されている。一方、ボディ領域17は、ベース層12よりも高不純物濃度で構成され、エミッタ領域16と同様に、ベース層12内において終端するように形成されている

50

。

### 【0018】

より詳しくは、エミッタ領域16は、トレンチ13間の領域において、トレンチ13の長手方向に沿ってトレンチ13の側面に接するように棒状に延設され、トレンチ13の先端よりも内側で終端する構造とされている。また、ボディ領域17は、2つのエミッタ領域16に挟まれてトレンチ13の長手方向（つまりエミッタ領域16）に沿って棒状に延設されている。なお、本実施形態のボディ領域17は、半導体基板10の一面10aを基準としてエミッタ領域16よりも深く形成されている。

### 【0019】

半導体基板10の一面10a上には、BPSG等で構成される層間絶縁膜18が形成されており、層間絶縁膜18には、エミッタ領域16の一部およびボディ領域17を露出させる第1コンタクトホール18aが形成されている。そして、層間絶縁膜18上には、第1コンタクトホール18aを介してエミッタ領域16およびボディ領域17と電気的に接続される上部電極19が形成されている。

10

### 【0020】

ドリフト層11のうちのベース層12側と反対側（すなわち、半導体基板10の他面10b側）には、N型のフィールドストップ層（以下では、単にFS層という）20が形成されている。このFS層20は、必ずしも必要なものではないが、空乏層の広がりを防ぐことで耐圧と定常損失の性能向上を図ると共に、半導体基板10の他面10b側から注入されるホールの注入量を制御するために備えてある。

20

### 【0021】

そして、FS層20を挟んでドリフト層11と反対側には、P型のコレクタ層21が形成され、コレクタ層21上（すなわち、半導体基板10の他面10b上）には、コレクタ層21と電気的に接続される下部電極22が形成されている。

### 【0022】

以上が本実施形態における素子部1の基本的な構成である。続いて、外周部2の基本的な構成について説明する。

### 【0023】

外周部2は、素子部1と同様のドリフト層11を有している。そして、ドリフト層11の表層部には、素子部1の電界集中が抑制されるよう、ベース層12よりも深くされたP<sup>+</sup>型のディープ層23が形成されている。具体的には、素子部1では、トレンチ13の底部に電界集中が発生し易いため、トレンチ13の底部の電界集中が抑制されるようP<sup>+</sup>型のディープ層23が形成されている。本実施形態では、ディープ層23は、複数形成されており、それぞれ素子部1を囲む環状構造とされている。つまり、複数のディープ層23は、多重リング構造を構成するように形成されている。

30

### 【0024】

なお、ディープ層23は、ベース層12より深くなるように形成されているが、深くするほどドリフト層11の実質的な厚さが薄くなつて耐圧が低下するため、ベース層12よりも1~3μm程度深くなるように形成することが好ましい。また、本実施形態では、複数のディープ層23のうちの最も素子部1側に位置するディープ層23は、素子部1に形成されたベース層12と接触するように形成されている。つまり、このディープ層23は、ベース層12と連なつて形成されているともいえる。

40

### 【0025】

また、外周部2では、素子部1と同様に、半導体基板10の一面10a上に層間絶縁膜18が形成されており、層間絶縁膜18には、ディープ層23を露出させる第2コンタクトホール18bが形成されている。そして、層間絶縁膜18上には、第2コンタクトホール18bを介してディープ層23と電気的に接続される外周電極24が形成されている。

### 【0026】

外周部2における半導体基板10の他面10b側は、FS層20が形成されている。そして、外周部2では、FS層20上（すなわち、半導体基板10の他面10b上）に下部

50

電極 2 2 が形成されている。

#### 【 0 0 2 7 】

以上が本実施形態における半導体装置の基本的構成である。なお、本実施形態では、N<sup>+</sup>型、N<sup>-</sup>型が第1導電型に相当しており、P型、P<sup>+</sup>型が第2導電型に相当している。また、上部電極 1 9 が第1電極に相当し、下部電極 2 2 が第2電極に相当している。

#### 【 0 0 2 8 】

次に、上記半導体装置の基本的な作動について説明する。上記半導体装置は、上部電極 1 9 が接地されると共に下部電極 2 2 に正の電圧が印加された状態でゲート電極 1 5 に外部のゲート回路から所定のゲート電圧が印加されると、ベース層 1 2 のうちのトレンチ 1 3 と接する部分に反転層（すなわち、チャネル領域）が形成される。そして、エミッタ領域 1 6 から反転層を介して電子がドリフト層 1 1 に供給されると共に、コレクタ層 2 1 からホールがドリフト層 1 1 に供給される。これにより、伝導度変調によってドリフト層 1 1 の抵抗値が低下し、上部電極 1 9 と下部電極 2 2 との間に電流が流れる。10

#### 【 0 0 2 9 】

そして、上記半導体装置は、上部電極 1 9 に正の電圧が印加されると共に下部電極 2 2 が接地され、例えば、ゲート電極 1 5 に 0 V の電圧が印加されることにより、上部電極 1 9 と下部電極 2 2 との間に流れていた電流が遮断される。なお、以下では、上部電極 1 9 と下部電極 2 2 との間に電流が流れている状態を半導体装置がオン状態であるとし、当該電流が遮断された状態を半導体装置がオフ状態であるとして説明する。また、本実施形態では、電子が第1キャリアに相当し、ホールが第2キャリアに相当している。20

#### 【 0 0 3 0 】

本実施形態では、オン状態からオフ状態にする際、外周部 2 にてブレークダウンの発生が抑制されるように、エミッタ領域 1 6 およびコレクタ層 2 1 の位置関係が調整されている。すなわち、上記のように、外周部 2 にベース層 1 2 より深いディープ層 2 3 を形成すると、外周部 2 におけるドリフト層 1 1 の実質的な厚さが薄くなり、外周部 2 の耐圧が低くなり易い。このため、本実施形態では、耐圧が低下したとしても外周部 2 にてブレークダウンが発生し難いように、エミッタ領域 1 6 とコレクタ層 2 1 の位置関係が調整されている。言い換えると、ディープ層 2 3 を形成することによって外周部 2 の耐圧が低下するため、低下した耐圧に基づいてキャリア密度が低くなるように、エミッタ領域 1 6 とコレクタ層 2 1 との位置関係が調整されている。30

#### 【 0 0 3 1 】

以下に、エミッタ領域 1 6 およびコレクタ層 2 1 の位置関係について、具体的に説明する。なお、以下では、図 1 に示されるように、ディープ層 2 3 のうちの最も素子部 1 側の位置を素子部 1 と外周部 2 との境界位置 K とする。また、複数のエミッタ領域 1 6 のうちの上部電極 1 9 から電子（すなわち、キャリア）が注入され得るエミッタ領域 1 6 において、最も外周部 2 側の位置（以下では、最外エミッタ位置という）と、境界位置 K との間の距離を第1距離 L 1 とする。そして、コレクタ層 2 1 における半導体基板 1 0 の面方向に沿った端部の位置と、境界位置 K との間の距離を第2距離 L 2 とする。なお、第2距離 L 2 は、コレクタ層 2 1 における半導体基板 1 0 の面方向に沿った端部の位置が素子部 1 内に位置する場合を正の距離とし、当該端部の位置が外周部 2 に位置する場合を負の距離とする。さらに、半導体基板 1 0 の板厚を第3距離 L 3 とする。そして、隣接するトレンチ 1 3 の間隔のうちの最も狭い部分の距離をトレンチ間隔 L 4 とする。40

#### 【 0 0 3 2 】

まず、上記のように、本実施形態の半導体装置は、ゲート電極 1 5 に所定のゲート電圧が印加されると、エミッタ領域 1 6 から電子がドリフト層 1 1 に供給されると共に、コレクタ層 2 1 からホールがドリフト層 1 1 に供給されることでオン状態となる。この際、図 2 に示されるように、トレンチ間隔 d 4 によってホール密度の分布が異なることが確認される。そして、トレンチ間隔 d 4 が狭いほど、ホール密度が高い部分の広がりが大きくなることが確認される。すなわち、図 2 では、図 2 ( c ) がホール密度の高い部分が最も広がっている。なお、図 2 は、第1距離 L 1 を 1 5 0 μm とし、第2距離 L 2 を 1 5 0 μm50

とし、第3距離L3を78μmとしたシミュレーション結果である。

#### 【0033】

このため、本発明者らは、板厚に対する一面側のキャリア広がりについて、トレンチ間隔L4に基づいた検討を行い、図3に示す結果を得た。すなわち、図3に示されるように、板厚に対する一面側のキャリア広がりA（以下では、単にキャリア広がりAという）は、トレンチ間隔L4を用いた次式で示される。

#### 【0034】

$$(数1) A = -0.30 \times L4 + 1.53$$

なお、本実施形態におけるキャリア広がりAは、次のように定義される。すなわち、キャリア広がりAは、ドリフト層11における最も半導体基板10の一面10a側の部分において、最外エミッタ位置の直下の部分を基準とし、当該基準からホール密度がドリフト層11の不純物濃度の10倍となる部分がどれだけ離れているかを示すものである。本実施形態では、ドリフト層11の不純物濃度が $1.0 \times 10^{14} \text{ cm}^{-3}$ とされているため、 $1.0 \times 10^{15} \text{ cm}^{-3}$ となる部分がどれだけ離れているかを示している。言い換えると、基準から、ホール密度が $1.0 \times 10^{15} \text{ cm}^{-3}$ 以上となる部分と、ホール密度が $1.0 \times 10^{15} \text{ cm}^{-3}$ 未満となる部分との境界がどれだけ離れているかを示すものである。例えば、キャリア広がりAが1であれば、ドリフト層11における最も半導体基板10の一面10a側の部分において、最外エミッタ位置の直下の部分からホール密度が $1.0 \times 10^{15} \text{ cm}^{-3}$ 未満となる部分は、外周部2側に78μm（すなわち、板厚分）以上離れた部分であることを意味している。また、例えば、キャリア広がりAが0.5であれば、ドリフト層11における最も半導体基板10の一面10a側の部分において、最外エミッタ位置の直下の部分からホール密度が $1.0 \times 10^{15} \text{ cm}^{-3}$ 未満となる部分は、外周部2側に39μm（すなわち、板厚の半分）以上離れた部分であることを意味している。

#### 【0035】

ここで、ホール密度がドリフト層11の不純物濃度の10倍となる部分を境界とするのは、ホール密度がドリフト層11の不純物濃度の10倍を超えると、ホールのプラス電荷によって電界強度が強くなり過ぎ、耐圧低下が顕著となるためである。つまり、本実施形態では、 $1.0 \times 10^{15} \text{ cm}^{-3}$ 以上となる部分が外周部2に達すると、当該部分から半導体装置が破壊され易くなる。また、キャリア広がりAは、板厚に対する比であるため、板厚×Aが基準からホール密度が $1.0 \times 10^{16} \text{ cm}^{-3}$ となる位置となる。

#### 【0036】

なお、ドリフト層11における最も半導体基板10の一面10a側の部分とは、素子部1であればベース層12との境界位置となる。そして、外周部2であれば、ディープ層23との境界位置となる。但し、外周部2の場合は、ディープ層23が形成されていない部分においては、ディープ層23が形成されている部分の境界位置と同じ深さの位置をドリフト層11における最も半導体基板10の一面10a側の部分としている。

#### 【0037】

また、トレンチ間隔d4は、隣接するトレンチ13に沿って形成される反転層同士が繋がらないように、少なくとも100nm程度は離間して形成することが好ましい。さらに、トレンチ間隔d4は、広すぎるとドリフト層11にホールを蓄積する効果が著しく低下するため、8μm以下であることが好ましい。

#### 【0038】

続いて、本発明者らは、オン状態からオフ状態にする際、外周部2にてブレークダウンが発生して半導体装置が破壊されるか否かについて、第1距離L1と第2距離L2との関係を検討し、図4に示す結果を得た。なお、図4は、トレンチ間隔L4が1.8μmであり、第3距離L3が78μmである際のシミュレーション結果である。つまり、図4は、キャリア広がりAが1である場合のシミュレーション結果である。言い換えると、基準とホール密度が $1.0 \times 10^{15} \text{ cm}^{-3}$ となる部分との間の長さが $78 \times 1$ となる場合のシミュレーション結果である。

10

20

30

40

50

## 【0039】

図4に示されるように、トレンチ間隔L4が $1.8\mu m$ の場合、第1距離L1および第2距離L2は、次式を満たせば半導体装置が破壊されないことが確認される。

## 【0040】

$$(数2) L1 = 78 \times 1 - L2$$

そして、図4では、第3距離L3が78であり、キャリア広がりAが1であるため、数式2を変形すると、次式となる。

## 【0041】

$$(数3)$$

$$L1 = L3 \times A - L2$$

10

このため、上記数式3を数式1に基づいて変形すると、次式が得られる。

## 【0042】

$$(数4) L1 = L3 \times (-0.30 \times L4 + 1.53) - L2$$

したがって、本実施形態では、上記数式を満たすように、第1距離L1、第2距離L2、第3距離L3、およびトレンチ間隔L4が設定されている。

## 【0043】

以上説明したように、本実施形態では、 $L1 = L3 \times (-0.30 \times L4 + 1.53) - L2$ を満たすように、第1距離L1、第2距離L2、第3距離L3、およびトレンチ間隔L4が設定されている。このため、オン状態からオフ状態にする際、外周部2でブレーカダウンが発生することを抑制でき、半導体装置が破壊されることを抑制できる。

20

## 【0044】

また、 $L1 = L3 \times (-0.30 \times L4 + 1.53) - L2$ とした場合、半導体装置が破壊されない限界のキャリア密度とすることができます。このため、 $L1 = L3 \times (-0.30 \times L4 + 1.53) - L2$ とした場合には、オン電圧の低減を図りつつ、半導体装置が破壊されることを抑制できる。

## 【0045】

なお、図1では、コレクタ層21における半導体基板10の面方向に沿った端部の位置が素子部1内に位置するものを示している。しかしながら、コレクタ層21における半導体基板10の面方向に沿った端部の位置は、上記数式3を満たすのであれば、図5に示されるように、外周部2に位置していてもよく、この場合は第2距離L2は負の値となる。

30

## 【0046】

## (第2実施形態)

第2実施形態について説明する。本実施形態は、第1実施形態に対して、複数のゲート電極15の一部をゲートパッド4に接続し、複数のゲート電極15の残部を上部電極19と接続したものであり、その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

## 【0047】

本実施形態では、図6に示されるように、複数のゲート電極15のうちの一部のゲート電極15aは、ゲートパッド4と接続されている。そして、複数のゲート電極15のうちの残部のゲート電極15bは、ゲートパッド4に接続されておらず、層間絶縁膜18に形成された第3コンタクトホール18cを介して上部電極19と接続されている。すなわち、上部電極19と接続されたゲート電極15bは、半導体装置がオン状態である際、ベース層12に反転層を形成する機能を発揮しない、いわゆるダミーゲート電極とされている。

40

## 【0048】

本実施形態では、一部のゲート電極15を第1ゲート電極15a、残部のゲート電極15を第2ゲート電極15bとすると、第1ゲート電極15aおよび第2ゲート電極15bは、半導体基板10の面方向に沿って交互に配置されている。そして、第1ゲート電極15aおよび第2ゲート電極15bは、第1ゲート電極15aと第2ゲート電極15bとの配列方向における最も外周部2側に第2ゲート電極15bが位置するように配置されてい

50

る。

#### 【0049】

なお、本実施形態では、エミッタ領域16は、上記第1実施形態と同様に、各トレンチ13に沿って形成されている。つまり、本実施形態では、エミッタ領域16は、第2ゲート電極15bが配置されるトレンチ13の側面にも形成されている。

#### 【0050】

また、第1距離L1は、上記のように、最外エミッタ位置と、境界位置Kとの間の距離である。このため、本実施形態の半導体装置では、第1ゲート電極15aが配置されるトレンチ13に接するエミッタ領域16であって、最も外周部2側の位置と、境界位置Kとの間の距離が第1距離L1となる。

10

#### 【0051】

以上説明したように、第2ゲート電極（すなわち、ダミーゲート電極）15bを有する半導体装置としても、上記数式3を満たすことにより、上記第1実施形態と同様の効果を得ることができる。

#### 【0052】

##### （第3実施形態）

第3実施形態について説明する。本実施形態は、第1実施形態に対して、トレンチ13の形状を変更したものであり、その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

#### 【0053】

20

本実施形態では、図8に示されるように、各トレンチ13は、対向する側面の間隔において、底部側の幅が開口部側の幅より長くされている。言い換えると、隣接するトレンチ13の間隔は、底部側の間隔が開口部側の間隔より短くされている。すなわち、本実施形態では、トレンチ13は、いわゆる壺形状とされている。なお、トレンチ間隔L4は、上記のように、隣接するトレンチ13の間隔のうちの最も狭い部分である。このため、本実施形態では、トレンチ間隔L4は、隣接するトレンチ13の間の部分のうちの底部側の部分となる。

#### 【0054】

このような半導体装置によれば、隣接するトレンチ13の間隔において、トレンチ13の開口部側の長さを長くできるため、エミッタ領域16およびボディ領域17の製造工程の簡略化を図りつつ、上記第1実施形態と同様の効果を得ることができる。

30

#### 【0055】

##### （他の実施形態）

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

#### 【0056】

例えば、上記各実施形態では、第1導電型をN型とし、第2導電型をP型とした例について説明したが、第1導電型をP型とし、第2導電型をN型とすることもできる。

#### 【0057】

また、上記第2実施形態において、第2ゲート電極15bが配置されるトレンチ13の側面に接するようにエミッタ領域16が形成されていなくてもよい。つまり、エミッタ領域16は、第1ゲート電極15aが配置されるトレンチ13の側面のみに形成されていてもよい。また、第2ゲート電極15bは、上部電極19と接続されておらず、ゲートパッド4と異なるゲートパッドと接続されて所定電位（例えば、グランド電位）に維持されるようにしてもよいし、電極と接続されずにフローティング状態とされていてもよい。さらに、第1ゲート電極15aおよび第2ゲート電極15bは、第1ゲート電極15aと第2ゲート電極15bとの配列方向における最も外周部2側に第1ゲート電極15aが位置していてもよい。

40

#### 【0058】

そして、上記第2実施形態を上記第3実施形態に組み合わせ、上記第3実施形態の半導

50

体装置において、第1ゲート電極15aおよび第2ゲート電極15bを有する構成としてもよい。

【符号の説明】

【0059】

- |     |            |    |

|-----|------------|----|

| 1   | 素子部        |    |

| 2   | 外周部        |    |

| 10  | 半導体基板      | 10 |

| 10a | 一面         |    |

| 10b | 他面         |    |

| 11  | ドリフト層      |    |

| 12  | ベース層       |    |

| 13  | トレンチ       |    |

| 14  | ゲート絶縁膜     |    |

| 15  | ゲート電極      |    |

| 16  | エミッタ領域     |    |

| 19  | 上部電極(第1電極) |    |

| 21  | コレクタ層      |    |

| 22  | 下部電極(第2電極) |    |

| 23  | ディープ層      |    |

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/06 | 3 0 1 V |

| H 01 L | 29/78 | 6 5 2 K |

| H 01 L | 29/78 | 6 5 5 C |

(72)発明者 志賀 智英

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

審査官 柴垣 宙央

(56)参考文献 特開2010-177243(JP,A)

特開2010-161335(JP,A)

特開2015-118989(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 7 8

H 01 L 29 / 0 6

H 01 L 29 / 7 3 9