# (19) World Intellectual Property Organization International Bureau

# (43) International Publication Date 5 July 2001 (05.07.2001)

# **PCT**

# (10) International Publication Number WO 01/48620 A1

(51) International Patent Classification<sup>7</sup>: G06F 13/28

(21) International Application Number: PCT/US00/35455

(22) International Filing Date:

28 December 2000 (28.12.2000)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data: 60/173,459 29 December 1999 (29.12.1999) Us

(71) Applicant (for all designated States except US): THE JOHNS HOPKINS UNIVERSITY [US/US]; Applied Physics Laboratory, 11100 Johns Hopkins Road, Laurel, MD 20723-6099 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): BADE, Paul

[US/US]; 3717 Park Overlook Court, Ellicott City, MD 21042 (US). **KAHN**, **Steven** [US/US]; 14130 Flint Rock Road, Rockville, MD 20853 (US). **VERVEN**, **David** [US/US]; 9453 Farewell Road, Columbia, MD 21045 (US).

- (74) Agents: COOCH, Francis et al.; The Johns Hopkins University, Applied Physics Laboratory, 11100 Johns Hopkins Road, Laurel, MD 20723-6099 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CR, CU, CZ, DE, DK, DM, DZ, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian

[Continued on next page]

(54) Title: SYSTEM, METHOD, AND COMPUTER PROGRAM PRODUCT FOR HIGH SPEED BACKPLANE MESSAGING

(57) Abstract: A system and method of enhanced backplane messaging among a plurality of computer boards communicating over a common bus uses a set of pre-allocated buffers on each computer board to receive messages from other computer boards. Each sending computer board is represented on each remote computer board by a descriptor ring with pointers to pre-allocated buffers on that remote computer board. When a sending computer board has a message to deliver to a remote computer board, the sending computer board uses its DMA controller to transfer the message into the pre-allocated buffers on the remote computer board. The sending computer board also sends a mailbox interrupt to the remote computer board. The remote computer board interrupt handler searches its descriptor rings and manipulates a series of pointers to move messages from the descriptor rings to the intended receiving application(s). Pointer manipulation is also used to replenish the descriptor ring(s) with empty buffer(s). In addition, chained DMA transfers are used to eliminate any data transfers by the processor itself across the bus. The chained DMA transfers transfer messages to the pre-allocated buffers, set flags indicating that a message is present in a buffer, send a mailbox interrupt to the remote computer board, and read back the address of the next pre-allocated buffer for that descriptor ring.

VO 01/48620 A1

# WO 01/48620 A1

patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GW, ML, MR, NE, SN, TD, TG).

#### Published:

— With international search report.

Before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments.

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

### TITLE OF THE INVENTION

System, Method, and Computer Program Product For High Speed Backplane Messaging

5

10

15

20

# FIELD OF THE INVENTION

The present invention relates generally to a system and method for exchanging messages among a plurality of computer boards connected via a bus on a common backplane.

# BACKGROUND OF THE INVENTION

Conventional backplane messaging schemes for exchanging messages among processors within a network utilizing a shared memory interconnect (bus) require a processor that wants to send a message (data packet) using the bus to request an empty buffer from the remote computer board processor, then transfer the data packet, and finally to notify the remote computer board processor of the arrival of the data packet. The overhead involved in this form of handshake for buffer allocation/de-allocation can significantly affect network performance.

### SUMMARY OF THE INVENTION

A system and method of enhanced backplane messaging among a plurality of computer boards communicating over a common bus uses a set of pre-allocated buffers on each computer board to receive messages from other computer boards. Each sending computer board is represented on each remote computer board by a descriptor ring with pointers to pre-allocated buffers on that remote computer board. When a sending computer board has a message to 10 deliver to a remote computer board, the sending computer board uses its DMA controller to transfer the message into the pre-allocated buffers on the remote computer The sending computer board also sends a mailbox board. interrupt to the remote computer board. The remote 15 computer board interrupt handler searches its descriptor rings and manipulates a series of pointers to move messages from the descriptor rings to the intended receiving application(s). Pointer manipulation is also 20 used to replenish the descriptor ring(s) with empty buffer(s). As a practical matter, pointer manipulation eliminates repeated copying of a message. Moreover, the use of pre-allocated buffers on each remote computer board achieves a significant performance boost over the 25 more conventional technique of buffer request and assignment.

In addition, chained DMA transfers are used to eliminate any data transfers by a computer board processor (CPU) across the bus. The chained DMA transfers transfer messages to the pre-allocated buffers,

set flags indicating that a message is present in a buffer, send a mailbox interrupt to the remote computer board, and read back the address of the next preallocated buffer for that descriptor ring.

Other aspects and features of the present invention will become apparent to those ordinarily skilled in the art upon review of the following description of specific embodiments of the invention in conjunction with the accompanying figures.

10

5

### BRIEF DESCRIPTION OF THE FIGURES

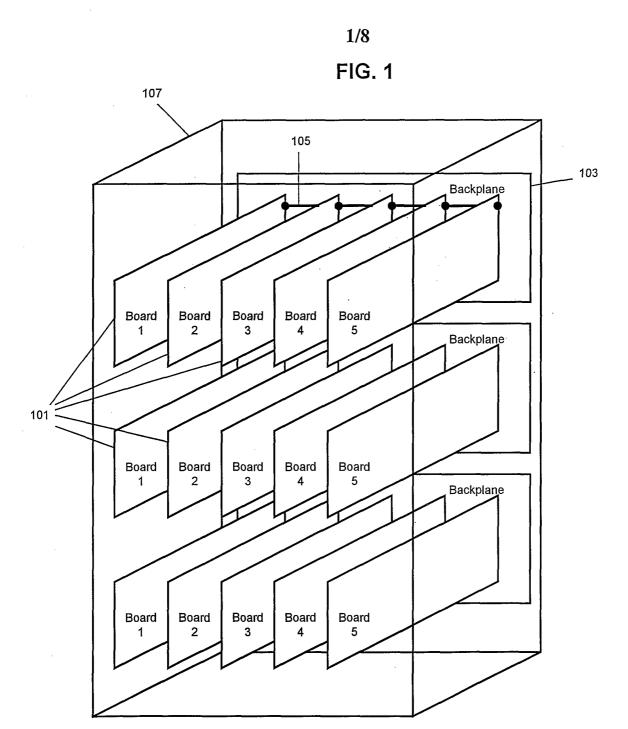

FIGURE 1 is a physical representation of the context and environment of the messaging scheme of the present invention.

and the high level processes or functions running on the computer board with respect to the messaging scheme of the present invention.

FIGURE 3 is a high level flow diagram for the initialization and registration process.

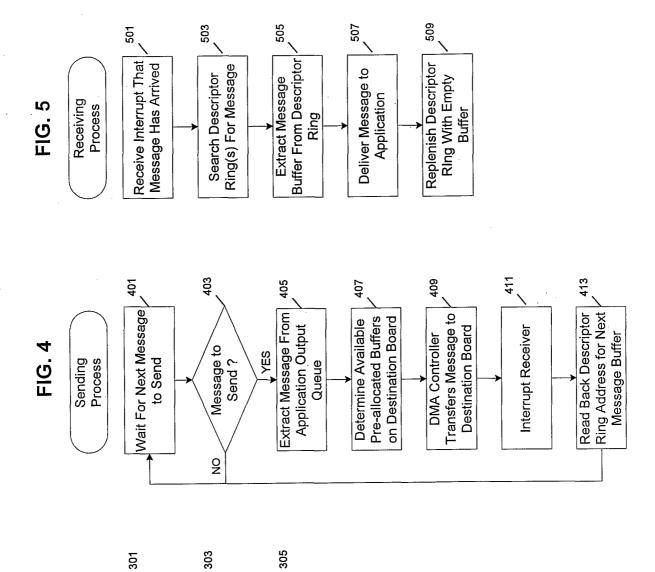

FIGURE 4 is a high level flow diagram for the sending process.

FIGURE 5 is a high level flow diagram for the receiving process.

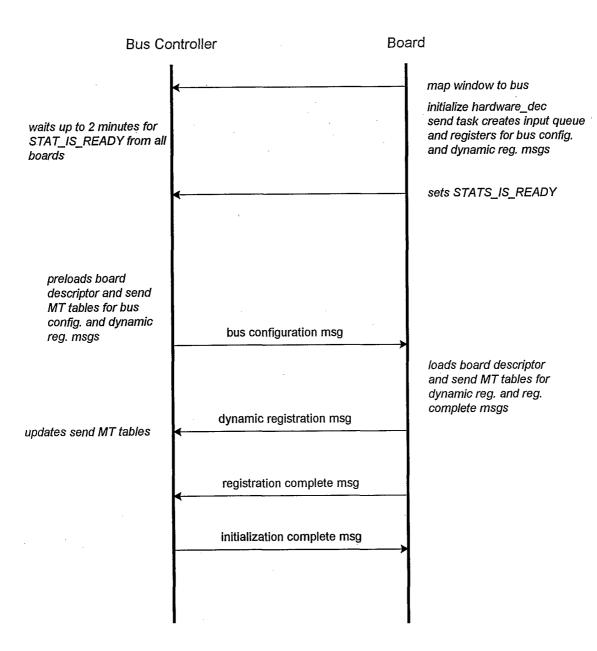

25 **FIGURE 6** is a more detailed message diagram for the initialization and registration process.

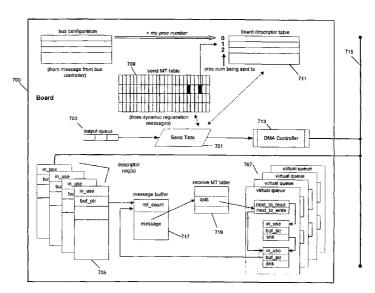

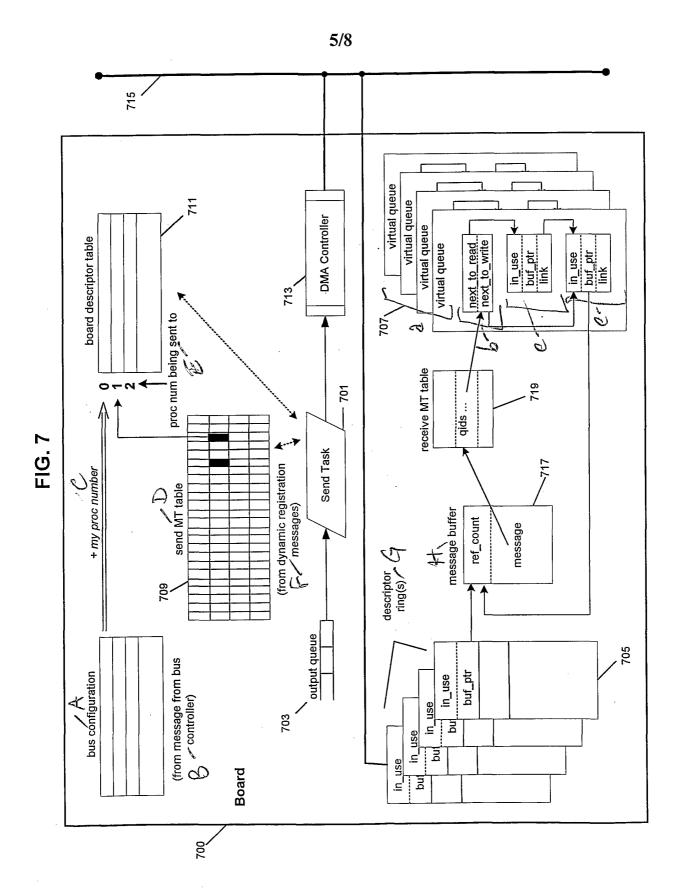

FIGURE 7 illustrates a more detailed schematic of the send and receive processes as they reside on a computer board.

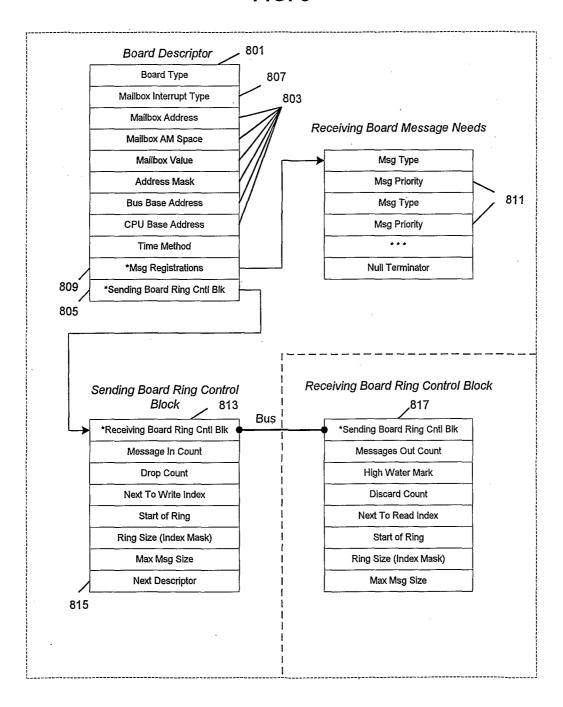

30 **FIGURE 8** illustrates examples of data structures used by the messaging scheme of the present invention.

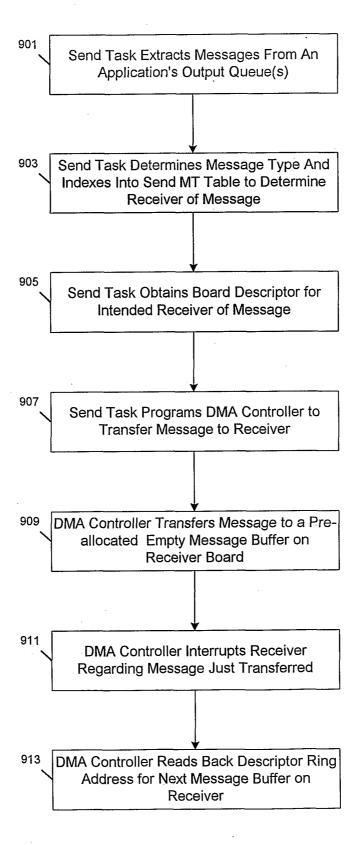

FIGURE 9 is a detailed flow diagram for the sending process.

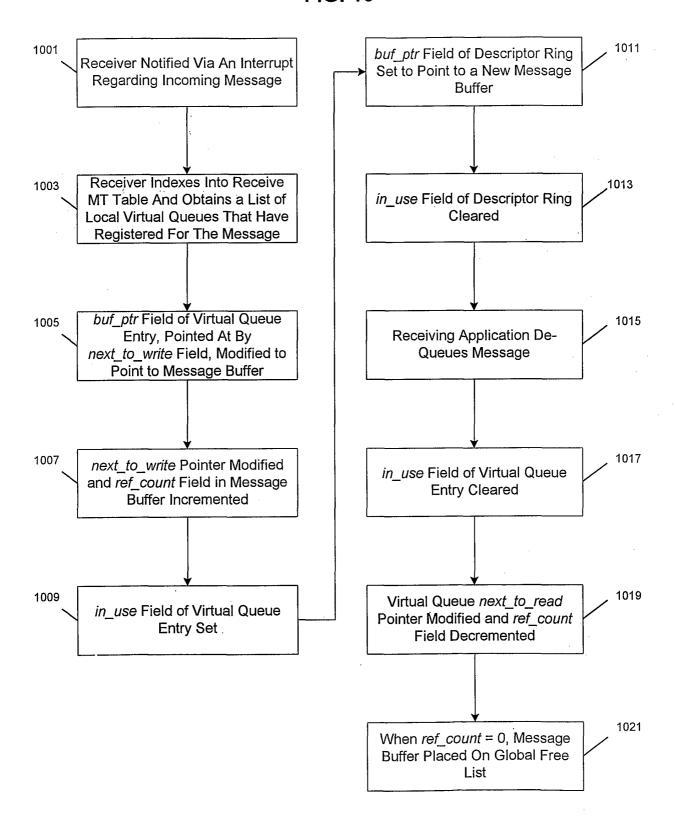

FIGURE 10 is a detailed flow diagram for the receiving process.

5

10

15

20

25

30

### DETAILED DISCLOSURE OF THE INVENTION

FIGURE 1 is a physical representation of the context and environment of the messaging scheme of the present invention. The purpose of the present invention is to provide a system and method for exchanging messages among a plurality of computer boards connected via a backplane bus. The terms backplane and bus may be used interchangeably throughout this description to refer to the means that connect the various computer boards. The term message refers to data or data packets that can be grouped together. Thus, the phrase messaging scheme generally refers to a scheme for sending and receiving data across a common bus or backplane. FIGURE 1 illustrates a cabinet 107 having three racks. A rack is a combination of a set of computer boards 101 connected to a common backplane 103. A bus 105 connects a set of computer boards 101 such that messages can be exchanged among the computer boards 101 connected to such a bus 105.

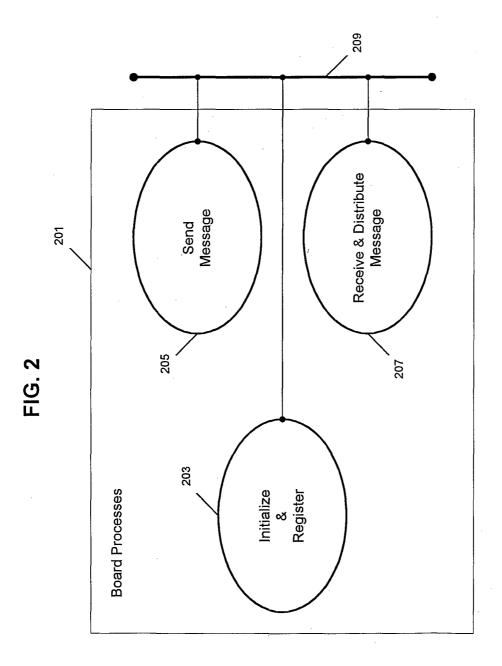

FIGURE 2 illustrates an individual computer board

201 and the high level processes or functions running on

the computer board with respect to the messaging scheme

of the present invention. It is to be understood that

each computer board likely has other processes and

functions running. Only the processes and functions

relevant to the present invention are shown, however.

There are three processes or functions that comprise the

messaging scheme of the present invention. The first is an initialization and registration process 203. The initialization and registration process 203 performs preliminary tasks necessary to prepare the computer board 201 for message exchanging with other computer boards. Another process is the send process 205 that is responsible for sending messages to other computer boards that are connected to the common backplane. The messages are obtained from application output queues residing on the computer board. The other process is a receive process 207 that is responsible for receiving messages from other computer boards that are connected to the common backplane and distributing the messages to intended application(s) on the local computer board. A bus 209 is shown to illustrate that each process has access to the bus in order to be able to send or receive data.

10

15

20

25

FIGURE 3 illustrates a registration process. are two primary tasks with respect to initializing a computer board to be able to exchange messages with other computer boards. One task is to initialize at least one descriptor ring 301 on the computer board. Descriptor rings are used to receive messages from other computer boards. The other task is to pre-allocate a plurality of buffers 303. The buffers will be used to store incoming messages. Pre-allocation of the buffers is a significant part of the messaging scheme of the present invention in order to provide a known destination for a message transfer as opposed to requiring the sender to request a new buffer prior to each message transfer. Once the descriptor rings have been initialized and buffers have been pre-allocated, the computer board completes the

registration process by notifying all other computer boards 305 connected to the backplane that it has initialized its descriptor rings and pre-allocated buffers.

5

10

15

20

25

30

Those of ordinary skill in the art can readily devise and implement alternate registration and initialization processes without departing from the spirit or scope of the present invention. Thus, any initialization and registration processes described herein are illustrative and not intended to limit the core sending and receiving techniques presented in this application.

FIGURE 4 illustrates the sending process generally. A send task is continually in a wait state waiting for the next message it is to send 401. When a message to send is present 403 the send task extracts the message from an output queue of an on-board application 405. send task next determines the availability of preallocated buffers on a remote computer board in which the receiving application resides 407. The buffer availability information is typically gathered by the DMA chain at the end of the last data transfer to the receiving computer board. Next, the send task instructs the DMA controller on the sending computer board to transfer the message to the remote computer board 409, interrupt the receiving computer board with a mailbox interrupt 411, and gather information of the availability of message buffers for the next transfer, i.e. read back the descriptor for the next message buffer 413. The DMA is, in effect, a message passing co-processor that relieves the sending computer board CPU from having to perform any transfers over the bus. If the CPU were to

perform transfers, it could block while waiting for access to a busy bus. Thus, DMA chaining is utilized to enhance the speed and efficiency of the present invention messaging scheme.

5

10

15

30

generally. An interrupt occurs notifying the receive process on the receiving computer board that a message is present 501 in one of the receiving computer board descriptor rings. The receive process searches among the descriptor ring(s) on the receiving computer board for a full message buffer 503. Once the descriptor ring containing the pointer to the message buffer is found, the receive process extracts the message buffer 505 from the descriptor ring and delivers the message 507 to the intended application using well known pointer manipulation techniques. After delivery, the receive process replenishes the descriptor ring 509 with an empty buffer.

initialization and registration process of each computer board that is connected to a common bus on a backplane.

The process is described with respect to executing across a VMEbus. One of ordinary skill in the art can readily apply the concepts and principles of the following

description and apply same to other buses. Thus, the present invention is not to be construed as limited to a VMEbus implementation.

As a computer board powers up it maps an area of its memory to a window on the VMEbus. At some point following power up, a bus controller probes the bus for computer boards that are connected to the bus. The bus controller then constructs its own bus configuration

table as a result of its probing the bus for computer boards.

Meanwhile, each computer board initializes its own hardware description block and its plurality of receive descriptor rings. The computer board then instructs its send task to create a virtual message queue that is registered to receive bus configuration and dynamic registration messages from the bus controller. Each computer board concludes initialization by setting a flag to notify the bus controller that the computer board is fully initialized.

10

15

20

25

The bus controller waits for a period of time for all of the computer boards present on the bus to perform the initialization process. Next, the bus controller pre-loads its computer board descriptor table with the board descriptors corresponding to all of the computer boards. The bus controller also pre-loads the send MT table used for sending the bus configuration and dynamic registration messages to all of the computer boards. At this point, the bus controller issues the bus configuration message to all the computer boards.

When each computer board receives the bus configuration message, it builds its own board descriptor table by reading the configuration information available on each computer board. Information in a board descriptor table is used to access a unique receive descriptor ring on a remote computer board when sending message(s) to a remote computer board.

Whenever the bus controller (or any computer board)

30 receives a dynamic registration message, it updates its

send MT table with the messages registered for by the

computer board that sent the dynamic registration

message. The send task on each computer board is responsible for receiving the dynamic registration message(s) and updating the send MT table. Once the bus controller has collected all of the registration complete messages from each computer board, it sends an initialization complete message to all computer boards to complete the entire system initialization process. Thus, the bus controller has several responsibilities including probing the VMEbus for computer boards, sending bus configuration messages, and sending the initialization complete message.

10

15

20

25

<sup>3</sup> 30

the send and receive hardware, software, and processes as they reside on a computer board. For ease of illustration, FIGURE 7 shows a single computer board 700 which includes the sending and receiving components. Each computer board is identical with respect to the message exchanging scheme of the present invention. Thus, reference to FIGURE 7 with respect to sending a message from one computer board to another computer board is appropriate since the receiving portion of the computer board shown in FIGURE 7 can be thought of as existing on another computer board connected via the bus.

The sending process is managed by a send task 701.

The send task is communicable with an output queue 703 into which an application places messages to be delivered to an application on a remote computer board. The receiving process includes an array of receive descriptor rings 705 (one ring per sender) to buffer incoming messages and any number of virtual input queues 707 from which applications retrieve their messages. From a receiving application's point of view the virtual input

queues 707 support the publish/subscribe messaging model. Thus, an application can register for any number of message labels without having to know any information about the sender and an application can block on a queue while awaiting arrival of a message.

5

10

15

20

25

30

Tracking a message as it travels from a source to its destination provides a more detailed understanding of board-to-board message transfers. Each computer board includes a send task 701 which extracts messages from the application's output queue (or queues). The send task doesn't actually copy the message. Rather, it peeks at the message type, and then indexes into a send MT (message type) table 709 to determine the destination of the message. Each row of the send MT table 709 table can be viewed as a bit array, where each bit that is set corresponds to the processor number of each remote computer board that has one or more virtual input queues 707 registered for the message.

A board descriptor table 711 is used to maintain all of the pertinent information needed for message delivery to each remote computer board. The board descriptor table 711 includes an entry for each remote computer board and is indexed by processor number. The board descriptor table 711 is composed of information copied from each remote computer board hardware descriptor. Information in the board descriptor table 711 includes how to interrupt the remote computer board, what the computer board address is (in both the processor's address space and on the VMEbus), and the computer board type.

The send task 701 thus consults the send MT table 709 to determine which computer boards are to receive a message. The send task 701 also obtains a board

descriptor for each remote computer board that is to receive a message. With this information (as well as some additional information), the send task 701 can program an onboard DMA controller 713 to transfer the message across a bus 715. Note that if multiple virtual input queues 707 on a remote computer board have registered for the same message, only one transfer across the bus is necessary.

5

20

25

30

The DMA transfer is made into an empty memory buffer 717. The message buffer 717 is pointed to by the descriptor ring 705, specifically the buf\_ptr of the next descriptor in the descriptor ring 705 on the receiving computer board. In addition, an in\_use flag is set for the descriptor ring 705. The sending process knows the message buffer on the receiving computer board is available because it had previously determined that the in use field for that descriptor ring 705 was not set.

Once the DMA transfer is completed, the receiver is notified via an interrupt. Within an interrupt handler, the receiver indexes into a receive MT table 719, based on the message type, and obtains a list of local virtual input queues 707 that have registered for the message. The local virtual input queue may also be referred to as an application input queue. For each virtual input queue 707, a buffer pointer of the queue entry pointed at by a next to write pointer is modified to point to the message buffer 717, the next to write pointer is modified, and the reference count field in the message buffer 717 is incremented by one. Finally, the in use field of the virtual queue 707 entry is set, the buffer pointer of the descriptor ring 705 is set to point to a new message

buffer 717 (obtained from a global free list), and the in use field of the descriptor ring 705 entry is cleared.

Later, when an application de-queues a message, the in use field of the virtual queue 707 entry is cleared, the virtual queue 707 next to read pointer is modified, and the reference count field of the message buffer 717 is decremented. Because multiple tasks might be dequeuing the same message buffer 717, updating of the reference count is protected, e.g., by task or interrupt locking. When the reference count goes to zero, the message buffer 717 is placed on the global free list.

10

15

20

25

30

FIGURE 8 illustrates examples of data structures used by the messaging scheme of the present invention. A board descriptor 801 can be thought of as the handle to all of the information with respect to a remote computer board that is used by the sending computer board in order to deliver a message to a remote computer board. The board descriptor 801 includes information on the addressing 803 of the remote computer board, a pointer 805 to the sending computer board ring control block, information on the mailbox interrupt 807 to be used upon delivery of a message, and a pointer 809 to a list of all the messages that have been registered for on this computer board, along with their priorities 811.

The sending computer board ring control block structure **813** contains all the information about the remote descriptor ring that is needed for message transfers. Note that the next descriptor field **815** includes a copy of the next descriptor on the remote computer board, as it was copied at the end of the previous DMA chain transfer operation. For efficiency, the next descriptor (containing a pointer to the next

dynamically allocated buffer) is copied during the DMA chain operation, since the *in\_use* flag is most likely not set, which indicates that the buffer pointer (buf\_ptr) is valid.

5

10

15

20

25

30

The receiving computer board descriptor ring control block 817 on the remote computer board, includes information about the receive descriptor ring(s) uniquely associated with the sending computer board. Also, the sending 813 and receiving 817 ring control block structures include fields to monitor ring overflow conditions (dropped messages) and the high water mark for messages in the ring.

FIGURE 9 illustrates the logic flow of the sending process on a given computer board. The computer board's send task extracts messages from an application's output queue or queues 901. The send task determines the message type and then indexes into the send MT table 903 that it created during the initialization process to determine which computer board is to receive the message. The send task obtains a board descriptor of the computer board that is to receive the message 905. The send task then programs the DMA controller to transfer the message 907 to the receiving computer board across the bus. The DMA transfer is sent to a pre-allocated empty message buffer on the receiving computer board 909. Recall, that message buffers were pre-allocated on all computer boards during the initialization and registration process.

Once the transfer is complete, the sending DMA controller sends a mailbox interrupt **911** to the receiving computer board to initiate the receive process on the receiving computer board. Lastly, the DMA controller reads back the address of the next message buffer

according to the receiving computer board descriptor ring 913.

The DMA controller chains together message transfers across the bus in order to expedite the message sending process when multiple destinations are involved. With respect to the present invention, there are multiple elements in a DMA chain executed by the DMA controller for each destination. One element writes the body and in use bit of message k to a queue on the remote computer board. Another element writes to the remote computer board mailbox interrupt location. Typically, the last element calls for reading the in-use bit of message k+1. At the end of the chain, after the VMEbus has been released, the sending DMA controller interrupts the local CPU. The local CPU then sets up the sending DMA controller for the next transfer while another computer board is free to use the backplane/bus. This scheme calls for one CPU interrupt per out-going message to ensure that the local computer board CPU does not have to poll the DMA controller waiting for a transfer complete status from the DMA controller. The overhead associated with the one CPU interrupt per out-going message may be reduced by having the CPU set up for all pending outgoing messages each time it is interrupted by the DMA controller with a transfer complete status. The multiple out-going messages would simply be added in to the DMA controller chain. This is most practical when multiple messages are targeted at different receiver queues.

10

15

20

25

FIGURE 10 illustrates the logic flow of the

receiving process on a given computer board. Following

the initialization process, each computer board is ready

for communications. As the last part of the DMA chain,

the receiver is notified of the message receipt via a mailbox interrupt 1001. The receiver then indexes, based on message type, into its receive MT table and obtains a list of local virtual queues that have registered to receive the message 1003. The buffer pointer field within the virtual queue that is pointed to by the next to write field is modified to point to the message buffer containing the message at issue 1005. The virtual queue next to write pointer is then modified and the ref count field in the message buffer is incremented 1007 and the in\_use flag of the virtual queue is set 1009. At this point, the buffer pointer field of the descriptor ring is set to point to a new message buffer 1011 and the in\_use flag of the descriptor ring is cleared 1013.

10

15

20

25

The receiving application on the receiving computer board de-queues the just queued message on the virtual queue 1015. After de-queuing, the *in\_use* flag of the virtual queue is cleared 1017 and the virtual queue next to read pointer is modified and the ref count field of the message buffer is decremented 1019. When the ref count value of the message buffer decrements back to zero, a message buffer is placed on the global free list 1021.

There are several advantages realized by the present invention. Foremost is the decoupling of communications between multiple senders accessing a common receiver. Using pre-allocated buffers eliminates many message buffer management issues associated with transferring data among processors on a bus. DMA (Direct Memory Access) hardware is used for all bus transfers ensuring that the processors never block while waiting for bus access. Thus, the CPU is not responsible for performing

transfers. Multiple point to point connections can be simultaneously active between multiple processors, and mutual exclusion capabilities such as Test-And-Set are not needed. Moreover, all message transfers are done with write commands, which are significantly more efficient than reading across a bus.

10

15

20

25

30

It is to be understood that the present invention illustrated herein is readily implementable by those of ordinary skill in the art as a computer program product having a medium with a computer program embodied thereon. The computer program product is capable of being loaded and executed on the appropriate computer processing device(s) in order to carry out the method or process steps described. Appropriate computer program code in combination with hardware implements many of the elements of the present invention. This computer code is often stored on storage media. This media can be a diskette, hard disk, CD-ROM, optical storage media, or tape. media can also be a memory storage device or collection of memory storage devices such as read-only memory (ROM) or random access memory (RAM). Additionally, the computer program code can be transferred to the appropriate hardware over some type of data network.

The present invention has been described, in part, with reference to flowchart or logic flow diagrams. It will be understood that each block of the flowchart diagrams or logic flow diagrams, and combinations of blocks in the flowchart diagrams or logic flow diagrams, can be implemented by computer program instructions.

These computer program instructions may be loaded onto a general purpose computer, special purpose computer, or other programmable data processing apparatus

to produce a machine, such that the instructions which execute on the computer or other programmable data processing apparatus create means for implementing the functions specified in the flowchart block or blocks or logic flow diagrams.

5

10

15

2.0

25

30

These computer program instructions may also be stored in a computer-readable memory that can direct a computer or other programmable data processing apparatus to function in a particular manner, such that the instructions stored in the computer-readable memory produce an article of manufacture including instruction means which implement the function specified in the flowchart blocks or logic flow diagrams. The computer program instructions may also be loaded onto a computer or other programmable data processing apparatus to cause a series of operational steps to be performed on the computer or other programmable apparatus to produce a computer implemented process such that the instructions which execute on the computer or other programmable apparatus provide steps for implementing the functions specified in the flowchart blocks or logic flow diagrams.

Accordingly, block(s) of flowchart diagrams and/or logic flow diagrams support combinations of means for performing the specified functions, combinations of steps for performing the specified functions and program instruction means for performing the specified functions. It will also be understood that each block of flowchart diagrams and/or logic flow diagrams, and combinations of blocks in flowchart diagrams and/or logic flow diagrams can be implemented by special purpose hardware-based computer systems that perform the specified functions or

steps, or combinations of special purpose hardware and computer instructions.

In the following claims, any means-plus-function clauses are intended to cover the structures described herein as performing the recited function and not only structural equivalents but also equivalent structures. Therefore, it is to be understood that the foregoing is illustrative of the present invention and is not to be construed as limited to the specific embodiments

10 disclosed, and that modifications to the disclosed embodiments, as well as other embodiments, are intended to be included within the scope of the appended claims. The invention is defined by the following claims, with equivalents of the claims to be included therein.

#### CLAIMS:

1

- 2 1. A method of backplane messaging among a plurality of

- 3 computer boards connected via a bus, each computer board

- 4 including a processor and a DMA controller and each

- 5 computer board capable of sending and receiving messages,

- 6 said method comprising:

- 7 initializing said plurality of computer boards, said

- 8 initialization for the purpose of preparing each computer

- 9 board to communicate with the other computer boards;

- sending messages, utilizing a the DMA controller

- 11 included on the computer board and not the processor of the

- 12 computer board, from any one of the plurality of computer

- 13 boards to any other of the plurality of computer boards;

- 14 and

- 15 receiving messages on any one of the plurality of

- 16 computer boards sent from any other of the plurality of

- 17 computer boards, said messages received into pre-allocated

- 18 message buffers on said computer boards, said pre-allocated

- 19 message buffers pointed to by a descriptor ring,

- wherein de-coupling of communications between multiple

- 21 sending computer boards attempting to access a common

- 22 receiving computer board is achieved.

- 24 2. The method of claim 1 wherein said sending step for a

- 25 computer board comprises:

- determining the message type of a message to be sent

- 27 to a receiving computer board;

- indexing into a send table to determine the identity

- 29 of the receiving computer board;

1 obtaining board descriptor data for the receiving 2 computer board; having the DMA controller and not the processor 3 transfer the message to a pre-allocated buffer on the 4 5 receiving computer board; having the DMA controller read back a descriptor ring 6 7 address for the next message buffer on the receiving computer board; and 8 having the DMA controller interrupt the receiver on a 9 receiving computer board in order to notify a receiving 10 computer board that a message has been placed into a 11 message buffer on the receiving computer board. 12 13 14 The method of claim 2 wherein said send table is 3. 15 comprised of bit array in which each bit corresponds to a 16 processor number for each computer board. 17 18 The method of claim 2 wherein said board descriptor data for a computer board is comprised of information 19 including an entry for the computer board, how to interrupt 20 the computer board, the address of the computer board in 21 22 its own processor space, the address of the computer board on the bus, and the type of the computer board. 23 24 25 The method of claim 2 wherein said having the DMA 26 controller transfer the message to a pre-allocated buffer on the receiving computer board is achieved via DMA 27 28 chaining. 29

- 1 6. The method of claim 5 wherein said having the DMA

- 2 controller transfer the message to a pre-allocated buffer

- 3 on the receiving computer board is achieved via DMA

- 4 chaining utilizing write commands only.

5

- 6 7. The method of claim 1 wherein said receiving step for a

- 7 computer board comprises:

- 8 searching the descriptor ring for a full message

- 9 buffer containing a received message, said descriptor ring

- 10 corresponding to a sending computer board;

- indexing into a receive table to obtain a list of

- 12 virtual queues that have registered for the received

- 13 message;

- 14 relaying the received message, via pointer

- 15 manipulation, from the message buffer to the virtual queues

- 16 that have registered for the received message; and

- 17 replenishing the descriptor ring with an empty message

- 18 buffer.

19

- 20 8. The method of claim 7 wherein a plurality of descriptor

- 21 rings corresponding to the other computer boards are

- 22 implemented on a computer board.

- 24 9. A method of backplane messaging between a sending

- 25 computer board having a processor and a receiving computer

- 26 board having a processor that are connected via a bus, the

- 27 sending computer board including a DMA controller, said

- 28 method comprising:

- on the sending computer board:

| 1  | determining the message type of a message to      |

|----|---------------------------------------------------|

| 2  | be sent to the receiving computer board;          |

| 3  | indexing into a send table to determine the       |

| 4  | identity of the receiving computer board;         |

| 5  | obtaining board descriptor data for the           |

| 6  | receiving computer board;                         |

| 7  | having the DMA controller and not the             |

| 8  | sending board processor transfer the message to a |

| 9  | pre-allocated buffer on the receiving computer    |

| 10 | board;                                            |

| 11 | having the DMA controller read back a             |

| 12 | descriptor ring address for the next message      |

| 13 | buffer on the receiving computer board; and       |

| 14 | having the DMA controller interrupt a             |

| 15 | receiver on the receiving computer board in order |

| 16 | to notify a receiving computer board that a       |

| 17 | message has been placed into a message buffer on  |

| 18 | the receiving computer board; and                 |

| 19 | on the receiving computer board:                  |

| 20 | searching a descriptor ring for a full            |

| 21 | message buffer containing a received message,     |

| 22 | said descriptor ring corresponding to the sending |

| 23 | computer board;                                   |

| 24 | indexing into a receive table to obtain a         |

| 25 | list of virtual queues that have registered for   |

| 26 | the received message;                             |

| 27 | relaying the received message, via pointer        |

| 28 | manipulation, from the message buffer to the      |

| 29 | virtual queues that have registered for the       |

| 30 | received message; and                             |

| 1   | replenishing the descriptor ring with an                  |

|-----|-----------------------------------------------------------|

| 2   | empty message buffer.                                     |

| 3   |                                                           |

| 4   | 10. On a computer board having a DMA controller and a     |

| 5   | processor, a method of sending a message over a bus, said |

| 6   | method comprising:                                        |

| 7   | determining the message type of a message to be sent      |

| 8   | to a receiving computer board;                            |

| 9   | indexing into a send table to determine the identity      |

| LO  | of the receiving computer board;                          |

| L1  | obtaining board descriptor data for the receiving         |

| L2  | computer board;                                           |

| L3  | having the DMA controller and not the processor           |

| L 4 | transfer the message to a pre-allocated buffer on the     |

| L5  | receiving computer board;                                 |

| L6  | having the DMA controller read back a descriptor ring     |

| L7  | address for the next message buffer on the receiving      |

| L8  | computer board; and                                       |

| L9  | having the DMA controller interrupt a receiver on the     |

| 20. | receiving computer board in order to notify a receiving   |

| 21  | computer board that a message has been placed into a      |

| 22  | message buffer on the receiving computer board.           |

| 23  |                                                           |

| 24  | 11. On a computer board having a processor, a method of   |

| 25  | receiving a message from a bus, said method comprising:   |

| 26  | searching a descriptor ring for a full message buffer     |

| 27  | containing a received message;                            |

| 28  | indexing into a receive table to obtain a list of         |

| 29  | virtual queues that have registered for the received      |

| 30  | message;                                                  |

| 1  | relaying the received message, via pointer                  |

|----|-------------------------------------------------------------|

| 2  | manipulation, from the message buffer to the virtual queues |

| 3  | that have registered for the received message; and          |

| 4  | replenishing the descriptor ring with an empty message      |

| 5  | buffer.                                                     |

| 6  |                                                             |

| 7  | 12. A system for backplane messaging among a plurality of   |

| 8  | computer boards connected via a bus, each computer board    |

| 9  | including a processor and a DMA controller and each         |

| 10 | computer board capable of sending and receiving messages,   |

| 11 | said system comprising:                                     |

| 12 | means for initializing said plurality of computer           |

| 13 | boards, said initialization for the purpose of preparing    |

| 14 | each computer board to communicate with the other computer  |

| 15 | boards;                                                     |

| 16 | means for sending messages, utilizing a the DMA             |

| 17 | controller included on the computer board and not the       |

| 18 | processor of the computer board, from any one of the        |

| 19 | plurality of computer boards to any other of the plurality  |

| 20 | of computer boards; and                                     |

| 21 | means for receiving messages on any one of the              |

| 22 | plurality of computer boards sent from any other of the     |

| 23 | plurality of computer boards, said messages received into   |

| 24 | pre-allocated message buffers on said computer boards, said |

| 25 | pre-allocated message buffers pointed to by a descriptor    |

| 26 | ring,                                                       |

| 27 | wherein de-coupling of communications between multiple      |

| 28 | sending computer boards attempting to access a common       |

| 29 | receiving computer board is achieved.                       |

| 30 |                                                             |

1 13. The system of claim 12 wherein said means for sending

- 2 comprises:

- 3 means for determining the message type of a message to

- 4 be sent to a receiving computer board;

- 5 means for indexing into a send table to determine the

- 6 identity of the receiving computer board;

- 7 means for obtaining board descriptor data for the

- 8 receiving computer board;

- 9 means for having the DMA controller and not the

- 10 processor transfer the message to a pre-allocated buffer on

- 11 the receiving computer board;

- means for having the DMA controller read back a

- 13 descriptor ring address for the next message buffer on the

- 14 receiving computer board; and

- means for having the DMA controller interrupt the

- 16 receiver on a receiving computer board in order to notify a

- 17 receiving computer board that a message has been placed

- 18 into a message buffer on the receiving computer board.

- 19

- 20 14. The system of claim 13 wherein said send table is

- 21 comprised of bit array in which each bit corresponds to a

- 22 processor number for each computer board.

- 23

- 24 15. The system of claim 13 wherein said board descriptor

- 25 data for a computer board is comprised of information

- 26 including an entry for the computer board, how to interrupt

- 27 the computer board, the address of the computer board in

- 28 its own processor space, the address of the computer board

- 29 on the bus, and the type of the computer board.

- 30

- 1 16. The system of claim 13 wherein said means for having

- 2 the DMA controller transfer the message to a pre-allocated

- 3 buffer on the receiving computer board is achieved via DMA

- 4 chaining.

5

- 6 17. The system of claim 16 wherein said means for having

- 7 the DMA controller transfer the message to a pre-allocated

- 8 buffer on the receiving computer board is achieved via DMA

- 9 chaining utilizing write commands only.

10

- 11 18. The system of claim 12 wherein said means for

- 12 receiving comprises:

- means for searching the descriptor ring for a full

- 14 message buffer containing a received message, said

- 15 descriptor ring corresponding to a sending computer board;

- means for indexing into a receive table to obtain a

- 17 list of virtual queues that have registered for the

- 18 received message;

- means for relaying the received message, via pointer

- 20 manipulation, from the message buffer to the virtual queues

- 21 that have registered for the received message; and

- 22 means for replenishing the descriptor ring with an

- 23 empty message buffer.

24

- 25 19. The system of claim 18 wherein a plurality of

- 26 descriptor rings corresponding to the other computer boards

- 27 are implemented on a computer board.

- 29 20. A system for backplane messaging between a sending

- 30 computer board having a processor and a receiving computer

| Τ  | board naving a processor that are connected via a bus, the |

|----|------------------------------------------------------------|

| 2  | sending computer board including a DMA controller, said    |

| 3  | system comprising:                                         |

| 4  | on the sending computer board:                             |

| 5  | means for determining the message type of a                |

| 6  | message to be sent to the receiving computer               |

| 7  | board;                                                     |

| 8  | means for indexing into a send table to                    |

| 9  | determine the identity of the receiving computer           |

| 10 | board;                                                     |

| 11 | means for obtaining board descriptor data                  |

| 12 | for the receiving computer board;                          |

| 13 | means for having the DMA controller and not                |

| 14 | the sending board processor transfer the message           |

| 15 | to a pre-allocated buffer on the receiving                 |

| 16 | computer board;                                            |

| 17 | means for having the DMA controller read                   |

| 18 | back a descriptor ring address for the next                |

| 19 | message buffer on the receiving computer board;            |

| 20 | and                                                        |

| 21 | means for having the DMA controller                        |

| 22 | interrupt a receiver on the receiving computer             |

| 23 | board in order to notify a receiving computer              |

| 24 | board that a message has been placed into a                |

| 25 | message buffer on the receiving computer board;            |

| 26 | and                                                        |

| 27 | on the receiving computer board:                           |

| 28 | means for searching a descriptor ring for a                |

| 29 | full message buffer containing a received                  |

| 1  | message, said descriptor ring corresponding to              |

|----|-------------------------------------------------------------|

| 2  | the sending computer board;                                 |

| 3  | means for indexing into a receive table to                  |

| 4  | obtain a list of virtual queues that have                   |

| 5  | registered for the received message;                        |

| 6  | means for relaying the received message, via                |

| 7  | pointer manipulation, from the message buffer to            |

| 8  | the virtual queues that have registered for the             |

| 9  | received message; and                                       |

| 10 | means for replenishing the descriptor ring                  |

| 11 | with an empty message buffer.                               |

| 12 |                                                             |

| 13 | 21. On a computer board having a DMA controller and a       |

| 14 | processor, a system for sending a message over a bus, said  |

| 15 | system comprising:                                          |

| 16 | means for determining the message type of a message to      |

| 17 | be sent to a receiving computer board;                      |

| 18 | means for indexing into a send table to determine the       |

| 19 | identity of the receiving computer board;                   |

| 20 | means for obtaining board descriptor data for the           |

| 21 | receiving computer board;                                   |

| 22 | means for having the DMA controller and not the             |

| 23 | processor transfer the message to a pre-allocated buffer on |

| 24 | the receiving computer board;                               |

| 25 | means for having the DMA controller read back a             |

| 26 | descriptor ring address for the next message buffer on the  |

| 27 | receiving computer board; and                               |

| 28 | means for having the DMA controller interrupt a             |

| 29 | receiver on the receiving computer board in order to notify |

1 a receiving computer board that a message has been placed

2 into a message buffer on the receiving computer board.

3

- 4 22. On a computer board having a processor, a system for

- 5 receiving a message from a bus, said system comprising:

- 6 means for searching a descriptor ring for a full

- 7 message buffer containing a received message;

- 8 means for indexing into a receive table to obtain a

- 9 list of virtual queues that have registered for the

- 10 received message;

- 11 means for relaying the received message, via pointer

- 12 manipulation, from the message buffer to the virtual queues

- 13 that have registered for the received message; and

- 14 means for replenishing the descriptor ring with an

- 15 empty message buffer.

- 17 23. A computer program product for backplane messaging

- 18 among a plurality of computer boards connected via a bus,

- 19 each computer board including a processor and a DMA

- 20 controller and each computer board capable of sending and

- 21 receiving messages, the computer program product having a

- 22 medium with a computer program embodied thereon, the

- 23 computer program product comprising:

- 24 computer program code for initializing said plurality

- 25 of computer boards, said initialization for the purpose of

- 26 preparing each computer board to communicate with the other

- 27 computer boards;

- computer program code for sending messages, utilizing

- 29 the DMA controller included on the computer board and not

- 30 the processor of the computer board, from any one of the

1 plurality of computer boards to any other of the plurality of computer boards; and 2 computer program code for receiving messages on any 3 one of the plurality of computer boards sent from any other 4 of the plurality of computer boards, said messages received 5 into pre-allocated message buffers on said computer boards, 6 7 said pre-allocated message buffers pointed to by a 8 descriptor ring, 9 wherein de-coupling of communications between multiple sending computer boards attempting to access a common 10 receiving computer board is achieved. 11 12 The computer program product of claim 23 wherein said 13 computer program code for sending comprises: 14 computer program code for determining the message type 15 of a message to be sent to a receiving computer board; 16 17 computer program code for indexing into a send table 18 to determine the identity of the receiving computer board; computer program code for obtaining board descriptor 19 data for the receiving computer board; 20 computer program code for having the DMA controller 21 22 and not the processor transfer the message to a preallocated buffer on the receiving computer board; 23 24 computer program code for having the DMA controller read back a descriptor ring address for the next message 25 26 buffer on the receiving computer board; and 27 computer program code for having the DMA controller 28 interrupt the receiver on a receiving computer board in

order to notify a receiving computer board that a message

1 has been placed into a message buffer on the receiving

2 computer board.

3

4 25. The computer program product of claim 24 wherein said

- 5 send table is comprised of bit array in which each bit

- 6 corresponds to a processor number for each computer board.

7

- 8 26. The computer program product of claim 24 wherein said

- 9 board descriptor data for a computer board is comprised of

- 10 information including an entry for the computer board, how

- 11 to interrupt the computer board, the address of the

- 12 computer board in its own processor space, the address of

- 13 the computer board on the bus, and the type of the computer

- 14 board.

15

- 16 27. The computer program product of claim 24 wherein said

- 17 computer program code for having the DMA controller

- 18 transfer the message to a pre-allocated buffer on the

- 19 receiving computer board is achieved via DMA chaining.

20

- 21 28. The computer program product of claim 27 wherein said

- 22 computer program code for having the DMA controller

- 23 transfer the message to a pre-allocated buffer on the

- 24 receiving computer board is achieved via DMA chaining

- 25 utilizing write commands only.

- 27 29. The computer program product of claim 23 wherein said

- 28 computer program code for receiving comprises:

- 29 computer program code for searching the descriptor

- 30 ring for a full message buffer containing a received

| 1  | message, said descriptor ring corresponding to a sending    |

|----|-------------------------------------------------------------|

| 2  | computer board;                                             |

| 3  | computer program code for indexing into a receive           |

| 4  | table to obtain a list of virtual queues that have          |

| 5  | registered for the received message;                        |

| 6  | computer program code for relaying the received             |

| 7  | message, via pointer manipulation, from the message buffer  |

| 8  | to the virtual queues that have registered for the received |

| 9  | message; and                                                |

| 10 | computer program code for replenishing the descriptor       |

| 11 | ring with an empty message buffer.                          |

| 12 |                                                             |

| 13 | 30. The computer program product of claim 29 wherein a      |

| 14 | plurality of descriptor rings corresponding to the other    |

| 15 | computer boards are implemented on a computer board.        |

| 16 |                                                             |

| 17 | 31. A computer program product for backplane messaging      |

| 18 | between a sending computer board having a processor and a   |

| 19 | receiving computer board having a processor that are        |

| 20 | connected via a bus, the sending computer board including a |

| 21 | DMA controller, the computer program product having a       |

| 22 | medium with a computer program embodied thereon, said       |

| 23 | computer program product comprising:                        |

| 24 | on the sending computer board:                              |

| 25 | computer program code for determining the                   |

| 26 | message type of a message to be sent to the                 |

| 27 | receiving computer board;                                   |

| 28 | computer program code for indexing into a                   |

| 29 | send table to determine the identity of the                 |

| 30 | receiving computer board;                                   |

| 1  | computer program code for obtaining board         |

|----|---------------------------------------------------|

| 2  | descriptor data for the receiving computer board; |

| 3  | computer program code for having the DMA          |

| 4  | controller and not the sending board processor    |

| 5  | transfer the message to a pre-allocated buffer on |

| 6  | the receiving computer board;                     |

| 7  | computer program code for having the DMA          |

| 8  | controller read back a descriptor ring address    |

| 9  | for the next message buffer on the receiving      |

| 10 | computer board; and                               |

| 11 | computer program code for having the DMA          |

| 12 | controller interrupt a receiver on the receiving  |

| 13 | computer board in order to notify a receiving     |

| 14 | computer board that a message has been placed     |

| 15 | into a message buffer on the receiving computer   |

| 16 | board; and                                        |

| 17 | on the receiving computer board:                  |

| 18 | computer program code for searching a             |

| 19 | descriptor ring for a full message buffer         |

| 20 | containing a received message, said descriptor    |

| 21 | ring corresponding to the sending computer board; |

| 22 | computer program code for indexing into a         |

| 23 | receive table to obtain a list of virtual queues  |

| 24 | that have registered for the received message;    |

| 25 | computer program code for relaying the            |

| 26 | received message, via pointer manipulation, from  |

| 27 | the message buffer to the virtual queues that     |

| 28 | have registered for the received message; and     |

| 29 | computer program code for replenishing the        |

| 30 | descriptor ring with an empty message buffer.     |

1 32. On a computer board having a DMA controller and a 2 processor, a computer program product for sending a message 3 over a bus, the computer program product having a medium 4 with a computer program embodied thereon, said computer 5 6 program product comprising: computer program code for determining the message type 7 of a message to be sent to a receiving computer board; 8 computer program code for indexing into a send table 9 to determine the identity of the receiving computer board; 10 computer program code for obtaining board descriptor 11 12 data for the receiving computer board; computer program code for having the DMA controller 13 and not the processor transfer the message to a pre-14 allocated buffer on the receiving computer board; 15 16 computer program code for having the DMA controller read back a descriptor ring address for the next message 17 buffer on the receiving computer board; and 18 computer program code for having the DMA controller 19 interrupt a receiver on the receiving computer board in 20 21 order to notify a receiving computer board that a message 22 has been placed into a message buffer on the receiving 23 computer board. 24 33. On a computer board having a processor, a computer 25 program product for receiving a message from a bus, the 26 computer program product having a medium with a computer 27 program embodied thereon, said computer program product 28 29 comprising:

| 1  | computer program code for searching a descriptor ring       |

|----|-------------------------------------------------------------|

| 2  | for a full message buffer containing a received message;    |

| 3  | computer program code for indexing into a receive           |

| 4  | table to obtain a list of virtual queues that have          |

| 5  | registered for the received message;                        |

| 6  | computer program code for relaying the received             |

| 7  | message, via pointer manipulation, from the message buffer  |

| 8  | to the virtual queues that have registered for the received |

| 9  | message; and                                                |

| 10 | computer program code for replenishing the descriptor       |

| 11 | ring with an empty message buffer.                          |

| 12 |                                                             |

| 13 | 34. A computer board for sending a message over a bus       |

| 14 | comprising:                                                 |

| 15 | a send table including identity information pertaining      |

| 16 | to at least one receiving computer board;                   |

| 17 | a processor for:                                            |

| 18 | determining the message type of a message to                |

| 19 | be sent to said at least one receiving computer             |

| 20 | board;                                                      |

| 21 | indexing into said send table to determine                  |

| 22 | the identity of said at least one receiving                 |

| 23 | computer board;                                             |

| 24 | obtaining board descriptor data for said at                 |

| 25 | least one receiving computer board; and                     |

| 26 | a DMA controller for:                                       |

| 27 | transferring the message to a pre-allocated                 |

| 28 | buffer on said at least one receiving computer              |

| 29 | board;                                                      |

| 1                | reading back a descriptor ring address for                  |

|------------------|-------------------------------------------------------------|

| 2                | the next message buffer on said at least one                |

| 3                | receiving computer board; and                               |

| 4                | interrupting a receiver task on said at                     |

| 5                | least one receiving computer board in order to              |

| 6                | notify said at least one receiving computer board           |

| 7                | that a message has been placed into a message               |

| 8                | buffer on said at least one receiving computer              |

| 9                | board.                                                      |

| LO               |                                                             |

| L1               | 35. The computer board of claim 34 wherein said send table  |

| L2               | is comprised of bit array in which each bit corresponds to  |

| L3               | a processor number for each computer board.                 |

| L 4              |                                                             |

| L5               | 36. The computer board of claim 34 wherein said board       |

| L <sup>-</sup> 6 | descriptor data for a computer board is comprised of        |

| L7               | information including an entry for the computer board, how  |

| L8               | to interrupt the computer board, the address of the         |

| L9               | computer board in its own processor space, the address of   |

| 20               | the computer board on the bus, and the type of the computer |

| 21               | board.                                                      |

| 22               |                                                             |

| 23               | 37. The method of claim 34 wherein said transferring the    |

| 24               | message to a pre-allocated buffer on said at least one      |

| 25               | receiving computer board is achieved via DMA chaining.      |

| 26               |                                                             |

| 27               | 38. The method of claim 37 wherein transferring the         |

| 28               | message to a pre-allocated buffer on said at least one      |

| 29               | receiving computer board is achieved via DMA chaining       |

| 30               | utilizing write commands only.                              |

|                  |                                                             |

| 1  |                                                         |

|----|---------------------------------------------------------|

| 2  | 39. A computer board for receiving a message over a bus |

| 3  | comprising:                                             |

| 4  | a receive table including a list of virtual queues      |

| 5  | that have registered for a received message;            |

| 6  | a processor for:                                        |

| 7  | searching a descriptor ring for a message               |

| 8  | buffer containing a received message;                   |

| 9  | indexing into said receive table to obtain a            |

| 10 | list of virtual queues that have registered for         |

| 11 | the received message;                                   |

| 12 | relaying the received message, via pointer              |

| 13 | manipulation, from the message buffer to the            |

| 14 | virtual queues that have registered for the             |

| 15 | received message; and                                   |

| 16 | replenishing the descriptor ring with an                |

| 17 | empty message buffer.                                   |

2/8

3/8

Pre-allocate a plurality

of Buffers

Initialize at least one

Registration

Process

Descriptor Ring

Boards of Initialization

Notify All Other

and Pre-allocation

4/8

FIG. 6

6/8

FIG. 8

7/8 FIG. 9

8/8 FIG. 10

## INTERNATIONAL SEARCH REPORT

Inte nal Application No PC T/US 00/35455

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 G06F13/28

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

$\begin{array}{ccc} & \text{Minimum documentation searched (classification system followed by classification symbols)} \\ & \text{IPC 7} & \text{G06F} \end{array}$

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, PAJ, INSPEC, COMPENDEX, IBM-TDB

| C. DOCUM   | ENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                             |                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                         | Relevant to claim No. |

| Υ          | US 4 876 664 A (BITTORF BRADLEY J ET AL) 24 October 1989 (1989-10-24) column 1, line 22 - line 30; figures 14,15 column 2, line 15 - line 34 column 19, line 62 -column 20, line 23 column 21, line 65 -column 22, line 20 | 1,12,23               |

| Y          | EP 0 646 876 A (NIPPON TELEGRAPH & TELEPHONE) 5 April 1995 (1995-04-05) page 3, line 15 - line 56; figures 1,2 page 5, line 20 - line 35                                                                                   | 1,12,23               |

| A          | EP 0 899 657 A (IBM) 3 March 1999 (1999-03-03) column 4, line 30 - line 57 column 5, line 14 - line 24; figure 4 column 5, line 49 -column 6, line 2                                                                       | 1-39                  |

| X Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | X Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Special categories of cited documents:</li> <li>"A" document defining the general state of the art which is not considered to be of particular relevance</li> <li>"E" earlier document but published on or after the international filling date</li> <li>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</li> <li>"O" document referring to an oral disclosure, use, exhibition or other means</li> <li>"P" document published prior to the international filling date but later than the priority date claimed</li> </ul> | <ul> <li>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</li> <li>"&amp;" document member of the same patent family</li> </ul> |

| Date of the actual completion of the international search  25 April 2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Date of mailing of the international search report $07/05/2001$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Name and mailing address of the ISA  European Patent Office, P.B. 5818 Patentlaan 2  NL – 2280 HV Rijswijk  Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,  Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Authorized officer  Henneman, P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## INTERNATIONAL SEARCH REPORT

Inte nal Application No

PCT/US 00/35455

|            | tion) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                      |                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                             | Relevant to claim No. |

| A          | WO 91 11768 A (AUSPEX SYSTEMS INC)<br>8 August 1991 (1991-08-08)<br>page 9, line 26 -page 10, line 15<br>page 11, line 10 - line 17<br>page 12, line 26 - line 33<br>page 13, line 8 - line 32 | 1-39                  |

| A          | US 4 449 182 A (KECK DALE R ET AL) 15 May 1984 (1984-05-15) claim 1                                                                                                                            | 1,12,23               |

|            | •                                                                                                                                                                                              |                       |

|            |                                                                                                                                                                                                |                       |

|            |                                                                                                                                                                                                |                       |

|            |                                                                                                                                                                                                |                       |

|            |                                                                                                                                                                                                |                       |