## (19) World Intellectual Property Organization

International Bureau

#

(43) International Publication Date 10 June 2004 (10.06.2004)

**PCT**

(10) International Publication Number  $WO\ 2004/049393\ A2$

(51) International Patent Classification<sup>7</sup>:

H01L

(21) International Application Number:

PCT/IB2003/006178

(22) International Filing Date:

27 November 2003 (27.11.2003)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

0214864

27 November 2002 (27.11.2002) FR

- (71) Applicant (for all designated States except US): S.O.I.TEC SILICON ON INSULATOR TECH-NOLOGIES [FR/FR]; Parc Technologique des Fontaines, Chemin des Franques, F-38190 Bernin (FR).

- (71) Applicants and

- (72) Inventors (for US only): SCHWARZENBACH, Walter [FR/FR]; 19, chemin du Mollard, F-38330 Saint Nazaire les Eymes (FR). WAECHTER, Jean-Marc [FR/FR]; Rue des Vignes, F-38660 Saint-Vincent-de-Mercuze (FR).

- (74) Agents: MARTIN, Jean-Jacques et al.; Cabinet Regimbeau, 20, Rue De Chazelles, F-75847 Paris Cedex 17 (FR).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (BW, GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- of inventorship (Rule 4.17(iv)) for US only

- of inventorship (Rule 4.17(iv)) for US only

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: ANNEALING PROCESS AND DEVICE OF SEMICONDUCTOR WAFER

(57) Abstract: The invention relates to a thermal annealing process for a wafer (T) of material chosen among the semiconductor materials for the purpose of detaching a layer from the said wafer at an embrittlement zone, characterised in that during annealing: -a basic thermal budget is applied to the wafer, said basic thermal budget being slightly inferior to the budget necessary to detach the layer, this budget being distributed in an even manner over the embrittlement zone; -an additional thermal budget is also applied to the wafer locally in a set region of the embrittlement zone so as to initiate the layer in this region. The invention also relates to a device for the implementation of such a process.

20

## ANNEALING PROCESS AND DEVICE OF SEMICONDUCTOR WAFER

This invention relates to a thermal annealing process for a wafer of material chosen among the semiconductor materials for the purpose of detaching a layer from the said wafer at an embrittlement zone.

And the invention also relates to a device purposed to carry out such annealing.

Such processes and devices are already known of.

10 The wafer can be made of a semiconductor material such as silicon.

The SMARTCUT® process is an example of a process implementing such stages.

Moreover it is to be specified that the surface of the layers thus created must generally respect very strict specifications concerning the state of their surface.

It is also common to find roughness specifications that must not exceed 5 Angstroms in terms of rms (root mean square).

Measurements of roughness are generally taken with an AFM (Atomic Force Microscope).

$1x1 \mu m^2$  to  $10x10 \mu m^2$  and less commonly  $50x50 \mu m^2$ , even  $100 \times 100 \, \mu \text{m}^2$ .

Also of note is that it is possible to measure the surface roughness by other methods, in particular via a "haze". This method notably has the advantage of quickly characterising the harmony of the roughness over a whole surface.

5

10

15

25

30

The haze, which is measured in ppm, comes from a process using the optical reflective properties of the surface to be characterised, and corresponds to an optical "background noise" diffused by the surface due to its micro-roughness.

It is also to be noted that if the layers must respect certain roughness values, they must also have a harmonious roughness over their whole surface.

In other terms, what is desired is not only a low mean roughness value, but also an even distribution of roughness over the layer surface.

It is specified that known cleaving processes such 20 as the one disclosed by US 6 013 563 or US 6 048 411 (which are part of the same patent family) do not provide an adequate solution for obtaining an improvement of surface roughness - let alone more specifically an even distribution of surface roughness.

The process of these patents indeed does not address the objective of improving the surface roughness of a layer.

The objective of these patents is a general objective of improving the "precision" of a cutting technique (see e.g. col. 1 l. 65 to col. 2 l. 12) - in fact these patents do not aim at improving the roughness, but more generally at avoiding the formation of multiple

5

cleave fronts during cleaving. It thus appears that the aforementioned processes that allow, according to the state of the art, the detachment following an annealing of a layer from a wafer of semiconductor material, do not always result in layer surface roughness that respects the aforementioned specifications.

Hence, there is a need to improve the controlling of the roughness of detached layers following an annealing.

A goal of the invention is to satisfy this need.

In order to meet this goal, the invention proposes, according to a first aspect, a thermal annealing process for a wafer of material chosen from among the semiconductor materials for the purpose of detaching a layer from the said wafer at an embrittlement zone, characterised in that during annealing:

- a basic thermal budget is applied to the wafer,

said basic thermal budget being slightly inferior to the

budget necessary to detach the layer, this budget being

distributed in an even manner over the embrittlement zone;

- an additional thermal budget is also applied to the wafer locally in a set region of the embrittlement zone so as to initiate the detachment of the layer in this region.

Preferable, but non-restrictive aspects of this 25 process are the following:

- during the application of a global thermal budget, different heating elements, located facing the wafer, are selectively controlled;

- the wafer is substantially placed vertically;

- the wafer is substantially placed horizontally;

- the application of a basic thermal budget is carried out in a first stage, then an application of an additional localised thermal budget is carried out in a second stage;

- the application of a basic thermal budget is carried out substantially simultaneously with the application of an additional localised thermal budget;

- annealing is applied, simultaneously, to several wafers;

- the flow of heat conducting gas is controlled in the different regions of the surface of the layer;

- the said control is carried out using a damper with a diffusion barrier geometry;

- the said control is carried out using a damper 15 with a perforated heating chamber geometry.

According to a second aspect, the invention also proposes a device for the implementation of such a process, characterised in that the device comprises:

- a multiplicity of heating elements designed to 20 face different parts of each wafer to be annealed;

- means of selectively controlling the heating capacity of each heating element;

- means of controlling the distribution of heat conducting gas in the device;

- 25 The preferable, but non-restrictive, aspects of this device are the following:

- the heating elements extend substantially horizontally;

- the heating elements have a general circular 30 form;

- the heating elements are placed one after the other according to a substantially vertical direction;

- the device comprises a wafer reception area into which the wafers are placed substantially vertically for heating purposes;

5

25

- the heating elements surround the wafer reception area;

- the heating elements extend substantially in the same plane;

- the heating elements extend in a concentric manner in relation to each other;

- the device comprises a wafer reception area into which the wafers are placed substantially horizontally for heating purposes;

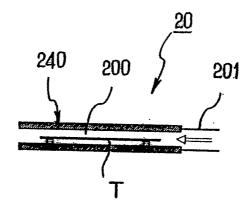

- the said means of controlling the distribution of gas comprise a diffusion damper enabling the flow of gas to be provoked according to a desired configuration, placed facing an opening enabling heat conducting gas to be introduced;

- the damper has a diffusion barrier geometry;

- the damper has a perforated heating chamber geometry;

Other aspects, aims and advantages of the invention will become clearer upon reading the description below of preferable embodiments of the invention, given in reference to the annexed drawings in which:

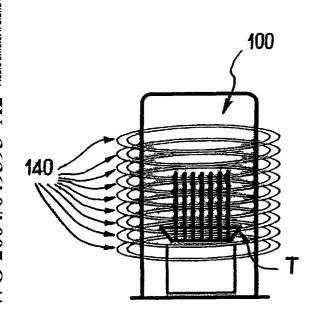

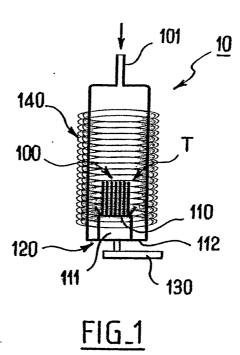

- figure 1 is a global skeletal representation of an annealing device according to the invention corresponding to a first embodiment;

- figure 2 is a detailed skeletal representation of part of this device;

- figure 3 is a representation of the distribution of haze on the surface of a layer, according to an alternative of the state of the art;

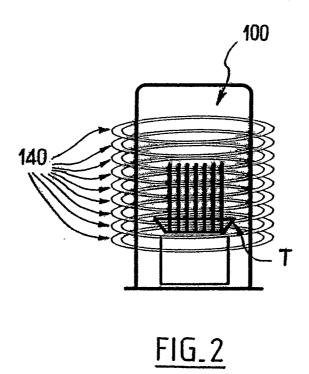

- figure 4 is a skeletal representation of an 5 annealing device according to the invention, corresponding to a second embodiment;

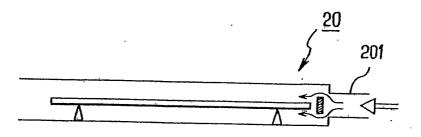

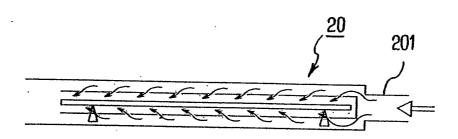

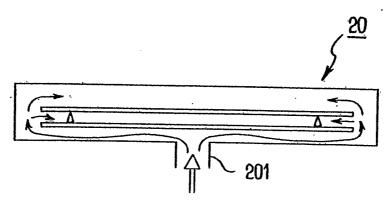

- figures 5a to 5c are skeletal representations of annealing devices according to the invention corresponding to a second embodiment, highlighting different means of orienting, in a desired manner, the flow of heat conducting gas.

10

25

30

In reference to figure 1 a first embodiment of an annealing device according to the invention has been represented.

It is to be noted that the wafers concerned with the rest of this document are wafers made in a semiconductor material such as silicon, and comprising an embrittlement zone.

The embrittlement zone could have been created via 20 implantation.

It extends in the thickness of the wafer at a constant depth (this embrittlement zone corresponds to a surface parallel to the sides of the wafer), thus defining the layer to be detached.

In general, annealing which is the subject of the invention can come under a process of the SMARTCUT® type.

The purpose of annealing which is applied to the wafers is to help in the detachment for each wafer of the layer of material which is defined in the thickness of the wafer by the embrittlement zone.

The device 10 in figure 1 comprises a heating chamber 100 designed to receive one or more wafers T in

order to subject them to annealing according to the invention.

The longitudinal axis of the device 10 is vertical - this device thus resembles a vertical oven.

It is to be noted that the wafers T are placed vertically in this chamber, and not horizontally as commonly known.

The wafers are received in a boat 110 which in turn is supported by a support 111.

10 The support 111 sits on a lid 112 which closes the fire hole 120 of the device.

Means 130 of handling the wafers are also designed for the introduction of the wafers into the device 10 and for their retraction after annealing.

15 The chamber 100 is fitted with an opening 101 located opposite the fire hole 120. A heat conducting gas can be introduced into the chamber via this opening.

A multiplicity of heating elements 140 surround the chamber 100.

20 These heating elements are placed one after the other according to a substantially vertical direction.

These heating elements can for example be electrodes capable of emitting heat when they are supplied with electricity.

It is to be noted that such a device comprises means (not represented in the figures) of rotating the boat supporting the wafers around the longitudinal axis of the device during annealing, as well as means of controlling and of regulating the flow of conducting gas.

These means contribute to providing a harmonious heating of the wafers (this corresponds to the basic

WO 2004/049393

5

15

20

25

30

thermal budget which will be made explicit later in this document).

Figure 2 provides a clearer view of the chamber 100, the wafers T and the heating elements 140 (their number being restricted in this figure for clarity reasons).

Means not represented in the figures allow for selective controlling of the electric supply of each heating element, so as to selectively control the heating capacity of each of these elements.

Thus, the vertical distribution of the thermal budget applied to the wafers during heating can be controlled.

Indeed the applicant observed that the usage of a classical vertical oven into which the wafers would be placed vertically as is represented in figures 1 and 2 produces a vertical temperature gradient.

And such a gradient results in, after the detachment of the layer from each wafer, a vertical gradient of roughness which endangers the harmony of the surface of the layer.

Indeed the roughness distributes generally speaking in horizontal "plies", and is not even on the surface of the detached layer (nor on that of the part of the wafer located on the other side of the embrittlement zone). Such an effect is represented in figure 3.

"Even" shall be understood as characterizing an even, homogeneous distribution.

It is also possible to selectively control groups of heating elements that receive the same set point for the heating temperature.

This is for example the case in an implementation configuration of the invention in which the heating elements are turns adjacent to each other.

In this type of configuration, it can be envisaged to individually control the electric supplies of each turn, or to control the respective electric supply of different groups of turns.

5

10

15

25

In the latter case, due to the closeness of the turns, there exists a hotter zone inside a group of turns supplied in the same manner (this zone being typically in the middle of the group, not taking into account the neighbouring groups of turns).

According to the invention such hot zones of the device can be exploited, for example to apply an additional thermal budget (which will be made explicit later in this document).

By selectively controlling the electric supply of the heating elements 140 the space distribution of the thermal budget applied to the wafers can be controlled.

It is also to be noted in figure 3 that the "plies" 20 are not straight bands, but have an undetermined shape.

This translates the effect of a difference of thermal budget respectively applied to the central region of the wafer and to its side edges.

It is also possible to selectively control the flow rate distribution of conducting gas in a horizontal section of the oven, so as to apply this gas flow rate to different areas of the section with the aim of cancelling out this unevenness observed on a horizontal section of 30 the wafer.

This selective controlling οf the flow distribution of conducting gas can be carried out as a

10

complement of the selective controlling of the electric supply of the heating elements that was mentioned above.

Thus, generally speaking - and as it will be detailed below - the space distribution of the thermal budget applied to the wafers T is controlled via the selective controlling of the electric supply of the different heating elements, and/or via the selective controlling of the flow rate distribution of heat conducting gas on the surface of the wafers.

5

15

25

30

It is thus, in particular, possible to apply to the wafers T a thermal budget that is evenly spaced out over the entire embrittlement zone of each wafer.

This can be visualised for example via haze measurements taken on the surface of the layers after their detachment.

To perform an even budget application to wafers in a type of device as those represented in figures 1 and 2, the lower heating elements are typically supplied with more electricity than the upper elements.

This compensates for the natural tendency of heat to rise in the chamber, and higher temperatures are generated in the upper part of this chamber.

In this way, the thermal budget applied to the wafers is ensured to be even over the entire embrittlement zone of each wafer.

More generally speaking, the selective controlling of the individual electric supplies of the different heating elements enables the precise controlling of the space distribution of the thermal budget applied to the wafers.

This controlling of the space distribution of the thermal budget applied to the wafers is used according to the invention so as to:

• on the one hand, apply to the wafers a thermal budget that is very even over the entire embrittlement zone of each wafer (as described above). This thermal budget (known as basic thermal budget) is controlled so as to be:

5

- from a qualitative point of view, very evenly spaced out over the embrittlement surface of each wafer;

- > and from a quantitative point of view, slightly inferior to the budget necessary to detach the layer from the wafer.

- on the other hand, in addition to this basic

thermal budget, an additional thermal budget, controlled

so as only to be applied to a localised area of each

wafer (creation of a controlled "hot point"). This

additional thermal budget can be applied for example by

selectively supplying electricity to one or more heating

elements, and adding to the aforementioned measures so as

to obtain a harmonious heating of the wafers. It is to be

noted that it is also possible to use a special

distribution of temperature in the annealing device (for

example by controlling the gas flow) so as to apply the

additional thermal budget.

And as will be demonstrated, these two applications of controlled thermal budget can be carried out sequentially one after the other, or substantially simultaneously.

30 The global thermal budget thus applied to the wafers (standard budget + additional budget) is therefore different to that which would be obtained if the wafers

were heated in a vertical oven where they would be placed vertically. Indeed, in this case the thermal budget would have a vertical gradient, as has already been demonstrated.

The global thermal budget thus corresponds to a thermal budget that could possibly have a localised hot point in terms of the embrittlement zone, but does not have any variations spread over a large part of this zone (for example over at least half of a characteristic quantity of this zone - this quantity typically being its diameter in the case of an embrittlement zone in the shape of a disk).

The installation of figures 1 and 2 corresponds to a preferred embodiment of an annealing device according to the invention.

15

20

It is however also possible to carry out such an even application of a global thermal budget with different installations.

Figure 4 thus represents a device 20 which is capable of performing an annealing process according to the invention on a wafer T or on a multiplicity of wafers.

The wafer(s) extends substantially horizontally, in a heating chamber 200.

The wafer is not directly lying on a solid surface.

25 It is supported by discrete holding means which contact only a very small surface of the wafer.

This feature of not contacting a face of the wafer to be cleaved with a solid surface is important, as it allows homogeneous exposition of the wafer to heat.

The chamber is fitted with an opening 201 for the introduction of heat conducting gas.

5

10

15

25

It is to be noted that, if the simplified representation in figure 4 shows a single opening 201 for the introduction of heat conducting gas, it is again possible to envisage provisions to ensure that the flow of this gas on the surface of the wafers does not generate unevenness in the thermal budgets absorbed by the different zones of the surface of each wafer.

In this regard, it can be envisaged, for example, that the device 20 comprises several openings 201 for the introduction of heat conducting gas, these openings being then regularly placed around the periphery of the device.

It is also possible, as an alternative or a complement, to envisage placing on the inside of the device, facing the opening 201 (or each opening 201), diffusion dampers enabling the flow of gas to be provoked according to a desired configuration.

Such dampers thus guarantee that the flow of gas is harmonious over the surface of the wafer.

Such dampers can have different geometries, for 20 example:

- a diffusion barrier geometry interposed between the gas and the wafers, meaning that the gas must go around the diffusion barrier so as to flow whilst facing the wafers (this type of configuration is illustrated in figures 5a and 5c).

- a perforated chamber geometry surrounding the plates, whose openings allow the gas to flow towards the wafers (fig 5b).

In all the embodiments of the invention (in particular in the case of a horizontal oven or a vertical oven) it is thus possible to control the thermal budget applied to the wafers via two principal means:

- the individual controlling of different heating elements;

- the controlling of the flows of heat conducting gas on the different regions of the surface of the wafer.

5 The device 20 comprises heating elements collectively designated by the reference 240.

These heating elements are located on both sides of the wafers.

Indeed, for cleaving the wafers, it is preferable that the heating elements shall be disposed around said wafers, and not located on one side only of the wafers (as this would be the case for a furnace designed not for cleaving, but for e.g. depositing material on one side of the wafer).

The heating elements 240 can consist of a series of individual heating elements (for example electrodes) which extend over the two same horizontal planes (one plane above the wafers, the other plane under the wafers).

Each heating element can thus be a circular element placed concentrically in relation to the other elements, the different elements having different diameters.

The elements are thus also placed concentrically in relation to the wafers when the latter are in the annealing position.

Once again, means (not represented) of selective and individual controlling of each heating element can be envisaged.

30

This guarantees that the global thermal budget applied to the wafers complies with what has been described above.

It is also possible to replace the elements 240 with controlled infrared lamps whose respective electric supplies are individually controlled.

And elements 240 of electrode type (for example in the shape of concentric circular elements) can be combined with infrared lamps that provide supplementary heat capable of:

5

10

- locally adjusting the thermal budget applied to the embrittlement zone so as to constitute an even basic thermal budget;

- but also selectively creating a hot point in this embrittlement zone by locally applying an additional thermal budget.

In all situations, in all the embodiments of the invention, the heating device is capable of:

- carrying out a harmonious heating of the wafers so as to apply an even basic thermal budget to the embrittlement zone of these wafers;

- whilst being able to apply a superior thermal

budget to a particular region of the embrittlement zone,

by creating a "hot point" in the embrittlement zone. This can be obtained:

- either by individually controlling one or more heating elements so as to create such a hot point via the localised increasing of the heating (at a specific time during annealing, or possibly throughout annealing). This corresponds to a preferred implementation of the invention which was already evoked earlier in the document;

> or, according to an alternative implementation of the invention, by exploiting the thermal configuration of the annealing device of the wafers in question:

- ✓ by exploiting a particular flow of heating gas;

- in addition, generally speaking, if the heating elements create, when they are controlled so as to apply an even thermal budget to the embrittlement zones of the wafers, a hot point in this embrittlement zone, it is possible to use this hot point during the annealing process so as to apply the desired additional budget.

5

10

25

While operating, the annealing device according to the invention thus applies an even basic thermal budget to the embrittlement zone of the wafers.

More precisely, this basic thermal budget corresponds to an energetic budget slightly inferior to the budget necessary to detach the layer from the wafer.

However the purpose, within the context of the invention, is not singly to harmonise the thermal budget applied to the wafers.

20 And the basic thermal budget is not designed to completely carry out the detachment of the layer of each wafer.

Indeed, such an even basic thermal budget is applied so as to reach a budget slightly inferior to that which is necessary to carry out the detachment of the layer from each wafer.

In this regard, the localised region having received the additional thermal budget corresponds to an initiating zone of the detachment.

In this initiating zone, the embrittlement zone of each wafer has received the basic thermal budget per surface unit as well as the additional thermal budget.

For each wafer, the sum of these two thermal budgets is sufficient to locally initiate the detachment of the layer from the wafer in the part of the embrittlement zone which corresponds to the initiating zone.

And this layer detachment then spontaneously propagates to the rest of the embrittlement zone which has received, per surface unit, a thermal budget slightly inferior to that needed to carry out the detachment: in these conditions, the solicitation corresponding to the propagation of the initial detachment is sufficient to propagate the detachment.

5

10

15

20

25

And this detachment thus propagates over the entire surface of the embrittlement zone, which leads to the complete detachment of the layer.

The applicant determined that proceeding in such a way led to more harmonious and lower roughness values compared with the case where the sole aim is to render even the thermal budget applied to the embrittlement zone, and to take the budget to a value allowing the detachment of the layer.

The local application of an additional thermal budget so as to create a hot point can be carried out in a constant manner throughout annealing. In this case, the standard budget and the additional budget are applied substantially simultaneously to the wafers.

It is also possible to carry out this local application during a specific stage of the annealing process, for example at the end of annealing.

And it is possible to treat a multiplicity of wafers 30 simultaneously in this manner.

After cleaving, the treated wafer can be taken out of the heating device by the arm of a robot, without

needing any prehension chucks (the arm of the robot can be a simple arm coming under the wafer to be taken, since said wafer is not contacting a solid surface).

It should be noted that the heating device of the invention comprises specific means which allow performing the thermal annealing of the invention.

In this respect, some of the known furnaces comprise some of the specific features of the device of the invention.

As an example, WO 99/49501 discloses a furnace for depositing material on one side of a wafer.

But such device is fundamentally different from the device of the invention, as its function (performing a deposition) induces structural differences.

- 15 Such differences comprise:

- the fact that the device of WO 99/49501 does not comprise heating elements on both sides of the wafer to be treated,

- the fact that in such device, the wafer is lying directly on a solid surface: it is therefore necessary to use means such as a prehension chuck to contact the upper surface of the wafer to retrieve it from the heating device, furthermore, such device does not address (and can not address) a configuration with the wafers disposed vertically (option which remains open in the case of the invention).

EP 291 147 also discloses a furnace.

But such furnace does not allow individual control of different heating elements.

Furthermore, such furnace does not either give any hint to control the flux of heating gases within the furnace.

19

Such furnace is therefore not suited to finely control the heat budget brought locally to the wafer.

EP 1 258 909 discloses a device with means to control the flux of a gas. But such control is very different from the control performed in the case of the invention: what is sought in this prior art device is a mechanical support of the wafer by a gas stream, without needing any other holders.

5

Of course, in the perspective of cleaving a wafer, 10 such support is not desired.

### CLAIMS

5

10

- 1. Thermal annealing process for a wafer (T) of material chosen among the semiconductor materials for the purpose of detaching a layer from the said wafer at an embrittlement zone, characterised in that during annealing:

- a basic thermal budget is applied to the wafer, said basic thermal budget being slightly inferior to the budget necessary to detach the layer, this budget being distributed in an even manner over the embrittlement zone;

- an additional thermal budget is also applied to the wafer locally in a set region of the embrittlement zone so as to initiate the detachment of the layer in this region.

- 2. Process according to the previous claim, characterised in that, during the application of a global thermal budget, different heating elements, located facing the wafer, are selectively controlled.

- 3. Process according to the previous claim,

20 characterised in that the wafer is placed substantially

vertically.

- 4. Process according to claim 2, characterised in that the wafer is placed substantially horizontally.

- 5. Process according to one of the previous claims, characterised in that the application of a basic thermal budget is carried out in a first stage, then an application of an additional localised thermal budget is carried out in a second stage.

- 6. Process according to one of claims 1 to 4, 30 characterised in that the application of a basic thermal

5

15

budget is carried out substantially simultaneously with the application of an additional localised thermal budget.

- 7. Process according to one of the previous claims, characterised in that annealing is applied, simultaneously, to several wafers.

- 8. Process according to one of the previous claims, characterised in that the flow of heat conducting gas is controlled in the different regions of the surface of the layer.

- 9. Process according to the previous claim, characterised in that the said control is carried out using a damper with a diffusion barrier geometry.

- 10. Process according to claim 8, characterised in that the said control is carried out using a damper with a perforated heating chamber geometry.

- 11. Device for the implementation of an annealing process according to one of the previous claims for the annealing of one or more wafers, characterised in that the device comprises:

- a multiplicity of heating elements designed to face different parts of each wafer to be annealed;

- means of selectively controlling the heating capacity of each heating element;

- means of controlling the distribution of heat 25 conducting gas in the device;

- 12. Device according to the previous claim, characterised in that the heating elements extend substantially horizontally.

- 13. Device according to the previous claim,

30 characterised in that the heating elements have a general circular form.

- 14. Device according to the previous claim, characterised in that the heating elements are placed one after the other according to a substantially vertical direction.

- 15. Device according to the previous claim, characterised in that the device comprises a wafer reception area into which the wafers are placed substantially vertically for heating purposes.

- 16. Device according to the previous claim,

10 characterised in that the heating elements surround the wafer reception area.

- 17. Device according to claim 11, characterised in that the heating elements extend substantially in the same plane.

- 18. Device according to the previous claim, characterised in that the heating elements extend in a concentric manner in relation to each other.

- 19. Device according to one of the two previous claims, characterised in that the device comprises a wafer reception area into which the wafers are placed substantially horizontally for heating purposes.

20

25

30

- 20. Device according to one of the nine previous claims, characterised in that the said means of controlling the distribution of gas comprise a diffusion damper enabling the flow of gas to be provoked according to a desired configuration, placed facing an opening enabling heat conducting gas to be introduced.

- 21. Device according to the previous claim, characterised in that the damper has a diffusion barrier geometry.

- 22. Device according to claim 20, characterised in that the damper has a perforated heating chamber geometry.

1/3

2/3

FIG\_3

FIG\_4

3/3

FIG.5a

FIG.5b

FIG.5c